Page 1

Robotisez votre ZX81

P. Gueulle - ETSF - MICRO-SYSTEMES

(extraits)

La mise à l’étude d’extension matérielles pour le ZX81 exige une connaissance sinon totale, du moins

satisfaisante de l’organisation interne de la machine.

Une auréole de mystère a toujours entouré les produits Sinclair, sans doute dans le but de protéger

autant que possible des techniques de pointe hautement vulnérables.C’est compter sans la persévérance

des passionnés.

De patientes recherches, d’innombrables recoupements entre des expériences et des lectures de

publications britanniques permettent maintenant aux membres de ce que certains ont baptisé le «clan

Sinclair», de se faire une idée beaucoup plus nette de ce qui se passe sous le petit capot noir...

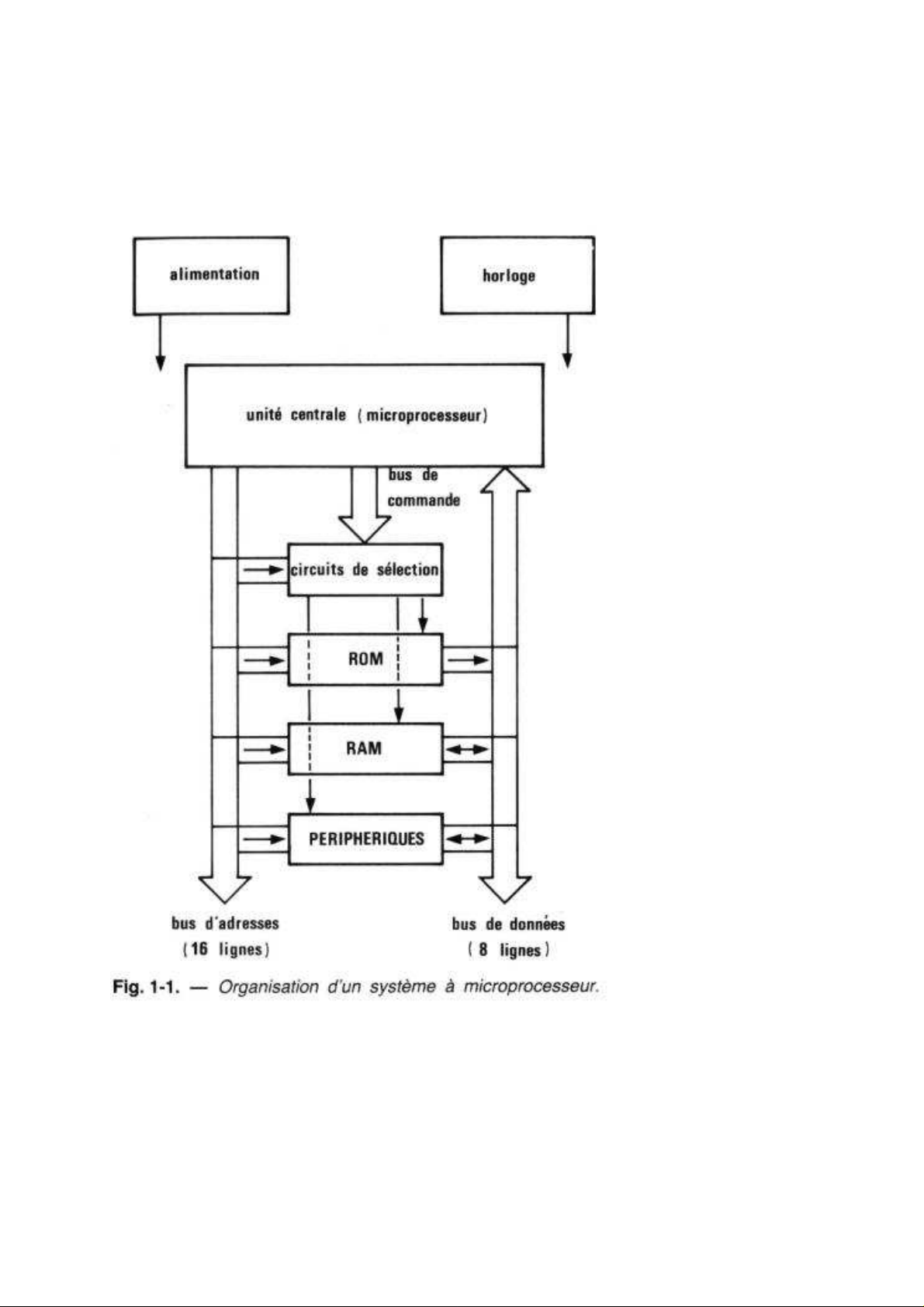

Organisation générale d’un système à microprocesseur

Le ZX 81 n’est qu’un cas particulier de système à microprocesseur, mais quel cas!

Une organisation commune se retrouve dans tous les systèmes microprogrammés, seules des variantes à

vrai dire mineures permettant de les distinguer (fig. 1-1).

Page 2

Si l’on excepte les organes «secondaires» que sont, par exemple, les circuits d’alimentation et d’horloge,

on peut scinder n’importe quel système en trois grandes parties:

· l’unité centrale, c’est-à-dire le microprocesseur lui-même, chargée d’exécuter tous les traitements

d’information proprement dits. Un jeu d’instructions, propre à chaque modèle de microprocesseur, fixe de

façon limitative la panoplie d’opérations élémentaires disponibles. C’est cela, le langage machine que l’on

utilisera...

Page 3

Outre les circuits logiques de traitement, dont le comportement est dicté par les instructions exécutées, le

microprocesseur contient un certain nombre de registres capables de stocker temporairement des

informations.

La plupart des instructions opèrent sur des données présentes dans des registres, et rangent le résultat

également dans un registre.

Le microprocesseur Z 80 A, autour duquel est bâti le ZX 81, est l’une des unités centrales possédant le

plus de registres, et le plus large jeu d’instructions : un sérieux gage de souplesse d’emploi!

· la mémoire se décompose elle-même en deux parties: la mémoire morte ou ROM, qui contient le

programme machine à exécuter ainsi que des données figées (par exemple la forme des caractères utilisés

par le ZX 81, ou encore la valeur de pi). Cette mémoire est programméeune fois pour toutes en usine, et

son contenu ne peut en aucun cas être altéré par l’utilisateur.

La mémoire vive ou RAM sert de «bloc-notes» au microprocesseur, qui y rangera à son gré (ou plutôt au

gré du programme!), les informations que les registres internes ne suffiraient pas à abriter.

Certains petits systèmes ne possèdent pas de RAM, et se contentent des registres. Le ZX 81 de base, lui,

possède 1 K-octet de RAM, soit l’équivalent de 1024 registres.

La mémoire vive est essentiellement volatile:tout son contenu s’efface dès la coupure de l’alimentation,

mais en revanche, on peut aussi bien y lire qu’y écrire des informations.

· les périphériques sont tous les organes qui, connectés à l’unité centrale, servent à communiquer avec

l’extérieur: écran vidéo, clavier, interface cassette, imprimante, cartes d’entrée-sortie, cartes sonores,

poignées de jeu, etc. Ces «accessoires» jouent un rôle essentiel car, sans eux, rien ne permettrait d’agir sur

le microprocesseur qui, lui-même, ne pourrait pas davantage commander quoi que ce soit!

Des liaisons doivent bien sûr exister entre tous ces éléments. Les informations sont constituées de huit

états logiques (1 ou 0) correspondant à la présence ou à l’absence d’une tension de cinq volts.

Huit fils (plus une masse) devraient donc relier chaque circuit extérieur à l’unité centrale.

Il faut également que le microprocesseur, lorsqu’il échange des informations avec, disons, une mémoire,

puisse indiquer à laquelle des «cases» de cette mémoire il s’intéresse : la ROM du ZX 81 comporte 8 192

«cases» ou «adresses», et sa RAM peut en compter 1024 ou beaucoup plus si des extensions lui sont

ajoutées.

En fait, le Z 80 peut distinguer jusqu’à 65 536 adresses différentes (64 fois 1024 soit 64 K adresses).

Moyennant un certain codage (le code binaire), on peut se contenter de seize fils pour véhiculer une

adresse reconnaissable sans ambiguïté.

Pour minimiser, autant que faire se peut, les liaisons déjà touffues nécessaires dans un système à

microprocesseur, on fait appel au principe du BUS

Un BUS est un groupe de lignes desservant, en parallèle, un certain nombre d’organes.

Le Z 80 possède un bus de données à huit lignes, et un bus d’adresses à seize lignes.

Comme il faut à tout prix éviter un mélange inextricable des données relatives à tel ou tel «abonné» du

bus, on utilise le système dit à trois états:

Page 4

Chaque «abonné» (mémoire, périphérique, ou même microprocesseur) est normalement dans un état dit

«haute impédance». Cet état «d’attente» le déconnecte entièrement du bus sur lequel il ne peut ni lire ni

écrire.

Des circuits supplémentaires de sélectionpeuvent ordonner à tel ou tel «abonné» de se connecter au bus,

soit en tant qu’« émetteur», soit en tant que «récepteur» d’informations. En effet, le bus de données peut

véhiculer des informations dans les deux sens : à partir de l’unité centrale ou vers elle.

Comme c’est le microprocesseur qui «décide» s’il veut envoyer ou recevoir des données (en fonction des

instructions qu’il exécute), il possède deux broches nommées RD et WR. Ces broches, qui font partie du

troisième et dernier bus du système, le bus de commande, sont normalement maintenues au «1 » logique

(+5V).

RD passe à zéro lorsque l’unité centrale veut acquérir une information. En même temps, le bus d’adresses

reçoit les «coordonnées» de l’information à aller chercher quelque part sur la «carte mémoire» de 64

K-octets.

Inversement, WR passe à zéro lorsque le bus d’adresses véhicule l’adresse à laquelle doit être acheminée

une information venant du microprocesseur.

Page 5

Les mémoires mortes, qui ne peuvent qu’être lues, possèdent seulement une entrée «de sélection» :

normalement placées dans l’état «haute impédance», elles passent en mode «émission» dès que cette

entrée (nommée CS) est mise à zéro.

Les mémoires vives et les périphériques peuvent fonctionner dans les deux sens lorsque CS est à un, l’état

«haute impédance» est forcé. Lorsque CS passe à zéro, l’état de l’organe dépend de celui d’une seconde

broche nommée WR: si WR est à un, le mode «émission» ou «lecture» est sélectionné. Dans le cas

contraire, on se trouve en mode «réception» ou «écriture». Il est facile de retenir cela en remarquant que

tous les signaux «surlignés» sont actifs à l’état zéro, et en sachant que CS signifie Chip Select, WR Write,

et RD Read : quelques mots anglais qui reviendront souvent!

Il est évidemment vital (parfois au sens propre en ce qui concerne la santé des composants!) qu’un ordre

parfait règne dans les accès au bus de données bidirectionnel.

Où irions-nous, Si l’unité centrale envoyait sur le bus une certaine donnée, pendant que la mémoire vive

serait en mode «écriture» mais la mémoire morte en mode «lecture»? Dans le meilleur des cas, une donnée

invraisemblable se trouverait écrite en RAM, mais des dégrada tions de matériel pourraient aussi se

produire.

Ce n’est pas directement l’unité centrale qui gère les accès au bus de données, sauf pour elle-même.

Mémoires et périphériques sont placés sous les ordres d’un «chef d’orchestre» nommé circuit de sélection.

Ce circuit logique relativement simple (les spécialistes diront combinatoire puisqu’il ne comporte que des

portes, à l’exclusion de toute bascule, registre, compteur...) combine entre eux les signaux WR et RD, et

certaines lignes du bus d’adresses unidirectionnel.

On peut affirmer que, mis à part le choix des différentes mémoires et des divers périphériques, c’est le

schéma du circuit de sélection qui détermine l’organisation matérielle du système complet, ou plan de

mémoire.

En plus de ces signaux, le Z 80 génère également une ligne MREQ, qui passe à zéro quand l’unité centrale

cherche à dialoguer avec de la mémoire (Memory Request).

Parallèlement, il existe aussi un signal IORQ passant à zéro losque le dialogue doit s’établir avec un

périphérique d’entrée-sortie (lnput Output Request).

En fait, de larges recouvrements peuvent s’opérer entre ces deux modes d’échanges de données.

Le cas du ZX 81 est un parfait exemple de ce que des concepteurs habiles peuvent obtenir par un choix

avisé des circuits de sélection : le principal avantage de ces choix est bien sûr une extrême simplicité du

schéma (quatre circuits intégrés, parfois cinq), et donc un prix de vente record, avec le succès que l’on

sait...

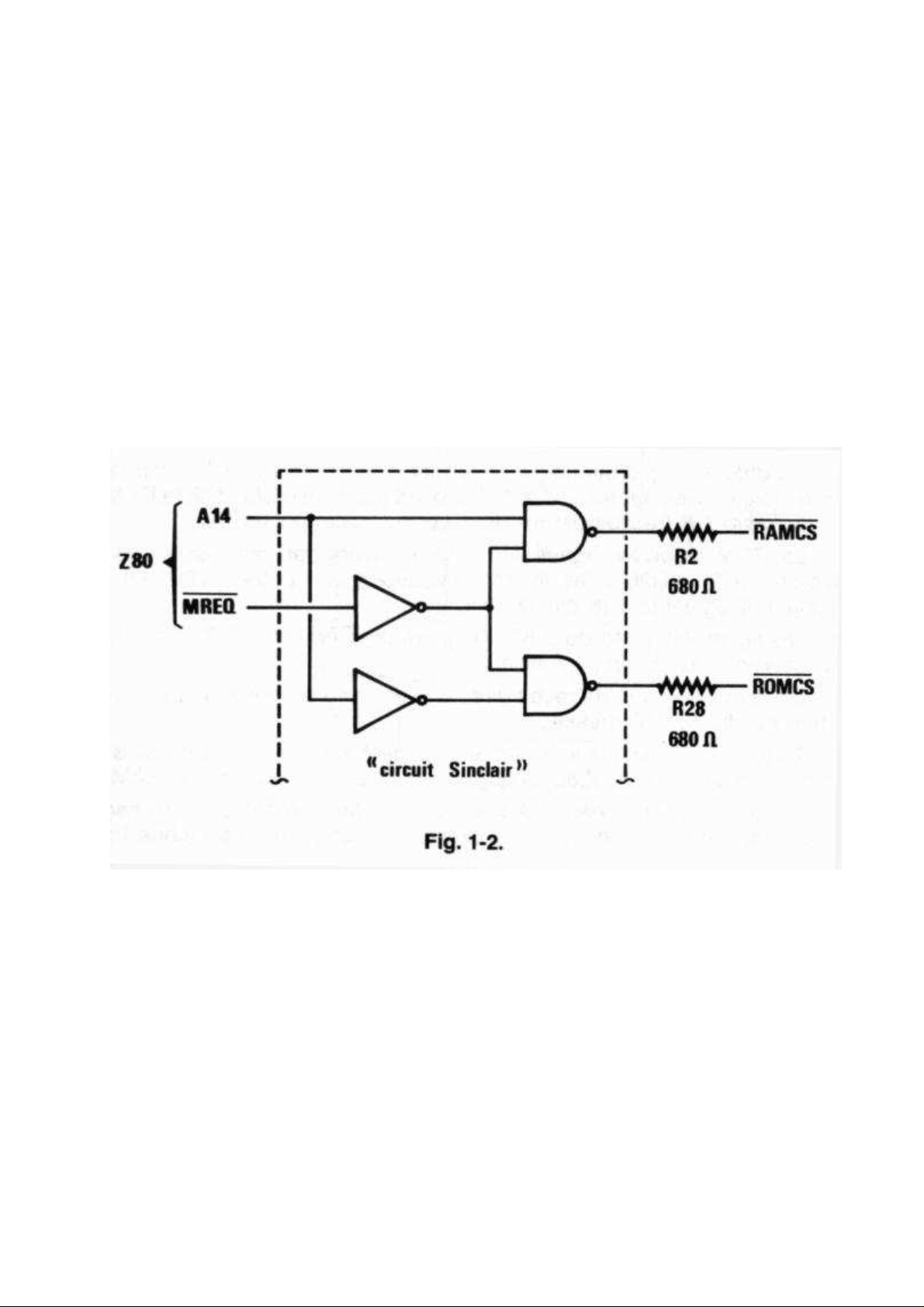

Les sélections mémoire du ZX 81

Page 6

Les circuits de sélection mémoire du ZX 81 sont inclus, comme bien d’autres fonctions de cette machine,

dans le fameux et bien mystérieux «circuit Sinclair».

On peut cependant se faire une idée assez précise de certains des circuits qu’il contient, en examinant le

schéma de cet «ancêtre» du ZX 81 que fut le ZX 80.

Le circuit de cette machine utilisait en effet uniquement des boîtiers TTL courants reliés entre eux par les

pistes du circuit imprimé.

C’est ainsi, par exemple, que nous avons reconstitué le schéma des circuits de sélection mémoire,

reproduit à la figure 1-2.

En tait, c’est purement et simplement la ligne A14 du bus d’adresses qui aiguille le microprocesseur vers

la ROM ou la RAM.

En incorporant l’effet de MREQ, on aboutit donc à la table de vérité de la figure 1-3, qui révèle un «effet

secondaire» intéressant : quel que soit l’état de la ligne WR, le passage à zéro simultané de MREQ et de

A14 entraîne une lecture de la ROM. Or, cette combinaison se présente non seulement lors de l’exécution

d’instructions PEEK sur le contenu de la ROM, mais aussi lors de tentatives de POKE, vouées à l’échec

puisqu’on ne peut écrire en ROM, mais que rien n’empêche de programmer, ne fût-ce que par erreur.

Page 7

Dans ces conditions, l’unité centrale enverrait une donnée sur le bus (l’argument de POKE), mais la

ROM, en mode lecture, en enverrait une autre, très certainement différente! Non seulement une telle

opération est absurde, mais elle risquerait d’endommager le Z 80 ou la ROM.

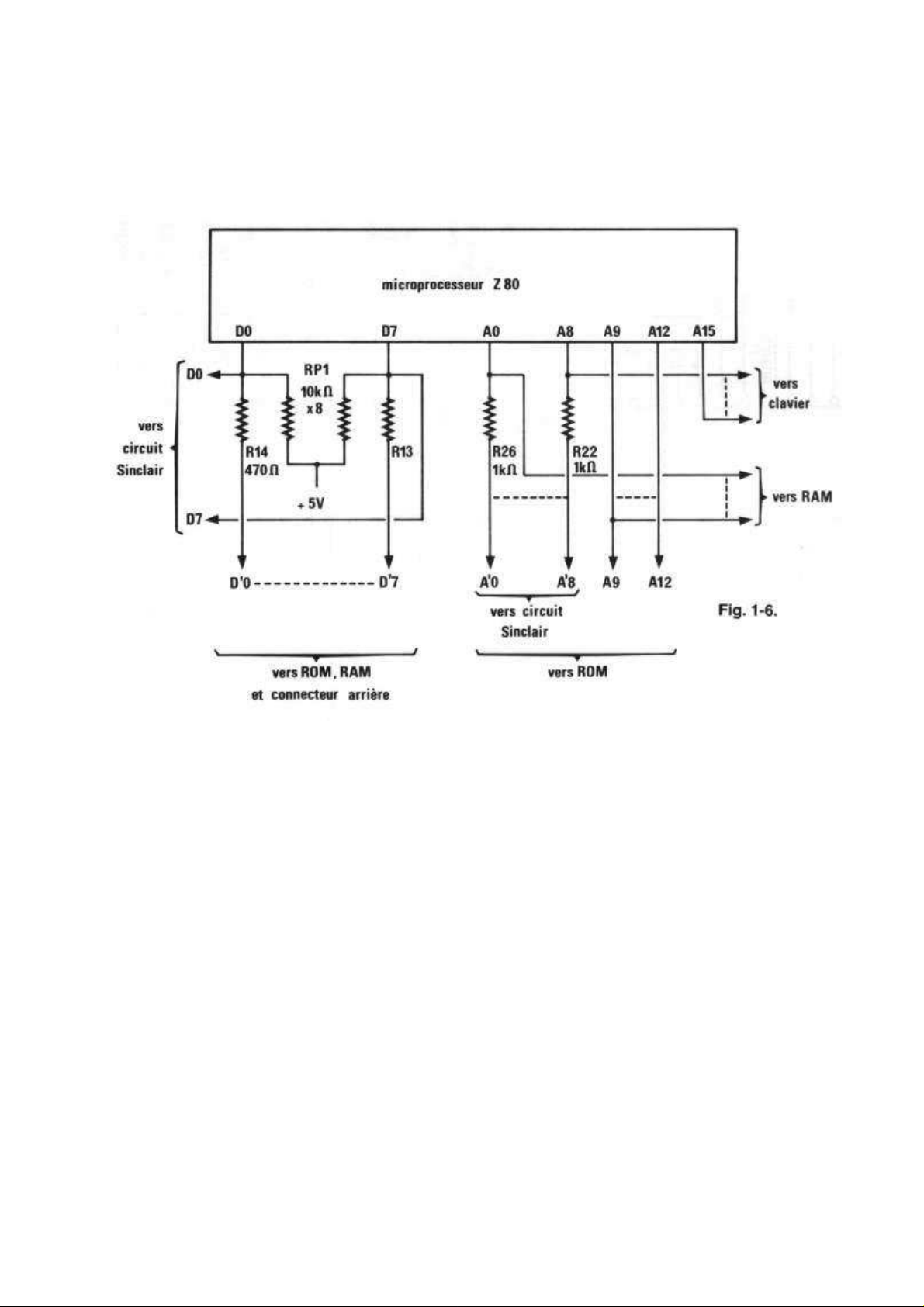

C’est certainement pour cette raison que les ingénieurs de chez Sinclair ont incorporé huit résistances en

série dans le bus de données (R7 à R15, de 470 ohms).

Par contre, le circuit Sinclair accède directement aux lignes de données de l’unité centrale, avec laquelle il

peut donc dialoguer en toute indépendance vis-à-vis des mémoires : ceci a son importance au sein du très

complexe processus d’affichage de l’image vidéo.

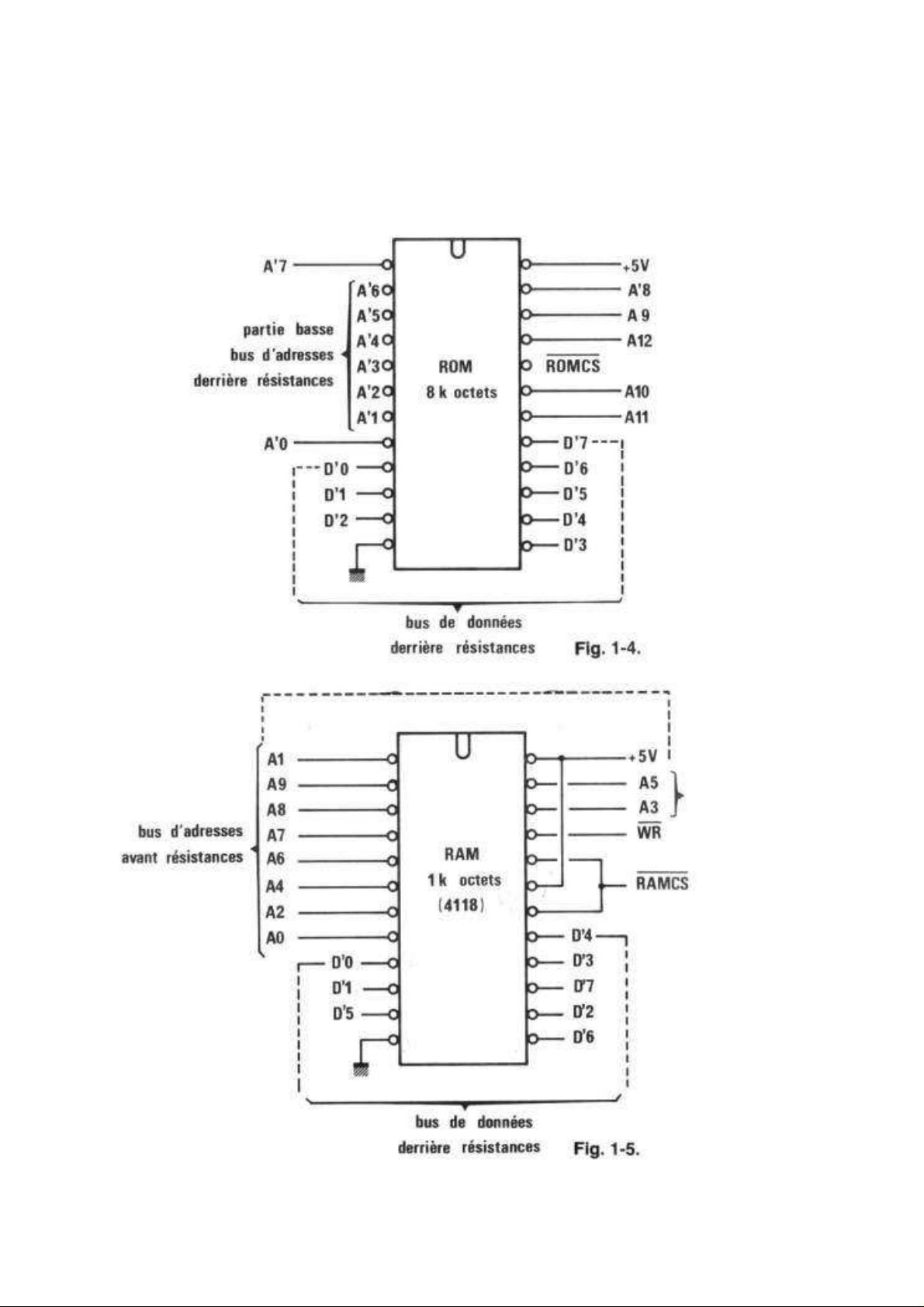

Du côté du bus d’adresses, un artifice semblable est utilisé, comme en témoignent les figures 1-4 et 1-5

(brochages de la ROM et de la RAM), et la figure 1-6 (raccordement des bus au microprocesseur).

Page 8

Page 9

La ROM reçoit les lignes A0 à A8 à travers des résistances de 1 kilo-ohm (R22 à R26). Ces lignes

«résistives» sont notées A0’ à A8’, et rejoignent également le circuit Sinclair.

Les lignes A9 à A12 du Z 80 rejoignent directement la ROM, mais ne desservent pas le circuit Sinclair.

En revanche, la RAM reçoit directement de l’unité centrale les lignes A0 à A9 du bus d’adresses.

Tout cela signifie que le circuit Sinclair peut assigner une adresse à la ROM pendant que le Z 80 dialogue

avec une adresse de la RAM.

Cette particularité est à la base du fonctionnement de l’affichage vidéo: en effet, la génération du signal

TV comporte des tâches trop rapides pour le microprocesseur, et c’est le circuit Sinclair qui s’en charge,

notamment en interrogeant le générateur de caractéres situé en haut de la ROM. Pendant ce temps, le Z

80 exécute des tâches plus lentes, en liaison avec la RAM...

Donc, la ROM reçoit les lignes A0 à A12, avec ou sans résistances:

chacune de ces lignes pouvant prendre deux états distincts (0 ou 1), c’est un total de 213=8192

combinaisons que l’on peut mettre en évidence à ce niveau.

Ce nombre de combinaisons distinctes du bus d’adresses correspond «comme par hasard» à la capacité de

la ROM, 8 K-octets, c’est-à-dire 8 192 cellules (8 x 1024).

Il est donc clair que, pour peu que le signal ROMCS soit mis à zéro, l’unité centrale pourra lire

individuellement n’importe quelle adresse de la ROM.

Page 10

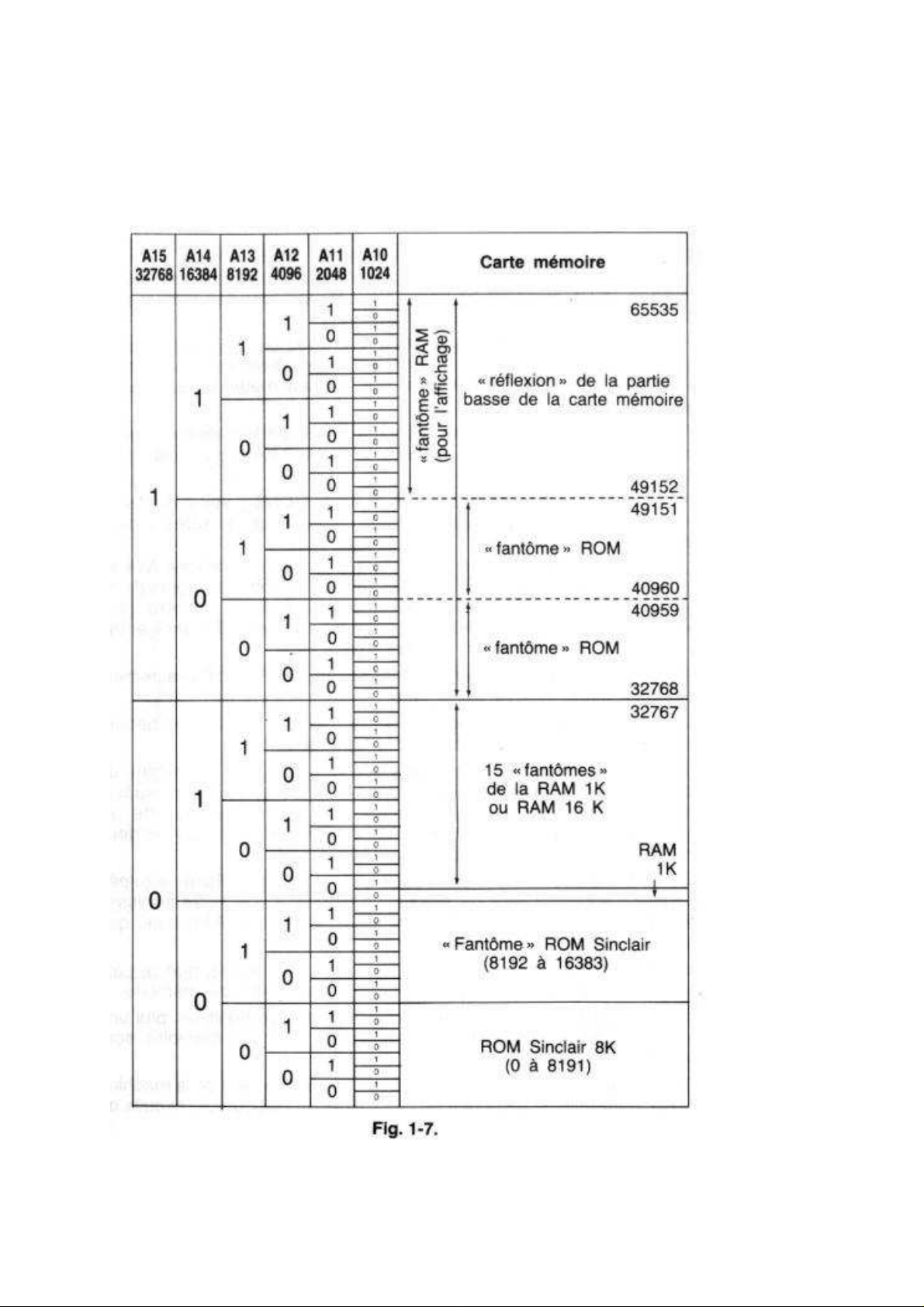

Seulement, ROMCS_ne tient compte que de l’état de la ligne A14 en plus de l’inévitable MREQ. Comme

il existe deux grands segments de 16 K-octets de l’espace mémoire pour lesquels A14 est à zéro (voir

figure 1-7), il est clair que la ROM ne pourra faire aucune différence entre, par exemple, l’adresse 8 191 et

l’adresse 40 959.

Pour ces deux adresses, en effet, les lignes A0 à A12 ont exactement les mêmes états, et A14 est à zéro.

A l’intérieur d’un même segment de 16 K-octets, la ROM ne tiendra pas davantage compte de l’état de la

ligne A13.

Finalement, donc, c’est quatre fois que l’on retrouvera le contenu de la ROM sur la carte mémoire de la

figure 1-7: une première fois «au bon endroit» (de 0 à 8 191) lorsque A15 et A13 sont à zéro, une seconde

fois juste à la suite entre 8 192 et 16 383 (A15 à zéro, mais A13 à un), et deux autres fois de façon

symétrique avec A15 à un.

La RAM de base de 1 K-octet subit un traitement similaire: équipée des lignes d’adresses A0 à A9, elle

peut distinguer 2

10

= 1024 adresses différentes, mais ignore superbement les lignes A10 à A13, ainsi que

A15

Résultat de ce dédain, c’est trente-deux fois, pas moins, que ce petit segment de 1024 octets est

«dédoublé» dans l’espace mémoire.

Le gaspillage est considérable : sur 64 K-octets disponibles, pas une adresse ne reste libre alors que

seulement 9 K de mémoire sont implantés (8 K de ROM et 1 K de RAM)!

En fait, cette libéralité ne nuit en rien au fonctionnement de la machine de base, mais évite le recours à de

complexes (donc coûteux) circuits de sélection.

Page 11

Page 12

Un ordinateur conçu dans le strict respect des «règles de l’art» aurait coûté deux à trois fois plus cher, et

aurait manqué le succès sans précédent qui fut celui du ZX 81...

C’est lorsque l’on cherche à adapter des extensions (de mémoire ou autres) que les choses se compliquent,

car il faut bien dégager de l’espace à la force du poignet!

Fort heureusement, Sinclair a renvoyé les lignes ROMCS et RAMCS sur le connecteur arrière, derrière

leurs résistances de 680 ohms. C’est dire que, de l’extérieur, on peut «forcer» un niveau zéro ou un sur les

mémoires, sans risquer d’endommager le microprocesseur qui, lui, n’en fait qu’à sa tête. Bien

évidemment, ces forçages ne doivent avoir lieu que dans des conditions parfaitement définies.

Le cas le plus simple est celui de l’extension 16 K-octets Sinclair: le câblage interne du module relie

purement et simplement la ligne RAMCS au + 5V, bloquant définitivement le bloc d’origine de 1 K-octet

de RAM.

Dans l’extension, on trouve 16 K-octets de RAM dynamique, ainsi qu’un tout nouveau circuit de sélection

«fabriquant» un signal RAMCS adapté à la configuration 16 K RAM.

1024 octets restent donc «au chômage», mais il existe des solutions pour leur trouver un emploi!

Les extensions de RAM de plus de 16 K-octets doivent éliminer aussi les «fantômes» de la ROM, en

agissant, de façon sélective, sur ROMCS. Des précautions sont à prévoir au-delà de l’adresse 49 151

(extensions 64 K), car les «fantômes supérieurs» de la RAM jouent un rôle dans le processus d’affichage.

Des restrictions d’emploi sont donc à prévoir tout en haut de la RAM.

Les accessoires autres que les extensions de RAM (cartes haute résolution, générateurs de caractères,

cartes sonores, etc.) affectionnent davantage les emplacements correspondant à des fantômes de la ROM,

et tout spécialement au premier (entre 8 192 et 16 383). Il est très facile de libérer cette zone au moyen

d’un simple transistor imposant un niveau haut à la ligne ROMCS lorsque A13 est à un.

Un montage analogue à celui de la figure 1-8se retrouve ainsi dans bon nombre d’accessoires pour le ZX

81.

Page 13

Le petit programme de la figure 1-9 permet, pour sa part, de prendre conscience de l’existence des trois

«fantômes» de la ROM, voire de vérifier leur présence (ou leur absence) lors de l’adaptation d’accessoires.

Cette possibilité d’accès externe à ROMCS et à RAMCS constitue véritablement la base de l’évolutivité

du ZX 81, puisqu’elle reporte sur les éventuels accessoires externes la complexité (donc le coût) des

sélections spéciales nécessaires, dont l’acheteur de la seule machine de base n’a finalement nul besoin.

Le connecteur arrière de l’ordinateur regroupe tous les signaux de l’unité centrale (y compris les bus

complets), plus certaines lignes spécifiques.C’est dire que les rêves les plus fou sont pratiquement tous

permis ...

Les ports d’entrée-sortie

Nous avons vu que l’entité centrale ne peut dialoguer avec la mémoire (ROM ou RAM) que lorsque la

ligne MREQ est à zéro.

De façon tout à fait symétrique; l’unité centrale Z80 peut dialoguer avec 65536 autres "adresses"

lorsque la ligne IORQ est à zéro..On ne parle alors plus de cellule mémoires , mais de ports

d’entrée-sortie.

Il importe de noter que ces "ports" n’ont aucune existence matérielle tant que des circuits appropriés ne

sont pas ajoutés au microprocesseur, pas plus qu’une adresse mémoire ne pourrait être utilisée hors de la

présence d’au moins un boitier de ROM ou de RAM.

En fait, la plupart des instructions d’accès aux ports n’utilisent que la moitié inférieure du bus

d’adresses, ce qui limite à 256 le nombre de ports couramment employés.

Page 14

Les périphériques d’origine du ZX 81 (clavier, écran, interface cassette et imprimante) utilisent déjà

quatre de ces ports, numérotés 251, 253, 254 et 255 (ou FB, FD, FE, FF en hexadécimal).

Seulement, le décodage de sélection est aussi rustique, sinon plus, que celui des sélections mémoire :

l’imprimante, par exemple, utilise le port FB, mais répond en fait à toute mise à zéro simultanée de A2 et

de IORQ. Les ports desservant le générateur d’interruptions destiné à l’affichage, le clavier, et l’interface

cassette ne sont guère mieux lotis.

Le résultat est que seuls seize ports restent disponibles à la discrétion de l’utilisateur. Il s’agit des ports

7,15, 23, 31, 39, 47, 55, 63, 71, 79, 87, 95, 103, 111, 119 et 127.

Bien des possibilités sont offertes par ce nombre, même réduit, d’accès d’entrée-sortie: souvent, un seul

port s’avère même suffisant.

Pour utiliser l’un de ces ports libres, il n’est pas nécessaire, comme dans le cas d’une adresse mémoire,

d’améliorer le décodage: un simple circuit combinatoire doit reconnaître la combinaison adéquate sur les

lignes A0 à A7, ainsi que l’état zéro de la ligne IORQ.

L’opération d’entrée sera déclenchée par la venue à zéro de la ligne RD, alors que c’est WR qui passe à

zéro lorsque le bus contient la donnée que l’unité centrale veut sortir sur le port.

Il est important de remarquer que les échanges d’informations entre le bus et le «milieu extérieur» sont

extrêmement brefs : quelques centaines de nanosecondes (moins d’un millionnième de seconde). En fait,

les transferts de données ne durent que le temps pendant lequel WR ou RD sont à zéro. Comme par

ailleurs un même port peut aussi bien servir à l’entrée ou à la sortie de données, il est clair que les

informations doivent, au niveau du périphérique, être stockées dans des sortes de «registres».

Le milieu extérieur viendra écrire ou lire dans ces registres à son rythme propre, alors que le

microprocesseur fera de même en toute indépendance.

En conséquence, il ne faut pas imaginer qu’il suffit d’appliquer une information sur un port pour que

l’unité centrale en prenne aussitôt connaissance: il faut attendre qu’une lecture du port en question se

produise, et c’est uniquement le programme en cours d’exécution qui en donne l’ordre.

Cette particularité est spécialement nette en ce qui concerne le clavier: lorsque la machine exécute un

programme, le clavier devient sans effet, touche BREAK exceptée, tant qu’une instruction INPUT ou

INKEY$ n’est pas exécutée.

En langage machine, il faut prévoir explicitement un sous-programme de lecture du clavier, faute de

quoi même le BREAK sera inopérant, avec tout ce que cela signifie...

En effet, c’est par interrogation du port FE (254 en décimal) qu’est effectuée la lecture du clavier.

Le clavier du ZX 81

Elément essentiel du faible coût du ZX 81, le clavier « à effleurement» est constitué de sortes de

«circuits imprimés souples» séparés par une feuille souple et isolante percée d’un trou en regard de chaque

touche.

Lorsqu’une pression du doigt est exercée sur une touche, les pastilles conductrices des deux circuits se

Page 15

déforment suffisamment pour venir se toucher à travers le trou. Il s’agit donc d’un contact électrique pur et

simple, comme dans une touche mécanique conventionnelle.

Les quarante touches du clavier n’utilisent que treize fils pour rejoindre les circuits de l’ordinateur, grâce à

une organisation en matrice dont la figure 1-10 donne le détail.

Page 16

Sous réserve de bien respecter ce schéma, rien n’empêche de connecter un clavier à touches mécaniques

à la place de ou en parallèle avec celui d’origine.

Il est par contre plus délicat de construire un clavier pouvant être branché, comme tant d’autres

accessoires, sur le connecteur arrière de l’ordinateur.

Page 17

En effet, Si le raccordement au bus d’adresses ne pose guère de problème (insertion de huit diodes

genre 1N4148), la liaison avec les broches KBD0 à KBD4 du circuit Sinclair n’est pas possible.

Ces broches sont en fait les entrées d’un circuit de port, incorporé dans le circuit Sinclair : à chaque

interrogation du clavier, le microprocesseur amène tour à tour à zéro chacune des lignes A11 à A15, tandis

qu’il interroge le port. Selon la ligne de ce port qui passe à zéro, l’unité centrale peut déterminer laquelle

des cinq touches de la rangée commutée est enfoncée.

Pour reconstituer ce fonctionnement à l’extérieur de la machine, il faudrait réaliser un circuit de port

d’entrée qui, relié aux bus de données, d’adresses, et de commandes, prendrait la place de celui incorporé

dans le circuit Sinclair.

L’opération inverse est d’ailleurs plus facile : brancher des contacts extérieurs en parallèle sur le clavier,

que l’on pourra interroger par de simples instructions INKEY$ (réalisation de poignées de jeu, par

exemple).

Les interruptions du ZX 81

Nous avons vu qu’une information arrivant sur un port n’est prise en compte par l’unité centrale que

selon son bon plaisir, parfois pas du tout Si le programme n’a pas prévu une lecture de ce port au bon

moment.

Or, certaines nouvelles de l’extérieur doivent être prises en considération sans délai : elles sont

prioritaires.

Par exemple, les lignes TV doivent être générées à une cadence parfaitement régulière, faute de quoi les

circuits du récepteur ne pourraient se synchroniser: une image instable apparaîtrait.

Un processus de génération vidéo doit donc démarrer dès réception d’une impulsion de synchronisation,

quitte à interrompre provisoirement l’exécution de tâches moins pressantes.

Tous les microprocesseurs acceptent des INTERRUPTIONS: sur réception d’un signal externe, ils

suspendent immédiatement le travail en cours, vont exécuter un sous-programme dit de traitement de

l’interruption, puis reviennent au programme principal là où ils l’avaient laissé. Ainsi, un périphérique

peut réquisitionner l’unité centrale dès qu’il en a un besoin urgent.

Seulement, la tâche principale peut parfois être encore plus importante que l’interruption. Il existe donc

deux types d’interruptions

Les interruptions masquables ne sont prises en compte qu’avec l’accord du programme principal : deux

instructions machine spéciales permettent de spécifier les segments du programme qui sont prioritaires, et

ceux qui ne le sont pas.

Les interruptions non masquablessont toujours exécutées, quelle que soit la tâche en cours. Elles

bénéficient du plus haut degré de priorité possible:

Page 18

Le microprocesseur Z 80 possède de nombreux modes de traitement des interruptions, utilisés de façon

ingénieuse par le ZX 81, notamment en ce qui concerne l’affichage vidéo. Le circuit Sinclair contient un

générateur d’interruptions pilotant la broche NMI du Z 80 (demande d’interruption non masquable), à une

cadence égale à celle de succession des images sur l’écran TV (25 images par seconde).

Dès la mise à zéro de NMI, le microprocesseur interrompt la tâche en cours, et part exécuter la routine

contenue, dans la ROM, à partir de l’adresse décimale 102. Entre différentes actions de préparation à

l’affichage, ce court sous-programme exécute une instruction HALT.

Cette instruction met la broche HALT à zéro, ce qui se répercute sur la broche WAIT par

l’intermédiaire du transistor TR1 (fig. 1-11).

L’unité centrale attend alors une interruption masquable, réclamée par le circuit Sinclair (dont la broche

10 rejoint l’entrée Ml du Z 80, entrée de demande d’interruption masquable).

C’est cette routine d’interruption masquable, logée en ROM à partir de l’adresse décimale 56, qui

appellera les divers sous-programmes nécessaires à la création d’une image TV, mais seulement Si le ZX

81 est en mode SLOW.

En effet, en mode FAST, les interruptions sont neutralisées (le générateur du circuit Sinclair est mis

hors service), ce qui multiplie par quatre la vitesse de la machine.

En mode SLOW, en effet, le ZX 81 passe 75 % du temps à s’occuper de l’image TV, contre 25 %

seulement à traiter les instructions BASIC...

Il est important de noter que l’appel des routines d’affichage par la routine d’interruption s’opère par

une instruction JP (IX).

De ce fait, en modifiant le contenu du registre IX, on peut dévier le microprocesseur vers des routines

d’affichage programmées en RAM par l’utilisateur.

L’écriture de telles routines est un travail extrêmement complexe, mais offre des possibilités étonnantes

: c’est selon ce procédé que fonctionnent les logiciels haute résolution graphique, qui permettent

d’accéder, sur l’écran, à 256 x 192 points indépendants sans le moindre accessoire matériel!

Page 19

La principale leçon à tirer de ce survol des interruptions du ZX 81 est bien entendu qu’un si large usage

de leurs possibilités ne laisse guère de place à l’utilisateur de ce côté, sauf, à la rigueur, en mode FAST.

Une très bonne connaissance du microprocesseur Z 80 est alors pratiquement indispensable.

L’interface cassette

Les deux prises destinées au raccordement d’un magnétophone à cassette (MIC et EAR) sont raccordées

plus ou moins directement au circuit Sinclair (fig. 1-12).C’est donc lui qui contient les montages

transformant les niveaux logiques émanant du microprocesseur en signaux audio, et inversement.

Le circuit débitant sur la prise MIC (micro) est piloté par le port 255: des effets sonores intéressants

peuvent être obtenus en agissant sur ce port au moyen de routines écrites en langage machine. Les signaux

ainsi créés pourront être enregistrés ou écoutés par l’intermédiaire du magnétophone, mais atteindront

également le récepteur TV, puisque le modulateur vidéo est attaqué par la même broche 16 du circuit

Sinclair.

Page 20

L’écran affichera donc de curieuses formes, tandis que le haut-parleur émettra certaines sonorités,

pourvu que le volume sonore ne soit pas à zéro.

C’est le port 254 qui vient interroger le circuit relié à la prise EAR (écouteur). Mais ce port ne servait-il

pas déjà au décodage du clavier?

En effet, les lignes KBD0 à KBD4 de la matrice du clavier (voir figure 1-10) correspondent bien à ce

port FE.

Seulement, un port peut accueillir jusqu’à huit lignes il en reste donc trois, qui ne sauraient être perdues!

La ligne 5 rejoint la broche 22 du circuit Sinclair, et contrôle donc la présence ou l’absence du strap qui

constitue le moyen de transformer le ZX 81 en une machine adaptée au standard américain de télévision

525 lignes/60 Hz. La ligne 6 passe à un lorsque des données valides entrent en machine par la prise EAR,

alors que la ligne 7 véhicule les données elles-mêmes, sous la forme d’un train de bits série.

Une application possible de cette remarque est la détection de signaux audio quelconques appliqués,

avec un niveau suffisant, à la prise EAR. Une simple interrogation périodique du port FE montrera

immédiatement si un signal est présent ou non.

De très simples routines en langage machine permettront donc à l’amateur imaginatif d’utiliser les

prises cassette très au-delà de leur vocation d’origine.

Les circuits annexes

Même Si ces circuits n’offrent pas d’immenses possibilités de recherche à l’amateur curieux, il est bon

de connaître le fonctionnement sommaire de l’alimentation, de l’horloge, et de la remise à zéro.

L’alimentation secteur, dont le schéma général apparaît à la figure 1-13 est scindée en deux parties: un

bloc secteur aussi simplifié que possible, qui fournit une tension non régulée variant entre 9 et 15 volts

environ.

Des modèles 700 mA et 1,2 A existent, selon que l’ordinateur fonctionne avec ou sans imprimante.

Une régulation à 5 V exactement est opérée dans le ZX 81 lui-même par un classique régulateur «3

pattes» 7805. Quelques condensateurs de découplage judicieusement répartis aux points stratégiques du

circuit complètent le schéma. Comme le 7805 a tendance à chauffer notablement, il peut être bénéfique

d’ajouter un montage pré-régulateur entre le bloc secteur et l’ordinateur (par exemple un régulateur 7808);

on y gagnera en fiabilité.

Le plus important est cependant de noter que cette alimentation travaille déjà non loin de ses limites de

sécurité. Si des accessoires «gourmands» devaient être adjoints, il pourrait s’avérer utile de les alimenter

separément.

Page 21

L’oscillateur d’horloge est incorporé dans le circuit Sinclair, mais utilise un élément de référence

extérieur. Au lieu d’un quartz, classique à ce niveau, un filtre céramique de téléviseur a été choisi en

raison de son coût trés inférieur.La précision de fréquence est moindre, mais encore suffisante.

La fréquence de l’oscillateur sert directement au fonctionnement des sytèmes vidéo du circuit

Sinclair.Un transistor extérieur opère une dernière mise en forme (figure 1-14).

Page 22

Enfin, le petit circuit de la figure 1-15 exploite le fait que la mise à la masse, même brève, de la broche

26 du microprocesseur, fait reprendre à celui-ci l’exécution du programme à partir de l’adresse zéro (le

début de la ROM).C5 étant déchargé à la mise en service du ZX81, la machine démarrera ainsi toujours

dans les conditions voulues.Un bouton de RESET peut éventuellemnt être rajouté ici.

Page 23

Une entrée par la prise cassette

En dehors de son clavier, le ZX 81 ne dispose normalement d’aucun moyen lui permettant de

recevoir des «nouvelles» du monde extérieur. Il existe bien sûr des modules d’entrée-sortie

adaptables, mais cette solution est souvent luxueuse par rapport aux besoins de l’application

envisagée.

Nous allons décrire ici un procédé très simple permettant d’utiliser la prise EAR (magnétophone)

du ZX 81 pour communiquer avec un piogramme en cours de déroulement.

1) A la découverte de la ROM

La mémoire morte (ROM) du ZX 81 contient le programme rédigé en langage machine,

permettant à l’ordinateur d’avoir le comportement que nous lui connaissons. Avec une autre

ROM, peut-être travaillerait-il en FORTH et non plus en BASIC?

Il est extrêmement instructif (et tout aussi difficile!) de désassembler certaines des routines

contenues dans cette partie de la mémoire, et sur le fonctionnement desquelles les fabricants

du ZX gardent un mutisme aussi jaloux que total. On peut ainsi parvenir à savoir que, lorsqu’un

signal BF de niveau suffisant est appliqué à la prise EAR, un octet 255 apparaît sur le port FE

(254) du microprocesseur Z 80.

Ainsi donc, Si nous arrivons à écrire un programme (en BASIC et langage machine) capable

d’aller lire périodiquement ce port, nous pourrons faire recevoir au ZX 81 des "nouvelles de

l’extérieur" autrement que par son clavier.

L’essentiel du problème consiste à ramener au BASIC le contenu du port 254. Le plus rapide est

d’utiliser la variable USR, donc de transiter d’abord par le registre A, puis par les registres B et C. La

figure 3-13 donne le détail de ces opérations, sous la forme de la liste d’assemblage, en code décimal, de

la routine machine utilisée.

Page 24

La figure 3-14, quant à elle, fournit un court programme Basic, capable de charger cette routine dans

une instruction REM, puis de la lancer de façon incessante, tant qu’un signal BF n’aura pas été identifié.A

ce moment seulement, le programme exécutera la ligne 100 et s’arrêtera.

2) Réalisation d’une interface d’entrée

...

Le montage trés simple, dont la figure 3-15 donne le shéma de principe, est capable de fournir, par

simple appui sur un bouton-poussoir, un signal BF parfaitement adapté à l’entrée EAR du ZX81. Par

ailleurs, la puissance disponible est suffisante pour permettre l’attaque simultanée d’un petit haut-parleur

...

17 K-octets pour le prix de 16!

Presque tous les utilisateurs de ZX 81 sont d’accord pour reconnaître qu’en dehors de la tricte initiation

à la programmation, la mise en oeuvre d’un module 16 K RAM (ou plus) s’impose pour la plupart des

utilisations courantes.

Il est intéressant de remarquer que la mise en service d’une extension mémoire déconnecte

automatiquement le boîtier RAM 1 K interne, par forçage à 1 de sa broche de sélection.

Dès lors, pourquoi ne pas tenter de lui redonner vie grâce à un petit montage très simple, qui

Page 25

introduit par la même occasion certains avantages plus que notables...

Organisation de la mémoire du ZX 81

Le ZX 81 est un ordinateur exceptionnellement économique, et ce résultat n’a pu être obtenu

par ses créateurs que grâce à une totale maîtrise des coûts d’étude et de production.

S’il faut reconnaître qu’aucun compromis n’a été accepté sur le plan de la qualité, il est tout

aussi certain que de nombreuses mesures simplificatrices ont été prises lors de la conception

des circuits (voir chapitre 1).

En particulier, le schéma de la partie logique contenue dans le fameux «chip Sinclair» a été

simplifié autant qu’il était humainement possible. Cela explique certaines «bizarreries» dans le

comportement de la machine, qui passent totalement inaperçues lors d’une utilisation «sage»,

mais qui apparaissent lorsque l’on cherche à pousser le ZX dans ses derniers retranchements!

Par exemple, le manuel nous apprend que la mémoire morte (ROM) occupe les adresses

mémoire 0 à 8 191, mais que la mémoire vive (RAM) se place entre 16 384 et 17 407 (ou 32 767 avec le

module 16 K).

Ce «plan d’occupation» laisse dans l’ombre une zone de 8 K-octets comprise entre les adresses 8 192 et

16 383. Une exploration de ce mystérieux intervalle au moyen de commandes PEEK permet de constater

que le contenu de la ROM apparaît une seconde fois entre ces deux

limites.

La raison de ce phénomène tient en ce que le signal de sélection du boîtier ROM (nommé ROMCS) est

dérivé de celui présent sur la ligne d’adresse A14. Seulement, A14 reste à zéro jusqu’à l’adresse 16 383

alors que la ROM se termine à 8191.

Les ingénieurs de chez Sinclair ont visiblement préféré perdre 8 K-octets d’espace mémoire, et

bénéficier ainsi de l’économie de quelques portes dans leur circuit intégré spécifique, à moins

qu’ils n’aient eu une autre idée en attente, telle qu’un BASIC «étendu» de 16 Ko

Quoi qu’il en soit, nous allons découvrir, avec l’aide de la figure 4-1, que cette zone abandonnée n’est

pas forcément perdue pour tout le monde!

Il est indispensable de construire de tels tableaux dès que l’on entreprend des interventions

sur l’organisation de la mémoire d’un ordinateur.

Le microprocesseur Z 80 possède seize «lignes d’adresse» notées A0 à A15, et permettant

donc de sélectionner jusqu’à 64 K adresses. Rien n’empêche de se représenter cette sélection

Page 26

de différentes façons, et notamment en imaginant que les lignes A10 à A15 servent à identifier

un bloc de 1 024 octets parmi les 64 existants, alors que les lignes A0 à A9 servent à «balayer»

les 1 024 octets de chaque bloc ainsi sélectionné.

Ainsi, la ROM 8 K pourrait être imaginée comme composée de huit blocs de 1 024 octets,

identifiés par les combinaisons suivantes de A15, A14, A13, A12, A11 et A10:

000000

000001

000010

000011

000100

000101

000110

000111

Pour sa part, la RAM 1 K serait identifiée uniquement par la combinaison : 010000, alors que le

premier bloc de 1024 octets de la zone inutilisée correspondrait à la combinaison

001000

En réalité, le «chip Sinclair» se contente de sélectionner la ROM lorsque A14 est à zéro, et la

RAM lorsque A14 est à un. Si nous décidions, par un câblage approprié, de modifier ce choix,

nous pourrions «déplacer» le bloc de 1024 octets constitué par le boîtier de RAM, n’importe où

dans la zone adressable par le Z 80, puisque ce boîtier lui-même ne dispose que des lignes

d’adresse A0 à A9 (voir figures 1-5 et 1-6), lesquelles, nous l’avons vu, ne servent qu’à son

«balayage», sans aucun lien avec la place occupée par les 1024 octets dans le «plan

d’occupation mémoire».

Eh bien, c’est exactement le genre d’exercice auquel nous allons nous livrer, avec, nous allons le

découvrir, un certain nombre d’avantages.

La modification proposée

Il aurait été permis de supposer que le bloc 16 K prévu pour augmenter la capacité mémoire du ZX 81

n’était muni, en fait, que de 15 K-octets de ROM venant en complément du 1 K-octet

d’origine.

En réalité, le bloc d’extension contient bien 16 K-octets, mais la mémoire disponible après son

raccordement est toujours de 16 K-octets!

L’explication est simple : par la broche 2A de son connecteur, le module 16 K impose un niveau + 5

volts à la broche RAMCS du boîtier 1 K RAM, ce qui le met complètement hors service. A côté de cela, le

bloc 16 K élabore son propre signal RAMCS à partir des lignes d’adresse du Z 80, dont il dispose en

totalité. Il existe de nombreux avantages à remettre en service, moyennant certains artifices, le boîtier 1K

normalement «laissé pour compte»...

En premier lieu, il n’est pas désagréable de disposer de 17 K-octets pour le prix de 16K!

Cependant, l’intérêt essentiel de la manipulation est qu’il est possible de «déplacer» ce bloc de

1 024 octets «récupérés», pour le placer dans la fameuse zone inutilisée de 8 K-octets. En eftet,

cette zone est entièrement ignorée par le BASIC, et seuls des POKE et des PEEK permettront

de communiquer avec elle, un peu à la manière des espaces mémoire placés au-dessus de

RAMTOP. Comme ces derniers, ce nouveau bloc de RAM ne pourra pas être sauvegardé sur

Page 27

cassette, mais son contenu pourra toujours être transféré, pour les besoins de la cause, dans

une zone accessible à la routine SAVE.

En revanche, le point le plus intéressant est que notre bloc «ajouté» est totalement à l’abri des

procédures d’initialisation du ZX 81.

On sait que le microprocesseur Z 80 commence toujours son premier programme à l’adresse 0,

notamment lors de la mise sous tension du ZX81. On peut appeler ce programme dit

«d’initialisation» en frappant, n’importe quand, la commande suivante

RAND USR 0 newline

De cette façon, on aura tôt fait de se rendre compte que cela efface tout ce qui pourrait se

trouver en mémoire, même au-dessus de RAMTOP.

Par contre, notre zone de 1 K-octet «protégée» survit à toute tentative d’effacement, que ce soit par le

programme d’initialisation, par NEW, ou par le chargement d’un programme! Seule une coupure

d’alimentation pourra en venir à bout.

Nous disposons donc là d’un espace exceptionnellement sûr, pour ranger des données

importantes, où surtout des PROGRAMMES EN LANGAGE MACHINE, qui nous seront très

bientôt fort utiles...

En effet, quiconques est livré aux joies de la programmation en assembleur sur le ZX 81 sait

forcément que le lancement d’un tel programme avant sa mise au point complète débouche neuf

fois sur dix sur un blocage de la machine obligeant à couper le courant. Une solution consiste à monter un

poussoir de remise à zéro de l’unité centrale (en parallèle sur C5), mais son utilisation efface toute la

mémoire!

La zone protégée dont nous vous proposons la création est tout à fait à l’abri des remises à zéro de

l’unité centrale. Aussi, en cas de blocage de la machine, on peut revenir au curseur en

utilisant ce poussoir de RAZ, puis lister, modifier, et relancer à loisir le programme en cours de

mise au point. Une fois cette mise au point terminée, on pourra «figer » ce logiciel dans une

mémoire EPROM, grâce au programmateur que nous décrirons.

La figure 4-1 montre que pour obtenir les résultats escomptés, il suffit d’empêcher la sélection de la

ROM lorsque A13 est à un, afin de libérer la zone inutilisée de 8 K-octets, et de valider le boîtier 1 K

RAM lorsque la combinaison suivante sera réalisée:

- module 16 K en place,

- A13 = 1

- A10, A11, A12, A14 = 0

- MREQ = 0

Le signal MREQ indique que l’unité centrale a besoin d’échanger des informations avec la

mémoire et rentre toujours dans la composition de signaux tels que RAMCS ou ROMCS (voir

figure 1-2). On notera que A15 n’est pas utilisée, car ce n’est qu’avec des blocs d’extension de

capacité supérieure à 16 K-octets que cette ligne pourrait passer à un niveau haut, et de tels

blocs possèdent souvent des zones protégées, rendant notre modification inutile. On remarquera aussi

qu’en l’absence de bloc 16 K, la RAM interne se bloque, empêchant la

machine de fonctionner, afin de signaler cet oubli à l’opérateur.

Réalisation pratique

Les fonctions logiques à réaliser étant très simples, le montage n’utilise que deux boîtiers TLL

très courants, et quelques composants annexes. Le schéma de la figure 4-2 ne fait que

concrétiser les conditions logiques précédemment énoncées.

Page 28

La mise en oeuvre pratique de la modification devra se dérouler en deux étapes:

D’une part, la construction d’un petit module sur un circuit imprimé gravé d’après la figure 4-3, et

câblé conformément au plan de la figure 4-4.

Page 29

D’autre part, la modification du ZX 81 en vue de l’incorporation de ce module dans son boîtier (il

reste suffisamment de place libre, notamment sous le clavier).

Il est nécessaire de couper, avec un outil tranchant mais précis, deux pistes du circuit

imprimé d’origine, situées chacune sur une face de la carte. Il s’agit de la piste reliant la

résistance R2 à la broche 20 du boîtier RAM (ou aux broches 8 des deux boîtiers RAM, selon la

version dont on dispose), et de celle reliant ces mêmes broches 20 ou 8 au contact 2A du

connecteur arrière.

Cela terminé, il pourra être intéressant de souder sur la carte de petits plots à souder ou à wrapper, aux

points suivants, faciles à repérer au moyen du schéma du ZX 81 et de la figure 4-2:

- ROMCS après R 28,

- RAMCS au niveau du ou des boîtiers de RAM,

- broche 2A du connecteur,

- A10, A11, A12, A13, A14, MREQ,

- + 5 V et masse.

Il ne reste plus, alors, qu’à raccorder le module à ces différents points et à passer aux essais,

non sans avoir monté le très utile poussoir de RAZ du Z80 en parallèle avec C5.

Mise en service

Cette adaptation effectuée, le ZX 81 doit fonctionner (avec son module 16 K), comme si rien

n’avait été fait.

Les choses changent, cependant, Si l’on entre le petit programme de la figure 4-5.

Page 30

Lancé sur un ZX 81 non modifié, ce programme échoue à ses trois tentatives de POKE et

déclenche, à la ligne 60, l’effacement complet de la mémoire puisque l’adresse 8 192 est une

sorte de «fantôme» de l’adresse 0.

Sur un ZX 81 modifié comme il a été expliqué, les lignes 20, 30 et 40 du programme chargent

dans la zone protégée le court programme machine suivant:

8192 JP 8192,

qui est aussitôt lancé par la ligne 60, après appui sur NEWLINE. Or, il s’agit d’un programme

«en boucle», incapable de s’arrêter seul. Habituellement, un tel programme bloque la machine

jusqu’à ce qu’une main secourable vienne couper l’alimentation!

Avec notre modification, on peut utiliser le poussoir de RAZ, ce qui efface bien sûr la partie

BASIC du programme, mais garde intacte la routine machine.

Pour s’en convaincre, il suffit de faire manuellement

RAND USR 8 192 newline, ou encore:

PRINT PEEK 8 192 newline

PRINT PEEK 8 193 newline

PRINT PEEK 8 194 newline

Grâce à cette toute petite démonstration, nos lecteurs amateurs de programmation en assembleur auront

pu constater l’intérêt que revêt pour eux l’utilisation de la nouvelle zone mémoire dont ils disposent à

présent, au prix d’une adaptation vraiment mineure de leur ZX 81.

Adaptation d’une EPROM 2716 au ZX 81

Tout ordinateur individuel possède une mémoire plus ou moins vaste, mais invariablement séparée en

deux parties, la ROM (ou mémoire morte) et la RAM (ou mémoire vive).

Traditionnellement, la ROM abrite le programme de base nécessaire dans tous les cas au fonctionnement

de la machine (moniteur, interpréteur, etc.).

Les programmes de l’utilisateur sont généralement chargés en RAM avant d’être lancés, soit par frappe au

clavier, soit a partir du lecteur de cassettes. Dans les deux cas, et spécialement avec le ZX 81, il faut un

temps non négligeable pour mener à bien ces opérations.

Certains ordinateurs peuvent recevoir des «cartouches» qu’il suffit d’embrocher pour que de nouveaux

programmes soient immédiatement disponibles. Ces chargeurs ne sont autres que des ROM

supplémentaires préprogrammées.

Avec le montage qui va être décrit, tout ZX 81 pourra ainsi accepter des ROM extérieures de 2 K-octets

que l’utilisateur pourra programmer, voire effacer, comme il l’entendra, au même titre qu’une cassette.

1) ROM contre cassette

Si l’on excepte l’entrée au clavier, qui ne peut en fait convenir qu’à la toute première mise en mémoire, et

la lecture de disquettes, réservée aux systèmes déjà évolués, il ne subsiste guère que deux procédés

courants permettant de charger des programmes sur un ordinateur individuel

La lecture de cassettes magnétiques est le procédé le plus répandu, car il ne réclame qu’un matériel très

Page 31

bon marché tout en restant très simple. L’approvisionnement en supports d’information (simples cassettes

audio) ne pose aucun problème.

Par contre, le chargement des programmes reste désespérément lent (30 secondes par K-octet pour le ZX

81), et en cas de coupure d’alimentation ou de blocage de l’unité centrale, le programme est intégralement

perdu, puisqu’il réside en RAM.

L’enfichage de modules préprogrammés (ROMs additionnelles) est massivement utilisé sur les ordinateurs

de jeux, les traductrices de poche, et certaines calculatrices programmables. Les avantages du procédé sont

déterminants: aucun appareil supplémentaire n’est nécessaire, chargement instantané et immunité totale

contre tous incidents tels que perte du contenu de la RAM.

Au chapitre des inconvénients, on peut citer un coût un peu supérieur (encore qu’en choisissant bien son

revendeur, on puisse acquérir des EPROMS de 2 K-octets pour le prix d’une très bonne cassette audio), et

surtout la nécessité d’un équipement spécial pour la programmation et l’effacement.

Achetés dans le commerce, ces appareils reviennent relativement cher, car ils sont surtout étudiés en vue

de besoins industriels.

Aussi, allons-nous décrire dans le prochain chapitre la réalisation pratique d’un programmateur exploitant

au maximum les possibilités du ZX 81, grâce à l’utilisation d’un circuit dérivé de notre carte à vingt

sorties étudiée au chapitre précédent.

Egalement, nous découvrirons que la construction d’un effaceur se ramène surtout à des opérations de

menuiserie puisque la plupart des électriciens peuvent fournir les tubes ultraviolets (germicides)

nécessaires, ainsi que leurs accessoires.

2) Adaptation d’une EPROM sur le ZX 81

Les EPROMS sont des ROM effaçables aux ultraviolets et reprogrammables aussi fréquemment qu’on le

souhaite. Leur avantage majeur en ce qui nous concerne est qu’elles n’exigent, en lecture, qu’une seule

tension d’alimentation de + 5 v, déjà disponible dans l’ordinateur. Dès lors, le principal rôle du circuit

d’adaptation sera de permettre l’adressage de l’EPROM dans une zone convenable de la mémoire.

Dans le cas du Zx 81, il est commode de remarquer que le plan d’occupation de l’espace mémoire

disponible réserve 16 K-octets à la ROM. Or, le BASIC Sinclair n’occupant que 8 K-octets, il est tout

indiqué de loger notre ROM personnelle à la suite!

Notre circuit devra alors adresser l’EPROM pour les 2 048 octets suivant l’adresse 8 191, mais en même

temps bloquer la ROM Sinclair qu’une ambiguïté de décodage adresse normalement deux fois!

Or, cette tâche rappelle à s’y méprendre celle du montage précédent, à ceci près que sa sortie

la broche de sélection de l’EPROM au lieu de la ligne RAMCS du ZX 81.

Le schéma de la figure 4-11 récapitule les connexions à établir avec la mémoire EPROM de type 2 716,

choisie en raison de son prix très abordable et de son excellente disponibilité auprès de la plupart des bons

revendeurs de composants.

doit attaquer

Page 32

Le décodage effectué sur les lignes d’adresse A11 à A15 est complet, ce qui permet de conserver intact

tout l’espace réservé à la RAM et ce, quelle que soit la capacité des éventuelles RAM additionnelles que

l’on pourrait raccorder en même temps. Par contre, il ne faudrait pas utiliser simultanément des

accessoires adressés entre 8 192 et 10 239.

La figure 4-12 donne le tracé d’un circuit imprimé prévu pour recevoir l’EPROM et ses circuits associés

sous une forme compacte, selon le plan de la figure 4-13. On pourra équiper ce module d’un connecteur

gigogne (qui sera décrit dans un autre chapitre) ou bien le loger à demeure dans le boîtier de l’ordinateur,

par exemple sous le clavier, Si cette place très accueillante n’est pas déjà occupée!

Page 33

En utilisant un support de bonne qualité, on pourra faire alterner plusieurs EPROMS sur le même

adaptateur mais, compte tenu du faible coût de ce circuit, il serait plus confortable d’équiper chaque

EPROM de son propre décodeur, afin de disposer de véritables «cartouches» enfichables.

Que mettre dans l’EPROM?

Compte tenu de la conception générale du ZX 81, le plus commode est de loger des programmes écrits en

langage machine dans cette mémoire morte additionnelle.

Il est devenu banal, en Grande-Bretagne, d’ajouter ces «compléments» au BASIC d’origine, sous la forme

de petites routines que l’on appelle par des RAND USR.

Page 34

En ce qui nous concerne, un chapitre entier sera consacré au développement d’idées de logiciels machine,

susceptibles de «résider» en EPROM, mais étroitement liés à l’exploitation des circuits d’entrée sortie

dans le cadre de toutes sortes d’automatismes utilitaires.

Sitôt la machine sous tension, un simple RAND USR 8 192 manuel suffira à lancer le programme, sans

autre forme de chargement. Cependant, nous décrirons aussi, ce qui est beaucoup moins classique, une

méthode permettant de «brûler» en EPROM de petits programmes BASIC dont l’écriture est bien

évidemment à la portée de tous nos lecteurs.

Loading...

Loading...