Silicon Laboratories SI2493-57-34-15-04, SI2494-39 User Manual

AN93

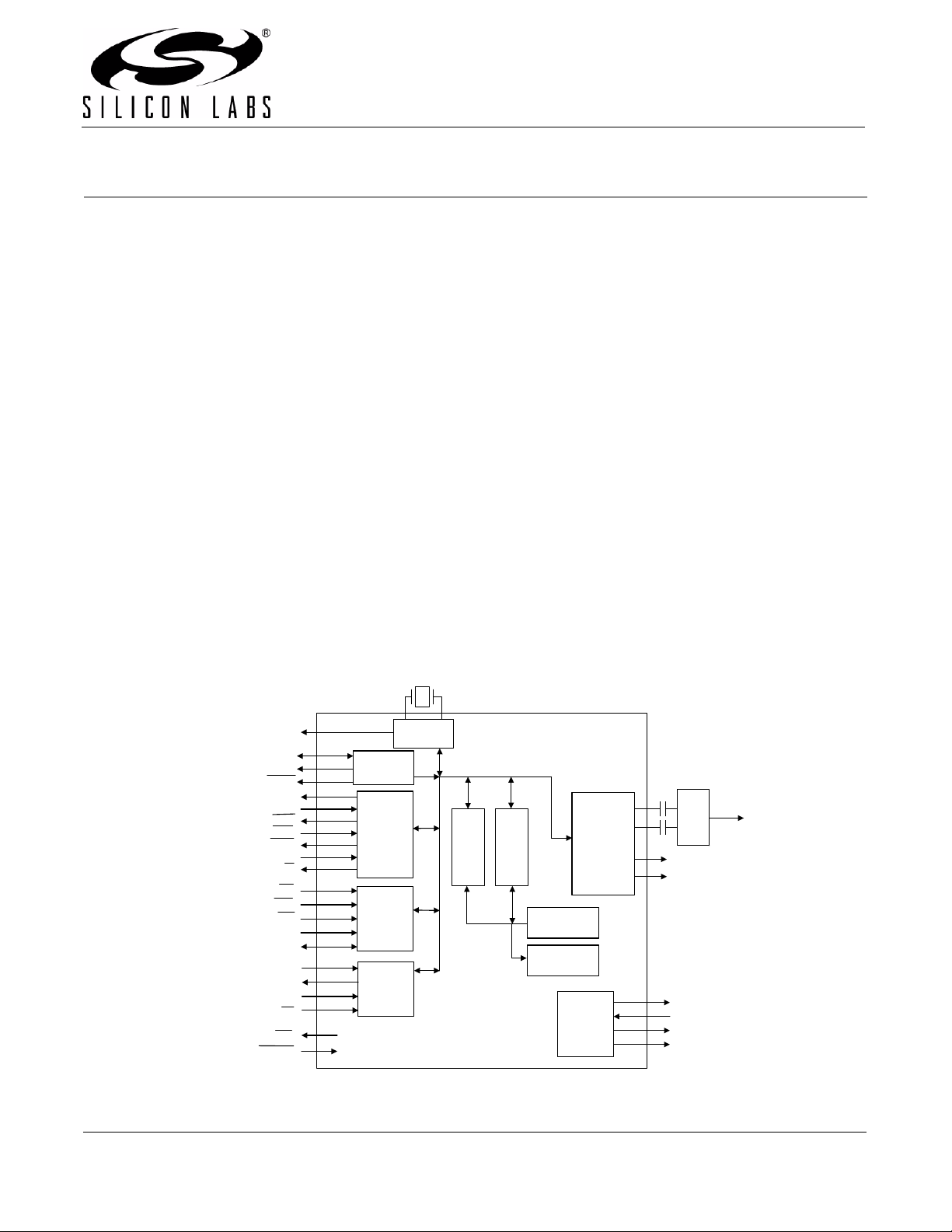

UART

Interface

Parallel

Interface

DSP

DAA

Interface

ROM

PLL

Clocking

XTI XTO

CLKOUT

INT

RESET

C1

To Phone

Line

AOUT

Data Bus

Controller

Si3018/10

RXD

TXD

CTS

RTS

DCD

ESC

RI

CS

WR

RD

A0

D0-D7

Program Bus

RAM

EEPROM

Interface

EESD

EECLK

EECS

C2

Si3000

Interface

FSYNC

SDO

SDI

MCLK

SPI

Interface

SDI

SDO

SCLK

SS

AOUTb

Si2493/57/34/15/04 (Revision D) and Si2494/39

Modem Designer’s Guide

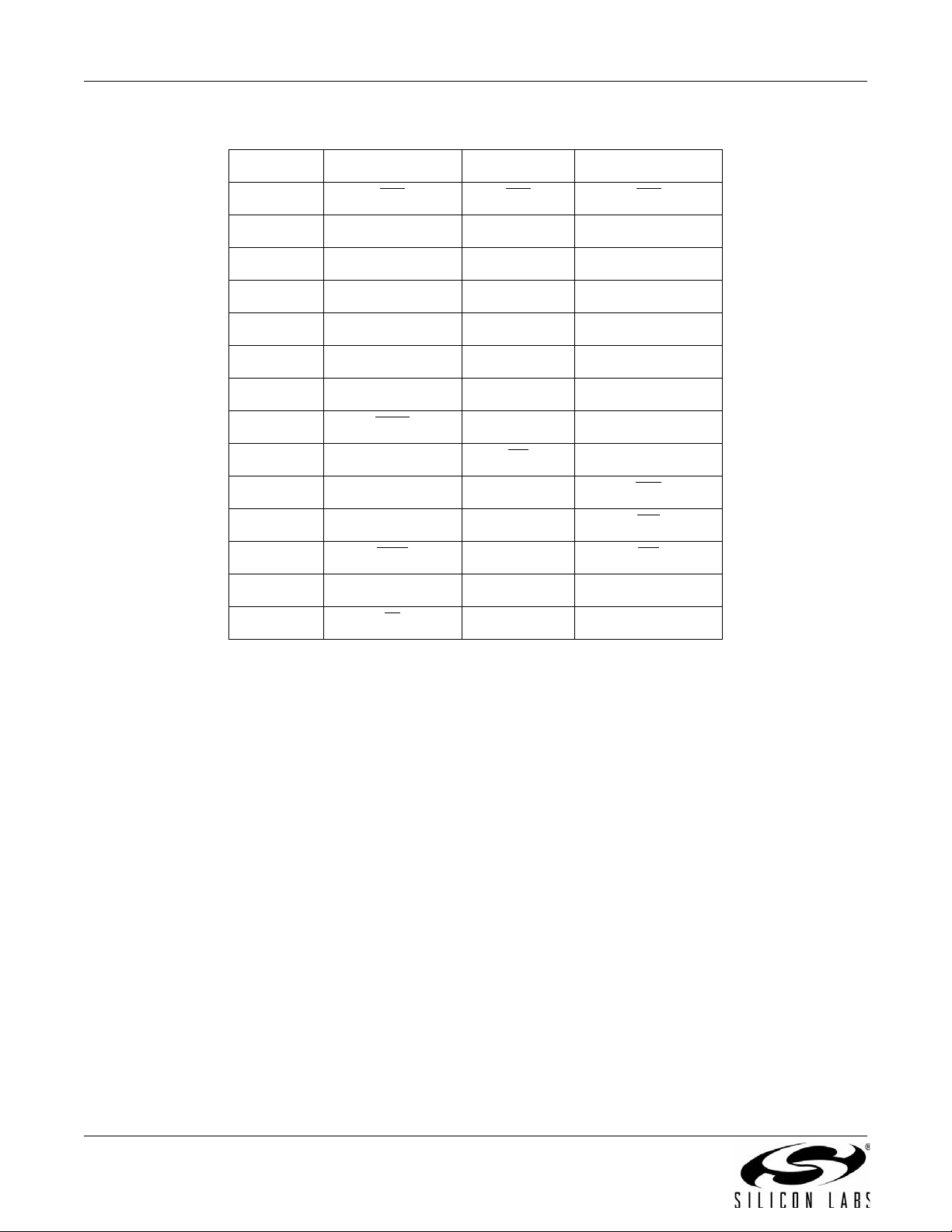

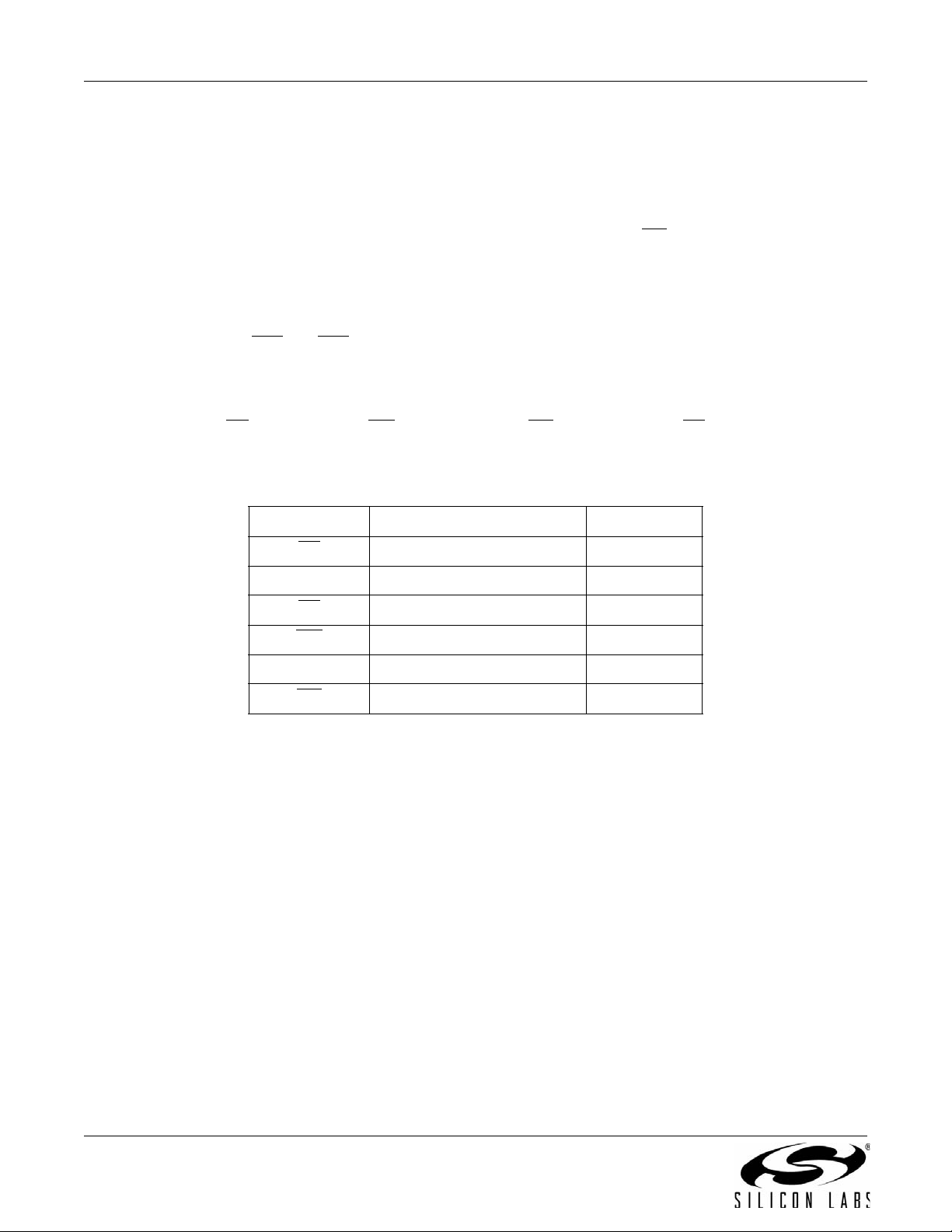

1. Introduction

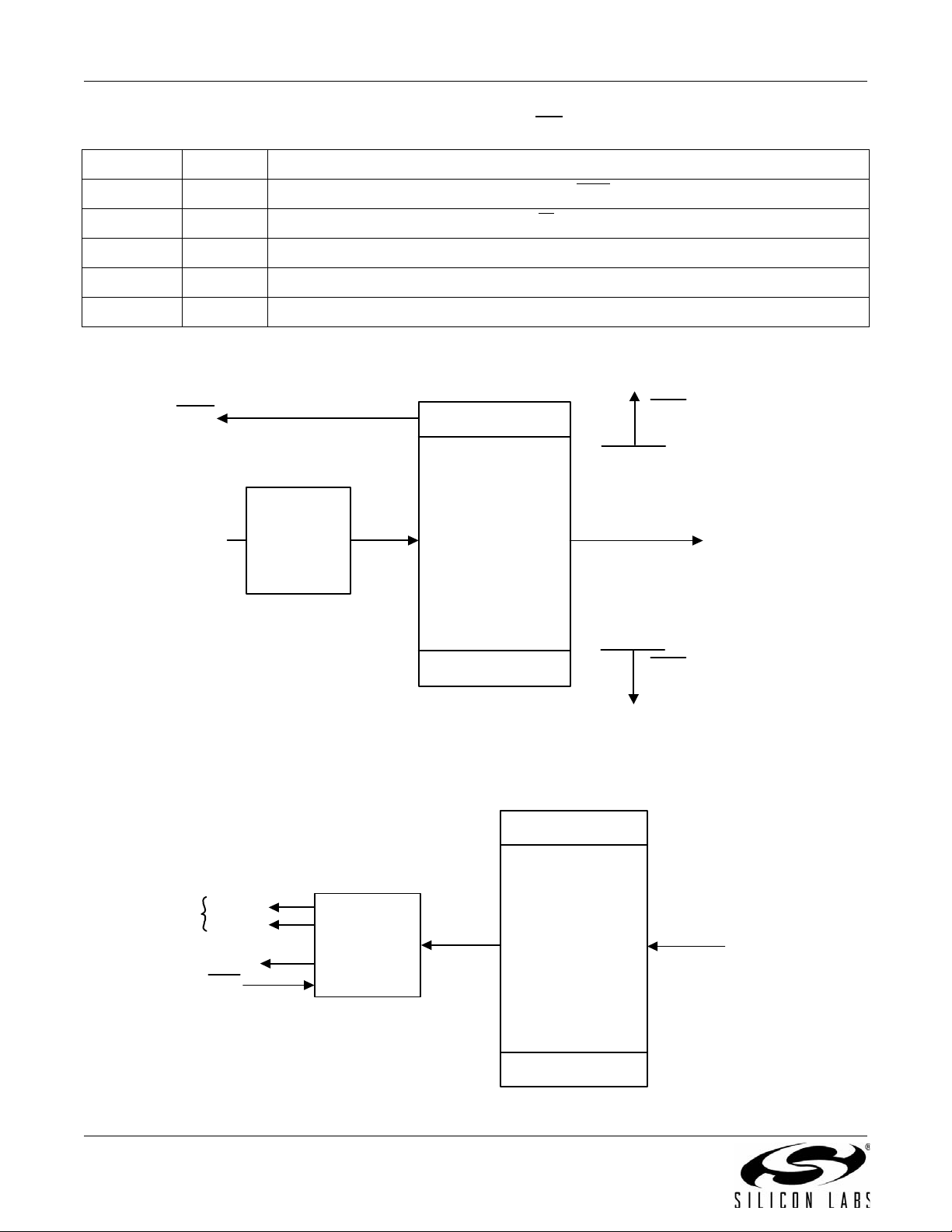

The Si2494/93/57/39/34/15/04 ISOmodem chipset family consists of a 38-pin QFN (Si2494/39) or 24-pin TSSOP

(Si2493/57/34/15/04) or 16-pin SOIC (Si2493/57/34/15/04) low-voltage modem device, and a 16-pin SOIC lineside DAA device (Si3018/10) connecting directly with the telephone local loop (Tip and Ring). This modem solution

is a complete hardware (controller-based) modem that connects to a host processor through a UART, parallel or

SPI interface. Parallel and EEPROM interfaces are available only on the 38-pin QFN or 24-pin TSSOP package

option. Refer to Table 4, “ISOmodem Capabilities,” on page 10 for available part number, capability and package

combinations. Isolation is provided by Silicon Laboratories’ isolation capacitor technology, which uses high-voltage

capacitors instead of a transformer. This isolation technology complies with global telecommunications standards

including FCC, ETSI ES 203 021, JATE, and all known country-specific requirements.

Additional features include programmable ac/dc termination and ring impedance, on-hook and off-hook intrusion

detection, Caller ID, loop voltage/loop current monitoring, overcurrent detection, ring detection, and the hookswitch function. All required program and data memory is included in the modem device. When the modem

receives a software or hardware reset, all register settings revert to the default values stored in the on-chip

program memory. The host processor interacts with the modem controller through AT commands used to change

register settings and control modem operation. Country, EMI/EMC, and safety test reports are available from

Silicon Laboratories representatives and distributors.

This application note is intended to supplement the Si2494/39 Revision A, Si2493 Revision D, and the Si2457/34/

15/04 Revision D data sheets. It provides all the hardware and software information necessary to implement a

variety of modem applications, including reference schematics, sample PCB layouts, AT command and register

reference, country configuration tables, programming examples and more. Particular topics of interest can be

easily located through the table of contents or the comprehensive index located at the back of this document.

Rev. 1.3 8/11 Copyright © 2011 by Silicon Laboratories AN93

This information applies to a product under development. Its characteristics and specifications are subject to change without notice.

Figure 1. Functional Block Diagram

AN93

2 Rev. 1.3

AN93

TABLE OF CONTENTS

Section Page

1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1. Selection Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2. Modem (System-Side) Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.1. Resetting the Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.1.1. Reset Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.1.2. Reset Strapping: General Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.1.3. Reset-Strap Options for 16-Pin SOIC Package . . . . . . . . . . . . . . . . . . . . . . . . 13

2.1.4. Reset-Strap Options for 24-Pin TSSOP Package . . . . . . . . . . . . . . . . . . . . . . 13

2.1.4.1. Reset Strapping Options for TSSOP-24 with UART-Interface. . . . . . . . . 14

2.1.4.2. Reset Strapping Options for TSSOP-24 with Parallel-Interface. . . . . . . . 14

2.1.4.3. Reset Strapping Options for TSSOP with SPI-Interface . . . . . . . . . . . . . 15

2.1.5. Reset Strapping Options for QFN Parts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.1.5.1. Reset Strapping Options for QFN Parts with UART Operation . . . . . . . . 15

2.1.5.2. Reset Strapping Options for QFN Parts with SPI Operation . . . . . . . . . . 16

2.1.5.3. Reset Strapping Options for QFN Parts with Parallel Operation . . . . . . . 16

2.2. System Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.2.1. Interface Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.2.2. Interface Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.2.3. UART Interface Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.2.3.1. UART Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.2.3.2. Autobaud . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

2.2.3.3. Flow Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.2.4. Parallel and SPI Interface Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.2.4.1. Hardware Interface Register 0. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2.2.4.2. Hardware Interface Register 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2.2.4.3. Parallel Interface Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2.2.4.4. SPI Interface Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

2.2.4.5. Interface Communication Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

2.3. Isolation Capacitor Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.4. Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.4.1. Power-Down Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.4.2. Wake-on-Ring Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.4.3. Sleep Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.5. SSI/Voice Mode (24-Pin TSSOP and 38-Pin QFN Only) . . . . . . . . . . . . . . . . . . . . . . 30

2.6. EEPROM Interface (24-Pin TSSOP and 38-Pin QFN Only) . . . . . . . . . . . . . . . . . . . . 31

2.6.1. Supported EEPROM Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

2.6.2. Three-Wire SPI Interface to EEPROM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.6.3. Detailed EEPROM Examples. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.6.4. Boot Commands (Custom Defaults) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.6.5. AT Command Macros (Customized AT Commands) . . . . . . . . . . . . . . . . . . . . 34

2.6.6. Firmware Upgrades . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

2.6.6.1. Boot Command Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Rev. 1.3 3

AN93

2.6.6.2. AT Command Macro Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

2.6.6.3. Autoloading Firmware Upgrade Example . . . . . . . . . . . . . . . . . . . . . . . . 35

2.6.6.4. Combination Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3. DAA (Line-Side) Device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

3.1. Hookswitch and DC Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

3.2. AC Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

3.3. Ringer Impedance and Threshold . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

3.4. Pulse Dialing and Spark Quenching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

3.5. Line Voltage and Loop Current Sensing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

3.6. Legacy-Mode Line Voltage and Loop Current Measurement . . . . . . . . . . . . . . . . . . . 42

3.7. Billing Tone Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

4. Hardware Design Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

4.1. Component Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

4.1.1. Power Supply and Bias Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

4.1.2. Hookswitch and DC Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

4.1.3. Clocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

4.1.4. Ringer Network. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

4.1.5. Optional Billing-Tone Filter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

4.2. Schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

4.3. Bill of Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

4.4. Layout Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

4.4.1. ISOmodem Layout Check List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

4.4.2. Module Design and Application Considerations. . . . . . . . . . . . . . . . . . . . . . . . 53

4.4.2.1. Module Design. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

4.4.2.2. Motherboard Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

4.5. Analog Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

4.5.1. Interaction between the AOUT Circuit and the

Required Modem Reset Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

4.5.2. Audio Quality . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

5. Modem Reference Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

5.1. Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

5.2. DSP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

5.3. Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

5.4. AT Command Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

5.5. Extended AT Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

5.6. S Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

5.7. U Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

5.7.1. U-Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

5.7.2. U00–U16 (Dial Tone Detect Filter Registers). . . . . . . . . . . . . . . . . . . . . . . . . . 97

5.7.3. U17–U30 (Busy Tone Detect Filter Registers). . . . . . . . . . . . . . . . . . . . . . . . . 98

5.7.4. U31–U33 (Ringback Cadence Registers) . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

5.7.5. U34–U35 (Dial Tone Timing Register) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

5.7.6. U37–U45 (Pulse Dial Registers). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

5.7.7. U46–U48 (DTMF Dial Registers) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

5.7.8. U49–U4C (Ring Detect Registers) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

5.7.9. U4D (Modem Control Register 1—MOD1). . . . . . . . . . . . . . . . . . . . . . . . . . . 103

5.7.10. U4E (Pre-Dial Delay Time Register). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

4 Rev. 1.3

AN93

5.7.11. U4F (Flash Hook Time Register) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

5.7.12. U50–U51 (Loop Current Debouncing Registers) . . . . . . . . . . . . . . . . . . . . . 105

5.7.13. U52 (Transmit Level Register) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

5.7.14. U53 (Modem Control Register 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

5.7.15. U54 (Calibration Timing Register) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

5.7.16. U62–U66 (DAA Control Registers). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

5.7.17. U67–U6A (International Configuration Registers) . . . . . . . . . . . . . . . . . . . . 108

5.7.18. U6C (Line-Voltage Status Register). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

5.7.19. U6E–U7D (Modem Control and Interface Registers). . . . . . . . . . . . . . . . . . 111

5.7.20. U80 (Transmit Delay for V.22 Fast Connect) . . . . . . . . . . . . . . . . . . . . . . . . 119

5.7.21. U87 (Synchronous Access Mode Configuration Register) . . . . . . . . . . . . . . 120

5.7.22. UAA (V.29 Mode Register). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

5.7.23. UIDA Response and Answer Tone Delay Register . . . . . . . . . . . . . . . . . . . 121

5.8. Firmware Upgrades . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

5.8.1. Method 1 (Fastest) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

5.8.2. Method 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

5.8.3. Method 3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

5.9. Escape Methods . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

5.9.1. +++ Escape . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

5.9.2. “9th Bit” Escape . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

5.9.3. “Escape Pin” Escape . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

5.10. Data Compression . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

5.11. Error Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

5.12. Wire Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

5.13. EPOS (Electronic Point of Sale) Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

5.13.1. EPOS Fast Connect. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

5.13.2. EPOS V.29 Fast Connect. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

5.14. Legacy Synchronous DCE Mode/V.80 Synchronous Access Mode . . . . . . . . . . . . 125

5.15. V.80 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

6. Programming Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

6.1. Quick Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

6.2. Country-Dependent Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

6.2.1. DC Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

6.2.2. Country Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

6.2.2.1. Country Initialization Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

6.2.2.2. Country-Setting Register Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

6.2.2.3. Special Requirements for India . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

6.2.2.4. Special Requirements for Serbia and Montenegro . . . . . . . . . . . . . . . . 147

6.2.3. Blacklisting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

6.3. Caller ID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

6.3.1. Force Caller ID Monitor (Always On) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

6.3.2. Caller ID After Ring Only . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

6.3.3. UK Caller ID with Wetting Pulse. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

6.3.4. Japan Caller ID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

6.3.5. DTMF Caller ID. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

6.4. SMS Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

6.5. Type II Caller ID/SAS Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

Rev. 1.3 5

AN93

6.6. Intrusion/Parallel Phone Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

6.6.1. On-Hook Condition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

6.6.1.1. Line Not Present/In Use Indication (Method 1—Fixed) . . . . . . . . . . . . . 161

6.6.1.2. Line Not Present/In Use Indication (Method 2—Adaptive). . . . . . . . . . . 162

6.6.2. Off-Hook Condition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

6.7. Modem-On-Hold . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

6.7.1. Initiating Modem-On-Hold. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

6.7.2. Receiving Modem-On-Hold Requests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

6.8. HDLC: Bit Errors on a Noisy Line . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

6.9. Overcurrent Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

6.10. Pulse/Tone Dial Decision . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

6.10.1. Method 1: Multiple Off-Hook Transitions. . . . . . . . . . . . . . . . . . . . . . . . . 169

6.10.2. Method 2: Single Off-Hook Transition . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

6.10.3. Method 3: Adaptive Dialing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

6.10.4. Automatic Phone-Line Configuration Detection . . . . . . . . . . . . . . . . . . . . . . 170

6.10.5. Line Type Determination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

6.11. Telephone Voting Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

6.12. V.92 Quick Connect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

7. Handset, TAM, and Speakerphone Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

7.1. Software Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

7.1.1. AT Command Set. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

7.1.2. AT+ Extended Commands. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

7.1.3. <DLE> Commands (DTE-to-DCE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

7.1.4. <DLE> Events (DCE-to-DTE). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

7.1.4.1. Simple Event Reporting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

7.1.4.2. Complex Event Reporting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

7.1.5. U Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

7.2. Voice Reference—Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

7.3. Si3000 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

7.3.1. Microphone and Speaker Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

7.3.2. Register Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

7.3.3. System Voice Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

7.3.3.1. TAM Hands-Free . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

7.3.3.2. TAM Handset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

7.3.3.3. Speakerphone . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

7.3.3.4. Handset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

7.3.3.5. TAM PSTN. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

7.4. Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

7.5. Handset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

7.5.1. Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

7.5.2. Handset Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

7.5.3. Call – Automatic Tone Dial. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

7.5.4. Call – Manual Off-Hook Tone Dial . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

7.5.5. Call – Automatic Pulse Dial . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

7.5.6. Answer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

7.5.7. Terminate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

6 Rev. 1.3

AN93

7.5.8. Speakerphone Transition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

7.6. Telephone Answering Machine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

7.6.1. Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

7.6.2. TAM Hands-Free—Idle. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

7.6.2.1. Record OGM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

7.6.2.2. Review OGM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

7.6.2.3. Record Local ICM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

7.6.2.4. Review ICM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

7.6.2.5. Speakerphone Transition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

7.6.2.6. Handset Transition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

7.6.3. TAM Handset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

7.6.3.1. Record OGM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

7.6.3.2. Review OGM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

7.6.3.3. Record Local ICM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

7.6.3.4. Review ICM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

7.6.4. TAM PSTN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

7.6.4.1. Normal Answer – OGM Playback with ICM Record. . . . . . . . . . . . . . . . 208

7.6.4.2. Interrupted Answer – OGM Playback with DTMF Menu Entry. . . . . . . . 210

7.6.4.3. Speakerphone Transition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 212

7.6.4.4. Handset Transition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 212

7.7. Speakerphone . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 212

7.7.1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 212

7.7.2. Simplex Speakerphone . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 212

7.7.3. External Microphone/Speaker Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

7.7.3.1. Transmit Gain Calibration—Speakerphone Dis abled . . . . . . . . . . . . . . 213

7.7.3.2. Receive Gain Calibration—Speakerphone Disabled . . . . . . . . . . . . . . . 216

7.7.3.3. Speakerphone Calibration—AEC Gain Calibration . . . . . . . . . . . . . . . . 217

7.7.4. Speakerphone Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

7.7.5. Simplex Speakerphone Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

7.7.6. Call—Automatic Tone Dial . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

7.7.7. Call—Manual Off-Hook Tone Dial . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

7.7.8. Call—Automatic Pulse Dial. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222

7.7.9. Answer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222

7.7.10. Handset Transition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222

7.7.11. Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223

7.8. Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223

7.9. References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223

8. Security Protocols . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

8.1. Implementing the SIA Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

8.1.1. Modem-Specific Implementation Details . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

8.1.1.1. Listen-In and V-channel Periods (Voice Pass-Through) . . . . . . . . . . . . 224

8.1.1.2. Inserting a V.32bis period (e.g., SIA Level-3 Video Block Support). . . . 224

8.1.1.3. Considerations when Disconnecting the Session . . . . . . . . . . . . . . . . . 225

8.2. Implementing the Ademco® Contact ID Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

8.2.1. Modem Specific Implementation Details . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

8.2.1.1. Handshake Tone Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

8.2.1.2. Session Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

Rev. 1.3 7

AN93

9. Chinese ePOS SMS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234

9.1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234

9.2. SMS AT Command Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235

9.2.1. SMS User Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

9.2.2. Procedure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

9.2.2.1. Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

9.2.2.2. Response 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

9.2.2.3. Response 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

9.2.2.4. Response 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

9.3. Example Session . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

10. Testing and Diagnostics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

10.1. Prototype Bring-Up (Si3018/10) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

10.1.1. Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

10.1.2. Visual Inspection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

10.1.3. Basic Troubleshooting Steps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

10.1.4. Host Interface Troubleshooting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243

10.1.5. Isolation Capacitor Troubleshooting. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244

10.1.6. Si3018/10 Troubleshooting. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244

10.1.7. Component Troubleshooting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244

10.2. Self Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 249

10.3. Board Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 250

10.4. Compliance Testing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 252

10.4.1. EMI. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 253

10.4.2. Safety . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 254

10.4.3. Surges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 254

10.5. AM-Band Interference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 255

10.6. Debugging the DTE interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256

Appendix A—EPOS Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

VISA II (7E1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

Recommendation V.80 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 258

The ISOmodem in EPOS Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260

A V.29 FastPOS Sample Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 261

Appendix B—Line Audio Recording . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

When to Use Audio Recording . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

Times When Audio Recording May Not Help . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

Hardware Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

Audio Playback and Analysis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 279

Examples of Line Impairments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 288

Appendix C—Parallel/SPI Interface Software Implementation . . . . . . . . . . . . . . . . . . . . . 290

Software Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 292

Compiler Option: Dot Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 299

Modem Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 299

Modem Interrupt Service Sample Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 300

Document Change List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 303

Contact Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 304

8 Rev. 1.3

AN93

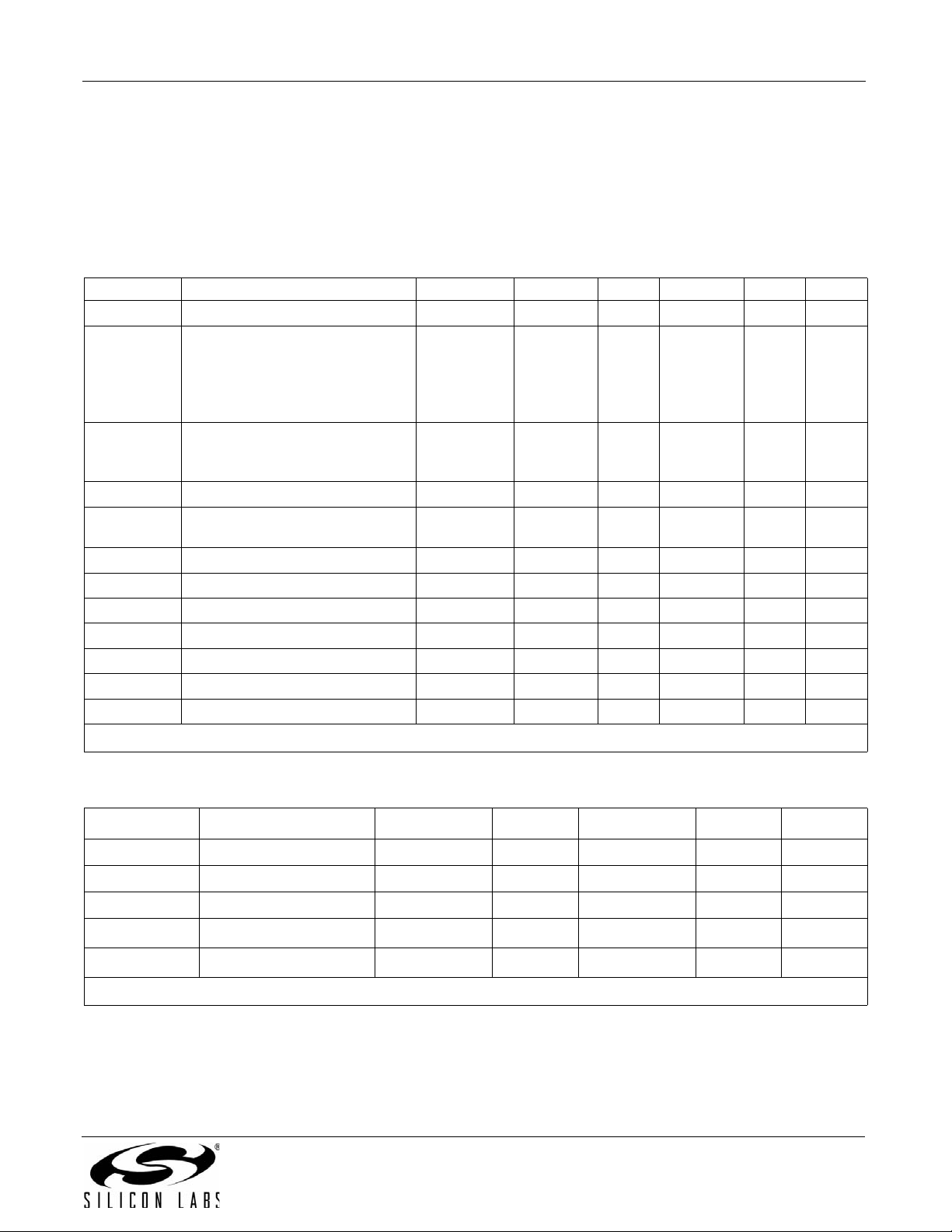

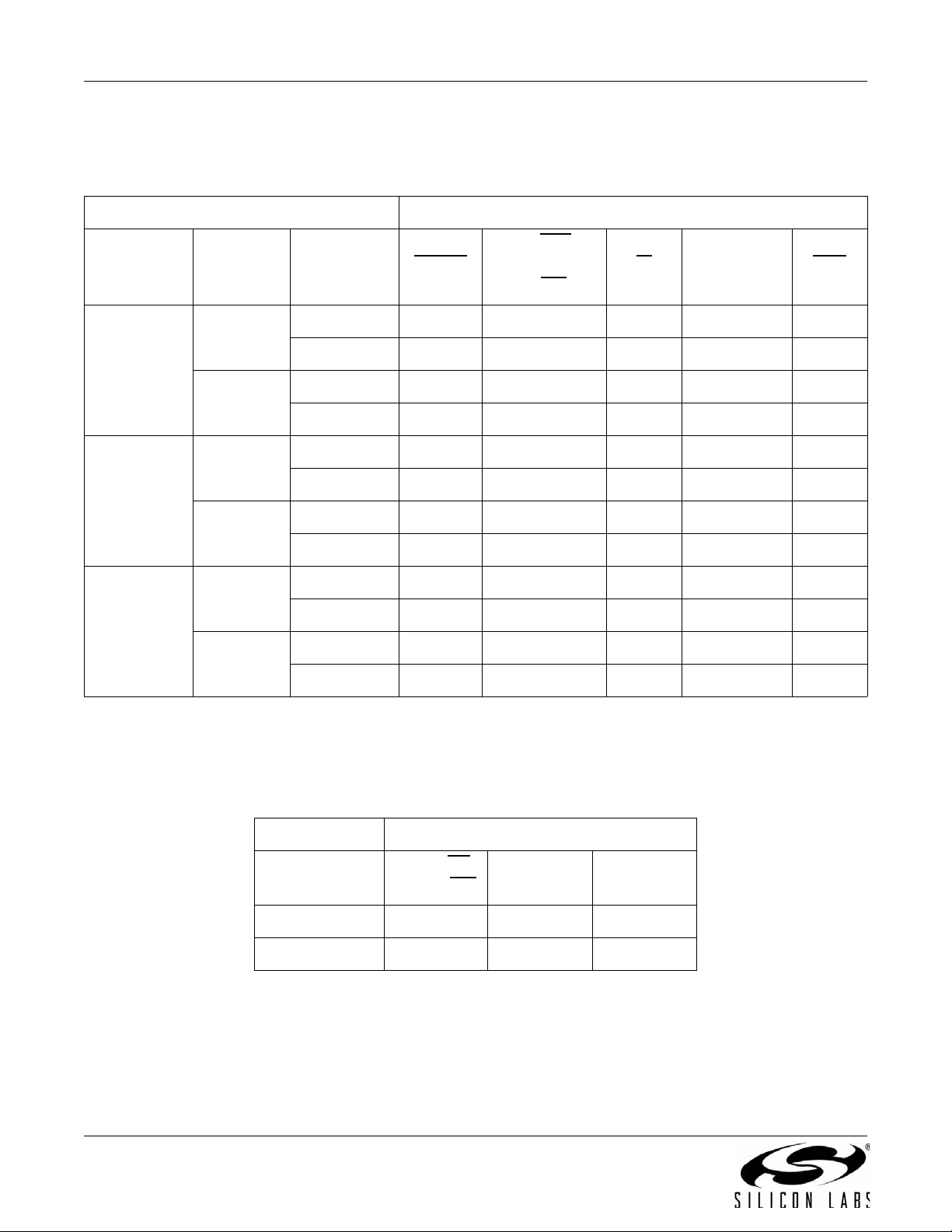

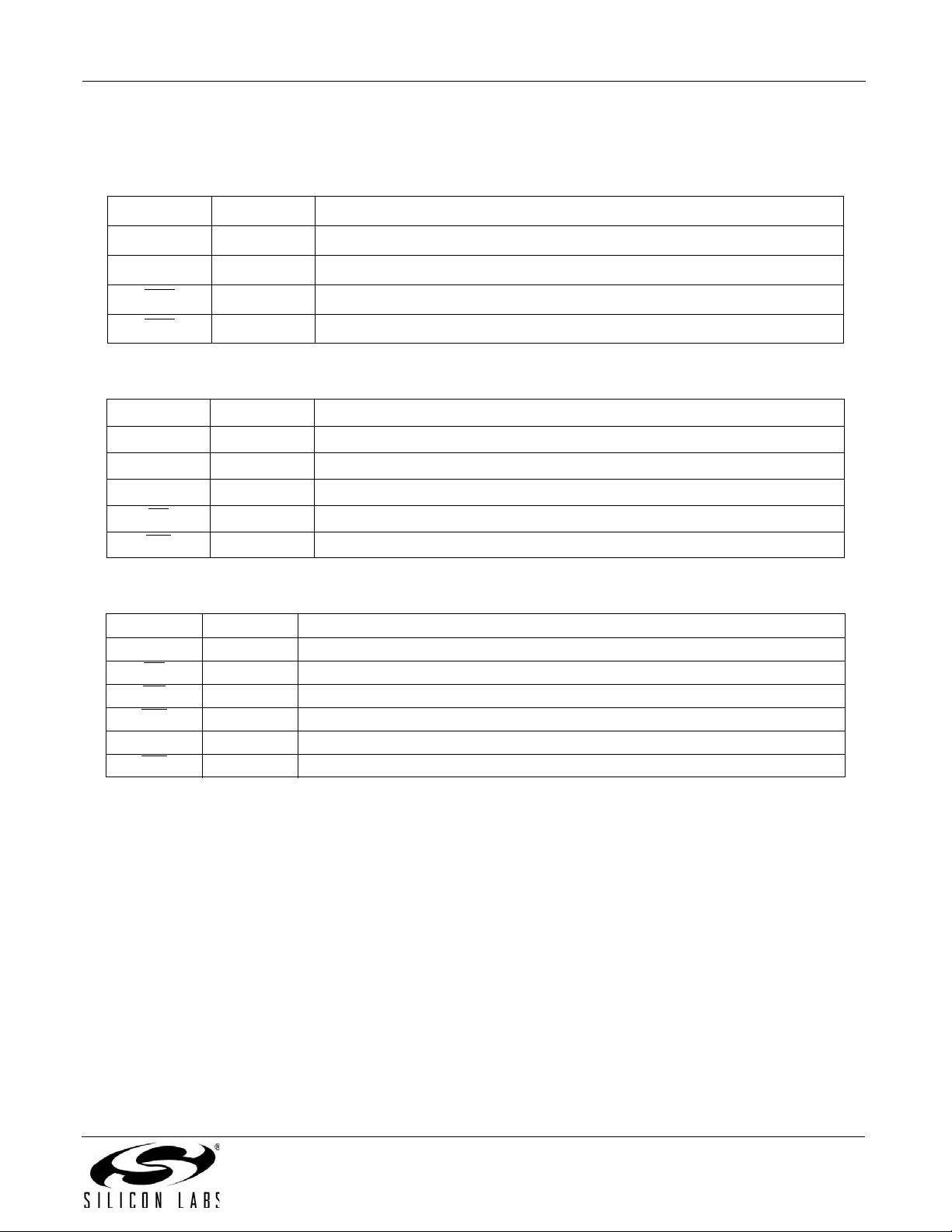

1.1. Selection Guide

Tables 1 through 3 list the modulations, protocols, carriers, tones and interface modes supported by the Si2494/39

and Si2493/57/34/15/04 ISOmodem family. The Si2493 supports all modulations and protocols from Bell 103

through V.92. The Si2457 supports all modulations and protocols from Bell 103 through V.90. The Si2434 supports

all modulations and protocols from Bell 103 through V.34. The Si2415 supports all modulations and protocols from

Bell 103 through V.32bis. The Si2404 supports all modulations and protocols from Bell 103 through V.22bis.

Table 1. Modulations

Modulation Data Rates (bps) Modulation Si2494/93 Si2457 Si2439/34 Si2415 Si2404

V.92* 48k, 40k, 32k, 24k PCM

V.90* 56k, 54.6k, 53.3k, 52k, 50.6k,

49.3k, 48k, 46.6k, 45.3k, 44k,

42.6k, 41.3k, 40k, 38.6k,

37.3k, 36k, 34.6k, 33.3k, 32k,

30.6k, 29.3k, 28k

V.34* 33.6k, 31.2k, 28.8k, 26.4k, 24k,

21.6k, 19.2k, 16.8k, 14.4k, 12k,

9600, 7200, 4800, 2400

V.32bis* 14.4k, 12k, 9600, 7200, 4800 TCM

V.32* 9600

9600, 4800

V.29FC* 9600 QAM

V.23 1200 FSK

V.22bis 2400, 1200 QAM

V.22 1200 DPSK

Bell 212A 1200 DPSK

V.21 300 FSK

Bell 103 300 FSK

*Note: With the Si3018 DAA only.

PCM

TCM

TCM

QAM

*

Table 2. Protocols

Protocol*

V.44 Compression

V.42bis Compression

V.42 Error Corre ct ion

MNP5 Compression

MNP2-4 Error Correction

*Note: The Si2494/93/57/39/34/15/04 family allows any supported protocol combined with any modulation.

Function Si2494/93 Si2457 Si2439/34 Si2415 Si2404

Rev. 1.3 9

AN93

Table 3. Carriers and Tones

Specification Transmit Carrier

(Hz)

V.92 Variable Variable per ITU-T V.92

V.90 Variable Variable per ITU-T V.90

V.34 Variable Variable per ITU-T V.34

V.32bis 1800 1800 2100 per ITU-T V.32bis

V.32 1800 1800 2100 per ITU-T V.32

V.29 1700 1700 per ITU-T V.29

V.22bis, V.22

Originate/answer

V.21

Originate/answer (M/S)

Bell 212A

Originate/answer

Bell 103

Originate/answer (M/S)

1200

2400

1180/980

1850/1650

1200

2400

1270/1070

2225/2025

Receive Carrier

(Hz)

2400

1200

1850/1650

1180/980

2400

1200

2225/2025

1270/1070

Answer

Tone (Hz)

2100 –43 dBm/–48 dBm

2100 –43 dBm/–48 dBm

2225 –43 dBm/–48 dBm

2225 –43 dBm/–48 dBm

Carrier Detect (Acquire/

Release)

–43 dBm/–48 dBm

–43 dBm/–48 dBm

–43 dBm/–48 dBm

–43 dBm/–48 dBm

Table 4. ISOmodem Capabilities

Part Numbers Package UART EEPROM SPI Parallel SSI/Voice

Si2493/57/34/15/04

Si2493/57/34/15/04

Si2494/39

Notes:

1. Die Revision D or later

2. The EEPROM interface option is available only when the UART or SPI interface is selected.

1

1

SOIC-16

TSSOP-24

QFN-38

2

10 Rev. 1.3

AN93

2. Modem (System-Side) Device

The Si24xx ISOmodem system-side devices contain a controller, a DSP, program memory (ROM), data memory

(RAM), UART, SPI and parallel interfaces, a crystal oscillator, and an isolation capacitor interface. The following

sections describe the reset sequence, the host interface, the isolation interface, low-power mod es, SSI/voice m ode

and the EEPROM interface.

2.1. Resetting the Device

Reset is required after power-on or brownout conditions (the supply dropping to less than the data sheet minimum).

The supply must be stable throughout the minimum required reset time described here and thereafter. A reset is

also required in order to come out of the power down mode.

Some operational choices, including the crystal oscillator frequency used and the command interface used (e.g.

UART vs SPI), is made during the reset time according to pull-down resistors placed on some modem pins. These

pins are modem output lines, but, during reset, the modem places them into a high-impedance mode with weak

internal pull-ups, then reads the user's strapping choices. It is important that the resultant state changes of these

pins during reset are not misinterpreted by the host.

For example the INT output pin of the modem (and perhaps others) can be strapped low with a 10 k resistor to

request SPI operation. If that mode is chosen, the host should take care not to enable this interrupt input before the

modem reset since the INT signal will transition from high to low and back up during reset in this case and can

generate an unexpected interrupt.

If an external clock signal is provided instead of a crystal attached to the modem, it is important that this external

clock signal be stable before the reset ends.

2.1.1. Reset Sequence

After power-on, the modem must be reset by asserting the RESET pin (low) for the required time then waiting a

fixed 300 ms before sending the first A T command. The reset re covery time of 300 ms is also applicable if the reset

is a SW triggered event, such as an ATZ command.

If a 4.9152 MHz crystal or an external 27 MHz clock is used, the reset must be asserted for 5 ms, and a wait of

300 ms duration must happen before an AT command is issued. If a 32 kHz crystal is used, the reset pulse must be

500 ms long and followed by the same 300 ms duration wait as that used for higher frequency clocks.

This is adequate to reset all the on-chip registers. No te tha t 16 µs after the customer-applied reset pulse starts, the

I/O pins will be tri-stated with a weak pull-up, and, 16 µs after the end of this reset pulse, the IO pins will switch to

inputs or outputs as appropriate to the mode indicated by the pull-down strapping. This 16 µs de lay is for newer

revs of the modem parts (those parts that introduce a 32 kHz crystal and SPI operation); older revs exhibit a delay

of only nanoseconds.

The reset sequence described above is appropriate for all user modes of the modem including UART, SPI, and

Parallel bus operation.

A software reset of the modem can also b e pe rfor med by issuing the command ATZ or by setting U-register 6E bit

4 (RST) high using AT commands. After issuing a software or hardware reset, the host must wait for the reset

recovery time before issuing any subsequent AT commands.

There is no non-volatile memory on the ISOmodem other than program ROM. When reset, the ISOmodem reverts

to the original factory default settings. Any set-up or configuration data and software updates must be reloaded

after every reset. This is true whether the reset occurs due to a power-down/power-up cycle, a power-on reset

through a manual reset switch, by writing U6E [4] (RST) = 1, or by executing ATZ.

A suggested reset sequence is as follows:

1. Apply an active-low pulse to the RESET

2. Wait at least the reset r ecovery time.

3. Load firmware updates (if required).

4. Set non-default DAA interface parameters—DCV, ACT, ILIM, OHS2, OHS, RZ, RT, (U67), LIM, (U68).

5. Set non-default cadence values—Busy Tone, Ringback, Ring.

pin; write RST bit or ATZ<CR>.

Rev. 1.3 11

AN93

6. Set non-default frequency values—Ring.

7. Set non-default filter parameters.

8. Set non-default S-register values.

The modem is now ready to detect rings, answer another modem, call, or dial out to a remote modem.

Some key default settings for the modem after reset or powerup include the following:

V.92 and fall-backs enabled (Si2494/93)

V.90 and fall-backs enabled (Si2457)

V.34 and fall-backs enabled (Si2439/34)

V.32bis and fall-backs enabled (Si2415)

V.22bis and fall-backs enabled (Si2404)

V.42/42bis enabled

+++ escape sequence enabled

Answer-on-ring is disabled

Speaker off

DTE echo enabled

Verbal result codes enabled

CTS only enabled

FCC (US) DAA and call progress settings

2.1.2. Reset Strapping: General Considerations

The different options available in the Si24xx ISOmodem family are selected by means of 10 k pulldown resistor s

placed at certain pins. During power-on or pin reset, the ISOmodem’s signal pins are read and the option resistors

are taken into account to determine the required configuration. After reset, the ISOmodem assumes the

functionality selected by the corresponding combination of pulldown resistors.

Below is a summary of reset-strap options. Not all options are available on all part number or packages. Refer to

Table 4, “ISOmodem Capabilities,” on page 10 for details.

Host interface: UART, parallel or SPI

Input clock frequency: 32 kHz, 4.9152 MHz or 27 MHz

Autobaud mode or fixed-rate UART communication (when UART interface is selected). Disabling the autobaud

feature at reset sets the rate to 19,200 baud.

EEPROM interface

Three-wire EEPROM or four-wire EEPROM when EEPROM interface is selected

Refer to "2.6. EEPROM Interface (24-Pin TSSOP and 38-Pin QFN Only)" on page 31 for more details on the

various ISOmodem EEPROM options.

The next few sections describe the various reset options that must be selected for each package. In all the tables,

the following conventions apply:

0 means a 10 k pulldown resistor to ground.

1 means the pin is left open. If a pin is left open, the internal pullup resistor is normally sufficient as long as the

pin is not driven externally during reset. If there is noise or special power-sequencing situations, then an

external pullup resistor may be needed.

12 Rev. 1.3

AN93

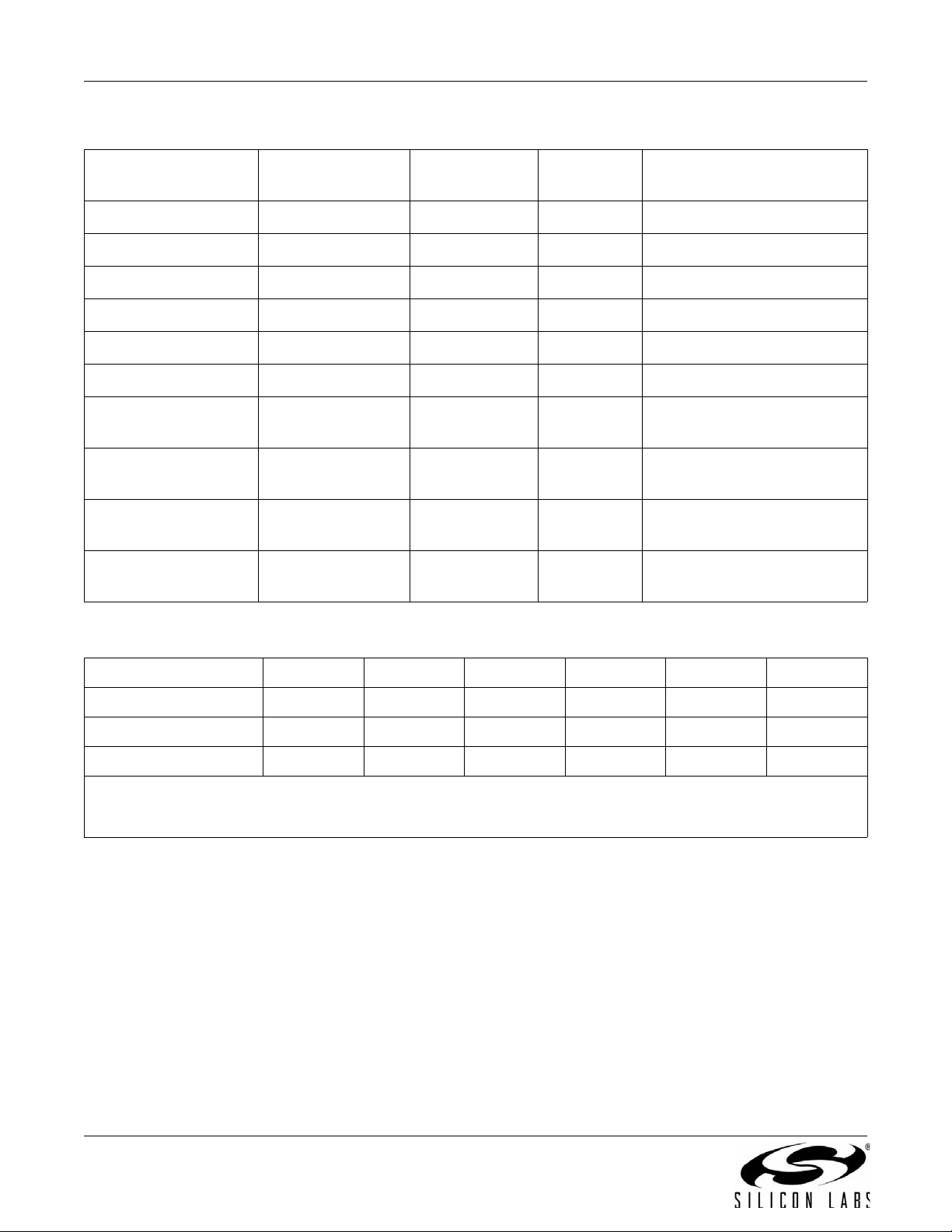

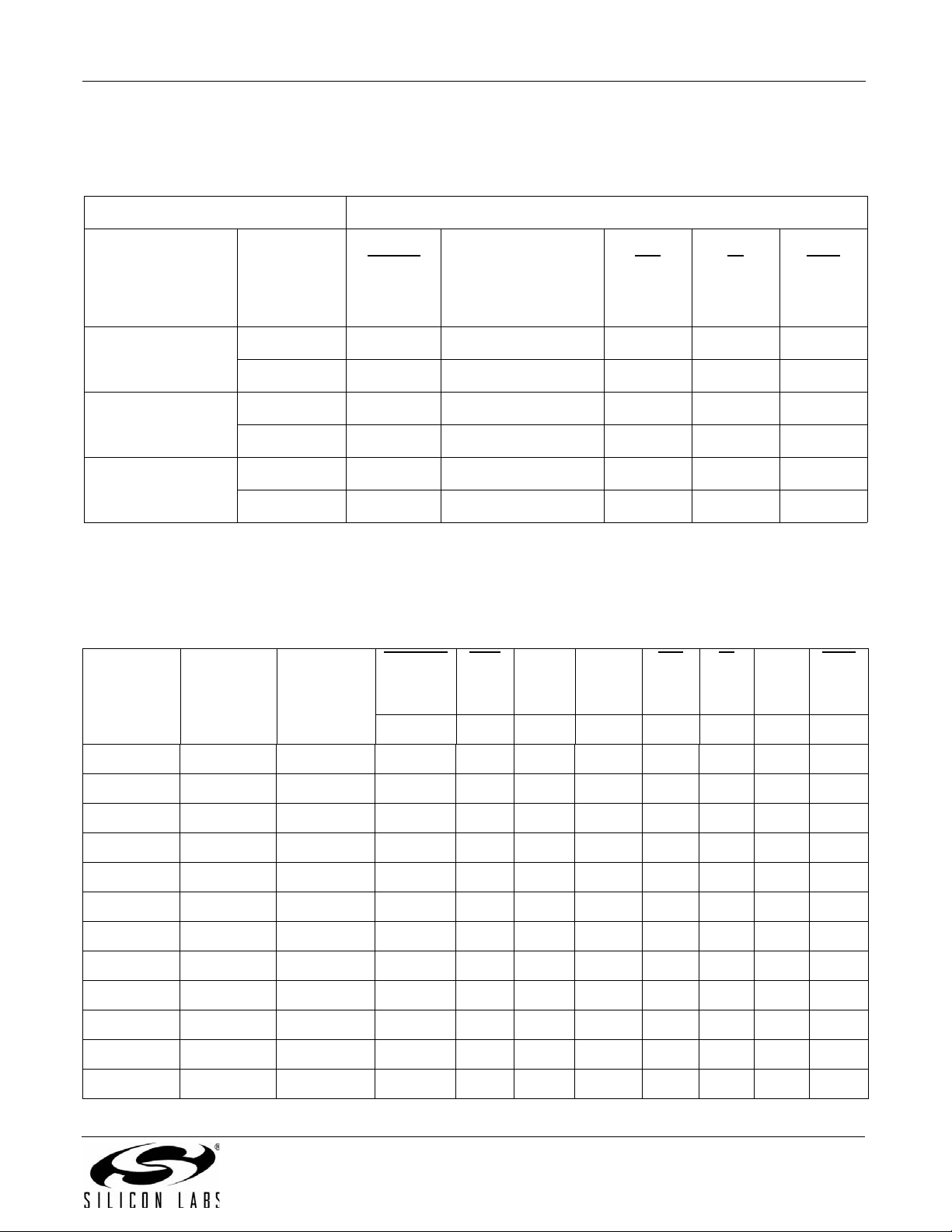

2.1.3. Reset-Strap Options for 16-Pin SOIC Package

The clock frequency and interface on the 16-pin SOIC package are selected according to Table 5 below. The

parallel interface, EEPROM and autobaud options are not available in the 16-pin SOIC package.

Table 5. SOIC-16 Reset-Strap Options

Mode Reset-Strap Pins

Interface Input Clock Pin 3

RI

UART 32 kHz 0 X 1 1 X

4.9152 MHz 1 X 1 1 1

27 MHz 1 X 1 1 0

SPI 32 kHz 1 1 X 0 1

4.9152 MHz 0 1 X 0 X

27 MHz 1 1 X 0 0

2.1.4. Reset-Strap Options for 24-Pin TSSOP Package

The pin-strapping options for the 24-pin TSSOP package are described in the three subsections below, depending

on the interface mode selected.

Pin 5, RXD/MISO Pin 7, CTS

/SCLK Pin 11

INT

Pin 15

DCD

Rev. 1.3 13

AN93

2.1.4.1. Reset Strapping Options for TSSOP-24 with UART-Interface

UART-interface options for the 24-pin TSSOP package are shown in Table 6 below.

Table 6. TSSOP-24 UART-Interface Options

Mode Reset-Strap Pins

Input Clock Autobaud

Disabled?

32 kHz No No 1 1 0 1 X

Yes No 1 1 0 0 X

4.9152 MHz No No 1 1 1 1 1

Yes No 1 1 1 0 1

27 MHz No No 1 1 1 1 0

Yes No 1 1 1 0 0

Three-Wire

EEPROM

Interface?

Yes 0 1 0 1 X

Yes 0 1 0 0 X

Yes 0 1 1 1 1

Yes 0 1 1 0 1

Yes 0 1 1 1 0

Yes 0 1 1 0 0

Pin 4

FSYNC

Pin 11, CTS

Pin 15, AOUT

Pin 16, INT

Pin 17

RI

Pin 18

SDI/EESD

Pin 23

DCD

2.1.4.2. Reset Strapping Options for TSSOP-24 with Parallel-Interface

Parallel-interface options for the 24-pin TSSOP package appear in Table 7 below. The EEPROM and autobaud

options are not available when the parallel interface is selected.

Table 7. TSSOP-24 Parallel-Interface Options

Mode Reset-Strap Pins

Input Clock Pin 9, RD

Pin 10, WR

27 MHz 1 0 0

4.9152 MHz 1 1 0

14 Rev. 1.3

Pin 11

SCLK

Pin 15

INT

2.1.4.3. Reset Strapping Options for TSSOP with SPI-Inter face

Table 8 lists the SPI-interface options for the 24-pin TSSOP package.

Table 8. TSSOP-24 SPI-Interface Clock-Frequency Options

Mode Reset-Strap Pins

AN93

Input Clock Three-Wire

EEPROM

Interface?

32 kHz No 1 1 0 1 1

Yes 0 1 0 1 1

4.9152 MHz No 1 1 0 0 X

Yes 0 1 0 0 X

27 MHz No 1 1 0 1 0

Yes 0 1 0 1 0

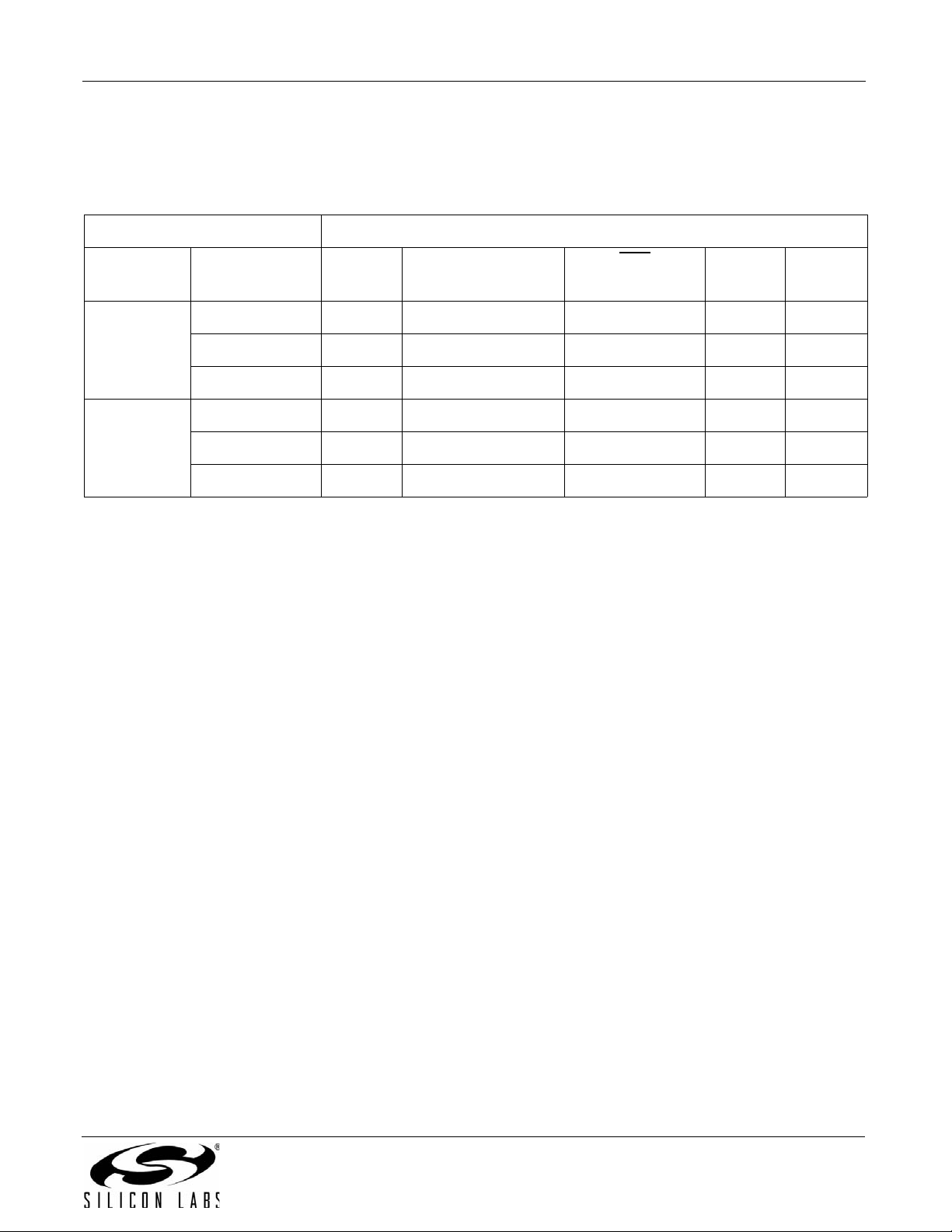

2.1.5. Reset Strapping Options for QFN Parts

2.1.5.1. Reset Strapping Options for QFN Parts with UART Operation

Table 9 lists the reset strapping options for QFN parts with UART operation.

Pin 4

FSYNC

Pin 9, RXD

Pin 11, SCLK

Pin 15, AOUT

Pin 18, SDI/EESD

Pin 16

INT

Pin 17

RI

Table 9. Reset Strapping Options for QFN Parts with UART Operation

Input Clk Auto-Baud

Disable

Three-Wire

EEPROM

Interface

FSYNCH CTS AOUT EECLK INT RI SDI DCD

Pin 23

DCD

Pin 2 Pin 21 Pin 15 Pin 13 Pin 35 Pin 19 Pin 8 Pin 28

32 kHz No No 1 1 1 1 1 1 1 1

Yes 0 1 1 1 1 1 1 1

Yes No 1 1 1 1 1 1 0 1

Yes 0 1 1 1 1 1 0 1

4.9152 MHz No N o 1 1 1 1 1 0 1 X

Yes 0 1 1 1 1 0 1 X

Yes No 1 1 1 1 1 0 0 X

Yes 0 1 1 1 1 0 0 X

27 MHz No No 1 1 1 1 1 1 1 0

Yes 0 1 1 1 1 1 1 0

Yes No 1 1 1 1 1 1 0 0

Yes 0 1 1 1 1 1 0 0

Rev. 1.3 15

AN93

2.1.5.2. Reset Strapping Options for QFN Parts with SPI Operation

Table 10 lists the reset strapping options for QFN parts with SPI operation.

Table 10. Reset Strapping Options for QFN parts with SPI Operation

Input Clk Three-Wire

EEPROM

Interface

32 kHz No 1 1 1 0 1 1 1 1

Yes 0 1 1 0 1 1 1 1

4.9152 MHz No 1 1 1 0 0 1 X 1

Yes 0 1 1 0 0 1 X 1

27 MHz No 1 1 1 0 1 1 0 1

Yes 0 1 1 0 1 1 0 1

2.1.5.3. Reset Strapping Options for QFN Parts with Parallel Operation

Table 11 lists the reset strapping options for QFN parts with parallel operation.

FSYNCH AOUT EECLK INT RI SDI DCD MISO

Pin 2 Pin 15 Pin 13 Pin 35 Pin 19 Pin 8 Pin 28 Pin 22

Table 11. Reset Strapping Options for QFN Parts with Parallel Operation

Input Clk CS

AOUT EECLK RD

Pin 21 Pin 15 Pin 13 Pin 22

32 kHz 1 0 1 1

10 1 1

4.9152 MHz 1 0 0 1

10 0 1

27 MHz 0 0 1 1

00 1 1

16 Rev. 1.3

AN93

2.2. System Interface

The ISOmodem can be connected to a host processor thro ugh a UAR T, SPI or parallel interface. Connection to the

chip requires low-voltage CMOS signal levels from the host and any other circuitry interfacing directly. The

following sections describe the digital interface options in detail.

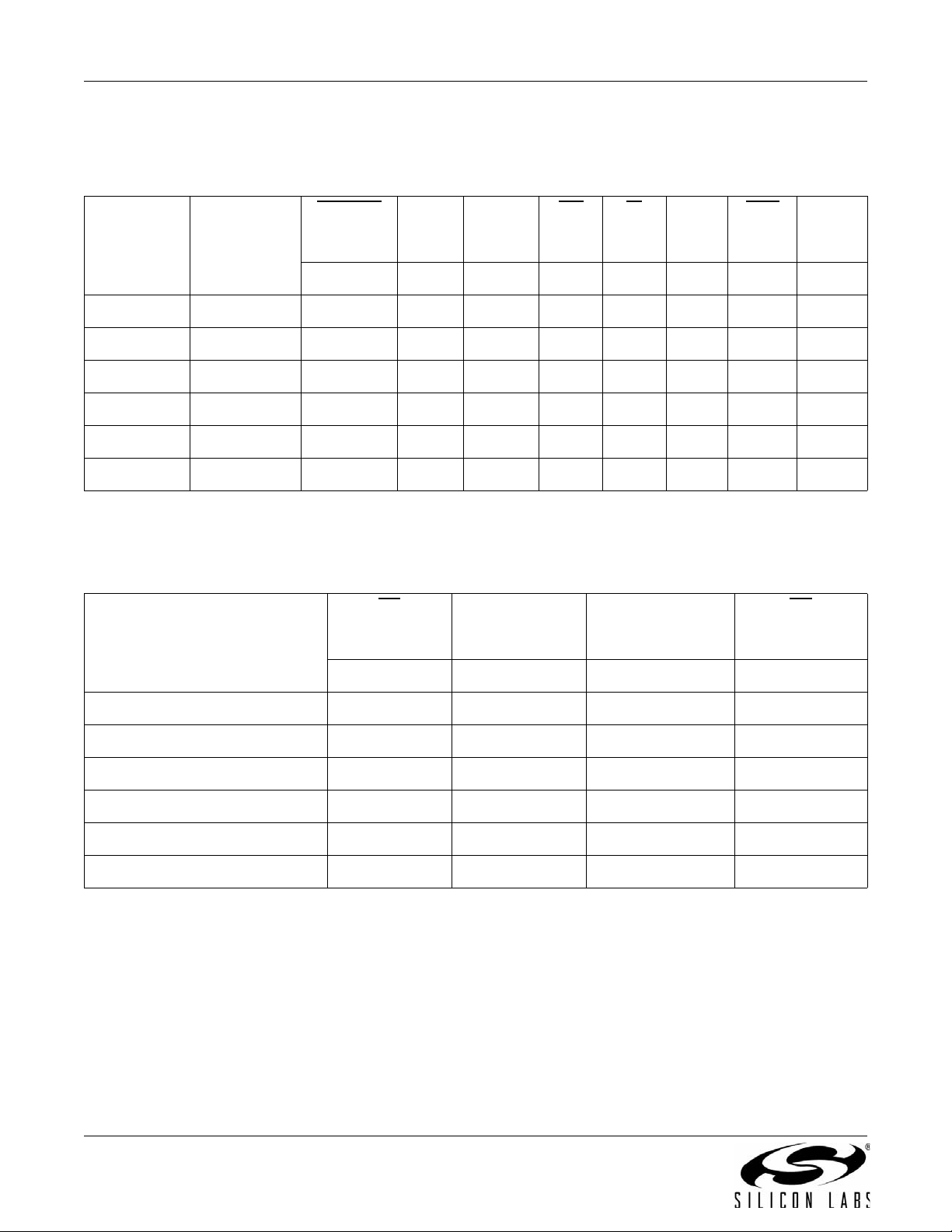

2.2.1. Interface Selection

The interface is selected during reset, as described in "2.1. Resetting the Device". Tables 12, 13, and 14 show the

functions of the affected pins for possible interface modes for 16-, 24- and 38-pin packages, respectively.

Table 12. Pin Functions vs. Interface Mode (SOIC-16)

Pin # UART Mode SPI Mode

3RI

5 RXD MISO

6 TXD MOSI

7CTS

11 INT

14 ESC ESC

15 DCD

16 RTS SS

RI

SCLK

INT

DCD

Table 13. Pin Functions vs. Interface Mode (TSSOP-24)

Pin # UART Mode SPI Mode Parallel Mode

2 FSYNC

3 CLKOUT (SSI) CLKOUT (SSI) A0

8RTS

9 RXD MISO RD

10 TXD MOSI WR

11 CTS SCLK CS

(SSI) FSYNC (SSI) D6

SS D7

15 AOUT AOUT INT

16 INT INT D0

17 RI

18 SDI (SSI) SDI (SSI) D2

22 ESC ESC D3

23 DCD

24 SDO (SSI) SDO (SSI) D5

Rev. 1.3 17

RI D1

DCD D4

AN93

Table 14. Pin Functions vs. Interface Mode (QFN-38)

Pin # UART Mode SPI Mode Parallel Mode

35 INT

34 GPIO18 GPIO18 D0

33 GPIO17 GPIO17 D1

32 GPIO16 GPIO16 D2

31 GPIO23 GPIO23 D3

30 GPIO24 GPIO24 D4

29 ESC D5

28 DCD

24 RTS SS

23 TXD MOSI WR

22 RXD MISO RD

21 CTS SCLK CS

20 GPIO11 G PIO11 A0

19 RI

INT INT

D6

D7

18 Rev. 1.3

2.2.2. Interface Signal Description

The following tables describe each set of UART, parallel and SPI interface signals:

Table 15. UART-Interface Signals

Signal Direction Description

TXD Input Data input from host TXD pin

RXD Output Data output to host RXD pin

AN93

RTS

CTS

Input Active-low request-to-send input for flow control

Output Clear to send: Si249 3 is ready to receive data on the TXD pin (active low)

Table 16. SPI-Interface Signals

Signal Direction Description

SCLK Input Serial data clock

MISO Output Serial data output

MOSI Input Ser ia l data input

SS

INT

Input Chip select (active low)

Output Interrupt (active low)

Table 17. Parallel-Interface Signals

Signal Direction Description

A0 Input Register selection (address inpu t)

CS

RD

WR

D[7:0] Bidirectional Parallel data bus

INT

Input Chip select (active low)

Input Read enable (active low)

Input Write enable (active low)

Output Interrupt (active low)

2.2.3. UART Interface Operation

The UART interface allows the host processor to communicate with the modem controller through a UART driver.

In this mode, the modem is analogous to an external “box” modem. The interface pins are 5 V tolerant and

communicate with TTL-compatible, low-voltage CMOS levels. RS232 interface chips, such as those used on the

modem evaluation board, can be used to make the UART interface directly compatible with a PC or terminal serial

port.

2.2.3.1. UART Options

The DTE rate is set by the autobaud feature after reset. When autobaud is disabled, the UART is configured to

19.2 kbps, 8-bit data, no parity and 1 stop bit on reset. The UART data rate is programmable from 300 bps to

307.2 kbps with the AT\Tn command (see Table 42, “Extended AT\ Command Set,” on page 81). After the AT\Tn

command is issued, the ISOmodem echoes the result code at the old DTE rate. After the result code is sent, all

subsequent communication is at the new DTE rate.

The DTE baud clock is within the modem crystal tolerance (typically ±50 ppm), except for DTE rates that are

uneven multiples of the modem clock. All DTE rates are within the +1%/–2.5% required by the V.14 specification.

Table 18 shows the ideal DTE rate, the actual DTE rate, and the approximate error.

Rev. 1.3 19

AN93

D1D0 D2 D3 D4 D5 D6 D7

START

BIT

MARK

STOP

BIT

BIT TIMES

BIT SAMPLING

SPACE

D1D0 D2 D3 D4 D5 D6 D7

START

BIT

MARK

STOP

BIT

BIT TIMES

BIT SAMPLING

SPACE

D8

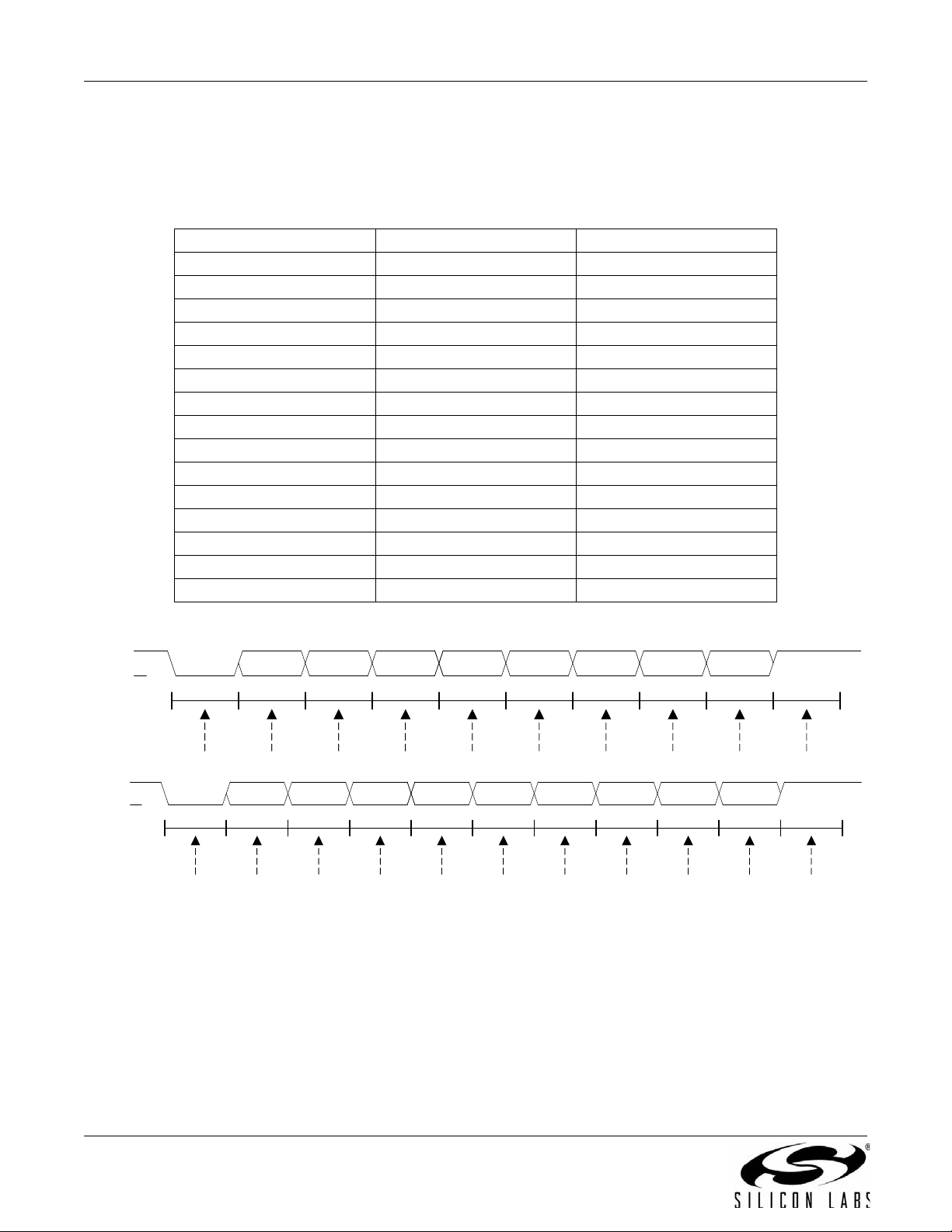

The UART interface synchronizes on the start bits of incoming characters and samples the data bit field and stop

bits. The interface is designed to accommodate character lengths of 8, 9, 10, and 11 bits giving data fields of 6, 7,

8, or 9 bits. Data width can be set to 6, 7, or 8 bits with the AT\Bn command. Parity can be set to odd, even, mark,

or space by the AT\Pn command in conjunction with AT\B2 or AT\B5. Other AT\Bn settings have no parity.

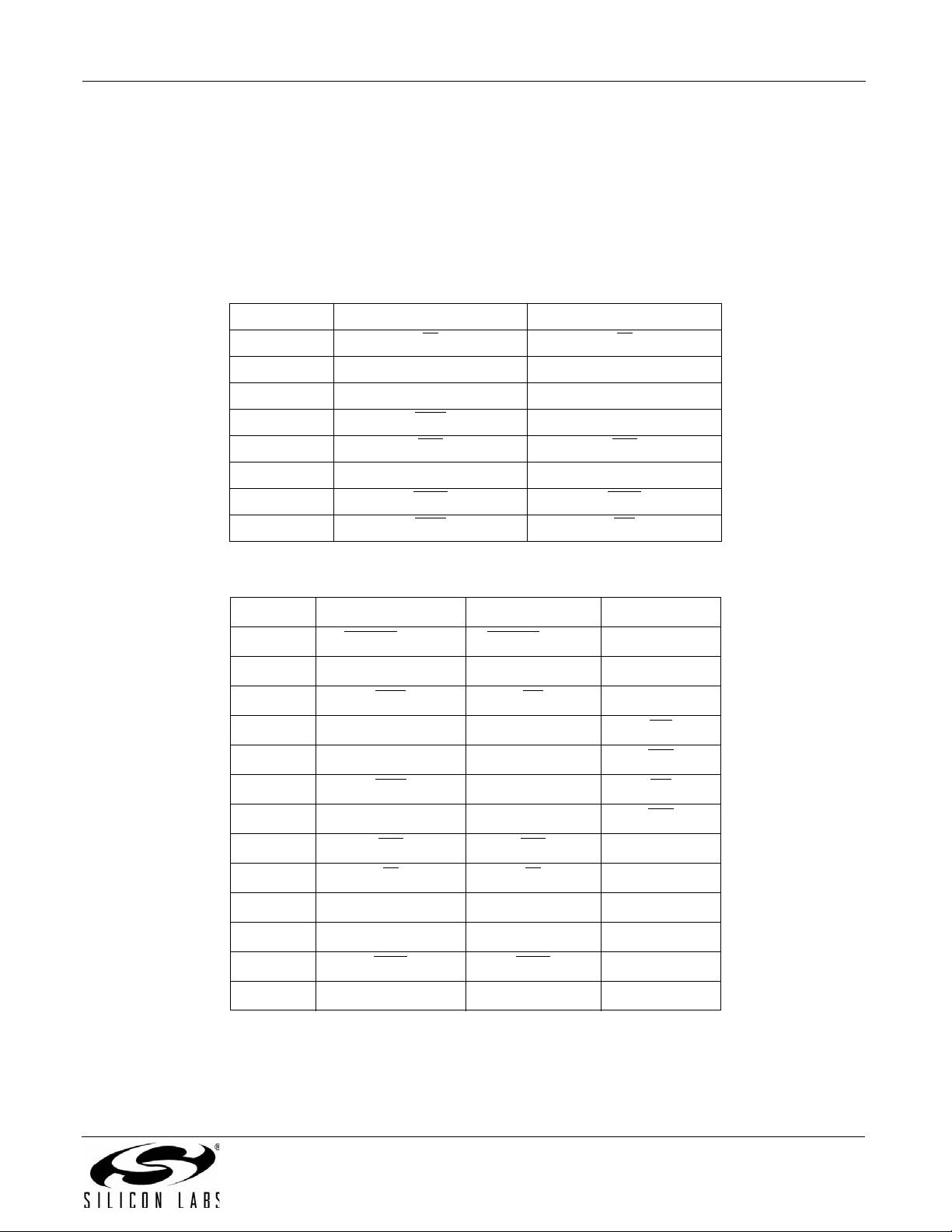

Table 18. DTE Rates

Ideal DTE Rate (bps) Actual DTE Rate (bps) Approximate Error(%)

300 300

600 600

1200 1200

2400 2400

7200 7202 0.01

9600 9600

12000 12003 0.02

14400 14400

19200 19200

38400 38400

57600 57488 0.2

115200 115651 0.4

230400 228613 0.8

245760 245760

307200 307200

Figure 2. Asychronous UART Serial Interface Timing Diagram

2.2.3.2. Autobaud

When set in UART interface mode, the ISOmodem in cludes an automatic baud rate detection feature that allows

the host to start transmitting data at any standard DT E r ate from 300 bps to 307.2 kbps. This feature is enabled by

default. When autobaud is enabled, it continually adjusts the baud rate, and the ISOmodem always echoes result

codes at the same baud rate as the most recently received character from the host. Autobaud can be turned off

using AT commands \T0 through \T15, and \T17. Host software should disable autobaud operation once the DTE

rate has been established. This prevents transients on TXD to cause inadvertent baud rate changes.

Autobaud is off when dialing, answering, and in data mode. When autobaud mode is off, the baud rate is set to the

most recently-active baud rate prior to entering one of these states. When autobaud mode is on, autoparity is

performed when either “at” or “AT” is detected. Autoparity detects the formats listed in Table 19.

20 Rev. 1.3

AN93

:

Table 19. Serial Formats Detected in Autobaud Mode

Symbol Data bits Parity Stop bits

7N1 7 None (mark) 1

7N2 7 None (mark) 2

7S1 7 None (space) 1

7O1 7 Odd 1

7E1 7 Even 1

8N1 8 None (mark) 1

8E1 8 Even 1

8O1 8 Odd 1

9N1 9 None (mark) 1

Note: For 7N1, the modem is programmed to 7 data bits, mark parity and one stop bit. This may be changed with the AT\P and

AT\B commands. In autobaud mode, 7N1 is properly interpreted and echoed, but the AT\P and AT\B commands must be

sent prior to dialing in order to lock the parity and format to 7N1. Otherwise, the ISOmodem lo cks to 7 bits, mark parity

and two stop bits (7N2).

2.2.3.3. Flow Control

The ISOmodem supports flow control through RTS

from the terminal (DTE) to the modem (DCE) indicating data may be sent from the modem to the terminal. CTS

(clear-to-send) is a control signal from the modem (DCE) to the terminal (DTE) indicating data may be se nt from

the terminal to the modem for transmission to the remote modem. This arrangement is typically referred to as

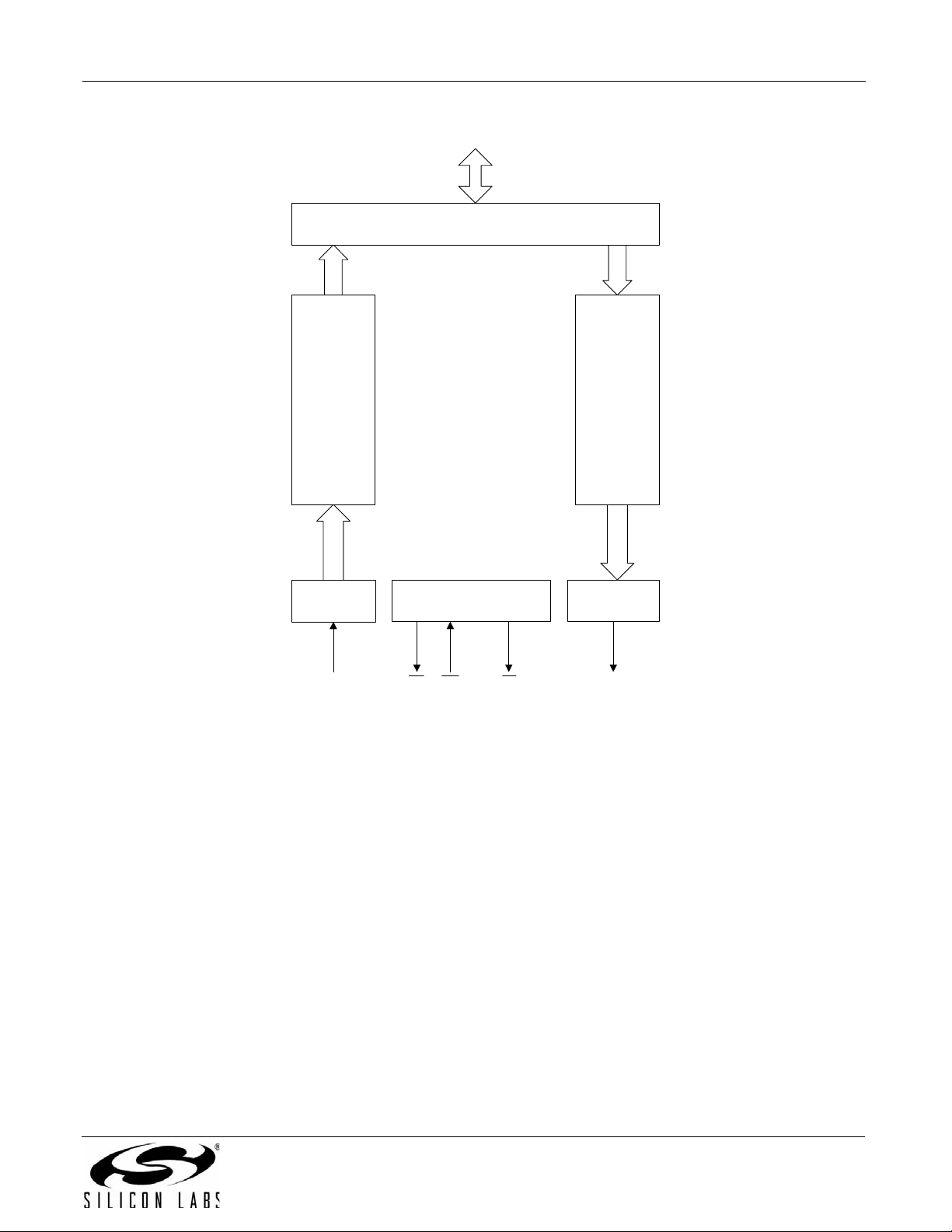

hardware flow control. There is a 14-character FIFO and a 1024 character elastic transmit buffer (see Figure 3).

goes inactive (high) when the 1024 character buffer reaches 796 characters, then reasserts (low) when the

CTS

buffer falls below 128 characters. There is no provision to compensate for FIFO overflow. Data received on TXD

when the FIFO is full are lost.

XON/XOFF is a software flow control method in which the modem and terminal control the data flow by sending

XON characters (^Q/0x11) and XOFF characters (^S/0x13). XON/XOFF flow control is enabled on the ISOmodem

with AT\Q4.

does not de-assert during a retrain (see Table 45: S9, Carrier presence timer and S10, Carrier loss timer).

DCD

always deasserts during initial training, retrain, and at disconnect regardless of the \Qn setting. For \Q0 CTS,

CTS

flow control is disabled; CTS

automatic retrains. The host can force a retrain by escaping to the command mode and sending ATO1 or ATO2.

The DCD

pin can be programmed to monitor the bits in r egister U7 0 listed in Table 20. The RI, PPD, OCD, CID, and RST bits

are sticky, and the AT:I command reads and clears these signals and deactivates the INT

and RI pins can be used as hardware monitors of the car rier detect an d ring sig nals. Add itionally, the INT

is inactive during data transfer. The modem remains in the data mode during normal

/CTS and XON/XOFF. RTS (request-to-send) is a control signal

pin if INT is enabled.

Rev. 1.3 21

AN93

796 Characters

128 Characters

1024 Character Elastic Tx Buffer

SRAM

CTS Deasserts

CTS A sserts

Transmit

14-Character

Hardw are

Buffer

Tx D ata

CTS

796 Characters

128 Characters

1024 Character Elastic Rx Buffer

SRAM

Receive

12-Character

Hardw are

Buffer

Rx data

RTS

RXF bit

REM bit

Parallel

Mode

Table 20. Register U70 Signals INT

Signal U70 Bit Function

DCD 0 Data Carrier Detect—active high (inverse of DCD

RI 1 Ring Indicator—active high (inverse of RI

PPD 2 Parallel Phone Detect

OCD 3 Overcurrent Detect

CID 4 Caller ID Preamble Detect

Can Monitor

pin)

pin)

Figure 3. Transmit Data Buffers

22 Rev. 1.3

Figure 4. Receive Data Buffers

A block diagram of the UART in the serial interface mode is shown in Figure 5.

11 Bits

to Data Bus

CONTROL

RX Shift

Register

TX Shift

Register

TX FIFO

MUX

TXD

(10)

CTS

(11)

RTS

(8)

RXD

(9)

INT

(16)

RX FIFO

.

AN93

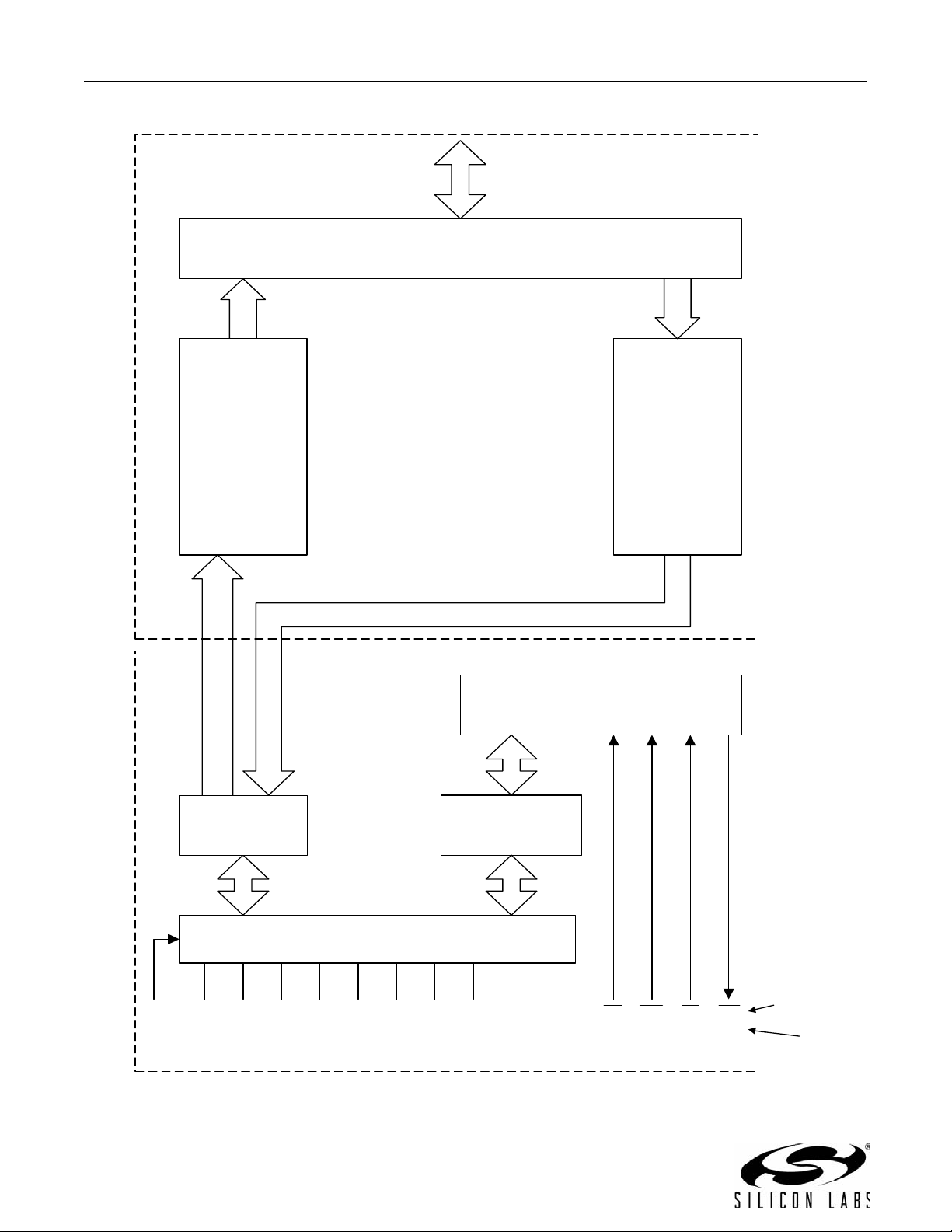

2.2.4. Parallel and SPI Interface Operation

Refer to "2.1. Resetting the Device" on page 11 for interface selection. The parallel interface has an 8-bit data bus

Figure 5. UART Serial Interface

and a single address bit. The SPI likewise operates with 8-bit data transfers, using a single address bit. When the

parallel or SPI interface mode is selected, the modem must be configured fo r a DTE interface or 8N1 only. The host

processor must calculate parity for the MSB. The modem sends bits as received by the host and does not calculate

parity. Refer to "Appendix C—Parallel/SPI Interface Software Implementation" on page 290 for detailed parallel or

SPI interface application information.

The parallel or SPI interface uses the FI FOs t o bu ffer data in the sam e way as in UART mode, with the addit ion o f

Hardware Interface Registers 0 (HIR0) and Hardware Interface Register 1 (HIR1). The Hardware Interface

Registers were formerly called Parallel Interface Registers (PIR0 and PIR1) in older products, because those

products would support only a parallel interface. Flow contr ol must be imple mented by monitor ing REM a nd TXE in

HIR1. There is no protection against FIFO overflow. Data transmitted when the transmit FIFO is full are lost.

Figure 6 shows the interaction of the transmit and receive FIFOs with the Hardware (Parallel) Interface Registers in

the case of a parallel interface. The arrangement is sim ilar wh en the SPI inter face is selecte d. Table 21 on page 25

shows a bit map of HIR0 and HIR1.

UART oriented control lines, such as RTS and CTS, are not used in Parallel and SPI Interface mode. They are

replaced by bits in the HIR1 register.

SPI and parallel operation only support s 8- bit dat a word s. The longer wor ds that are implied by the \B5 (8P1) & \B6

8X1 commands are not allowed. These commands should not be used.

Rev. 1.3 23

AN93

11 Bits

to Da ta Bus

CONTROL

Para lle l I/F

Register 1

MUX

Para lle l I/F

Register 0

A

0

(3)

D

0

(16)

D

1

(17)

D

2

(18)

D

3

(22)

D

4

(23)

D

5

(24)

D

6

(4)

D

7

(8)

RD

(9)WR(10)CS(11)

INT

(15)

MUX

Parallel Interface Unique

Shared-Serial/Parallel

Parallel mode pin function

Parallel mode pin number

TX FIFO

14 Characters

RX FIFO

12 Characters

24 Rev. 1.3

Figure 6. Parallel Interface

AN93

Table 21. Hardware Interface Register Bit Map

A0 RD WR Action Register D7 D6 D5 D4 D3 D2 D1 D0

0 0 1 Read HIR0 Modem data or command from receive FIFO

0 1 0 Write Modem data or command to transmit FIFO

1 0 1 Read HIR1 RXF TXE REM INTM INT ESC RTS

1 1 0 Write RXF TXE *Note INTM *Note ESC RTS n/a

*Note: RE M and INT are read-only bits.

2.2.4.1. Hardware Interface Register 0

Hardware Interface Register 0 (HIR0) is the eight-bit wide read/write location where modem data and commands

are exchanged with the host. Writing a byte to the HIR0 adds that byte to the modem’s transmit FIFO (AT

command buffer in command mode or data transmission in data mode). If data are available (modem data in data

mode or command responses, such as OK, in command mode), reading from the HIR0 fetches data from the

modem’s receive FIFO. The maximum burst data rate is approximately 350 kbps (45 kBps).

2.2.4.2. Hardware Interface Register 1

Hardware Interface Register 1 (HIR 1) contains various s tatus and control flags for use by the host to perform data

flow control, to escape to command mode and to query various in terrup t co ndition s. The HIR1 bit ma p is de scr ibe d

in Table 22. This register is reset to 0x63.

CTS

Table 22. Hardware Interface Register 1

Bit Name R/W Reset Function

7RXFR/W 0Receive FIF O Almost Full

6TXER/W 1Transmit FIFO Almost Empty

5REM R 1Receive FIFO Empty

4INTMR/W 0Interrupt Mask

0 = INT pin triggered on risin g ed ge of RXF or TXE only

1 = INT pin triggered on rising edge of RXF, TXE or INT (bit 3 below)

3INT R 0Interrupt

0 = No interrupt

1 = Interrupt triggered

2 ESC R/W 0 Escape

1RTS

0CTS

Bit 7 (RXF) is a read/write bit that gives the status of the 12-byte deep receive FIFO. If RXF = 0, the receive FIFO

contains less than 10 bytes. If RXF = 1, the receive FIFO contains more than 9 bytes and is full or almost full.

Writing RXF = 0 clears the interrupt.

R/W 1 Request-to-Send (active low) — Deprecated — for flow control, use the

TXE and REM bits for polling- or interrupt-based communication.

This bit must be written to zero.

R1Clear-to-Send (active low) — Deprecated — for flow control, use the TXE

and REM bits for polling- or interrupt-based communication.

Rev. 1.3 25

AN93

Bit 6 (TXE) is a read/write bit that gives the status of the 14-byte deep transmit FIFO. If TXE = 0, the transmit FIFO

contains three or more bytes. If TXE = 1, the transmit FIFO contains two or fewer bytes. Writing TXE = 0 clears the

interrupt but does not change the state of TXE.

Bit 5 (REM) is a read-only bit that indicates when the receive FIFO is empty. If REM = 0, the receive FIFO contains

valid data. If REM = 1, the r eceive FIFO is empty. The timer interrupt set by U6F ensures that the receive FIFO

contents 9 bytes are serviced properly.

Bit 4 (INTM) is a read/write bit that controls whether or not INT (bit 3) triggers the INT

Bit 3 (INT) is a read-only bit that reports Interrupt status. If INT = 0, no interrupt has occurred. If INT = 1, an

interrupt due to CID, OCD, PPD, RI, or DCD (U70 bits 4 , 3, 2, 1, 0, respectively) has occurr ed. This bit is reset by :I.

Bit 2 (ESC) is a read/write bit that is functionally equivalent to the ESC pin in the serial mode. The operation of this

bit, like the ESC pin, is enabled by setting U70 [15] (HES) = 1.

The use of bits 1 and 0 (RTS

of bits 6 and 5 (TXE and REM) is recommended for polling- and interrupt-based communication.

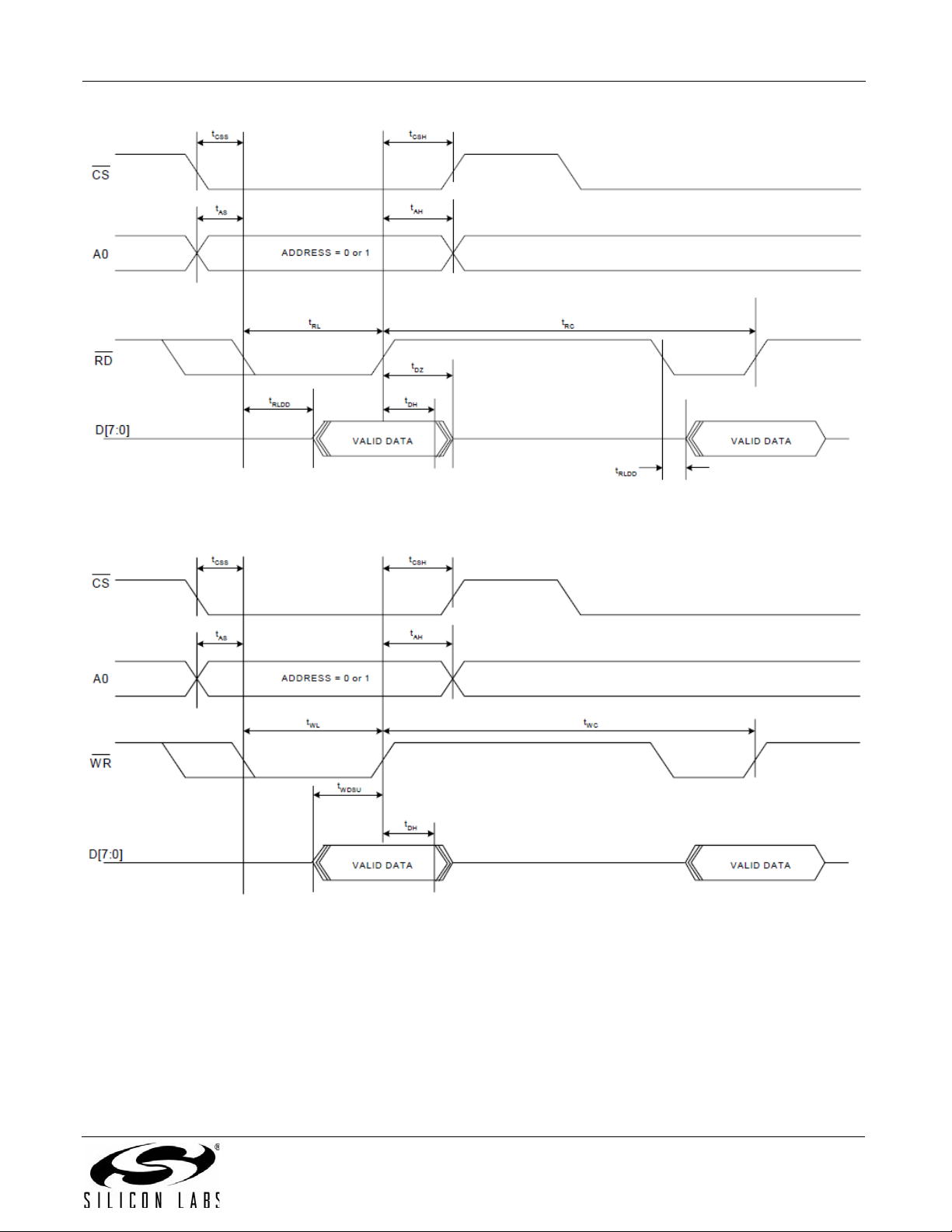

2.2.4.3. Parallel Interface Operation

When the device is powered up for parallel interface, the pins include eight data lines (D7–D0), a single address

(A0), a read strobe (RD

the parallel-interface signals:

and CTS) has been deprecated for both parallel and SPI interfaces. Instead, the use

), a write strobe (WR), an interrupt line (INT), and chip select (CS). Table 23 summarizes

Table 23. Parallel Interface Signals

pin.

Signal Function Direction

CS

A0 Register address Input

RD

WR

D[7:0] Data bus Bidirectional

INT

Refer to the device data sheet for timing characteristics. Address pin A0 allows the host processor to choose

between the two interface register s, HIR0 and HIR1. The timing diagrams below show typical parallel-interface

operation. Refer to the respective product data sheets for timing specifications.

Chip Select (active low) Input

Read strobe (active low) Input

Write strobe (active low) Input

Interrupt (active low) Output

26 Rev. 1.3

Figure 7. Parallel Interface Read Timing

AN93

Figure 8. Parallel Interface Write Timing

Rev. 1.3 27

AN93

Z

Z

Z

Z

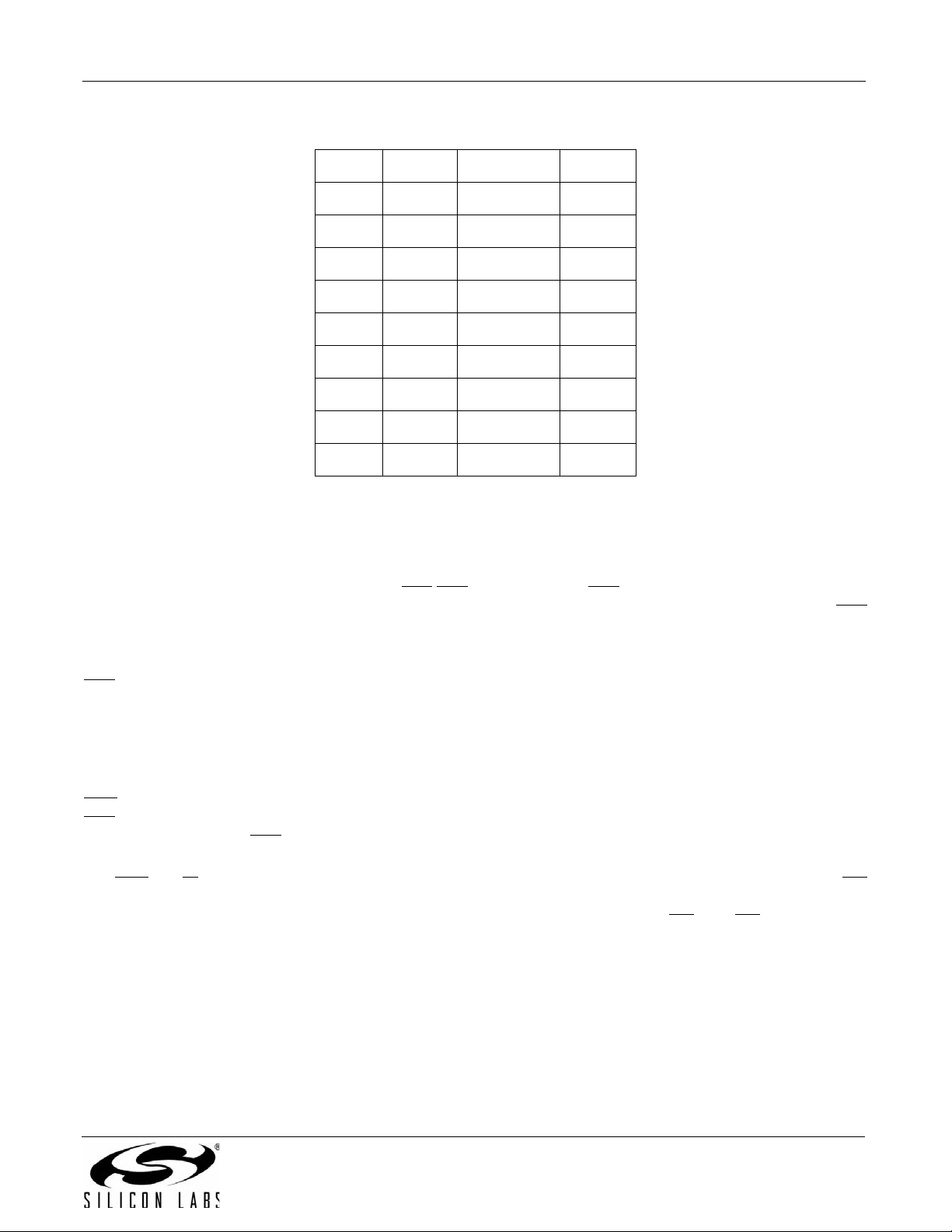

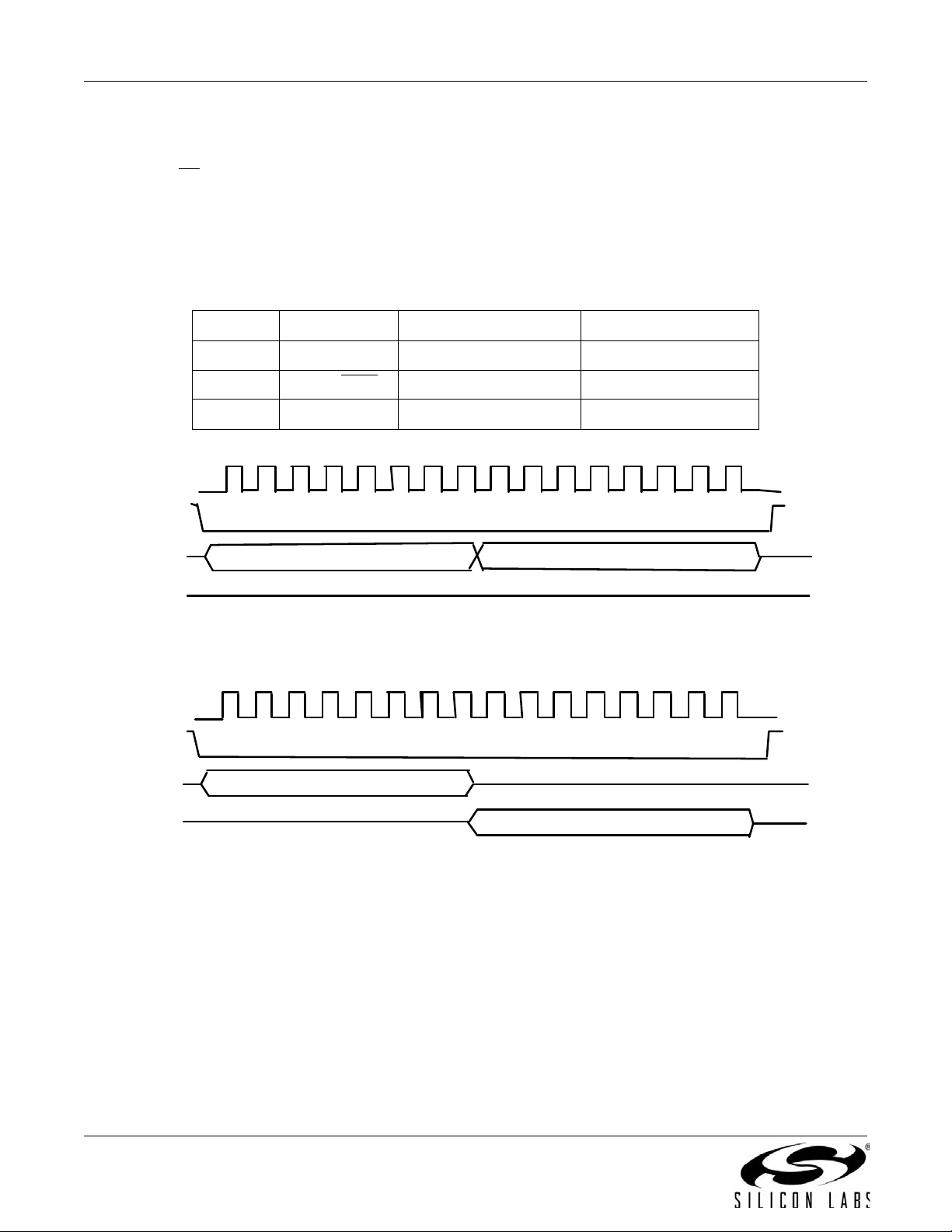

2.2.4.4. SPI Interface Operation

SPI interface operation is supported in the Si2493/57/34/15/04 Re vision D o r later and the Si24 94/39 Revision A or

later. When the device is powered up for SPI interface, the modem becomes an SPI slave, and the pins are

configured to SS

modem) and SCLK (serial data clock input). The HIR0 and HIR1 registers described above are also available in

SPI mode. Each SPI operation consists of a control-and-address byte and a data byte. The bit definitions of the

control-and-address byte are shown in Table 24. The timing diagrams that follow show SPI read and write

waveforms. Refer to the device data sheet for timing characteristics.

(chip select input, active low), MOSI (serial data input to modem), MISO (serial data output from

Table 24. SPI Control-and-Address Bit Definitions

Bit Function Meaning when High Meaning when Low

7 Address Access HIR1 Access HIR0

SCK

NSS

MISO

MOSI

SCK

NSS

MISO

MOSI

6 Read/Write

5:0 Reserved Not allowed Must be all zeroes

Ad dre ss /C ont r ol

Read register Write register

Data

SPI2‐ByteWriteProtocol

Address/Control

Data

Hi‐

Hi‐

Hi‐

Hi‐

SPI2‐ByteRe ad Pr oto col

Figure 9. SPI Read and Write Timing Diagrams

2.2.4.5. Interface Communication Modes

Data flow control is implemented in the SPI and parallel interfaces differently from UART mode. When parallel or

SPI mode is selected, data communication may be driven by interrupts or by polling. Refer to "Appendix C—

Parallel/SPI Interface Software Implementation" on page 290 for implementation details for both methods. The

parallel and SPI interfaces have four sources of interrupts and only one inter rupt pin. The four interrupts are:

1. RXF Interrupt: receive FIFO almo st full

2. TXE Interrupt: transmit FIFO almost empty

3. Timer Interrupt: receive FIFO not empty

4. U70 Interrupt: various conditions, such as ringing, parallel phone pickup, etc. as defined in register U70

The source of the interrupt can be determined by reading HIR1.

28 Rev. 1.3

AN93

2.3. Isolation Capacitor Interface

The isolation capacitor is a proprietary high-speed interface connecting the modem chip and the DAA chip through

a high-voltage isolation barrier provided by two capacitors. It serves three purposes. First, it transfers control

signals and transmit data from the modem chip to the DAA chip. Second, it transfers receive and status data from

the DAA chip to the modem chip. Finally , it provides po wer from th e mo dem chip to the DAA chip while the modem

is in the on-hook condition. The signaling on this interface is intended for communication between the modem and

the DAA chips and cannot be used for any other purpo se. It is import ant to kee p the length of the ISOcap™ p ath as

short and direct as possible. The layout guidelines for the pins and components associated with this interface are

described in "4.4. Layout Guidelines" on page 49 and must be carefully followed to ensure proper operation and

avoid unwanted emissions.

2.4. Low-Power Modes

2.4.1. Power-Down Mode

The Power-Down mode is a lower power state than sleep mode. It is entered immediately upon writing

U65 [13] (PDN) = 1. Once in the Power-Down mode, the modem requires a hardware reset via the RESET

become active again.

2.4.2. Wake-on-Ring Mode

The ISOmodem can be set to enter a low-power wake-on-ring mode when not connected. Wake-on-ring mode is

entered using the command AT&Z. The ISOmodem returns to the active mode when one of the following happens:

There is a 1 to 0 transition on TXD in the UART mode

There is a 1 to 0 transition on CS in the parallel mode

There is a 1 to 0 transition on SSS in the SPI mode

An incoming ring is detected

A parallel telephone is picked up

Line polarity reversal

2.4.3. Sleep Mode

The ISOmodem can be set to enter a low-power sleep mode when not connected and after a period of inactivity

determined by the S24 register.

The ISOmodem enters the sleep mode S24 seconds after the last DTE activity, after the transmit FIFO is empty,

and after the last data are received from the remote modem. The ISOmodem returns to the active mode when one

of the following happens:

There is a 1 to 0 transition on TXD in the UART mode

There is a 1 to 0 transition on CS in the parallel mode

There is a 1 to 0 transition on SSS in the SPI mode

An incoming ring is detected

A parallel telephone is picked up

Line polarity reversal

The delay range for S24 is 1 to 255 seconds. The default se tting of S24 = 0 disables the sleep timer and keeps the

modem in the normal power mode regardless of activity level.

pin to

Rev. 1.3 29

AN93

Si24xx Modem

Si3000 Voice Codec

Si30xx

DAA

Handset

HOST

AT commands

Responses

2- wire

SDISDO

FSYNC MCLK

CLKOUT

SDI

SDO

FSYNC

TDMA Interface

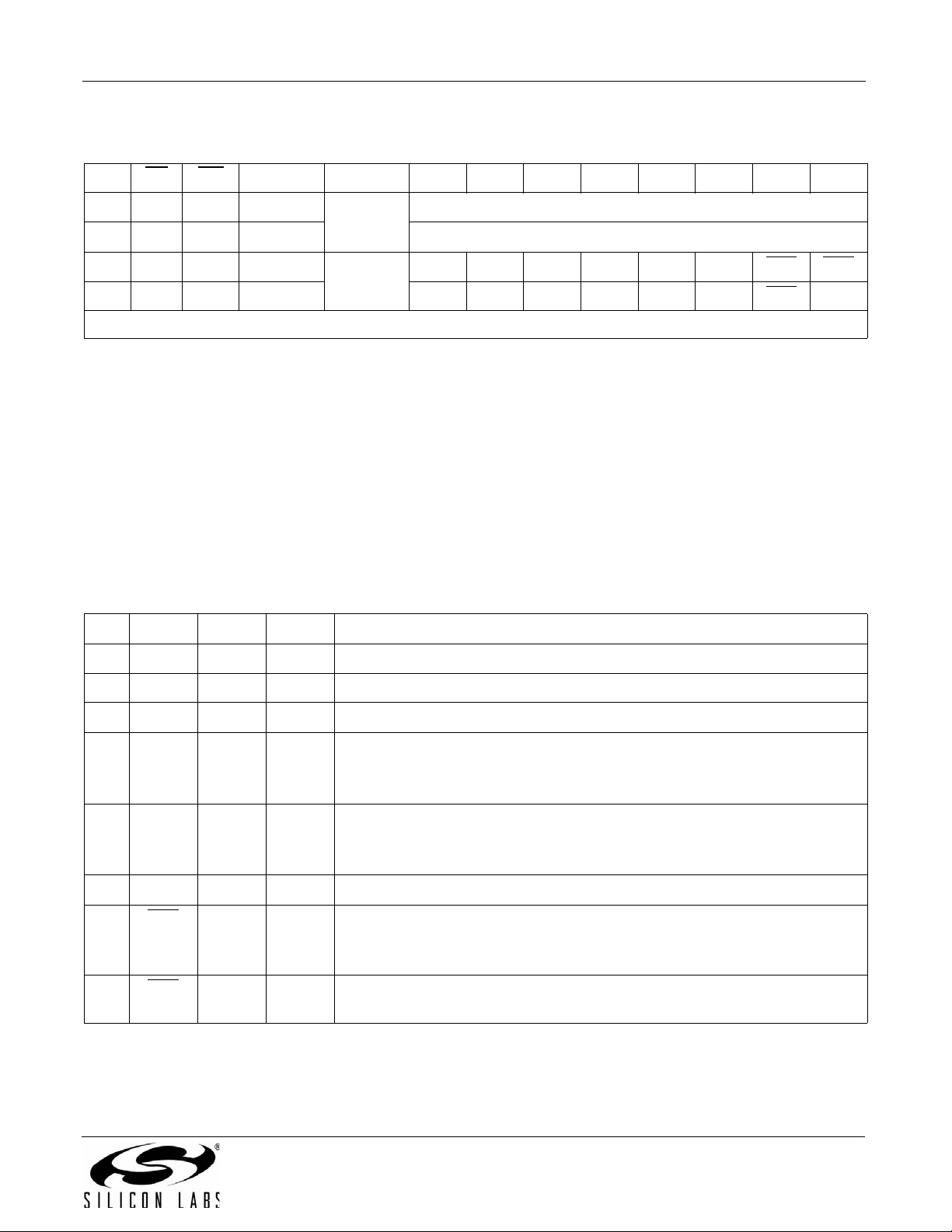

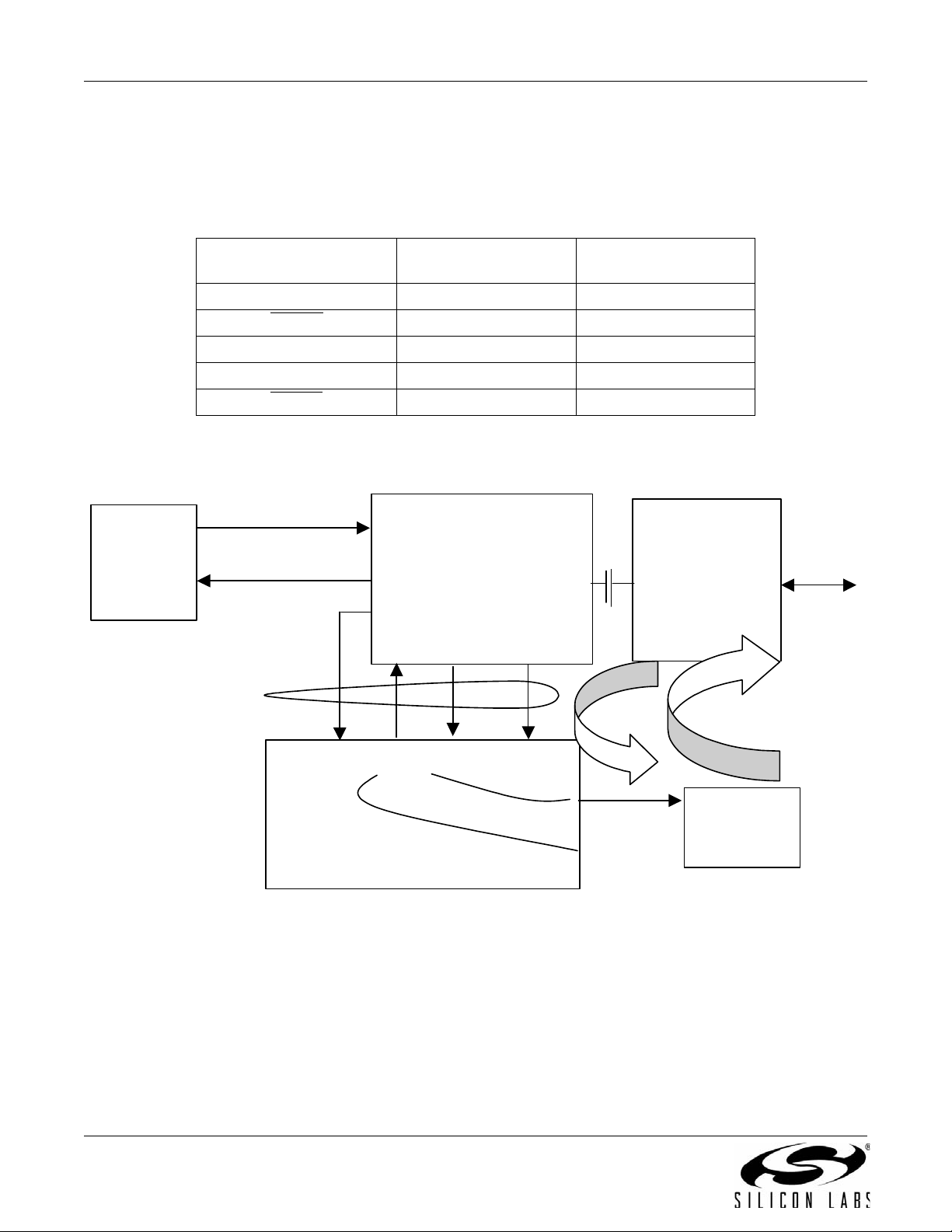

2.5. SSI/Voice Mode (24-Pin TSSOP and 38-Pin QFN Only)

Voice mode is supported in the Si2439 and the Si2494. Table 25 lists the pin connections for the ISOmodem SSI

interface. This interface enables Voice Mode operation. See "7. Handset, TAM, and Speakerphone Operation" on

page 173 for additional information.

Table 25. SSI Interface Pin Connection

Signal Pin Number

(TSSOP-24)

CLKOUT 3 3

FSYNC

SDI 18 8

SDO 24 9

RESET

The Si3000 is used in conjunction with the ISOmodem to transmit and receive 16-bit voice samples to and from

telephone lines as shown in Figure 10.

42

12 16

Pin Number

(QFN-38)

Figure 10. Voice Mode Block Diagram

30 Rev. 1.3

Loading...

Loading...