Page 1

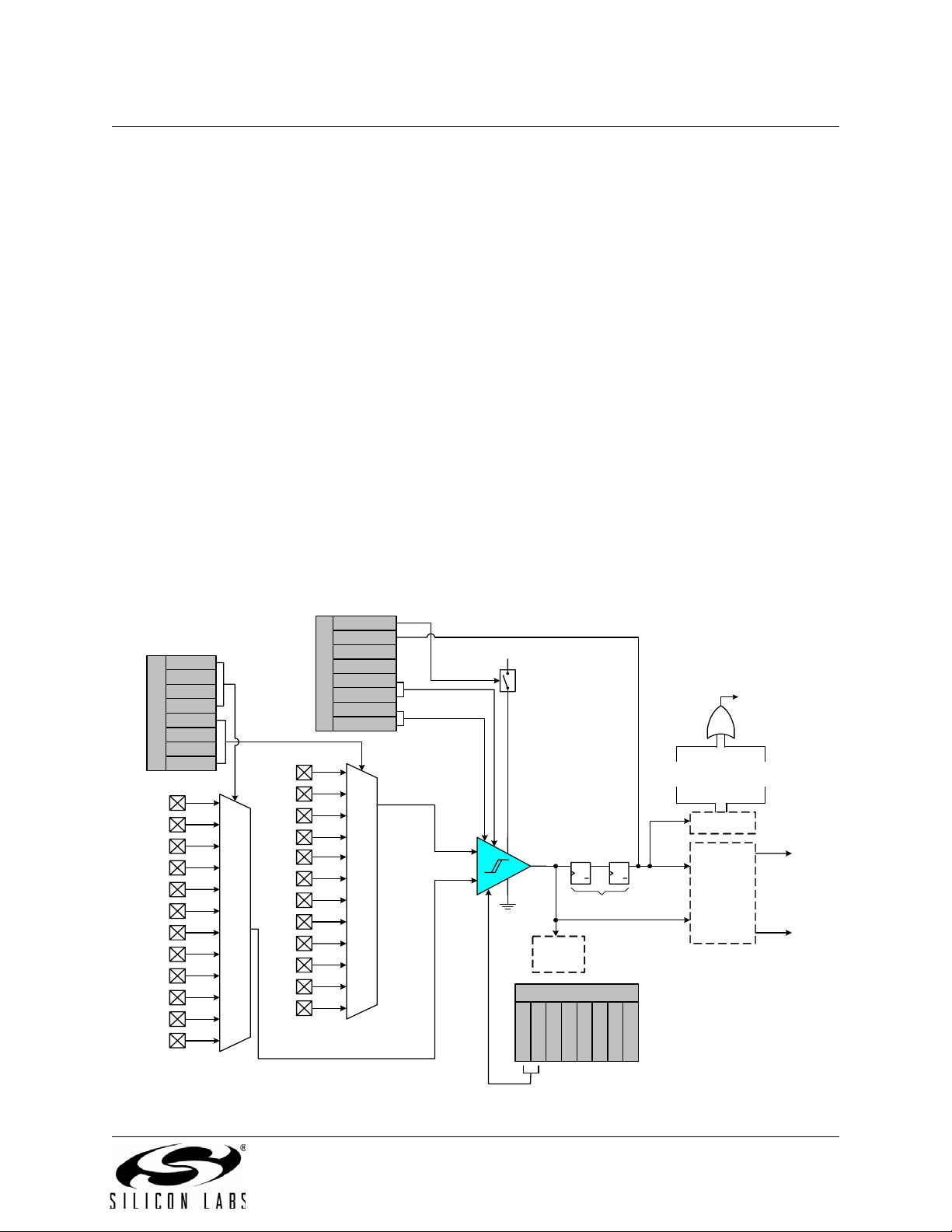

C8051F410/1/2/3

2.0 V, 32/16 kB Flash, smaRTClock, 12-bit ADC

Analog Peripherals

- 12-Bit ADC

• ±1 LSB INL; no missing codes

• Programmable throughput up to 200 ksps

• Up to 24 external inputs

• Data dependent windowed interrupt generator

• Built-in temperature sensor (±3 °C)

-

Two 12-Bit Current Mode DACs

- Two Comparators

• Programmable hysteresis and response time

• Configurable as wake-up or reset source

- POR/Brownout Detector

- Voltage Reference—1.5, 2.2 V (programmable)

On-Chip Debug

- On-chip debug circuitry facilitates full-speed, non-

intrusive in-system debug (No emulator required)

- Provides breakpoints, single stepping

- Inspect/modify memory and registers

- Complete development kit

Supply Voltage 2.0 to 5.25 V

- Built-in LDO regulator: 2.1 or 2.5 V

High Speed 8051 µC Core

- Pipelined instruction architecture; executes 70% of

instructions in 1 or 2

system clocks

- Up to 50 MIPS throughput with

50 MHz system clock

- Expanded interrupt handler

Memory

- 2304 bytes internal data RAM (256 + 2048)

- 32/16 kB Flash; In-system programmable in

byte sectors

512

- 64 bytes battery-backed RAM (smaRTClock)

Digital Peripherals

- 24 port I/O; push-pull or open-drain, up to 5.25 V

tolerance

- Hardware SMBus™ (I2C™ Compatible), SPI™, and

UART serial ports available concurrently

- Four general purpose 16-bit counter/timers

- Programmable 16-bit counter/timer array with six

capture/compare modules, WDT

- Hardware smaRTClock operates down to 1 V with

64 bytes battery-backed RAM and backup voltage

regulator

Clock Sources

- Internal oscillators: 24.5 MHz 2% accuracy supports

UART operation; clock multiplier up to 50

MHz

- External oscillator: Crystal, RC, C, or Clock

(1 or 2 pin modes)

- smaRTClock oscillator: 32 kHz Crystal or

self-resonant oscillator

- Can switch between clock sources on-the-fly

32-PIN LQFP or 28-PIN 5x5 QFN

Temperature Range: –40 to +85 °C

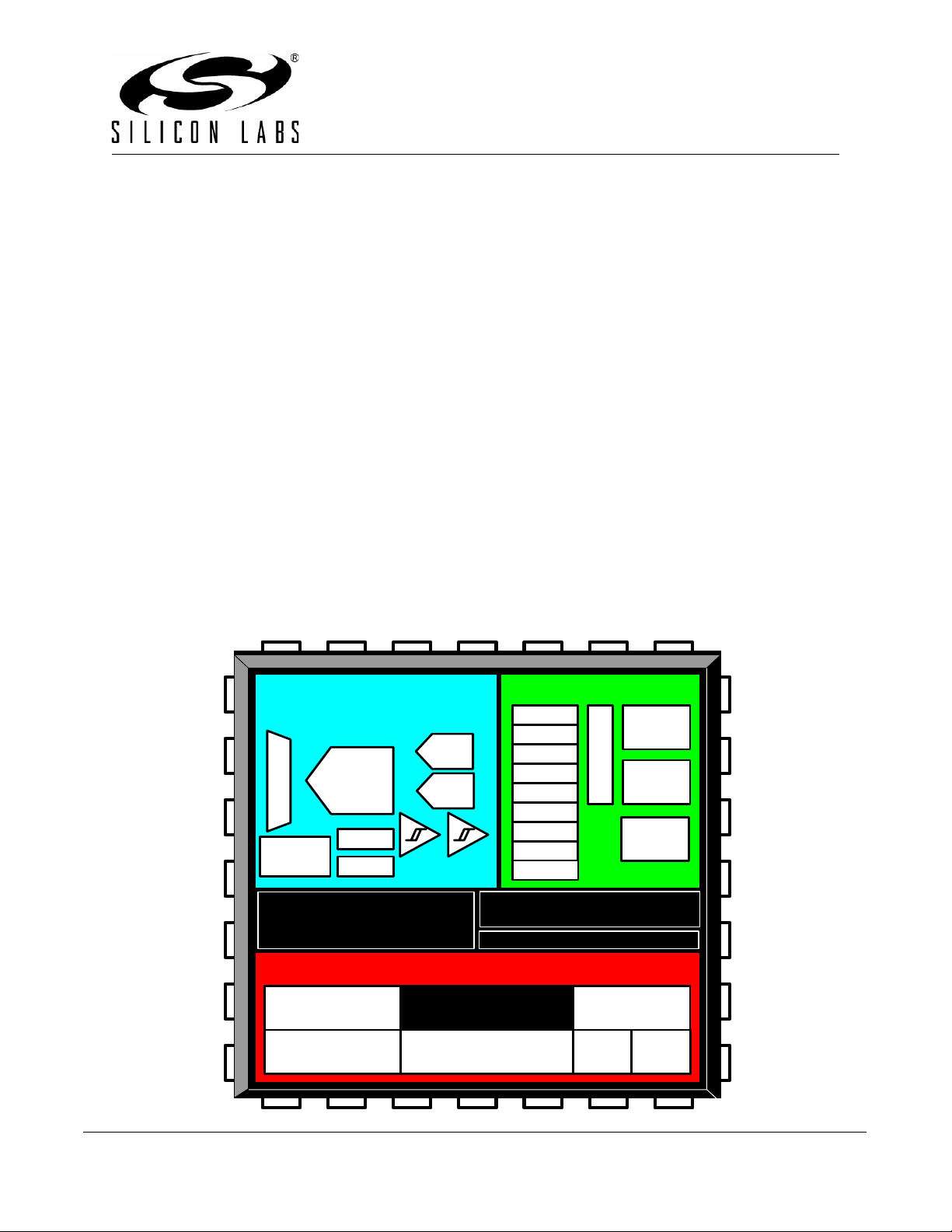

ANALOG

PERIPHERALS

A

M

U

X

TEMP

SENSOR

24.5 MHz PRECISION

INTERNAL OSCILLATOR

WITH CLOCK MULTIPLIER

32/16 kB

ISP FLASH

FLEXIBLE

INTERRUPTS

12-bit

200 ksps

ADC

+

VREF

VREG

-

VOLTAGE

COMPARATORS

HIGH-SPEED CONTROLLER CORE

12-bit

IDAC

12-bit

IDAC

+

-

SMBus

Timer 0

Timer 1

Timer 2

Timer 3

INTERNAL OSCILLATOR

HARDWARE smaRTClock

8051 CPU

(50 MIPS)

DEBUG

CIRCUITRY

DIGITAL I/O

UART

SPI

PCA

CRC

LOW FREQUENCY

POR

Port 0

Port 1

CROSSBAR

Port 2

2368 B

SRAM

WDT

Rev. 1.0 2/07 Copyright © 2007 by Silicon Laboratories C8051F41x

Page 2

C8051F410/1/2/3

NOTES:

2 Rev. 1.0

Page 3

C8051F410/1/2/3

Table of Contents

1. System Overview.................................................................................................... 19

1.1. CIP-51™ Microcontroller................................................................................... 25

1.1.1. Fully 8051 Compatible Instruction Set...................................................... 25

1.1.2. Improved Throughput............................................................................... 25

1.1.3. Additional Features. ..... ..... ............................ .... ..... ..... ............................ . 25

1.2. On-Chip Debug Circuitry................................................................................... 26

1.3. On-Chip Memory............................................................................................... 27

1.4. Operating Modes.... ..... .... ............................ ..... ..... ............................ .... ........... 28

1.5. 12-Bit Analog to Digital Converter..................................................................... 29

1.6. Two 12-bit Current-Mode DACs.................................................... ..... .... ..... ...... 29

1.7. Programmable Comparators............................................................................. 30

1.8. Cyclic Redundancy Check Unit......................................................................... 31

1.9. Voltage Regulator............................................................................................. 31

1.10.Serial Ports................................ .... ............................ ..... ..... .... ......................... 31

1.11.smaRTClock (Real Time Clock)....................................................................... 32

1.12.Port Input/Output.............................................................................................. 33

1.13.Programmable Counter Array........................................................................... 34

2. Absolute Maximum Ratings .................................................................................. 35

3. Global DC Electrical Characteristics.................................................................... 36

4. Pinout and Package Definitions............................................................................ 41

5. 12-Bit ADC (ADC0).................................................................................................. 51

5.1. Analog Multiplexer............................................................................................ 51

5.2. Temperature Sensor......................................................................................... 52

5.3. ADC0 Operation................................................................................................ 52

5.3.1. Starting a Conversion............................................................................... 53

5.3.2. Tracking Modes........................................................................................ 53

5.3.3. Timing....................................................................................................... 54

5.3.4. Burst Mode...............................................................................................56

5.3.5. Output Conversion Code.......................................................................... 57

5.3.6. Settling Time Requirements..................................................................... 58

5.4. Programmable Window Detector...................................................................... 63

5.4.1. Window Detector In Single-Ended Mode................................................. 66

6. 12-Bit Current Mode DACs (IDA0 and IDA1)........................................................ 69

6.1. IDAC Output Scheduling............................................ ..... ............................ ..... . 69

6.1.1. Update Output On-Demand..................................................................... 69

6.1.2. Update Output Based on Timer Overflow ................................................70

6.1.3. Update Output Based on CNVSTR Edge................................................. 70

6.2. IDAC Output Mapping................................................ ............................ ..... ..... . 70

6.3. IDAC External Pin Connections........................................................................ 73

7. Voltage Reference.................................................................................................. 77

8. Voltage Regulator (REG0)...................................................................................... 81

9. Comparators ......................................................................................................... 83

Rev. 1.0 3

Page 4

C8051F410/1/2/3

10.CIP-51 Microcontroller........................................................................................... 93

10.1.Instruction Set................................................................................................... 94

10.1.1.Instruction and CPU Timing..................................................................... 94

10.1.2.MOVX Instruction and Program Memory................................................. 95

10.2.Register Descriptions....................................................................................... 98

10.3.Power Management Modes............................................................................101

10.3.1.Idle Mode............................................ ..... ..... .... ............................ ..... ....102

10.3.2.Stop Mode.............................................................................................. 102

10.3.3.Suspend Mode....................................................................................... 102

11.Memory Organization and SFRs......................................................................... 103

11.1.Program Memory............................................................................................ 103

11.2.Data Memory.................................................................................................. 104

11.3.General Purpose Registers................................................. .... ..... ..... ............. 104

11.4.Bit Addressable Locations....................... .... ............................ ..... ..... .... ......... 104

11.5.Stack............................................................................................................... 104

11.6.Special Function Registers............................................................................. 105

12.Interrupt Handler ........................ ..... .... ............................ ..... ..... .... ....................... 110

12.1.MCU Interrupt Sources and Vectors............ ..... ............................ ..... .... ..... ....110

12.2.Interrupt Priorities........................................................................................... 110

12.3.Interrupt Latency............................................................................................. 110

12.4.Interrupt Register Descriptions....................................................................... 112

12.5.External Interrupts................................................. .... ..... ............................ ....117

13.Prefetch Engine................................................. ..... ..... ............................ .... ..... .... 119

14.Cyclic Redundancy Check Unit (CRC0) ............................................................. 121

14.1.CRC Algorithm......................................... .... ..... ..... ............................ .... ..... ....121

14.2.Preparing for a CRC Calculation.................................................................... 123

14.3.Performing a CRC Calculation....................................................................... 123

14.4.Accessing the CRC0 Result...........................................................................123

14.5.CRC0 Bit Reverse Feature............................................................................. 123

15.Reset Sources....................................................................................................... 127

15.1.Power-On Reset............................................................................................. 128

15.2.Power-Fail Reset / VDD Monitor .................................................................... 129

15.3.External Reset....................................................... .... ..... ............................ ....130

15.4.Missing Clock Detector Reset........................................................................ 130

15.5.Comparator0 Reset........................................................................................ 130

15.6.PCA Watchdog Timer Reset ..........................................................................131

15.7.Flash Error Reset........................................................................................... 131

15.8.smaRTClock (Real Time Clock) Reset........................................................... 132

15.9.Software Reset............................................................................................... 132

16.Flash Memory ....................................................................................................... 135

16.1.Programming The Flash Memory................................................................... 135

16.1.1.Flash Lock and Key Functions............................................................... 135

16.1.2.Flash Erase Procedure.......................................................................... 135

16.1.3.Flash Write Procedure........................................................................... 136

16.2.Non-volatile Data Storage......................................... ..... ..... ........................... 137

4 Rev. 1.0

Page 5

C8051F410/1/2/3

16.3.Security Options............................................................................................. 137

16.4.Flash Write and Erase Guidelines.................................................................. 139

16.4.1.VDD Maintenance and the VDD Monitor............................................... 139

16.4.2.16.4.2 PSWE Maintenance.................................................................... 140

16.4.3.System Clock........................ ..... ............................ ..... .... ..... .................. 140

16.5.Flash Read Timing......................................................................................... 142

17.External RAM........................................................................................................ 145

18.Port Input/Output............................. .... ..... ............................ ..... .... ..... .................. 147

18.1.Priority Crossbar Decoder.............................................................................. 149

18.2.Port I/O Initialization....................................................................................... 151

18.3.General Purpose Port I/O................................. ..... .... ............................ ..... ....154

19.Oscillators............................................................................................................. 165

19.1.Programmable Internal Oscillator...................................................................165

19.1.1.Internal Oscillator Suspend Mode.......................................................... 166

19.2.External Oscillator Drive Circuit...................................................................... 168

19.2.1.Clocking Timers Directly Through the External Oscillator...................... 168

19.2.2.External Crystal Example....................................................................... 168

19.2.3.External RC Example............................................................................. 170

19.2.4.External Capacitor Example................................................................... 170

19.3.Clock Multiplier............................................................................................... 172

19.4.System Clock Selection.................................................................................. 174

20.smaRTClock (Real Time Clock)........................................................................... 177

20.1.smaRTClock Interface.................................................................................... 178

20.1.1.smaRTClock Lock and Key Functions................................................... 178

20.1.2.Using RTC0ADR and RTC0DAT to Access

smaRTClock Internal Registers.............................................................. 178

20.1.3.smaRTClock Interface Autoread Feature............................................... 178

20.1.4.RTC0ADR Autoincrement Feature.........................................................179

20.2.smaRTClock Clocking Sources...................................................................... 182

20.2.1.Using the smaRTClock Oscillator in Crystal Mode................................ 182

20.2.2.Using the smaRTClock Oscillator in Self-Oscillate Mode ...................... 182

20.2.3.Automatic Gain Control (Crystal Mode Only)....................... ..... ............. 183

20.2.4.smaRTClock Bias Doubling...................................................................183

20.2.5.smaRTClock Missing Clock Detector..................................................... 183

20.3.smaRTClock Timer and Alarm Function......................................................... 185

20.3.1.Setting and Reading the smaRTClock Timer Value............................... 185

20.3.2.Setting a smaRTClock Alarm...................................... .... ....................... 186

20.4.Backup Regulator and RAM........................................................................... 187

21.SMBus ................................................................................................................... 191

21.1.Supporting Documents................................................................................... 192

21.2.SMBus Configuration......................................................................................192

21.3.SMBus Operation........................................................................................... 192

21.3.1.Arbitration...............................................................................................193

21.3.2.Clock Low Extension.............................................................................. 193

21.3.3.SCL Low Timeout................................................................................... 194

Rev. 1.0 5

Page 6

C8051F410/1/2/3

21.3.4.SCL High (SMBus Free) Timeout.......................................................... 194

21.4.Using the SMBus.............................................. ............................ ..... .... ..... ....194

21.4.1.SMBus Configuration Register............................... ..... ........................... 195

21.4.2.SMB0CN Control Register..................................................................... 198

21.4.3.Data Register........................ ............................ ..... ..... .... ....................... 201

21.5.SMBus Transfer Modes.................................................................................. 201

21.5.1.Master Transmitter Mode....................................................................... 201

21.5.2.Master Receiver Mode........................................................................... 202

21.5.3.Slave Receiver Mode.............................................................................203

21.5.4.Slave Transmitter Mode......................................................................... 204

21.6.SMBus Status Decoding.................................................................................204

22.UART0.................................................................................................................... 207

22.1.Enhanced Baud Rate Generation................................................................... 208

22.2.Operational Modes................................................ .... ..... ..... ...........................209

22.2.1.8-Bit UART............................................................................................. 209

22.2.2.9-Bit UART............................................................................................. 210

22.3.Multiprocessor Communications.................................................................... 210

23.Enhanced Serial Peripheral Interface (SPI0)...................................................... 217

23.1.Signal Descriptions.........................................................................................218

23.1.1.Master Out, Slave In (MOSI).................................................................. 218

23.1.2.Master In, Slave Out (MISO).................................................................. 218

23.1.3.Serial Clock (SCK)................................................................................. 218

23.1.4.Slave Select (NSS)................................................................................ 218

23.2.SPI0 Master Mode Operation ......................................................................... 219

23.3.SPI0 Slave Mode Operation........................................................................... 220

23.4.SPI0 Interrupt Sources................................................................................... 221

23.5.Serial Clock Timing........................ ..... ..... .... ..... ............................ ..... .... ..... ....221

23.6.SPI Special Function Registers......................................................................222

24.Timers.................................................................................................................... 231

24.1.Timer 0 and Timer 1....................................................................................... 231

24.1.1.Mode 0: 13-bit Counter/Timer................................................................ 231

24.1.2.Mode 1: 16-bit Counter/Timer................................................................ 233

24.1.3.Mode 2: 8-bit Counter/Timer with Auto-Reload...................................... 233

24.1.4.Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)................................. 234

24.2.Timer 2 ..........................................................................................................239

24.2.1.16-bit Timer with Auto-Reload................................................................ 239

24.2.2.8-bit Timers with Auto-Reload................................................................240

24.2.3.External/smaRTClock Capture Mode..................................................... 241

24.3.Timer 3 ..........................................................................................................244

24.3.1.16-bit Timer with Auto-Reload................................................................ 244

24.3.2.8-bit Timers with Auto-Reload................................................................245

24.3.3.External/smaRTClock Capture Mode..................................................... 246

25.Programmable Counter Array (PCA0)................................................................ 249

25.1.PCA Counter/Timer................................. .... ............................ ..... ..... .... ......... 250

25.2.Capture/Compare Modules............................................................................ 251

6 Rev. 1.0

Page 7

C8051F410/1/2/3

25.2.1.Edge-triggered Capture Mode................................................................ 252

25.2.2.Software Timer (Compare) Mode........................................................... 253

25.2.3.High Speed Output Mode....................................................................... 254

25.2.4.Frequency Output Mode........................................ ..... .... ..... .................. 255

25.2.5.8-Bit Pulse Width Modulator Mode......................................................... 256

25.2.6.16-Bit Pulse Width Modulator Mode.......................................................257

25.3.Watchdog Timer Mode................................................................................... 257

25.3.1.Watchdog Timer Operation.................................................................... 258

25.3.2.Watchdog Timer Usage......................................................................... 259

25.4.Register Descriptions for PCA........................................................................ 261

26.C2 Interface........................ .... ..... ..... ............................ .... ..... ..... ........................... 265

26.1.C2 Interface Registers.................................................................................... 265

26.2.C2 Pin Sharing............................................................................................... 267

Document Change List............................................................................................. 268

Contact Information.................................................................................................. 270

Rev. 1.0 7

Page 8

C8051F410/1/2/3

NOTES:

8 Rev. 1.0

Page 9

C8051F410/1/2/3

List of Figures

1. System Overview

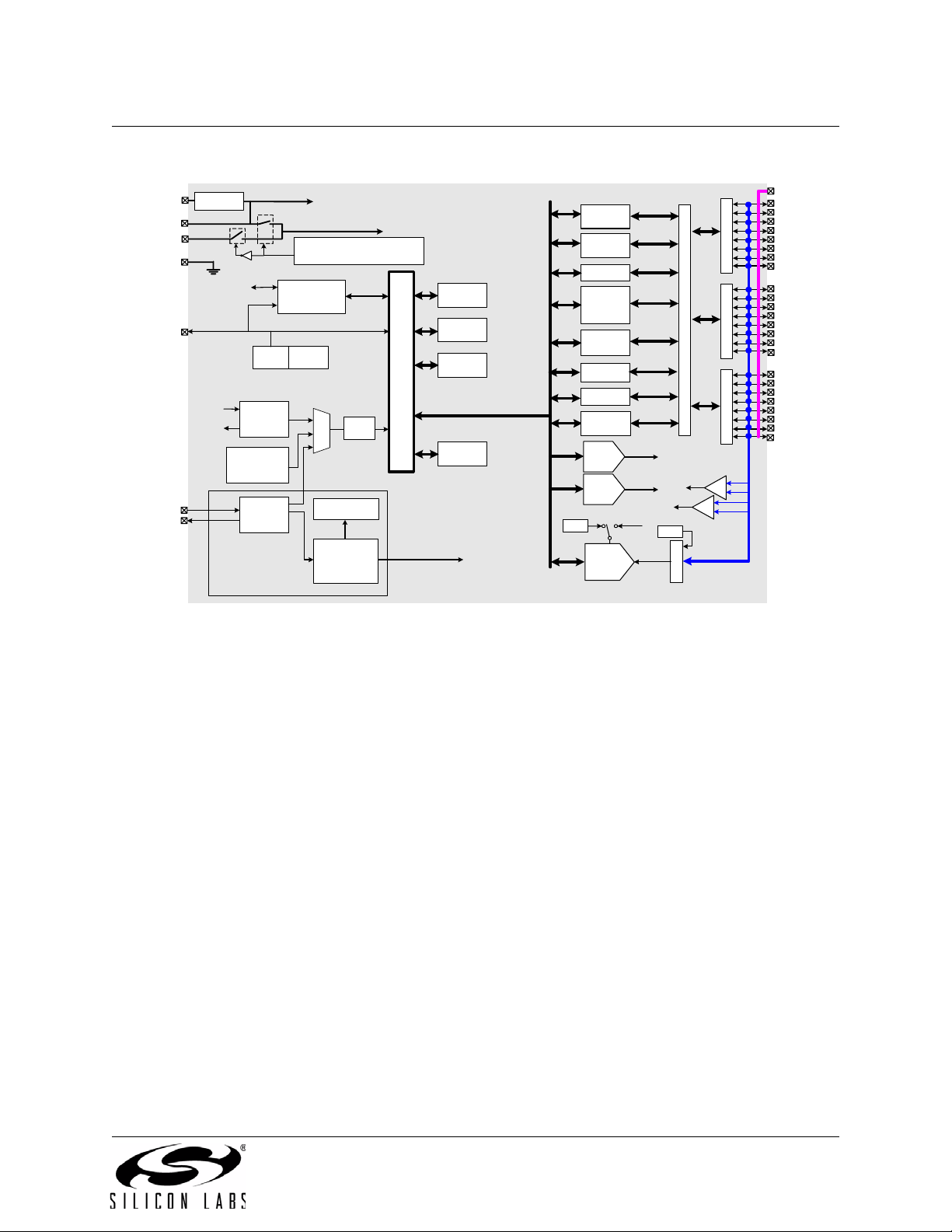

Figure 1.1. C8051F410 Block Diagram.................................................................... 21

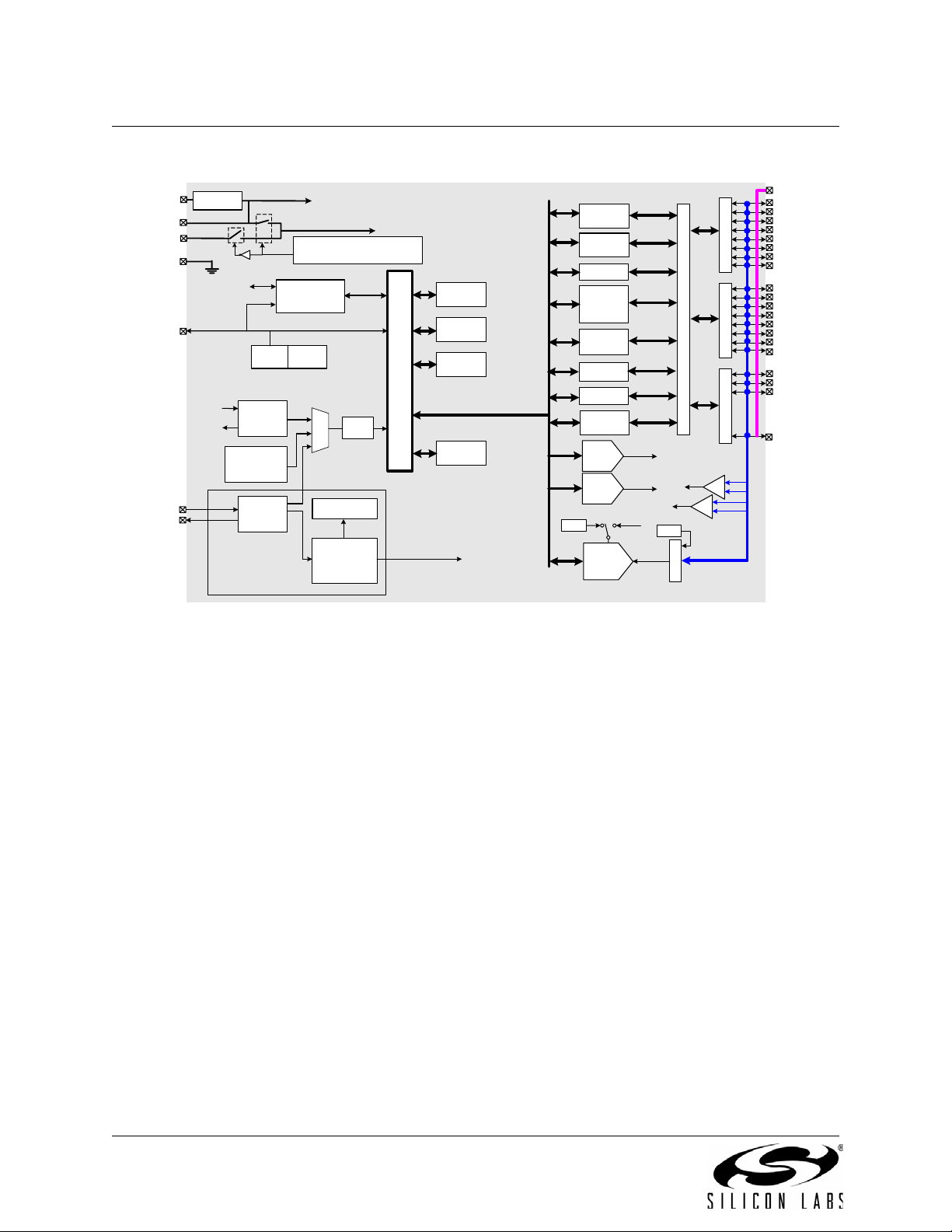

Figure 1.2. C8051F411 Block Diagram.................................................................... 22

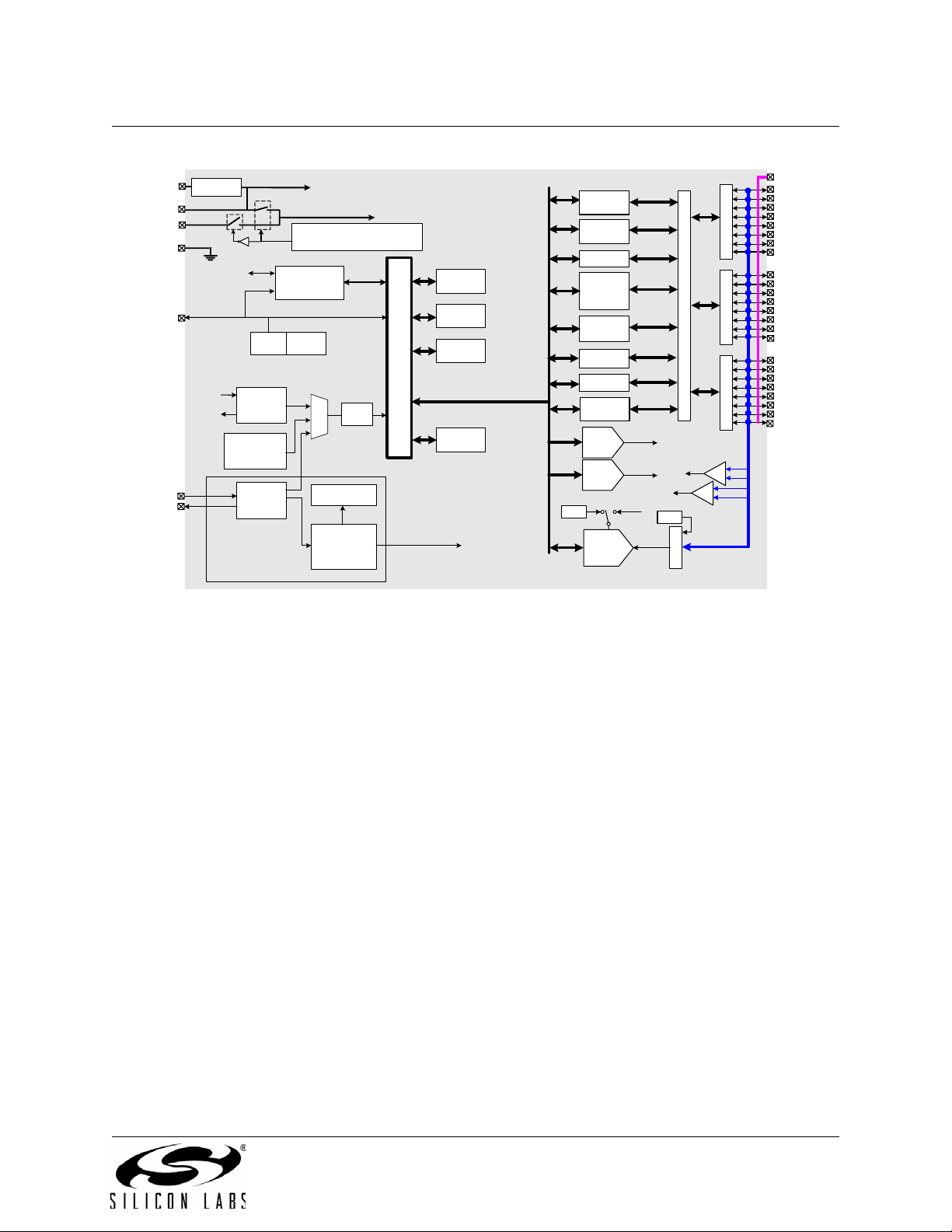

Figure 1.3. C8051F412 Block Diagram.................................................................... 23

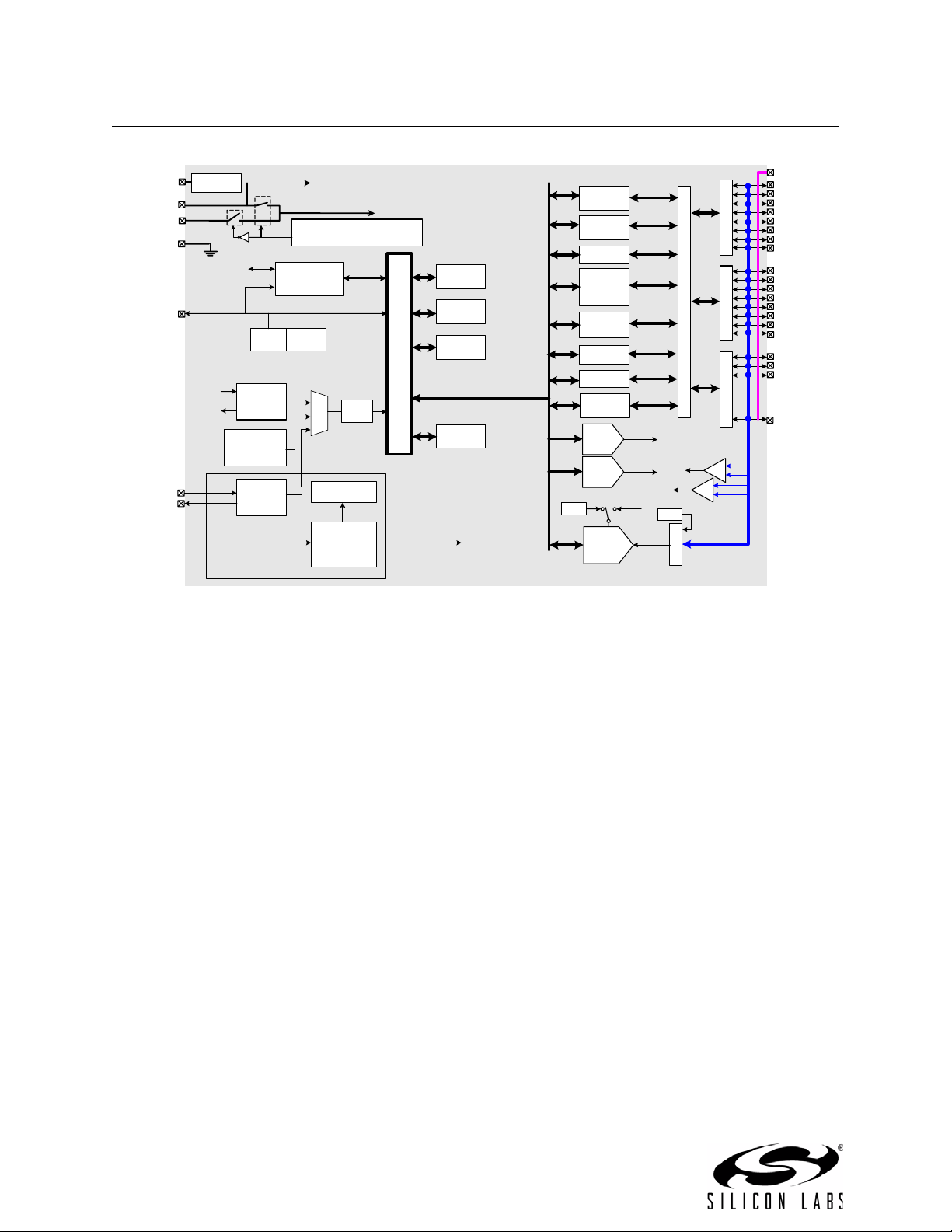

Figure 1.4. C8051F413 Block Diagram.................................................................... 24

Figure 1.5. Development/In-System Debug Diagram............................................... 26

Figure 1.6. Memory Map.......................................................................................... 27

Figure 1.7. 12-Bit ADC Block Diagram..................................................................... 29

Figure 1.8. IDAC Block Diagram.............................................................................. 30

Figure 1.9. Comparators Block Diagram.................................................................. 31

Figure 1.10. smaRTClock Block Diagram................................................................ 32

Figure 1.11. Port I/O Functional Block Diagram....................................................... 33

Figure 1.12. PCA Block Diagram.............................................................................. 34

2. Absolute Maximum Ratings

3. Global DC Electrical Characteristics

4. Pinout and Package Definitions

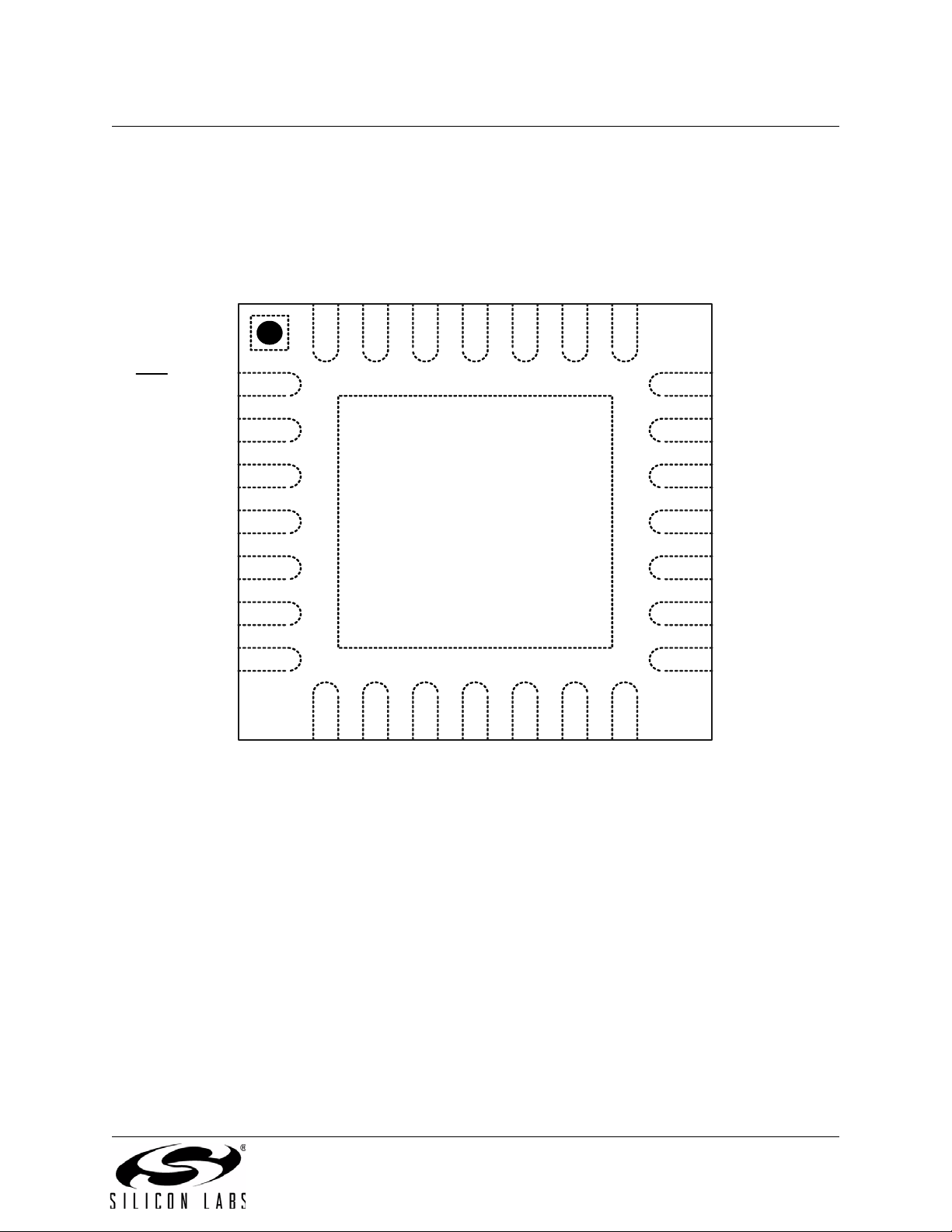

Figure 4.1. LQFP-32 Pinout Diagram (Top View) .................................................... 44

Figure 4.2. QFN-28 Pinout Diagram (Top View)...................................................... 45

Figure 4.3. LQFP-32 Package Diagram................................................................... 46

Figure 4.4. QFN-28 Package Drawing..................................................................... 47

Figure 4.5. Typical QFN-28 Landing Diagram.......................................................... 48

Figure 4.6. Typical QFN-28 Solder Paste Mask....................................................... 49

5. 12-Bit ADC (ADC0)

Figure 5.1. ADC0 Functional Block Diagram............................................................ 51

Figure 5.2. Typical Temperature Sensor Transfer Function..................................... 52

Figure 5.3. ADC0 Tracking Modes........................................................................... 54

Figure 5.4. 12-Bit ADC Tracking Mode Example..................................................... 55

Figure 5.5. 12-Bit ADC Burst Mode Example with Repeat Count Set to 4............... 56

Figure 5.6. ADC0 Equivalent Input Circuits.............................................................. 58

Figure 5.7. ADC Window Compare Example: Right-Justified Single-Ended Data... 66

Figure 5.8. ADC Window Compare Example: Left-Justified Single-Ended Data ..... 66

6. 12-Bit Current Mode DACs (IDA0 and IDA1)

Figure 6.1. IDAC Functional Block Diagram............................................................. 69

Figure 6.2. IDAC Data Word Mapping...................................................................... 70

Figure 6.3. IDAC Pin Connections ........................................................................... 74

7. Voltage Reference

Figure 7.1. Voltage Reference Functional Block Diagram....................................... 77

8. Voltage Regulator (REG0)

Figure 8.1. External Capacitors for Voltage Regulator Input/Output........................ 81

Figure 8.2. External Capacitors for Voltage Regulator Input/Output........................ 81

9. Comparators

Figure 9.1. Comparator0 Functional Block Diagram................................................ 83

Figure 9.2. Comparator1 Functional Block Diagram................................................ 84

Rev. 1.0 9

Page 10

C8051F410/1/2/3

Figure 9.3. Comparator Hysteresis Plot................................................................... 85

10.CIP-51 Microcontroller

Figure 10.1. CIP-51 Block Diagram.......................................................................... 93

11.Memory Organization and SFRs

Figure 11.1. Memory Map......................................................................................103

12.Interrupt Handler

13.Prefetch Engine

14.Cyclic Redunda ncy Check Unit (CRC0)

Figure 14.1. CRC0 Block Diagram......................................................................... 121

Figure 14.2. Bit Reverse Register..........................................................................123

15.Reset Sources

Figure 15.1. Reset Sources.................................................................................... 127

Figure 15.2. Power-On and VDD Monitor Reset Timing ........................................ 128

16.Flash Memory

Figure 16.1. Flash Program Memory Map.............................................................. 137

17.External RAM

18.Port Input/Output

Figure 18.1. Port I/O Functional Block Diagram..................................................... 147

Figure 18.2. Port I/O Cell Block Diagram............................................................... 148

Figure 18.3. Crossbar Priority Decoder with No Pins Skipped............................... 149

Figure 18.4. Crossbar Priority Decoder with Crystal Pins Skipped ........................ 150

Figure 18.5. Port 0 Input Overdrive Current Range..................... .... ....................... 152

19.Oscillators

Figure 19.1. Oscillator Diagram.............................................................................. 165

Figure 19.2. 32.768 kHz External Crystal Example................................................169

Figure 19.3. Example Clock Multiplier Output........................................................ 172

20.smaRTClock (Re al Time Clock)

Figure 20.1. smaRTClock Block Diagram.............................................................. 177

21.SMBus

Figure 21.1. SMBus Block Diagram....................................................................... 191

Figure 21.2. Typical SMBus Configuration............................................................. 192

Figure 21.3. SMBus Transaction............................................................................ 193

Figure 21.4. Typical SMBus SCL Generation.........................................................196

Figure 21.5. Typical Master Transmitter Sequence................................................ 202

Figure 21.6. Typical Master Receiver Sequence.................................................... 202

Figure 21.7. Typical Slave Receiver Sequence...................................................... 203

Figure 21.8. Typical Slave Transmitter Sequence..................................................204

22.UART0

Figure 22.1. UART0 Block Diagram....................................................................... 207

Figure 22.2. UART0 Baud Rate Logic................................................................ ....208

Figure 22.3. UART Interconnect Diagram.............................................................. 209

Figure 22.4. 8-Bit UART Timing Diagram............................................................... 209

Figure 22.5. 9-Bit UART Timing Diagram............................................................... 210

Figure 22.6. UART Multi-Processor Mode Interconnect Diagram.......................... 211

10 Rev. 1.0

Page 11

C8051F410/1/2/3

23.Enhanced Serial Peripheral Interface (SPI0)

Figure 23.1. SPI Block Diagram.............................................................................217

Figure 23.2. Multiple-Master Mode Connection Diagram.......................................220

Figure 23.3. 3-Wire Single Master and Slave Mode Connection Diagram............. 220

Figure 23.4. 4-Wire Single Master and Slave Mode Connection Diagram............. 220

Figure 23.5. Data/Clock Timing Relationship......................................................... 222

Figure 23.6. SPI Master Timing (CKPHA = 0)........................................................ 227

Figure 23.7. SPI Master Timing (CKPHA = 1)........................................................ 227

Figure 23.8. SPI Slave Timing (CKPHA = 0)..........................................................228

Figure 23.9. SPI Slave Timing (CKPHA = 1)..........................................................228

24.Timers

Figure 24.1. T0 Mode 0 Block Diagram.................................................................. 232

Figure 24.2. T0 Mode 2 Block Diagram.................................................................. 233

Figure 24.3. T0 Mode 3 Block Diagram.................................................................. 234

Figure 24.4. Timer 2 16-Bit Mode Block Diagram .................................................. 239

Figure 24.5. Timer 2 8-Bit Mode Block Diagram .................................................... 240

Figure 24.6. Timer 2 Capture Mode Block Diagram............................................... 241

Figure 24.7. Timer 3 16-Bit Mode Block Diagram .................................................. 244

Figure 24.8. Timer 3 8-Bit Mode Block Diagram .................................................... 245

Figure 24.9. Timer 3 Capture Mode Block Diagram............................................... 246

25.Programmable Counter Array (PCA0)

Figure 25.1. PCA Block Diagram............................................................................ 249

Figure 25.2. PCA Counter/Timer Block Diagram....................................................250

Figure 25.3. PCA Interrupt Block Diagram............................................................. 251

Figure 25.4. PCA Capture Mode Diagram.............................................................. 252

Figure 25.5. PCA Software Timer Mode Diagram.................................................. 253

Figure 25.6. PCA High-Speed Output Mode Diagram............................................ 254

Figure 25.7. PCA Frequency Output Mode............................................................255

Figure 25.8. PCA 8-Bit PWM Mode Diagram......................................................... 256

Figure 25.9. PCA 16-Bit PWM Mode...................................................................... 257

Figure 25.10. PCA Module 5 with Watchdog Timer Enabled................................. 258

26.C2 Interface

Figure 26.1. Typical C2 Pin Sharing....................................................................... 267

Rev. 1.0 11

Page 12

C8051F410/1/2/3

NOTES:

12 Rev. 1.0

Page 13

C8051F410/1/2/3

List of Tables

1. System Overview

Table 1.1. Product Selection Guide ......................................................................... 20

Table 1.2. Operating Modes Summary .................................................................... 28

2. Absolute Maximum Ratings

Table 2.1.Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

3. Global DC Electrical Characteristics

Table 3.1.Global DC Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 3.2. Index to Electrical Characteristics Tables ............................................... 39

4. Pinout and Package Definitions

Table 4.1. Pin Definitions for the C8051F41x .......................................................... 41

Table 4.2. LQFP-32 Package Dimensions ..............................................................46

Table 4.3. QFN-28 Package Dimensions ................................................................ 47

5. 12-Bit ADC (ADC0)

Table 5.1. ADC0 Examples of Right- and Left-Justified Samples ........................... 57

Table 5.2. ADC0 Repeat Count Examples at Various Input Voltages ..................... 57

Table 5.3.ADC0 Electrical Characteristics (VDD = 2.5 V, V

Table 5.4.ADC0 Electrical Characteristics (VDD = 2.1 V, V

6. 12-Bit Current Mode DACs (IDA0 and IDA1)

Table 6.1.IDAC Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

7. Voltage Reference

Table 7.1.Voltage Reference Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . 79

8. Voltage Regulator (REG0)

Table 8.1.Voltage Regulator Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . 82

9. Comparators

Table 9.1.Comparator Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 92

10.CIP-51 Microcontroller

Table 10.1. CIP-51 Instruction Set Summary .......................................................... 95

11.Memory Organization and SFRs

Table 11.1. Special Function Register (SFR) Memory Map ..................... .... ......... 105

Table 11.2. Special Function Registers ................................................................. 106

12.Interrupt Handler

Table 12.1. Interrupt Summary .............................................................................. 111

13.Prefetch Engine

14.Cyclic Redunda ncy Check Unit (CRC0)

Table 14.1. Example 16-bit CRC Outputs ............................................................. 122

15.Reset Sources

Table 15.1.Reset Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

16.Flash Memory

Table 16.1. Flash Security Summary .................................................................... 138

Table 16.2.Flash Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

17.External RAM

= 2.2 V) . . . . . . . . 67

REF

= 1.5 V) . . . . . . . . 68

REF

Rev. 1.0 13

Page 14

C8051F410/1/2/3

18.Port Input/Output

Table 18.1.Port I/O DC Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . 163

19.Oscillators

Table 19.1.Oscillator Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 175

20.smaRTClock (Re al Time Clock)

Table 20.1. smaRTClock Internal Registers .......................................................... 179

21.SMBus

Table 21.1. SMBus Clock Source Selection .......................................................... 195

Table 21.2. Minimum SDA Setup and Hold Times ................................................ 196

Table 21.3. Sources for Hardware Changes to SMB0CN ..................................... 200

Table 21.4. SMBus Status Decoding ..................................................................... 205

22.UART0

Table 22.1. Timer Settings for Standard Baud Rates

Using the Internal Oscillator ............................................................... 214

Table 22.2. Timer Settings for Standard Baud Rates

Using an External 25.0 MHz Oscillator ............................................... 214

Table 22.3. Timer Settings for Standard Baud Rates

Using an External 22.1184 MHz Oscillator ......................................... 215

Table 22.4. Timer Settings for Standard Baud Rates

Using an External 18.432 MHz Oscillator ........................................... 215

Table 22.5. Timer Settings for Standard Baud Rates

Using an External 11.0592 MHz Oscillator ......................................... 216

Table 22.6. Timer Settings for Standard Baud Rates

Using an External 3.6864 MHz Oscillator ........................................... 216

23.Enhanced Serial Peripheral Interface (SPI0)

Table 23.1.SPI Slave Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

24.Timers

25.Programmable Counter Array (PCA0)

Table 25.1. PCA Timebase Input Options ............................................................. 250

Table 25.2. PCA0CPM Register Settings for PCA Capture/Compare Modules .... 251

Table 25.3. Watchdog Timer Timeout Intervals ..................................................... 260

26.C2 Interface

14 Rev. 1.0

Page 15

C8051F410/1/2/3

List of Registers

SFR Definition 5.1. ADC0MX: ADC0 Channel Select . . . . . . . . . . . . . . . . . . . . . . . . . . 59

SFR Definition 5.2. ADC0CF: ADC0 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

SFR Definition 5.3. ADC0H: ADC0 Data Word MSB . . . . . . . . . . . . . . . . . . . . . . . . . . 61

SFR Definition 5.4. ADC0L: ADC0 Data Word LSB . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

SFR Definition 5.5. ADC0CN: ADC0 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

SFR Definition 5.6. ADC0TK: ADC0 Tracking Mode Select . . . . . . . . . . . . . . . . . . . . 63

SFR Definition 5.7. ADC0GTH: ADC0 Greater-Than Data High Byte . . . . . . . . . . . . . 64

SFR Definition 5.8. ADC0GTL: ADC0 Greater-Than Data Low Byte . . . . . . . . . . . . . . 64

SFR Definition 5.9. ADC0LTH: ADC0 Less-Than Data High Byte . . . . . . . . . . . . . . . . 65

SFR Definition 5.10. ADC0LTL: ADC0 Less-Than Data Low Byte . . . . . . . . . . . . . . . . 65

SFR Definition 6.1. IDA0CN: IDA0 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

SFR Definition 6.2. IDA0H: IDA0 Data High Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

SFR Definition 6.3. IDA0L: IDA0 Data Low Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

SFR Definition 6.4. IDA1CN: IDA1 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

SFR Definition 6.5. IDA1H: IDA0 Data High Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

SFR Definition 6.6. IDA1L: IDA1 Data Low Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

SFR Definition 7.1. REF0CN: Reference Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

SFR Definition 8.1. REG0CN: Regulator Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

SFR Definition 9.1. CPT0CN: Comparator0 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

SFR Definition 9.2. CPT0MX: Comparator0 MUX Selection . . . . . . . . . . . . . . . . . . . . 87

SFR Definition 9.3. CPT0MD: Comparator0 Mode Selection . . . . . . . . . . . . . . . . . . . . 88

SFR Definition 9.4. CPT1MX: Comparator1 MUX Selection . . . . . . . . . . . . . . . . . . . . 89

SFR Definition 9.5. CPT1MD: Comparator1 Mode Selection . . . . . . . . . . . . . . . . . . . . 90

SFR Definition 9.6. CPT1CN: Comparator1 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

SFR Definition 10.1. SP: Stack Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

SFR Definition 10.2. DPL: Data Pointer Low Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

SFR Definition 10.3. DPH: Data Pointer High Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

SFR Definition 10.4. PSW: Program Status Word . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

SFR Definition 10.5. ACC: Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

SFR Definition 10.6. B: B Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

SFR Definition 10.7. PCON: Power Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

SFR Definition 12.1. IE: Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

SFR Definition 12.2. IP: Interrupt Priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

SFR Definition 12.3. EIE1: Extended Interrupt Enable 1 . . . . . . . . . . . . . . . . . . . . . . 114

SFR Definition 12.4. EIP1: Extended Interrupt Priority 1 . . . . . . . . . . . . . . . . . . . . . . 115

SFR Definition 12.5. EIE2: Extended Interrupt Enable 2 . . . . . . . . . . . . . . . . . . . . . . 116

SFR Definition 12.6. EIP2: Extended Interrupt Priority 2 . . . . . . . . . . . . . . . . . . . . . . 116

SFR Definition 12.7. IT01CF: INT0/INT1 Configuration . . . . . . . . . . . . . . . . . . . . . . . 118

SFR Definition 13.1. PFE0CN: Prefetch Engine Control . . . . . . . . . . . . . . . . . . . . . . 119

SFR Definition 14.1. CRC0CN: CRC0 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

SFR Definition 14.2. CRC0IN: CRC0 Data Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

SFR Definition 14.3. CRC0DAT: CRC0 Data Output . . . . . . . . . . . . . . . . . . . . . . . . . 125

SFR Definition 14.4. CRC0FLIP: CRC0 Bit Flip . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Rev. 1.0 15

Page 16

C8051F410/1/2/3

SFR Definition 15.1. VDM0CN: VDD Monitor Control . . . . . . . . . . . . . . . . . . . . . . . . 130

SFR Definition 15.2. RSTSRC: Reset Source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

SFR Definition 16.1. PSCTL: Program Store R/W Control . . . . . . . . . . . . . . . . . . . . . 141

SFR Definition 16.2. FLKEY: Flash Lock and Key . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

SFR Definition 16.3. FLSCL: Flash Scale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

SFR Definition 16.4. ONESHOT: Flash Oneshot Period . . . . . . . . . . . . . . . . . . . . . . 143

SFR Definition 17.1. EMI0CN: External Memory Interface Control . . . . . . . . . . . . . . 145

SFR Definition 18.1. XBR0: Port I/O Crossbar Register 0 . . . . . . . . . . . . . . . . . . . . .153

SFR Definition 18.2. XBR1: Port I/O Crossbar Register 1 . . . . . . . . . . . . . . . . . . . . .154

SFR Definition 18.3. P0: Port0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .155

SFR Definition 18.4. P0MDIN: Port0 Input Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

SFR Definition 18.5. P0MDOUT: Port0 Output Mode . . . . . . . . . . . . . . . . . . . . . . . . . 156

SFR Definition 18.6. P0SKIP: Port0 Skip . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

SFR Definition 18.7. P0MAT: Port0 Match . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .157

SFR Definition 18.8. P0MASK: Port0 Mask . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

SFR Definition 18.9. P0ODEN: Port0 Overdrive Mode . . . . . . . . . . . . . . . . . . . . . . . .157

SFR Definition 18.10. P1: Port1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .158

SFR Definition 18.11. P1MDIN: Port1 Input Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

SFR Definition 18.12. P1MDOUT: Port1 Output Mode . . . . . . . . . . . . . . . . . . . . . . . .159

SFR Definition 18.13. P1SKIP: Port1 Skip . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .159

SFR Definition 18.14. P1MAT: Port1 Match . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .160

SFR Definition 18.15. P1MASK: Port1 Mask . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

SFR Definition 18.16. P2: Port2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .161

SFR Definition 18.17. P2MDIN: Port2 Input Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

SFR Definition 18.18. P2MDOUT: Port2 Output Mode . . . . . . . . . . . . . . . . . . . . . . . .162

SFR Definition 18.19. P2SKIP: Port2 Skip . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .162

SFR Definition 19.1. OSCICN: Internal Oscillator Control . . . . . . . . . . . . . . . . . . . . .167

SFR Definition 19.2. OSCICL: Internal Oscillator Calibration . . . . . . . . . . . . . . . . . . .167

SFR Definition 19.3. OSCXCN: External Oscillator Control . . . . . . . . . . . . . . . . . . . . 171

SFR Definition 19.4. CLKMUL: Clock Multiplier Control . . . . . . . . . . . . . . . . . . . . . . . 173

SFR Definition 19.5. CLKSEL: Clock Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

SFR Definition 20.1. RTC0KEY: smaRTClock Lock and Key . . . . . . . . . . . . . . . . . . . 180

SFR Definition 20.2. RTC0ADR: smaRTClock Address . . . . . . . . . . . . . . . . . . . . . . 181

SFR Definition 20.3. RTC0DAT: smaRTClock Data . . . . . . . . . . . . . . . . . . . . . . . . .182

Internal Register Definition 20.4. RTC0CN: smaRTClock Control . . . . . . . . . . . . . . . 184

Internal Register Definition 20.5. RTC0XCN: smaRTClock Oscillator Control . . . . . . 185

Internal Register Definition 20.6. CAPTUREn: smaRTClock Timer Capture . . . . . . . 186

Internal Register Definition 20.7. ALARMn: smaRTClock Alarm . . . . . . . . . . . . . . . . 187

Internal Register Definition 20.8. RAMADDR: smaRTClock Backup RAM Address . . 187

Internal Register Definition 20.9. RAMDATA: smaRTClock Backup RAM Data . . . . . 188

SFR Definition 21.1. SMB0CF: SMBus Clock/Configuration . . . . . . . . . . . . . . . . . . . 197

SFR Definition 21.2. SMB0CN: SMBus Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

SFR Definition 21.3. SMB0DAT: SMBus Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .201

SFR Definition 22.1. SCON0: Serial Port 0 Control . . . . . . . . . . . . . . . . . . . . . . . . . . 212

SFR Definition 22.2. SBUF0: Serial (UART0) Port Data Buffer . . . . . . . . . . . . . . . . . 213

16 Rev. 1.0

Page 17

C8051F410/1/2/3

SFR Definition 23.1. SPI0CFG: SPI0 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . 223

SFR Definition 23.2. SPI0CN: SPI0 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

SFR Definition 23.3. SPI0CKR: SPI0 Clock Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

SFR Definition 23.4. SPI0DAT: SPI0 Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .226

SFR Definition 24.1. TCON: Timer Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235

SFR Definition 24.2. TMOD: Timer Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

SFR Definition 24.3. CKCON: Clock Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

SFR Definition 24.4. TL0: Timer 0 Low Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

SFR Definition 24.5. TL1: Timer 1 Low Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

SFR Definition 24.6. TH0: Timer 0 High Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

SFR Definition 24.7. TH1: Timer 1 High Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

SFR Definition 24.8. TMR2CN: Timer 2 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

SFR Definition 24.9. TMR2RLL: Timer 2 Reload Register Low Byte . . . . . . . . . . . . . 243

SFR Definition 24.10. TMR2 RLH: Timer 2 Reload Register High Byte . . . . . . . . . . . 243

SFR Definition 24.11. TMR2L: Timer 2 Low Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243

SFR Definition 24.12. TMR2H Timer 2 High Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243

SFR Definition 24.13. TMR3CN: Timer 3 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . 247

SFR Definition 24.14. TMR3RLL: Timer 3 Reload Register Low Byte . . . . . . . . . . . . 248

SFR Definition 24.15. TMR3 RLH: Timer 3 Reload Register High Byte . . . . . . . . . . . 248

SFR Definition 24.16. TMR3L: Timer 3 Low Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . 248

SFR Definition 24.17. TMR3H Timer 3 High Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . 248

SFR Definition 25.1. PCA0CN: PCA Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 261

SFR Definition 25.2. PCA0MD: PCA Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262

SFR Definition 25.3. PCA0CPMn: PCA Capture/Compare Mode . . . . . . . . . . . . . . . 263

SFR Definition 25.4. PCA0L: PCA Counter/Timer Low Byte . . . . . . . . . . . . . . . . . . . 264

SFR Definition 25.5. PCA0H: PCA Counter/Timer High Byte . . . . . . . . . . . . . . . . . . . 264

SFR Definition 25.6. PCA0CPLn: PCA Capture Module Low Byte . . . . . . . . . . . . . . . 264

SFR Definition 25.7. PCA0CPHn: PCA Capture Module High Byte . . . . . . . . . . . . . . 264

C2 Register Definition 26.1. C2ADD: C2 Address . . . . . . . . . . . . . . . . . . . . . . . . . . . 265

C2 Register Definition 26.2. DEVICEID: C2 Device ID . . . . . . . . . . . . . . . . . . . . . . . . 265

C2 Register Definition 26.3. REVID: C2 Revision ID . . . . . . . . . . . . . . . . . . . . . . . . . 266

C2 Register Definition 26.4. FPCTL: C2 Flash Programming Control . . . . . . . . . . . . 266

C2 Register Definition 26.5. FPDAT: C2 Flash Programming Data . . . . . . . . . . . . . . 266

Rev. 1.0 17

Page 18

C8051F410/1/2/3

NOTES:

18 Rev. 1.0

Page 19

C8051F410/1/2/3

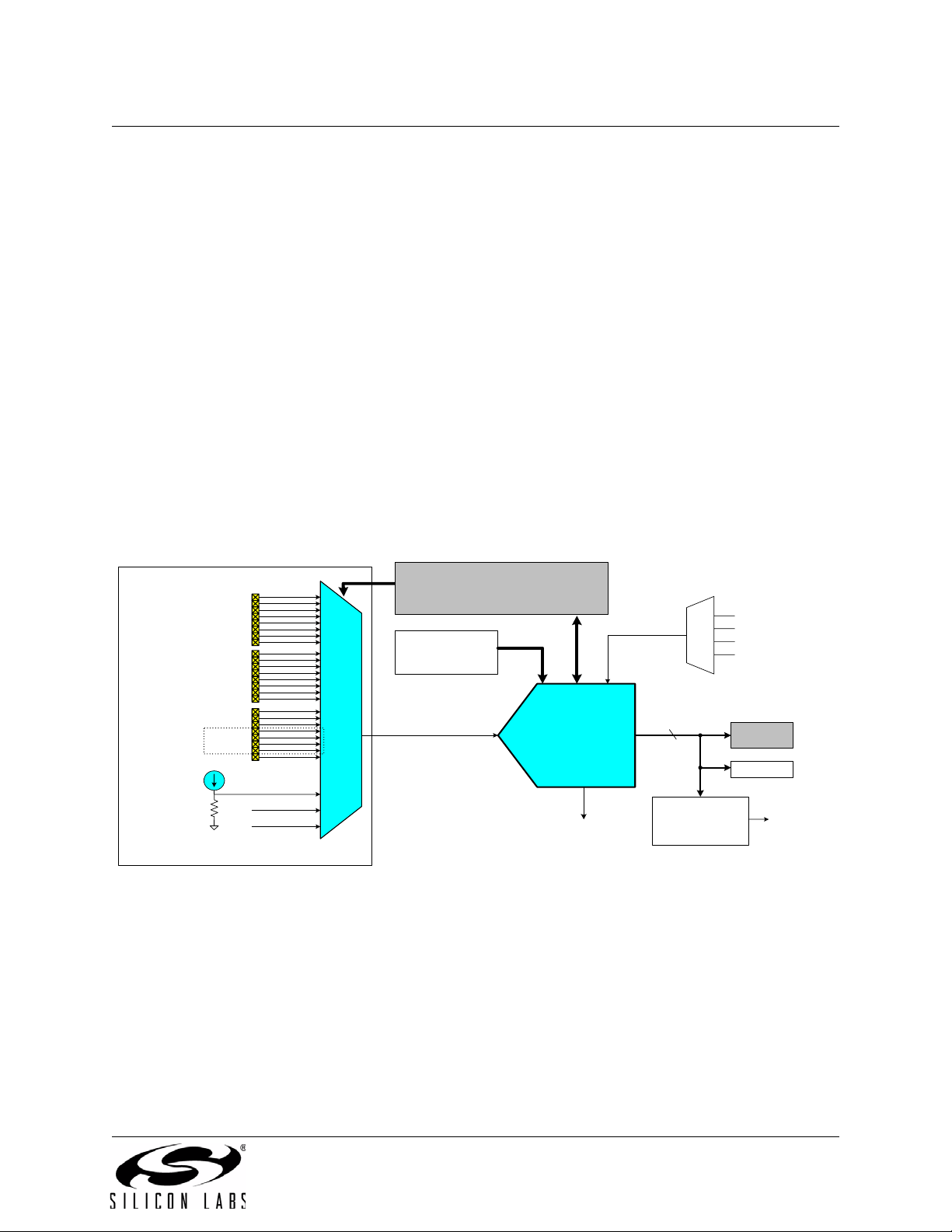

1. System Overview

C8051F41x devices are fully integrated, low power, mixed-signal system-on-a-chip MCUs. Highlighted features are listed below. Refer to Table 1.1 for specific product feature selection.

• High-speed pipelined 8051-compatible microcontroller core (up to 50 MIPS)

• In-system, full-speed, non-intrusive debug interface (on-chip)

• True 12-bit 200 ksps ADC with analog multiplexer and 24 analog inputs

• Two 12-bit Current Output DACs

• Precision programmable 24.5 MHz internal oscillator

• Up to 32 kB bytes of on-chip Flash memory

• 2304 bytes of on-chip RAM

• SMBus/I2C, Enhanced UART, and SPI serial interfaces implemented in hardware

• Four general-purpose 16-bit timers

• Programmable Counter/Timer Array (PCA) with six capture/compare modules and Watchdog Timer

function

• Hardware smaRTClock (Real Time Clock) operates down to 1 V with 64 bytes of Backup RAM and a

Backup Voltage Regulator

• Hardware CRC Engine

• On-chip Power-On Reset, VDD Monitor, and Temperature Sensor

• On-chip Voltage Comparators

• Up to 24 Port I/O

With on-chip Power-On Reset, VDD monitor, Watchdog Timer, and clock oscillator , the C8051F41x devices

are truly standalone system-on-a-chip solutions. Th e Fl as h m emo ry c an be re progr am med ev en in -c irc ui t,

providing non-volati le data storage , and also allow ing field upg rades of the 8051 firmware. U ser software

has complete contr ol of all peripherals, a nd may individually shut down any or all peripher als for power

savings.

The on-chip Silicon Laboratories 2-Wire (C2) Development Interface allows non-intrusive (uses no on-chip

resources), full speed, in-circuit debugging using the production MCU installed in the final application. This

debug logic supports inspection and modification of memory and registers, setting breakpoints, single

stepping, run and halt commands. All a nalog and digital peripheral s are fully function al while debugging

using C2. The two C2 i nterface pins can be shared with us er functions, allowi ng in-system pro gramming

and debugging without occupying package pins.

Each device is specified for 2.0-to-2.75 V operation (supply voltage can be up to 5.25 V using on-chip regulator) over the industrial temperature range (–45 to +85 °C). The C8051F41x are available in 28-pin QFN

(also referred to as MLP or MLF) or 32-pin LQFP packages.

Rev. 1.0 19

Page 20

C8051F410/1/2/3

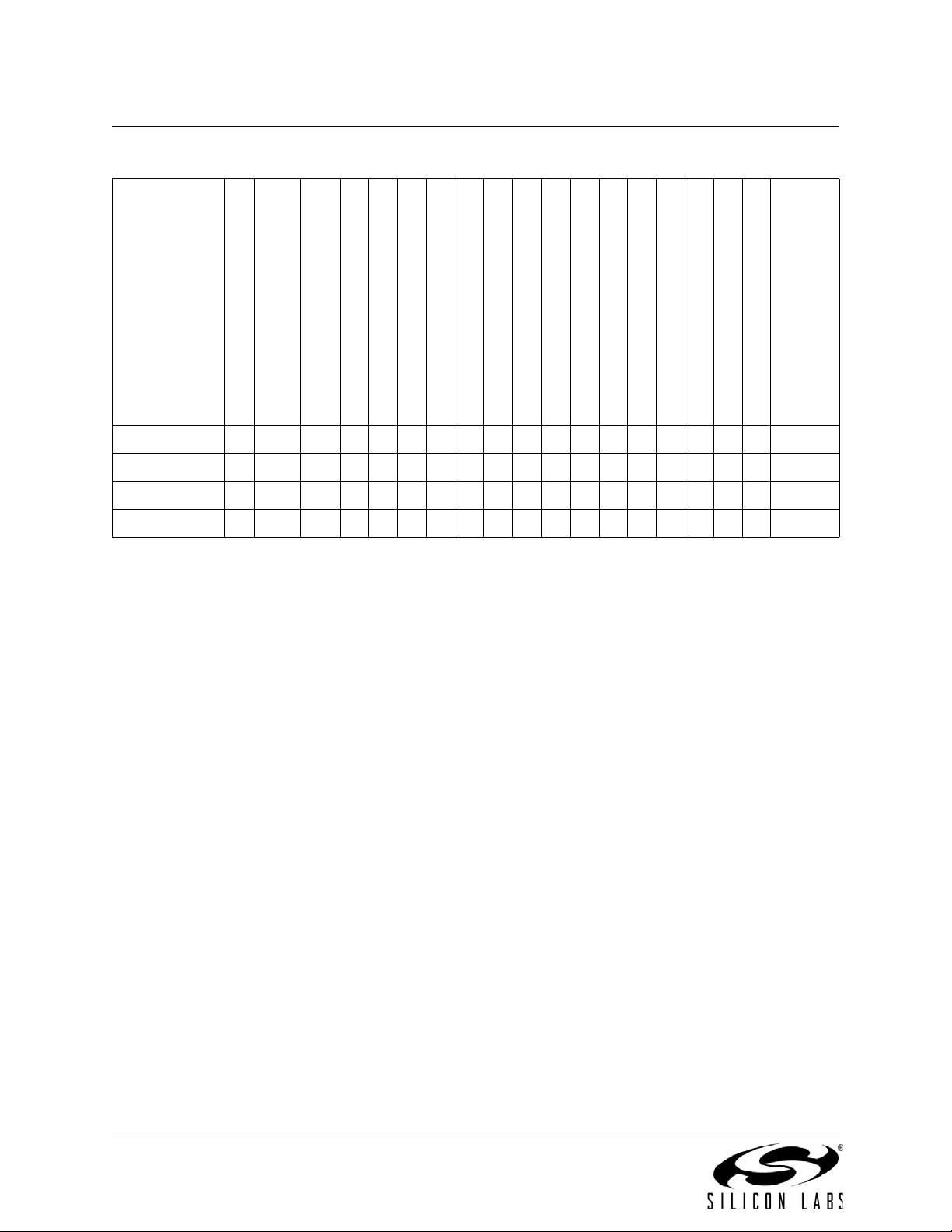

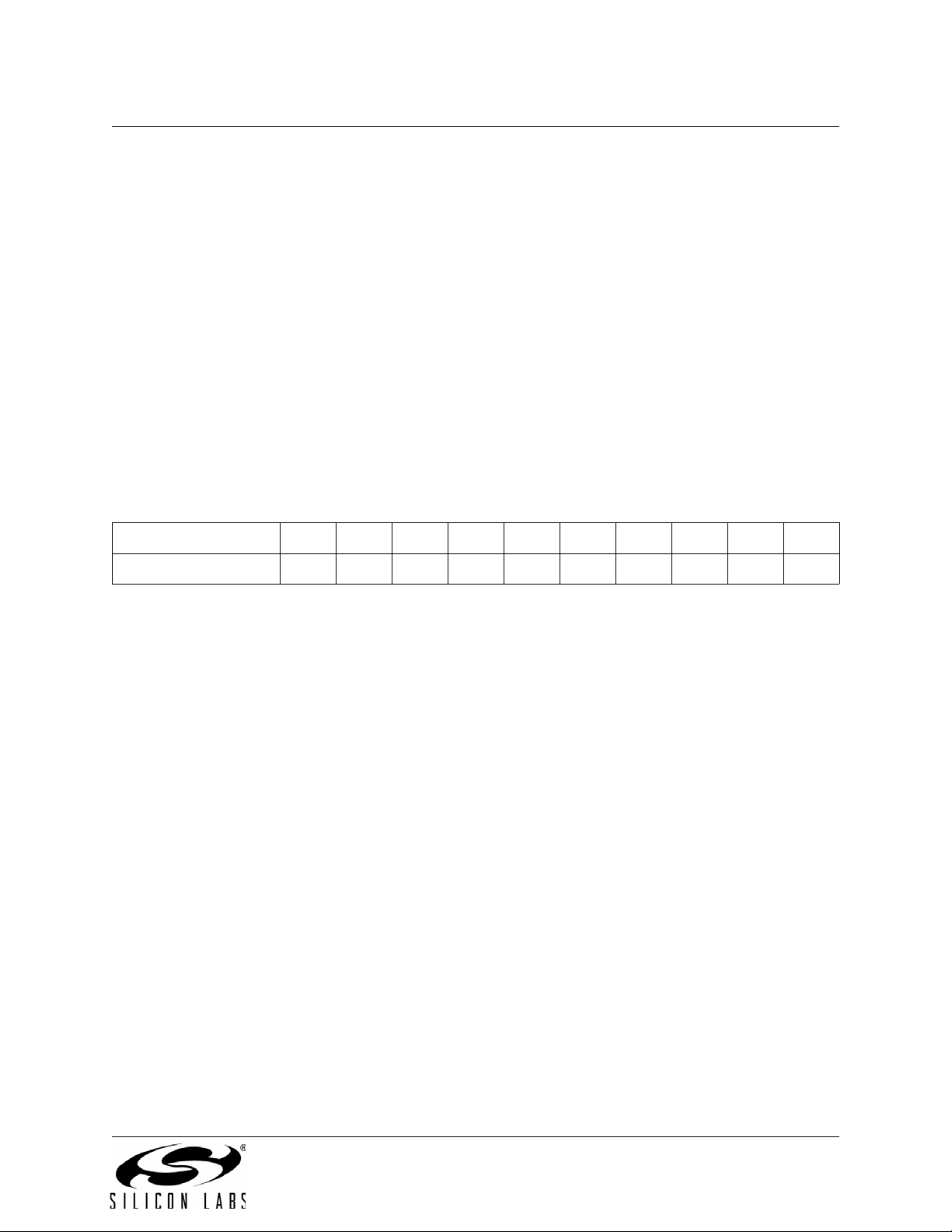

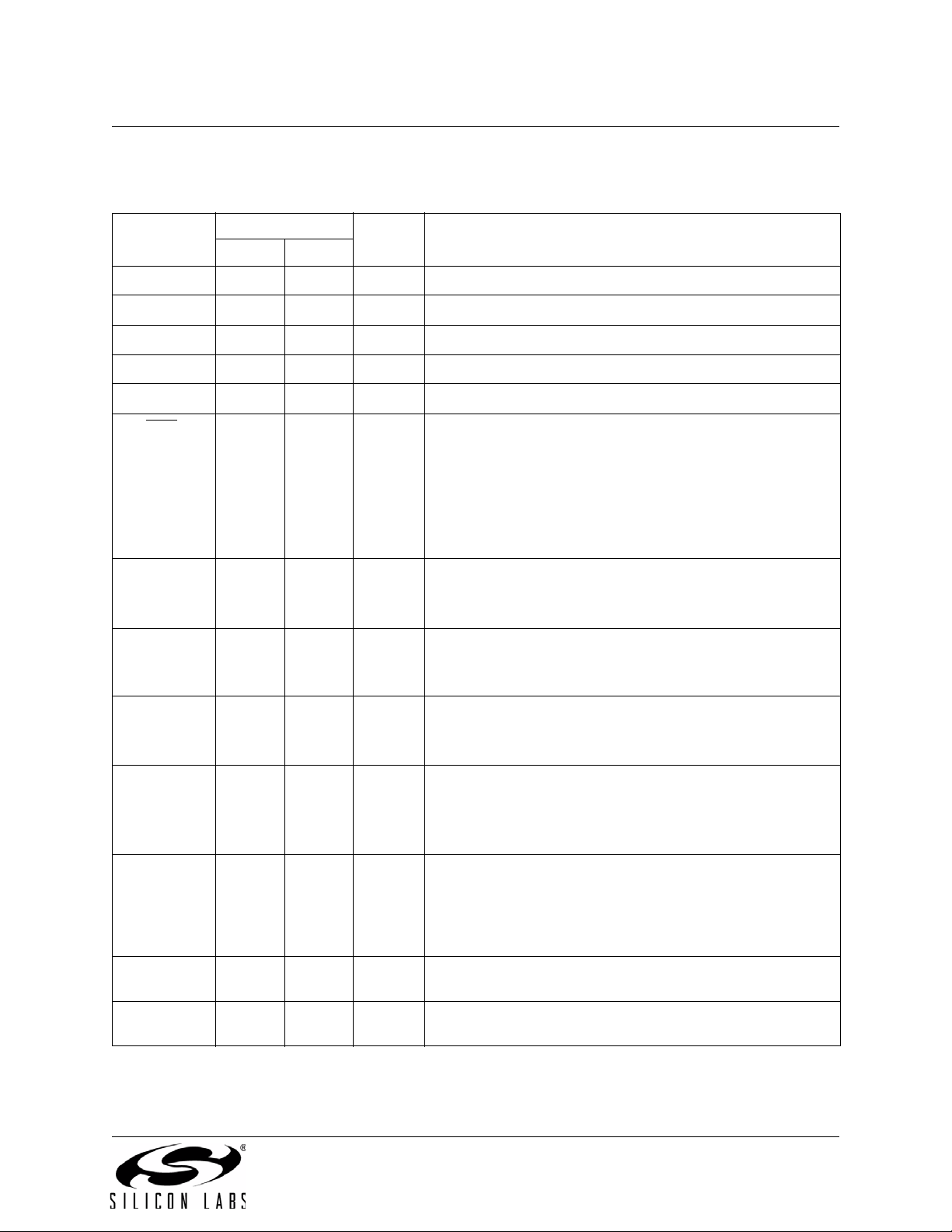

Table 1.1. Product Selection Guide

Ordering Part Number

C8051F410-GQ 50 32 kB 2368

C8051F411-GM 50 32 kB 2368

C8051F412-GQ 50 16 kB 2368

C8051F413-GM 50 16 kB 2368

MIPS (Peak)

Flash Memory

RAM

Calibrated Internal 24.5 MHz Oscillator

Clock Multiplier

SMBus/I2C

SPI

3 3 3 3 3

3 3 3 3 3

3 3 3 3 3

3 3 3 3 3

UART

Timers (16-bit)

Programmable Counter Array

Port I/Os

12-bit ADC ±1 LSB INL

smaRTClock (Real Time Clock)

Two 12-bit Current Output DACs

Internal Voltage Reference

Temperature Sensor

Analog Comparators

Lead-Free (RoHS compliant)

4

3

24

3 3 3 3 3 3 3

4

3

20

3 3 3 3 3 3 3

4

3

24

3 3 3 3 3 3 3

4

3

20

3 3 3 3 3 3 3

Package

LQFP-32

QFN-28

LQFP-32

QFN-28

20 Rev. 1.0

Page 21

C8051F410/1/2/3

VREGIN

VDD

VRTC-BACKUP

GND

/RST/C2CK

XTAL3

XTAL4

VREG

C2D

XTAL1

XTAL2

24.5 MHz

2% Oscillator

smaRTClock Block

(to rest of chip)

POR

External

Oscillator

Circuit

32 KHz

Oscillator

(to smarRTClock Block)

Battery Switch-Over Circuit

(VDD >= VRTC-BACKUP)

Debug HW

Reset

Brown-

Out

Clock

Mult.

64B RAM

smaRTClock

State

Machine

x16

8

FLASH

0

5

1

C

SFR Bus

o

r

e

smaRTClock Alarm

Engine

32 kB

256 B

SRAM

2 kB

XRAM

CRC

VREF

Port 0

Latch

Port 1

Latch

UART

Timer

0,1,2,3

PCA x6 /

WDT

SMBus

SPI

Port 2

Latch

12-bit

IDAC0

12-bit

IDAC1

12-bit

200 ksps

ADC

VDD

IDAC0

IDAC1

Temp

VIO

P

0

D

r

v

C

R

P

O

1

S

S

D

B

r

A

v

R

P

2

D

r

v

CP0

+

-

CP1

+

-

A

AIN0-AIN23

M

U

X

P0.0/IDAC0

P0.1/IDAC1

P0.2

P0.3

P0.4/TX

P0.5/RX

P0.6/CNVST

P0.7

P1.0/XTAL1

P1.1/XTAL2

P1.2/VREF

P1.3

P1.4

P1.5

P1.6

P1.7

P2.0

P2.1

P2.2

P2.3

P2.4

P2.5

P2.6

P2.7/C2D

Figure 1.1. C8051F410 Block Diagram

Rev. 1.0 21

Page 22

C8051F410/1/2/3

VREGIN

VDD

VRTC-BACKUP

GND

/RST/C2CK

XTAL3

XTAL4

VREG

C2D

XTAL1

XTAL2

24.5 MHz

2% Oscillator

smaRTClock Block

(to rest of chip)

POR

External

Oscillator

Circuit

32 KHz

Oscillator

(to smaRTClock Block)

Battery Sw itch - O ve r C irc ui t

(VDD >= VRTC -BACKUP)

Debug HW

Reset

Brown-

Out

Clock

Mult.

64B RAM

smaRTClock

State

Machine

x16

8

FLASH

0

5

1

C

SFR Bus

o

r

e

smaRTClock Alarm

Engine

32 kB

256 B

SRAM

2 kB

XRAM

CRC

VREF

Port 0

Latch

Port 1

Latch

UART

Timer

0,1,2,3

PCA x6 /

WDT

SMBus

SPI

Port 2

Latch

12-bit

IDAC0

12-bit

IDAC1

12-bit

200 ksps

ADC

VDD

IDAC0

IDAC1

Temp

VIO

P

0

D

r

v

C

R

P

O

1

S

S

D

B

r

A

v

R

P

2

D

r

v

CP0

+

-

CP1

+

-

A

AIN0-AIN20

M

U

X

P0.0/IDAC0

P0.1/IDAC1

P0.2

P0.3

P0.4/TX

P0.5/RX

P0.6/CNVST

P0.7

P1.0/XTAL1

P1.1/XTAL2

P1.2/VREF

P1.3

P1.4

P1.5

P1.6

P1.7

P2.0

P2.1

P2.2

P2.7/C2D

Figure 1.2. C8051F411 Block Diagram

22 Rev. 1.0

Page 23

C8051F410/1/2/3

VREGIN

VDD

VRTC-BACKUP

GND

/RST/C2CK

XTAL3

XTAL4

VREG

C2D

XTAL1

XTAL2

24.5 MHz

2% Oscilla to r

smaRTClock Block

(to rest of chip)

POR

External

Oscillator

Circuit

32 KHz

Oscillator

(to smaRTClocl Block)

Battery Switch-Over Circuit

(VDD >= VRTC-BACKUP)

Debug HW

Reset

Brown-

Out

Clock

Mult.

64B RAM

smaRTClock

State

Machine

x16

8

FLASH

0

5

1

C

SFR Bus

o

r

e

smaRTClock Alarm

Engine

16 kB

256 B

SRAM

2 kB

XRAM

CRC

VREF

Port 0

Latch

Port 1

Latch

UART

Timer

0,1,2,3

PCA x6 /

WDT

SMBus

SPI

Port 2

Latch

12-bit

IDAC0

12-bit

IDAC1

12-bit

200 ksps

ADC

VDD

IDAC0

IDAC1

Temp

VIO

P

0

D

r

v

C

R

P

O

1

S

S

D

B

r

A

v

R

P

2

D

r

v

CP0

+

-

CP1

+

-

A

AIN0-AIN23

M

U

X

P0.0/IDAC0

P0.1/IDAC1

P0.2

P0.3

P0.4/TX

P0.5/RX

P0.6/CNVST

P0.7

P1.0/XTAL1

P1.1/XTAL2

P1.2/VREF

P1.3

P1.4

P1.5

P1.6

P1.7

P2.0

P2.1

P2.2

P2.3

P2.4

P2.5

P2.6

P2.7/C2D

Figure 1.3. C8051F412 Block Diagram

Rev. 1.0 23

Page 24

C8051F410/1/2/3

VREGIN

VDD

VRTC-BACKUP

GND

/RST/C2CK

XTAL3

XTAL4

VREG

C2D

XTAL1

XTAL2

24.5 MHz

2% Oscillato r

smaRTClock Block

(to rest of chip)

POR

External

Oscillator

Circuit

32 KHz

Oscillator

(to smaRTClock Block)

Battery Switch-Over Circuit

(VDD >= VRTC-BACKUP)

Debug HW

Reset

Brown-

Out

Clock

Mult.

64B RAM

smaRTClock

State

Machine

x16

8

FLASH

0

5

1

C

SFR Bus

o

r

e

smaRTClock Alarm

Engine

16 kB

256 B

SRAM

2 kB

XRAM

CRC

VREF

Port 0

Latch

Port 1

Latch

UART

Timer

0,1,2,3

PCA x6 /

WDT

SMBus

SPI

Port 2

Latch

12-bit

IDAC0

12-bit

IDAC1

12-bit

200 ksps

ADC

VDD

IDAC0

IDAC1

Temp

VIO

P

0

D

r

v

C

R

P

O

1

S

S

D

B

r

A

v

R

P

2

D

r

v

CP0

+

-

CP1

+

-

A

AIN0-AIN20

M

U

X

P0.0/IDAC0

P0.1/IDAC1

P0.2

P0.3

P0.4/TX

P0.5/RX

P0.6/CNVST

P0.7

P1.0/XTAL1

P1.1/XTAL2

P1.2/VREF

P1.3

P1.4

P1.5

P1.6

P1.7

P2.0

P2.1

P2.2

P2.7/C2D

Figure 1.4. C8051F413 Block Diagram

24 Rev. 1.0

Page 25

C8051F410/1/2/3

1.1. CIP-51™ Microcontroller

1.1.1. Fully 8051 Compatible Instruction Set

The C8051F41x devices use Silicon Laboratories’ proprietary CIP-51 microcontroller core. The CIP-51 is

fully compatible with the MCS-5 1™ instruc tion se t. Standard 803x/805x assembl ers and compile rs can be

used to develop software. The C8051F41x family has a superset of all the peripherals included with a stan

dard 8052.

1.1.2. Improved Throughput

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all ins truction s except for MU L and DIV take 12 or 24 syste m

clock cycles to execute, and usually have a maximum system clock of 12-to-24

51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more

than eight system clock cycles.

With the CIP-51's system clock running at 50 MHz, it has a peak throughput of 50 MIPS. The CIP-51 has a

total of 109 instructions. The table below shows the total number of instructions that require each execution

time.

MHz. By contrast, the CIP-

-

Clocks to Execute 1 2 2/4 3 3/5 4 5 4/6 6 8

Number of Instructions 26 50 5 10 7 5 2 1 2 1

1.1.3. Additional Features

The C8051F41x SoC famil y includes several key enhancements to the CIP-51 co re and peripherals to

improve performance and ease of use in end applications.

An extended interrupt handler allows the numerous analog and digital peripherals to operate independently of the controller core and interrupt the controller only when necessary. By requiring less intervention

from the microcontrol ler co re, an interru pt-driv en sy stem is more efficient and a llows for eas ier impl emen

tation of multi-tasking, real-time systems.

Eight reset sources are available: power-on reset ci rcuitry (POR), an on-chip VDD monitor, a Watchdog

Timer, a Missing Clock Detector, a voltage level detection from Comparator0, a smaRTClock alarm or

missing smaRTClock cl ock detector reset, a forced software reset, an ex ternal reset pin, and an illegal

Flash access protection circuit. Each reset source except for the POR, Reset Input Pin, or Flash error may

be disabled by the user in so ftware. The WDT may be permanently enab led in software after a pow er-on

reset during MCU initialization.

The internal oscillator is factory calibrated to 24.5 MHz ±2%. An external oscillator drive circuit is also

included, allowing an external crystal, ceramic resonator, capacitor , RC, or CMOS clock source to generate

the system clock. A clock multiplier allows for operation at up to 50

lator can be extremel y useful in low power applications, allowi ng the system to maintain accurate time

while the MCU is not po wered, or its internal oscillator is sus pended. The MCU ca n be reset or have its

oscillator awakened using the smaRTClock alarm function.

MHz. The dedicated smaRTClock oscil-

-

Rev. 1.0 25

Page 26

C8051F410/1/2/3

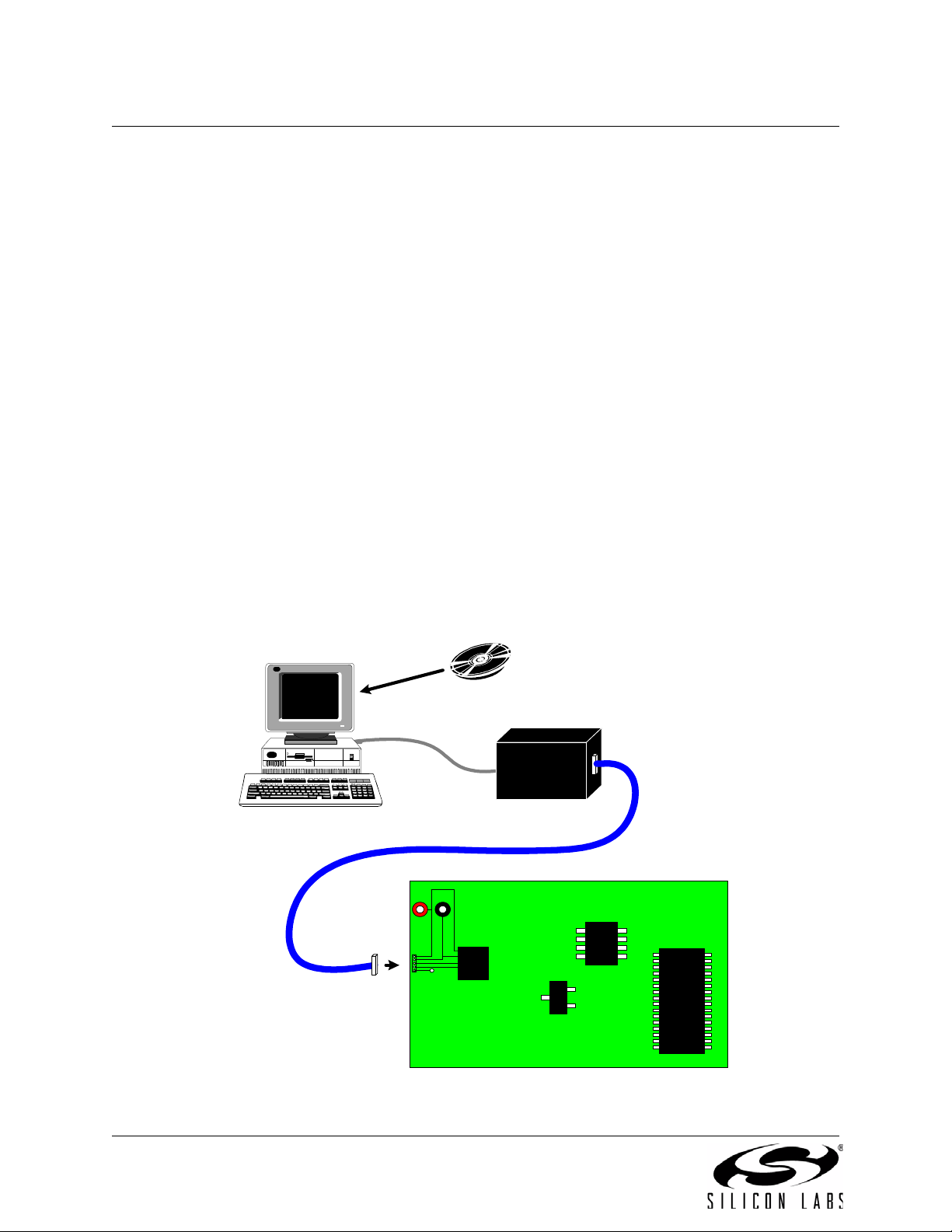

1.2. On-Chip Debug Circuitry

The C8051F41x devices include on-chip Silicon La boratories 2-Wire (C2) debug circuitry that provides

non-intrusive, full speed, in-circuit debugging of the production part installed in the end application.

Silicon Laboratories’ debugging system supports inspection and modification of memory and registers,

breakpoints, and single stepping . No addi tional targe t RAM, prog ram memo ry, timers, or communications

channels are required. All the digital and analog peripherals are functional and work correctly while debug

ging. All the peripherals (except for the ADC and SMBus) are stalled when the MCU is halted, during single

stepping, or at a breakpoint in order to keep them synchronized.

The C8051F410DK development kit provides all the hardware and software necessary to develop application code and perfo rm in-circuit debugging wi th the C8051F41x MCUs. The k it includes software with a

developer's studio and debugger, a USB debug adapter, a target applicati on board with the associated

MCU installed, and the required cables and wall-mount power supply. The development kit requires a com

puter with Windows®98 SE or later installed . As shown in Figure 1.5, the PC is connected to the USB

debug adapter. A six-inch ribbon cable connects th e USB debug ad apter to the user's application boa rd,

picking up the two C2 pins and GND.

The Silicon Labor atories ID E interface is a vastly superior deve loping a nd debugging configuration, compared to standard MCU em ulators that use on-b oard "ICE Chi ps" and requi re the MCU in the app lication

board to be socketed. Sil icon La bor ato rie s’ de bug paradi gm i ncre ases ease of use and preserves the per

formance of the precision analog peripherals.

-

-

-

WINDOWS 98 SE or later

Silicon Laboratories Integrated

Development Environment

USB

Debug

Adapter

C2 (x2), GND

VDD GND

C8051F41x

TARGET PCB

Figure 1.5. Development/In-System Debug Diagram

26 Rev. 1.0

Page 27

C8051F410/1/2/3

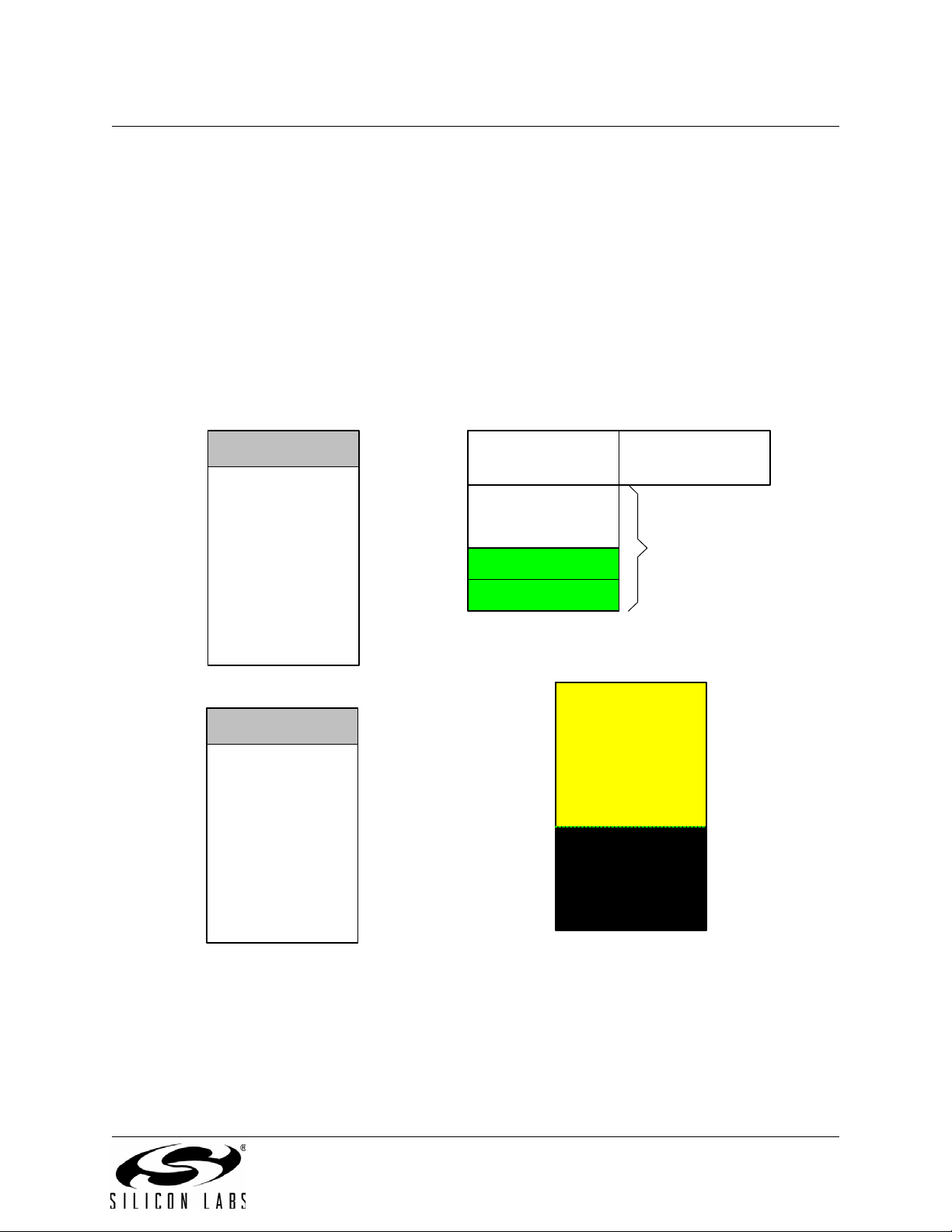

1.3. On-Chip Memory

The CIP-51 has a standa rd 8051 program and data addr ess configuration. It inc ludes 256 bytes of data

RAM, with the upper 128 bytes dual-mapped. Indirect addressing accesses the upper 128 bytes of general

purpose RAM, and d irect addr essing a ccesses the 128-by te SFR add ress space. The lower 128 bytes of

RAM are accessible via direct and indirect addressing. The first 32 bytes are addressable as four banks of

general purpose registers, and the next 16 bytes can be byte addressable or bit addressable.

Program memory con sists of 32 kB (‘F410/1) or 16 kB (‘F41 2/3) of Flash. This memory may be reprogrammed in-system in 512 byte sectors and requires no special off-chip programming voltage.

PROGRAM/DATA MEMORY

(Flash)

‘F410/1

0x7E00

0x7DFF

0x0000

0x4000

0x3FFF

RESERVED

32 kB Flash

(In-System

Programmab le in 51 2

Byte Sectors)

‘F412/3

RESERVED

16 kB Flash

(In-System

Programmable in 512

Byte Sectors)

0xFF

0x80

0x7F

0x30

0x2F

0x20

0x1F

0x00

DATA MEMORY (RAM)

INTERNAL DATA ADDRESS SPACE

Upper 128 RAM

(Indirect Addressing

Only)

(Direct and Indirect

Addressing)

Bit Addressable

General Purpose

Registers

Special Function

Register's

(Direct Addressing Only)

Lower 128 RAM

(Direct and Indirect

Addressing)

EXTERNAL DATA ADDRESS SPACE

0xFFFF

Same 2048 bytes as from

0x0000 to 0x07FF, wrapped

on 2048-byte boundaries

0x0800

0x07FF

XRAM - 2048 Bytes

(accessible using MOVX

instruction)

0x0000

0x0000

Figure 1.6. Memory Map

Rev. 1.0 27

Page 28

C8051F410/1/2/3

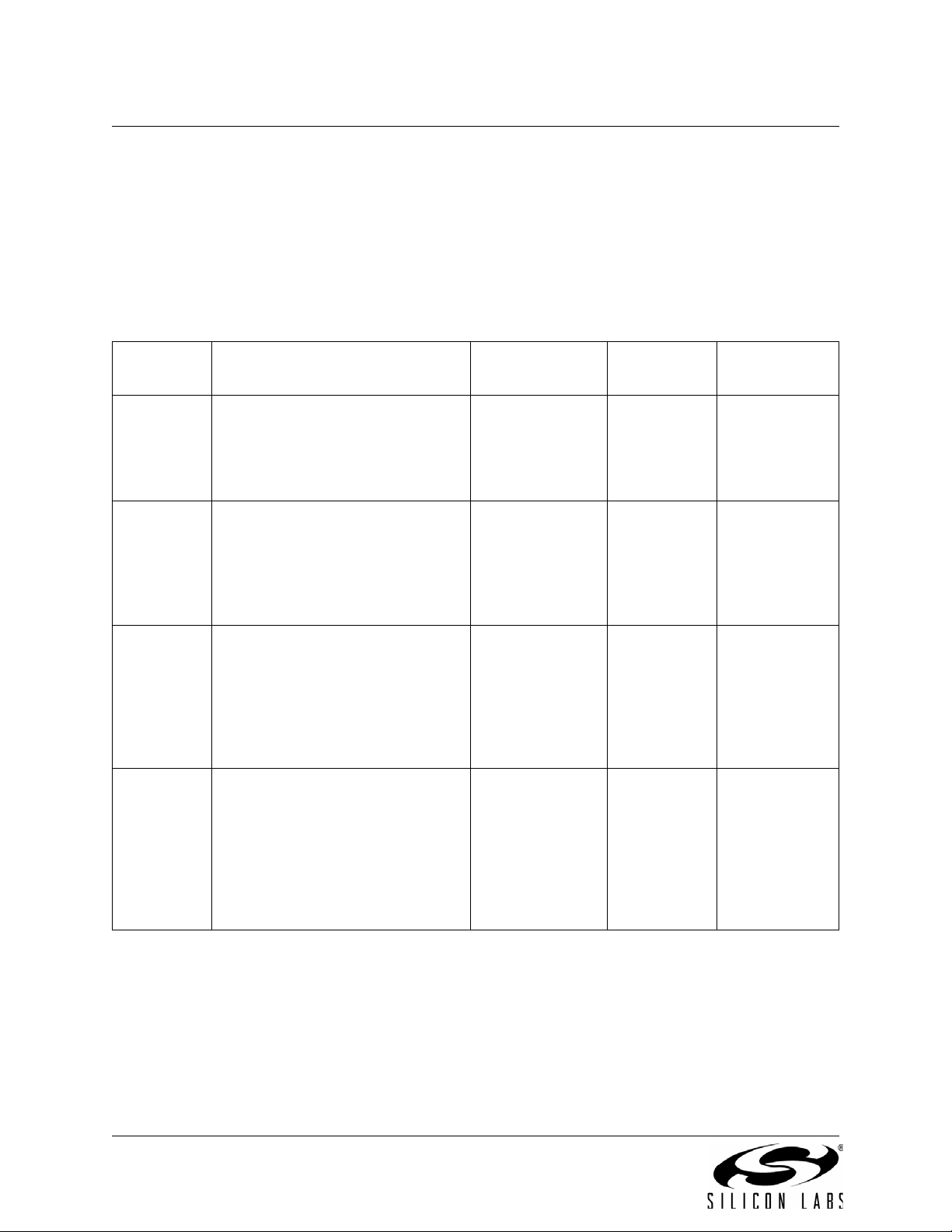

1.4. Operating Modes

The C8051F41x devices have four operating modes: Active (Normal), Idle, Suspend, and Stop. Active

mode occurs during normal ope ration when the oscillator and peri pherals are active. Idle mode halts the

CPU while leaving the peripherals and internal clocks active. Suspend mode halts SYSCLK until a waken

ing event occurs, which also halts all peripherals using SYSCLK. In Stop mode, the CPU is halted, all interrupts and timers are inactive, and the internal oscillator is stopped. The various operating modes are

described in

Table 1.2 below:

Table 1.2. Operating Modes Summary

-

Active

Idle

Suspend

Stop

Properties

•SYSCLK active

• CPU active (accessing Flash)

• Peripherals active or inactive

depending on user settings

• smaRTClock active or inactive

•SYSCLK active

• CPU inactive (not accessing

Flash)

• Peripherals active or inactive

depending on user settings

• smaRTClock active or inactive

•SYSCLK inactive

• CPU inactive (not accessing

Flash)

• Peripherals enabled (but not

operating) or disabled depend

ing on user settings

• smaRTClock active or inactive

•SYSCLK inactive

• CPU inactive (not accessing

Flash)

• Digital peripherals inactive;

analog peripherals enabled

(but not operating) or disabled

depending on user settings

• smaRTClock inactive

Power

Consumption

Full — —

Less than Full IDLE

Low SUSPEND

-

Very low STOP

How

Entered?

(PCON.0)

(OSCICN.5)

(PCON.1)

How Exited?

Any enabled

interrupt or

device reset

Wakening

event or exter

nal/MCD reset

External or

MCD reset

-

See Section “10.3. Power Management Modes” on page 101 for Idle and Stop mode details. See Sec-

tion “19.1.1. Internal Oscillator Suspend Mode” on page 166 for more information on Suspend mode.

28 Rev. 1.0

Page 29

C8051F410/1/2/3

1.5. 12-Bit Analog to Digital Converter

The C8051F41x devices include an on-ch ip 12-bit SAR ADC wit h a 27-channel single -ended input mul tiplexer and a maximum throughput of 200 ksps. The ADC system includes a configurable analog m ultiplexer that selects the positive ADC input, which is measured with respect to GND. Ports 0–2 are available

as ADC inputs; additionally, the on-chip Temperature Sensor output and the co re sup ply vo ltage (V

available as ADC inputs. User firmware may shut down the ADC or use it in Burst Mode to save power.

Conversions can be started in four wa ys: a s oftware comman d, an ove rf low of Timer 2 or 3, or an ex ternal

convert start signal. This flexibility allows the start of conversion to be triggered by software events, a peri

odic signal (timer ov erfl ows ), or ex ternal HW si gn als . Co nv ersi on c om pl eti ons ar e i ndicated by a status bit

and an interrupt (if enab led ) and occ ur a fter 1, 4 , 8, o r 1 6 s amp le s h av e be en ac cumulated by a hardware

accumulator. The resulting data word is latched into the ADC data SFRs upon completion of a conversion.

When the system clo ck is slow, Burst Mode allows ADC0 to automa tically wake from a low pow er shut

down state, acquire and accu mulate samples, then re-enter the low power shutdown state without CPU

intervention.

Window compare registers for the ADC data can be configured to interrupt the controller when ADC data is

either within or o utside of a specified range. Th e ADC can monitor a key v oltage continuously in back

ground mode, but not interrupt the controller unless the converted data is within/outside the specified

range.

DD

) are

-

-

-

P2.3-2.6

available on

C8051F410/2

Temp

Sensor

Analog Multiplexer

P0.0

P0.7

P1.0

P1.7

P2.0

P2.7

VDD

GND

19-to-1

AMUX

Configuration, Control, and Data Registers

Burst Mode

Logic

12-Bit

SAR

ADC

End of

Conversion

Interrupt

Start

Conversion

16

Window Compare

Logic

AD0BUSY (W)

Timer 3 Overflow

CNVSTR Rising Edge

Timer 2 Overflow

ADC Data

Registers

Accumulator

Window

Compare

Interrupt

Figure 1.7. 12-Bit ADC Block Diagram

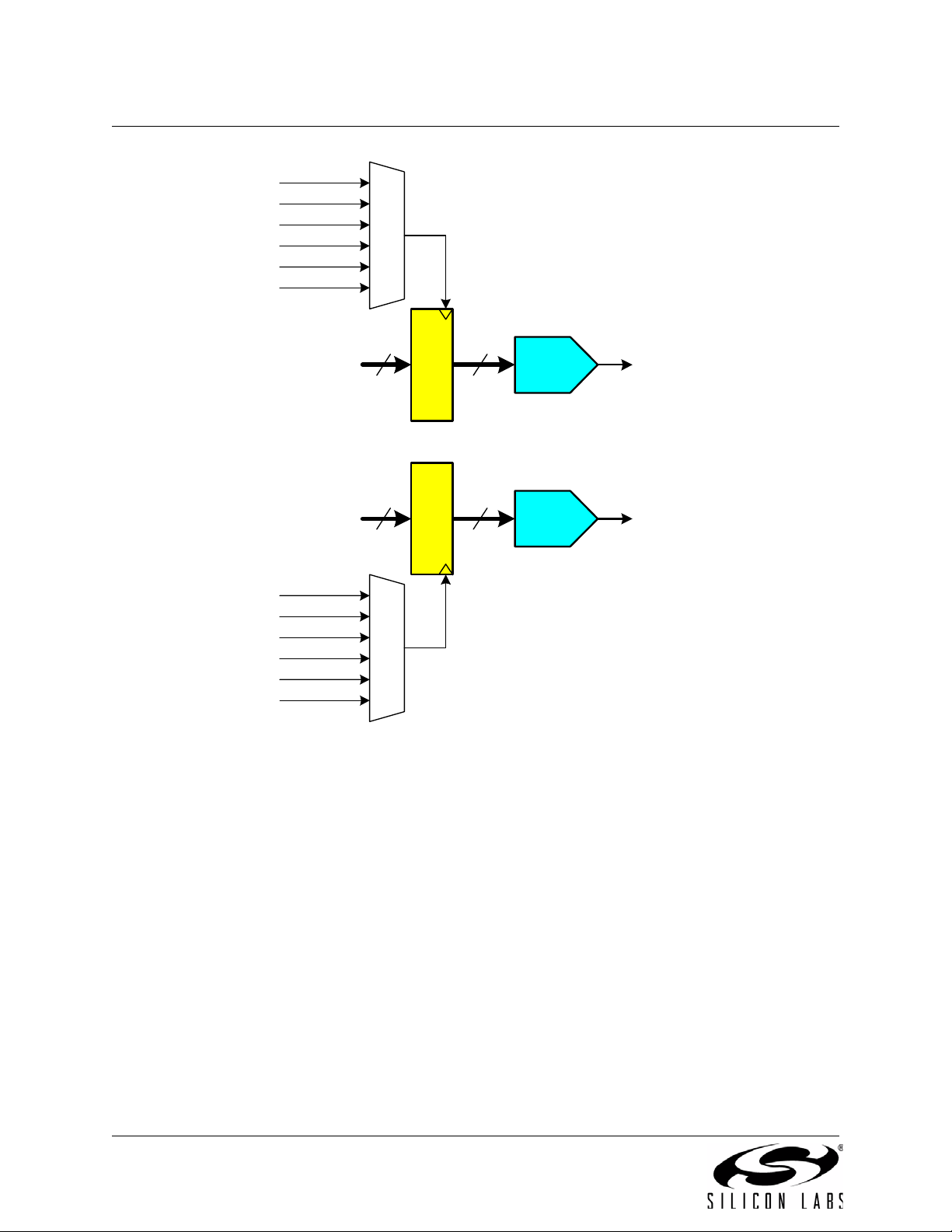

1.6. Two 12-bit Current-Mode DA Cs

The C8051F41x devices in cl ude two 12-bit current-mode Digital-to-Analog Con verte rs (ID ACs ). Th e max imum current output of the IDACs can be adjusted for four different current settings; 0 .25 mA, 0.5 mA,

1

mA, and 2 mA. A flexible output update mechanism allows for seamless full-scale changes, and supports

jitter-free updates for waveform generation. The IDAC outputs can be merged onto a single port I/O pin for

increased full -scale current ou tput or increase d resolution. IDAC updates can be p erformed on-dem and,

scheduled on a Timer overflow, or synchronized with an external signal.

of the IDAC circuitry.

Figure 1.8 shows a block diagram