C8051F320/1

Full Speed USB, 16 k ISP FLASH MCU Family

Analog Peripherals

- 10-Bit ADC

• Up to 200 ksps

• Up to 17 or 13 external single-ended or differential

inputs

• VREF from external pin, internal reference, or VDD

• Built-in temperature sensor

• External conversion start input

- Tw o Comparators

- Internal Voltage Reference

- POR/Brown-Out Detector

USB Function Controller

- USB specification 2.0 compliant

- Full speed (12 Mbps) or low speed (1.5 Mbps)

operation

- Integrated clock recovery; no external crystal

required for full speed or low speed

- Supports eight flexible endpoints

- 1 kB USB buffer memory

- Integrated transceiver; no externa l resi sto rs required

On-Chip Debug

- On-chip debug circuitry facilitates full speed,

non-intrusive in- sy ste m d ebu g (n o em ul ato r req uire d)

- Provides breakpoints, single stepping,

inspect/modify memory and registers

- Superior performance to emulation systems using

ICE-chips, target pods, and sockets

Voltage Regulator Input: 4.0 to 5.25 V

High Speed 8051 µC Core

- Pipelined instruction architecture; executes 70% of

instructions in 1 or 2

system clocks

- Up to 25 MIPS throughput with 25 MHz clock

- Expanded interrupt handler

Memory

- 2304 bytes internal RAM (1k + 256 + 1k USB FIFO)

- 16 kB Flash; In-system programmable in 512-byte

sectors

Digital Peripherals

- 25/21 Port I/O; All 5 V tolerant with high sink current

- Hardware enhanced SPI™, enhanced UART, and

SMBus™ serial ports

- Four gen eral purpose 16-bit c ounter/timers

- 16-bit programmable counter array (PCA) with five

capture/compare modules

- Real time clock mode using external clock source

and PCA or timer

Clock Sources

- Internal Oscillator: 0.25% accuracy with clock

recovery enabled. Supports all USB and UART

modes

- External oscillator: Crystal, RC, C, or Clock

(1 or 2 pin modes)

- Can switch between clock sources on-the-fly;

useful in power saving strategies

RoHS Compliant Packages

- 32-pin LQFP (C8051F320)

- 28-pin QFN (C8051F321)

T e mperature Range: –40 to +85 °C

ANALOG

PERIPHERALS

A

M

U

X

TEMP

SENSOR

10-bit

200 ksps

ADC

PRECISION INTERNAL

OSCILLATOR

+

+

-

VREGVREF

DIGITAL I/O

UART

SPI

SMBus

PCA

Timer 0

Timer 1

Timer 2

Timer 3

USB Controller /

Transceiver

CROSSBAR

Port 0

Port 1

Port 2

Port 3

HIGH-SPEED CONTROLLER CO R E

16 kB

ISP FLASH

16

INTERRUPTS

Rev. 1.2 6/07 Copyright © 2007 by Silicon Laboratories C8051F32x

This information applies to a product under development. Its characteristics and specifications are subject to change without notice.

8051 CPU

(25MIPS)

DEBUG

CIRCUITRY

2304 B

SRAM

POR

WDT

C8051F320/1

2 Rev. 1.2

C8051F320/1

Table of Contents

1. System Overview.................................................................................................... 15

1.1. CIP-51™ Microcontroller Core.......................................................................... 18

1.1.1. Fully 8051 Compatible.............................................................................. 18

1.1.2. Improved Throughput............................................................................... 18

1.1.3. Additional Features. ..... ..... .... ............................ ..... ..... ............................ . 18

1.2. On-Chip Memory............................................................................................... 19

1.3. Universal Serial Bus Controller................................................ ......................... 20

1.4. Voltage Regulator............................................................................................. 21

1.5. On-Chip Debug Circuitry................................................................................... 21

1.6. Programmable Digital I/O and Crossbar........................................................... 22

1.7. Serial Ports....................................................................................................... 23

1.8. Programmable Counter Array........................................................................... 23

1.9. 10-Bit Analog to Digital Converter..................................................................... 24

1.10.Comparators..................................................................................................... 25

2. Absolute Maximum Ratings .................................................................................. 27

3. Global Electrical Characteristics .......................................................................... 28

4. Pinout and Package Definitions............................................................................ 30

5. 10-Bit ADC (ADC0).................................................................................................. 38

5.1. Analog Multiplexer............................................................................................ 39

5.2. Temperature Sensor......................................................................................... 40

5.3. Modes of Operation..........................................................................................42

5.3.1. Starting a Conversion............................................................................... 42

5.3.2. Tracking Modes........................................................................................ 43

5.3.3. Settling Time Requirements..................................................................... 44

5.4. Programmable Window Detector...................................................................... 49

5.4.1. Window Detector In Single-Ended Mode................................................. 51

5.4.2. Window Detector In Differential Mode...................................................... 52

6. Voltage Reference.................................................................................................. 54

7. Comparators ......................................................................................................... 56

8. Voltage Regulator (REG0)...................................................................................... 66

8.1. Regulator Mode Selection................................................................................. 66

8.2. VBUS Detection................................................................................................ 66

9. CIP-51 Microcontroller .......................................................................................... 70

9.1. Instruction Set................................................................................................... 71

9.1.1. Instruction and CPU Timing..................................................................... 71

9.1.2. MOVX Instruction and Program Memory ................................................. 72

9.2. Memory Organization............................................. .... ..... ............................ ..... . 76

9.2.1. Program Memory...................................................................................... 76

9.2.2. Data Memory............................................................................................ 77

9.2.3. General Purpose Registers...................................................................... 77

9.2.4. Bit Addressable Locations........................................................................ 77

9.2.5. Stack ....................................................................................................... 77

9.2.6. Special Function Registers.............. .... ..... ............................ ..... .... ..... ...... 78

Rev. 1.2 3

C8051F320/1

9.2.7. Register Descriptions............................................................................... 82

9.3. Interrupt Handler............................................................................................... 86

9.3.1. MCU Interrupt Sources and Vectors........................................................ 86

9.3.2. External Interrupts.................................................................................... 87

9.3.3. Interrupt Priorities..................................................................................... 87

9.3.4. Interrupt Latency...................................................................................... 88

9.3.5. Interrupt Register Descriptions................................................................. 89

9.4. Power Management Modes.............................................................................. 96

9.4.1. Idle Mode.................................................................................................. 96

9.4.2. Stop Mode................................................................................................ 96

10.Reset Sources ....................................................................................................... 98

10.1.Power-On Reset............................................................................................... 99

10.2.Power-Fail Reset / VDD Monitor .................................................................... 100

10.3.External Reset.................................... ..... .... ..... ............................ ..... .... ..... ....101

10.4.Missing Clock Detector Reset........................................................................ 101

10.5.Comparator0 Reset........................................................................................ 101

10.6.PCA Watchdog Timer Reset ..........................................................................101

10.7.Flash Error Reset........................................................................................... 101

10.8.Software Reset............................................................................................... 102

10.9.USB Reset............................................... .... ..... ..... ............................ .... ..... ....102

11.Flash Memory ..................................................................................................... 105

11.1.Programming The Flash Memory...................................................................105

11.1.1.Flash Lock and Key Functions............................................................... 105

11.1.2.Flash Erase Procedure.......................................................................... 105

11.1.3.Flash Write Procedure........................................................................... 106

11.2.Non-volatile Data Storage......................................... ..... ..... ........................... 106

11.3.Security Options............................................................................................. 107

11.4.Flash Write and Erase Guidelines.................................................................. 109

11.4.1.VDD Maintenance and the VDD Monitor............................................... 109

11.4.2.16.4.2 PSWE Maintenance....................................................................110

11.4.3.System Clock........................ ..... ............................ ..... .... ..... .................. 110

12.External RAM ...................................................................................................... 113

12.1.Accessing User XRAM................................ ..... ..... ............................ .... ..... ....113

12.2.Accessing USB FIFO Space..........................................................................113

13.Oscillators............................................................................................................. 115

13.1.Programmable Internal Oscillator................................................................... 115

13.1.1.Programming the Internal Oscillator on C8051F320/1 Devices............. 116

13.1.2.Internal Oscillator Suspend Mode.......................................................... 117

13.2.External Oscillator Drive Circuit...................................................................... 118

13.2.1.Clocking Timers Directly Through the External Oscillator...................... 118

13.2.2.External Crystal Example....................................................................... 118

13.2.3.External RC Example............................................................................. 119

13.2.4.External Capacitor Example................................................................... 119

13.3.4x Clock Multiplier ........... ..... ..... ............................ .... ..... ..... ........................... 121

13.4.System and USB Clock Selection .................................................................. 122

4 Rev. 1.2

C8051F320/1

13.4.1.System Clock Selection.................................................. ..... .................. 122

13.4.2.USB Clock Selection.............................................................................. 122

14.Port Input/Output ................. ..... ............................ ..... .... ..... ............................ .... 125

14.1.Priority Crossbar Decoder.............................................................................. 127

14.2.Port I/O Initialization....................................................................................... 129

14.3.General Purpose Port I/O.......................................... ..... ............................ ....131

15.Universal Serial Bus Controller (USB)................................................................ 138

15.1.Endpoint Addressing............................................. .... ............................ ..... ....139

15.2.USB Transceiver................................................... .... ............................ ..... ....139

15.3.USB Register Access.............................. .... ............................ ..... ..... .... ..... ....141

15.4.USB Clock Configuration................................................................... .... ..... ....145

15.5.FIFO Management......................................................................................... 146

15.5.1.FIFO Split Mode.....................................................................................146

15.5.2.FIFO Double Buffering........................................................................... 147

15.5.3.FIFO Access.......................................................................................... 147

15.6.Function Addressing.......................................................................................148

15.7.Function Configuration and Control................................................................ 148

15.8.Interrupts........................................................................................................151

15.9.The Serial Interface Engine............................................................................ 156

15.10.Endpoint0..................................................................................................... 156

15.10.1.Endpoint0 SETUP Transactions .......................................................... 157

15.10.2.Endpoint0 IN Transactions................................................................... 157

15.10.3.Endpoint0 OUT Transactions............................................................... 158

15.11.Configuring Endpoints1– 3................ ..... .... ............................ ..... ..... ............. 160

15.12.Controlling Endpoints1–3 IN......................................................................... 161

15.12.1.Endpoints1-3 IN Interrupt or Bulk Mode............................................... 161

15.12.2.Endpoints1-3 IN Isochronous Mode..................................................... 161

15.13.Controlling Endpoints1–3 OUT..................................................................... 164

15.13.1.Endpoints1-3 OUT Interru pt or Bulk Mode.............................. ............. 164

15.13.2.Endpoints1-3 OUT Isochronous Mode................................................. 165

16.SMBus ................................................................................................................... 169

16.1.Supporting Documents................................................................................... 170

16.2.SMBus Configuration......................................................................................170

16.3.SMBus Operation........................................................................................... 170

16.3.1.Arbitration...............................................................................................171

16.3.2.Clock Low Extension.............................................................................. 171

16.3.3.SCL Low Timeout................................................................................... 171

16.3.4.SCL High (SMBus Free) Timeout.......................................................... 172

16.4.Using the SMBus.............................................. ............................ ..... .... ..... ....172

16.4.1.SMBus Configuration Register............................... ..... ........................... 173

16.4.2.SMB0CN Control Register..................................................................... 176

16.4.3.Data Register........................ ............................ ..... ..... .... ....................... 179

16.5.SMBus Transfer Modes.................................................................................. 180

16.5.1.Master Transmitter Mode....................................................................... 180

16.5.2.Master Receiver Mode........................................................................... 181

Rev. 1.2 5

C8051F320/1

16.5.3.Slave Receiver Mode.............................................................................182

16.5.4.Slave Transmitter Mode.........................................................................183

16.6.SMBus Status Decoding.................................................................................184

17.UART0.................................................................................................................... 187

17.1.Enhanced Baud Rate Generation................................................................... 188

17.2.Operational Modes.................... ............................ .... ..... ............................ ....188

17.2.1.8-Bit UART.............................................................................................189

17.2.2.9-Bit UART.............................................................................................190

17.3.Multiprocessor Communications.................................................................... 190

18.Enhanced Serial Peripheral Interface (SPI0)...................................................... 195

18.1.Signal Descriptions.........................................................................................196

18.1.1.Master Out, Slave In (MOSI).................................................................. 196

18.1.2.Master In, Slave Out (MISO).................................................................. 196

18.1.3.Serial Clock (SCK)................................................................................. 196

18.1.4.Slave Select (NSS)................................................................................ 196

18.2.SPI0 Master Mode Operation ......................................................................... 197

18.3.SPI0 Slave Mode Operation........................................................................... 198

18.4.SPI0 Interrupt Sources................................................................................... 199

18.5.Serial Clock Timing........................ ..... ..... .... ..... ............................ ..... .... ..... ....199

18.6.SPI Special Function Registers...................................................................... 202

19. Timers ................................................................................................................... 209

19.1.Timer 0 and Timer 1....................................................................................... 209

19.1.1.Mode 0: 13-bit Counter/Timer................................................................ 209

19.1.2.Mode 1: 16-bit Counter/Timer................................................................ 211

19.1.3.Mode 2: 8-bit Counter/Timer with Auto-Reload...................................... 211

19.1.4.Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)................................. 212

19.2.Timer 2 ..........................................................................................................217

19.2.1.16-bit Timer with Auto-Reload................................................................ 217

19.2.2.8-bit Timers with Auto-Reload................................................................218

19.2.3.USB Start-of-Frame Capture.................................................................. 219

19.3.Timer 3 ..........................................................................................................222

19.3.1.16-bit Timer with Auto-Reload................................................................ 222

19.3.2.8-bit Timers with Auto-Reload................................................................223

19.3.3.USB Start-of-Frame Capture.................................................................. 224

20.Programmable Counter Array (PCA0) ............. ..... ............................ ..... .... ..... .... 227

20.1.PCA Counter/Timer................................. .... ............................ ..... ..... .... ......... 228

20.2.Capture/Compare Modules............................................................................ 229

20.2.1.Edge-triggered Capture Mode................................................................ 230

20.2.2.Software Timer (Compare) Mode........................................................... 232

20.2.3.High Speed Output Mode....................................................................... 233

20.2.4.Frequency Output Mode........................................ ..... .... ..... .................. 234

20.2.5.8-Bit Pulse Width Modulator Mode......................................................... 235

20.2.6.16-Bit Pulse Width Modulator Mode.......................................................236

20.3.Watchdog Timer Mode................................................................................... 236

20.3.1.Watchdog Timer Operation....................................................................237

6 Rev. 1.2

C8051F320/1

20.3.2.Watchdog Timer Usage......................................................................... 238

20.4.Register Descriptions for PCA........................................................................ 239

21.C2 Interface................................. ..... .... ..... ............................ ..... .... ....................... 245

21.1.C2 Interface Registers.................................................................................... 245

21.2.C2 Pin Sharing............................................................................................... 247

Rev. 1.2 7

C8051F320/1

List of Figures and Tables

1. System Overview

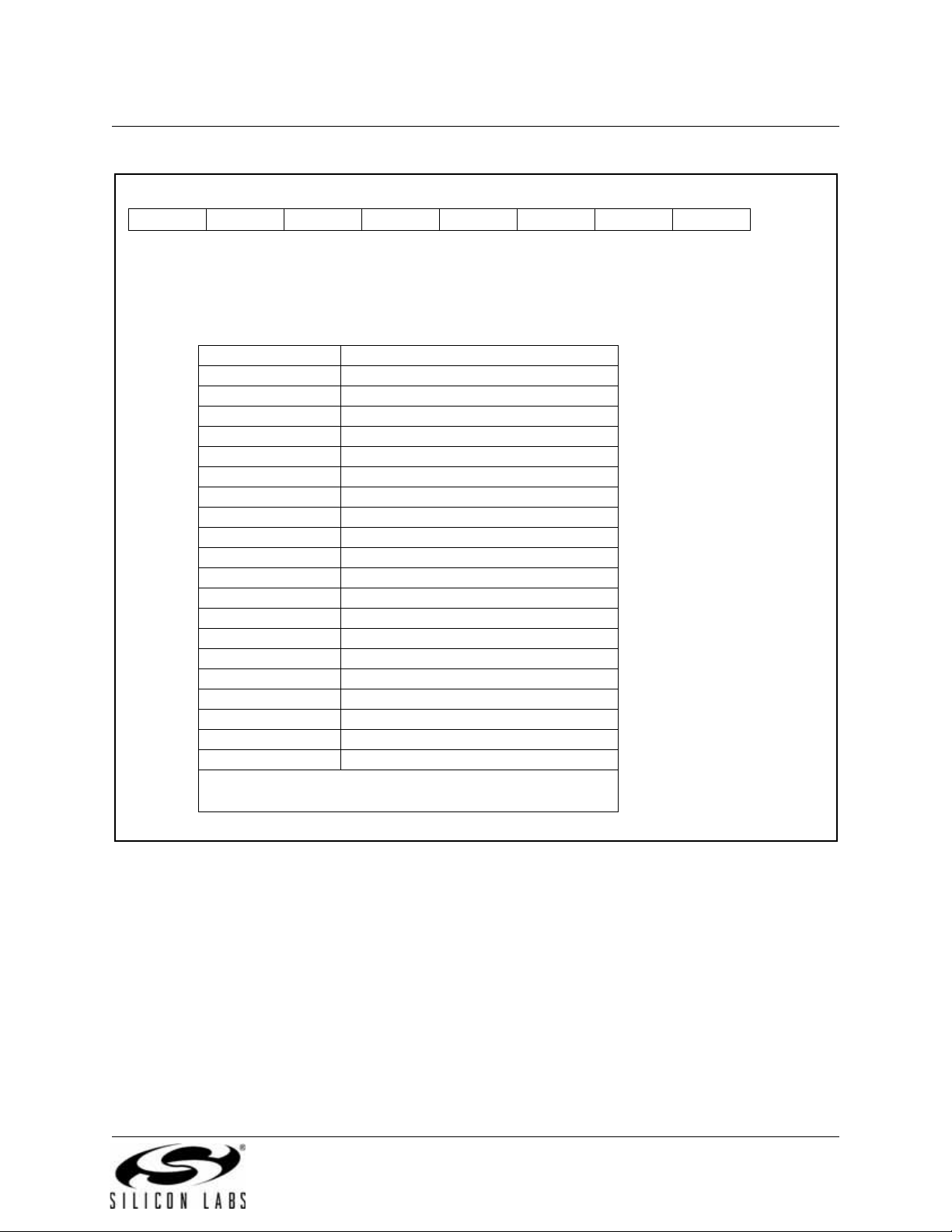

Table 1.1. Product Selection Guide........................................................................ 16

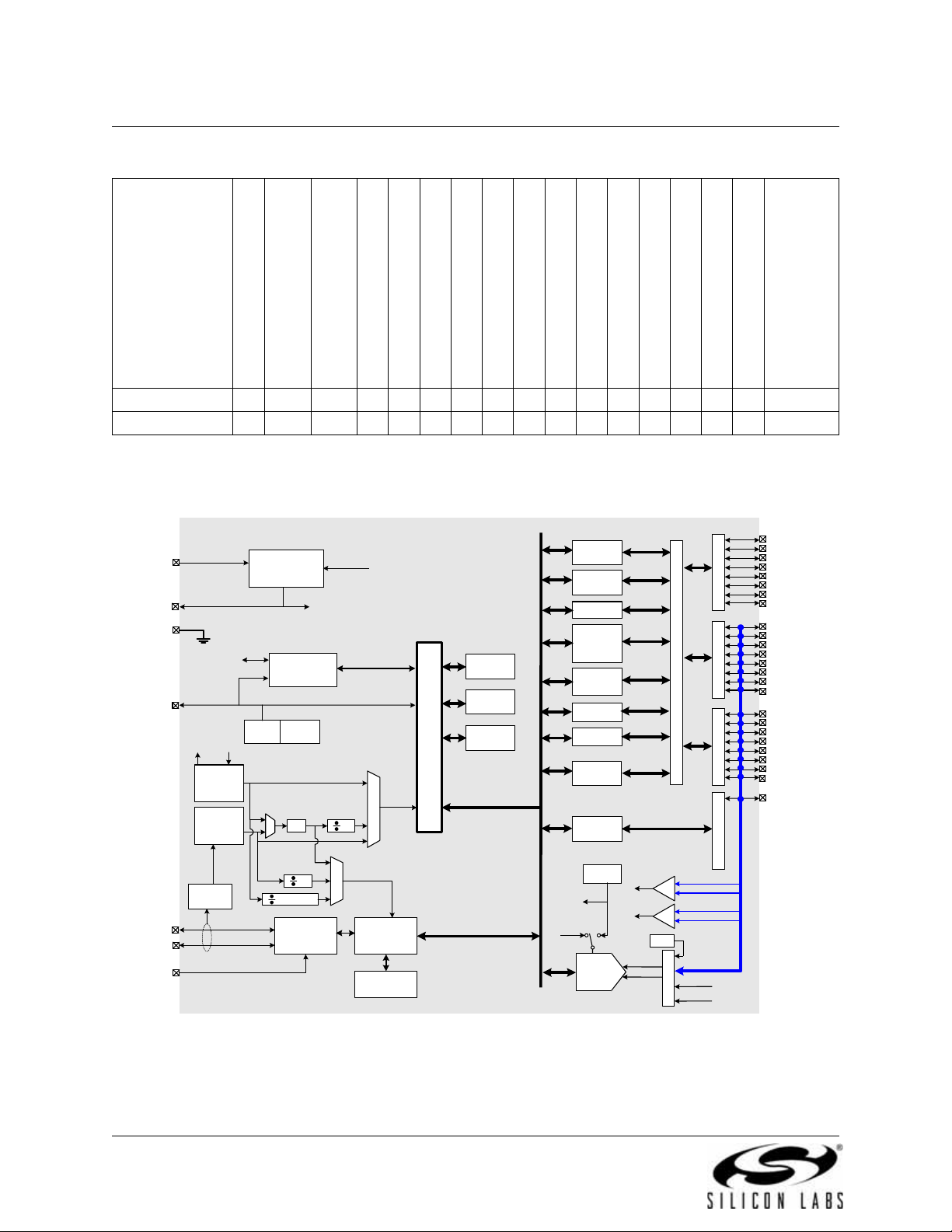

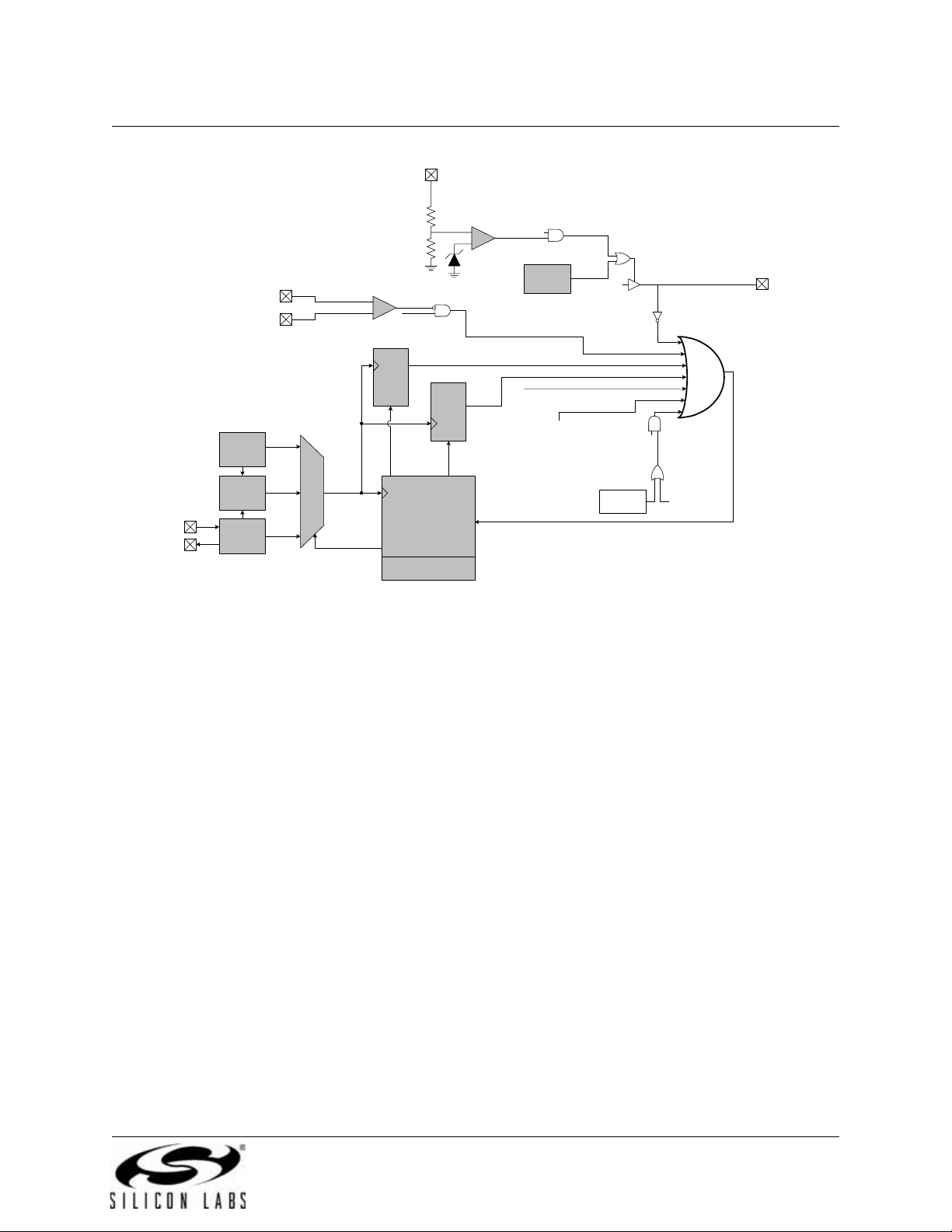

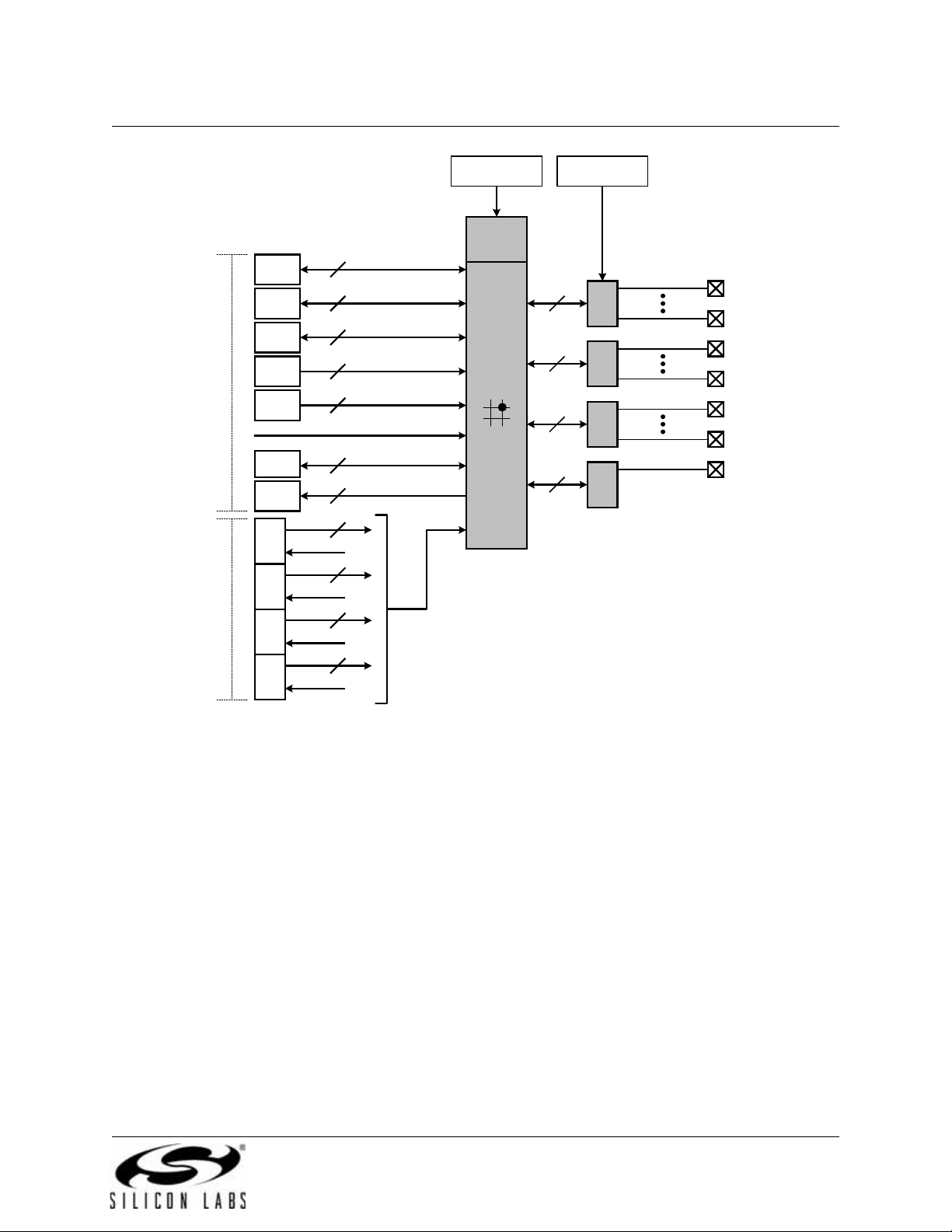

Figure 1.1. C8051F320 Block Diagram.................................................................... 16

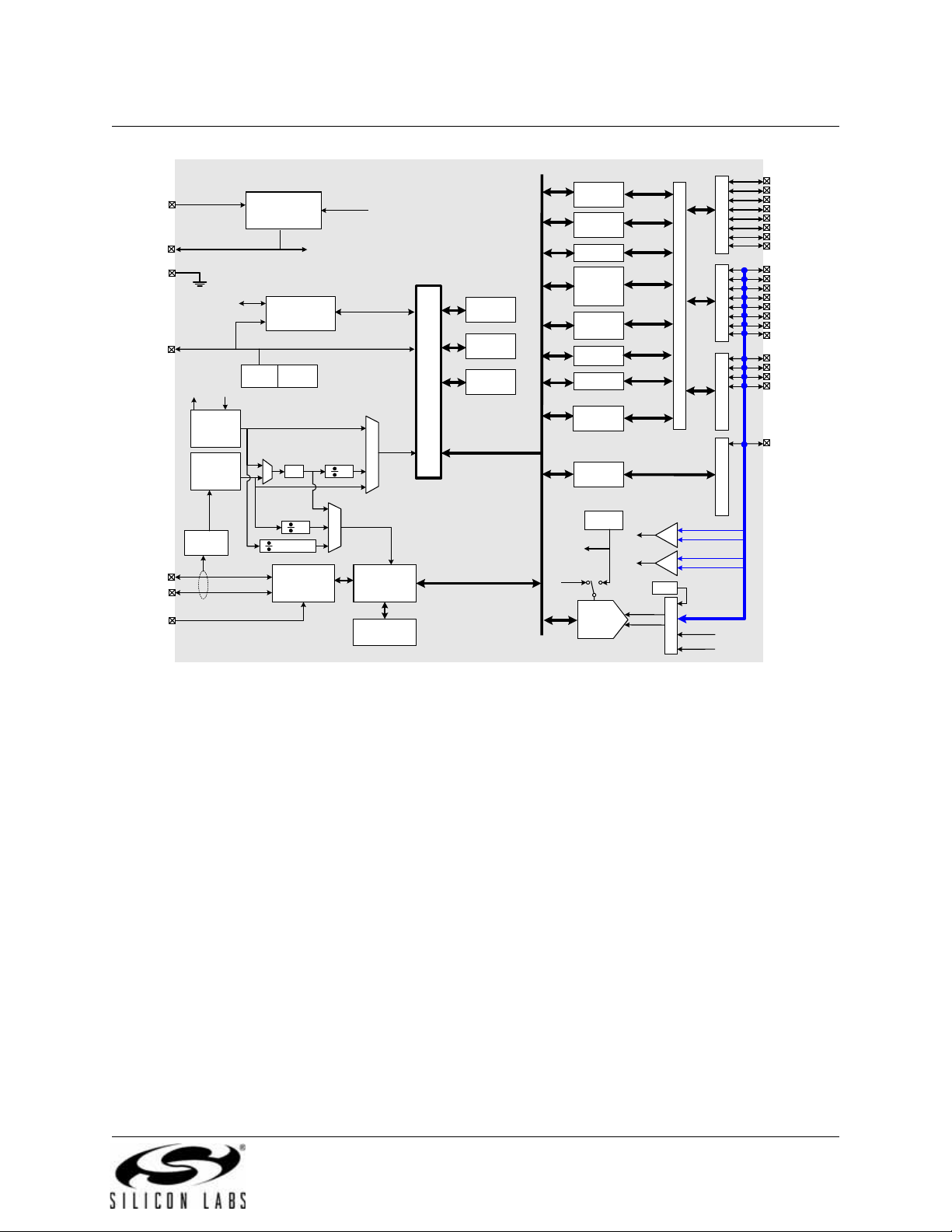

Figure 1.2. C8051F321 Block Diagram.................................................................... 17

Figure 1.3. On-Chip Clock and Reset ...................................................................... 19

Figure 1.4. On-Board Memory Map.......................................................................... 20

Figure 1.5. USB Controller Block Diagram............................................................... 21

Figure 1.6. Development/In-System Debug Diagram............................................... 22

Figure 1.7. Digital Crossbar Diagram....................................................................... 23

Figure 1.8. PCA Block Diagram ............................................................................... 24

Figure 1.9. PCA Block Diagram ............................................................................... 24

Figure 1.10. 10-Bit ADC Block Diagram................................................................... 25

Figure 1.11. Comparator0 Block Diagram................................................................ 26

2. Absolute Maximum Ratings

Table 2.1. Absolute Maximum Ratings .................................................................... 27

3. Global Electrical Characteristics

Table 3.1. Global Electrical Characteristics ............................................................. 28

Table 3.2. Index to Electrical Characteristics Tables.............................................. 29

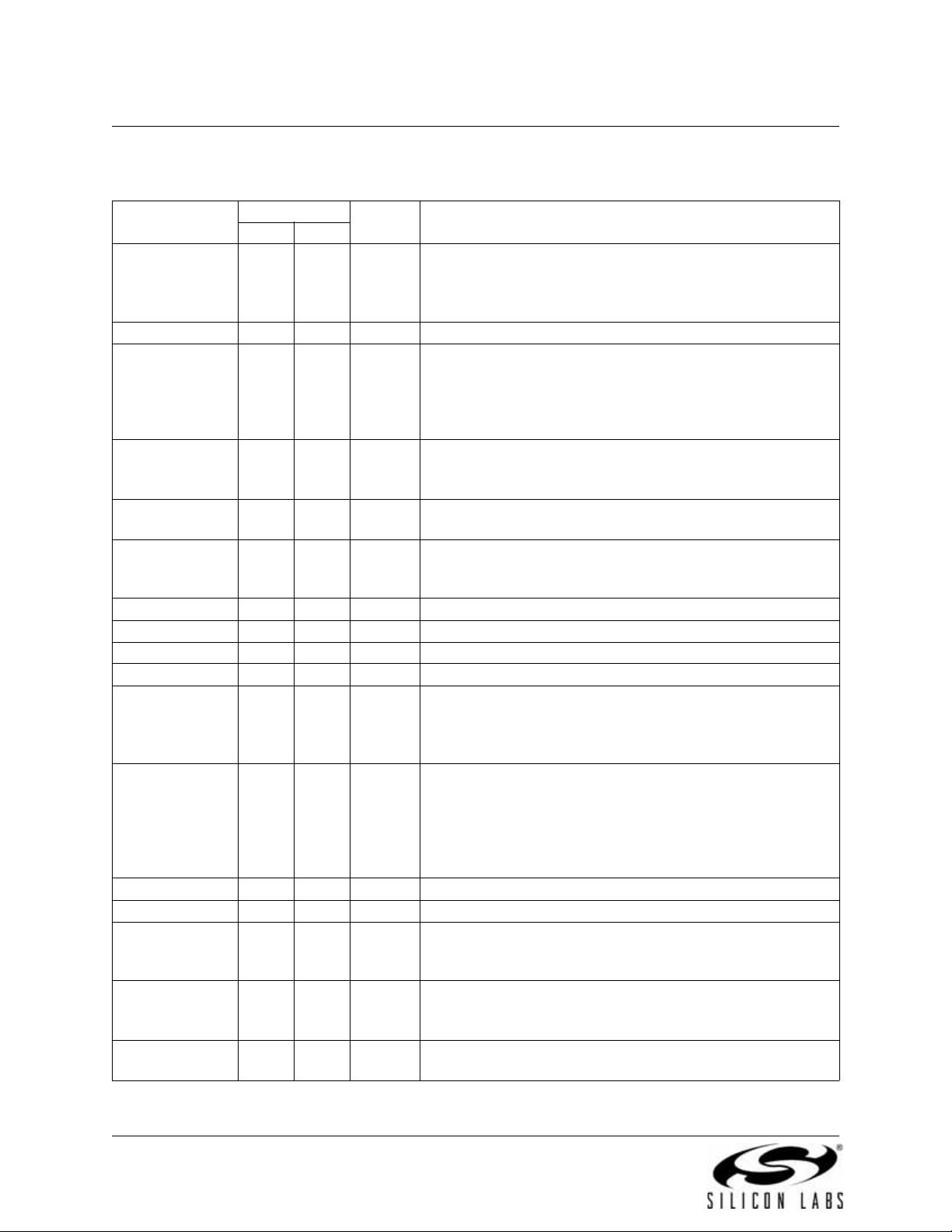

4. Pinout and Package Definitions

Table 4.1. Pin Definitions for the C8051F320/1...................................................... 30

Figure 4.1. LQFP-32 Pinout Diagram (Top View) .................................................... 32

Figure 4.2. LQFP-32 Package Diagram................................................................... 33

Table 4.2. LQFP-32 Package Dimensions.............................................................. 33

Figure 4.3. QFN-28 Pinout Diagram (Top View)...................................................... 34

Figure 4.4. QFN-28 Package Drawing..................................................................... 35

Table 4.3. QFN-28 Package Dimensions................................................................ 35

Figure 4.5. Typical QFN-28 Landing Diagram.......................................................... 36

Figure 4.6. QFN-28 Solder Paste Recommendation................................................37

5. 10-Bit ADC (ADC0)

Figure 5.1. ADC0 Functional Block Diagram............................................................ 38

Figure 5.2. Temperature Sensor Transfer Function................................................. 40

Figure 5.3. Temperature Sensor Error with 1-Point Calibration (VREF = 2.40 V).... 41

Figure 5.4. 10-Bit ADC Track and Conversion Example Timing.............................. 43

Figure 5.5. ADC0 Equivalent Input Circuits.............................................................. 44

Figure 5.6. ADC Window Compare Example: Right-Justified Single-Ended Data... 51

Figure 5.7. ADC Window Compare Example: Left-Justified Single-Ended Data ..... 51

Figure 5.8. ADC Window Compare Example: Right-Justified Differential Data ....... 52

Figure 5.9. ADC Window Compare Example: Left-Justified Differential Data.......... 52

Table 5.1. ADC0 Electrical Characteristics ............................................................. 53

6. Voltage Reference

Figure 6.1. Voltage Reference Functional Block Diagram....................................... 54

Table 6.1. Voltage Reference Electrical Characteristics ......................................... 55

8 Rev. 1.2

C8051F320/1

7. Comparators

Figure 7.1. Comparator0 Functional Block Diagram................................................ 56

Figure 7.2. Comparator1 Functional Block Diagram................................................ 57

Figure 7.3. Comparator Hysteresis Plot................................................................... 58

Table 7.1. Comparator Electrical Characteristics .................................................... 65

8. Voltage Regulator (REG0)

Figure 8.1. External Capacitors for Voltage Regulator Input/Output........................ 66

Table 8.1. Voltage Regulator Electrical Specifications ............................................ 67

Figure 8.2. REG0 Configuration: USB Bus-Powered............................................... 67

Figure 8.3. REG0 Configuration: USB Self-Powered............................................... 68

Figure 8.4. REG0 Configuration: USB Self-Powered, Regulator Disabled .............. 68

Figure 8.5. REG0 Configuration: No USB Connection............................................. 69

9. CIP-51 Microc ontroller

Figure 9.1. CIP-51 Block Diagram............................................................................ 70

Table 9.1. CIP-51 Instruction Set Summary............................................................ 72

Figure 9.2. Memory Map.......................................................................................... 76

Table 9.2. Special Function Register (SFR) Memory Map...................................... 78

Table 9.3. Special Function Registers ............... ..... ..... .... ............................ ..... ..... . 79

Table 9.4. Interrupt Summary ................................................................................. 88

10.Reset Sources

Figure 10.1. Reset Sources...................................................................................... 98

Figure 10.2. Power-On and VDD Monitor Reset Timing .......................................... 99

Table 10.1. Reset Electrical Characteristics .......................................................... 104

11.Flash Memory

Table 11.1. Flash Electrical Characteristics .......................................................... 106

Figure 11.1. Flash Program Memory Map and Secu rity Byte............................. ....107

Table 11.2. Flash Security Summary..................................................................... 108

12.External RAM

Figure 12.1. External Ram Memory Map................................................................113

Figure 12.2. XRAM Memory Map Expanded View................................................. 114

13.Oscillators

Figure 13.1. Oscillator Diagram.............................................................................. 115

Table 13.1. Typical USB Full Speed Clock Settings...............................................122

Table 13.2. Typical USB Low Speed Clock Settings..............................................123

Table 13.3. Internal Oscillator Electrical Characteristics ....................................... 124

14.Port Input/Output

Figure 14.1. Port I/O Functional Block Diagram..................................................... 125

Figure 14.2. Port I/O Cell Block Diagram............................................................... 126

Figure 14.3. Crossbar Priority Decoder with No Pins Skipped............................... 127

Figure 14.4. Crossbar Priority Decoder with Crystal Pins Skipped ........................ 128

Table 14.1. Port I/O DC Electrical Characteristics ................................................ 137

15.Universal Serial Bus Controller (USB)

Figure 15.1. USB0 Block Diagram.......................................................................... 138

Table 15.1. Endpoint Addressing Scheme............................................................. 139

Figure 15.2. USB0 Register Access Scheme ......................................................... 141

Rev. 1.2 9

C8051F320/1

Table 15.2. USB0 Controller Registers ..................................................................143

Figure 15.3. USB FIFO Allocation..........................................................................146

Table 15.3. FIFO Configurations............................................................................ 147

Table 15.4. USB Transceiver Electrical Characteristics ........................................ 168

16.SMBus

Figure 16.1. SMBus Block Diagram....................................................................... 169

Figure 16.2. Typical SMBus Configuration............................................................. 170

Figure 16.3. SMBus Transaction............................................................................ 171

Table 16.1. SMBus Clock Source Selection ........................................................... 173

Figure 16.4. Typical SMBus SCL Generation.........................................................174

Table 16.2. Minimum SDA Setup and Hold Times................................................. 174

Table 16.3. Sources for Hardware Changes to SMB0CN...................................... 178

Figure 16.5. Typical Master Transmitter Sequence................................................ 180

Figure 16.6. Typical Master Receiver Sequence.................................................... 181

Figure 16.7. Typical Slave Receiver Sequence...................................................... 182

Figure 16.8. Typical Slave Transmitter Sequence..................................................183

Table 16.4. SMBus Status Decoding...................................................................... 184

17.UART0

Figure 17.1. UART0 Block Diagram....................................................................... 187

Figure 17.2. UART0 Baud Rate Logic............................................. ..... ..... .... ..... ....188

Figure 17.3. UART Interconnect Diagram.............................................................. 189

Figure 17.4. 8-Bit UART Timing Diagram............................................................... 189

Figure 17.5. 9-Bit UART Timing Diagram............................................................... 190

Figure 17.6. UART Multi-Processor Mode Interconnect Diagram.......................... 191

Table 17.1. Timer Settings for Standard Baud Rates Using The Internal Oscillator 194

18.Enhanced Serial Peri pheral Interfac e (SPI0)

Figure 18.1. SPI Block Diagram............................................................................. 195

Figure 18.2. Multiple-Master Mode Connection Diagram....................................... 198

Figure 18.3. 3-Wire Single Master and Slave Mode Connection Diagram............. 198

Figure 18.4. 4-Wire Single Master Mode and 4-Wire

Slave Mode Connection Diagram.............................................. ..... ....198

Figure 18.5. Master Mode Data/Clock Timing........................................................ 200

Figure 18.6. Slave Mode Data/Clock Timing (CKPHA = 0).................................... 200

Figure 18.7. Slave Mode Data/Clock Timing (CKPHA = 1).................................... 201

Figure 18.8. SPI Master Timing (CKPHA = 0)........................................................ 206

Figure 18.9. SPI Master Timing (CKPHA = 1)........................................................ 206

Figure 18.10. SPI Slave Timing (CKPHA = 0)........................................................207

Figure 18.11. SPI Slave Timing (CKPHA = 1)........................................................207

Table 18.1. SPI Slave Timing Parameters ............................................................. 208

19.Timers

Figure 19.1. T0 Mode 0 Block Diagram.................................................................. 210

Figure 19.2. T0 Mode 2 Block Diagram.................................................................. 211

Figure 19.3. T0 Mode 3 Block Diagram.................................................................. 212

Figure 19.4. Timer 2 16-Bit Mode Block Diagram .................................................. 217

Figure 19.5. Timer 2 8-Bit Mode Block Diagram .................................................... 218

10 Rev. 1.2

C8051F320/1

Figure 19.6. Timer 2 SOF Capture Mode (T2SPLIT = ‘0’)...................................... 219

Figure 19.7. Timer 2 SOF Capture Mode (T2SPLIT = ‘1’)...................................... 219

Figure 19.8. Timer 3 16-Bit Mode Block Diagram .................................................. 222

Figure 19.9. Timer 3 8-Bit Mode Block Diagram .................................................... 223

Figure 19.10. Timer 3 SOF Capture Mode (T3SPLIT = ‘0’).................................... 224

Figure 19.11. Timer 3 SOF Capture Mode (T3SPLIT = ‘1’).................................... 224

20.Programmable Counter Array (PCA0)

Figure 20.1. PCA Block Diagram............................................................................ 227

Table 20.1. PCA Timebase Input Options.............................................................. 228

Figure 20.2. PCA Counter/Timer Block Diagram....................................................228

Table 20.2. PCA0CPM Register Settings for PCA Capture/Compare Modules..... 229

Figure 20.3. PCA Interrupt Block Diagram............................................................. 230

Figure 20.4. PCA Capture Mode Diagram.............................................................. 231

Figure 20.5. PCA Software Timer Mode Diagram.................................................. 232

Figure 20.6. PCA High Speed Output Mode Diagram............................................233

Figure 20.7. PCA Frequency Output Mode............................................................234

Figure 20.8. PCA 8-Bit PWM Mode Diagram......................................................... 235

Figure 20.9. PCA 16-Bit PWM Mode...................................................................... 236

Figure 20.10. PCA Module 4 with Watchdog Timer Enabled................................. 237

Table 20.3. Watchdog Timer Timeout Intervals...................................................... 239

21.C2 Interface

Figure 21.1. Typical C2 Pin Sharing....................................................................... 247

Rev. 1.2 11

C8051F320/1

List of Registers

SFR Definition 5.1. AMX0P: AMUX0 Positive Channel Select . . . . . . . . . . . . . . . . . . 45

SFR Definition 5.2. AM X0 N: AMU X0 Ne ga ti ve Ch an nel Select . . . . . . . . . . . . . . . . . . 46

SFR Definition 5.3. ADC0CF: ADC0 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

SFR Definition 5.4. ADC0H: ADC0 Data Word MSB . . . . . . . . . . . . . . . . . . . . . . . . . . 47

SFR Definition 5.5. ADC0L: ADC0 Data Word LSB . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

SFR Definition 5.6. ADC0CN: ADC0 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

SFR Definition 5.7. ADC0GTH: ADC0 Greater-Than Data High Byte . . . . . . . . . . . . . 49

SFR Definition 5.8. ADC0GTL: ADC0 Greater-Than Data Low Byte . . . . . . . . . . . . . 49

SFR Definition 5.9. ADC0LTH: ADC0 Less-Than Data High Byte . . . . . . . . . . . . . . . . 50

SFR Definition 5.10. ADC0LTL: ADC0 Less-Than Data Low Byte . . . . . . . . . . . . . . . 50

SFR Definition 6.1. REF0CN: Reference Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

SFR Definition 7.1. CPT0CN: Comparator0 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

SFR Definition 7.2. CPT0MX: Comparator0 MUX Selection . . . . . . . . . . . . . . . . . . . . 60

SFR Definition 7.3. CPT0MD: Comparator0 Mode Selection . . . . . . . . . . . . . . . . . . . . 61

SFR Definition 7.4. CPT1CN: Comparator1 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

SFR Definition 7.5. CPT1MX: Comparator1 MUX Selection . . . . . . . . . . . . . . . . . . . . 63

SFR Definition 7.6. CPT1MD: Comparator1 Mode Selection . . . . . . . . . . . . . . . . . . . . 64

SFR Definition 8.1. REG0CN: Voltage Regulator Control . . . . . . . . . . . . . . . . . . . . . . 69

SFR Definition 9.1. DPL: Data Pointer Low Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

SFR Definition 9.2. DPH: Data Pointer High Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

SFR Definition 9.3. SP: Stack Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

SFR Definition 9.4. PSW: Program Status Word . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

SFR Definition 9.5. ACC: Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

SFR Definition 9.6. B: B Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

SFR Definition 9.7. IE: Interrupt Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

SFR Definition 9.8. IP: Interrupt Priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

SFR Definition 9.9. EIE1: Extended Interrupt Enable 1 . . . . . . . . . . . . . . . . . . . . . . . . 92

SFR Definition 9.10. EIP1: Extended Interrupt Priority 1 . . . . . . . . . . . . . . . . . . . . . . . 93

SFR Definition 9.11. EIE2: Extended Interrupt Enable 2 . . . . . . . . . . . . . . . . . . . . . . . 94

SFR Definition 9.12. EIP2: Extended Interrupt Priority 2 . . . . . . . . . . . . . . . . . . . . . . . 94

SFR Definition 9.13. IT01CF: INT0/INT1 Configuration . . . . . . . . . . . . . . . . . . . . . . . . 95

SFR Definition 9.14. PCON: Power Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

SFR Definition 10.1. VDM0CN: VDD Monitor Control . . . . . . . . . . . . . . . . . . . . . . . . 100

SFR Definition 10.2. RSTSRC: Reset Source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

SFR Definition 11.1. PSCTL: Program Store R/W Control . . . . . . . . . . . . . . . . . . . . . 111

SFR Definition 11.2. FLKEY: Flash Lock and Key . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

SFR Definition 11.3. FLSCL: Flash Scale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

SFR Definition 12.1. EMI0CN: External Memory Interface Control . . . . . . . . . . . . . . 114

SFR Definition 13.1. OSCICN: Internal Oscillator Control . . . . . . . . . . . . . . . . . . . . .117

SFR Definition 13.2. OSCICL: Internal Oscillator Calibration . . . . . . . . . . . . . . . . . . .117

SFR Definition 13.3. OSCXCN: External Oscillator Control . . . . . . . . . . . . . . . . . . . . 120

SFR Definition 13.4. CLKMUL: Clock Multiplier Control . . . . . . . . . . . . . . . . . . . . . . . 121

SFR Definition 13.5. CLKSEL: Clock Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

12 Rev. 1.2

C8051F320/1

SFR Definition 14.1. XBR0: Port I/O Crossbar Register 0 . . . . . . . . . . . . . . . . . . . . . 130

SFR Definition 14.2. XBR1: Port I/O Crossbar Register 1 . . . . . . . . . . . . . . . . . . . . . 131

SFR Definition 14.3. P0: Port0 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .132

SFR Definition 14.4. P0MDIN: Port0 Input Mode Register . . . . . . . . . . . . . . . . . . . . . 132

SFR Definition 14.5. P0MDOUT: Port0 Output Mode Register . . . . . . . . . . . . . . . . . 132

SFR Definition 14.6. P0SKIP: Port0 Skip Register . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

SFR Definition 14.7. P1: Port1 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

SFR Definition 14.8. P1MDIN: Port1 Input Mode Register . . . . . . . . . . . . . . . . . . . . . 133

SFR Definition 14.9. P1MDOUT: Port1 Output Mode Register . . . . . . . . . . . . . . . . . 134

SFR Definition 14.10. P1SKIP: Port1 Skip Register . . . . . . . . . . . . . . . . . . . . . . . . . .134

SFR Definition 14.11. P2: Port2 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .134

SFR Definition 14.12. P2MDIN: Port2 Input Mode Register . . . . . . . . . . . . . . . . . . . . 135

SFR Definition 14.13. P2MDOUT: Port2 Output Mode Register . . . . . . . . . . . . . . . .135

SFR Definition 14.14. P2SKIP: Port2 Skip Register . . . . . . . . . . . . . . . . . . . . . . . . . .135

SFR Definition 14.15. P3: Port3 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .136

SFR Definition 14.16. P3MDIN: Port3 Input Mode Register . . . . . . . . . . . . . . . . . . . . 136

SFR Definition 14.17. P3MDOUT: Port3 Output Mode Register . . . . . . . . . . . . . . . .136

SFR Definition 15.1. USB0XCN: USB0 Transceiver Control . . . . . . . . . . . . . . . . . . . 140

SFR Definition 15.2. USB0ADR: USB0 Indirect Address . . . . . . . . . . . . . . . . . . . . . . 142

SFR Definition 15.3. USB0DAT: USB0 Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

USB Register Definition 15.4. INDEX: USB0 Endpoint Index . . . . . . . . . . . . . . . . . . . 144

USB Register Definition 15.5. CLKREC: Clock Recovery Control . . . . . . . . . . . . . . . 145

USB Register Definition 15.6. FIFOn: USB0 Endpoint FIFO Access . . . . . . . . . . . . . 147

USB Register Definition 15.7. FADDR: USB0 Function Address . . . . . . . . . . . . . . . . 148

USB Register Definition 15.8. POWER: USB0 Power . . . . . . . . . . . . . . . . . . . . . . . . 150

USB Register Definition 15.9. FRAMEL: USB0 Frame Number Low . . . . . . . . . . . . . 151

USB Register Definition 15.10. FRAMEH: USB0 Frame Number High . . . . . . . . . . . 151

USB Register Definition 15.11. IN1INT: USB0 IN Endpoint Interrupt . . . . . . . . . . . . 152

USB Register Definition 15.12. OUT1INT: USB0 Out Endpoint Interrupt . . . . . . . . . . 153

USB Register Definition 15.13. CMINT: USB0 Common Interrupt . . . . . . . . . . . . . . .154

USB Register Definition 15.14. IN1IE: USB0 IN Endpoint Interrupt Enable . . . . . . . . 155

USB Register Definition 15.15. OUT1IE: USB0 Out Endpoint Interrupt Enable . . . . . 155

USB Register Definition 15.16. CMIE: USB0 Common Interrupt Enable . . . . . . . . . . 156

USB Register Definition 15.17. E0CSR: USB0 Endpoint0 Control . . . . . . . . . . . . . . . 159

USB Register Definition 15.18. E0CNT: USB0 Endpoint 0 Data Count . . . . . . . . . . . 160

USB Register Definition 15.19. INMAX: USB0 IN Endpoint n Maximum Packet Size 160

USB Register Definition 15.20. EINCSRL: USB0 IN Endpoint Con trol Low Byte . . . . 163

USB Register Definition 15.21. EINCSRH: USB0 IN Endpoint Control High Byte . . . 164

USB Register Definition 15.22. OUTMAX: USB0 Out Endpoint Max Packet Size . . . 165

USB Register Definition 15.23. EOUTCSRL: USB0 OUT Endpoint Control High Byte 166

USB Register Definition 15.24. EOUTCSRH: USB0 OUT Endpoint Control Low Byte 167

USB Register Definition 15.25. EOUTCNTL: USB0 OUT Endpoint Count Low . . . . .167

USB Register Definition 15.26. EOUTCNTH: USB0 OUT Endpoint Count High . . . . 167

SFR Definition 16.1. SMB0CF: SMBus Clock/Configuration . . . . . . . . . . . . . . . . . . . 175

SFR Definition 16.2. SMB0CN: SMBus Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

Rev. 1.2 13

C8051F320/1

SFR Definition 16.3. SMB0DAT: SMBus Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .179

SFR Definition 17.1. SCON0: Serial Port 0 Control . . . . . . . . . . . . . . . . . . . . . . . . . . 192

SFR Definition 17.2. SBUF0: Serial (UART0) Port Data Buffer . . . . . . . . . . . . . . . . . 193

SFR Definition 18.1. SPI0CFG: SPI0 Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . 203

SFR Definition 18.2. SPI0CN: SPI0 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

SFR Definition 18.3. SPI0CKR: SPI0 Clock Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

SFR Definition 18.4. SPI0DAT: SPI0 Data Register . . . . . . . . . . . . . . . . . . . . . . . . . . 205

SFR Definition 19.1. TCON: Timer Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

SFR Definition 19.2. TMOD: Timer Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .214

SFR Definition 19.3. CKCON: Clock Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

SFR Definition 19.4. TL0: Timer 0 Low Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

SFR Definition 19.5. TL1: Timer 1 Low Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

SFR Definition 19.6. TH0: Timer 0 High Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

SFR Definition 19.7. TH1: Timer 1 High Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

SFR Definition 19.8. TMR2CN: Timer 2 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

SFR Definition 19.9. TMR2RLL: Timer 2 Reload Register Low Byte . . . . . . . . . . . . . 221

SFR Definition 19.10. TMR2 RLH: Timer 2 Reload Register High Byte . . . . . . . . . . . 221

SFR Definition 19.11. TMR2L: Timer 2 Low Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

SFR Definition 19.12. TMR2H Timer 2 High Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

SFR Definition 19.13. TMR3CN: Timer 3 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

SFR Definition 19.14. TMR3RLL: Timer 3 Reload Register Low Byte . . . . . . . . . . . . 226

SFR Definition 19.15. TMR3 RLH: Timer 3 Reload Register High Byte . . . . . . . . . . . 226

SFR Definition 19.16. TMR3L: Timer 3 Low Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

SFR Definition 19.17. TMR3H Timer 3 High Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

SFR Definition 20.1. PCA0CN: PCA Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240

SFR Definition 20.2. PCA0MD: PCA Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 241

SFR Definition 20.3. PCA0CPMn: PCA Capture/Compare Mode . . . . . . . . . . . . . . . 242

SFR Definition 20.4. PCA0L: PCA Counter/Timer Low Byte . . . . . . . . . . . . . . . . . . . 243

SFR Definition 20.5. PCA0H: PCA Counter/Timer High Byte . . . . . . . . . . . . . . . . . . 243

SFR Definition 20.6. PCA0CPLn: PCA Capture Module Low Byte . . . . . . . . . . . . . . . 243

SFR Definition 20.7. PCA0CPHn: PCA Capture Module High Byte . . . . . . . . . . . . . . 244

C2 Register Definition 21.1. C2ADD: C2 Address . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

C2 Register Definition 21.2. C2 Device ID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

C2 Register Definition 21.3. REVID: C2 Revision ID . . . . . . . . . . . . . . . . . . . . . . . . . 246

C2 Register Definition 21.4. FPCTL: C2 Flash Programming Control . . . . . . . . . . . . 246

C2 Register Definition 21.5. FPDAT: C2 Flash Programming Data . . . . . . . . . . . . . . 246

14 Rev. 1.2

C8051F320/1

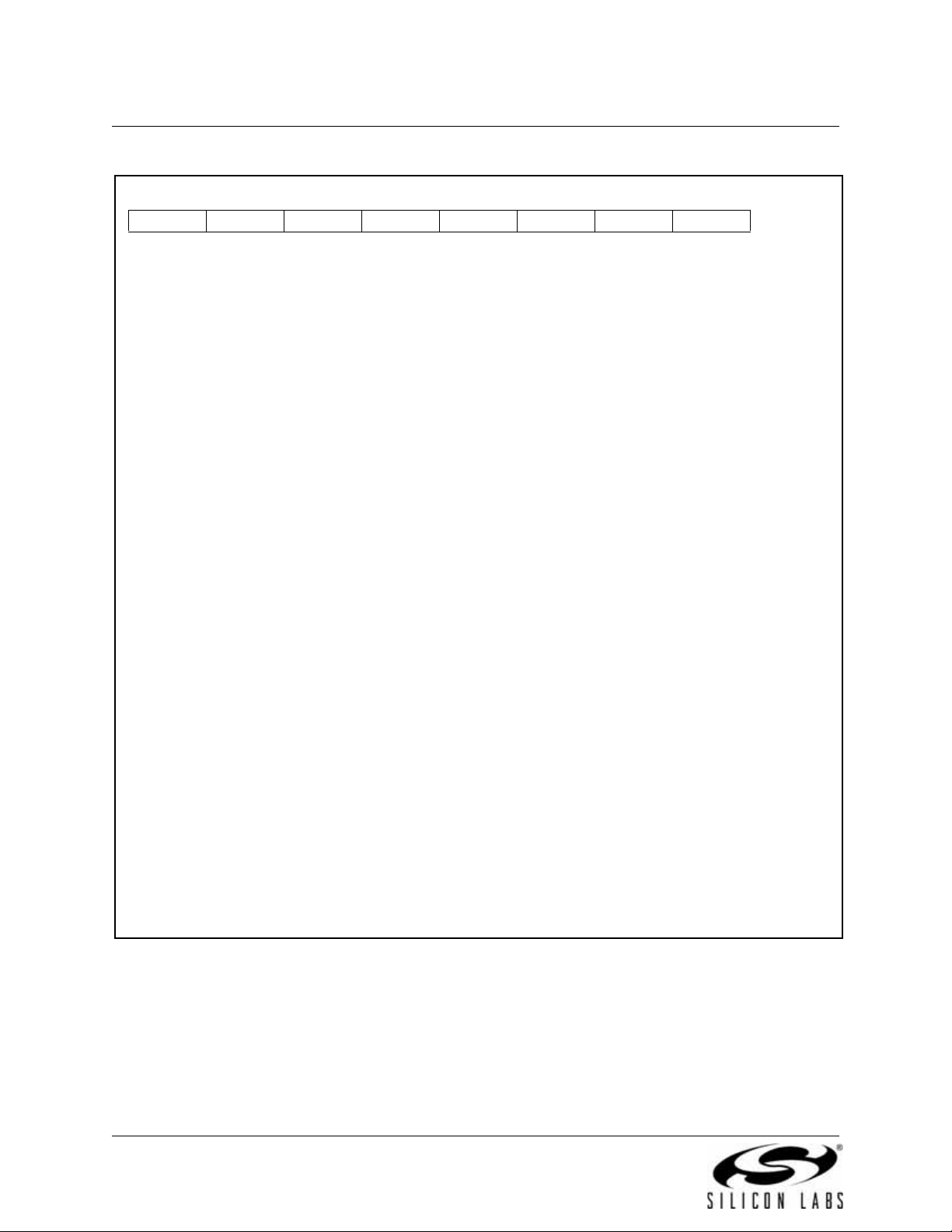

1. System Overview

C8051F320/1 devices a r e fu ll y int egrate d m ix ed-s ig nal S ystem - on-a- Chip MCUs. Highlighted fe atu res ar e

listed below. Refer to

• High-speed pipelined 8051-compatible microcontroller core (up to 25 MIPS)

• In-system, full-speed, non-intrusive debug interface (on-chip)

• Universal Serial Bus (USB) Function Controller with eight flexible endpoint pipes, integrated transceiver, and 1 k FIFO RAM

• Supply Voltage Regulator (5-to-3 V)

• True 10-bit 200 ksps 17-channel single-ended/differential ADC with analog multiplexer

• On-chip Voltage Reference and Temperature Sensor

• On-chip Voltage Comparators (2)

• Precision programmable 12 MHz internal oscillator and 4x clock multiplier

• 16 kB of on-chip Flash memory

• 2304 total bytes of on-chip RAM (256 + 1k + 1 k USB FIFO)

•SMBus/I2C, Enhanced UART, and Enhanced SPI serial interfaces implemented in hardware

• Four general-purpose 16-bit timers

• Programmable Counter/Timer Array (PCA) with five capture/compare modules and Watchdog Timer

function

• On-chip Power-On Reset, VDD Monitor, and Missing Clock Detector

• 25/21 Port I/O (5 V tolerant)

With on-chip Power-On Reset, VDD monitor, Voltage Regulator, Watchdog Timer, and clock oscillator,

C8051F320/1 devices ar e truly stand-alo ne Sy s tem -on- a- Chip sol uti ons. T he Flas h mem ory can be repr o

grammed in-circuit, prov iding non -volatile data stor age, and also al lowing fiel d upgrades of the 8051 firmware. User software has c omplete control of all peripherals, and may individually shut down an y or all

peripherals for power savings.

Table 1.1 for specific product feature selection.

-

The on-chip Silicon Labs 2-Wire (C2) Development Interface allows non-intrusive (uses no on-chip

resources), full speed, in-circuit debugging using the production MCU installed in the final application. This

debug logic supports inspection and modification of memory and registers, setting breakpoints, single

stepping, run and halt commands. All a nalog and digital peripheral s are fully function al while debugging

using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging with

out occupying package pins.

Each device i s specifi ed for 2.7- to-3.6 V ope ration ove r the industr ial temper ature range (–4 0 to +85 °C).

(Note that 3.0-to-3.6

input signals up to 5

V is required for USB commu nication.) The Port I/O and /RST pins are tolerant of

V. C8051F320/1 are available in a 32-pin LQFP or a 28-pin QFN package.

-

Rev. 1.2 15

C8051F320/1

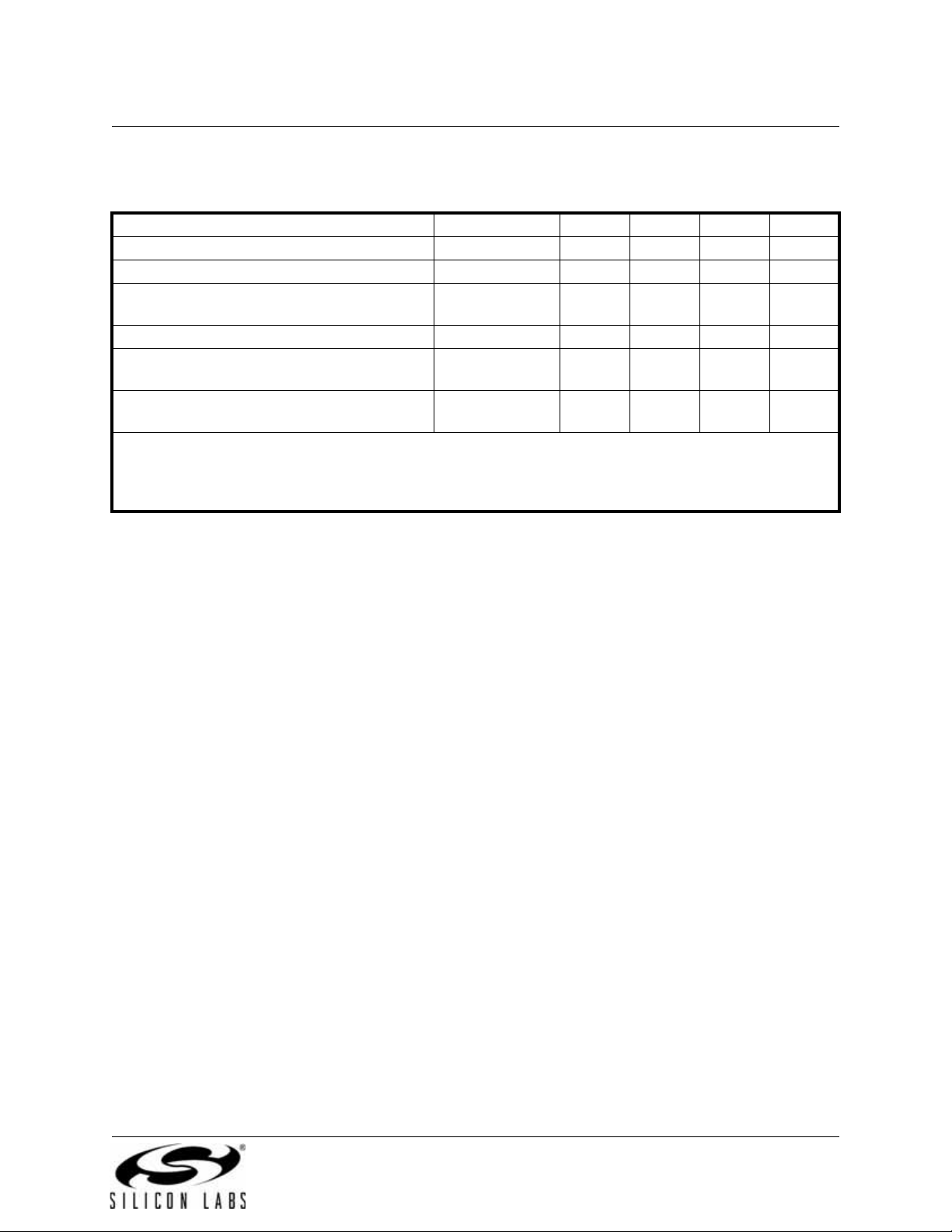

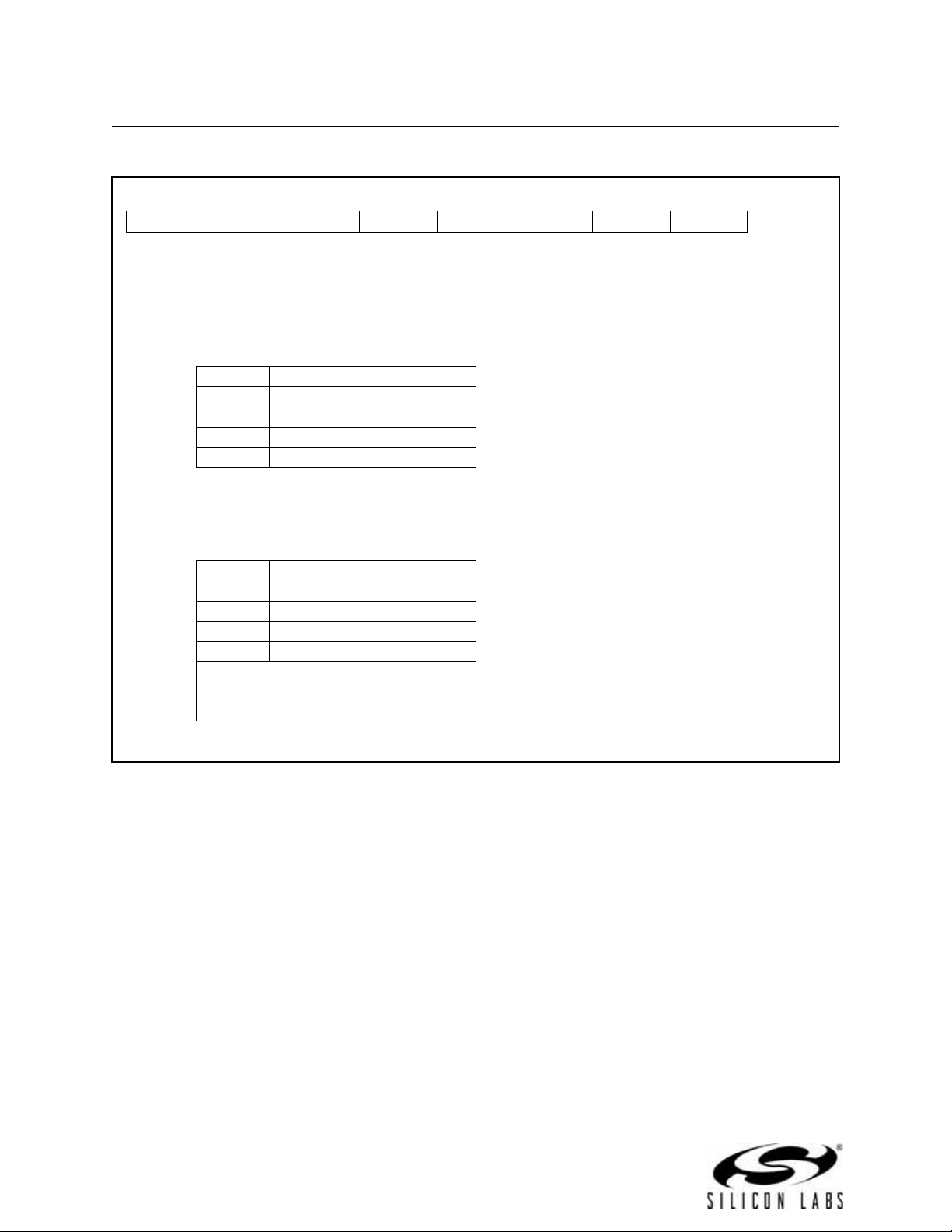

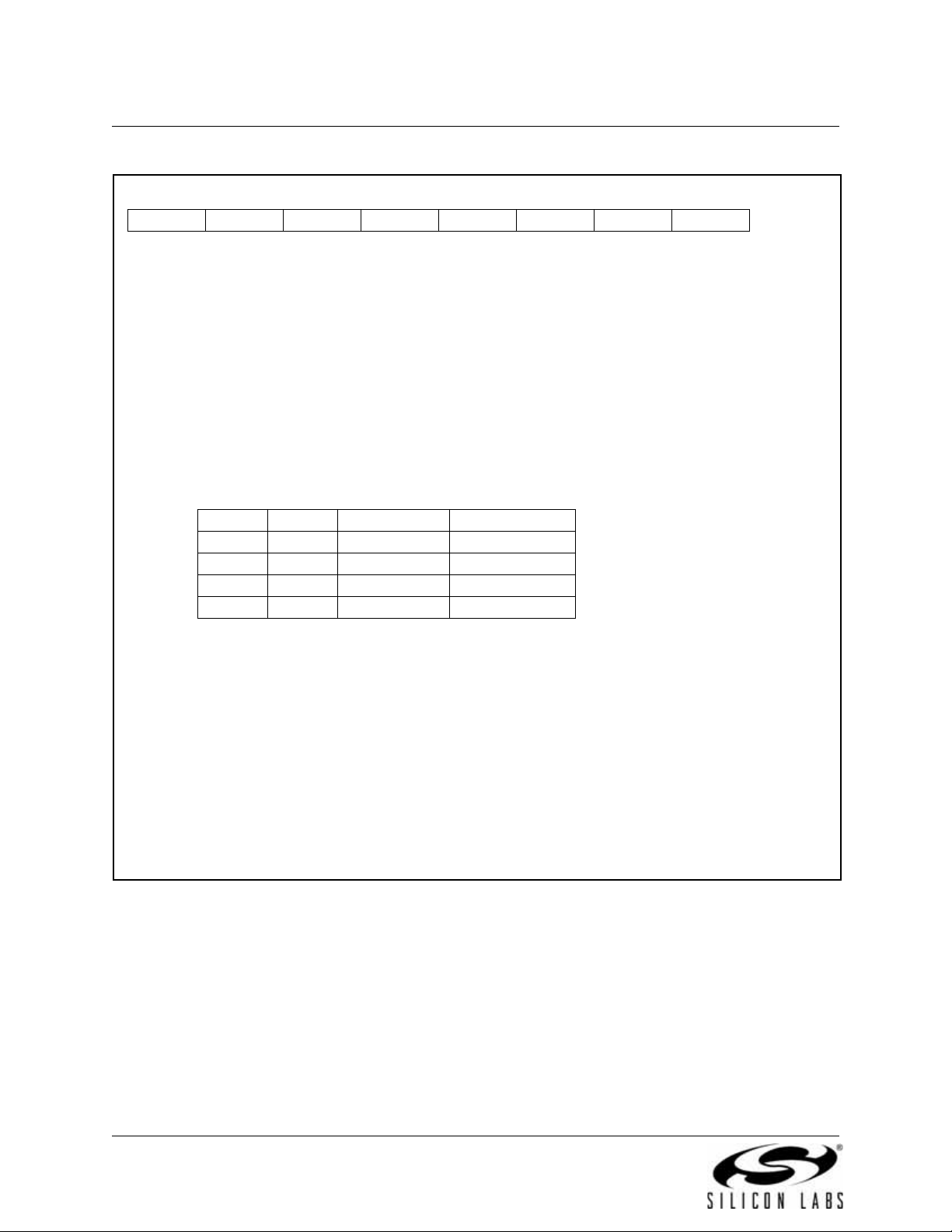

Table 1.1. Product Selection Guide

C

2

MIPS (Peak)

Flash Memory

C8051F320-GQ 25 16 k 2304 999999 4 9 25 999 2LQFP-32

C8051F321-GM 25 16 k 2304 999999 4 9 21 999 2QFN-28

RAM

Calibrated Internal Oscillator

USB

Supply Voltage Regulator

SMBus/I

Enhanced SPI

UART

Timers (16-bit)

Programmable Counter Array

Digital Port I/Os

10-bit 200ksps ADC

Temperature Sensor

Voltage Reference

Analog Comparators

Package

REGIN

VDD

GND

/RST/C2CK

VBUS

D+

D-

Analog/Digital

C2D

XTAL1 XTAL2

External

Oscillator

Circuit

12MHz

Internal

Oscillator

Clock

Recovery

5.0V

Power

IN

Regulator

POR

Voltage

OUT

Debug HW

Brown-

Out

x4 2

2

1,2,3,4

USB

Transceiver

Enable

USB Clock

Controller

1K byte USB

System

Clock

USB

SRAM

Reset

8

0

5

1

C

o

r

SFR Bus

e

16kbyte

FLASH

256 byte

SRAM

1K byte

XRAM

VREF

VDD

Port 0

Latch

Port 1

Latch

UART

Timer

0,1,2,3 /

RTC

PCA/

WDT

SMBus

SPI

Port 2

Latch

Port 3

Latch

VREF

10-bit

200ksps

ADC

P

0

D

r

v

C

P

R

1

O

S

D

S

r

B

v

A

R

P

2

D

r

v

P

3

D

r

v

CP0

+

-

CP1

+

-

Temp

A

AIN0-AIN16

M

VDD

U

X

VREF

P0.0

P0.1

P0.2/XTAL1

P0.3/XTAL2

P0.4

P0.5

P0.6/CNVSTR

P0.7/VREF

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

P2.0

P2.1

P2.2

P2.3

P2.4

P2.5

P2.6

P2.7

P3.0/C2D

Figure 1.1. C8051F320 Block Diagram

16 Rev. 1.2

C8051F320/1

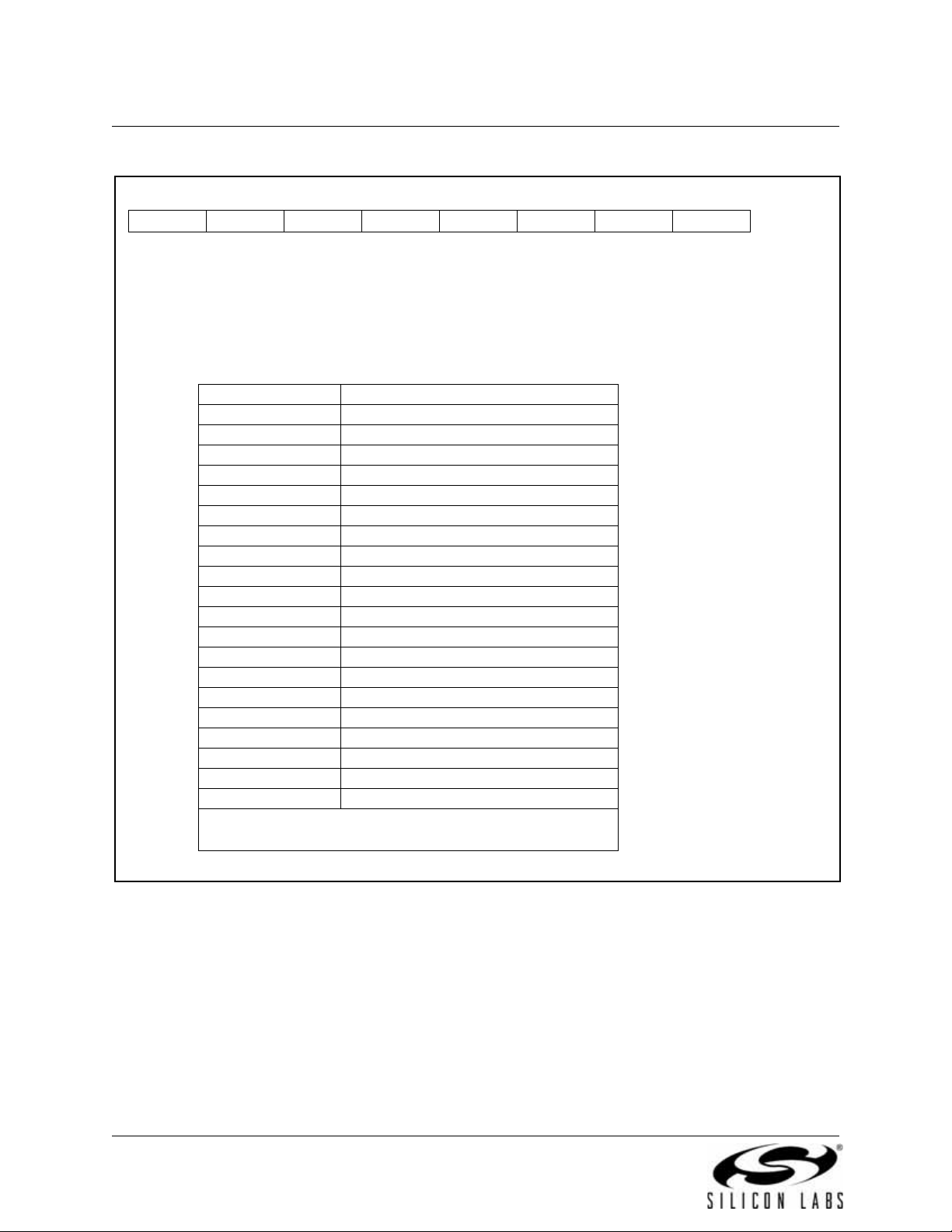

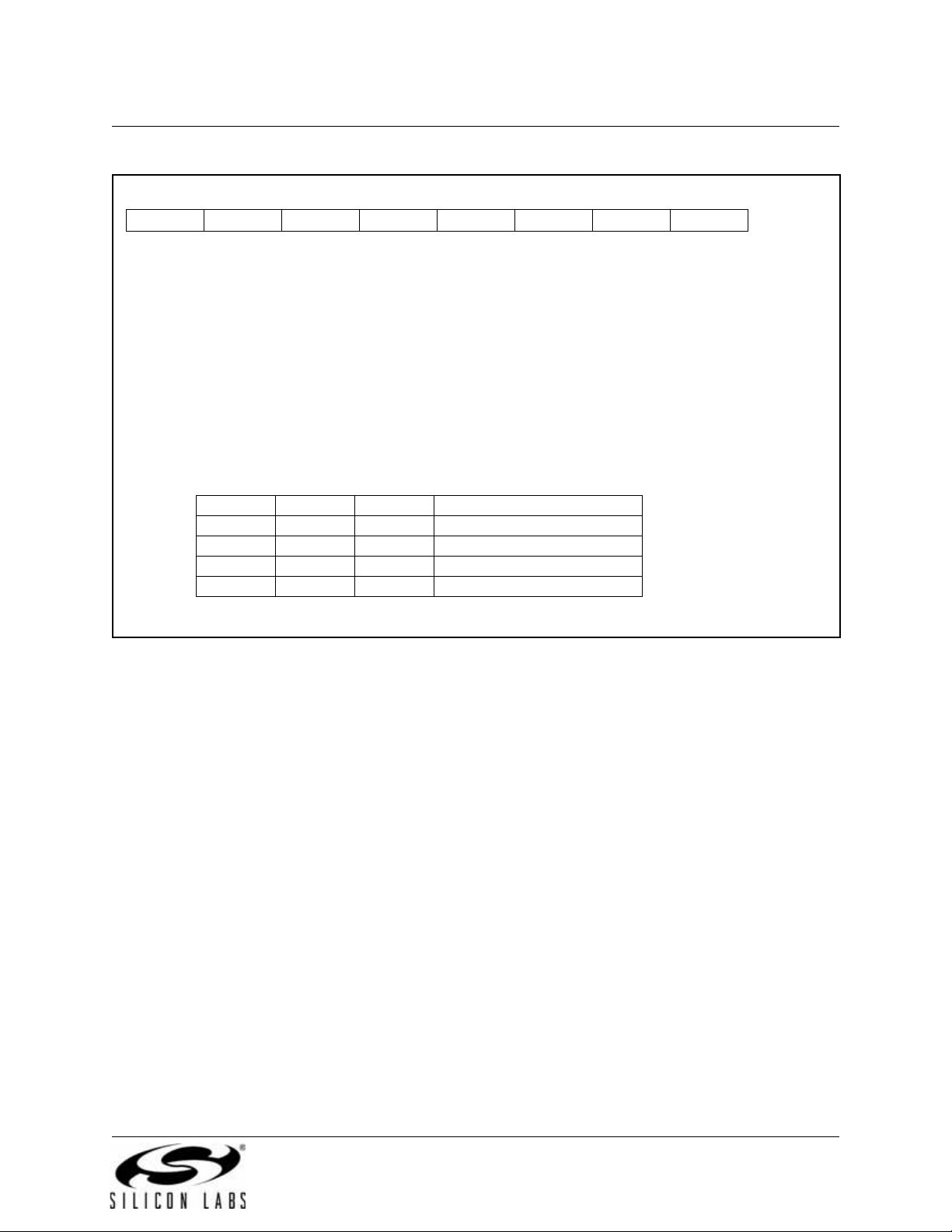

REGIN

VDD

GND

/RST/C2CK

VBUS

D+

D-

Analog/Digital

C2D

XTAL1 XTAL2

External

Oscillator

Circuit

12MHz

Internal

Oscillator

Clock

Recovery

5.0V

Power

IN

Regulator

POR

Voltage

OUT

Debug HW

Brown-

Out

x4 2

2

1,2,3,4

USB

Transceiver

Enable

USB Clock

Controller

1K byte USB

System

USB

SRAM

Reset

Clock

8

0

5

1

C

o

SFR Bus

r

e

16kbyte

FLASH

256 byte

SRAM

1K byte

XRAM

VREF

VDD

Port 0

Latch

Port 1

Latch

UART

Timer

0,1,2,3 /

RTC

PCA/

WDT

SMBus

SPI

Port 2

Latch

Port 3

Latch

VREF

10-bit

200ksps

ADC

P

0

D

r

v

C

P

R

1

O

S

D

S

r

B

v

A

R

P

2

D

r

v

P

3

D

r

v

CP0

+

-

CP1

+

-

Temp

A

AIN0-AIN11

M

VDD

U

X

VREF

P0.0

P0.1

P0.2/XTAL1

P0.3/XTAL2

P0.4

P0.5

P0.6/CNVSTR

P0.7/VREF

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

P2.0

P2.1

P2.2

P2.3

P3.0/C2D

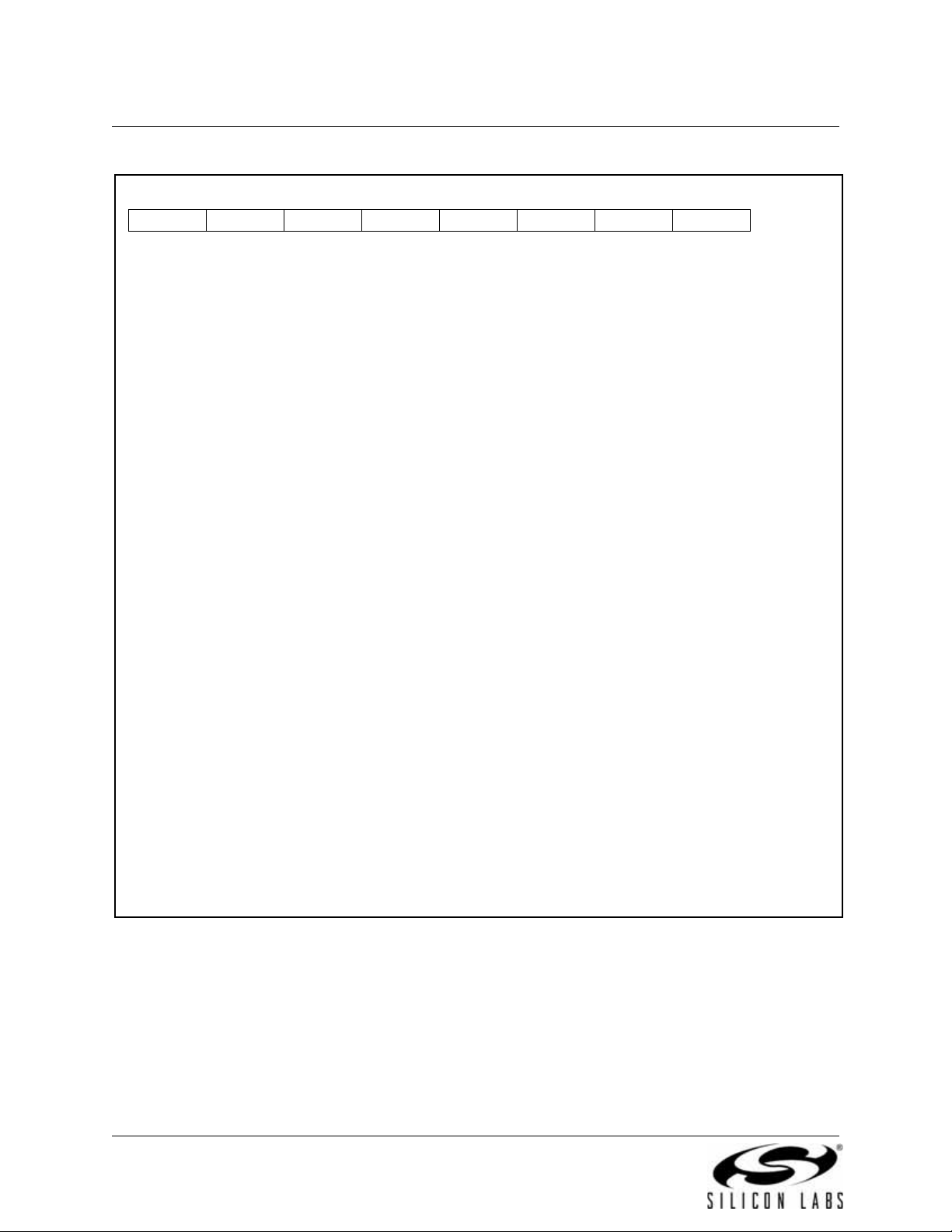

Figure 1.2. C8051F321 Block Diagram

Rev. 1.2 17

C8051F320/1

1.1. CIP-51™ Microcontroller Core

1.1.1. Fully 8051 Compatible

The C8051F320/1 fami ly utilize s Silico n Labs' pr oprietary CIP-5 1 microcontr oller cor e. The CIP-51 is fully

compatible with the MCS-51™ instruction set; standard 803x/805x assemblers and compilers can be used

to develop software. The CIP-51 core offers all the perip herals included with a standard 8052, including

four 16-bit counter/time rs, a full-duplex UART with extended b aud rate configuration, an enha nced SPI

port, 2304

pins.

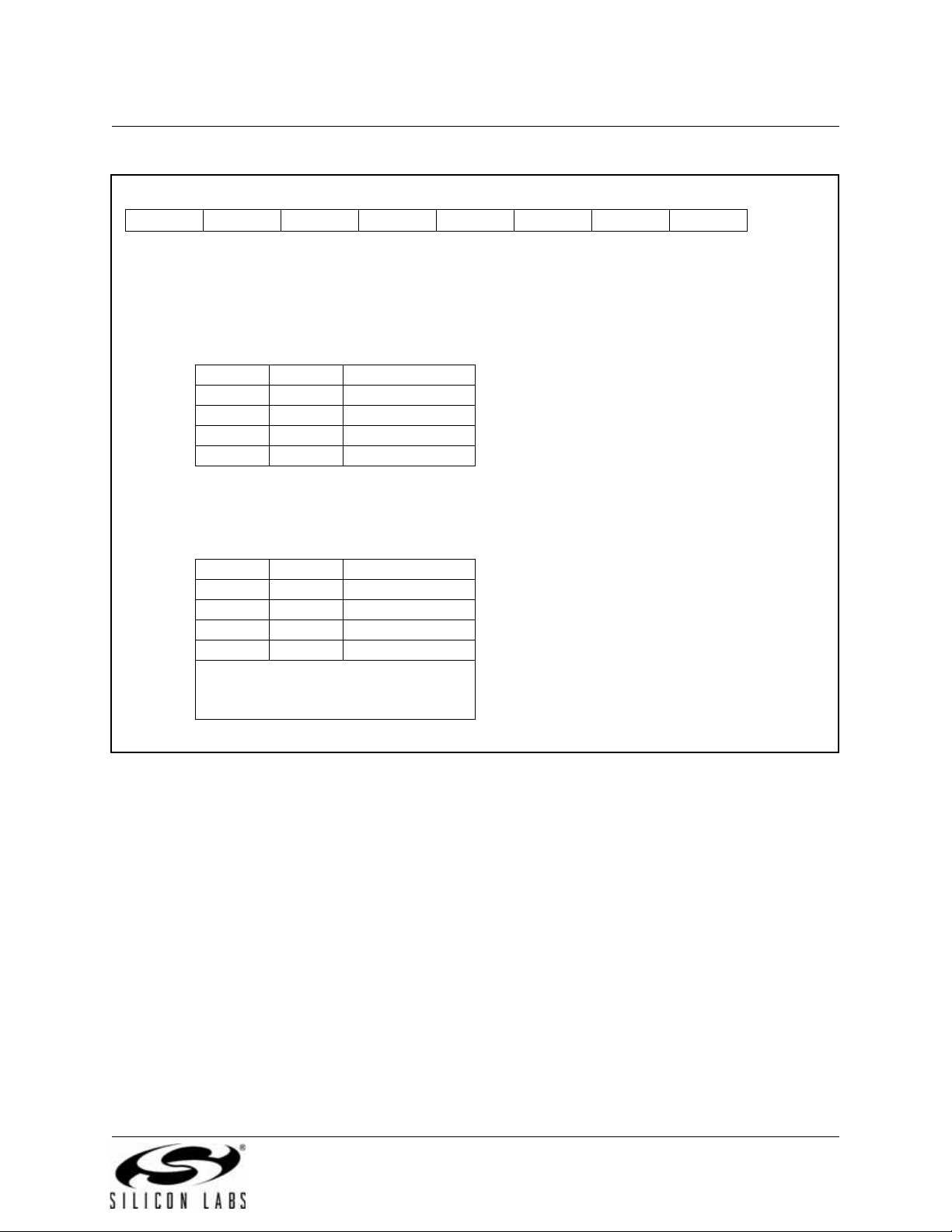

1.1.2. Improved Throughput

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all ins truction s except for MU L and DIV take 12 or 24 syste m

clock cycles to execute wi th a maxi mum sys tem clo ck of 12-t o-24

cutes 70% of its instructions in one or two system clock cycles, with only four instructions taking more than

four system clock cycles.

The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that

require each execution time.

Number of Instructions 26 50 5 14 7 3 1 2 1

bytes of on-chip RAM, 128 by te Special Function Reg is ter ( SFR) ad dr ess s pace, a nd 2 5/2 1 I/O

MHz. By contrast, the CIP- 51 core exe-

Clocks to Execute 1 2 2/3 3 3/4 4 4/5 5 8

1.1.3. Additional Features

The C8051F320/1 SoC family in cludes several key enha ncements to the CIP-51 core and peripher als to

improve performance and ease of use in end applications.

The extended interrupt handler provides 16 interrupt sources into the CIP-51 (as opposed to 7 for the standard 8051), allowing numerous analog and digital peripherals to interrupt the controller. An interrupt driven

system requires less intervention by the MCU, giving it more effective throughput. The extra interrupt

sources are very useful when building multi-tasking, real-time systems.

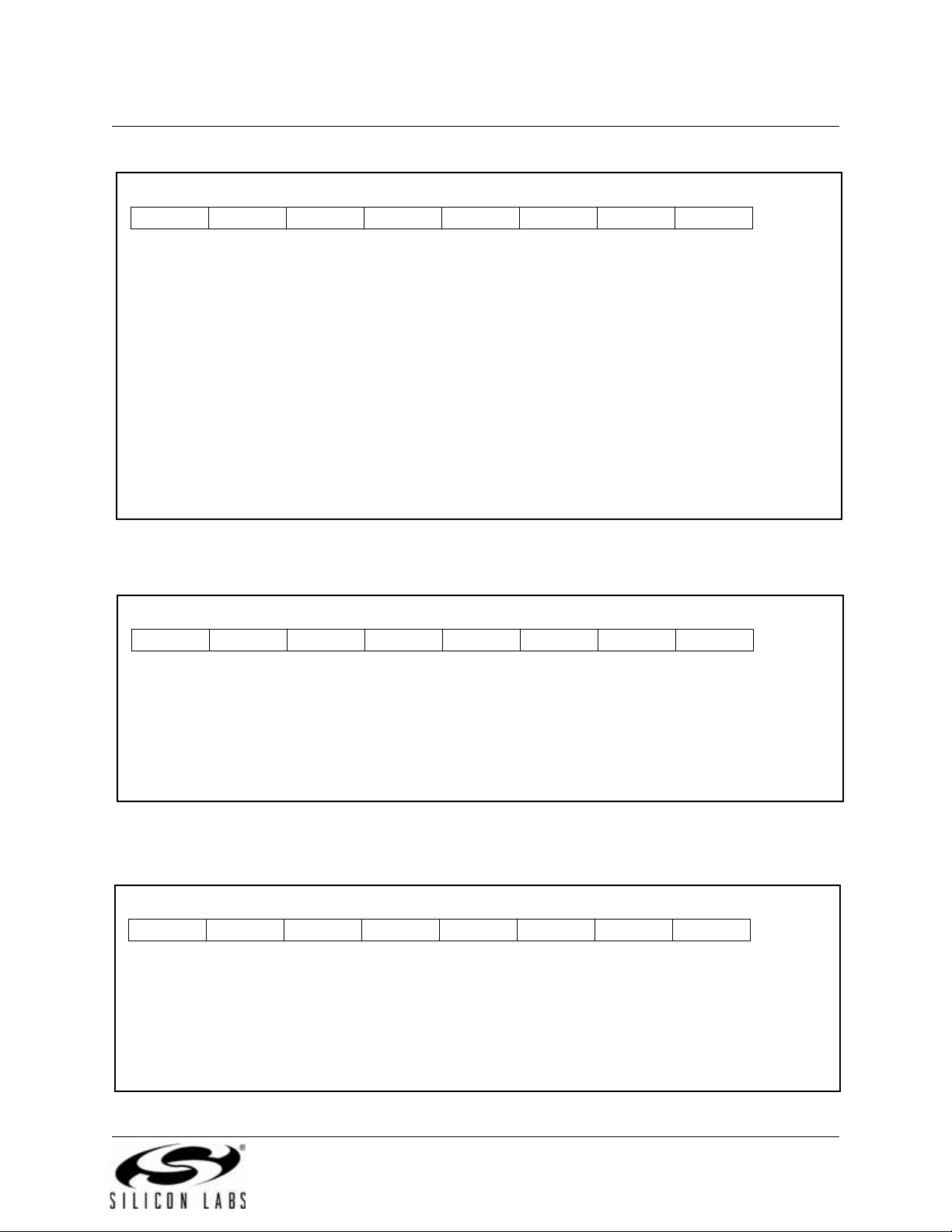

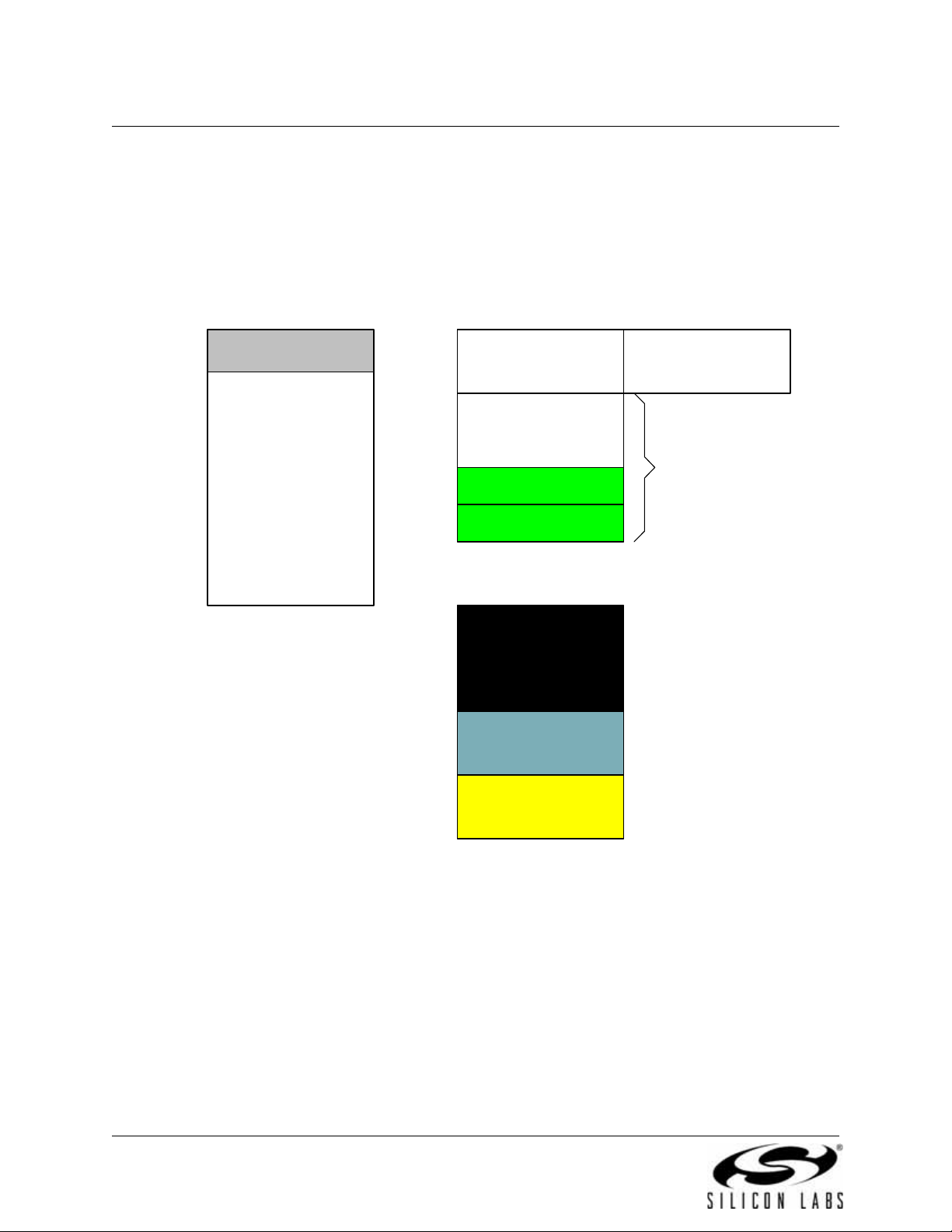

Nine reset sources are av ailable: power-on reset circuitry (PO R), an on-chip VDD monitor (forces rese t

when power supply vo ltage drops below V

(USB bus reset or a VB US tr an si tio n), a Watchdog Timer, a Missing Clock Detec tor, a voltage leve l d ete ction from Comparator0, a forc ed software reset, an extern al reset pi n, and an err ant Flash read /write protection circuit. Each reset source except for the POR, Reset Inpu t Pin, or Flash error ma y be disabled by

the user in software. The W DT may be permanently enabled in softw are after a power-on reset during

MCU initialization.

The internal oscillator is factory calibrated to 12 MHz ±1.5%, and the internal oscillator period may be user

programmed in ~0.2 5% incremen ts. A clock r ecovery mechani sm allo ws the int ernal osc illator to b e used

with the 4x Clock Multiplier as the USB clock source in Full Speed mode; the internal oscillator can also be

used as the USB clock source in Low Speed mode. External oscillators may also be used with the 4x Clock

Multiplier. An external oscillato r driv e circ uit is also incl uded, a llowin g an ex terna l crys tal, cer amic reso na

tor, capacitor, RC, or CMOS clock source to generate the system clock. The system clock may be configured to use the internal oscill ator, external oscillator, or the Clock Multip lier ou tput divid ed by 2. If desir ed,

the system clock s our ce may be switched on-the-fly between os c illato r sour c es. A n ex te rn al osci ll ato r ca n

be extremely useful in low power appl ications , allowi ng the MCU to run from a slow (pow er saving ) exter

nal clock source, while periodically switching to the internal oscillator as needed.

as given in Table 10.1 on page 104), the USB controller

RST

-

-

18 Rev. 1.2

XTAL1

XTAL2

Internal

Oscillator

Clock

Multiplier

External

Oscillator

Drive

Px.x

Px.x

System

Clock

Clock Select

Comparator 0

+

-

Missing

Clock

Detector

(one-

shot)

EN

MCD

Enable

Microcontroller

Extended Interrupt

VDD

C0RSEF

CIP-51

Core

Handler

PCA

WDT

EN

WDT

Enable

Supply

Monitor

+

-

System Reset

Enable

Power On

Reset

Software Reset (SWRSF)

Errant

FLASH

Operation

C8051F320/1

'0'

(wired-OR)

Reset

Funnel

Enable

USB

Controller

VBUS

Transition

/RST

Figure 1.3. On-Chip Clock and Reset

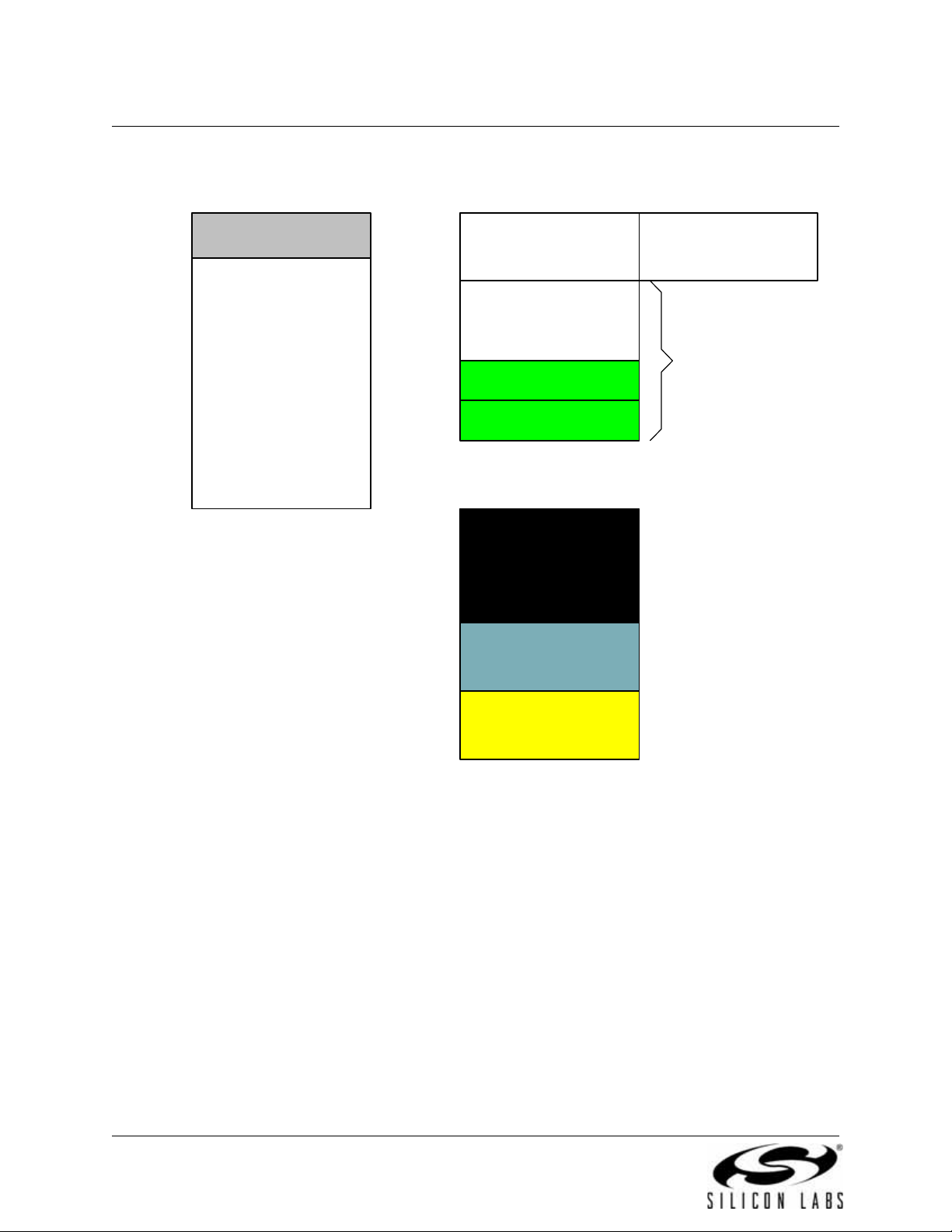

1.2. On-Chip Memory

The CIP-51 has a standa rd 8051 program and data addr ess configuration. It inc ludes 256 bytes of data

RAM, with the upper 128 bytes dual-mapped. Indirect addressing accesses the upper 128 bytes of general

purpose RAM, and direct add ressing acce sses the 128 byte SF R address space. The lower 128 bytes of

RAM are accessible via direct and indirect addressing. The first 32 bytes are addressable as four banks of

general purpose registers, and the next 16 bytes can be byte addressable or bit addressable.

Program memory consists of 16 kB of Flash. This m emory may be r eprogrammed in-s ystem in 512 byte

sectors, and requir es no speci al off-chip progr amming vol tage. See

ory map.

Figure 1.4 for the MCU syst em mem-

Rev. 1.2 19

C8051F320/1

t

0

PROGRAM/DATA MEMORY

(Flash)

0x3E00

x3DFF

RESERVED

16 K Flash

(In-System

Programm ab le in 512

Byte Sectors)

0xFF

0x80

0x7F

0x30

0x2F

0x20

0x1F

0x00

INTERNAL DATA ADDRESS SPACE

Upper 128 RAM

(Indirect Addressing

(Direct and Indirect

Bit Addressable

General Purp os e

DATA MEMORY (RAM)

Only)

Addressing)

Registers

(Direct Addre ss ing Only)

Special Function

Register's

Lower 128 RAM

(Direct and Indirec

Addressing )

EXTERNAL DATA ADDRESS SPACE

0x0000

0xFFFF

Same 2048 bytes as from

0x0000 to 0x07FF, wrapped

on 2 kB boundaries

0x0800

0x07FF

USB FIFOs

0x0400

0x03FF

0x0000

1024 Bytes

XRAM - 1024 Bytes

(accessable using MOVX

instruction)

Figure 1.4. On-Board Memory Map

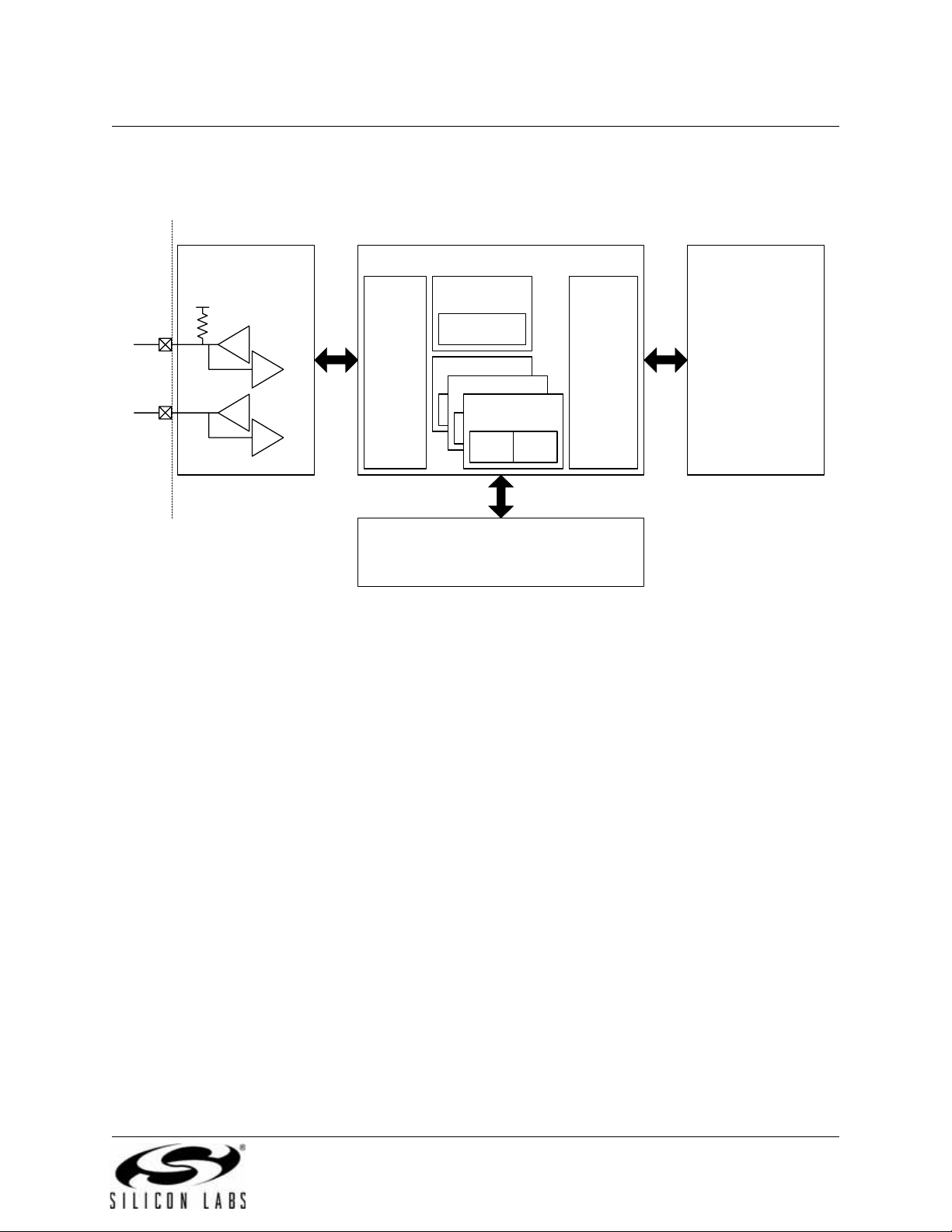

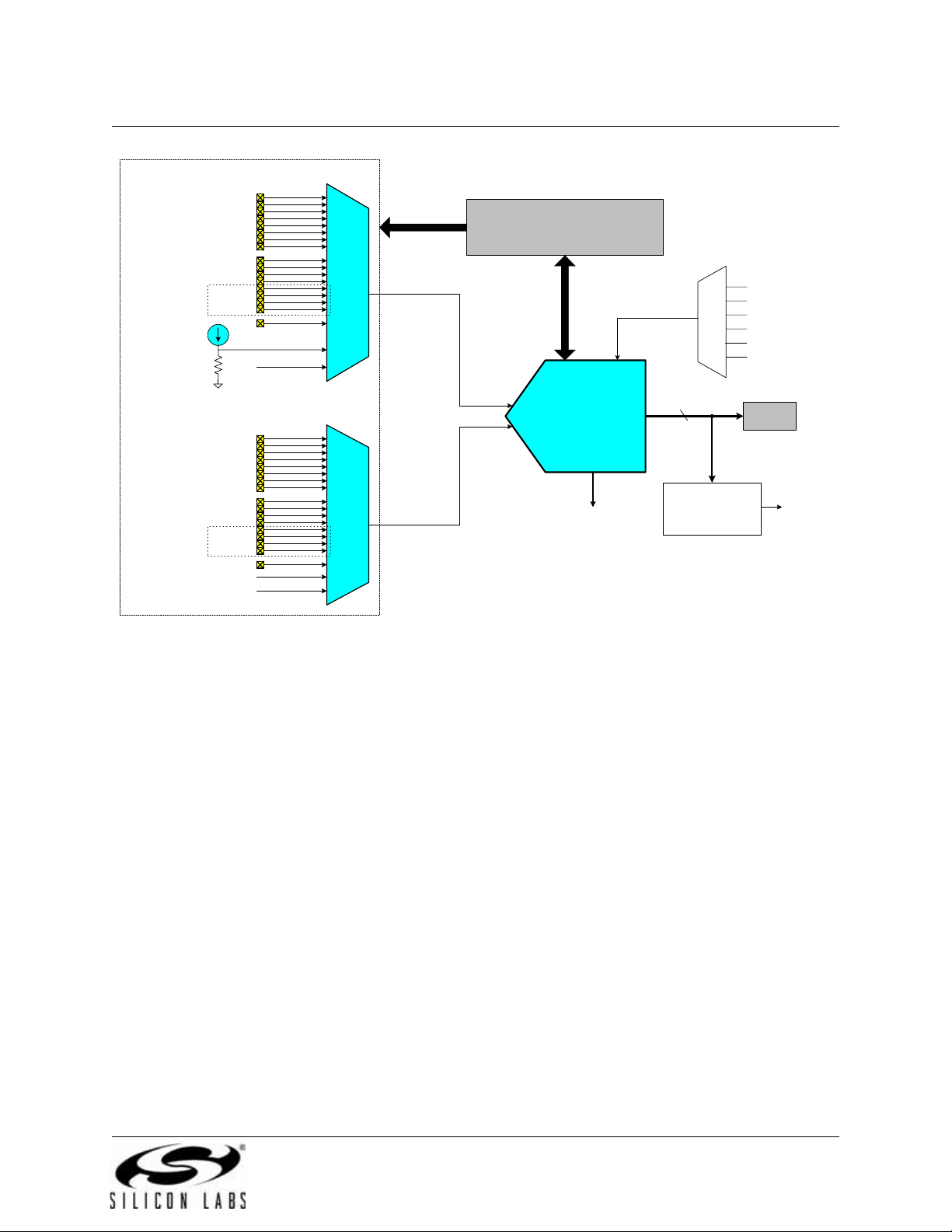

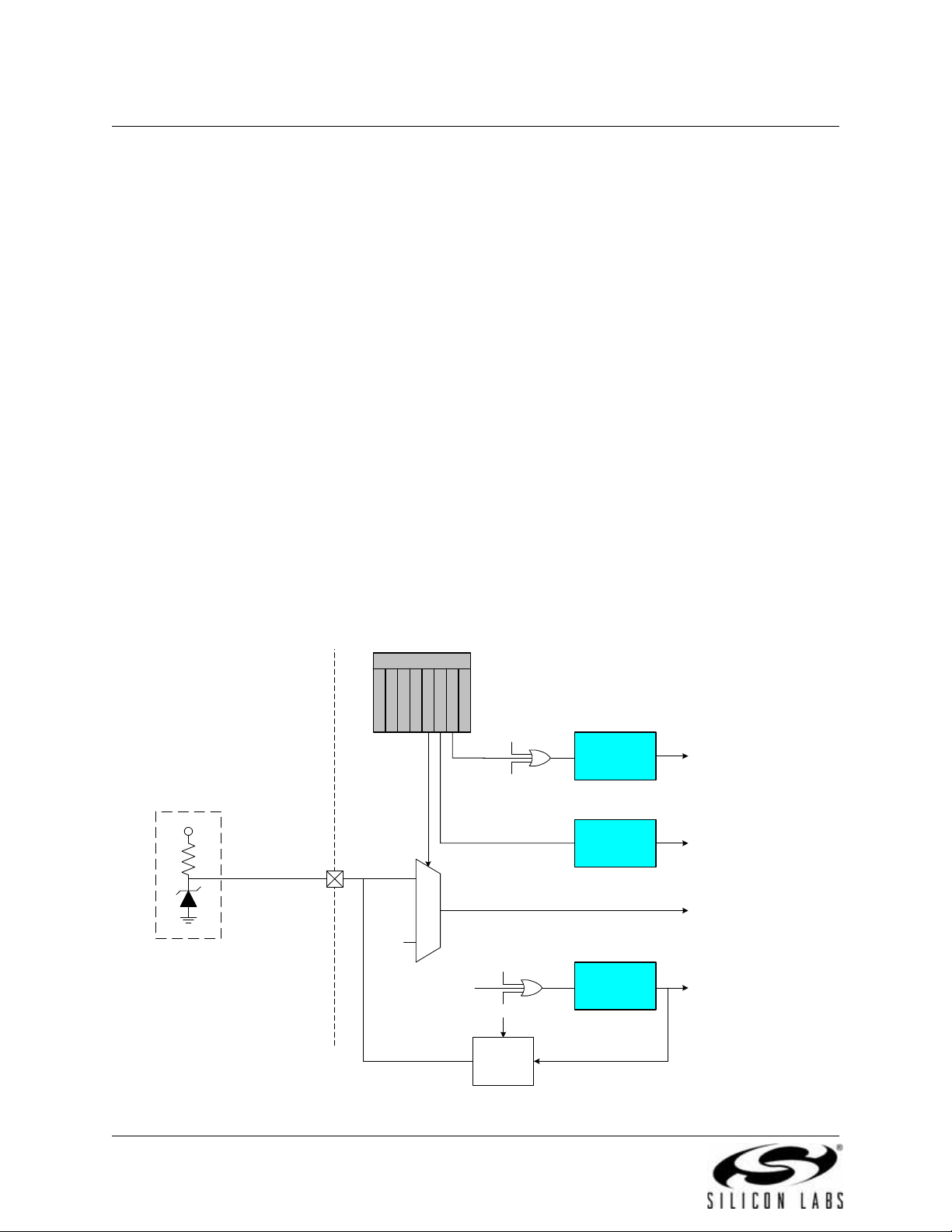

1.3. Universal Serial Bus Controller

The Universal Ser ial Bus Co ntroller (USB 0) is a US B 2.0 co mpliant Full or Low Speed function with integrated transceiver and endpoint FIFO RAM. A total of eight en dpoint pipes are available: a bi -directional

control endpoint (Endpoint0) and three pairs of IN/OUT endpoints (Endpoints1-3 IN/OUT).

A 1 k block of XRAM is used as dedicated USB FIFO space. This FIFO space is distributed among

Endpoints0–3; Endpoint1–3 FIFO slots can be c onfigured as IN, OUT, or both IN and OUT (split mode).

The maximum FIFO size is 512 bytes (Endpoint3).

USB0 can be operated as a Full or Low Speed function. On-chip 4x Clock Multiplier and clock recovery circuitry allow both Full and Low Speed options to be implemented with the on-chip precision oscillator as the

USB clock source. An ex ternal oscill ator sourc e can also be used with the 4x Cl ock Multi plier to generat e

the USB clock. The CPU clock source is independent of the USB clock.

20 Rev. 1.2

C8051F320/1

The USB Transceiver is USB 2.0 compliant, and includes on-chip matching and pull-up resistors. The pullup resistors can be enabled/disabled in software, and will appear on the D+ or D– pin according to the soft

ware-selected speed setting (Full or Low Speed).

Transceiver Serial Interface Engine (SIE)

-

VDD

D+

Data

Transfer

Control

D-

Endpoint0

IN/OUT

Endpoint1

Endpoint2

Endpoint3

IN OUT

IN OUT

IN OUT

USB FIFOs

(1k RAM)

USB

Control,

Status, and

Interrupt

Registers

CIP-51 Core

Figure 1.5. USB Controller Block Diagram

1.4. Voltage Regulator

C8051F320/1 devices include a 5-to-3 V voltage regulator (REG0). When enabled, the REG0 output

appears on the VDD pin and can be us ed to power external devices. REG 0 can be enabled/disabled by

software.

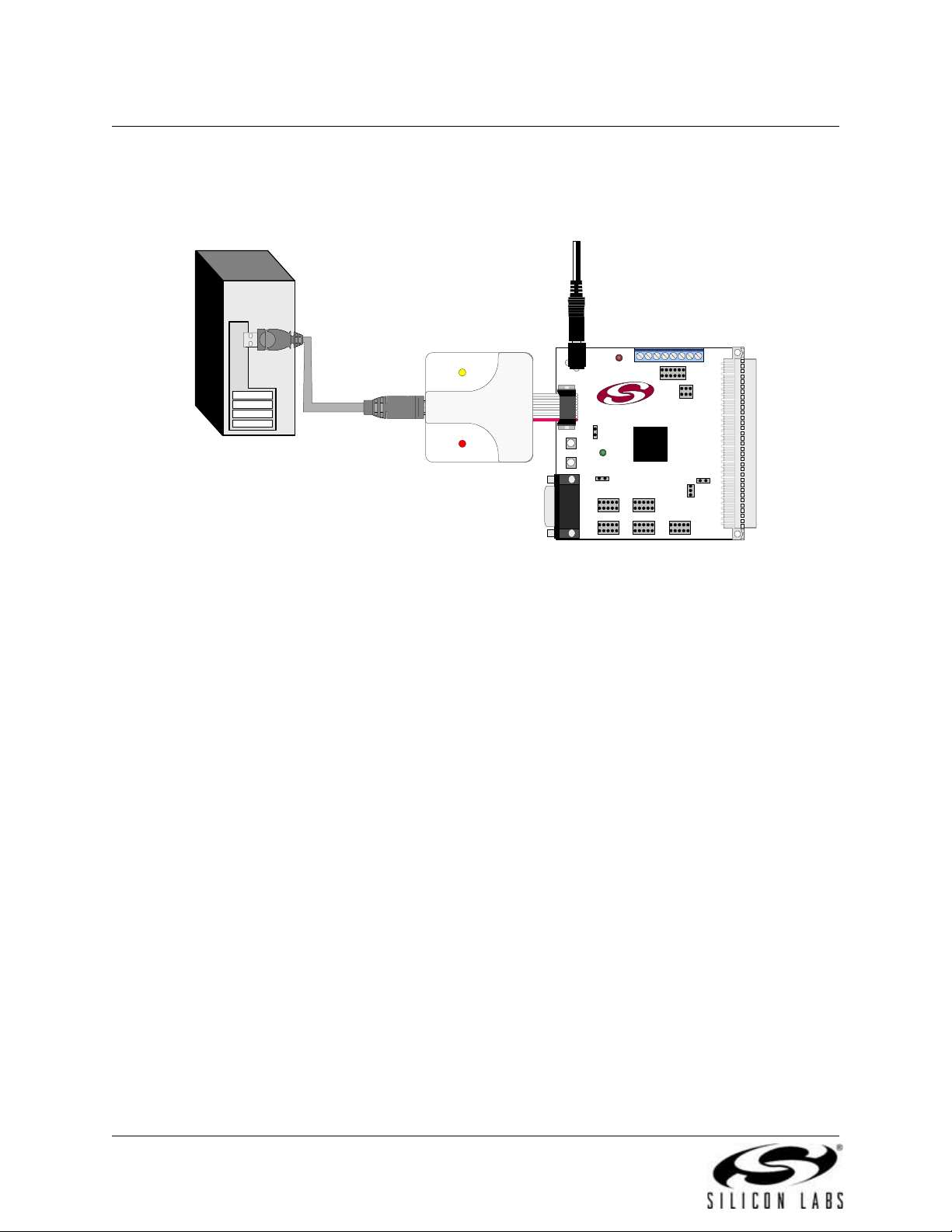

1.5. On-Chip Debug Circuitry

The C8051F320/1 devices include on-chip Silicon Labs 2-Wire (C2) debug circuitry that provides non-intrusive, full speed, in-circuit debugging of the production part installed in the end application.

Silicon Labs' debugging system supports inspection and modification of memory and registers, breakpoints, and single stepping. No additi onal target RAM , progra m memory, timers, or communication s channels are required. A ll th e digital and analog peri pher a ls ar e func ti ona l a nd work co rre ctl y whi le deb ugg ing .

All the peripherals (ex cep t for the US B, AD C, a nd S MBu s) are stall ed whe n the MCU is halted, during sin

gle stepping, or at a breakpoint in order to keep them synchronized.

The C8051F320DK development kit provides all the hardware and software necessary to develop application code and pe rform in- circuit debuggin g with the C8051F320/ 1 MCUs. T he kit in cludes software with a

developer's studio and debugger, 8051 assembler and linker, evaluation ‘C’ compiler, and a debug

adapter. It also has a target application board with the C8051F320 MCU installed, the necessary cables for

connection to a PC, and a wall-mount power supply. The development kit c ontents may also be used to

program and debug the de vi ce on the production PCB using the appro priat e c onn ec tio ns for th e pr og ram

ming pins.

The Silicon Labs IDE interf ace is a vas tly superio r developing and debuggi ng configur ation, compared t o

standard MCU emulators that use on-b oard "ICE Chips" and require the MCU in the application board t o

Rev. 1.2 21

-

-

C8051F320/1

be socketed. Silico n Labs' debug paradigm inc reases ease of use and p reserves the perfor mance of the

precision analog peripherals.

AC/DC

PC

Adapter

Target Board

PWR

SILICON LABORATORIES

MCU

P1.6

Port 2 Port 0

Port 4Port 3Port 1

USB

Cable

USB Debug Adapter

USB DEBUG ADAPTER

Silicon Laboratories

StopPower

Run

P3.7RESET

Figure 1.6. Development/In-System Debug Diagram

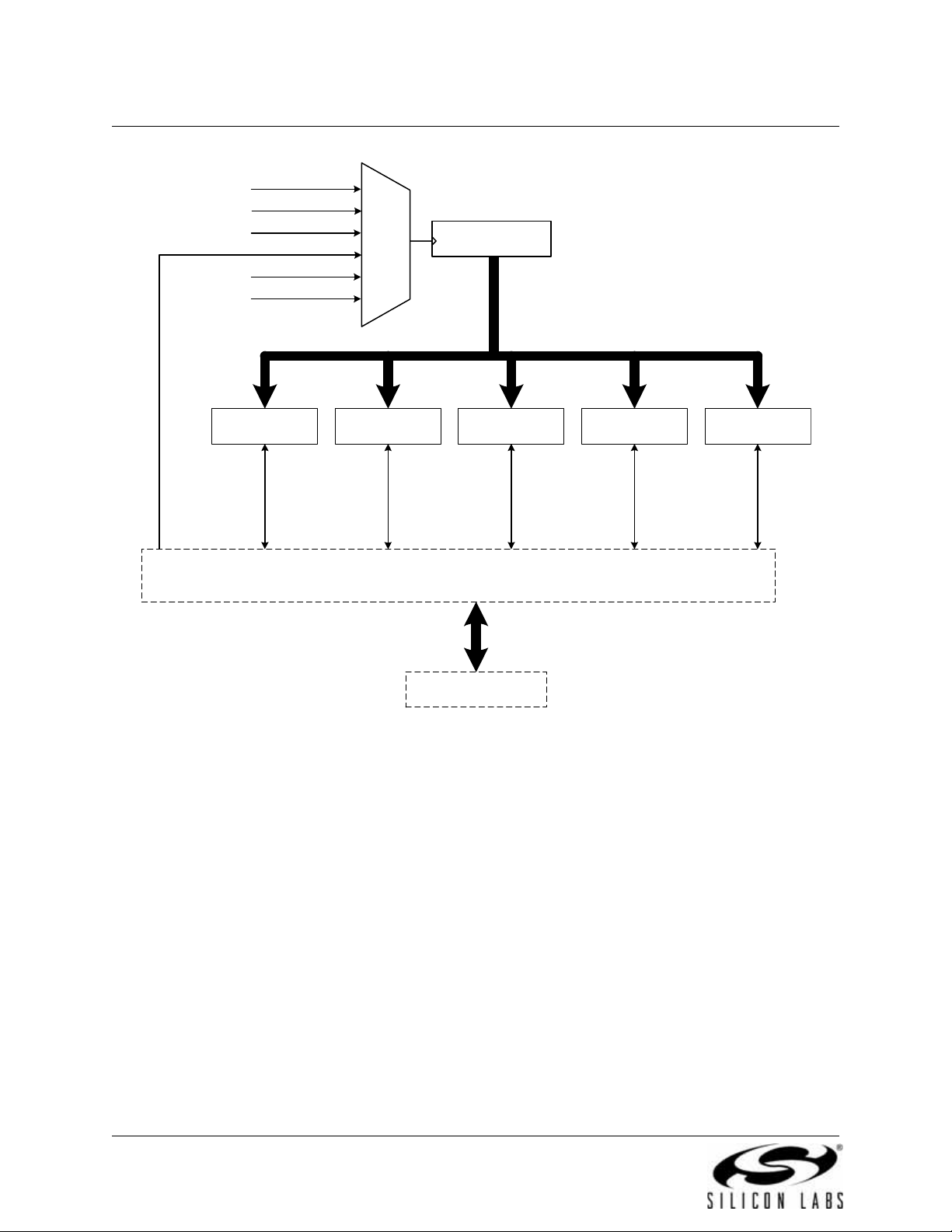

1.6. Programmable Digital I/O and Crossbar

C8051F320 devices include 25 I/O pins (three byte-wide Ports and one 1-bit-wide Port); C8051F321

devices include 21 I/O pins (two byte-wide Ports, one 4-bit-wide Port, and one 1-bit-wide Port). The

C8051F320/1 Ports behave like typical 8051 Ports with a few enhancements. Each Port pin may be config

ured as an analog inp ut o r a di gital I/ O pin . Pi ns s ele ct ed a s d ig ital I/Os may a ddi tio nal ly be co nfi gured for

push-pull or open-dr a in outp ut. Th e “weak pull-ups” that are fix ed on ty pic al 80 51 dev ices m ay be globally

disabled, providing power savings capabilities.

The Digital Crossbar all ows m apping of internal digital sys tem r eso urces to Port I/O pins ( Se e Fig ur e 1.7).

On-chip counter/tim ers, serial buses, HW inter rupts, comparator outputs, and other d igital signals in the

controller can be configured to appear on the Port I/O pins specified in the Crossbar Control registers. This

allows the user to select the exact mix of general purpose Po rt I/O and digital resources needed fo r the

particular application.

-

22 Rev. 1.2

C8051F320/1

Highest

Priority

Lowest

Priority

XBR0, XBR1,

PnSKIP Registers

PnMDOUT,

PnMDIN Registers

Priority

Decoder

(P0.0-P0.7)

(P1.0-P1.7)

(P2.0-P2.7)

(P3.0)

2

P0

4

2

2

2

6

2

8

8

8

8

Digital

Crossbar

8

I/O

Cells

P1

8

I/O

Cells

P2

8

I/O

Cells

P3

1

I/O

Cells

Note: P2.4-P2.7 only available

on the C8051F320

P0.0

P0.7

P1.0

P1.7

P2.0

P2.7

P3.0

UART

SPI

SMBus

CP0

Outputs

CP1

Outputs

SYSCLK

(Internal Dig it al Sign al s)

PCA

T0, T1

P0

P1

P2

(Port Latches)

P3

Figure 1.7. Digital Crossbar Diagram

1.7. Serial P orts

The C8051F320/1 F amily inc ludes an SM Bus/I2C interface, a full-duplex UA RT with enhanced baud rate

configuration, an d an Enhanced S PI interface. Eac h of the serial buses is fully implemented in hardware

and makes extensive use of the CIP-51's interrupts, thus requiring very little CPU intervention.

1.8. Programmable Counter Array

An on-chip Programmable Counter/Timer Array (PCA) is included in addition to the four 16-bit general purpose counter/timers. The PCA consists of a dedicated 16-bit counter/timer time base with five programmable capture/compare modules. The PCA clock is derived from one of six sources: the system clock divided

by 12, the system clock divided by 4, Timer 0 overflows, an External Clock Input (ECI), the system clock, or

the external oscilla tor c lock s ourc e di vi de d by 8 . T he ext er nal cloc k sour c e s ele ct ion is u sef ul for real - tim e

clock functional ity, where the PCA is cl ocked by an ext ernal sou rce while the int ernal osc illator d rives the

system clock.

Each capture/compare module can be configured to operate in one of six modes: Edge-Triggered Capture,

Software Timer, High Speed Output, 8- or 16-bit Pulse Width Modulator, or Frequency Output. Additionally,

Capture/Compare Module 4 offers watchdog timer (WDT) capabilities. Following a system reset, Module 4

is configured and enabled in WDT mode. The PCA Capture/Compare Module I/O and External Clock Input

may be routed to Port I/O via the Digital Crossbar.

Rev. 1.2 23

C8051F320/1

SYSCLK/12

SYSCLK/4

Timer 0 Overflow

ECI

SYSCLK

External Clock/8

PCA

CLOCK

MUX

16-Bit Counter/Timer

Capture/Compare

Module 0

ECI

CEX0

Capture/Compare

Module 1

CEX1

Capture/Compare

Module 2

CEX2

Capture/Compare

Module 3

CEX3

Capture/Compare

Module 4 / WDT

CEX4

Crossbar

Port I/O

Figure 1.9. PCA Block Diagram

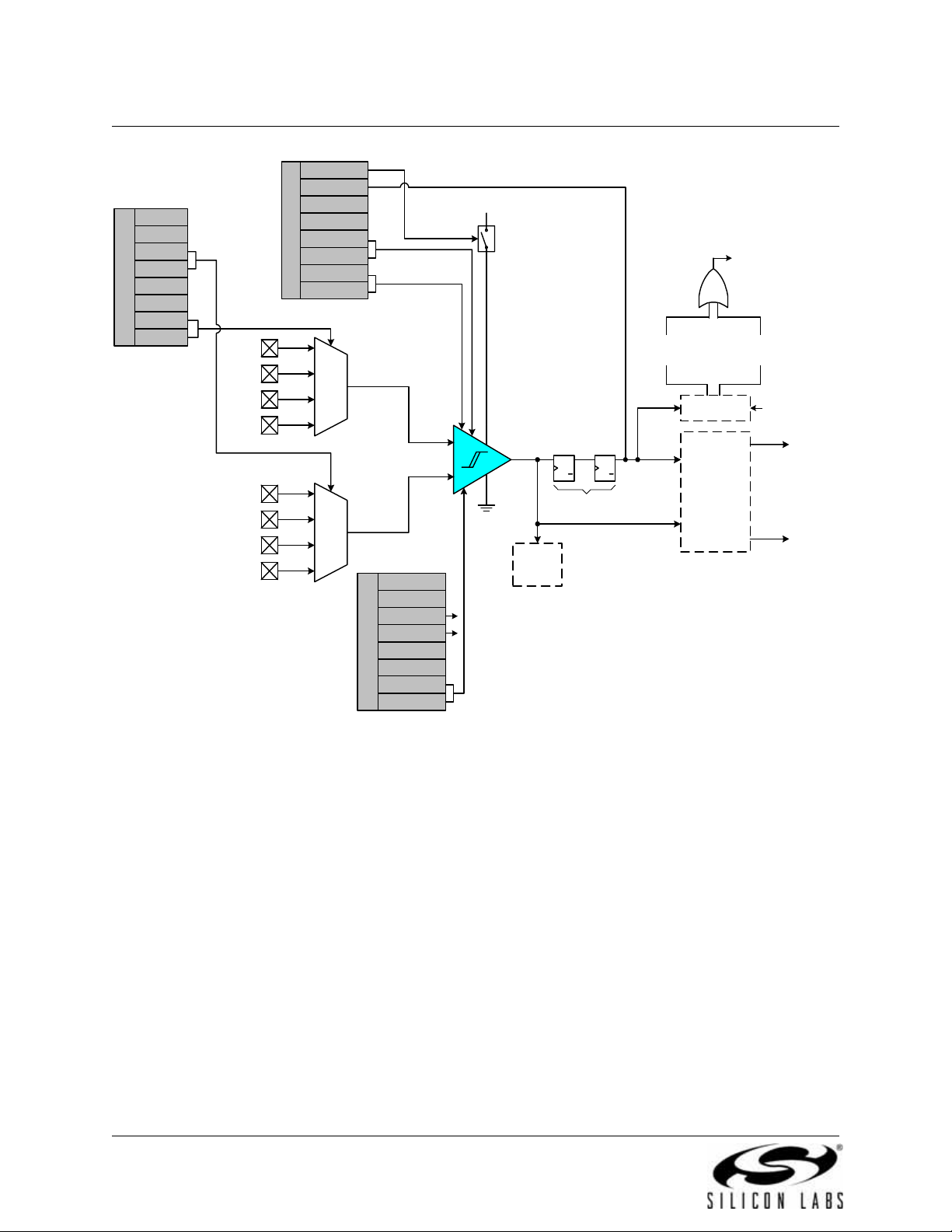

1.9. 10-Bit Analog to Digital Converter

The C8051F320/1 devices inclu de an on-chip 10-bit SAR ADC with a 17-channel differential input multiplexer. With a maximum throughput of 200 ksps, th e AD C offers tru e 10 -bit l in eari ty w ith an INL of ±1LSB.

The ADC system includ es a configurable ana log multiplexer that selects both positiv e and negative ADC

inputs. Ports1-3 are available as ADC inpu ts; additional ly, the on-chip Te mperat ure Sens or outpu t and the

power supply voltage (VDD) a re avai lable as ADC inputs. Us er firm ware ma y sh ut down the A DC to s ave

power.

Conversions can be started in six ways: a software command, an overflow of Timer 0, 1, 2, or 3, or an

external convert start signal. This flexibility allows the start of conversion to be triggered by software

events, a periodic sig nal (timer ove rflows), or e xternal HW sig nals. Convers ion completi ons are ind icated

by a status bit and an interrupt (if enable d). The resulting 10-bit data word is latched into the ADC da ta

SFRs upon completion of a conversion.

Window compare registers for the ADC data can be configured to interrupt the controller when ADC data is

either within or o utside of a specified range. Th e ADC can monitor a key v oltage continuously in back

ground mode, but not interrupt the controller unless the converted data is within/outside the specified

range.

24 Rev. 1.2

P2.4-2.7

available on

C8051F320

Temp

Sensor

Analog Multiplexer

P1.0

P1.7

P2.0

P2.7

P3.0

VDD

P1.0

19-to-1

AMUX

Configuration, Control, and Data Registers

(+)

10-Bit

SAR

(-)

ADC

C8051F320/1

000 AD0BUSY (W)

Start

Conversion

16

001

010

011

100

101

Timer 0 Overflow

Timer 2 Overflow

Timer 1 Overflow

CNVSTR Input

Timer 3 Overflow

ADC Data

Registers

P2.4-2.7

available on

C8051F320

P1.7

P2.0

P2.7

P3.0

VREF

GND

19-to-1

AMUX

End of

Conversion

Interrupt

Window Compare

Logic

Window

Compare

Interrupt

Figure 1.10. 10-Bit ADC Block Diagram

1.10. Comparators

C8051F320/1 devices include two on- chip voltage comparators tha t are enabled/disabled and configured

via user software. Port I/O pins may be configured as comparator inputs via a selection mux. Two compar

ator outputs may be routed to a Port pin if desired: a latched out put and/or an unlatch ed (asynchronous)

output. Comparator response tim e is programmable, allowin g the user to select between hig h-speed and

low-power modes. Positive and negative hysteresis are also configurable.

Comparator interrupts may be generated on rising, falling, or both edges. When in IDLE mode, these interrupts may be used as a “wake-up” source. Comparator0 may also be configured as a reset source.

Figure 1.11 shows the Comparator0 block diagram.

-

Rev. 1.2 25

C8051F320/1

CMX0N1

CMX0N0

CPT0MX

CMX0P1

CMX0P0

P1.0

P1.4

P2.0

P2.4

P1.1

P1.5

P2.1

P2.5

CP0EN

CP0OUT

CP0RIF

CP0FIF

CP0HYP1

CPT0CN

CP0HYP0

CP0HYN1

CP0HYN0

CP0 +

CP0 -

VDD

CP0

Interrupt

CP0

Rising-edg e

Interrupt

Logic

+

-

SET

D

(SYNCHRONIZER)

SET

D

Q

Q

CLR

CLR

Q

Q

Crossbar

GND

CP0

Falling-edge

CP0RIE

CP0FIE

CP0

CP0A

Reset

Decision

Tree

Note: P2.4 and P2.5 availab le

only on C8051F320

Figure 1.11. Comparator0 Block Diagram

CP0RIE

CP0FIE

CPT0MD

CP0MD1

CP0MD0

26 Rev. 1.2

C8051F320/1

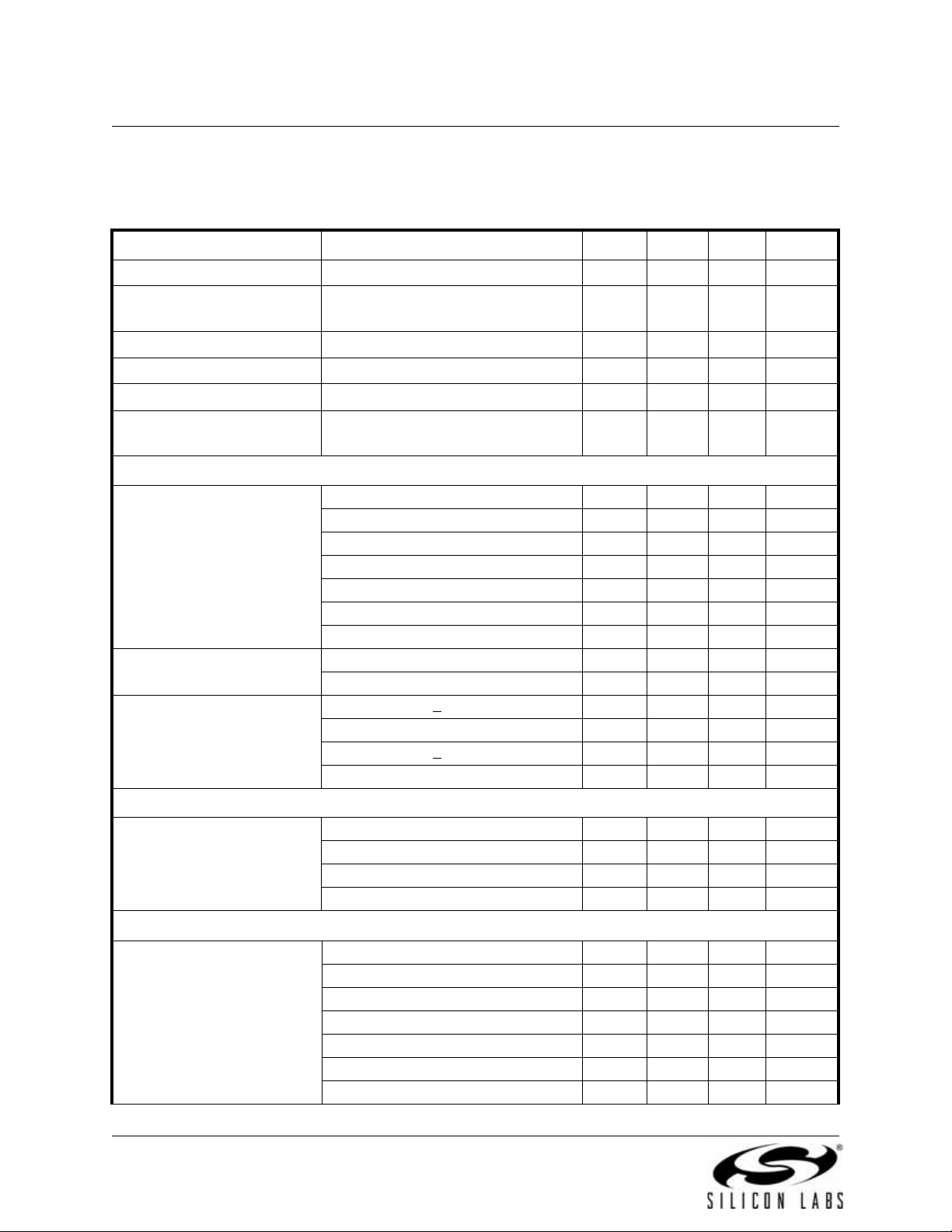

2. Absolute Maximum Ratings

Table 2.1. Absolute Maximum Ratings

Parameter Conditions Min Typ Max Units

Ambient temperature under bias

Storage Temperature –65 — 150 °C

Voltage on any Port I/O Pin or /RST with

respect to GND

Voltage on VDD with respect to GND –0.3 — 4.2 V