Stereo Decoder/Noise Blanker TDA 4340X

1 Overview

1.1 Features

• Internal reference voltage source

• Adjustment free oscillator with

ceramic resonator 456 kHz

• Pilot dependent mono/stereo switching with

hysteresis

• Stereo indicator output

• Analogue control of mono/stereo change over (stereo noise control, SNC)

• Pilot canceller (19 kHz)

• Adjacent channel noise suppression (114 kHz)

• MUTE facility

• Analogue control of deemphasis (high cut control, HCC).

• Stereo inputs for additional signal source at output amplifiers

• Interference noise detector with integrated high-pass filter

• (IF level signal or MPX input)

• MPX input low-pass filter

• Noise blanking at MPX demodulator outputs

• Input and output level adjustable (resistor values)

P-DSO-20-1

Type Ordering Code Package

TDA 4340X Q67000-A5058 P-DSO-20-1

1.2 Application

The TDA 4340X is an integrated circuit providing the stereo decoder function and noise

blanking for FM car radio applications.

Semiconductor Group 1 04.96

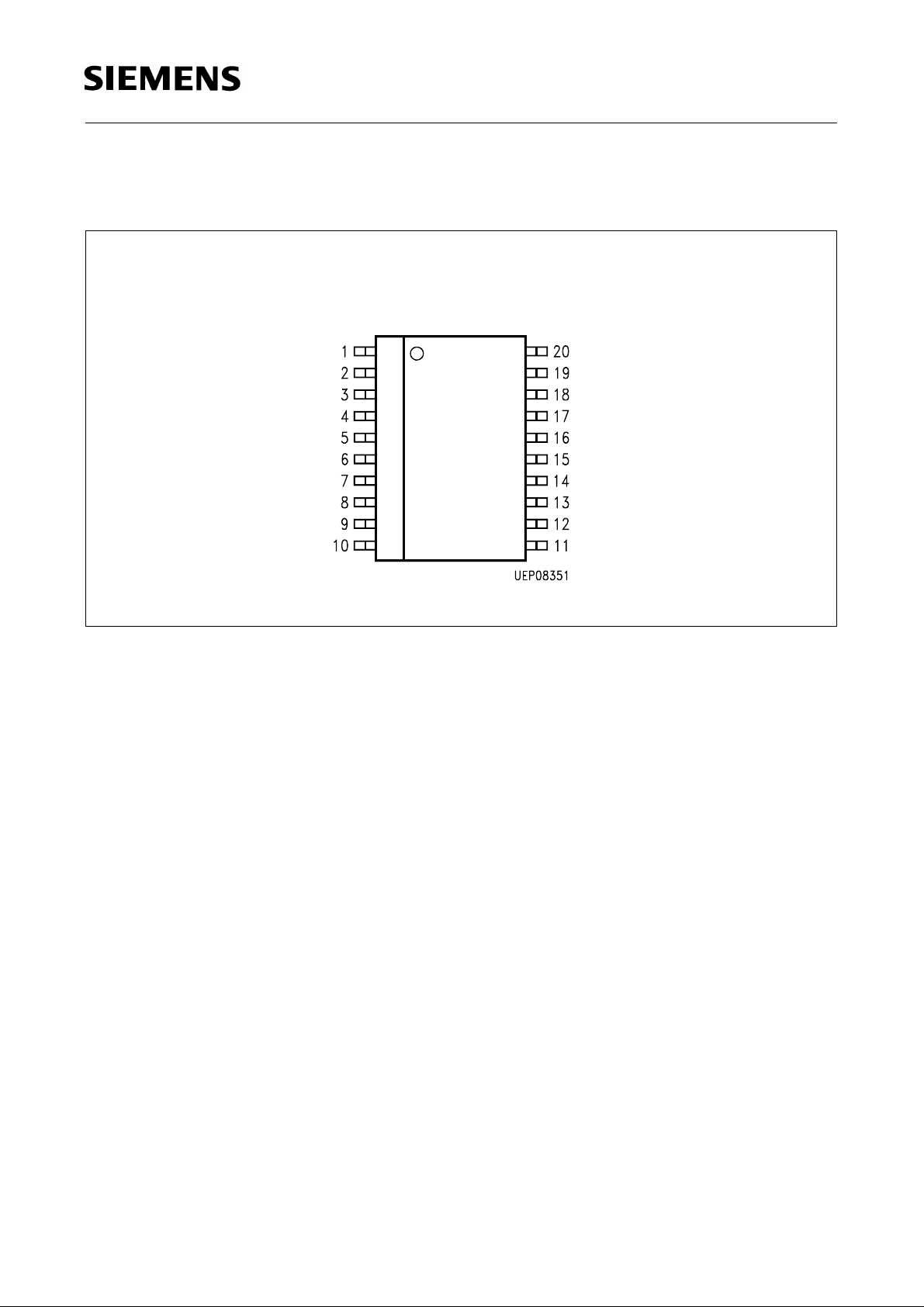

1.3 Pin Configuration

(top view)

TDA 4340X

P-DSO-20-1

Figure 1

Semiconductor Group 2 04.96

1.4 Pin Definitions and Functions

Pin No. Function

1 Phase detector output, PLL loop filter

2 Oscillator pin (456 kHz)

3 Ground

4 Reference current pin, external reference resistor

5 Positive supply voltage

6 Interference detector input, noise detector input

7 Timing capacitor for monoflop (gate time)

Low voltage applied turns off oscillator, phase detector, pilot detector, SNC

and changes the time constant for HCC, noise gate monoflop

8 Hold capacitor for noise detector average level

Low voltage applied mutes the stereo decoder output, noise level capacitor

TDA 4340X

9 Auxiliary input left, output amplifier left

10 Audio signal output left

11 Audio signal output right

12 Auxiliary input right, output amplifier right

13 HCC timing/hold capacitor, deemphasis right

14 HCC timing/hold capacitor, deemphasis left

15 Input for HCC voltage

16 Input for SNC voltage

17 Input for reference level control voltage (HCC and SNC)

18 Pilot indicator output, open collector, active low

19 Pilot detector output

Low voltage applied switches the stereodecoder to mono state

20 Input for MPX signal

Semiconductor Group 3 04.96

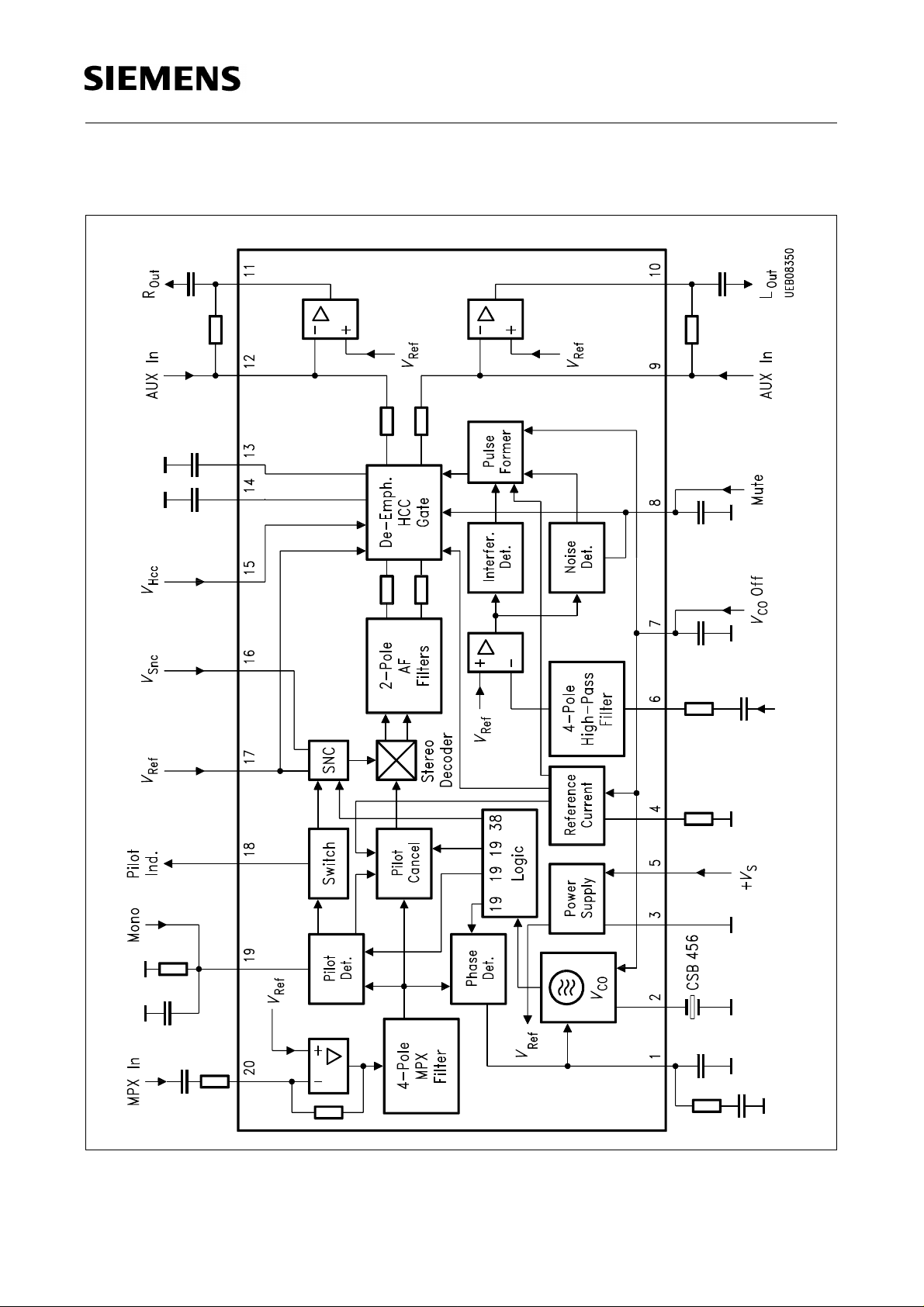

1.5 Functional Block Diagram

TDA 4340X

Figure 2

Block Diagram

Semiconductor Group 4 04.96

TDA 4340X

2 Circuit Description

Power Supply, Reference Current

A temperature stable, low noise reference voltage generator is used for better ripple

rejection and for the generation of a reference current. This current is used as a time

base for the deemphasis, the gate time of the pulse former, and the pilot cancellation,

avoiding temperature and tolerance effects.

MPX Input, MPX Filter

Adjusting the value of the input resistor, the MPX input can be adapted to the output level

of the FM demodulator. A 4-pole low-pass filter determines the bandwidth of the MPX

signal.

Voltage Controlled Oscillator, Phase Detector

The 456 kHz oscillator and the frequency dividers are used as walsh function generators

(suppression of 3rd order harmonics) for:

– 38 kHz for the stereo decoder

– 19 kHz inphase for phase detector and pilot cancellation

– 19 kHz quadrature for the phase detector.

The phase detector locks the on-chip 19 kHz signal to the pilot tone in the MPX signal at

90° phase.

Pilot Detector, Pilot Indicator, Pilot Cancellation

The voltage at the pilot detector output is proportional to the pilot tone input level. If that

level is high enough, the pilot indicator output is activated and the pilot Cancellation

turned on: a 19 kHz signal proportional to the voltage at the pilot detector output is added

to the MPX signal with inverse polarity, cancelling the 19 kHz pilot tone.

Interference Detector, Noise Detector, Pulse Former

The signal from the interference input (MPX or field strength signal) passes a 4-pole

high-pass to the noise blanking circuitry. The average noise level is stored on an external

capacitor. The interference detector compares the actual noise level with that stored on

the capacitor and triggers the pulse former if there is a significant difference. The pulse

former generates a gate pulse for the HCC block. During that pulse time the outputs of

the deemphasis circuit are switched to hold mode.

Semiconductor Group 5 04.96

TDA 4340X

3 Electrical Characteristics

3.1 Absolute Maximum Ratings

T

= – 40 °C to 85 °C

A

Parameter Symbol Limit Values Unit Remarks

min. max.

PLL loopfilter

Oscillator

Reference current

Supply voltage

Noise detector input

Noise gate monoflop

Noise level capacitor

Output amplifier left

AF output left

AF output right

Output amplifier right

Deemphasis right

Deemphasis left

HCC voltage

SNC voltage

V

I

I

V

V

V

V

V

I

I

V

V

V

V

V

2

4

10

11

1

5

6

7

8

9

12

13

14

15

16

05 V

– 1 0.1 mA

– 1 0 mA

0 13.2 V

05 V

0 V

5

V

0 V5– 1.5 V

06 V

– 1 0.3 mA

– 1 0.3 mA

06 V

05 V

05 V

0 13.2 V

0 13.2 V

Reference level voltage

Pilot indicator output

Pilot detector output

MPX input

Junction temperature

Storage temperature

Thermal resistance

ESD voltage, HBM

V

I

V

V

T

T

R

V

17

18

19

20

j

S

thSA

ESD

0 13.2 V

02 mA

0 V5– 1.5 V

06 V

– 40 150 °C

– 40 125 °C

95 K/W

– 4 4 kV 100 pF, 1500 Ω

Note: Maximum ratings are absolute ratings; exceeding only one of these values may

cause irreversible damage to the integrated circuit.

Semiconductor Group 6 04.96

TDA 4340X

3.2 Operating Range

Parameter Symbol Limit Values Unit

min. max.

Supply voltage

Ambient temperature

V

T

S

A

7.5 13.2 V

– 40 85 °C

Note: In the operating range the functions given in the circuit description are fulfilled.

3.3 AC/DC Characteristics

VS = 10 V, TA = 25 °C

Parameter Symbol Limit Values Unit Test Condition

min. typ. max.

Supply current

Supply current

Total harmonic

distortion

Signal to noise ratio

Channel separation 32 40 dB

I

S

I

S

THD

S/N

15 20 mA Osc. ON

10 15 mA Osc. OFF, V7 = 1 V

0.1 0.3 % f = 1 kHz

74 80 dB 20 Hz … 16 kHz,

Stereo

f = 1 kHz

MPX input level 1.7 Vpp

Overdrive margin of

input

AF output voltage 660 mVrms

Overdrive margin of

output

AF output DC

voltage

Difference of output

voltage levels

Muting depth 80 100 dB

DC offset at MUTE – 50 0 50 mV

DC offset

stereo ON/OFF

48 dB

69 dB

2.6 3 3.4 V

1dB

– 30 0 30 mV

THD = 1 %

f = 1 kHz, Stereo

THD = 1 %

f = 1 kHz

Semiconductor Group 7 04.96

3.3 AC/DC Characteristics (cont’d)

VS = 10 V, TA = 25 °C

Parameter Symbol Limit Values Unit Test Condition

min. typ. max.

Carrier and Harmonic Suppression

TDA 4340X

Pilotsignal

subcarrier

Intermodulation

f

= 10 kHz a

mod

f

= 13 kHz a

mod

Traffic Radio

f = 57 kHz a

a

19

a

38

1)

a

57

1)

a

76

1)

2

44 50 dB f = 19 kHz

44 50 dB f = 38 kHz

50 60 dB f = 57 kHz

50 60 dB f = 76 kHz

60 65 dB fS = 2 × 10 kHz … 19 kHz

91 % Mono, 9 % pilot, ƒS = 1 kHz

1)

3

60 75 dB fS = 3 × 13 kHz … 38 kHz

91 % Mono, 9 % pilot, ƒS = 1 kHz

57

1)

70 dB fS = 1 kHz ± 23 Hz

91 % Mono, 9 % pilot, fm = 1 kHz,

5 % Traffic Radio Carrier

(f = 57 kHz, fm = 23 Hz AM,

m = 60 %)

SCA (subsidiary communications authorization)

f = 67 kHz a

67

1)

70 dB fS = 9 kHz

81 % Mono, 9 % pilot,

f

= 1 kHz, 10 % SCA carrier

m

ACI (adjacent channel interference)

f = 119 kHz a

f = 190 kHz a

Ripple rejection

1)

No subject of production testing.

1)

114

1)

190

1)

60 70 dB V5 = 10 V, 100 mVrms, f = 1 kHz

80 dB

70 dB

Semiconductor Group 8 04.96

3.3 AC/DC Characteristics (cont’d)

VS = 10 V, TA = 25 °C

Parameter Symbol Limit Values Unit Test Condition

min. typ. max.

Mono/Stereo Control

Pilot threshold

voltage:

– for Stereo

ON

– for Stereo

OFF

– hysteresis

Stereo indicator

output:

– Pilot OFF

– Pilot ON

V

PIL on

V

PIL off

V

18 off

I

18 on

5

1.5

20

14

3

30 mVrms

mVrms

dB V

0.5

10

V

µA

PIL on/VPIL off

I

= 1 mA

18

V

= 13.2 V

18

TDA 4340X

External Control Voltages (active low)

Threshold voltage

V

19 thr

1 1.2 V

for external mono

control (pin 19)

Threshold voltage

V

8 thr

1 1.5 V

for MUTE (pin 8)

Threshold voltage

V

7 thr

1 1.5 V

for VCO OFF (pin 7)

Deemphasis

Reference voltage

V

17

0.5 4.5 V Reference level 100 Hz

Control Range

Minimum τ

Maximum τ

τ

τ

1.5 ×τ

τ

2.7 ×τ

deemph

deemph

deemph

= τ

=

nom

=

nom

nom

V

V

V

min

max

15

15

15

45 50 55 µs V17 = 3 V, V15 = 6 V,

135 150 165 µs V17 = 3 V, V15 = 0 V

V

–

17

220

V

–

17

400

V

17

V

17

170

V

17

300

–

–

V

17

120

V

17

200

C

C

V

17

–

mV V17 = 3 V, C

–

mV V17 = 3 V, C

= 6.8 nF

deemph

= 6.8 nF

deemph

= 3 V, C

deemph

deemph

deemph

= 6.8 nF

= 6.8 nF

= 6.8 nF

Semiconductor Group 9 04.96

3.3 AC/DC Characteristics (cont’d)

VS = 10 V, TA = 25 °C

Parameter Symbol Limit Values Unit Test Condition

min. typ. max.

Control Range (osc. OFF)

TDA 4340X

Minimum τ

Maximum τ

AM min

AM max

Stereo/Mono Blend Control

Channel separation

Channel separation

Reference voltage

V

16

V

16

V

17

Oscillator

Max. osc. frequency

Min. osc. frequency

VCO gain ∆

Oscillator voltage

Oscillator swing

f

osc max

f

osc min

f/∆V

V

2 DC

V

2 AC

1

13 15 17 µs V17 = 3 V, V15 = 6 V, V7 = 1 V

C

deemph

= 6.8 nF

35 40 45 µs V17 = 3 V, V15 = 0 V, V7 = 1 V

V

17

140

V

17

190

–

–

V

17

115

V

17

170

–

–

C

V

–90mV 15 dB sep.

17

V

–

17

150

mV 6 dB sep.

deemph

= 6.8 nF

0.5 4.5 V

0.7 1.0 2.0 % 100% × (f

– 2.0 – 1.0 – 0.7 % 100% × (f

/456 kHz – 1)

max

/456 kHz – 1)

min

– 13 – 10 – 7 kHz/V

345V

800 1100 1400 mVpp

PLL

PD gain ∆i/∆Φ

5 7.0 9 µA/rad V

= 54 mVrms

pilot

1)

Noise Detector

Input resistance

Input high-pass filter

Trigger threshold

Trigger threshold

Maximum noise

R

6

f

in, 6

V

6 min

V

6 dyn

V

6maxmean

75 100 135 kΩ

80 100 120 kHz – 3 dB

10 mVrms V8 = V8 (V

f

= 200 kHz

6

160 mVrms V8 = V8 (V

f

= 200 kHz

6

80 mVrms f6 = 200 kHz

= 0),

6 mean

= 50 mVrms),

6 mean

mean value

Semiconductor Group 10 04.96

3.3 AC/DC Characteristics (cont’d)

VS = 10 V, TA = 25 °C

Parameter Symbol Limit Values Unit Test Condition

min. typ. max.

TDA 4340X

Suppression pulse

40 µs

duration

Input offset current

Pulse threshold

I

V

, I

13

6 burst

14

1)

– 50 0 50 nA

1)

130 200 mVpp 100 kHz single burst repetition

rate 100 Hz both polarities

C

=1nF

in, 6

1)

No subject of production testing.

Note: The listed characteristics are ensured over the operating range of the integrated

circuit. Typical characteristics specify mean values expected over the production

spread. If not otherwise specified, typical characteristics apply at

T

= 25°C and

A

the given supply voltage.

Semiconductor Group 11 04.96

TDA 4340X

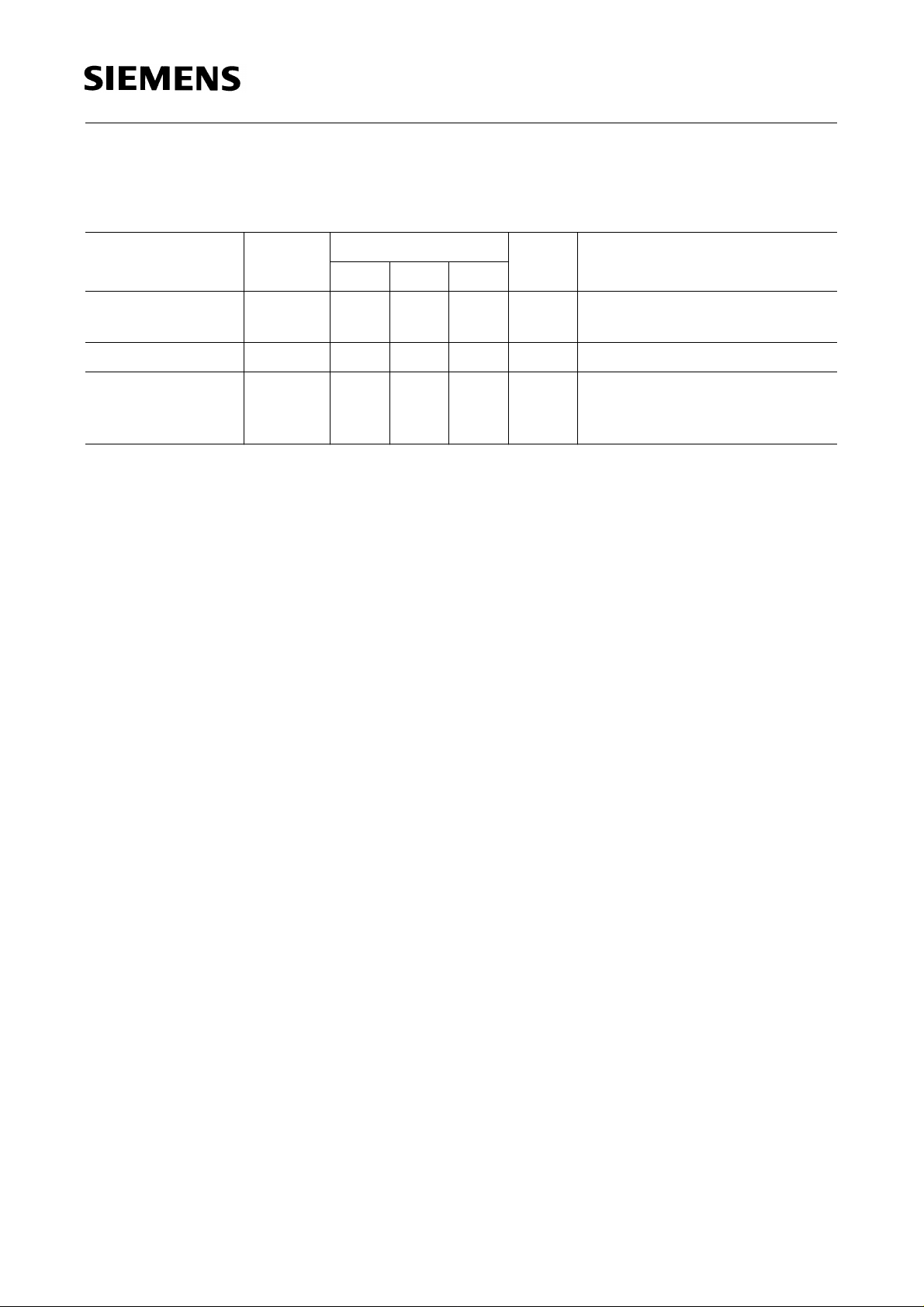

Figure 3

Test Circuit

Semiconductor Group 12 04.96

TDA 4340X

Figure 4

Application Circuit

Semiconductor Group 13 04.96

Diagrams

TDA 4340X

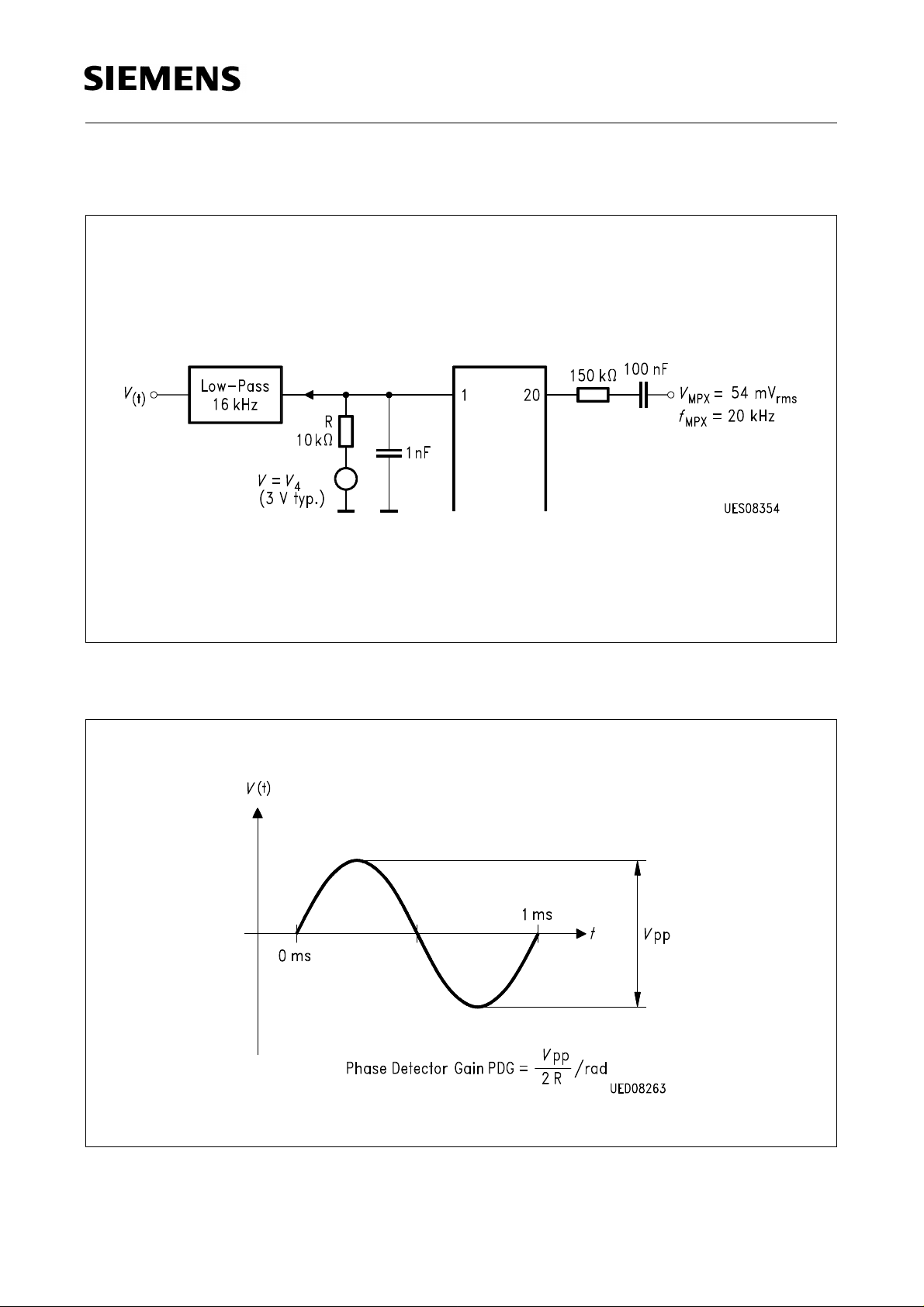

Figure 5

Definition of Phase Detector Gain

Figure 6

Phase Detector Gain

Semiconductor Group 14 04.96

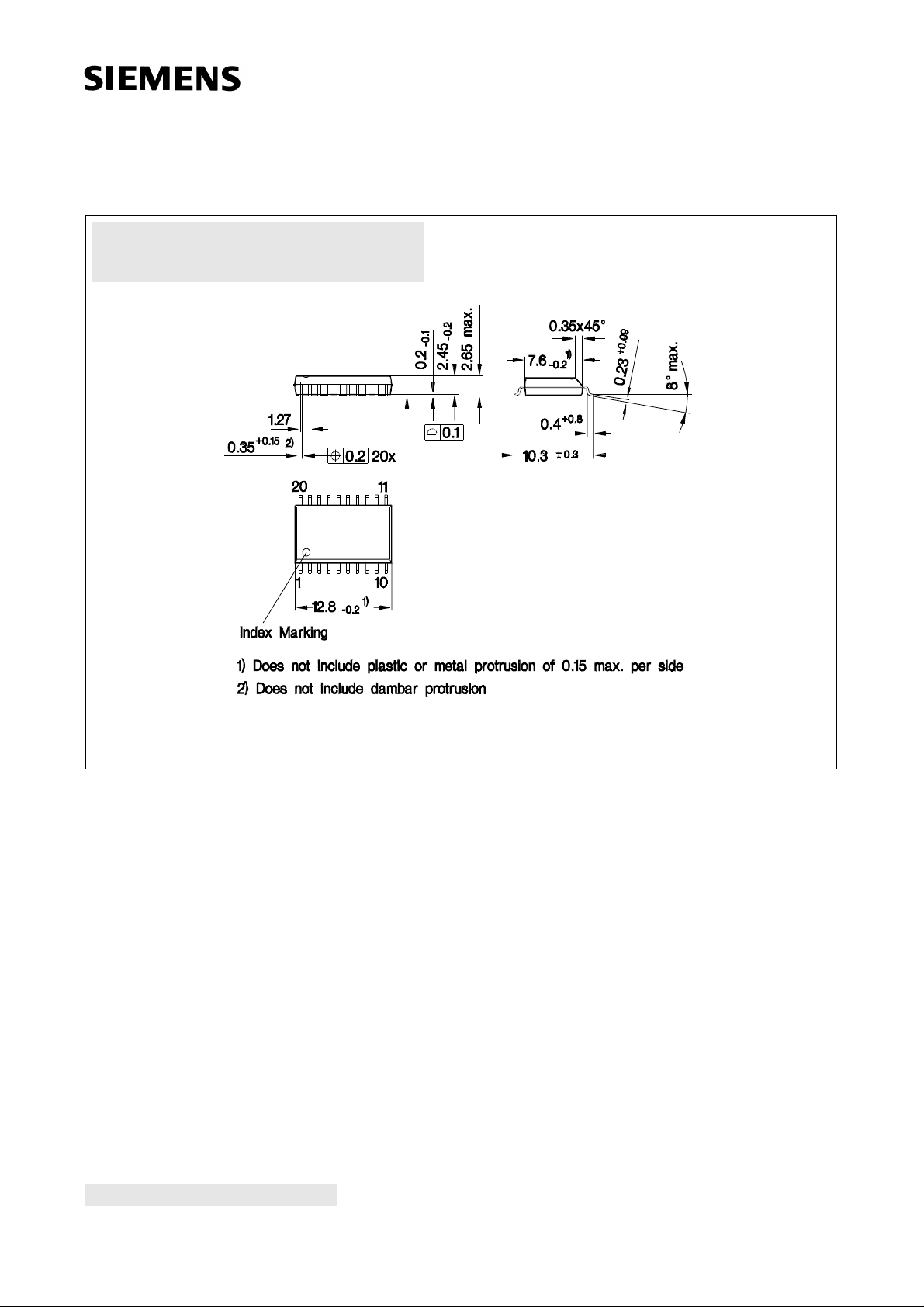

4 Package Outlines

P-DSO-20-1

(Plastic Dual Small Outline Package)

TDA 4340X

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”.

SMD = Surface Mounted Device

GPS05094

Dimensions in mm

Semiconductor Group 15 04.96

Loading...

Loading...