Siemens TDA16888, TDA16888G Datasheet

High Performance Power Combi Controller TDA 16888

1Overview

1.1 Features

PFC Section

– IEC 1000-3 compliant

– Additional operation mode as auxiliary power supply

– Fast, soft switching totem pole gate drive (1 A)

– Dual loop control (average current and voltage

sensing)

– Leading edge triggered pulse width modulation

– Peak current limitation

– Topologies of PFC preconverter are boost or flyback

– Continuous/discontinuous mode possible

– 94% maximum duty cycle

P-DIP-20-5

P-DSO-20-1

PWM Section

– Improved current mode control

– Fast, soft switching totem pole gate drive (1 A)

– Soft-start management

– Trailing edge triggered pulse width modulation

– Topologies of PWM converter are feed forward or flyback

– 50% maximum duty cycle to prevent transformer saturation

f

PWM

= f

PFC

–

Type Ordering Code Package

▼ TDA 16888 Q67000-A9284-X201-K5 P-DIP-20-5

▼

TDA 16888G Q67000-A9310-A702 P-DSO-20-1

▼ New type

Semiconductor Group 1 Data Sheet 1998-05-06

TDA 16888

Special Features

– High power factor

–Typical 50µA start-up supply current

– Low quiescent current (15 mA)

– Undervoltage lockout with internal stan d-by operatio n

– Internally synchronized fixed operating frequency ranging from 15 kHz to 200 kHz

– External synchroniz ati on poss ible

– Shutdown of both outputs externally triggerable

– Peak current limitation

– Overvoltage protection

– Average current sensing by noise filtering

1.2 General Remarks

The TDA 16888 comprises the complete control for power factor controlled switched

mode power supplies. Wi th its PFC and PWM sec tion being internal ly synchronized, it

applies for off-line converters with input voltages ranging from 90 V to 270 V.

While the preferred topologies of the PFC preconverter are boos t or flyback, the PWM

section can be designed as forward or flyback converter. In order to achieve minimal line

current gaps the maximum duty cycle of the PFC is about 94%. The maximum duty cycle

of the PWM, however, is limited to 50% to prevent transformer saturation.

Semiconductor Group 2 Data Sheet 1998-05-06

TDA 16888

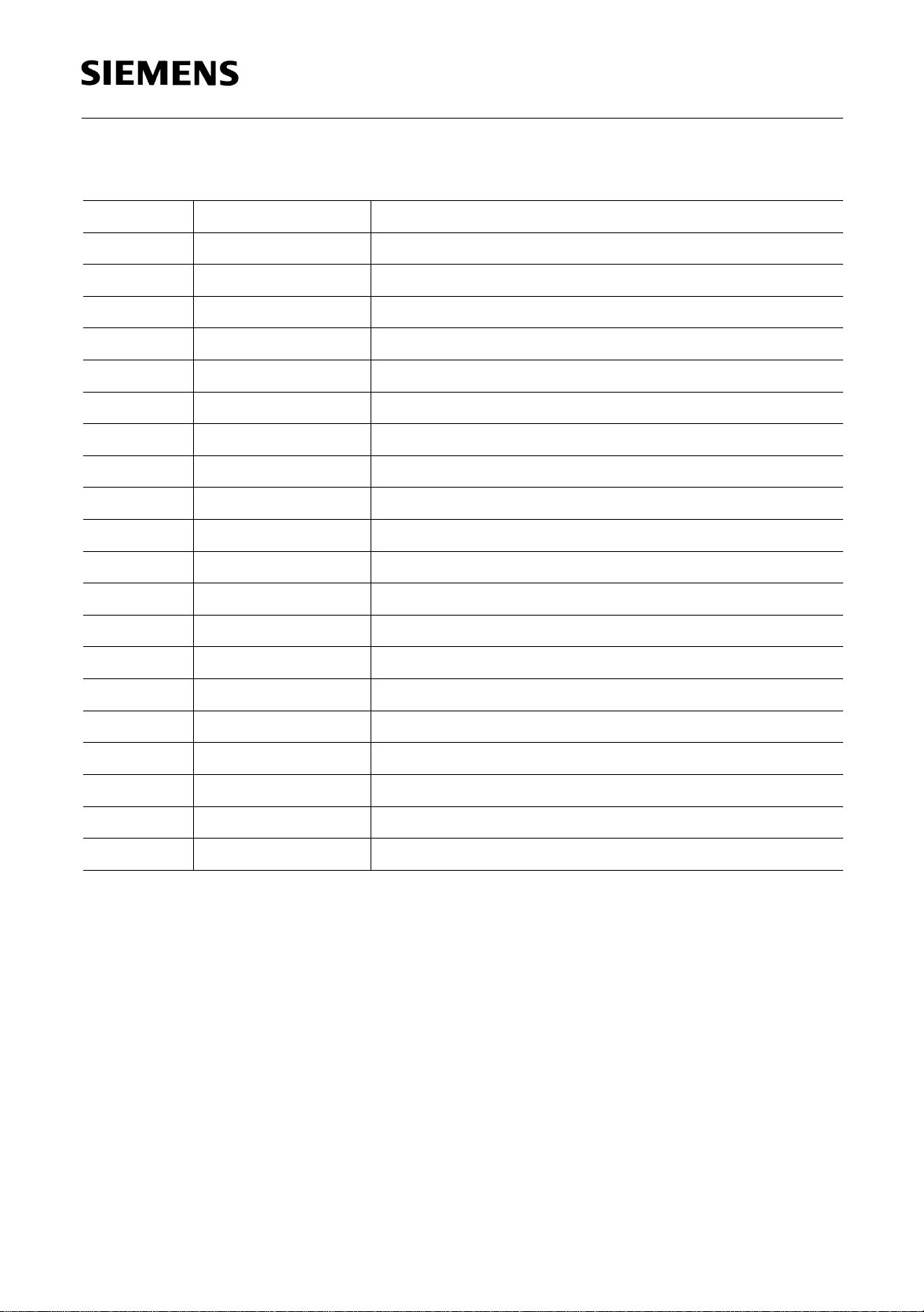

P-DSO-20-1P-DIP-20-5

20

19

18

17

16

15

14

13

12

11

AUX VS

PFC VS

PFC VC

PFC FB

ROSC

PWM RMP

PWM IN

PWM SS

SYNC

REF

CC

1

2

3

4

5

6

7

8

9

10

AEP02461

PFC IAC

V

PFC CC

PFC CS

GND S

PFC CL

GND

PFC OUT

V

PWM OUT PWM CS

PFC IAC

V

REF

PFC CC

PFC CS

GND S

PFC CL

GND

PFC OUT

V

CC

PWM OUT

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

AEP02486

AUX VS

PFC VS

PFC VC

PFC FB

ROSC

PWM RMP

PWM IN

PWM SS

SYNC

PWM CS

Figure 1 Pin Configuration (top view)

Semiconductor Group 3 Data Sheet 1998-05-06

1.3 Pin Definitions and Functions

Pin No. Symbol Function

1 PFC IAC AC line voltage sensing input

TDA 16888

2

V

REF

7.5 V reference

3 PFC CC PFC current loop compensation

4 PFC CS PFC current sense

5 GND S Ground sensing input

6 PFC CL Sensing i nput for PFC current limitation

7 GND Ground

8 PFC OUT PFC driver output

9

V

CC

Supply voltage

10 PWM OUT PWM driver output

11 PWM CS PWM current sense

12 SYNC Oscillator synchronization inpu t

13 PWM SS PWM soft-start

14 PWM IN PWM output voltage sensing input

15 PWM RMP PWM voltage ramp

16 ROSC Oscillator frequency set-up

17 PFC FB PFC voltage loop feedback

18 PFC VC PFC voltage loop compensation

19 PFC VS PFC output voltage sensing input

20 AUX VS Auxiliary power supply voltage sense

Semiconductor Group 4 Data Sheet 1998-05-06

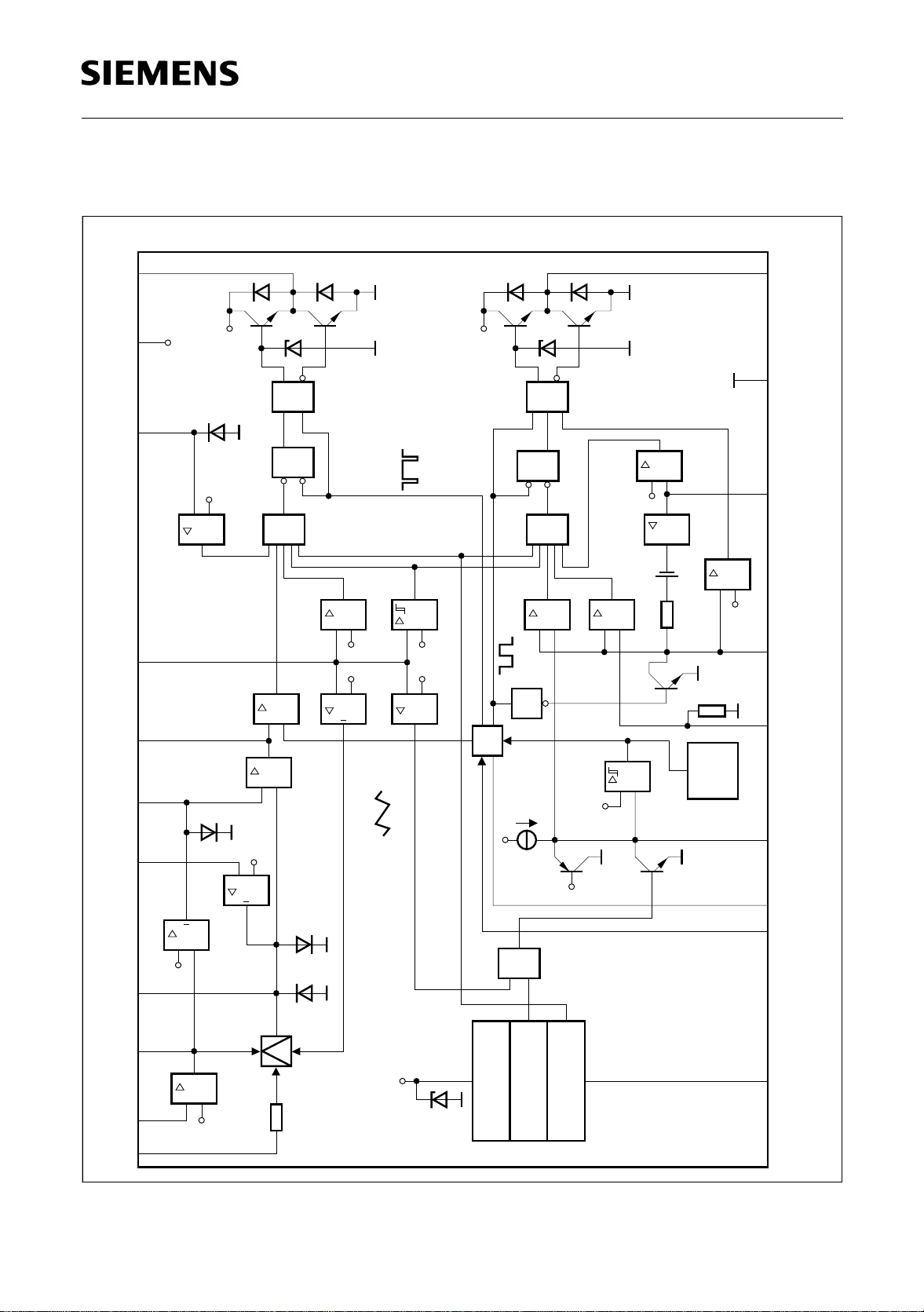

1.4 Block Di a g r am

TDA 16888

PFC

V

PFC

PFC

PFC

OUT

CC

CL

VS

CC

9

6

19

3

C3

10

OUT

PWM

AEB02357

S

V

S

V

Z1

S

V

Z2

7

&

&&

GND

D4

FF1

R

S

FF2

R

S

1 V

+

_

&

C1

C2

+

_

_

+

OTA2

C6

_

+

5.5 V 1 V

_

+

6 V

5.5 V

4 V

+

_

C7

1

C4

C8

_

+

Osc

C9

_

+

1 V

5

OP3

1

V

1.5 V

_

+

C10

Ω

1

R

10 k

3

R

_

+

Ω

100 k

0.4 V

11

15

CS

PWM

RMP

PWM

14

PWM

S

GND

VS

AUX

CSIAC

PFC PFC

FB VC

PFC

PFC

Figure 2

5

20

OTA3

18 4

OP1

17

1 8

+

1.2 V

_

Bias

PWM

Control

13

16

SS IN

PWM

ROSC

D3

OTA1

OP2

+

_

+

5 V

_

A

µ

1

30

Ι

C5

0.45 V

0.4 V

_

+

7.4 V

6 V

12

_

D1 D2

M

Q

3

M

2

M

+

5 V

1

M

Ω

2

R

10 k

S

V

Z3

17.5 V

1

<

_

11 V-14 V

Voltage Reference

Power Management

Undervoltage Lockout

7.5 V (Output Disable)

2

SYNC

REF

V

Semiconductor Group 5 Data Sheet 1998-05-06

TDA 16888

2 Functional Description

Power Supply

The TDA 16888 is protecte d again st overvolta ges ty pically above 17.5 V by an internal

V

Zener diod e Z3 at pin 9 (

ESD circuitry.

By means of its power manageme nt the TDA 16888 will switch from in ternal stand-by,

which is characterized by negligible current consumption, to operation mode as soon as

a supply voltage threshold of 14 V at pin 9 (

ringing at switch-over an undervoltage lockout is implemented, which will cause the

power management t o switch from operation mode t o internal stand-by as soon as th e

supply voltage falls bel ow a threshold of 11 V. Therefore, even if the supply voltage wil l

fall below 14 V, operation mode will be maintained as lo ng as the sup ply voltage is well

above 11 V.

) and against electrostatic discharging at any pin by special

CC

V

) is exceeded. To avoid uncontrolled

CC

As soon as the supply v oltage has stabilize d, which is d etermined by the TDA 16888’ s

power management and its soft-start feature at pin 13 (PWM SS), the PWM section will

be enabled by means of its internal bias control.

Protection Circuitry

Both PFC and PWM section are equipped with a fast overvoltage protection (C6)

sensing at pin 19 (PFC VS), which when being activated will immediately shut down both

gate drives. In addition to improve the PFC section’s load regulation it uses a fast but soft

overvoltage protection (OTA2) prior to the one described above, which when being

Q

activated will cause a well controlled throttling of the multiplier output

.

M

In case an undervoltage of the PFC output voltage is detecte d at pin 19 (PFC VS) by

comparator C4 the gate drive of t he PWM section will be s hut down in order to reduce

the load current an d to increase the PFC output voltage. This u ndervoltage shutdown

has to be prior to the undervoltage lockout of the internal power management and

V

therefore has to be bound to a threshold voltage at pin 9 (

) well above 11 V.

CC

In order to prevent the external circuitry from destruction the PFC output PFC OUT

(pin 8) will immediately be switched off by comparator C2, if the voltage at pin 19

(PFC VS) drops to ground caused by a broken wire. In a similar way measures are taken

to handle a broken wire at any other pin in order to ensure a safe operation of the IC and

its adjoining circuitry.

If necessary both outputs, PFC OUT (pin 8) an d PWM OUT (pin 10), can be shutdown

on external request. This is accom plished by shorti ng the external refe rence voltag e at

V

pin 2 (

characteristic, which will cut down the o utput current whe n

) to ground. To protect the external reference, i t is equipped with a foldback

REF

V

(pin 2 ) is shorted (see

REF

Figure 4).

Semiconductor Group 6 Data Sheet 1998-05-06

TDA 16888

Both PFC and PWM section are equipped with a peak current limitation, which is realized

by the comparators C3 and C9 sensing at pin 6 (PFC CL) and pin 11 (PWM CS)

respectively. When being activated this current limitation will immediately shut down the

respective gate drive PFC OUT (pin 8) or PWM OUT (pin 10).

Finally each pin is protected against electrostatic discharge.

Oscillator/Synchronization

The PFC and PWM clock signals as well as the PFC voltage ramp are synchronized by

the internal oscillator (see Figure 18). The oscillator’s frequency is set by an external

resistor connected to pin 16 (ROSC) and ground (see Figure 5). The corresponding

capacitor, however, is integrated to guarantee a low current cons umption and a high

resistance against elec tromagnetic interferenc es. In order to ensure superior prec ision

of the clock frequency, the clock signal CLK OSC is derived from a triangular instead of

a saw-tooth signal. Furthermore to provide a clock reference CLK OUT with exactly 50%

duty cycle, the frequency of the oscillator’s clock signal CLK OSC is halved by a D-latch

before being fed into the PFC and PWM section respectively (see Figure 18).

The ramp signal of the PFC section

V

PFC RMP

is composed of a slowly falling and a

steeply rising edge. This ramp has been reversed in contrast to the common practice, in

order to simultaneously allow for current measurement at pin 5 (GND S) and for external

compensation of OP2 by means of pin 5 (GND S) and pin 3 (PFC CC).

The oscillator can be synchronized with an external clock signal supplied at pin 12

(SYNC). However, since the oscilla tor’s frequency is halved before being fed into the

PFC and PWM section, a synchronization frequency being twice the operating frequency

is recommended. As long as th e synchronization signal is H the os cillator’s triangular

V

signal

is interrupted and its clock signal CLK OSC is H (see Figure 19 and

OSC

Figure 20). However, as soon as the external clock changes from H to L the oscillator is

released. Correspondingly, by means of an external clock signal supplied at pin 12

f

(SYNC) the oscillator frequency

varied on principle only within the range from 0.66

set by an external resistor at pin 16 (ROSC) can be

OSC

f

OSC

to 2 f

. If the oscillator has to

OSC

be synchronized over a wider freq uency rang e, a synch roni zation by means of the s ink

current at pin 16 (ROSC) has to be preferred to a synchronization by means of pin 12

(SYNC). Anyhow, please note, that pin 12 (SYNC) is not meant to permanently

shutdown both PFC and PWM section. It can be used to halt the oscil lator freezi ng the

prevailing state of both drivers but does not allow to automatically shut th em down. A

V

shutdown can be achieved by shorting pin 2 (

) to ground, instead.

REF

Finally, In order to reduce the overall current consumption under low load conditions, the

oscillator frequency itself is halv ed as long as the voltage at pin 13 (PWM SS) is less

than 0.4 V (disabled PWM section).

Semiconductor Group 7 Data Sheet 1998-05-06

TDA 16888

PFC Section

At normal operation the PFC section operates with dual loop control. An inner loop,

which includ es OP2, C 1, FF1 and the PF C’s driv er, cont rols the s hape of the lin e current

by average current control enabling either continuous or discontinuous operation. By the

outer loop, which is supported by OP1, the multiplier, OP2, C1, FF1 and the PFC's driver,

the PFC output voltage is controlled. Furthermore there is a third control loop composed

of OTA1, OP2, C1, FF1 and the PFC’s driver, which allows the PFC section to be

operated as an auxiliary power su pply even when the PWM section is disabled. With

disabled PWM section, however, the PFC section is operated with ha lf of its nominal

operating frequency in order to reduce the overall current consumption.

Based on a pulse-wi dth-m odulation, which is leading edge triggered with respect to the

internal clock reference CLK OUT and which is trailing edge modulated according to the

PFC ramp signal

V

PFC RMP

PFC section is designed fo r a maximum duty cycl e of ca. 94% to achiev e minimal line

current gaps.

and the output voltage of OP2 V

PFC CC

(see Figure 1 8), the

PWM Section

The PWM section is e quipped with improved cu rrent mode con trol containin g effective

slope compensation as well as enhanced spike suppression in contrast to the commonly

used leading edge current blanking. This is achieved by the chain of operational amplifier

V

OP3, voltage source

and the 1st order low pass filter composed of R1 and an external

1

capacitor, which is connected to pin 15 (PWM RMP). For crosstalk suppression between

PFC and PWM section a signal-to-no ise ratio comparable to voltage mode controlled

PWM’s is set by operational amplifier OP3 performing a fivefold amplification of the PWM

load current, which is sense d by an external shunt resistor. In order to simulta neously

perform effective slope compensation and to suppress leading spikes, which are due to

parasitic capacitances bei ng disch arged whenever the power transisto r is switched on,

V

the resulting signal is su bsequently increas ed by the constant volta ge of

and finally

1

fed into the 1st order low pass fi lter. The peak ramp voltage, that in this way can be

V

reached, amounts to ca. 6. 5 V. By combination of voltag e source

and the following

1

low pass filter a basic ramp (step response) with a leading notch is crea ted, which will

fully compensate a leading spike (see Figure 12) provided, the external capacitor at

pin 15 (PWM RMP) and the external current sensing shunt resistor are scaled properly.

Semiconductor Group 8 Data Sheet 1998-05-06

TDA 16888

The pulse-width-modulation of the PWM section is trailing edge modulated according to

the PWM ramp signal

V

PWM RMP

pin 14 (PWM IN) (see Figure 18). In contrast to the PFC secti on, however, the pulsewidth-modulation of the PWM section is trailing edge triggered with respect to the

internal clock reference CLK OUT in order to avoid undesirable electromagnetic

interference of both section s. Moreover the maximu m duty cycl e of the PWM is limited

to 50% to prevent transformer saturation.

By means of the above mentioned improved current mode control a stable pulse-widthmodulation from maximum load down to no lo ad is achi eved. Finally, in case of no load

conditions the PWM section may as well be disabled by shorting pin 13 (PWM SS) to

ground.

at pin 15 (PWM RMP) and the input volta ge V

PWM IN

at

Semiconductor Group 9 Data Sheet 1998-05-06

TDA 16888

3 Functional Block Description

Gate Drive

Both PFC and PWM section use fast tot em pole gate drives at pin 8 (PFC OUT) and

pin 10 (PWM OUT) respectively, which are designed to avoid cross conduction currents

and which are equipped with Zener diodes (Z1, Z2) in order to improve the control of the

attached power transistors as well as to protect them against undesirable gate

overvoltages. At voltages below the undervoltage lockout threshold these gate drives are

active low. In order to keep the switching losses of the involved power diodes low and to

minimize electroma gnetic emissions, both gate drives are optimized for s oft switching

operation. This is achie ved by a novel slope cont rol of the rising edge at each d river’s

output (see Figure 13).

Oscillator

The TDA 16888’s clock signals as well as the PFC voltage ram p are provided by the

internal oscillator. Th e oscillat or’s frequency i s set by a n external resistor connected to

pin 16 (ROSC) and ground (see Figure 5). The correspon ding capacitor, however, is

integrated to guarantee a low current consumption and a high resistance against

electromagnetic interferences. In order to ensure superior precision of the clock

frequency, the clock signal CLK OSC is derived from the minima and maxima of a

triangular instead of a saw-tooth signal (see Figure 18). Furthe rmor e, to pr ovide a cl ock

reference CLK OUT with exactly 50% duty cycle, the freq uency of the os cillator ’s clock

signal CLK OSC is halved by a D-latch before being fed into the PFC and PWM section

respectively.

The ramp signal of the PFC section

V

PFC RMP

is composed of a slowly falling and a

steeply rising edge, the latter of which is triggered by the rising edge of the clock

reference CLK OUT. This ramp has been revers ed in c ontrast to t he common practic e,

in order to simultaneously allow for current measurement at pin 5 (GND S) and for

external compensation of OP2 by means of pin 5 (GND S) and pin 3 (PFC CC). The

slope of the falling edge, which in conjunction with the output of OP2 controls the pulsewidth-modulation of the PFC output signal

V

PFC OUT

, is derived from the current set by the

external resistor at pin 16 (ROSC). In this way a cons tant amplitu de of the ram p signal

(ca. 4.5 V) is ensured. In contrast, the slope of the rising edge, which marks the minimum

blanking interval and therefore li mits the max imum duty c ycle

t

of the PFC output

on,max

signal, is determined by an internal current source.

In contrast to the PFC section the ramp signal of the PWM section is trailing edge

triggered with respect to the internal clock reference CLK OUT to avoid undesirable

electromagnetic interference of both sections. Moreover, the maximum duty cycle of the

PWM is limited by the risi ng edge of the clock reference CLK OUT to 50% to pr event

transformer saturation.

Semiconductor Group 10 Data Sheet 1998-05-06

TDA 16888

The oscillator can be synchronized with an external clock signal supplied at pin 12

V

(SYNC). As long as this clock signal is H the oscillator’s triangular signal

interrupted and its clock signal CLK OSC is H (see Figure 19 and Figure 20). However,

as soon as the external clock changes from H to L the oscillator is released.

Correspondingly, by me ans of an external clock signal su pplied at pin 12 (SYNC) the

f

oscillator frequency

principle only within the range from 0.66

set by an extern al resisto r at p in 16 (ROSC) can be varied on

OSC

f

OSC

to 2 f

. Please note, that the slope of the

OSC

falling edge of the PFC ramp is not influenced by the synchronization frequency. Instead

the lower voltage peak is modulated. Consequently, on the one hand at high

synchronization frequencies

f

SYNC

> f

the amplitude of the ramp signal and

OSC

correspondingly its signal-to-noise ratio is decreased (see Figure 19). On the other hand

at low synchronization frequencies

f

SYNC

< f

the lower voltage peak is clamped to the

OSC

minimum ramp voltage (typ. 1.1 V), that at least can be achieved (see Figure 20), which

may cause undefined PFC dut y cycles as th e voltage

V

PFC CC

at pin 3 (PFC CC) drops

below this threshold. However, if the oscillator has to be synchronized over a wide

frequency range, a synch ronizati on by m eans of the sink current a t pin 16 (ROSC) has

to be preferred to a synchronization by means of pin 12 (SYNC).

OSC

is

In order to reduce the overall current consumption under low load conditions, the

oscillator frequency itself is halv ed as long as the voltage at pin 13 (PWM SS) is less

than 0.4 V (disabled PWM section).

Multiplier

I

The multiplier serves to pro vide the c ontrolled current

I

of the sinusoidal input current

R

of the 10 k Ω resistor

, the magnitude of the PFC output voltage VM2 given at pin 18

2

derived from the voltage at pin 1 (PFC IAC) by means

M1

(PFC VC) and the possibility for soft overvoltage protection

Protection Circuitry

). By means of this current the required power factor as well as the

by combination of the shape

QM

V

M3

(see

Chapter

magnitude of the PFC output voltage is ensured. To achieve an excellen t performan ce

V

over a wide range of output po wer and i nput voltage , the input vol tage

is amplified

M2

by an exponential function before being fed into the multiplier (see Figure 8).

Voltage Amplifier OP1

Being part of the outer loop the error amplifier OP1 c ontrols the magnitude of the PFC

output voltage by comparis on of the PFC output voltage me asured at pin 17 (PFC FB)

with an internal reference voltage. The latter is fixed to 5 V in order to achieve immunity

from external noise. To allow fo r individual fe edback the ou tput of OP1 is con nected to

pin 18 (PFC VC).

Semiconductor Group 11 Data Sheet 1998-05-06

TDA 16888

Current Amplifier OP2

Being part of the inner loop the error amplifier OP2 controls the shape of the line current

I

by comparison of the controlled current

is achieved by setting the pulse width of the PFC gate drive in conjunction with the

comparator C1. In order to limit the voltage range supplied at pin 4 (PFC CS) and at pin 5

(GND S), clamping diodes D1, D2 and D3 are connected with these pins and ground. To

allow for individual feedback the output of OP2 is connected to pin 3 (PFC CC).

Ramp Amplifier OP3

For crosstalk suppression between PFC and PWM section a signal-to-noise ratio

comparable to voltage mode controlled PWMs is set by operational amplifier OP3

performing a fivefold amplification of the PWM load current, which is sensed by an

external shunt resistor. In order to suppress leading spikes, which are du e to parasitic

capacitances being discharged whenever the power transistor is switched on, the

resulting signal is subsequ ently increased by the constant voltage of

into a 1st order low pass filter. By combination of voltage source

pass filter a step response with a leading notch is created, which will fully compensate a

leading spike (see Figure 12) provided, the external capacitor at pin 15 (PWM RMP)

and the external current sensing shunt resistor are scaled properly.

with the measured average line current. This

QM

V

and finally fed

1

V

and the following low

1

Operational Transconductance Amplifier OTA1

The TDA 16888’s auxiliary power supply mode is controlled by the fast operational

transconductance amplifier OTA1. When under low load or no load conditions a voltage

below 5 V is sensed at pin 20 (AUX VS), it will sta rt to superimpose its output on the

output Q

of the multiplier and in thi s way will replace the error a mplifier OP1 and the

M

multiplier. At normal operat ion, however, when the voltage at pin 20 (AUX VS) is well

above 5 V, this operational transconductance amplifier is disabled.

Operational Transconductance Amplifier OTA2

By means of the operational transconductance amplifier OTA2 sensing at pin 19

(PFC VS) a f ast but soft overvo ltage protection of t he PFC output voltag e is achieved,

which when being activated (

multiplier output Q

(see Figure 9).

M

V

PFC VS

> 5.5 V) will cause a well controlled throttling of the

Operational Transconductance Amplifier OTA3

In order to achieve offset compensation of error amplifier OP2 under low load conditions,

that will not suffice to start OTA1, the operational transc onductance amplifier OTA3 is

introduced. It will start operation as soon as these conditions are reached, i.e. the voltage

at pin 18 (PFC VC) falls below 1.2 V.

Semiconductor Group 12 Data Sheet 1998-05-06

Loading...

Loading...