Siemens SAB-C502-2R20N, SAB-C502-2R20P, SAB-C502-2RN, SAB-C502-2RP, SAB-C502-L20N Datasheet

...

Data Sheet 08.94

Microcomputer Components

C502

8-Bit CMOS Microcontroller

http://www.siemens.de/

Semiconductor/

Semiconductor Group 1 08.94

8-Bit CMOS Microcontroller

Preliminary

C502

●

Fully compatible to standard 8051 microcontroller

●

Versions for 12 / 20 MHz operating frequency

● 16 K × 8 ROM (SAB-C502-2R only)

●

256 × 8 RAM

●

256 × 8 XRAM (additional on-chip RAM)

●

Eight datapointers for indirect addressing of program and external data memory

(including XRAM)

●

Four 8-bit ports

●

Three 16 -bit Timers / Counters (Timer 2 with Up/Down Counter feature)

● USART with programmable 10-bit Baudrate-Generator

●

Six interrupt sources, two priority levels

●

Programmable 15-bit Watchdog Timer

●

Oscillator Watchdog

●

Fast Power On Reset

●

Power Saving Modes

●

P-DIP-40 package and P-LCC-44 package

● Temperature ranges: SAB-C502

T

A

: 0 ˚C to 70 ˚C

SAF-C502

T

A

: – 40 ˚C to 85 ˚C

SAB-C502

Semiconductor Group 2

C502

The SAB-C502-L/C502-2R described in this document is compatible with the SAB 80C52 and can

be used for all present SAB 80C52 applications.

The SAB-C502-2R contains a non-volatile 16 K × 8 read-only program memory, a volatile 256 × 8

read/write data memory, four ports, three 16-bit timers/counters, a six source, two priority level

interrupt structure, a serial port and versatile fail save mechanisms. The SAB-C502-L/C502-2R

incorporates 256 × 8 additional on-chip RAM called XRAM. For higher performance eight

datapointers are implemented. The SAB-C502-L is identical, except that it lacks the program

memory on chip. Therefore the term SAB-C502 refers to both versions within this specification

unless otherwise noted.

Semiconductor Group 3

C502

Ordering Information

Note:Extended temperature range – 40 ˚C to 110 ˚C (SAH-C502) on request.

Type Ordering

Code

Package Description

(8-Bit CMOS microcontroller)

SAB-C502-LN

SAB-C502-LP

Q67120-C838

Q67120-C889

P-LCC-44

P-DIP-40

for external memory 12 MHz

SAB-C502-2RN

SAB-C502-2RP

Q67120-C839

Q67120-C890

P-LCC-44

P-DIP-40

with mask-programmable ROM,

12 MHz

SAB-C502-L20N

SAB-C502-L20P

Q67120-C885

Q67120-C891

P-LCC-44

P-DIP-40

for external memory 20 MHz

SAB-C502-2R20N

SAB-C502-2R20P

Q67120-C884

Q67120-C892

P-LCC-44

P-DIP-40

with mask-programmable ROM,

20 MHz

SAF-C502-LN

SAF-C502-LP

Q67120-C883

Q67120-C893

P-LCC-44

P-DIP-40

for external ROM, 12 MHz,

ext. temp. – 40 ˚C to 85 ˚C

SAF-C502-2RN

SAF-C502-2RP

Q67120-C886

Q67120-C894

P-LCC-44

P-DIP-40

with mask-programmable ROM,

12 MHz, ext. temp. – 40 ˚C to 85 ˚C

SAF-C502-L20N

SAF-C502-L20P

Q67120-C887

Q67120-C895

P-LCC-44

P-DIP-40

for external memory, 20 MHz,

ext. temp. – 40 ˚C to 85 ˚C

SAF-C502-2R20N

SAF-C502-2R20P

Q67120-C888

Q67120-C896

P-LCC-44

P-DIP-40

with mask-programmable ROM,

20 MHz, ext. temp. – 40 ˚C to 85 ˚C

Semiconductor Group 4

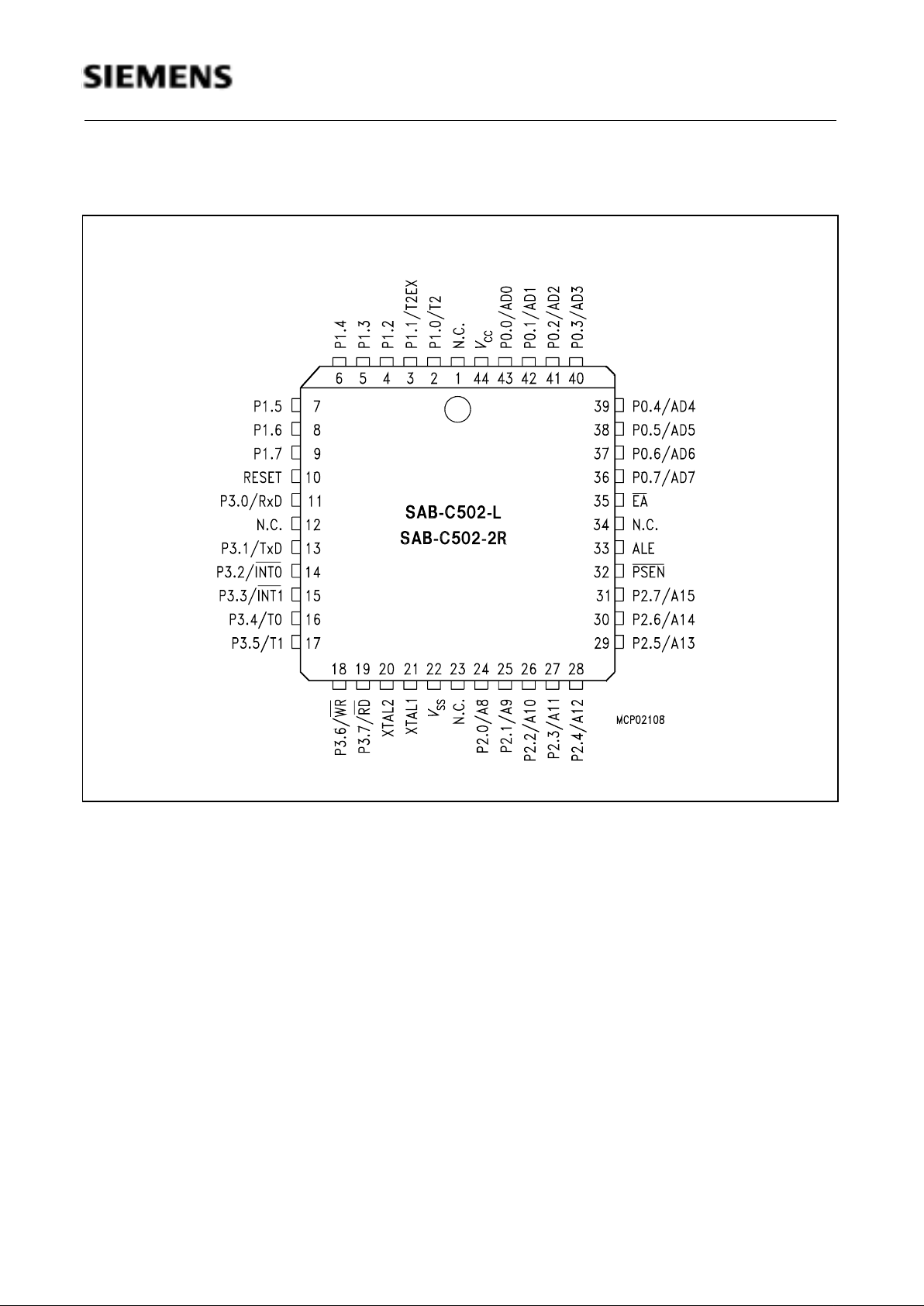

Pin Configuration

(top view)

(P-LCC-44)

C502

Semiconductor Group 5

C502

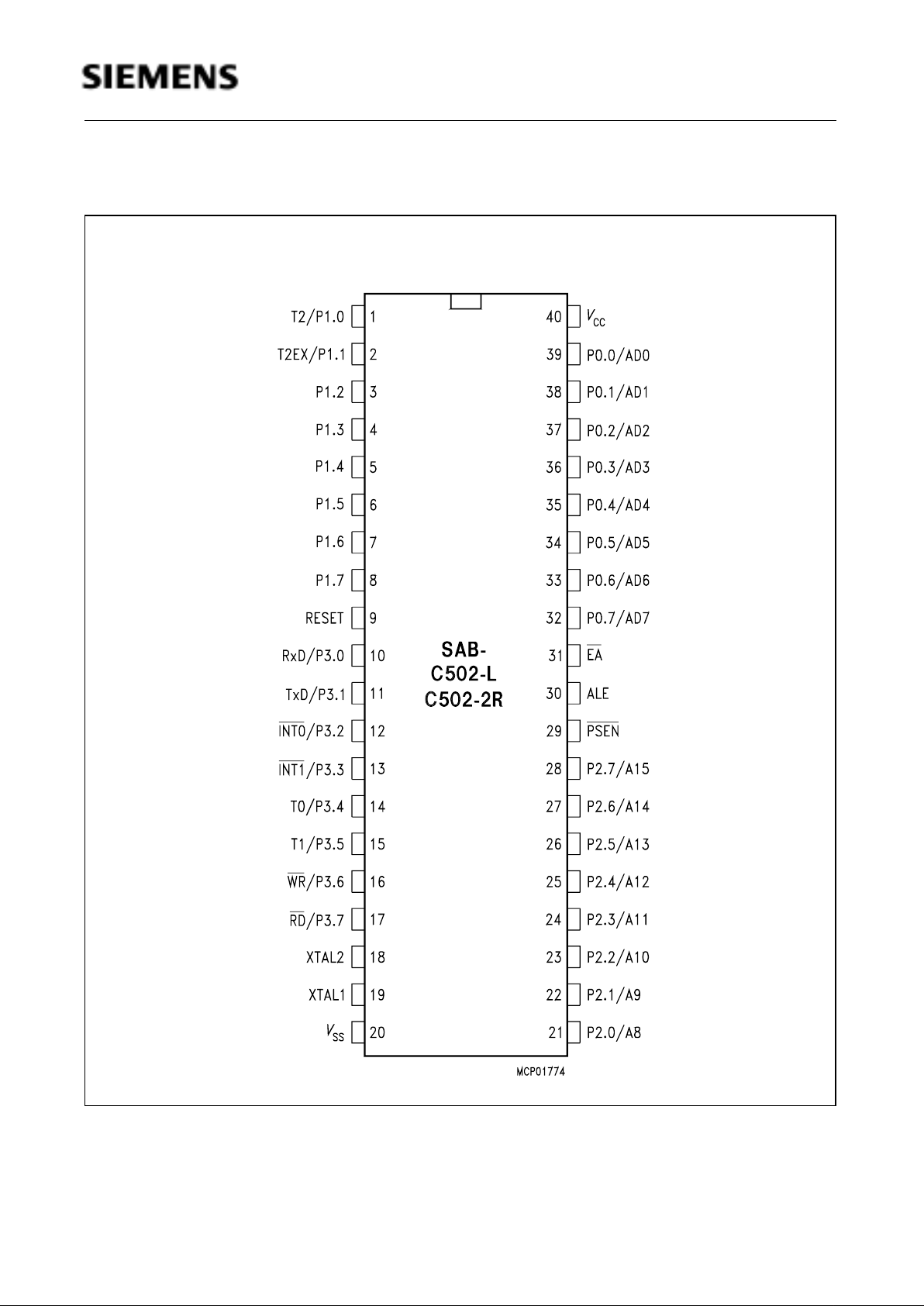

Pin Configuration

(top view)

(P-DIP-40)

Semiconductor Group 6

Logic Symbol

C502

Semiconductor Group 7

C502

Pin Definitions and Functions

Symbol Pin Number I/O*) Function

P-LCC-44 P-DIP-40

P1.7 – P1.0 9–2

2

3

8–1

1

2

I Port 1

is a bidirectional I/O port with internal pull-up

resistors. Port 1 pins that have 1s written to

them are pulled high by the internal pull-up

resistors, and in that state can be used as

inputs. As inputs, port 1 pins being externally

pulled low will source current (

I

IL

, in the DC

characteristics) because of the internal pull-up

resistors. Port 1 also contains the timer 2 pins

as secondary function. The output latch corresponding to a secondary function must be programmed to a one (1) for that function to

operate.

The secondary functions are assigned to the

pins of port 1, as follows:

P1.0 T2 Input to counter 2

P1.1 T2EX Capture - Reload trigger of

timer 2 / Up-Down count

*) I = Input

O = Output

Semiconductor Group 8

P3.0 – P3.7 11, 13–19

11

13

14

15

16

17

18

19

10–17

10

11

12

13

14

15

16

17

I/O Port 3

is a bidirectional I/O port with internal pull-up

resistors. Port 3 pins that have 1s written to

them are pulled high by the internal pull-up

resistors, and in that state can be used as

inputs. As inputs, port 3 pins being externally

pulled low will source current (I

IL

, in the DC

characteristics) because of the internal pull-up

resistors. Port 3 also contains the interrupt,

timer, serial port 0 and external memory strobe

pins that are used by various options. The output latch corresponding to a secondary function must be programmed to a one (1) for that

function to operate.

The secondary functions are assigned to the

pins of port 3, as follows:

P3.0 R×D receiver data input

(asynchronous) or data input/

output (synchronous) of serial

interface 0

P3.1 T×D transmitter data output

(asynchronous) or clock output

(synchronous) of the serial

interface 0

P3.2 INT0

interrupt 0 input/timer 0 gate

control

P3.3 INT1 interrupt 1 input/timer 1 gate

control

P3.4 T0 counter 0 input

P3.5 T1 counter 1 input

P3.6 WR the write control signal latches

the data byte from port 0 into the

external data memory

P3.7 RD the read control signal enables

the external data memory to

port 0

XTAL2 20 18 – XTAL2

Output of the inverting oscillator amplifier

*)I = Input

O = Output

Pin Definitions and Functions (cont’d)

Symbol Pin Number I/O*) Function

P-LCC-44 P-DIP-40

C502

Semiconductor Group 9

C502

XTAL1 21 19 – XTAL1

Input to the inverting oscillator amplifier and

input to the internal clock generator circuits.

To drive the device from an external clock

source, XTAL1 should be driven, while XTAL2

is left unconnected. There are no requirements

on the duty cycle of the external clock signal,

since the input to the internal clocking circuitry

is divided down by a divide-by-two flip-flop.

Minimum and maximum high and low times as

well as rise fall times specified in the AC

characteristics must be observed.

P2.0 – P2.7 24–31 21–28 I/O Port 2

ia a bidirectional I/O port with internal pull-up

resistors. Port 2 pins that have 1s written to

them are pulled high by the internal pull-up

resistors, and in that state can be used as

inputs. As inputs, port 2 pins being externally

pulled low will source current (

I

IL

, in the DC

characteristics) because of the internal pull-up

resistors. Port 2 emits the high-order address

byte during fetches from external program

memory and during accesses to external data

memory that use 16-bit addresses (MOVX

@DPTR). In this application it uses strong

internal pull-up resistors when issuing 1s.

During accesses to external data memory that

use 8-bit addresses (MOVX @Ri), port 2

issues the contents of the P2 special function

register.

PSEN

32 29 O The Program Store Enable

output is a control signal that enables the

external program memory to the bus during

external fetch operations. It is activated every

six oscillator periodes except during external

data memory accesses. Remains high during

internal program execution.

*) I = Input

O = Output

Pin Definitions and Functions (cont’d)

Symbol Pin Number I/O*) Function

P-LCC-44 P-DIP-40

Semiconductor Group 10

RESET 10 9 I RESET

A high level on this pin for two machine cycles

while the oscillator is running resets the

device. An internal diffused resistor to V

SS

permits power-on reset using only an external

capacitor to

V

CC

.

ALE 33 30 O The Address Latch Enable

output is used for latching the low-byte of the

address into external memory during normal

operation. It is activated every six oscillator

periodes except during an external data

memory access.

EA

35 31 I External Access Enable

When held at high level, instructions are

fetched from the internal ROM (SAB-C502-2R

only) when the PC is less than 4000H. When

held at low level, the SAB-C502 fetches all

instructions from external program memory.

For the SAB-C502-L this pin must be tied low.

P0.0 – P0.7 43–36 39–32 I/O Port 0

is an 8-bit open-drain bidirectional I/O port.

Port 0 pins that have 1s written to them float,

and in that state can be used as highimpedance inputs. Port 0 is also the

multiplexed low-order address and data bus

during accesses to external program or data

memory. In this application it uses strong

internal pull-up resistors when issuing 1s.

Port 0 also outputs the code bytes during

program verification in the SAB-C502-2R.

External pull-up resistors are required during

program verification.

V

SS

22 20 – Circuit ground potential

V

CC

44 40 – Supply terminal for all operating modes

N.C. 1, 12,

23, 34

––No connection

*) I = Input

O = Output

Pin Definitions and Functions (cont’d)

Symbol Pin Number I/O*) Function

P-LCC-44 P-DIP-40

C502

Semiconductor Group 11

C502

Functional Description

The SAB-C502 is fully compatible to the standard 8051 microcontroller family.

It is compatible with the SAB 80C52. While maintaining all architectural and operational

characteristics of the SAB 80C52 the SAB-C502 incorporates some enhancements in the Timer2

and Fail Save Mechanism Unit.

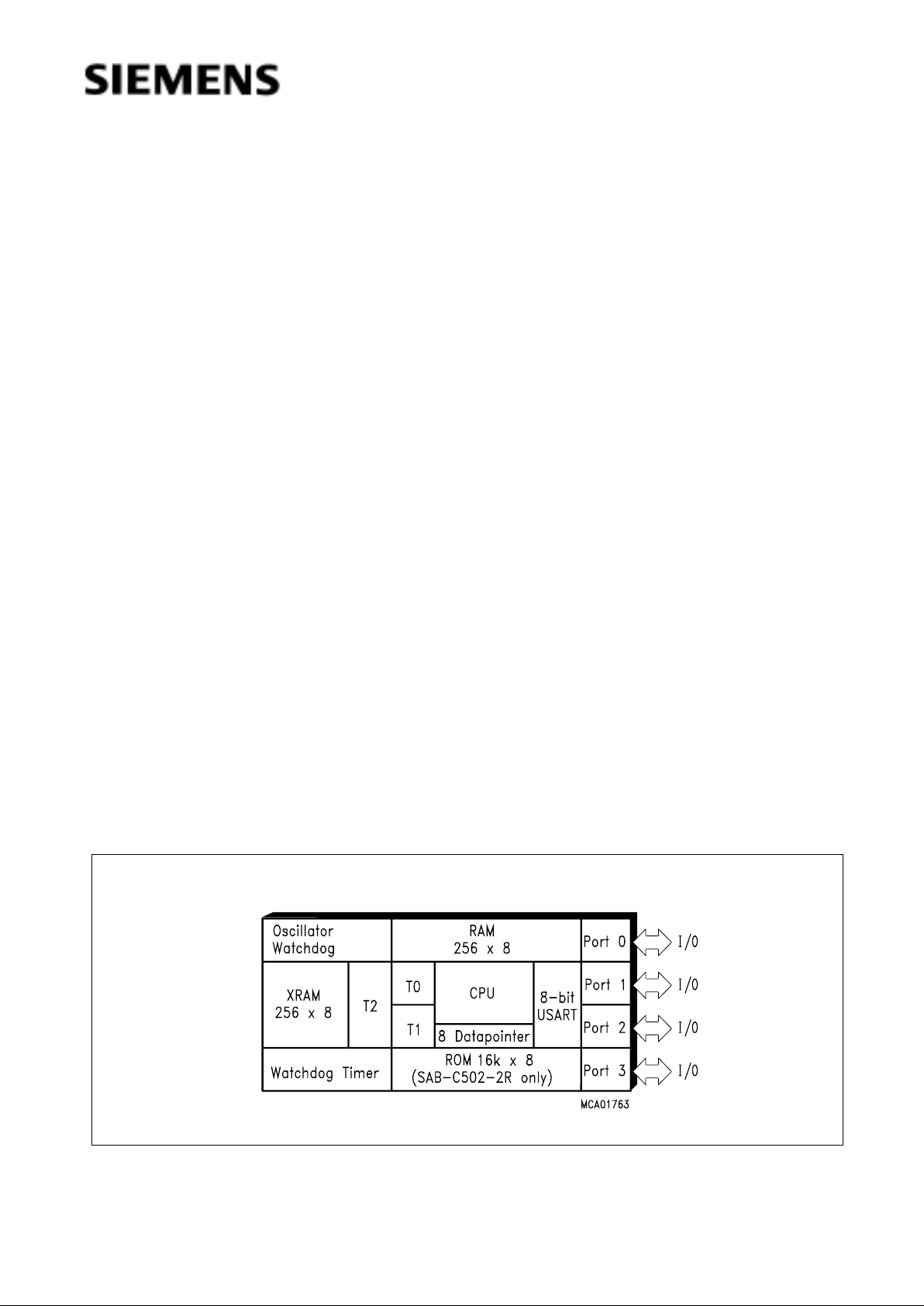

Figure 1 shows a block diagram of the SAB-C502.

Figure 1

Block Diagram of the SAB-C502

Semiconductor Group 12

CPU

The SAB-C502 is efficient both as a controller and as an arithmetic processor. It has extensive

facilities for binary and BCD arithmetic and excels in its bit-handling capabilities. Efficient use of

program memory results from an instruction set consisting of 44 % one-byte, 41 % two-byte, and

15 % three-byte instructions. With a 12 MHz crystal, 58 % of the instructions execute in 1.0 µs

(18 MHz : 667 ns).

Special Function Register PSW

Reset value of PSW is 00H.

Bit Function

CY Carry Flag

AC Auxiliary Carry Flag (for BCD operations)

F0 General Purpose Flag

RS1 RS0

00

01

10

11

Register Bank select control bits

Bank 0 selected, data address 00H - 07

H

Bank 1 selected, data address 08H - 0F

H

Bank 2 selected, data address 10H - 17

H

Bank 3 selected, data address 18H - 1F

H

OV Overflow Flag

F1 General Purpose Flag

P Parity Flag.

Set/cleared by hardware each instruction cycle to indicate an odd/

even number of “one” bits in the accumulator, i.e. even parity.

CY AC F0 RS1 RS0 OV F1 P

MSB LSB

76543210

Addr. D0

H

PSW

Bit No.

C502

Semiconductor Group 13

C502

Special Function Registers

All registers, except the program counter and the four general purpose register banks, reside in the

special function register area.

The 36 special function register (SFR) include pointers and registers that provide an interface

between the CPU and the other on-chip peripherals. There are also 128 directly addressable bits

within the SFR area.

All SFRs are listed in table 1, table 2 and table 3. In table 1 they are organized in numeric order

of their addresses. In table 2 they are organized in groups which refer to the functional blocks of the

SAB-C502. Table 3 illustrates the contents of the SFRs.

Table 1

Special Function Register in Numeric Order of their Addresses

1)

: Bit-addressable Special Function Register

2)

: X means that the value is indeterminate and the location is reserved

Address Register Contents

after Reset

Address Register Contents

after Reset

80

H

81

H

82

H

83

H

84

H

85

H

86

H

87

H

P0

1)

SP

DPL

DPH

reserved

reserved

WDTREL

PCON

FF

H

07

H

00

H

00

H

00

H

000X0000

B

2)

98

H

99

H

9A

H

9B

H

9C

H

9D

H

9E

H

9F

H

SCON

1)

SBUF

reserved

reserved

reserved

reserved

reserved

reserved

00

H

XX

H

2)

XX

H

2)

XX

H

2)

XX

H

2)

XX

H

2)

XX

H

2)

XX

H

2)

88

H

89

H

8A

H

8B

H

8C

H

8D

H

8E

H

8F

H

TCON

1)

TMOD

TL0

TL1

TH0

TH1

reserved

reserved

00

H

00

H

00

H

00

H

00

H

00

H

XX

H

2)

XX

H

2)

A0

H

A1

H

A2

H

A3

H

A4

H

A5

H

A6

H

A7

H

P2

1)

reserved

reserved

reserved

reserved

reserved

reserved

reserved

FF

H

XX

H

2)

XX

H

2)

XX

H

2)

XX

H

2)

XX

H

2)

XX

H

2)

XX

H

2)

90

H

91

H

92

H

93

H

94

H

95

H

96

H

97

H

P1

1)

XPAGE

DPSEL

reserved

XCON

reserved

reserved

reserved

FF

H

00

H

XXXXX000

B

2)

XX

H

2)

F8

H

XX

H

2)

XX

H

2)

XX

H

2)

A8

H

A9

H

AA

H

AB

H

AC

H

AD

H

AE

H

AF

H

IE

1)

reserved

SRELL

reserved

reserved

reserved

reserved

reserved

0X000000

B

2)

XX

H

2)

D9

H

XX

H

2)

XX

H

2)

XX

H

2)

XX

H

2)

XX

H

2)

Loading...

Loading...