ICs for Communications

Analog Line Interface Solution

ALIS

PSB 4595 Version 2.1

PSB 4596 Version 2.1

Data Sheet 06.98

DS 1

ALIS

Revision History: Current Version: 06.98

Previous Version:

Page

(in previous

Version)

Edition 06.98

This edition was realized using the software system FrameMaker

Published by Siemens AG,

HL AT

Page

(in new

Version)

Subjects (major changes since last revision)

.

© Siemens AG 1998.

All Rights Reserved.

Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for

applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact t he Semiconductor Group Offices in Germany or

the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in

question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales

office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice

you for any costs incurred.

Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components

systems

1 A critical component is a component used in a life-support device or system whose failure can reasonably be

2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or

2

with the express written approval of the Semiconductor Group of Siemens AG.

expected to cause the failure of that life-support device or system, or to affect its safety or effec tiveness of that

device or system.

maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

1

of the Semiconductor Group of Siemens AG, may only be used in life-support devices or

PSB 4595 / PSB 4596

Analog Line Interface Solution

Table of Contents Page

1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

1.2 Logic Symbol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

2 Pin Definition and Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

2.1 Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

2.2 Pin Definition of ALIS-A PSB 4595 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

2.3 Pin Definition of ALIS-D PSB 4596 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

3 System Integration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

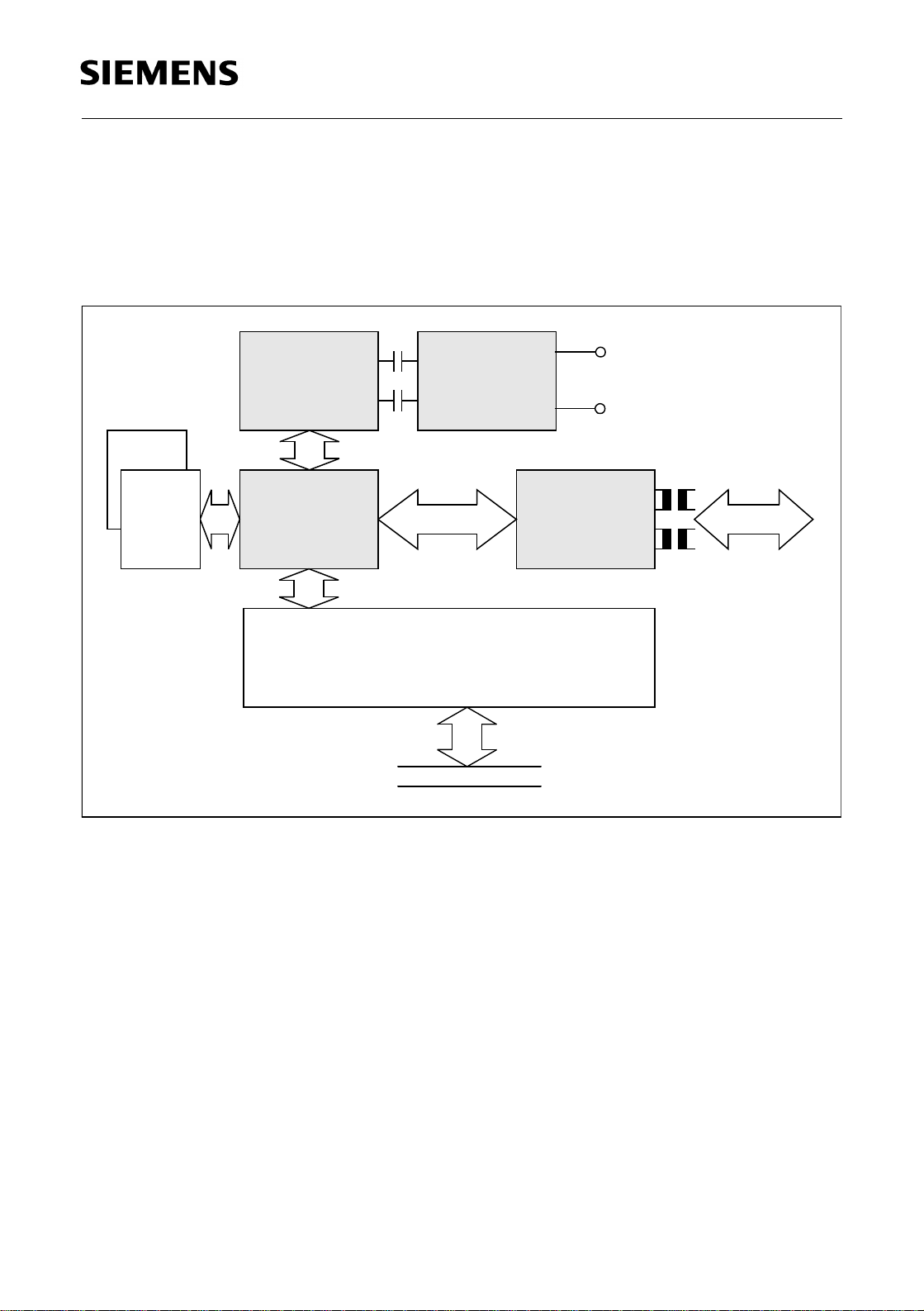

3.1 ALIS with DSP-based Modem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

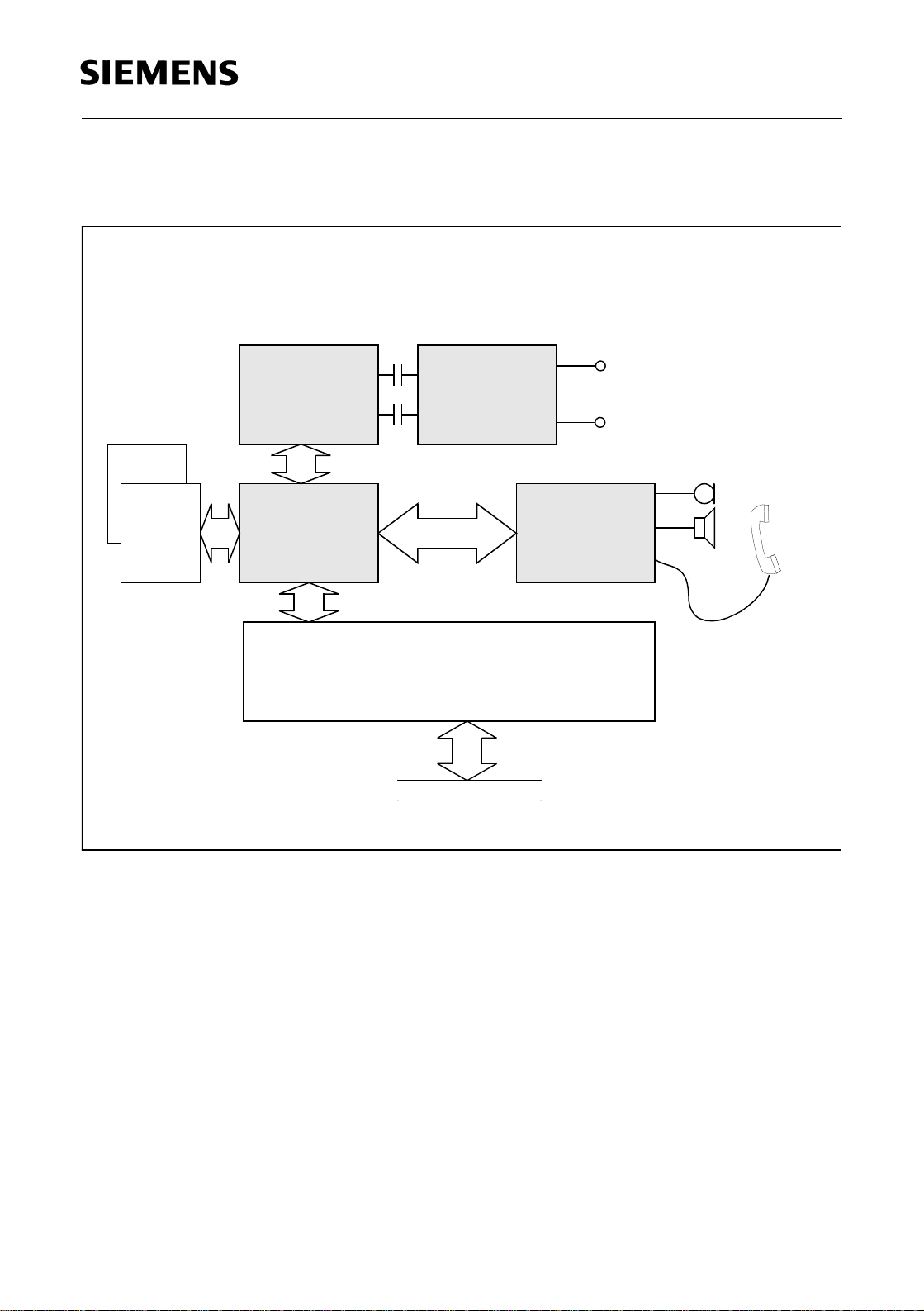

3.2 ALIS with Software Modem . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

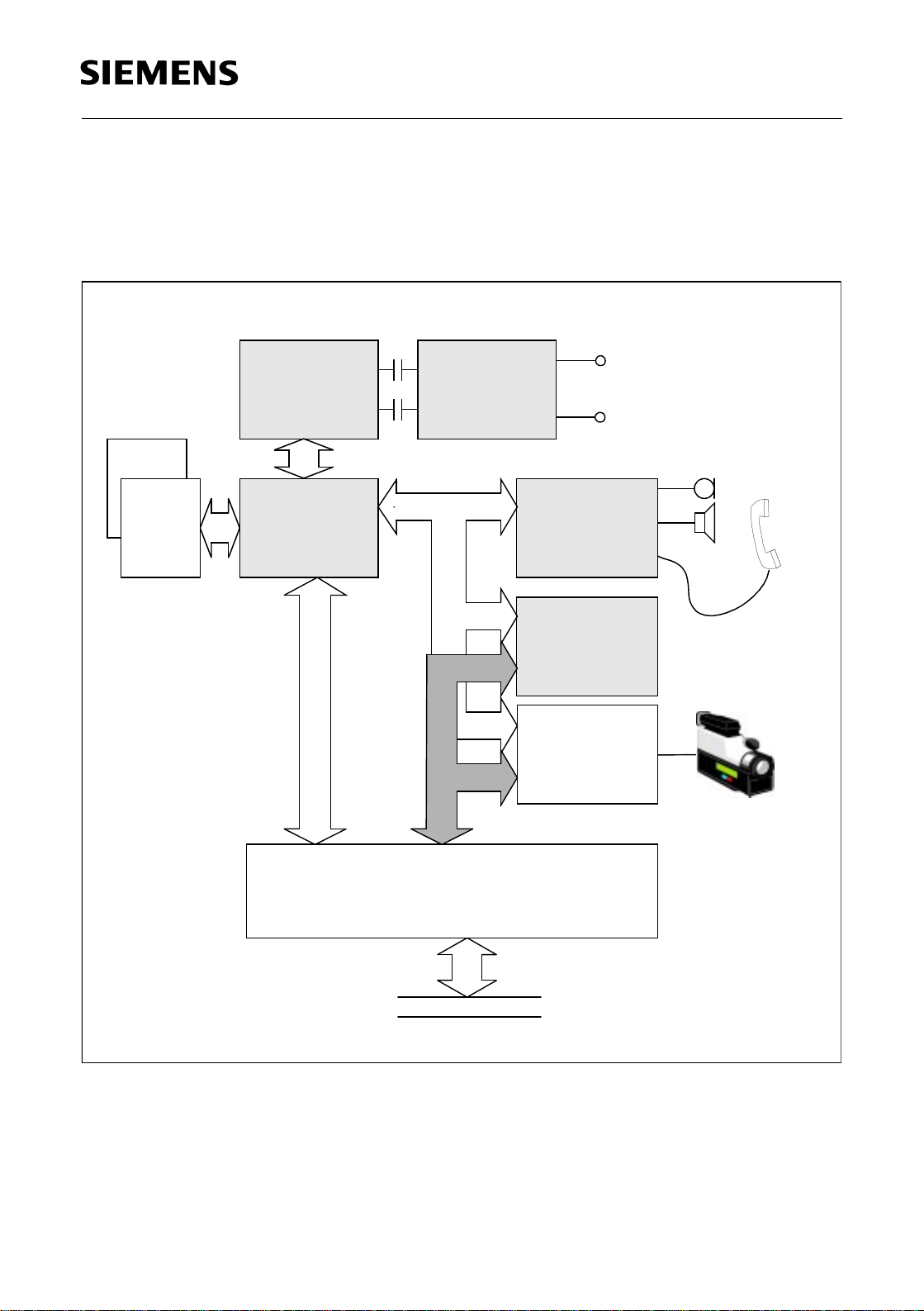

3.3 Hybrid Modem (ISDN plus Analog) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

3.4 Modem with Speakerphone . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

3.5 Analog Videophone . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

4 ALIS Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

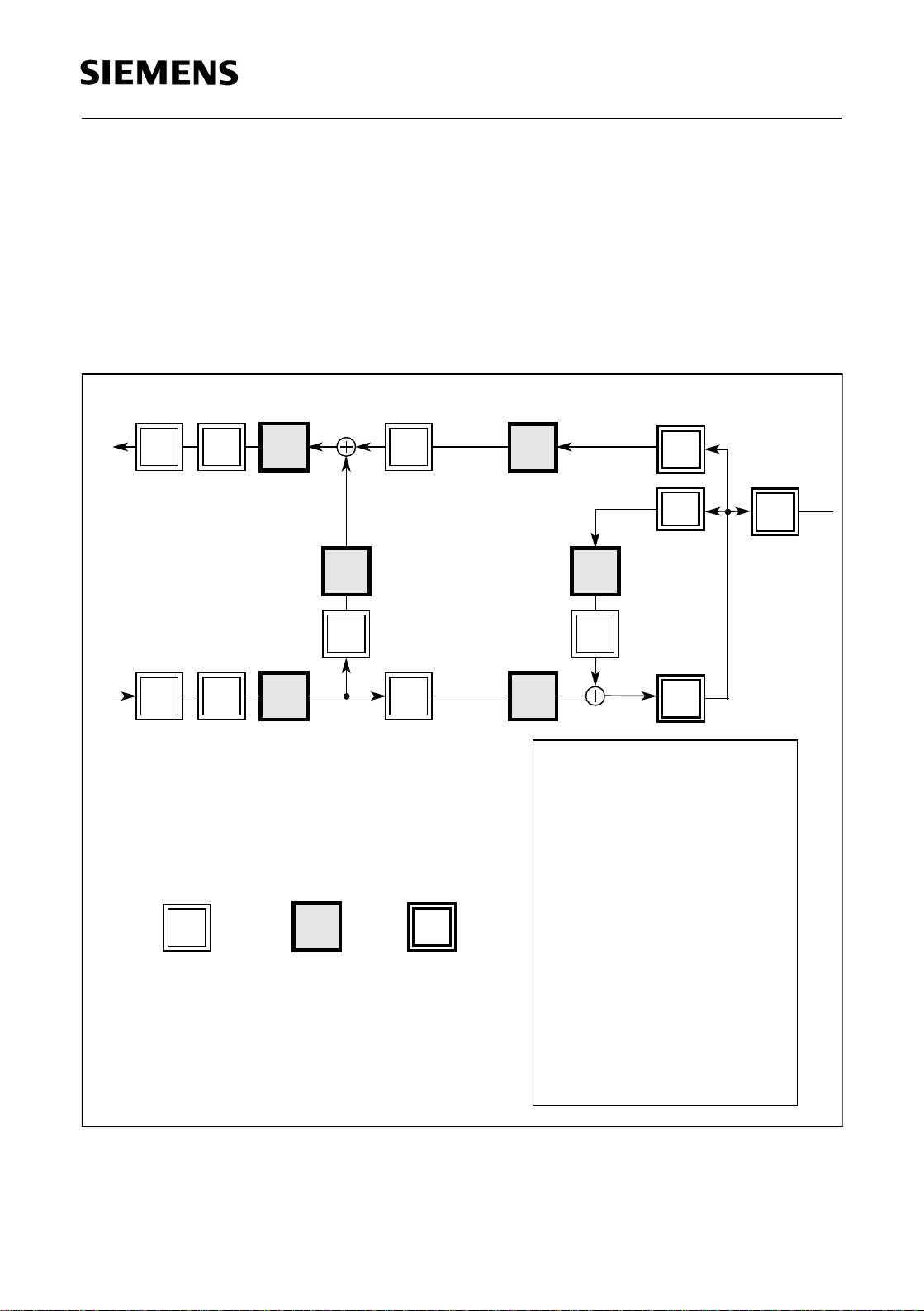

4.1 ALIS Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

4.2 ALIS AC Signal Flow Graph . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

4.2.1 Receive Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

4.2.2 Transmit Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

4.2.3 Loops . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

4.2.4 Test Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

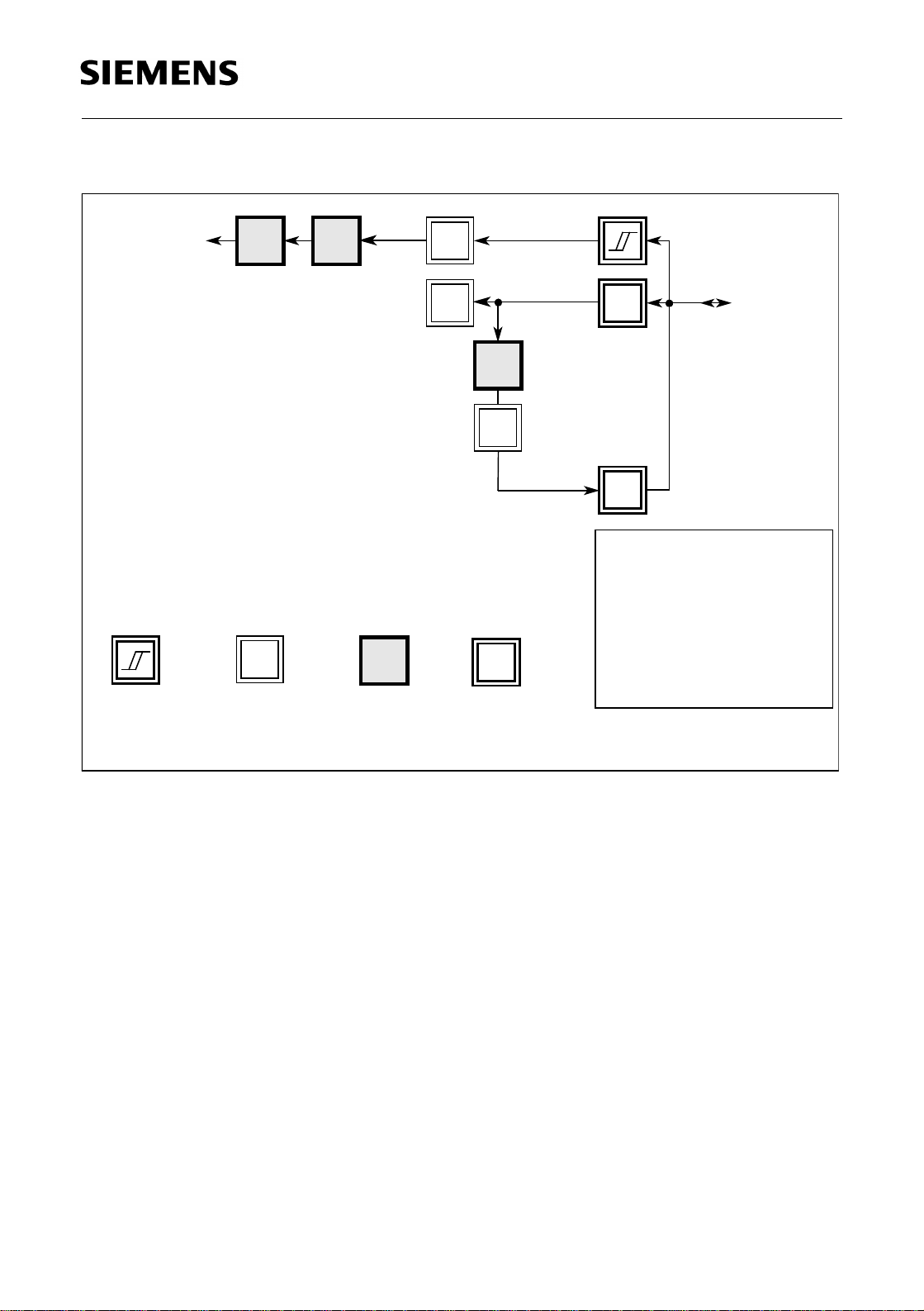

4.3 ALIS Ring and Caller ID Signal Flow Graph . . . . . . . . . . . . . . . . . . . . . . . . .23

4.3.1 Caller ID (CID) Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

4.3.2 Ring-Level Metering (RLM) Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

4.3.3 Loops . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

4.3.3.1 Test Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

5 Configuration Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

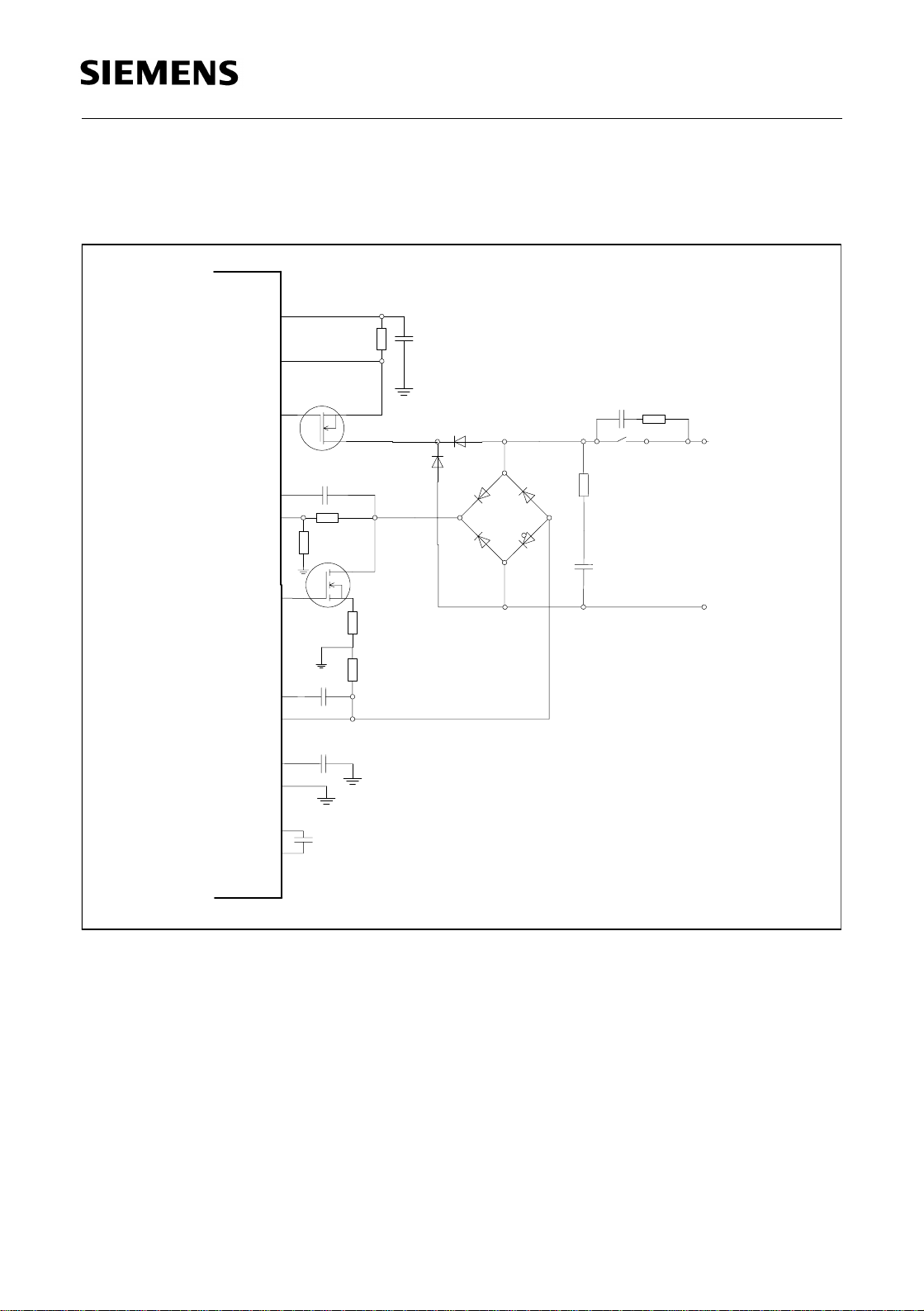

5.1 Connection to the Telephone Line . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

5.2 Host Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

5.2.1 The µ-Controller Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

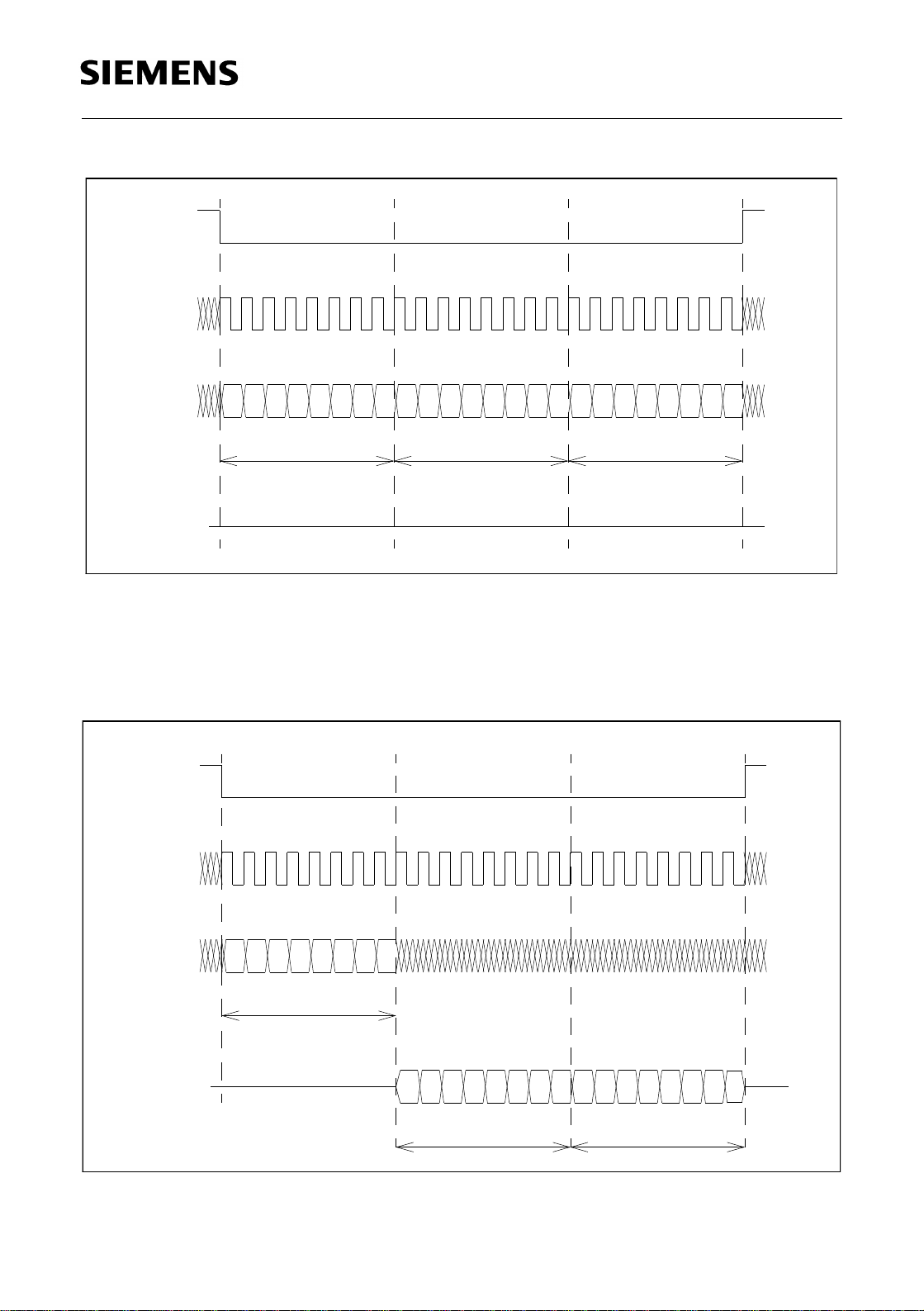

5.2.2 The Data Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

5.2.3 Interface Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

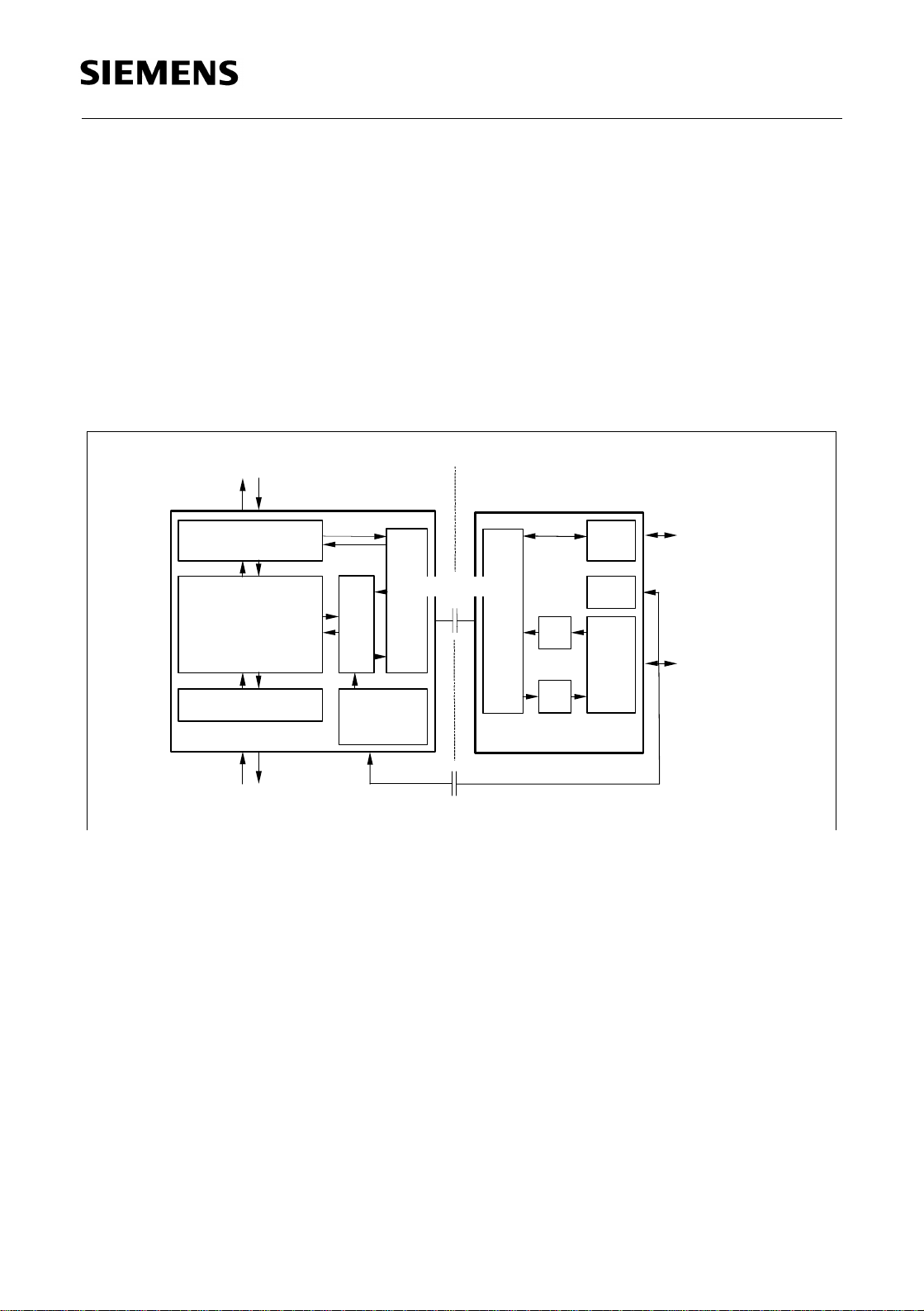

5.2.3.1 Demux Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

5.2.3.2 Multiplex Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

5.3 Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

5.3.1 External clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

5.3.2 Crystal clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

5.4 Capacitor Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

5.5 Caller ID Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

6 Programming ALIS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Semiconductor Group 3 Data Sheet 06.98

PSB 4595 / PSB 4596

Analog Line Interface Solution

Table of Contents Page

6.1 Types of Commands and Data Bytes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

6.1.1 Storage of Programming Information: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

6.2 SOP Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

6.2.1 CR0 Configuration Register 0 (Filters) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

6.2.2 CR1 Configuration Register 1 (Dialing) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

6.2.3 CR2 Configuration Register 2 (Caller ID) . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

6.2.4 CR3 Configuration Register 3 (Test Loops) . . . . . . . . . . . . . . . . . . . . . . . . . .42

6.2.5 CR4 Configuration Register 4 (Analog Ga in) . . . . . . . . . . . . . . . . . . . . . . . . .4 3

6.2.6 CR5 Configuration Register 5 (Version) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

6.3 XOP Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

6.3.1 XR0 Extended Register 0 (Interrupt Register) . . . . . . . . . . . . . . . . . . . . . . . .4 4

6.3.2 XR1 Extended Register 1 (Interru pt Enable Register) . . . . . . . . . . . . . . . . . .46

6.3.3 XR2 Extended Register 2 (Cadence Time Out) . . . . . . . . . . . . . . . . . . . . . . .47

6.3.4 XR3 Extended Register 3 (DC Characteristic) . . . . . . . . . . . . . . . . . . . . . . . .47

6.3.5 XR4 Extended Register 4 (Cadence) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

6.3.6 XR5 Extended Register 5 (Ring Timer) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

6.3.7 XR6 Extended Register 6 (Power State) . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

6.3.8 XR7 Extended Register 7 (Vdd) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

6.4 COP Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

6.5 CAO Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

6.6 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

6.6.1 CR Registers: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

6.6.2 XR Registers: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

7 ALIS Command Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

7.1 SOP Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

7.1.1 SOP - Write Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

7.1.2 SOP - Read Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

7.2 XOP Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

7.2.1 XOP - Write Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

7.2.2 XOP - Read Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

7.3 COP Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

7.3.1 COP - Write Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

7.3.2 COP - Read Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

7.4 CAO Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

7.4.1 CAO - Write Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

7.4.2 CAO - Read Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

7.5 Example of a Mixed Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

8 Interrupt Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

8.1 Nature and Sources of Interrupts: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

8.1.1 Interrupt Indication at Signal Change: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

8.1.2 Interrupt Indication at Event: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

Semiconductor Group 4 Data Sheet 06.98

PSB 4595 / PSB 4596

Analog Line Interface Solution

Table of Contents Page

8.1.3 Interrupt Indication at High Level: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

9 Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

9.1 Reset (Basic Settings Mode) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

9.2 Deep Sleep Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

9.3 Sleep Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

9.4 Ringing Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

9.5 Conversation Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

9.6 Pulse Dialing Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

9.7 Operating Flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

9.8 Flow of Ring Sequence and Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

9.8.1 Successful Ring Sequence, Auto Ring Enabl ed, no Caller ID . . . . . . . . . . . .67

9.8.2 Successful Ring Sequence, Auto Ring En abled, Caller ID . . . . . . . . . . . . . .68

9.8.3 Unsuccessful Ring Sequence, Auto Ring Enabled, no Caller ID . . . . . . . . . .6 9

9.8.4 Unsuccessful Ring Sequence, Auto Ring Enabled, Caller ID . . . . . . . . . . . .70

9.8.5 Successful Ring Sequence, Auto Ring Disabled, No Calle r ID . . . . . . . . . . .71

9.8.6 Successful Ring Sequence, Auto Ring Disabled, Calle r ID . . . . . . . . . . . . . .72

9.8.7 Unsuccessful Ring Sequence, Auto Ring Disabled, no Caller ID . . . . . . . . .73

9.8.8 Unsuccessful Ring Sequence, Auto Ring Disabled, Caller ID . . . . . . . . . . . .74

9.8.9 Unsuccessful Ring Sequence, Auto Ring Enabled . . . . . . . . . . . . . . . . . . . .75

9.8.10 Unsuccessful Ring Sequence, Auto Ring Disabled . . . . . . . . . . . . . . . . . . . .76

9.8.11 Start from Deep Sleep Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .77

10 Modem Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78

10.1 Pulse Dialing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78

10.2 DTMF Dialing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78

10.2.1 Programming the ALIS DTMF Tone Generators . . . . . . . . . . . . . . . . . . . . . .78

10.3 Caller ID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

10.3.1 Characteristics for Caller ID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

10.3.2 Storage and Reading of Caller ID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 0

10.3.3 Programming the ALIS Caller ID Coefficients . . . . . . . . . . . . . . . . . . . . . . . .81

10.4 Billing Pulse . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 1

10.5 Ring Detect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

10.5.1 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

10.5.2 Programming the ALIS Ring Detect Coefficients . . . . . . . . . . . . . . . . . . . . . .82

10.5.3 Ring Threshold in Sleep Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .82

11 Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .83

11.1 Programmable Filters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .83

11.2 DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .83

11.2.1 DC Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .84

11.2.2 Programming Ranges for DC Termination . . . . . . . . . . . . . . . . . . . . . . . . . . .84

11.2.3 Input Current in Puls Dialing Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

11.3 AC Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

Semiconductor Group 5 Data Sheet 06.98

PSB 4595 / PSB 4596

Analog Line Interface Solution

Table of Contents Page

11.3.1 Ringer Impedance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

11.4 ALIS Caller ID Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .86

11.4.1 Ring Detect Levels and Frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .86

11.5 ALIS Cap Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .86

12 Electrical Performance Characteristic . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

12.1 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

12.2 Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .88

12.3 DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .88

12.3.1 ALIS-A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .88

12.3.2 ALIS-D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

12.4 AC Transmission Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .91

12.4.1 Absolute Gain Error . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .91

12.4.2 Gain Tracking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .92

12.4.3 Harmonic Distortion plus Noise . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .92

12.4.4 Harmonic Distortion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .93

12.4.5 Return Loss . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .93

12.4.6 Frequency Response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .94

12.4.6.1Receive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .94

12.4.6.2Transmit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .95

12.4.7 Group Delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .96

12.4.7.1Group Delay Absolute Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .96

12.4.7.2Group Delay Distortion Receive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .96

12.4.7.3Group Delay Distortion Transmit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .97

12.4.8 Out-of-Band Signals at TIP/RING Receive . . . . . . . . . . . . . . . . . . . . . . . . . .98

12.4.9 Out-of-Band Signals at TIP/RING Transmit . . . . . . . . . . . . . . . . . . . . . . . . . .99

12.4.10 Trans-hybrid Loss . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .100

12.5 AC Timing Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101

12.5.1 Input/ Output Waveform for AC Tests . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101

12.5.2 Reset Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101

12.5.3 Control Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101

12.5.4 Data Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102

12.5.5 Package Outlines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104

Semiconductor Group 6 Data Sheet 06.98

PSB 4595 / PSB 4596

Analog Line Interface Solution

Overview

1 Overview

The PSB 4595 and PSB 4596 two-chip solution forms the complete front end of a modem

or fax machine. This Analog Line Interface S olution (AL IS) consists of a DAA, a codec

and a hybrid circuit, and bridges the gap between the phone line and the data pump. The

analog PSB 4595 is manufactured in low-power BiCMOS technology and the digital PSB

4596 in CMOS technology. The ALIS concept is a fully programmable modem front end

which allows a single design for the worldwide market:

• Adaptation to specific countries and applications is achieved by downloading

appropriate coefficient sets.

• Isolation is achieved by a digital capacitor interface, without a transformer; making the

ALIS particularly suitable for designing PCMCIA modems.

• Thanks to an advan ced digital-filter concept in combination with the programmable

electronic DAA, ALIS provides both excellent transmission performance and high

adaptability. This second-generation digital filter concept also allows maximum

autonomy between the various filter b locks. This performance make s ALIS suitable for

V.34+ and V.90 modem applications.

A minimum number of external components is required to complete the functional range

of ALIS. Its internal precision is based on a very accurate band-gap reference. The

frequency behavi or is determined largely by digital filters which exhibit no fluctuations.

As a result of the ADC and DAC concepts, its linearity is limited only by second-order

parasitic effects.

The ALIS chip set can be easily adapted and connecte d to vario us modem data pumps

or to host-based modem solutions. The flexible digital interface of ALIS allows easy

programming via the modem data pump or a controller.

Siemens offers a range of reference and evaluation tools for the ALIS chip set. For

appropriate tools, please contact your nea rest Siemens representative.

Semiconductor Group 7 Data Sheet 06.98

Analog Line Interface Solution

ALIS

1.1 Features

• ALIS substitutes data access arrangement (DAA),

codec and hybrid

• Ring detecti on: level, frequency and cadence

• Caller ID: detection, decodi ng and storage

• Programmable to different country requirements

• Programma ble DC characteristics

• ALIS supports V.34+ and V.90

• ALIS complies with ETS 300 001 and FCC

requirements

• Isolation by digital cap acitor interface

• Analog part powered from the tip/ring line by an

integrated voltage regulator

• High performance analog-to-digital and digital-toanalog conversion

• DSP-based solution for adapting the transmission

behavior, especially for

- AC impedance matching

- trans-hybrid balancing

- frequency response

- gain

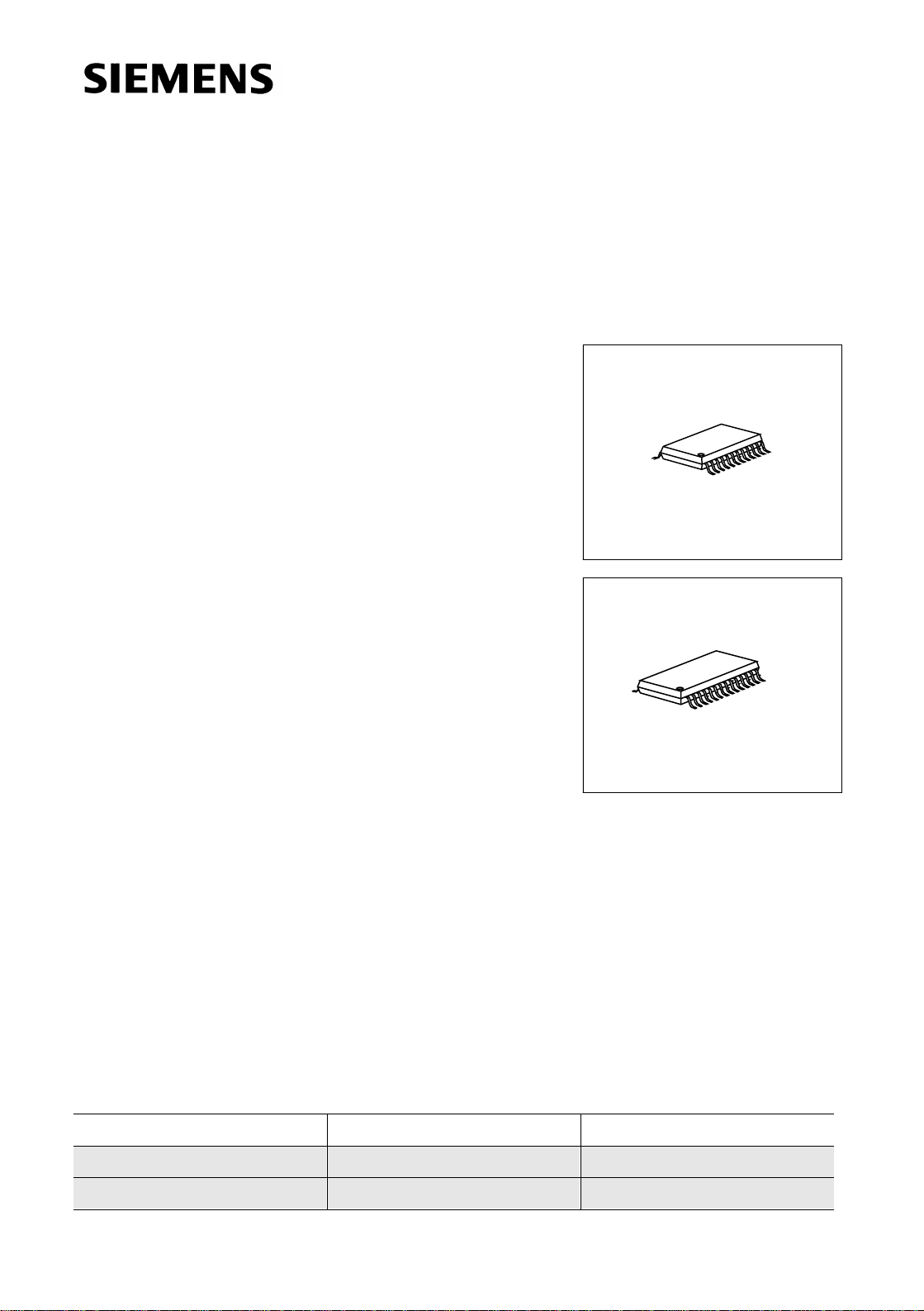

PSB 4595

PSB 4596

CMOS

P-TSSOP24

P-SSOP28

• Advanced test capabilities:

- digital loops

- analog loops

• High-pass fil te r in rece ive path to suppress line interference (50/60 Hz)

• Isolated control pin s for general purpose use

• Advanced low-po wer 0.8µ m analog B ICMOS technolog y for ALIS analog and 0.8µ m

CMOS technology for ALIS digital

• Two-chip solution: the P-TSSOP24 and P-SSOP28 packages are PCMCIA-compliant

Type Ordering Code Package

PSB 4595 V2.1 P-TSSOP24

PSB 4596 V2.1 P-SSOP28

Semiconductor Group 8 Data Sheet 06.98

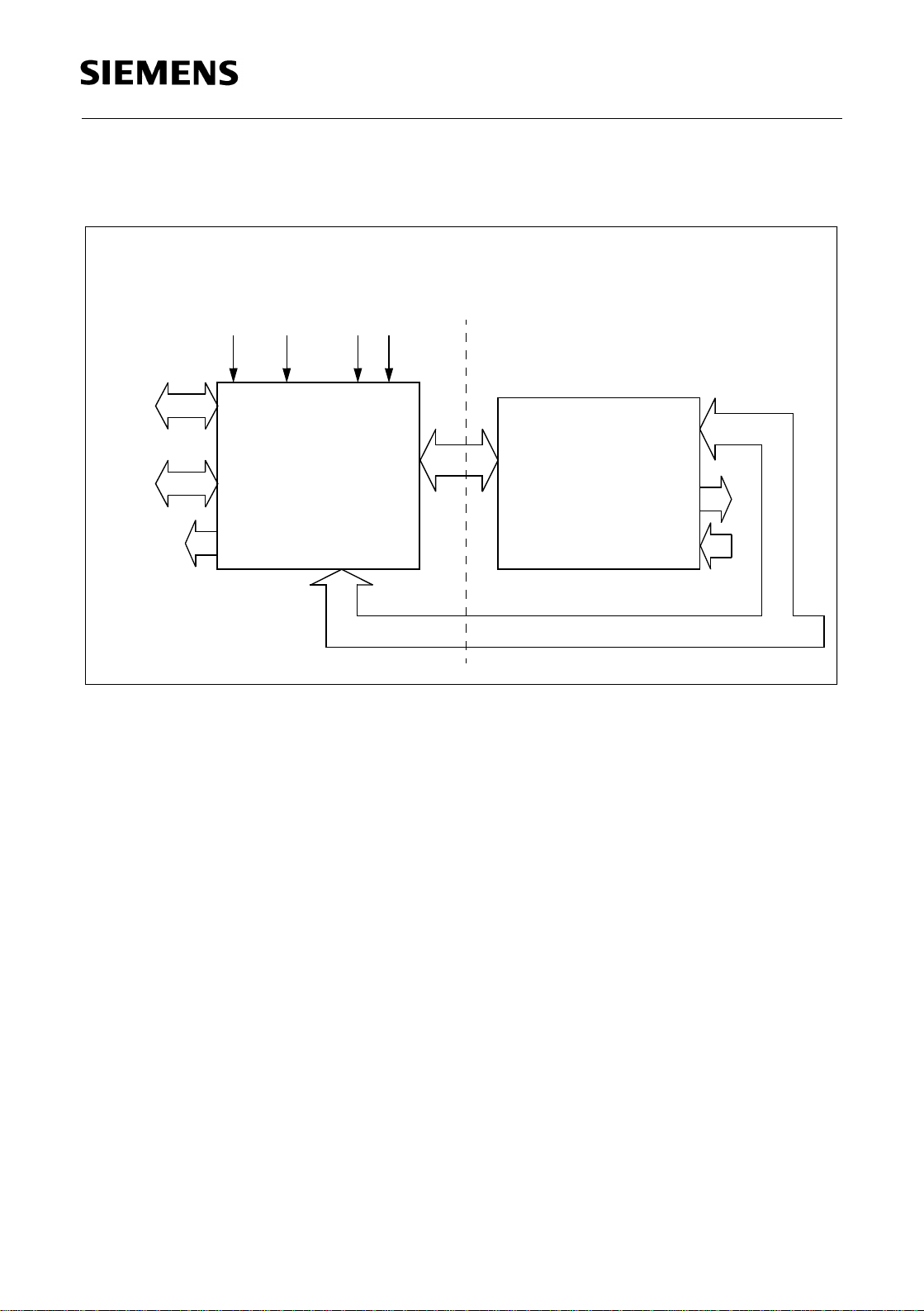

1.2 Logic Symbol

RESETMCLK

Data

Interface

PSB 4595 / PSB 4596

Analog Line Interface Solution

Isolation

VssVdd

Cap

Interface

µC

Interface

ALIS-D

SO

Caller ID

Interface

Figure 1 Logic Symbol of the ALIS Chipset

ALIS _A

ALIS-A

SO

SI

TIP/RING

Semiconductor Group 9 Data Sheet 06.98

2 Pin Definition and Functions

VDD_SENS

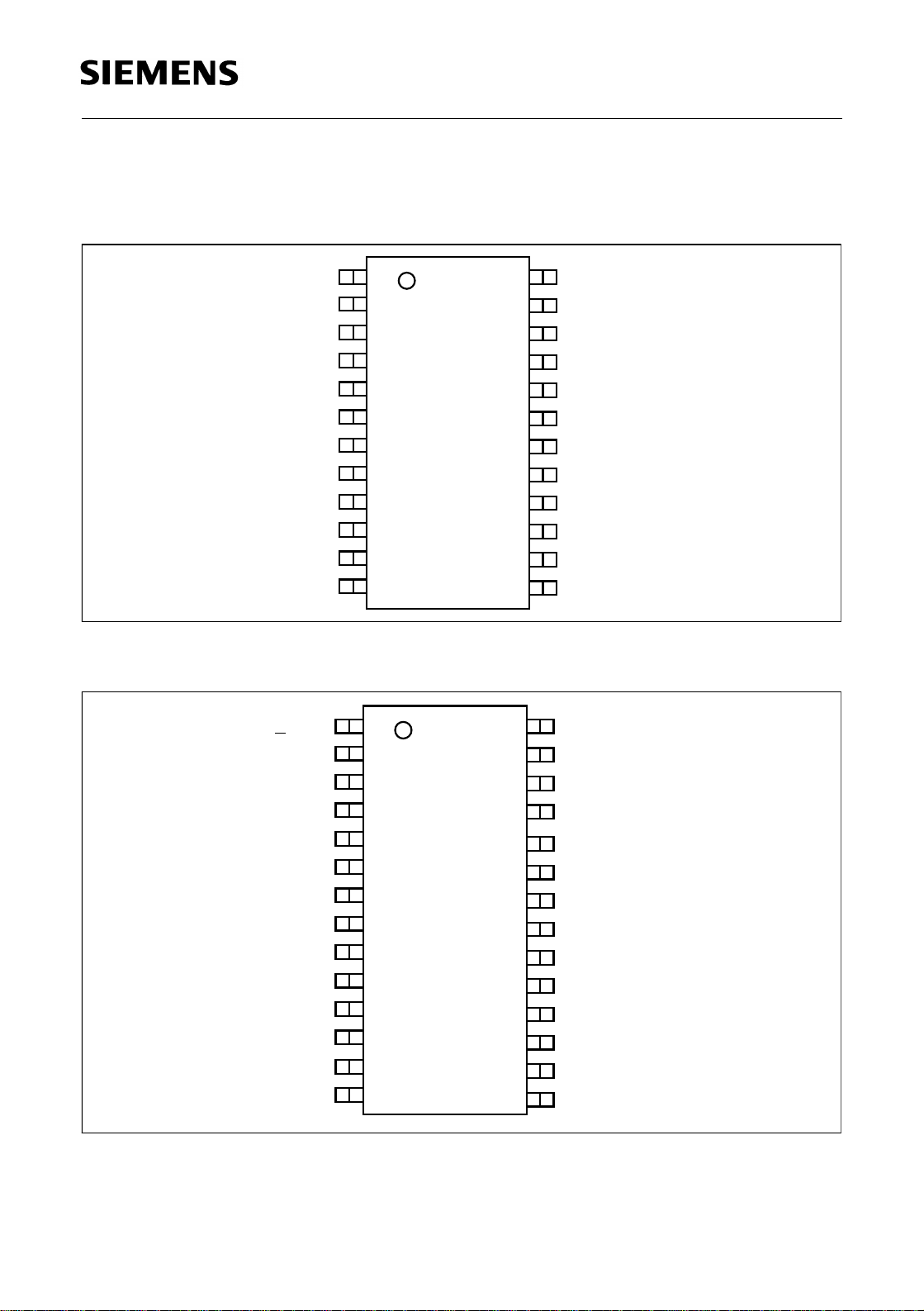

2.1 Pin Configuration

PSB 4595 / PSB 4596

Analog Line Interface Solution

Pin Definition and Functions

CAP1

CAP2

VREF

TIP

TIP_AC

RING

RING_AC

SO_0

SO_1Q

CAP_B22

CAP_B21

CAP_A22

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

Figure 2 Pin Configuration of ALIS-A (Top View)

CAP_A12

CAP_B11

1

2

28

27

GNDA

T1G

VDDA

NC

T2G

SI_0

SI_1

TEST

CAP_C21

CAP_C22

CAP_A21

CAP_A11

CAP_C12

CAP_B12

ID_Ain

Afeedback

ID_Bin

Bfeedback

VDD

GND

CS

DCLK

DIN

DOUT

INT

3

4

5

6

7

8

9

10

11

12

13

14

26

25

24

23

22

21

20

19

18

17

16

15

CAP_C11

VDDA

GNDA

RESET

SO

MCLK1

MCLK2

MODE

DAT_CLK

DAT_IN/SEL

DAT_OUT

FSC

Figure 3 Pin Configuration of ALIS-D (Top View)

Semiconductor Group 10 Data Sheet 06.98

PSB 4595 / PSB 4596

Analog Line Interface Solution

Pin Definition and Functions

2.2 Pin Definition of ALIS-A PSB 4595

Pin No. Symbol Function Descriptions

22 VDDA Power Programmable supply for the circuitry

24 GNDA Power Analog ground: All signals are referred to

this pin

4 TIP I TIP AC+DC sense input

5 TIP_AC I TIP AC sense input

6 RING I RING AC+DC sense input

7 RING_AC I RING AC sense input

23 T1G O Gate for external transistor T1 (AC/DC

control)

19 T2G O Gate for external transistor T2 (VDDA

control)

21 VDD_SENS I VDDA sense input

3 VREF I/O Reference voltage: Must be connected to

GNDA via an external capacito r of more

than 10 nF (typ. 15 nF)

1 CAP1 I/O Pin for external capacitor of more than 1

µ

F for DC filtering to pin Cap2

2 CAP2 I/O See Cap1

18 SI_0 I Auxiliary input pin 0

17 SI_1 I Auxiliary input pin 1

8 SO_0 O Auxiliary output pin 0

9 SO_1Q O Auxiliary output pin 1

16 TEST I Must be connected permanently to GNDA

13 CAP_A21 I Must be connected via a capacitor of more

than 5pF to CAP_A11.

12 CAP_A22 I Must be connected via a capacitor of more

than 5pF to CAP_A12.

11 CAP_B21 O Must be connected via a capacitor of more

than 5pF to CAP_B11.

10 CAP_B22 O Must be connected via a capacitor of more

than 5pF to CAP_B12.

Semiconductor Group 11 Data Sheet 06.98

PSB 4595 / PSB 4596

Analog Line Interface Solution

Pin Definition and Functions

Pin No. Symbol Function Descriptions

15 CAP_C21 I Must be connected via a capacitor of more

than 5pF to CAP_C11.

14 CAP_C22 I Must be connected via a capacitor of more

than 5pF to CAP_C12.

Table 1: ALIS-A Pin Definition

Semiconductor Group 12 Data Sheet 06.98

PSB 4595 / PSB 4596

Analog Line Interface Solution

Pin Definition and Functions

2.3 Pin Definition of ALIS-D PSB 4596

Pin No. Symbol Function Description

8 VDD Power +5 Volt supply for the digital circuitry

9 GND Power Ground digital: All sig nals are referred to

this pin

25 VDDA Power +5 Volt supply for the analog circuitry

24 GNDA Powe r Ground analog: All analog signals are

referred to this pin

21 MCLK1 I Master clock1: One pin of a crystal or

ceramic resonator is connected. This pin

can also be driven from an external

clocking source of 16.384 MHz,

synchronous to FSC (MCLK=FSC*2048)

20 MCLK2 O Master clock2: The other pin of a crystal or

ceramic resonator is connected. When

MCLK1 is driven by an external clock, this

pin should be left open

23 RESET I Reset input: Forces the device to default

mode (low active)

15 FSC BI As input: Frame synchronisation clock,

8kHz, identifies the beginning of the

frame. FSC must be synchronous to

MCLK (MCLK=FSC*2048)

As Output: Indicates the beginning of a

new frame

17 DAT_IN /

SEL

16 DAT_OUT O Data interface: Transmit data to the DSP.

I Data interface: Receive data from the

DSP. The data is received in 16-bit bursts

every 125 ms.

Interface selection pin in MUX mode.

The data is transmitted in 16-bit bursts

every 125 ms

18 DAT_CLK I Data clock 128 to 1024 kHz: Determines

the rate at which data is shifted into or out

of the data interface

10 CS I µ-controller interface: Chip select enable

to read or write data. Active low

Semiconductor Group 13 Data Sheet 06.98

Analog Line Interface Solution

Pin No. Symbol Function Description

PSB 4595 / PSB 4596

Pin Definition and Functions

11 DCLK I

12 DIN I

13 DOUT TRI

14 INT O

19 MODE I Interface mode pin (parallel or MUX

4 ID_Ain I Input for caller ID comparator (connection

6 ID_Bin I

5 A feedback O Feedback for caller ID comparator

7 B feedback O Feedback for caller ID comparator

28 CAP_A11 O Must be connected via a capacitor of more

1 CAP_A12 O Must be connected via a capacitor of more

µ

-controller interface: Clock. Maximum

clock rate 1024 kHz

µ

-controller interface: Input data

µ

-controller interface: DOUT is high ’Z’ if

no data is transmitted

µ

-controller interface: Interrupt output pin

mode)

to TIP)

Input for caller ID comparator (connection

to RING)

than 5pF to CAP_A21.

than 5pF to CAP_A22.

2 CAP_B11 I Must be connected via a capacitor of more

than 5pF to CAP_B21.

3 CAP_B12 I

26 CAP_C11 O Must be connected via a capacitor of more

27 CAP_C12 O Must be connected via a capacitor of more

22 SO O Auxiliary output pin

Table 2: ALIS-D Pin Definition

Must be connected via a capacitor of more

than 5pF to CAP_B22.

than 5pF to CAP_C21.

than 5pF to CAP_C22.

Semiconductor Group 14 Data Sheet 06.98

PSB 4595 / PSB 4596

Analog Line Interface Solution

System Integration

3 System Integration

ALIS can be used in different modem applicati ons to connect the data pump to the TIP /

RING wire.

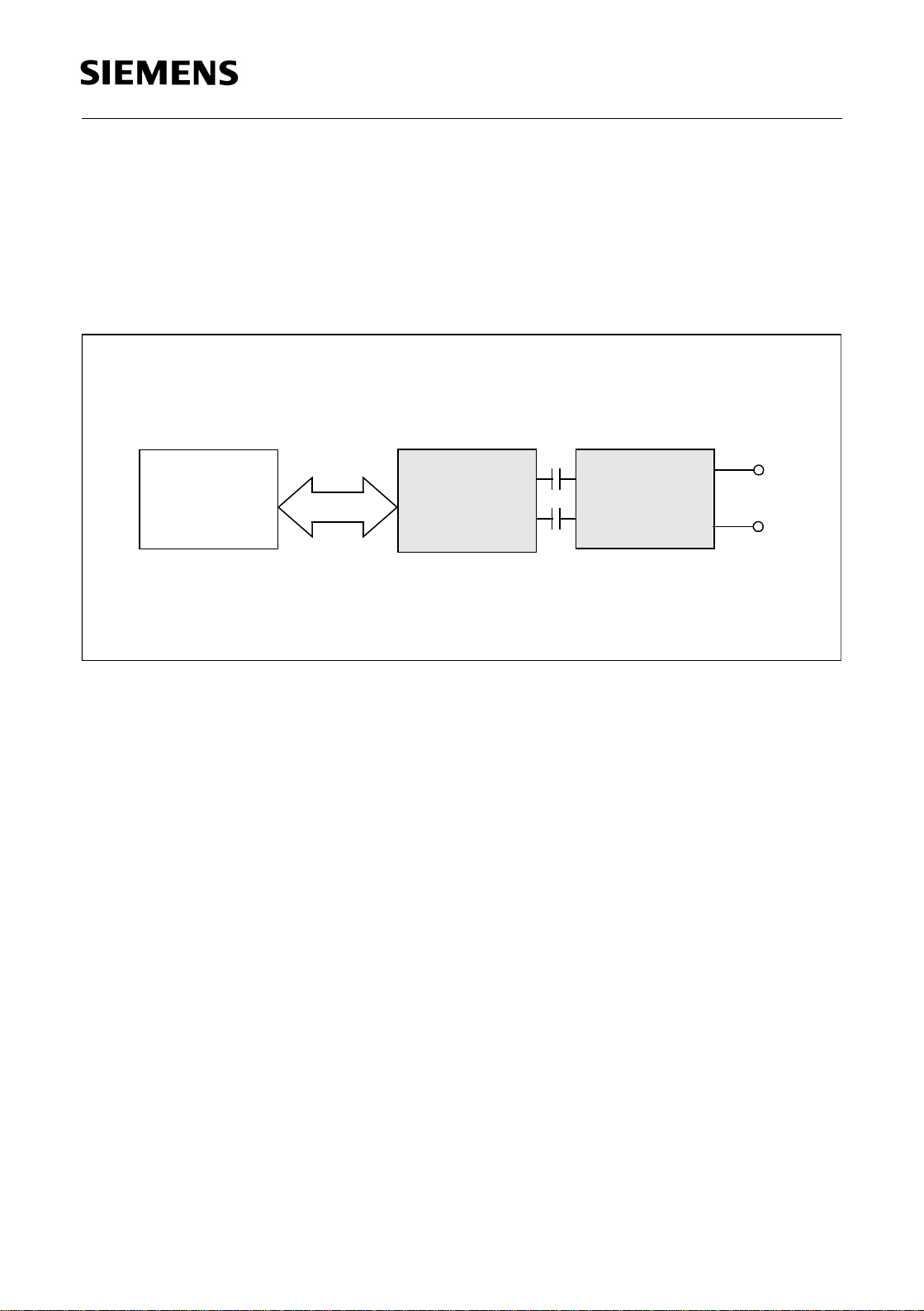

3.1 ALIS with DSP-based Modem

For a modem data pump, the ALIS pro vides the front-end to the tip/ring.

Data Pump

V.34

V.90

ALIS-D

SI

PSB 4596

ALIS-A

Tip/Ring

PSB 4595

Note: SI: Serial Interface

Figure 4 DSP-based Modem Application

Isolation is provided by a capacitor inte rface, without transformer. This allows ver y flat

frequency response over the entire voice band, even at low frequencies.

In V.90 Modem applications, the 50/60 Hz hig h-pass filter can be turned off.

Semiconductor Group 15 Data Sheet 06.98

PSB 4595 / PSB 4596

Analog Line Interface Solution

System Integration

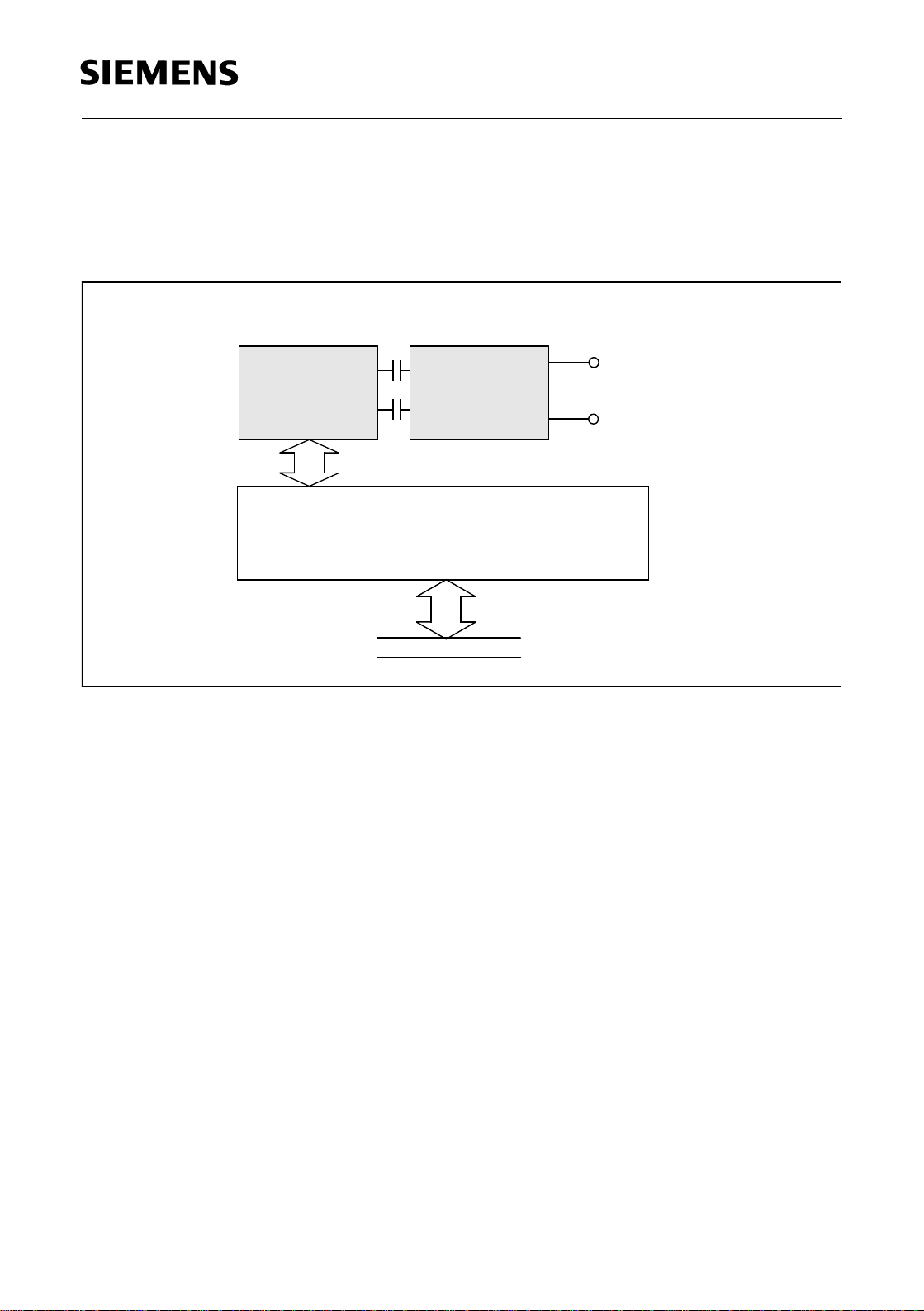

3.2 ALIS with Software Modem

ALIS also supports software modems wh ere V.34 runs on the host computer (e.g. in

combination with a USB controller).

ALIS-D

PSB 4596

SI

Microcontroller with USB or PCI Interface

USB or PCI

Figure 5 Software Modem Application

ALIS-A

Tip/Ring

PSB 4595

Semiconductor Group 16 Data Sheet 06.98

PSB 4595 / PSB 4596

Analog Line Interface Solution

System Integration

3.3 Hybrid Modem (ISDN plus Analog)

In combination with the SIEMENS ISDN chip set, ALIS supports hybrid modems, ,

allowing connection to either the TIP/RING line or to an S or U-interface for ISDN

applications.

ALIS-A

Tip/Ring

PSB 4595

ISAC-S TE

S-Interface *IOM-2 Interface

PSB 2186 *

Flash

SRAM

ALIS-D

PSB 4596

SI

ISAR34

PSB 7115

Microcontroller with USB or V.24 In te rface

USB or V.24

Figure 6 Hybrid Modem Application, with S-interface: ISAR34 Enhanced Data Access Controller (PSB 7115) and ISDN Access Co ntroller for S-Bus ISAC-S TE (PSB

2186)

* Figure 4 shows a hybrid modem with the ISDN S-interface. To meet the ISDN Uinterface, the ISAC-S TE PSB 2186 is repla ced by the IEC-Q TE PSB 21911.

Semiconductor Group 17 Data Sheet 06.98

3.4 Modem with Speakerphone

PSB 4595 / PSB 4596

Analog Line Interface Solution

System Integration

Flash

SRAM

ALIS-D

PSB 4596

SI

ISAR34

IOM-2 Interface

PSB 7115

ALIS-A

TIP/RING

PSB 4595

ARCOFI-SP

PSB 2163

Microcontroller with USB or V.24 Interface

USB or V.24

Figure 7 Application wi th Speakerphone: ARCOFI-SP Audio Ringing Codec (PSB

2160, PSB 2163, PSB 2165, PSB 2168) and ISAR34 Enhanced Data Access Controller (PSB 7115)

Semiconductor Group 18 Data Sheet 06.98

PSB 4595 / PSB 4596

Analog Line Interface Solution

System Integration

3.5 Analog Videophone

The diagram below shows a system solution for an analog videophone application using

a SIEMENS chip set.

Flash

SRAM

ALIS-D

PSB 4596

SI

ISAR34

PSB 7115

ALIS-A

PSB 4595

IOM-2 Interface

Tip/Ring

ARCOFI-SP

PSB 2163

JADE AN

PSB 7230

VIDEO

CODEC

Microcontroller with USB or V.24 Interface

USB or V.24

Figure 8 ARCOFI-(SP) Audio Ringing Codec (PSB 2160, PSB 2163, PSB 2165, PSB

2168) ; ISAR34 Enhanced Data Access Controller (PSB 7115); JADE Joint Audio

Decoder Encoder (PSB 7230, PS B 723 8)

Semiconductor Group 19 Data Sheet 06.98

PSB 4595 / PSB 4596

Analog Line Interface Solution

ALIS Implementation

4 ALIS Implementation

The ALIS chip set repla ces all the major parts of a conventional front end for mod em

solutions. The circuit consists of two major parts, a DSP-based codec and an electronic

DAA. Advanced features such as ring detection, pulse dialing and caller ID are

integrated on-chip. Additional operating modes such as sleep mode or ringing mode are

implemented to minimize power consumption .

4.1 ALIS Block Diagram

The tip/ring telephone line interface is connected mainly with the ALIS-A. It is also

connected with the ALIS-D for Caller ID functions..

Control Data

Control Interfac e

DSP

Data Interface

Transmit/Receive Data

HWFilter

Caller ID

Isolation

Cap. Int erface

A/D

D/A

I/O

Vdd

Control

Hybrid

and

Filters

ALIS-AALIS-D

Control

TIP/RING

Figure 9 ALIS Block Diagram

The analog front end (ALIS-A) is connected t o the line via TIP/RING. The programmable

supply voltage for AL IS-A is generate d from the line by the Vdd control. Two/four wire

conversion is implemente d in the hybrid circuit. Ana log anti-aliasing pre -filters (PREFI)

and smoothing post-filters (POFI) are included for signal conditioning. High-performance

over-sampling analog-to-digital converters (ADCs) and digital-to-analog converters

(DACs) assure the required conversion accuracy. The ADCs and DACs are connected

to the digital signal processor (DSP) on the digital part (ALIS-D) via a dedicated capacitor

interface which also provides the requi red isolation to the line . Special hardwa re filters

perform filtering functions such as interpolation and decimation. The DSP handles all the

necessary algorithms. These include bandpass filtering, sample rate conversion, ringing

detection, and caller ID decoding. All programmable filters and functions are also

controlled and processed by the DSP. The control interface allows external control of the

ALIS features and provide s transp arent access to ALIS commands an d signaling pin s.

Thus pre-calculated sets of coefficients can be downlo aded from the system to the o n-

Semiconductor Group 20 Data Sheet 06.98

PSB 4595 / PSB 4596

Analog Line Interface Solution

ALIS Implementation

chip coefficient RAM (CRAM) in order to progr am the fil ters. Transmit an d receive data

is transferred to and from the data pump via the data interfa ce .

4.2 ALIS AC Signal Flow Graph

ALIS architecture is based on digital filters. The data path through these filters is shown

in the next few diagrams. The filter concept also allows maximum autonomy between the

different filter blocks. Each filter block has a one -to-one corresp onden ce with a specific

network element. Marked filters (gre y) can be programmed by the user.

digital out

FRRAR1

digital in

user-programmable block

Definition:

Transmit:Digital-to-Analog

Receive :Analog-to-Digital

RFIX1

XFIX1FRXAX1

fixed filter block

THFIX

TH

AR2

AX2

fixed functional block

RFIX2

XFIX2

Legend:

DAA

AR1

FRR

RFIX1

AR2

RFIX2

ADC

THFIX

TH

IMFIX

IM

AX1

FRX

XFIX1

AX2

XFIX2

DAC

ADC

ADC

IMFIX

IM

DAC

Data Access Arrangement, Fix ed Part

Amplification Receive Filter 1

Equalizatio n Rec e iv e

Receive Filter Fixed Part 1

Amplification Receive Filter 2

Receive Filter Fixed Part 2

Analog-to-Digital Converter

Transhybrid Filter Fix ed Part

Transhybrid Filter

Impedance Filter Fixed Part

Impedance Filter

Amplification Transmit Filter 1

Equalization Trans m it

Transmit Filter Fixed Part 1

Amplification Transmit Filter 2

Transmit Filter Fixed Part 2

Digital-to-Analog Converter

DAA

Tip/

Ring

Figure 10 AC Signal Flow Graph

Semiconductor Group 21 Data Sheet 06.98

PSB 4595 / PSB 4596

Analog Line Interface Solution

ALIS Implementation

4.2.1 Receive Path

After passing the DAA and a simple anti-aliasing pre-filter with an analog gain stage, the

voice signal is converted to a 1-bit digital data strea m in the sigma-delta converte r. The

first down-sampling steps are performed in fast digital hardware filters. Subsequent

processing is implemented in the digital structure which allows easy and flexible

programming of parameters. Finally, the fully processed signal is transferred to the data

interface.

Subsequent processing is done by microcode in the digital filter structure to allow

adaptability. Gain adjustment is pro vided in two stages, AR1 and AR2. The total gain

adjustment is programmable in two ranges: from 14 to 24 dB, in steps of 0.5 dB; and from

-3 to 14 dB, with steps between 0.02 and 0.05 dB.

Located inbetween is a decimation stage to reduce the sampling rate to the 8 kHz PCM

rate, and a low-pass filter to band-limit the signal in accord ance with ITU-T G.714 and

ETSI (NET33) recommendations (in RFIX1); also an equalization stage (in FRR).

Finally, the signal is passed out to the Serial Data Interface (SDI).

ALIS meets or exceeds all ITU and ETSI (NET33) recommendations on attenuation

distortion and group delay.

4.2.2 Transmit Path

The digital input signal is received via the data interface. Low-pass filtering, gain

correction and frequency-response correction are implemented in the digital filter

structure. The up-sampling in terpolation is then performed by fast hard ware structures

to reduce the DSP load. The up- sampled 1-bit data stream is converted to an analo g

equivalent which is smoothed by a post-filter (POFI) and conv erted to a 2-wire signal in

the DAA.

There are also two independent tone generators which can insert tones into the Transmit

path. They have adjustable frequencies, default 2 kHz, and a programmable bandpassfilter to adapt the output for DTMF. When either tone generator is on, the data signal

transmission is suppressed.

4.2.3 Loops

ALIS implementation inclu des two loops. One is used to generate the AC-terminatio n

impedance (IM) and the other is used to perform proper hybrid balancing (TH). A simple

additional path IM (from the receive to the transmit path) supports the impedancematching function.

4.2.4 Test Features

Several analog and digital test loops are implemented in ALIS. The receive and transmit

paths may be short-circuited at two different points for test purposes.

Semiconductor Group 22 Data Sheet 06.98

Analog Line Interface Solution

4.3 ALIS Ring and Caller ID Signal Flow Graph

PSB 4595 / PSB 4596

ALIS Implementation

CID out

comparator for CID

CIDL

user-programmabl e block

CIDH

fixed filter block

CIDBP

RLM

RIM

FIX

RIM

fixed functional block

Tip/Ring

ADC

DAC

Legend:

Caller ID Lowpass

CIDL

Caller ID Hilbert Transformer

CIDH

Caller ID Bandpass

CIDBP

RLM

Ring Level Metering

Analog-to-Digital Converter

ADC

Ringer Impedace Filter Fixed Part

RIMFIX

Ringer Impedace Filter

RIM

DAC

Digital-to-Analog Converter

Figure 11 Ring Signal Flow Graph

These data paths operate only when the A LIS is in Ringi ng state.

4.3.1 Caller ID (CID) Path

The Caller ID receiver meets Bellcore specifications TR-NWT-000030 and

SR-TSV-002476 for Caller ID. In this service, the calling party’s information (Calling Line

Identification Presenta tion (CLIP)) is transmitted in the silent interva l between the first

and second ring. ALIS receives and stores up to 4096 bits of the 1200 baud FSK

(Frequency Shift Keying) signal. The decodi ng scheme meets the Bell 202 and ITU-T

V.23 specifications.

The FSK signal which contains the caller information is converted to a 1-bit data stream

by a comparator in order to minimize power consumption. Down-sampling steps are

performed in fast digital hardware filters. To decode the caller ID, bandpass filtering,

Hilbert transformation and other functions are implemented. The output CID-out is

sampled at 1200 baud, an d stored in the CID-RAM.

Semiconductor Group 23 Data Sheet 06.98

PSB 4595 / PSB 4596

Analog Line Interface Solution

ALIS Implementation

4.3.2 Ring-Level Metering (RLM) Path

The analog signal is converted to a 1-bit data stream in the ADC. After decimation in

hardware filters, the remaining processing is done in the digital filter structure (in RLM):

bandpass filtering to select the ringing frequency, and integration to determine if the

amount of energy in-band has exceeded the threshold for a valid ring signal. The

bandpass parameters and threshold are programmable.

Ringing is detected in this path. Th e digital input is bandpass filtered, integrated and

compared to a threshold to determine if a ringing signal has occurred. The threshold and

bandpass filters are programmab le. The result of this operation can be monito red by

reading the RMR bit (see “CR1 Configuration Register 1 (Diali ng)” on page 40).

4.3.3 Loops

A loop is available to generate the Ring-termination impedance (RIM).

4.3.3.1 Test Features

There are three loopbacks on ALIS-D to test interfaces:

- Host interface: loopback from the PCM in te rface (just inside ALIS-D)

- Caller ID interface: loopback from Caller ID input to capacitor interface

- Capacitor interface: loopb ack throug h different parts of the capacitor interface

There are two loopbacks on ALIS-A:

- Tip/ring interface: loopback from the tip/ring, before the ADC

- Codec: loopback from the tip/ring, after the codec

Semiconductor Group 24 Data Sheet 06.98

5 Configuration Overview

5.1 Connection to the Telephone Line

VDDA

SENS

VDD

T2

T2G

-

AC

TIP

TIP

PSB 4595 / PSB 4596

Analog Line Interface Solution

Configuration Overview

TIP

T1

T1G

RING-AC

RING

VREF

GNDA

CAP1

CAP2

RING

Figure 12 Connection of ALIS-A to the Telephone Line

As shown in the figure, ALIS-A requires a minimum of components to complete the DAA:

- Protection circuit: not shown.

- Bridge: using Schottky diodes will improve the performance at low feedin g condition s.

Recommended: Dual Schottky diode SIE M ENS BAT 240A.

- Resistors for current sensing.

- Capacitors for AC coupling and VDD buffering.

Semiconductor Group 25 Data Sheet 06.98

PSB 4595 / PSB 4596

Analog Line Interface Solution

Configuration Overview

- Two transistors (T1, T2) to handle the line current. T2 must be of depletion type, in order

to deal with start-up. Recommen ded tran sistors: T1: SIE MENS BS P 88; T2: SIEMENS

BSP 129.

- Components for EMC protection: no t shown, as they depend on the board layout.

ALIS-D can optionally be connected to the tip/ring to provide Caller ID functions. The CID

circuit requires two capacitors and four resistors.

5.2 Host Interface

The host interface consists of a serial µ-controller interface and a 16-bit linear data

interface. They are used to connect ALIS either to a

The two serial interfaces can be accessed on two separate serial ports or in timemultiplex (MUX) mode on a single serial port.

5.2.1 The µ-Controller Interface

µ

-

controller and or to a data pump.

The ALIS internal con figuration registers, the auxiliary po rts, and the Coefficient RAM

(CRAM) are programmable via the serial µ-controller interface. This interface consists of

four pins:

CS: Chip select, to enable inte rface (active low)

DCLK: Clock, 1 kHz to 1024 kHz

DIN: Data input

DOUT: Data output

CS is used to start serial access to the ALIS registers and the Coefficient RAM. Following

a CS falling edge, the first eight bits received at DIN specify the command. Subsequent

data bytes (the number depends on the command) are stored in the selected

configuration registers or th e selected part of the CRAM.

Serial interface specification: 8 bit, no parity, no start/stop bit. Every command must

begin with a CS falling edge.

Semiconductor Group 26 Data Sheet 06.98

CS

DCLK

PSB 4595 / PSB 4596

Analog Line Interface Solution

Configuration Overview

DIN

36547 210 36547 210

36547 210

Control Data Byte 1 Data Byte 2

High ’Z’

DOUT

Figure 13 Example of a Write Access, two Data Bytes transferred

If the first eight bits received via DIN specify a read command, ALIS will start to respond

via DOUT with its specific identification byte. The number of specified d ata bytes within

the command (contents of configuration registers or contents of the CRAM) will follow on

DOUT.

CS

DCLK

DIN

36547 210

Control

High ’Z’

DOUT

36547 210

36547 210

Identification Data Byte 1

Figure 14 Example of a Read Access, one Data Byte transferred via DOUT

Semiconductor Group 27 Data Sheet 06.98

PSB 4595 / PSB 4596

Analog Line Interface Solution

Configuration Overview

The data transfer is synchronized by DCLK. DIN is latched at the falling edge of DCLK,

while DOUT changes with the rising edge of DCLK. During the execution of a command

which is followed by output data (read command), the device will not accept any new

command via DIN. The data transfer sequence can be interrupted by setting CS to ’1’.

To reduce the number of connections to the µ-processor, DIN and DOUT may be

strapped together to form a bi-directiona l data pin.

5.2.2 The Data Interface

A serial data inte rface is used for tran sferring voice data. The inte rface consists of five

pins:

DAT_CLK: Clock, 128 kHz to 1024 kHz

FSC: Frame synchronization clock, 8 kHz

DAT_IN: Transmit data input

DAT_OUT: Receive data output

The Frame Sync (FSC) pulse identifies the beginning of a receive and a transmit frame.

DAT_CLK synchronizes the data transfer on DAT_IN and DAT_OUT. The data bytes are

first serialized to 16-bit width and MSB. The rising edge indicates the start of the bit, while

the falling edge is used to latch the conten ts of the received data.

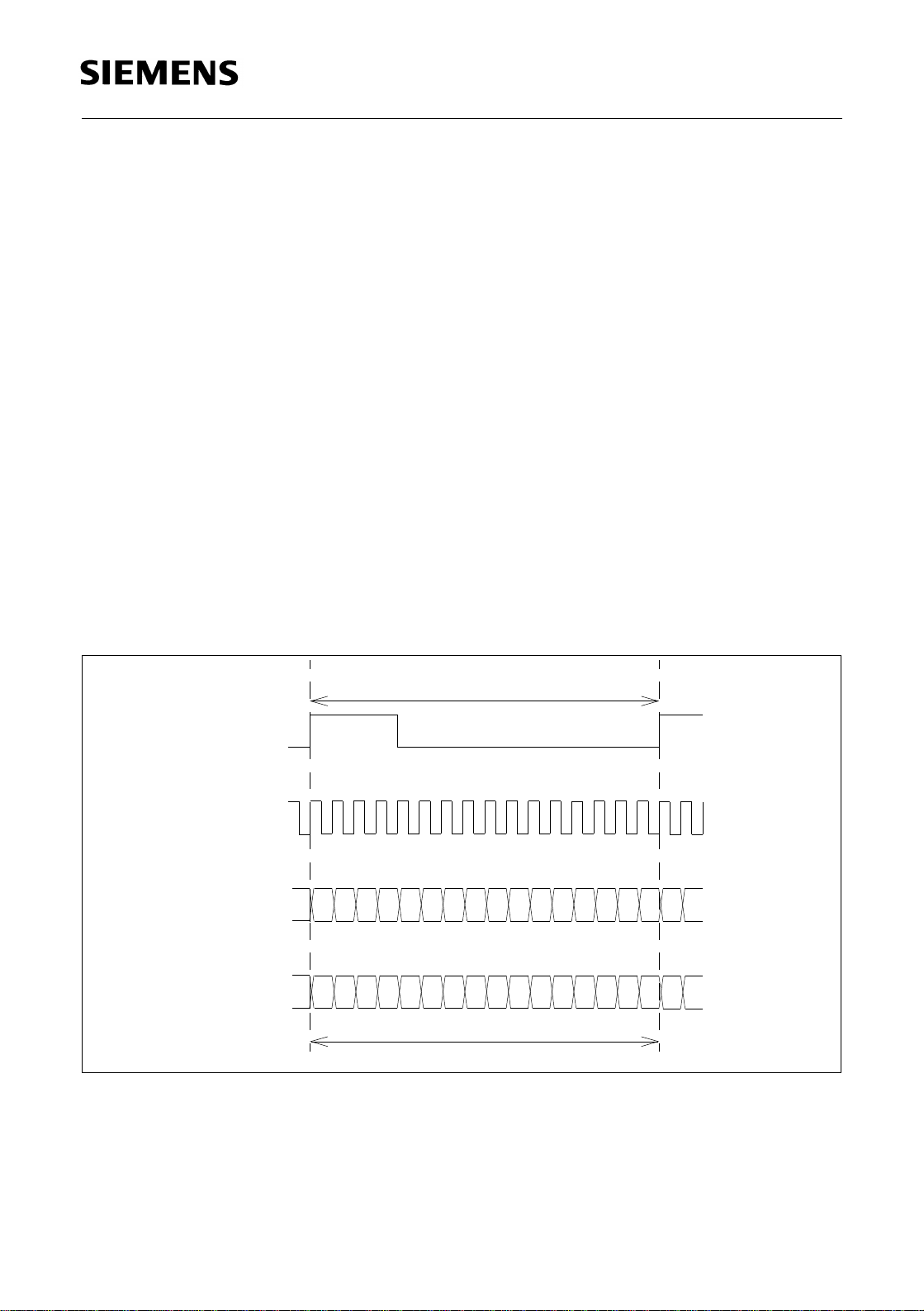

125 µS

FSC

DAT_CLK

DAT_IN

DAT_OUT

0

0

1114 13 1215 10 9 8 36547 210

1114 13 1215 10 9 8 36547 210

16 Bit Voicedata MSB first

12

12

Figure 15 Example of a Clock Rate of 128 kb/s

Semiconductor Group 28 Data Sheet 06.98

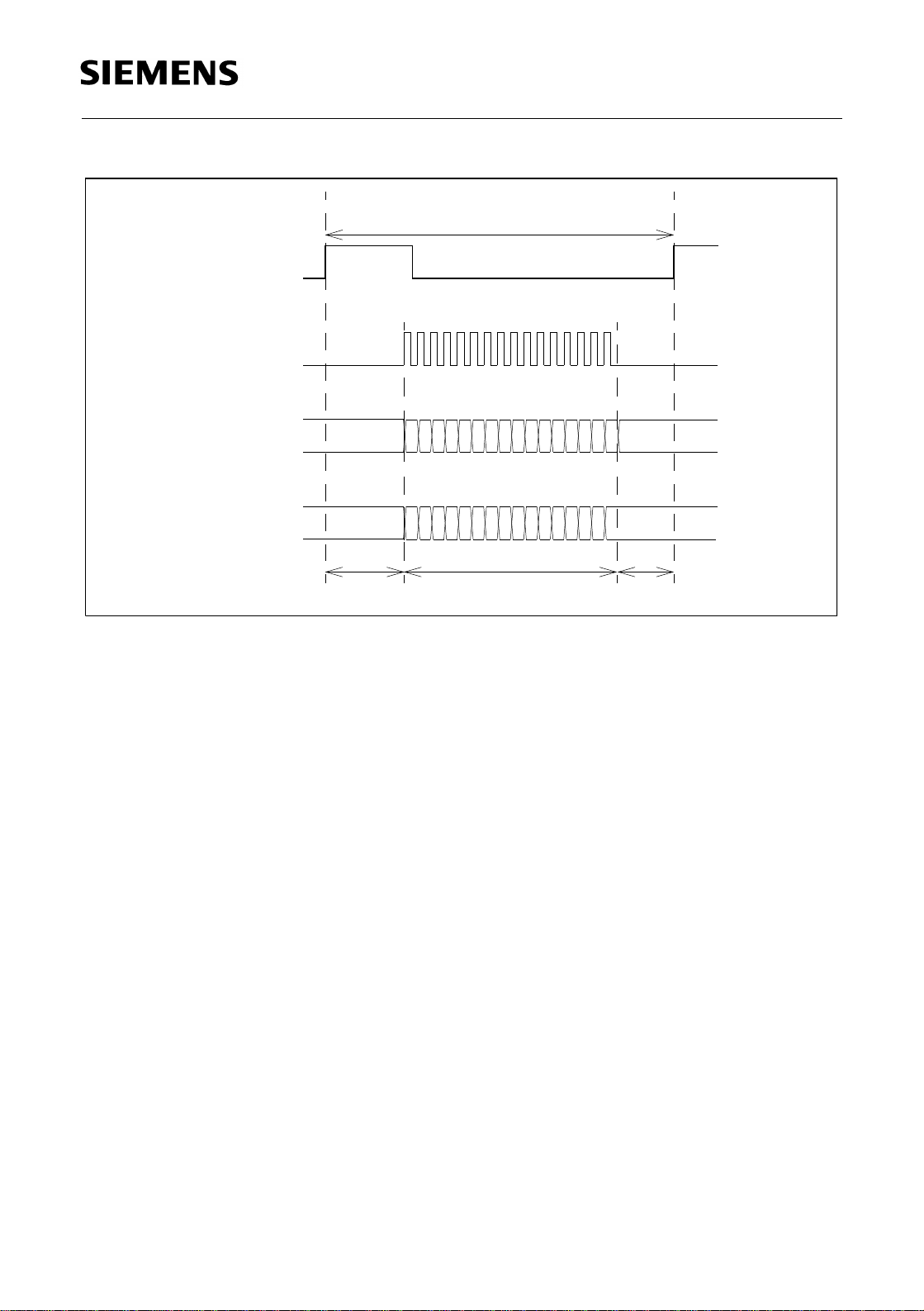

FSC

DAT_CLK

PSB 4595 / PSB 4596

Analog Line Interface Solution

Configuration Overview

125 µS

DAT_IN

DAT_OUT

1114131215 10 9 8 36547 210

1114131215 10 9 8 36547210

Voice

t

tStoptStart

Figure 16 Example of a Clock Rate higher than 128 kb/s

The data package must stay within the frame, t

> 0 and t

Start

Stop

> 0.

The FSC signal can be generated externally by the ho st or by ALIS.

Semiconductor Group 29 Data Sheet 06.98

PSB 4595 / PSB 4596

Analog Line Interface Solution

Configuration Overview

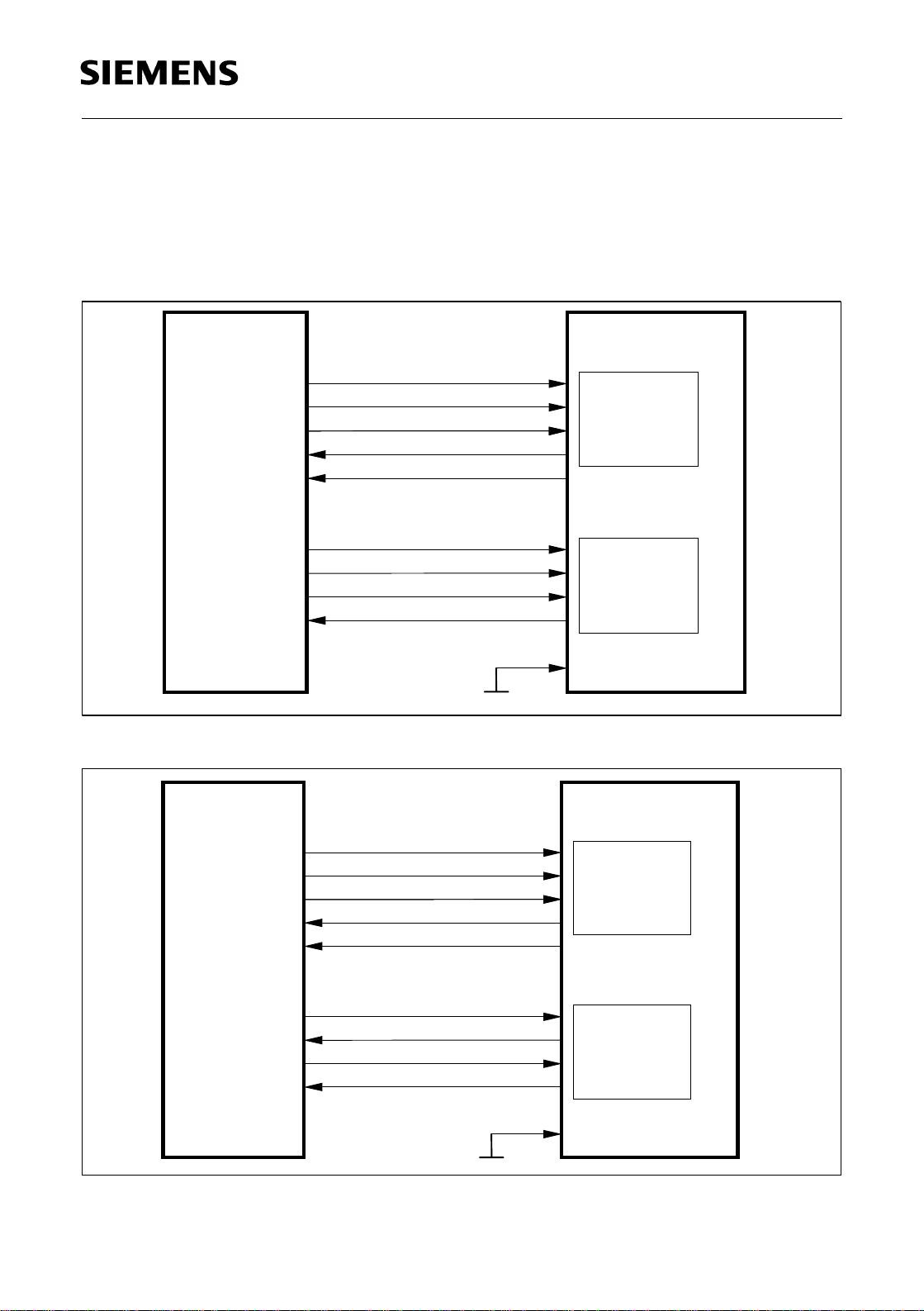

5.2.3 Interface Modes

5.2.3.1 Demux Mode

Connection of the MODE pin to GND allows the µC and the data interface to be

accessed via two serial ports.

DSP

(Data Pump)

DCLK

CS

DIN

DOUT

INT

DAT_CLK

FSC

DAT_IN

DAT_OUT

MODE

Figure 17 Host Interface in Demux Mode, FSC as Input

DSP

(Data Pump)

DCLK

CS

DIN

DOUT

INT

µC Interface

ALIS-D

µC Interface

Data

Interface

ALIS-D

DAT_CLK

FSC

DAT_IN

DAT_OUT

Data

Interface

MODE

Figure 18 Host Interface in Demux Mode, FSC as Output

Semiconductor Group 30 Data Sheet 06.98

Loading...

Loading...