Siemens BGA425 Datasheet

BGA 425

Semiconductor Group

Jul-14-19981

Si-MMIC-Amplifier

in SIEGET 25-Technologie

VPS05605

4

2

1

3

Preliminary data

• Multifunctional casc. 50 Ω block (LNA / MIX)

• Unconditionally stable

• Gain |

S

21

|2 = 18.5 dB at 1.8 GHz (appl.1)

gain |

S

21

|2 = 22 dB at 1.8 GHz (appl.2)

IP

3out

= +7 dBm at 1.8 GHz (

V

D

=3V,

I

D

=9.5mA)

• Noise figure

NF

= 2.2 dB at 1.8 GHz

• Reverse isolation >28 dB (appl.1) >35 dB (appl.2)

• typical device voltage

V

D

= 2 V to 5 V

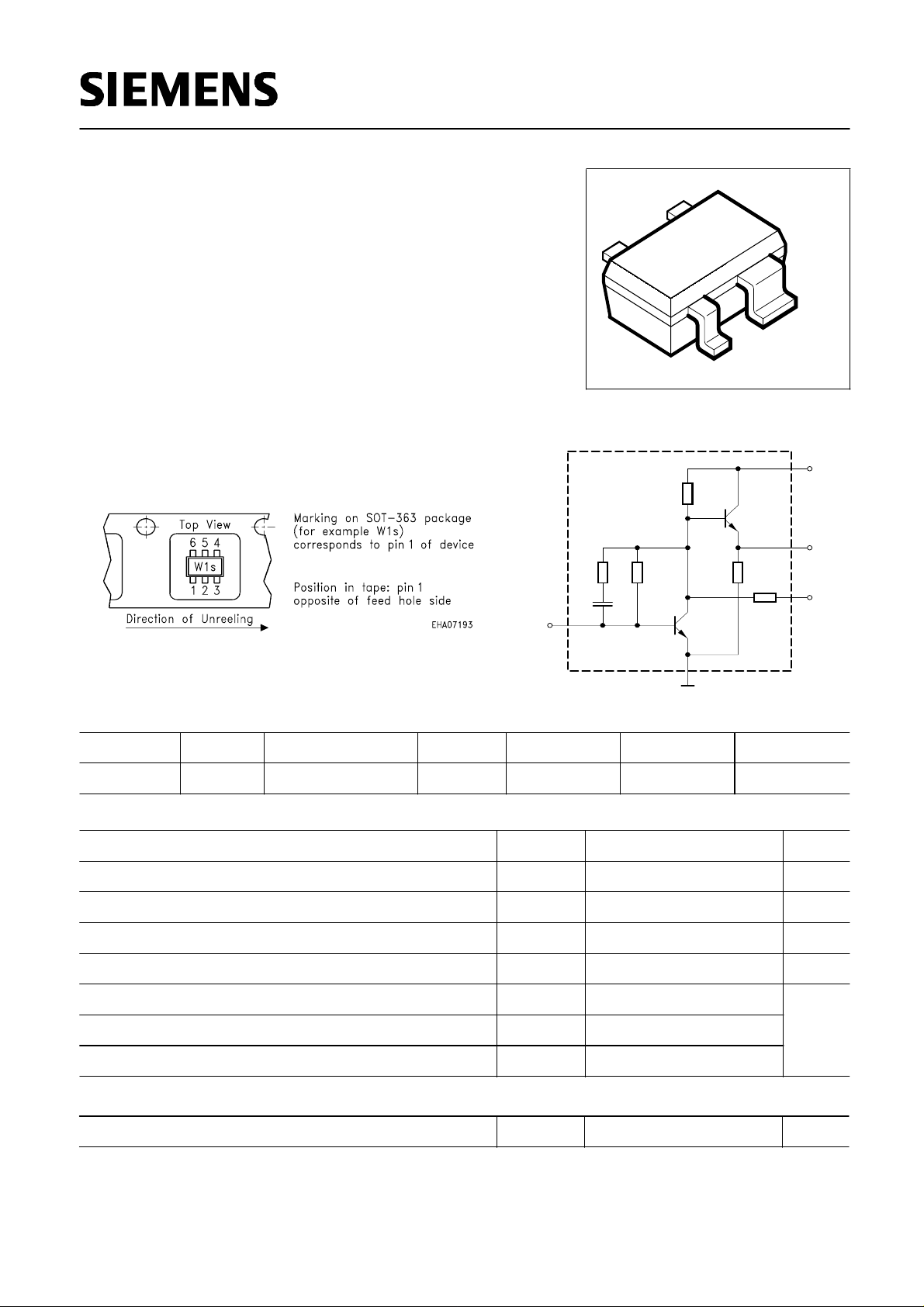

Tape loading orientation

Circuit Diagram

EHA07371

V

2, 5

4

IN

OUTA

+

3

6

OUTB

1

GND

ESD: Electrostatic discharge sensitive device,

observe handling precaution!

PIN Configuration

Type Marking Ordering Code 1, Out B 3, Out A2, GNDPackage

BGA 425 4, IN 5, GND 6, +VBMs Q62702-G0058 SOT-343

Maximum Ratings

Parameter

Symbol Value Unit

Device current

I

D

25 mA

Device voltage

V

D

,+V

V6

Total power dissipation,

T

S

≤ tbd °C

P

tot

150 mW

R

F

input power

P

RFin

-10 dBm

Junction temperature

T

j

150 °C

Ambient temperature

T

A

-65 ...+150

Storage temperature

T

stg

-65 ...+150

Thermal Resistance

Junction - soldering point

1)

R

thJS

≤ tbd

K/W

1)

T

S

is measured on the ground lead at the soldering point to the pcb

Semiconductor Group 1 1998-11-01

BGA 425

Semiconductor Group

Jul-14-19982

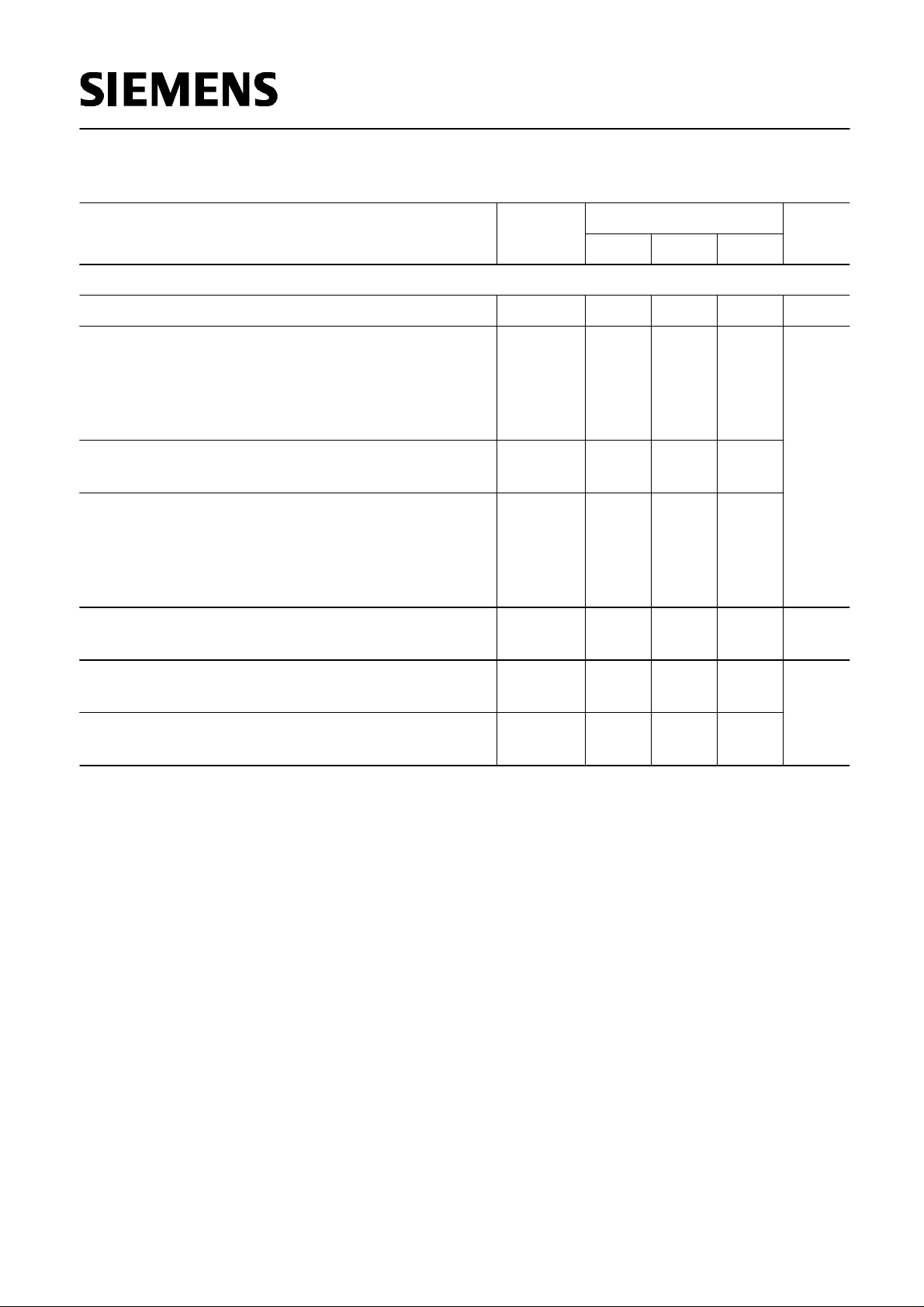

Electrical Characteristics at

T

A

= 25 °C, unless otherwise specified.

Parameter

Symbol Values Unit

min. typ. max.

AC characteristics

V

D

= 3V,

Z

o

= 50Ω, Testfixture Appl.1

Device current

I

D

8.5 9.5 10.5 mA

Insertion power gain

f

= 0.1 GHz

f

= 1 GHz

f

= 1.8 GHz

|

S

21

|

2

-

-

-

27

22

18.5

-

-

-

dB

Reverse isolation

f

= 1.8 GHz

S12

- 28 -

Noise figure

f

= 0.1 GHz

f

= 1 GHz

f

= 1.8 GHz

NF

-

-

-

1.9

2

2.2

-

-

-

Intercept point at the output

f

= 1.8 GHz

IP

3out

-

+ 7

- dBm

Return loss input

f

= 1.8 GHz

RL

in

- >13 - dB

Return loss output

f

= 1.8 GHz

RL

out

- >7 -

Semiconductor Group 2 1998-11-01

BGA 425

Semiconductor Group

Jul-14-19983

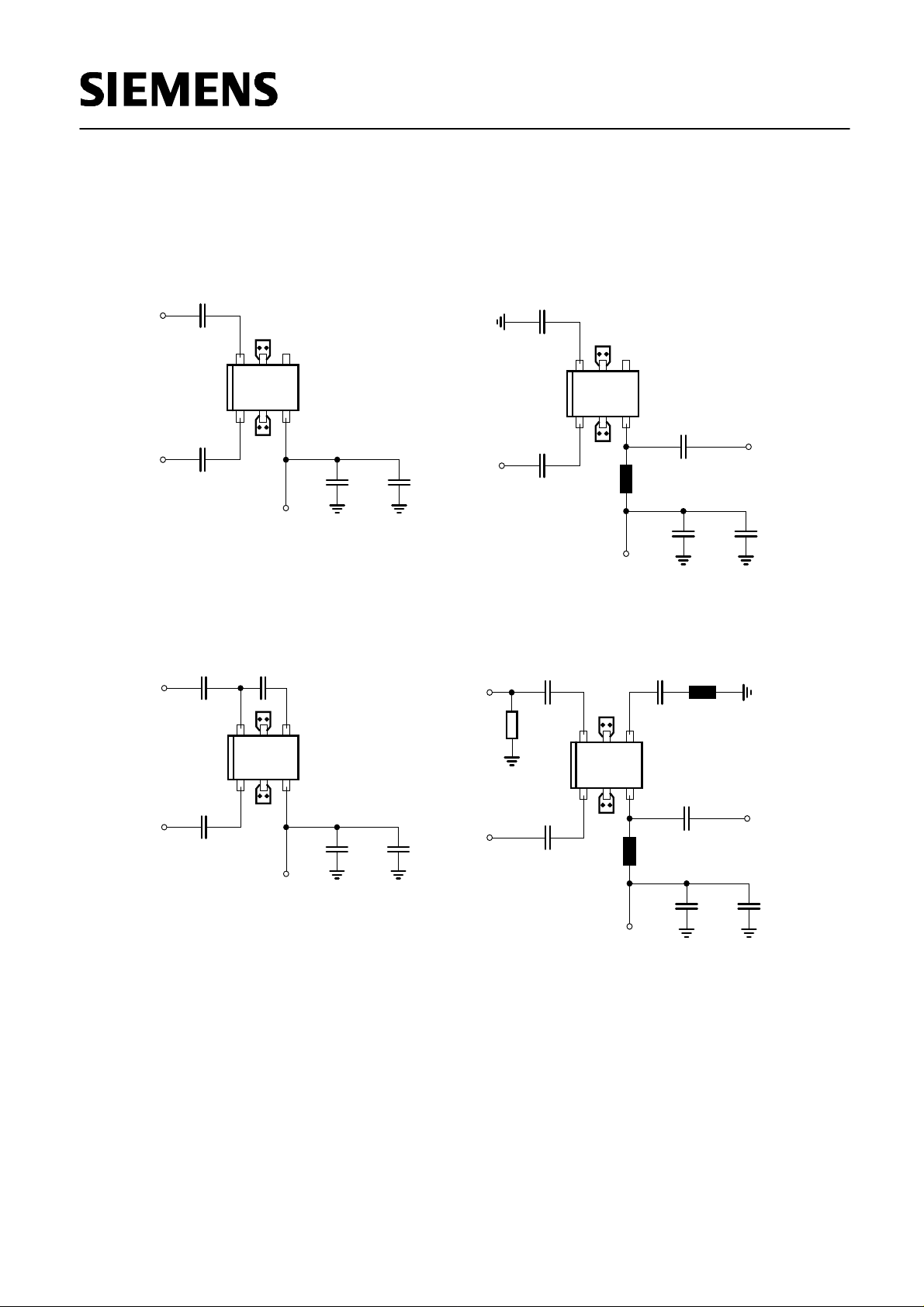

Typical configuration

Application 1 - 3 (LNA)

Application 4 (Mix)

Appl.1

Appl.2

EHA07372

100 pF

100 pF

100 pF10 nF

+3 V

RF OUT

RF IN

BGA 425

EHA07373

2.2 pF

100 pF

100 pF10 nF

+3 V

RF OUT

RF IN

100 pF

100 nH

BGA 425

Appl.3 Appl.4

EHA07375

1 nF

100 pF

IF

RF

47 pF

180 nH

LO

Ω33

47 pF

22 nH

10 nF 100 pF

+

V

BGA 425

EHA07374

100 pF

100 pF

100 pF10 nF

+3 V

RF OUT

RF IN

100 pF

BGA 425

Note: 1) Large-value capacitors should be connected from pin 6 to ground right at the device

to provide a low impedance path! (appl. 1)

2) The use of plated through holes right at pin 2 and 5 is essential for pc-board-applications.

Thin boards are recommended to minimize the parasitic inductance to ground!

3) For more information please see application note 028 and 030.

Semiconductor Group 3 1998-11-01

Loading...

Loading...