Page 1

SERVICE MANUAL

MODEL UP-600

SRV Ke y : LKGIM7113RCZZ

PRINTER : DP-750

(For "U & A" version)

CONTENTS

CHAPTER 1. SPECIFICATIONS ................................................................1 - 1

CHAPTER 2 . OPTIONS..................... .............. .............. .............. ...............2 - 1

CHAPTER 3. SERVICE PRECAUTION......................................................3 - 1

CHAPTER 4. SR V. RESET AND M ASTER RESET....................................... 4 - 1

CHAPTER 5. DIAGNOSTICS SPECIFICATIONS.......................................5 - 1

CHAPTER 6. CIRCUIT DESCRIPTION ......................................................6 - 1

CHAPTER 7. TCP/IP I/F PWB DESCRIPTION...........................................7 - 1

CHAPTER 8. CIRCUIT DIAGRAM..............................................................8 - 1

CHAPTER 9. PWB LAYOUT.......................................................................9 - 1

Parts marked with " " are important for maintaining the safety of the set. Be sure to replace these parts with specified

ones for maintaining the safety and performance of the set.

This document has been published to be used

SHARP CORPORATION

for after sales service only.

The contents are subject to change without notice.

Page 2

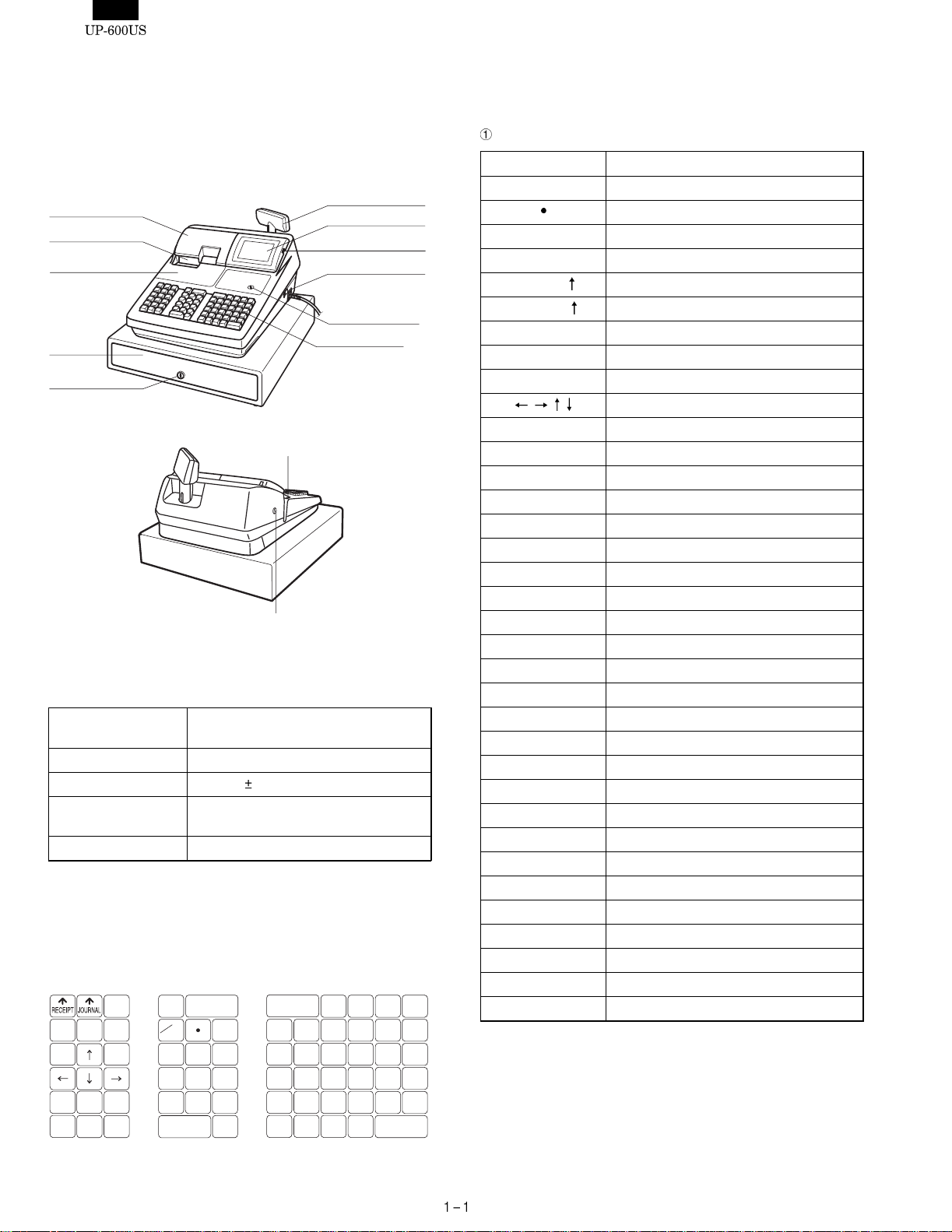

CHAPTER 1. SPECIFICATION

1. APPEARANCE

External view

Front view

Journal cover

Receipt paper

Ribbon cover

Drawer

Drawer lock

Rear view

Validation opening

Printer cover lock

2. RATING

External dimensions :

With a drawer

Weight : With a drawer 16.4kg

Power source 120V AC

Power consumption Stand-by : 16 W

Working temperatures 0 to 40 °C

445 (W) x 485 (D) x 312 (H) mm

10%, 60Hz

Operating : 57 W (max.)

3. KEYBOARD

1) STANDARD KEYBOARD LAYOUT

PRICE

CHANGE

5

4

3

2

1

10

9

8

7

6

MISC

FUNC

CONV

#

TAX

RFND

CANCEL

TAX

SHIFT

VOID

RCPT

PAGE

UP

PAGE

DOWN

ENTER

#/TM

CASH

@

FOR

7

4

1

#

0

PLU/UPC

CL

89

56

2

3

00

Customer display

(Pop-up type)

Operator display

Contrast control

Power switch

Mode switch

Keyboard

AMT

INQ

SHIFT

15

20

TEND

14

19

13

18

12

11

MDSE

17

16

AUTO

FS

FS

AUTO

NEXT

NS

CHK#CH

SBTL

CA/AT

SBTL

2) KEY TOP NAME

Standard key top

KEY TOP DESCRIPTION

0-9,00 Numeric keys

Decimal Point key

CL Clear key

@/FOR Multiplication key

RECEIPT

JOURNAL

PAGE UP Page up key

PAGE DOWN Page down key

CANCEL Cancel key

ENTER Enter key

RFND Refund Key

RCPT Receipt print Key

TAX SHIFT Tax 1 shift key

VOID Void Key

PLU/UPC PLU/UPC code entry key

AUTO1, 2 Automatic sequencing 1 and 2 keys

MISC FUNC Miscellaneous function key

CONV# Currency conversion menu key

CHK# Check Menu Key

CH# Charge Menu Key

SBTL Subtotal Key

CA/AT Cash / amount tendered key

(Dept) 1 to 22 Department 1 to 22 Keys

CASH# Cashier number entry

FS SHIFT Food stamp shift key

FS TEND Food stamp tender key

NS No sale key

TAX Manual tax key

NEXT $ Next higher dollar key

MDSE SBTL Merchandise subtotal key

AMT Amount entry key

#/TM Non-add code/Date & Time display key

INQ Inquiry key

1

2

$

#

PRICE CHANGE UPC price change key

Receipt paper feed key

Journal paper feed key

Cursor keys

Page 3

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

Optional key top

KEY TOP DESCRIPTION

000 Numeric Key

(D-PLU) 1 to 123 Direct PLU 1 to 123 Keys

(Dept) 21 to 99 Department 21 to 99 Keys

%1 to 5 Percent 1 to 5 keys

(-)1 to 5 Discount 1 to 5 keys

CH1 to 9 Charge 1 to 9 keys

CASH MENU Cash menu key

FUNC. MENU Function menu key

RP SEND Remote printer send key

GRT EX Gratuity exempt key

CA2 to 5 Cash 2 to 5 keys

CONV1 to 4 Conversion 1 to 4 keys

RA1 to 2 Received-on-Account 1 and 2 keys

PO1 to 2 Paid out key 1 and 2 keys

AUTO3 to 25 Automatic sequencing 3 and 25 keys

CHK1 to 5 Check 1 to 5 keys

P1 to 6 Price level shift 1 to 6 keys

LEVEL1 to 5 Menu level shift 1 to 5 keys

GD1 to 3 SHIFT Group discount shift 1 to 3 keys

CASH TIP Cash tip key

CHARGE TIP Charge tip key

TIP PAID Tip paid key

EAT IN1 to 3 Eat in 1 to 3 keys

TAX2 to 4 SHIFT Tax 2 to 4 shift keys

SCALE Scale e n try key

OPEN TARE Tare entry key

BAL Balance ke y

DEPOSIT Deposit key

DEPOSIT RF Deposit refund key

DEPT# Department number key

BACK SPACE Back space key

TRANS OUT Transfer out key

TRANS IN Transfer in key

RCP SW Receipt ON/OFF key

WASTE Waste mode key

BS Bill separation key

BT Bill totalize / bill transfer key (CHECK-ADD)

PRINT Val idation print key

BILL Bill print key

PAST VOID Past void key

SBTL VOID Subtotal void key

GDSC %1 to %3 Group discount %1 to 3 keys

COVER CNT Cover count key

N.C New check key

KEY TOP DESCRIPTION

C_NEXT Condiments next key

EDIT TIP Edit tip key

RP ROUND Repeat round key

PLU MENU1 to 50 PLU menu 1 to 50 keys

MACRO1 to 4 Macro 1 to 4 keys

UPSIZE Upsize key

CAP.1 to 10 Data capture 1 to 10 keys

GLU RECALL Table # recall key

MSG1 to 5 Message 1 to 5 keys

MSG# Message menu Key

DELETE Delete key

TRAY SBTL Tray subtotal key

RTN Return key

GAS SBTL Gasoline sales subtotal key

REPEAT Repeat key

IND. PAYMENT Individual payment key

CUST Customer code entry key

BIRTH Birthday entry key

TABLE # Table no. (seat no.) entry key

VOID MENU Void menu key

RFND SALE Refund sale key

P-SHIFT# Price shift menu key

FINAL Tentative finalization key

LEVEL# PLU level shift menu key

SRVC Service key

GLU Guest Look-up key

Page 4

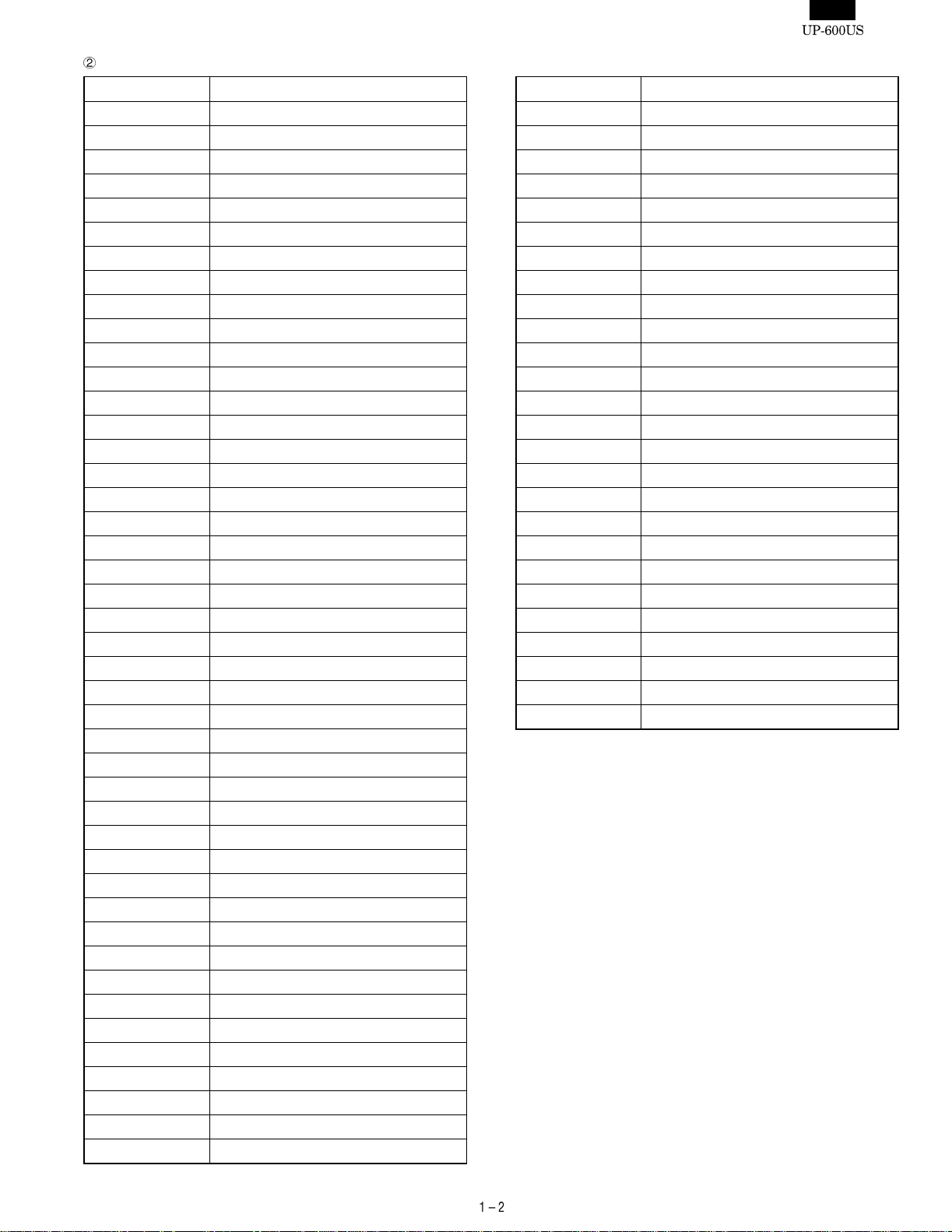

3) PROGRAMMING KEY LAYOUT

3. DISPLAY

A

L

R

X

@

FOR

7

4

1

89

56

2

0

CL

00

G

B

C

D

3

E

F

M

S

Y

H

N

I

O

J

P

K

Q

Z

T

U

V

CA/AT

W

: The shaded area contains the character keys which are

used for programming characters.

KEY TOP DESCRIPTION

SHIFT Used for programming characters.

Entering upper-case letters

You can enter an upper-case letter by using this

key. Press this key just before you enter the

upper-case letter. You should press this key each

time you enter an upper-case letter.

DC Used for programming characters.

Entering double-size characters

This key toggles the double-size character mode

and the normal-size character mode. The default

is the normal-size character mode. When the

double-size character mode is selected, the letter

"W" appears at the bottom of the display.

INS Used for programming characters.

To select a text editing mode

Toggles between the insert mode ("_") and the

overwrite mode ("■").

DEL Used for programming characters.

To delete a character or figure

Deletes a character or figure in the cursor position.

BACK SPACE Used for programming characters.

To delete a character or figure

Backs up the cursor for deleting the character or

figure at the left of the cursor. When your POS

terminal is in the insert mode, this key deletes the

character or the value at the cursor position.

Used to move the cursor.

ENTER Used to program each setting.

TL Used to finalize programming.

CANCEL Used to cancel programming and to get back to

the previous screen.

PREV

RECORD

Used to go back to the previous record, e.g. from

the department 2 programming window back to

the department 1 programming window.

NEXT

RECORD

Used to go to the next record, for example, in

order to program unit prices for sequential

departments.

PAGE DOWN Used to scroll the window to go to the next page.

PAGE UP Used to scroll the window to go back to the

previous page.

CL Used to clear the last setting you have

programmed or clear the error state.

Used to toggle between two or more options.

SBTL Used to list those options which you can toggle by

] key.

the [

RECALL Used to call up a desired code.

Numeric keys Used for entering figures.

SBTL

1) OPERATOR DISPLAY

•

Screen example 1 (REG mode)

Server code

Scroll guidance:

Mode name

Time

Numeric entry

Price level shift indicator

(P1-P6)

PLU level shift indicator

(L1-L5)

When a transaction information

occupies more than 5 lines, scroll

key(s) appears to indicate you can

scroll to the direction.

Status area 1:

Sales information

area:

Sales information

you have just entered

such as items and

prices will appear

between 2nd line and

6th line.

Total is always appear

at 7th line.

Status area 2:

: Shows the PLU/UPC price level

currently selected.

: Shows the PLU level currently se-

lected.

Receipt shift indicator (r) : Shows the receipt shift status.

Stock alarm indicator ( ! ) : Appears when the stock of the PLU

which you entered is zero, negative

or reaches the minimum stock.

Electronic message indicator (M)

Receipt ON/OFF status indicator (R)

: Appears when an electronic mail is

received. (Status 1 area)

: Appears when the receipt ON-OFF

function signs OFF.

Sentinel mark (X) : Appears in the lower right corner of

the screen when the cash in drawer

exceeds a programmed sentinel

amount.

The sentinel check is performed for

the total cash in drawer.

• Screen example 2 (PGM mode)

Programming item

information area

Programming area:

Programmable items

are listed.

Caps lock indicator

(A/a):

Double-size character mode

indicator (W):

Appears when the double-size

character mode is

selected during text programming.

The upper-case letter “A”

appears when caps lock is on,

and the lower-case letter “a”

appears when caps lock is off

during text programming.

Page 5

Screen save mod e

When you want to save the electric power or save the display’s life,

use the screen save function. This function can turn the LCD off when

a server does not operate the POS terminal for an extended period of

time. You can program the time for which your POS terminal should

keep the normal status (in which the backlight is "ON") before it goes

into the screen save mode.

To go back to the normal mode, press any key.

Device type LCD display

Dot format 320(W) x 240(H) Full dot

Dot size 0.24 (W) x 0.21 (H) mm

Dot space 0.02 mm

Dot color White

Back color Dark blue

2) DISPLAY ADJUSTMENT (OPERATION DISPLAY)

You can adjust the contrast of the display by using the contrast

control, and also you can adjust the display angle. Pull up t he tab, the

display will head up.

Tab

Contrast control

Turning the control backwards

darkens the display and

turning it forwards lightens the

display.

The backlight in the display is a consumable part.

When the LCD display may no longer be adjusted and becomes

darker, you should change the backlight.

3) CUSTOMER DISPLAY (Pop-up-type)

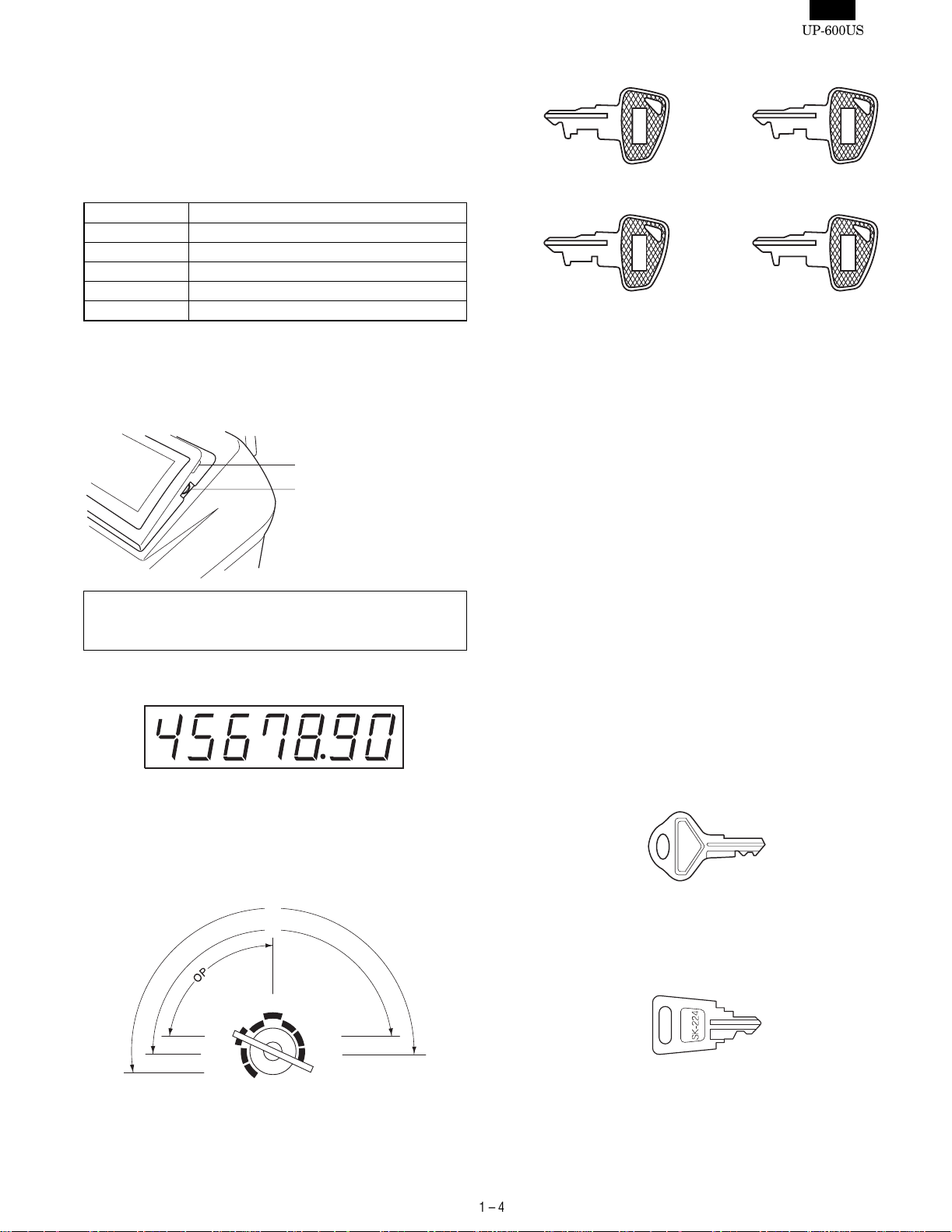

• Manager key (MA)

• Operator key (OP)

MA

OP

• Submanager key (SM)

SM

• Service key (SRV)

SRV

The mode switch has these settings:

OFF: This mode locks all register operations.

No change occurs to register data.

OP X/Z: This setting allows cashiers/clerks to take X or Z reports for

their sales information. (This setting may be used only

when your register has been programmed for "OP X/Z

mode available" in the PGM2 mode.)

REG: For entering sales

PGM1: To program those items that need to be changed often:

e.g., unit prices of departments, PLUs or UPCs, and percentages

PGM2: To program all PGM1 items and those items that do not

require frequent changes: e.g., date, time, or a variety of

register functions

MGR: For manager’s and submanager’s entries

The manager can use this mode to make entries that are

not permitted to be made by cashiers/servers -for example,

after-transaction voiding and override entry.

X1/Z1: To take the X/Z report for various daily totals

X2/Z2: To take the X/Z report for various periodic (weekly or

monthly) consolidation

4. KEYS AND SWITCHES

1) MODE SWITCH AND MODE KEYS

MA

SM

X / Z

1

2

REG

MGR

X

1/Z1

X2/Z

2

OP

OFF

PGM

PGM

2) DRAWER LOCK KEY

This key locks and unlocks the drawer. To lock it, turn 90 degrees

counterclockwise. To unlock it, turn 90 degrees clockwise.

SK1-2

4) PRINTER COVER LOCK KEY

This key locks and unlocks the printer cover. To lock it, turn 90

degrees counterclockwise. To unlock, turn 90 degrees clockwise.

Page 6

5. PRINTER (DP-750)

1) SPECIFICATIONS

Part number: DP-750

•

• No. of stations: 2

• Printing system: Mechanical serial dot

• Direction of printing: Bidirectional

• Printing capacity: Receipt – 24 characters

Journal – 24 characters

Validation – 55 characters (one line only)

• Character size: 1.36 (W) 2.75 (H) mm at 7 7 dots

Print pitch:

Column distance 1.59 mm

Row distance 4.23 mm

• Total number of dots: Receipt – 108 dots/216 positions

Journal – 108 dots/216 positions

Validation – 248 dots/495 positions

• Font: 7 7 dots (including half dot)

Space between characters – 1 dot (2 positions)

• Distance between dots: 0.353 mm (H) 0.353 mm (W)

• Print speed: Approx. 3.0 lines/sec.

• Paper feed speed: Receipt – Approx. 30 lines/sec.

Journal – Approx. 30 lines/sec.

• Reliability: MCBF – 4 million lines (excluding the

print head)

Head life – 50 million characters (at 4

dots/1 character/1 pin)

• Validation form sensor: Not available

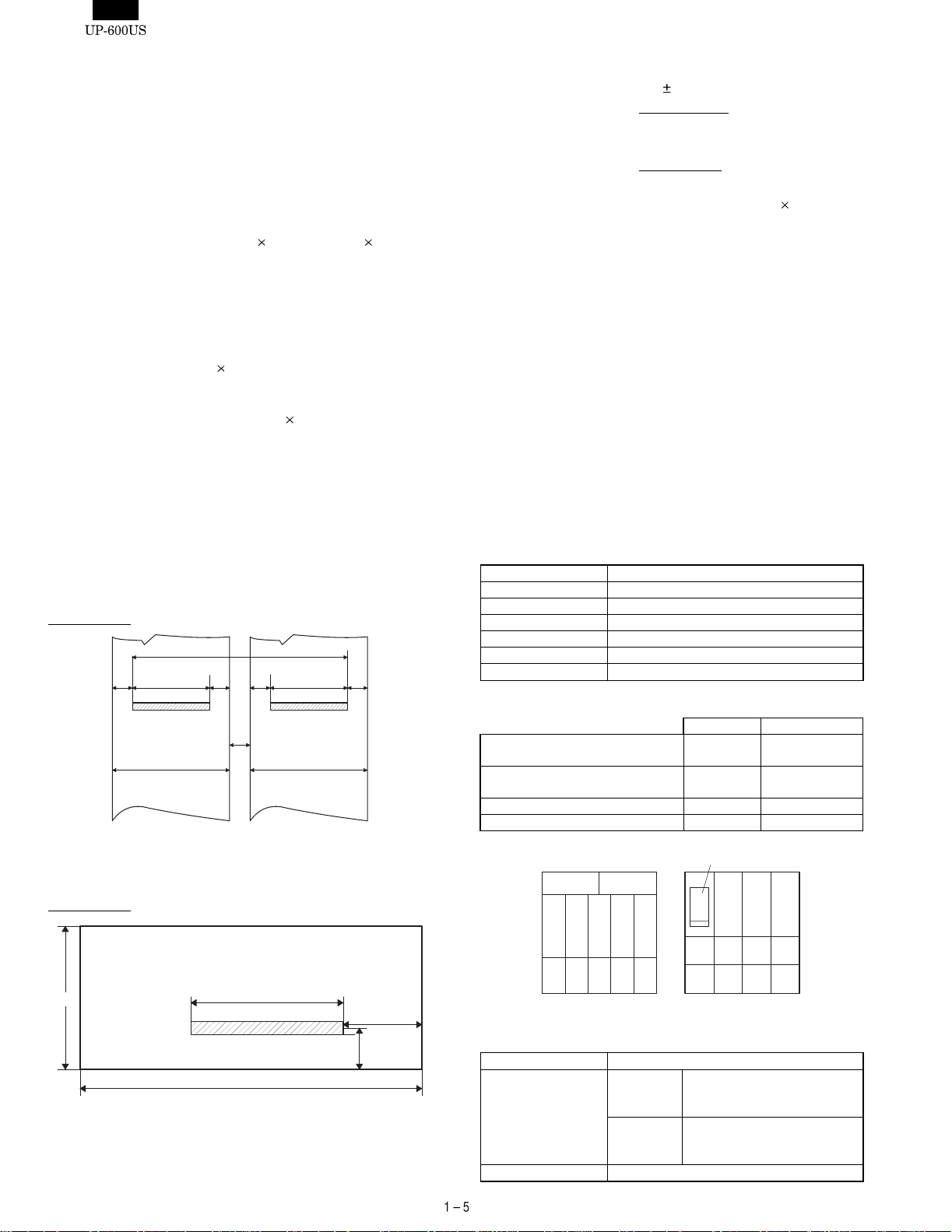

2) PRINTING AREA

Receipt/journal

87.08

3.56 3.56 3.56

37.87

4.2

44.5± 0.5

RECEIPT JOURNAL

Fig. 5-1

37.87

44.5± 0.5

3.56

Unit : mm

3) PAPER

•

Paper roll dimensions: 44.5 0.5mm in width, 83mm in diameter

• Paper quality: Journal/ Receipt

Bond paper (paper thickness: 0.06 to

0.09mm, paper weight: 52.3 to 64g/m

Validation form

Thickness: 0.07 to 0.14mm

Size:130mm or more (W)

70mm or more (H)

4) INKING

•

Ink supply system: Ink ribbon

• Form: Cartridge/Endless ribbon

• Specification: Material – Nylon

• Ribbon life: Approx. 6 million characters

• Print color: Purple

5) LOGO STAMP : None

6) CUTTER

• Method: Manual

6. DRAWER

1) SPECIFICATION

(1) Drawer box and drawer

Model name SK-460

Size 445 (W) x 464 (L) x 118 (H)

Color GRAY 368

Material Metal

Bell —

Release lever Standard equipment; Front key

Drawer open sensor Standard equipment

2) MONEY CASE

U version A version

Separation from the drawer

Allowed

Separation of the coin

compartments from the money case

Bill separator No Standard (1 pcs)

Number of compartments 7B/5C 4B/8C

Allowed Allowed

Disallowed Disallowed

Bill separator

2

)

Validation form

70

87.0 (PRINT AREA)

130

Fig. 5-2

20

22

Unit : mm

3) LOCK

Location of the lock Front

Method of locking

and unlocking

Key No. SK1-2

Locking: Insert the drawer lock key into

Unlocking: Insert the drawer lock key into

A version : 4B/8CU version : 7B/5C

the lock and turn it 90 degrees

counterclockwise.

the lock and turn it 90 degrees

clockwise.

Page 7

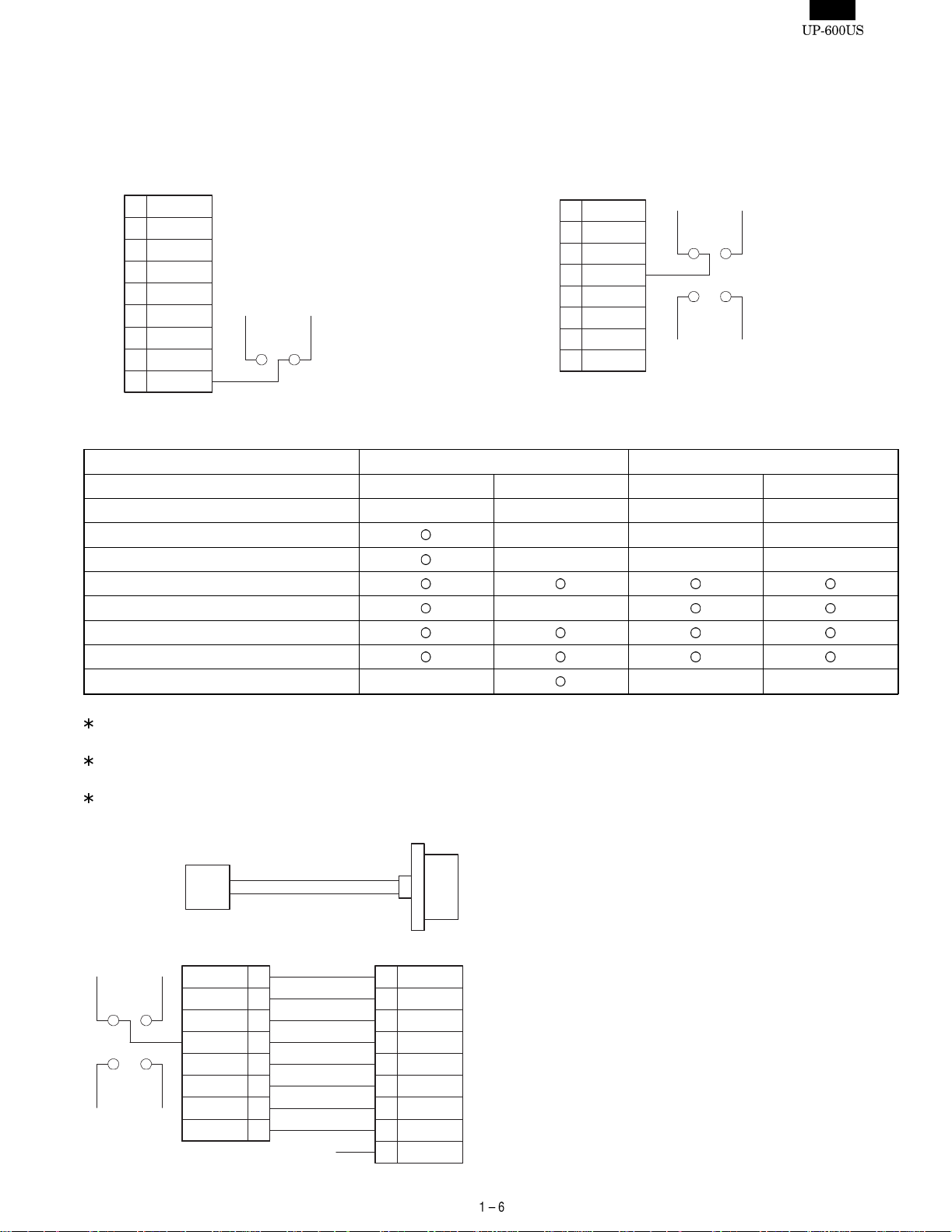

7. RS232 INTERFACE

This machine has two RS232 standard ports for communication to PC, Hand scanner (ER-A6HS1) and etc.

1) PORT 1 (CH1) (CN402)

Connector type: D-SUB 9pin

Data rate: max. 38,400 bps

/CD

1

2

RD

3

SD

/ER

4

5

GND

/DR

6

/RS

7

/CS

8

VCC(+5V)

/CI

S401

2) PORT2 (CH2) (CN403)

Connector type: Modular jack RJ45 8pin

Data rate: max. 115,200 bps

/RS

1

2

/ER

3

SD

4

5

GND

RD

6

/DR

7

/CS

8

CD

S404

S403

GND

CI

VCC

(+5V)

9

3) OPTIONAL DEVICES THAT CAN BE CONNECTED

Standard port Option port (ER-A5RS)

Port No. Port1: CH1 Port2: CH2 Port3: Port4:

Type D-SUB 9pin Moduler RJ45 D-SUB 9pin D-SUB 9pin

CI/+5V selectable

ER-A6HS1 (+5V necessary)

Scanner (+5V not necessary)

Modem –

PC

Printer, Scale

POS utility, 02fd.exe – ––

–––

–––

The ER-A6HS1 cannot be connected to port 2, 3 and 4 because it

requires +5V.

The modem cannot be connected to port 2 because it uses a

different signal line.

For the modular RJ45 to D-Sub 9pin conversion cable, see the

following.

Moduler RJ45 D-sub 9pin

S404

S403

CI

VCC

(+5V)

/RS

/ER

SD

GND

RD

/DR

/CS

/RS

1

2

3

4

5

6

7

8

(Open)

7

4

/ER

3

SD

/CD

1

5

GND

RD

2

/RS

6

/CS

8

/CI

9

CD

GND

Page 8

Page 9

Symbol/PartsCod)

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

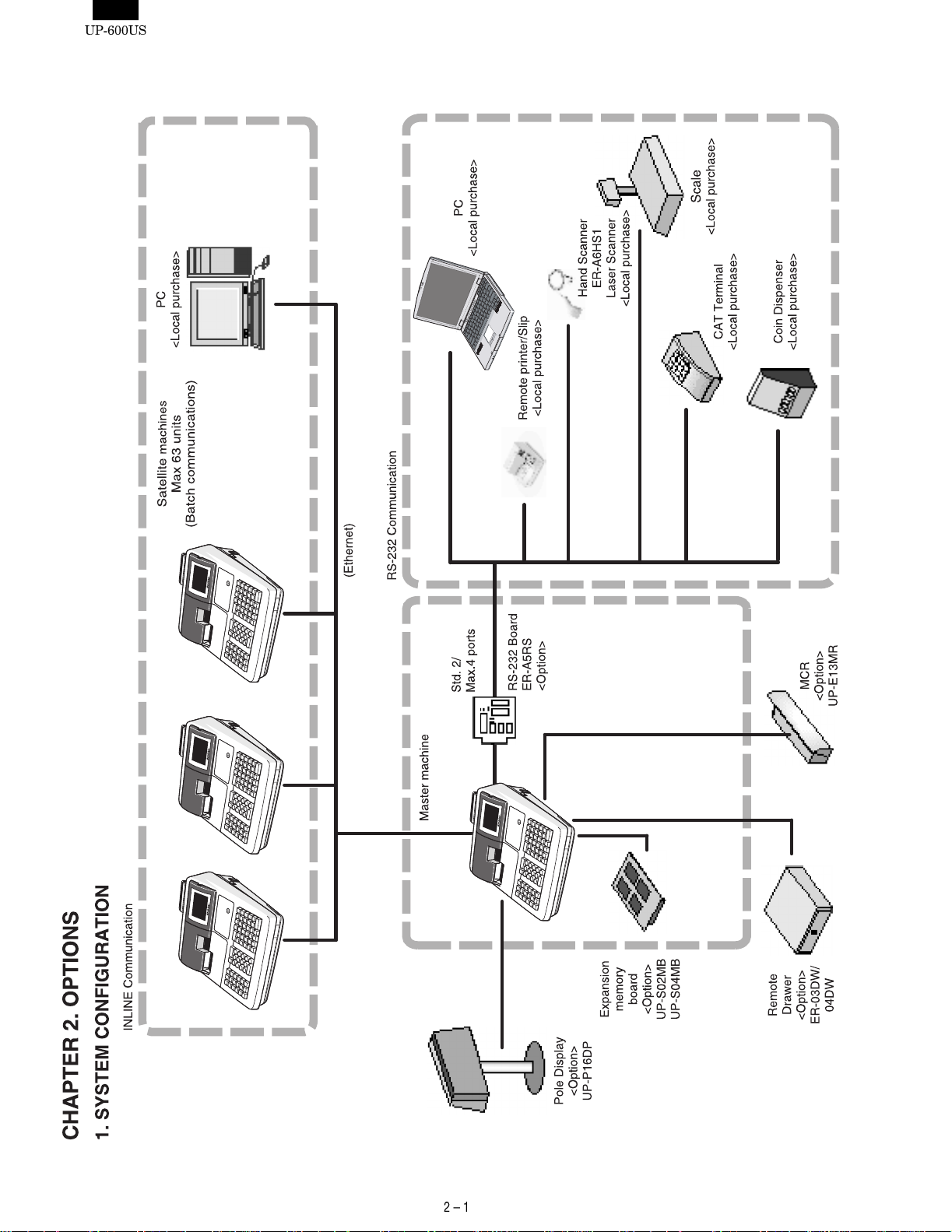

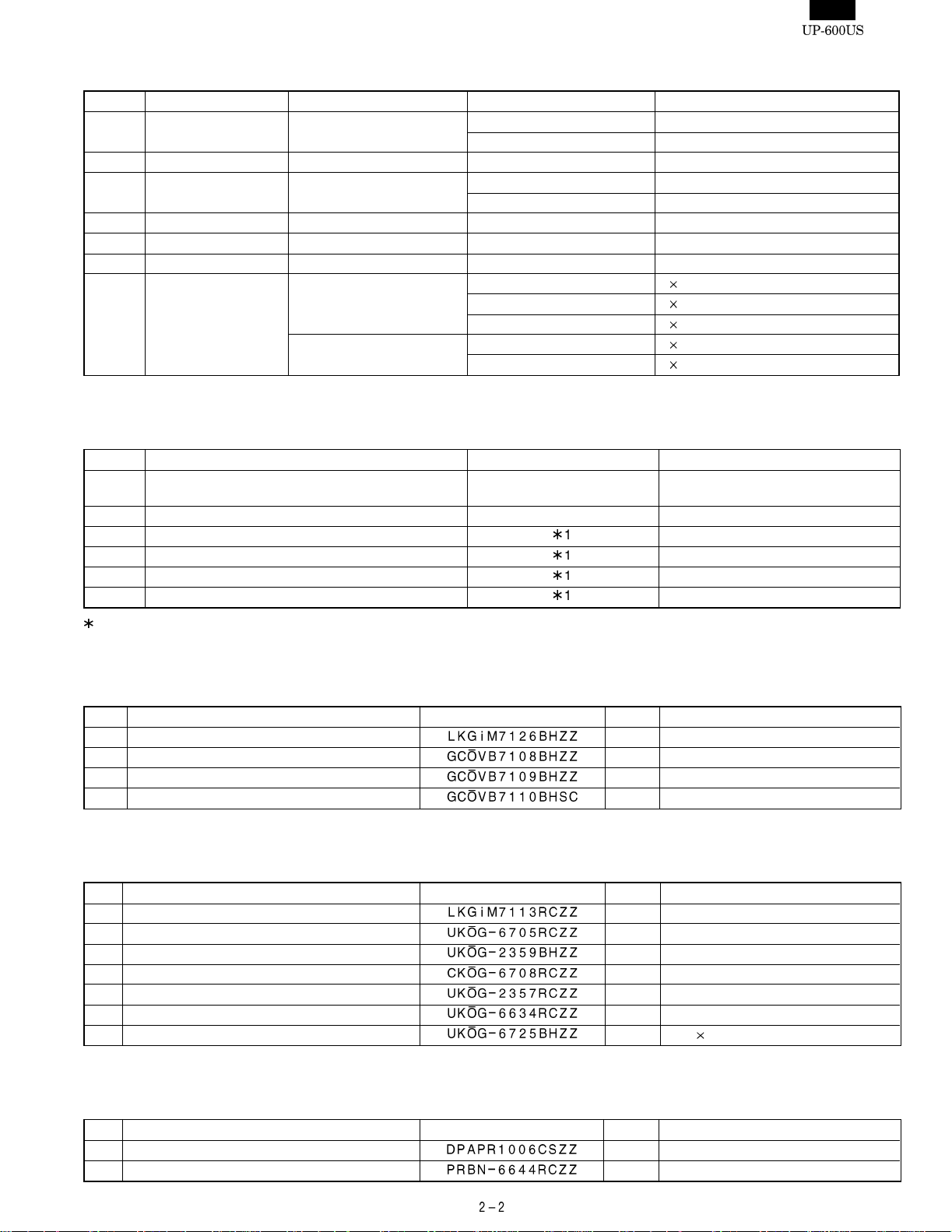

2. SALES OPTIONS

No. CLASSIFICATION COMPONENT NAME MODEL NAME REMARK

1 Memory Expansion RAM board UP-S02MB 2M bytes PS-RAM board

UP-S04MB 4M bytes PS-RAM board

2 Display Remote display (Pole type) UP-P16DP 11-Dig.7-Seg. + 16-Dig.Dot

3 Drawer Remote drawer ER-03DW 7B/5C coin case

ER-04DW 5B/5C coin case

4 On-line function RS232 I/F board ER-A5RS 2 ports RS232 I/F

5 Card reader MCR (Magnetic Card Reader) UP-E13MR ISO Type 1 : 3 stripe card

6 Scanner Bar code hand scanner ER-A6HS1

7 Expansion key kit Key top kit ER-11KT7 1

ER-12KT7 1

ER-22KT7 2

Dummy key kit ER-11DK7G 1

ER-51DK7G 5

1 Key top kit

2 Key top kit

2 Key top kit

1 Dummy key kit

1 Dummy key kit

3. LOCAL PURCHASE OPTIONS

No. COMPONENT NAME MODEL NAME REMARK

1 External printers TM-T88/85, TM-T88 (2), TM-T80

2 Slip printer TM-295

3Scale I/F

4 Coin dispenser

5 Color kitchen monitor

6 CAT terminal

1: Please consult with your Sharp regional sales manager.

TM-U200, TM-300

4. SERVI C E OP TIO N S

No. NAME PARTS CODE PRICE DESCRIPTION

1 Mode key grip cover

2 Drip proof mode switch cover

3 Drip proof keyboard cover

4 Text preset keyboard cover

AX For MA key only

BA

BF

BH

5. SERVICE TOOLS

No. NAME PARTS CODE PRICE DESCRIPTION

1 Service key

2 RS232 Loop Back Connector

3 RS232 modular Loop Back Connector

4 Expansion PWB for option board

5 MCR test card

6 Key top remover

7 Key top inst. Jig

AF

BC For RS232 D-SUB 9pin connector

BC For RS232 RJ45 Modular jack connector

BU Fo r ER-A5 RS

BL For UP-E13MR

AX

BB For 2 2 key top

6. SUPPLIES

No. NAME PARTS CODE PRICE DESCRIPTION

1 Roll paper

2 Ink libbon

AR 5 roll/pack

AZ Purple

Page 10

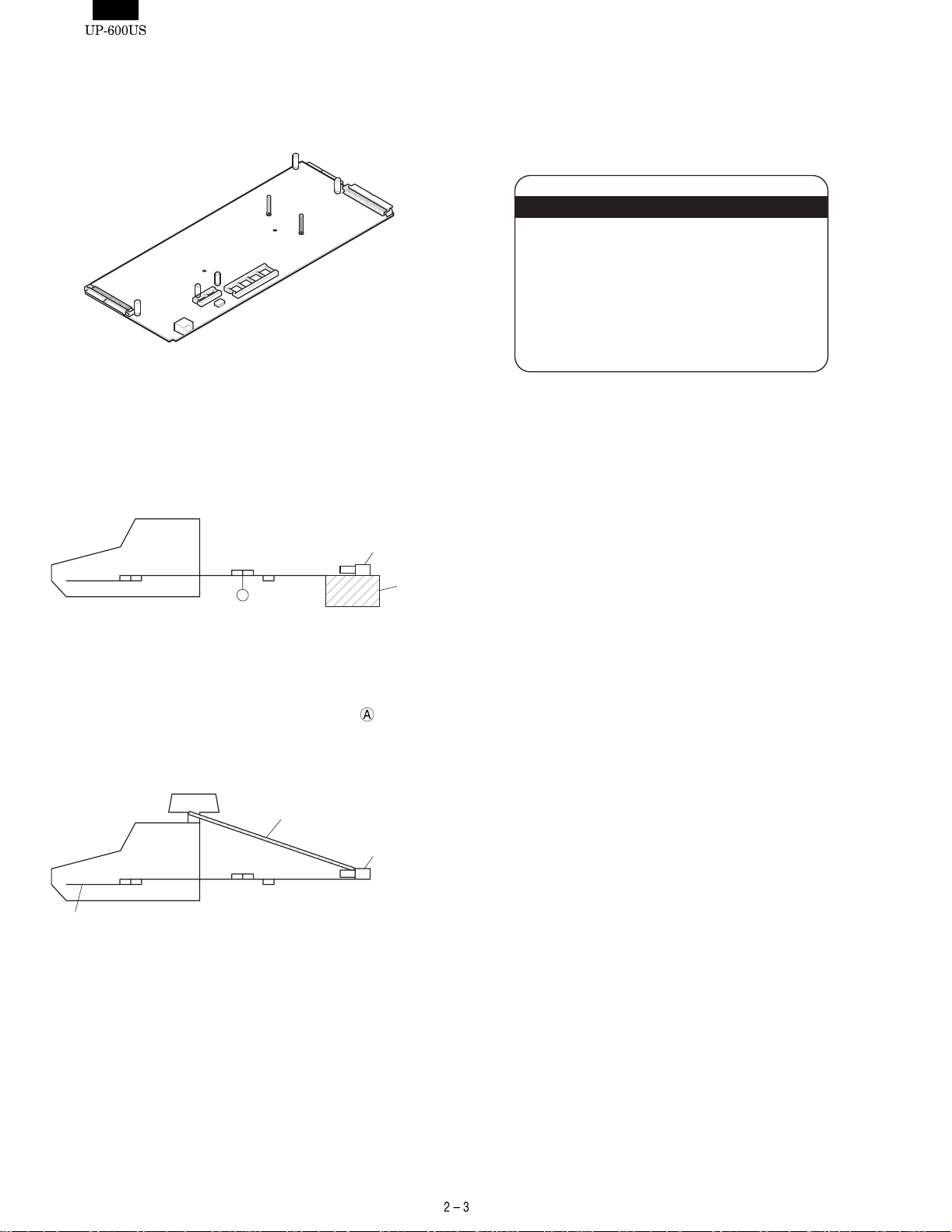

7. HOW TO USE SERVICE TOOLS

1) EXPANSION PWB : CKOG-6708RCZZ

•

External view

Purpose 1 : Used f or servicing and repairing of options (such as the

ER-A5RS) which are connected with the main body option connector.

[Procedure 1]

Use an insulator base as shown in the shaded section when performing servicing.

Main PWB

UP-600

Expansion PWB

(CKOG-6708RCZZ)

ER-A5RS

PWB

A

Loop back connectors

UKOG-6705RCZZ

Base

2) MCR TEST CARD : UKOG-2357RCZZ

•

Used when executing the diagnostics of the UP-E13MR.

• External view

To check the option I/F PWB from the solder side, connect the I/ F

PWB to OPTCN2. To check from the parts side, connect to OPTCN3.

(Note) The option I/F PWB should be held horizontally so that no

excessive stress is applied to connecting section

.

[Procedure 2]

Pop up

String

UP-600

Expansion PWB

Main PWB

Control ROM

(CKOG-6708RCZZ)

ER-A5RS

PWB

Put a string between the pop up and the option PWB. Adjust the

length of the string so that the CKOG-6708RCZZ and the option PWB

are not binding. Once verified, then you may proceed with performing

service.

Loop back connectors

UKOG-6705RCZZ

Page 11

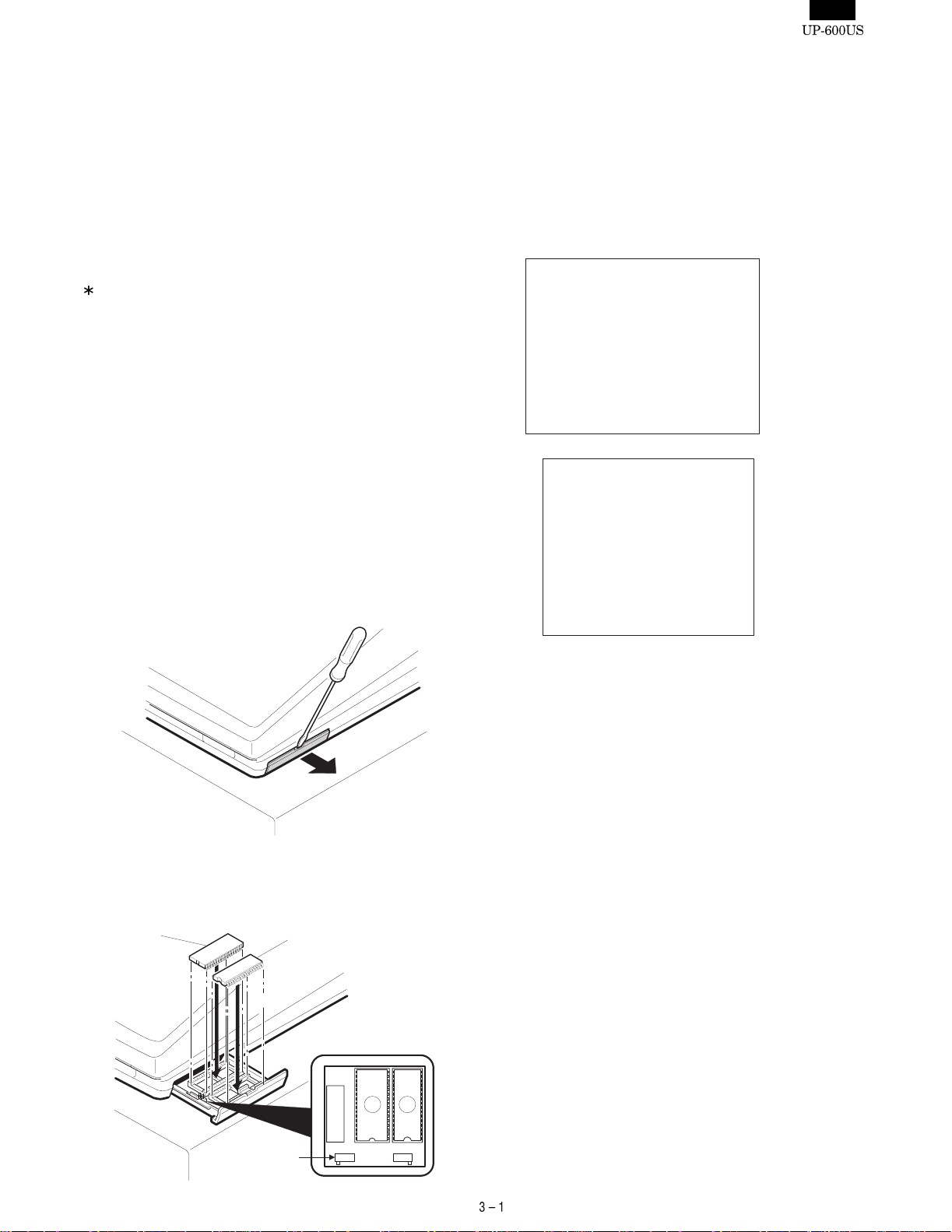

CHAPTER 3. SERVICE PRECAUTION

1. IPL (Initial Program Loading) FUNCTION

1) INTRODUCTION

The application software of the UP-600 is written in the flash ROM.

In the following cases, writing of the application software into the flash

ROM is required.

• When the flash ROM is replaced with a new one. The service part

flash ROM does not include the application software in it.

• When IPL writing is required because of a change in the software.

The service part of the main PWB unit includes the flash ROM with

the application software written in it, and there is no need for

writing the application software when replacing the main PWB unit.

2) IPL PROCEDURE

There are two ways for the IPL procedures.

• IPL from P-ROM

• IPL from PC communication (Please refer to the next section)

The detailed descriptions on the above procedures are given below.

3) IPL FROM P-ROM

Master ROM-1 : VHI27801RAS1A

Master ROM-2 : VHI27801RAT1A

Before installation, turn off the power switch on the UP-600 and unplug the AC cord from the AC outlet.

1. Insert a screwdriver into the sl it on the right side of the lower

cabinet to remove the option RAM case.

4. Place the mode key to any position except OFF or SRV’.

5. Turn on the power switch of the UP-600.

6. The following display is shown and the IPL procedure is started.

When the procedure is completed, the message of "Completed"

is shown.

IPL from PROM

Version check…

Erase …

IPL write start

26 27 28 29 2A 2B

2C 2D 2E 2F 30 31

32 33 34 35 36 37

38 39 3A 3B 3C 3D

3E 3F

Verify …

Completed.

IPL write completed

2. IPL switch (SW301) on the IPL ROM PWB: Set the IPL switch

(SW301) to the ON position.

3. Install the ROMs into the IC sockets on the IPL ROM PWB as

shown below.

ROM1 ROM2

7. Turn off the power switch of UP-600.

8. Remove to the ROMs from the IPL ROM PWB.

9. IPL switch (SW301) on the IPL ROM PWB: Set the IPL switch

(SW301) to the OFF position.

10. Perform one of the master reset procedures.

SW301

ROM1 ROM2

on off

Page 12

Symbol/PartsCod)

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

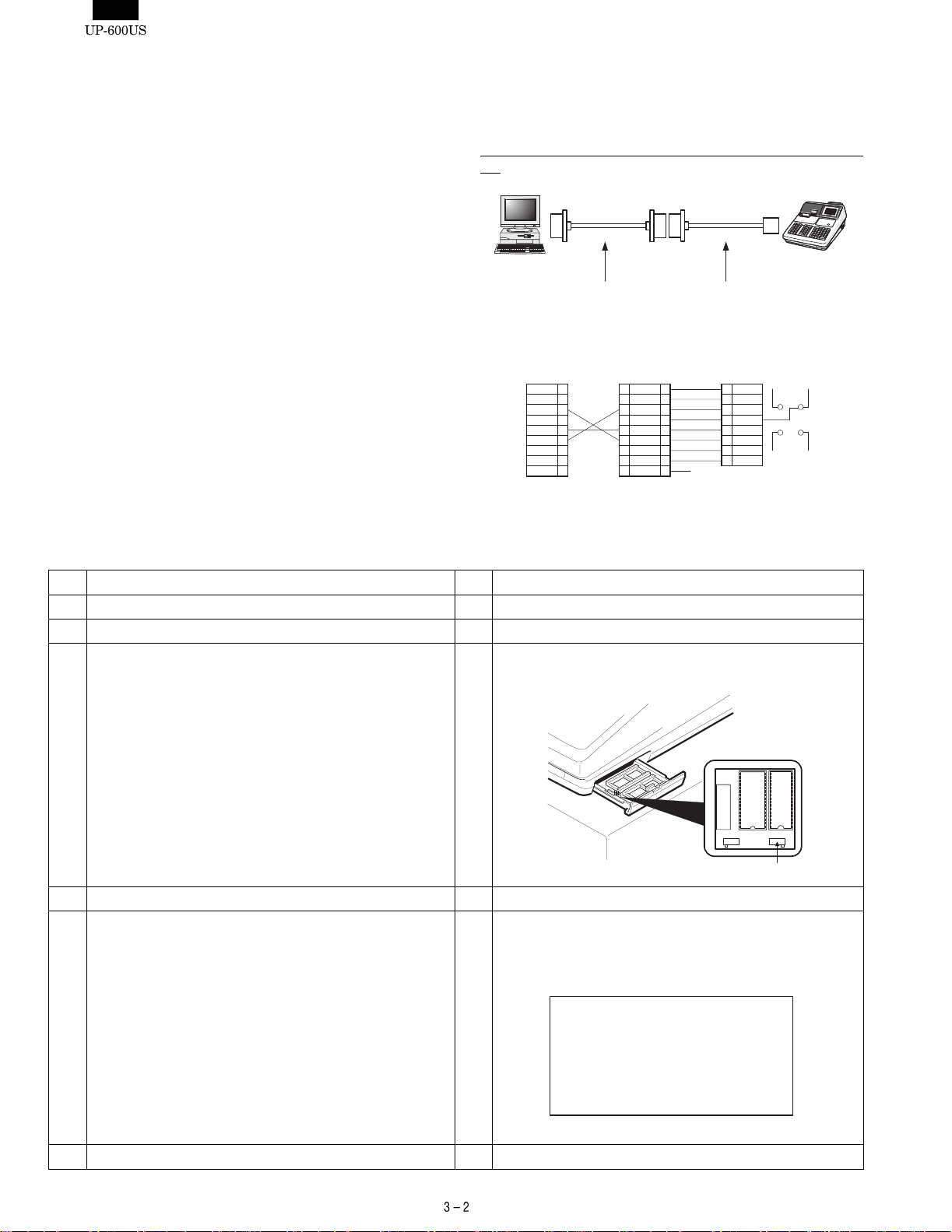

2. UP-600 UTILITY TOOLS

1) OUTLINE

This Specification document describes the explanation about " POSUTILITYTOOL.EXE and "02FD.EXE".

"POSUTILITYTOOL.EXE"and "02FD.EXE" works on Windows 95/98

of PC and they have the following

Functions by connecting UP-600 with RS232.

POSUTILITYTOOL.EXE : IPL of UP-600 Program Object

02FD.EXE : All RAM Data Upload/Download

(PC software tool instead of the current ER-02FD.)

3) PROCEDURE

3) -1. POS UTILITY

2) CONNECTION

PC and UP-600 are connected by RS232.

Connect the CH2 port of the UP-600 t o the RS-232 interface of the

PC.

CI

VCC

(+5V)

S404

S403

UP-600:CH2

CD

GND

PC

D-SUB 9pin - D-SUB 9pin

cable

RS232 Cable Connecting:

[PC]

D-sub 9pin

7

4

3

SD

1

5

GND

2

RD

6

8

9

D-sub 9pin

/RS

7

/ER

4

3

/CD

1

GND

5

2

/DR

6

/CS

8

/CI

9

D-SUB 9pin - modular RJ-45

conversion cable

[UP-600]

(Open)

Moduler RJ45

/RS

1

/ER

2

SD

3

4

GND

5

RD

6

/DR

7

/CS

8

7

4

3

SD

1

5

2

RD

6

8

9

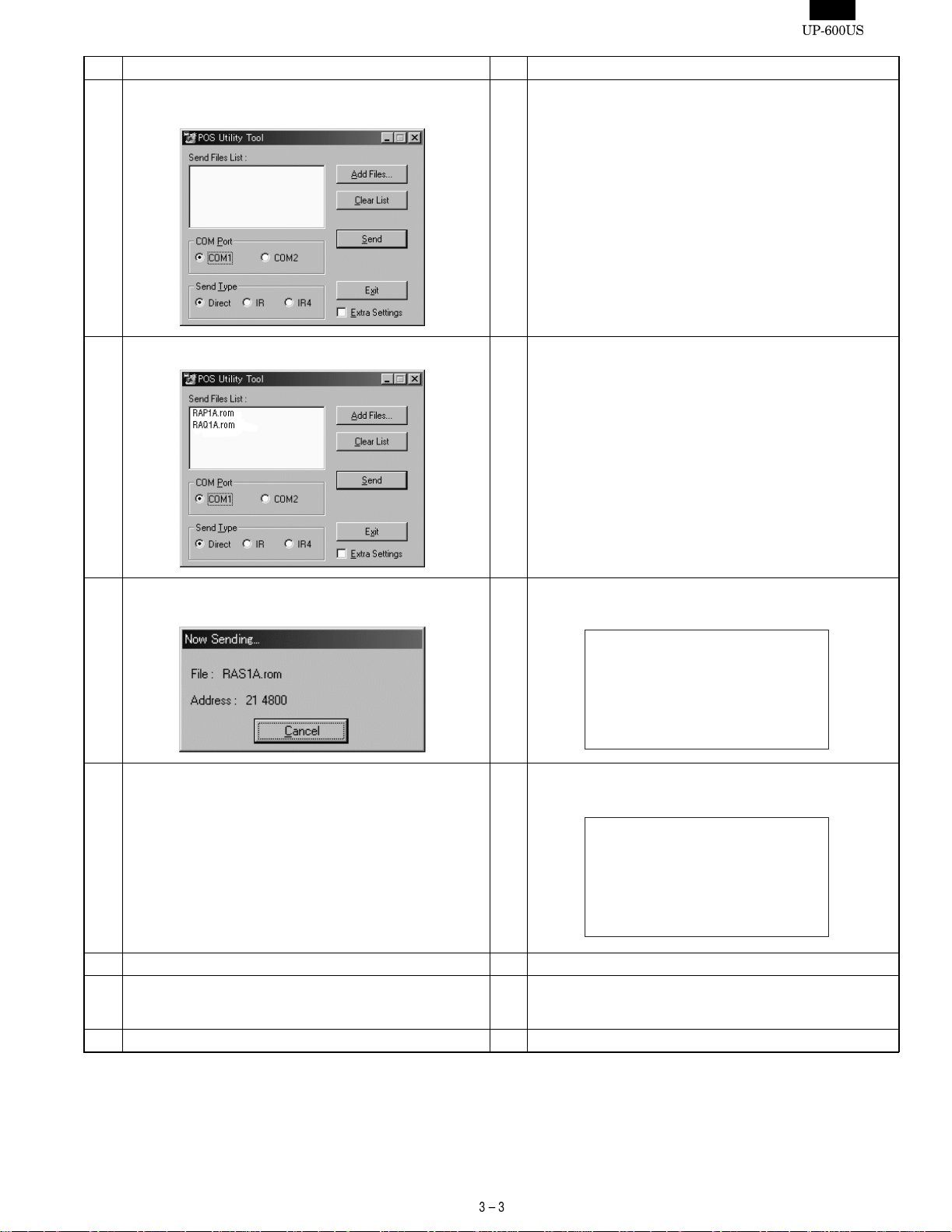

No Procedure on P.C. side No Procedure on UP-600 side

1 Install the "POSUTILITYTOOL.EXE" on the P.C.

2 Turn OFF the power.

3 Select "IPL Mode".

Set the "IPL Switch" (SW302) of the UP-600 to "ON".

on off

4 Turn ON the power.

5 Starting of "IPL Mode".

The UP-600 displays

"IPL from Serial I/O"

IPL from Serial I/O

on off

SW302

6 Connect the P.C. and the UP-600 (CH2) via RS232. (Fig 1)

Page 13

No Procedure on P.C. side No Procedure on UP-600 side

7 Execute the "POSUTILITUTOOL.EXE" on the P.C.

*Please close all other applications while using this utility.

8 Select the ROM object Files by clicking the "Add Files.." button.

9 Push the "SEND" button.

Program data is sent to the UP-600 automatically.

10 When data sending is completed,

the initial Window is shown after "Complete" window.

Program data is received from the P.C. automatically.

9

The UP-600 displays.

IPL from Serial I/O

Connected IRDA 115200

21 22 23 24 25 26 27 28

The UP-600 displays

10

"Completed."

IPL from Serial I/O

Connected IRDA 115200

21 22 23 24 25 26 27 28

29 2A 2B 2C 2D 2E 2F

Completed.

IPL from Serial I/O

Connected IRDA 115200

30 31 32 33 34 35 36 37

38 39 3A 3B 3C 3D 3E 3F

Completed.

11 Turn OFF the power.

Select "Normal Mode".

12

Set the "IPL swit ch" to "OFF".

(Ref. Hardware manual)

13 Execute the "Service Reset" on UP-600.

Page 14

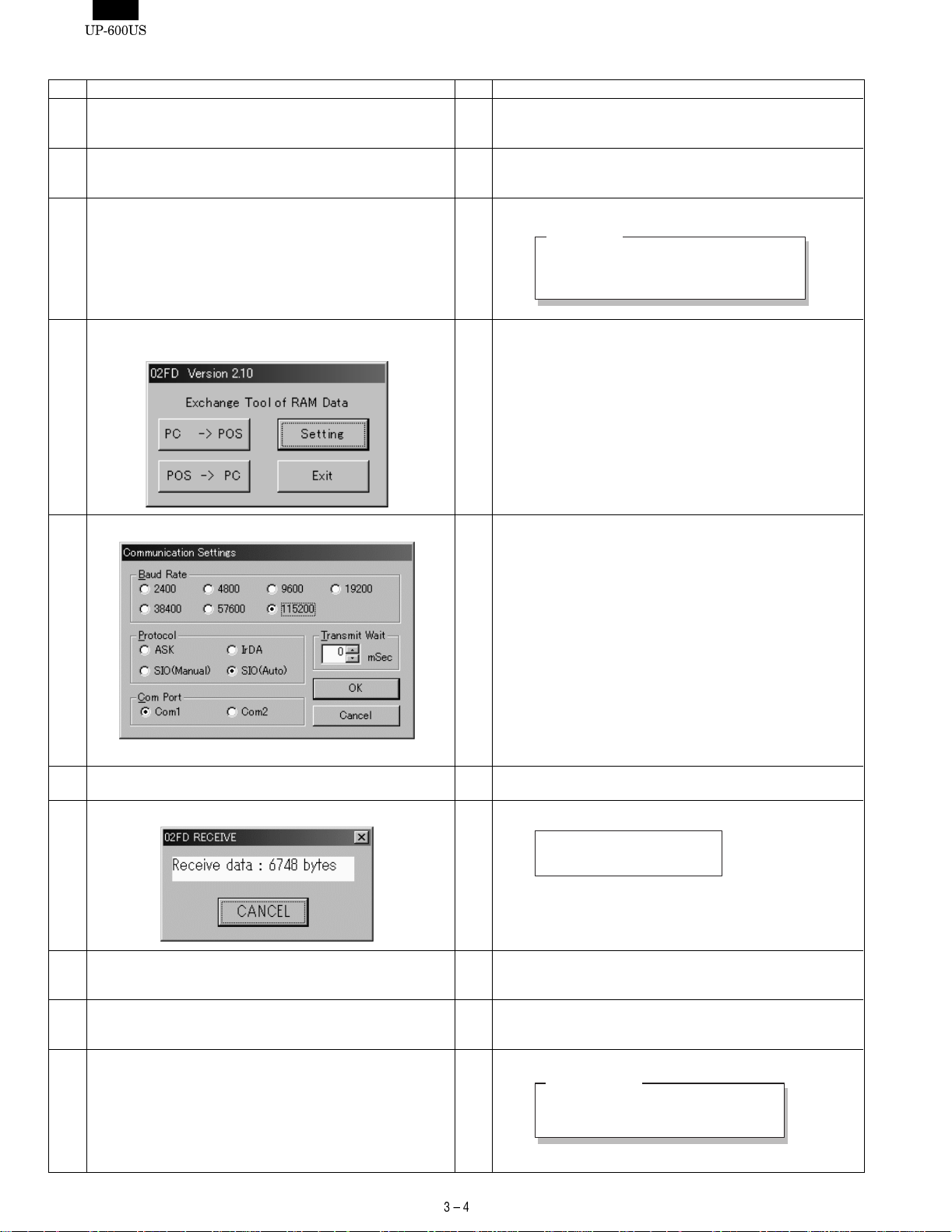

3) -2. 02FD

No Procedure on P.C. side No Procedure on UP-600 side

1 Install the "02FD.EXE" on the P.C.

ALL RAM Data UpLoad : Go to "2"

ALL RAM Data DownLoad : Go to "9"

2 ALL RAM Data UpLoad

Connect the P.C. and the UP-600 (CH2) via RS232. (Fig 1)

4 Execute the "02FD.EXE" on the P.C.

*Please close all other applications while using this utility.

2 Enter the SRV mode.

Select " 2 SETTING ".

Select " 14 BACKUP SEND"

3 The UP-600 displays

BACKUP SEND

SEND DATA ALL RAM

SPEED PROGRAMMED SPEED

5 Set the Communication method by pushing the "Setting" Button.

Push the "OK" Button.

6 Push the "Receive Start" Button.

And Select the Receiving File.

7 Communication starts. 7 Push CA/AT key. The UP-600 displays

SENDING 00000

8 The UpLoad is completed.

The initial Window is shown.

8 The UpLoad is completed.

The SETTING menu is shown.

Push the "Exit" Button.

9 ALL RAM Data UpLoad

Connect the P.C. and the UP-600 (CH2) via RS232. (Fig 1)

9 Enter the SRV mode.

Select " 2 SETTING".

Select " 15 BACKUP RECEIVE"

10 The UP-600 displays

BACKUP RECEIVE

SPEED PROGRAMMED SPEED

Push the CA/AT key.

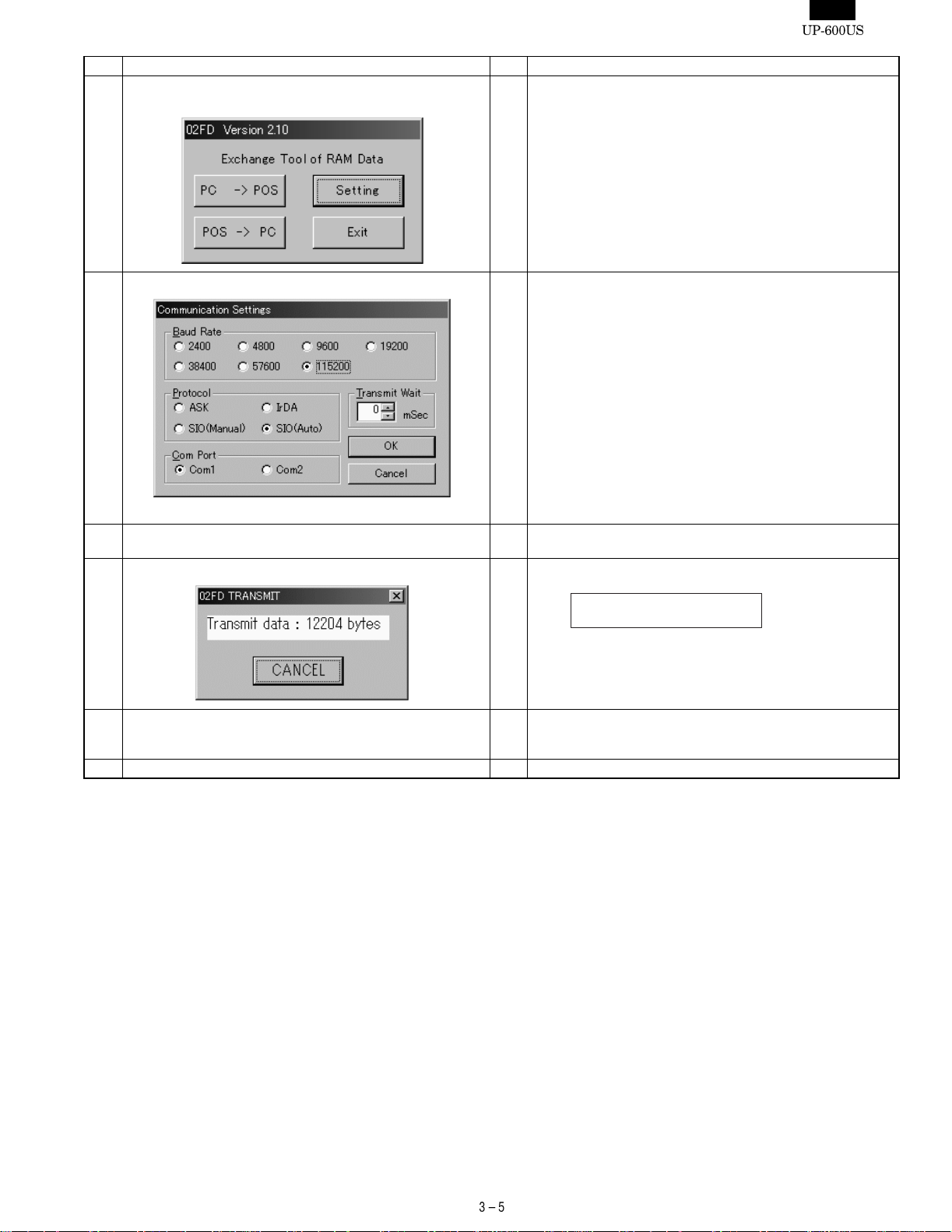

Page 15

No Procedure on P.C. side No Procedure on UP-600 side

11 Execute the "02FD.EXE" on the P.C.

*Please close all other applications while using this utility.

12 Set the Communication method by pushing the "Setting" Button.

Push The "OK" Button.

13 Push the "Transmit Start" Button.

And Select the Sending File.

14 Communication starts. 14 The UP-600 displays

15 The DownLoad is completed.

The initial Window is shown.

Push the "Exit" Button.

3. NOTE FOR HANDLING OF LCD

• The LCD elements are made of glass. Use extreme care when

handling the LCD.

Any strong shock applied to the LCD can cause damage.

• If the LCD element is broken and the liquid has leaked, do not

come in contact with it. If the liquid is attached to your skin or cloth,

immediately clean with soap.

• Use the unit under the rated conditions to prevent against damage.

• Be careful not to drop water or other liquids on the display surface.

• The reflection plate and the polarizing plate are easily scratched.

Be careful not to touch them with hard objects such as glass,

tweezers, etc. Never hit, push, or rub the surface with hard objects.

• When installing t he unit, be careful not t o apply stress to the LCD

module. If excessive stress is applied, abnormal display or uneven

color may result.

RECEIVING 00000

15 The DownLoad is completed.

The SETTING menu is shown.

16 Execute the " Service Reset " on the UP-600

Page 16

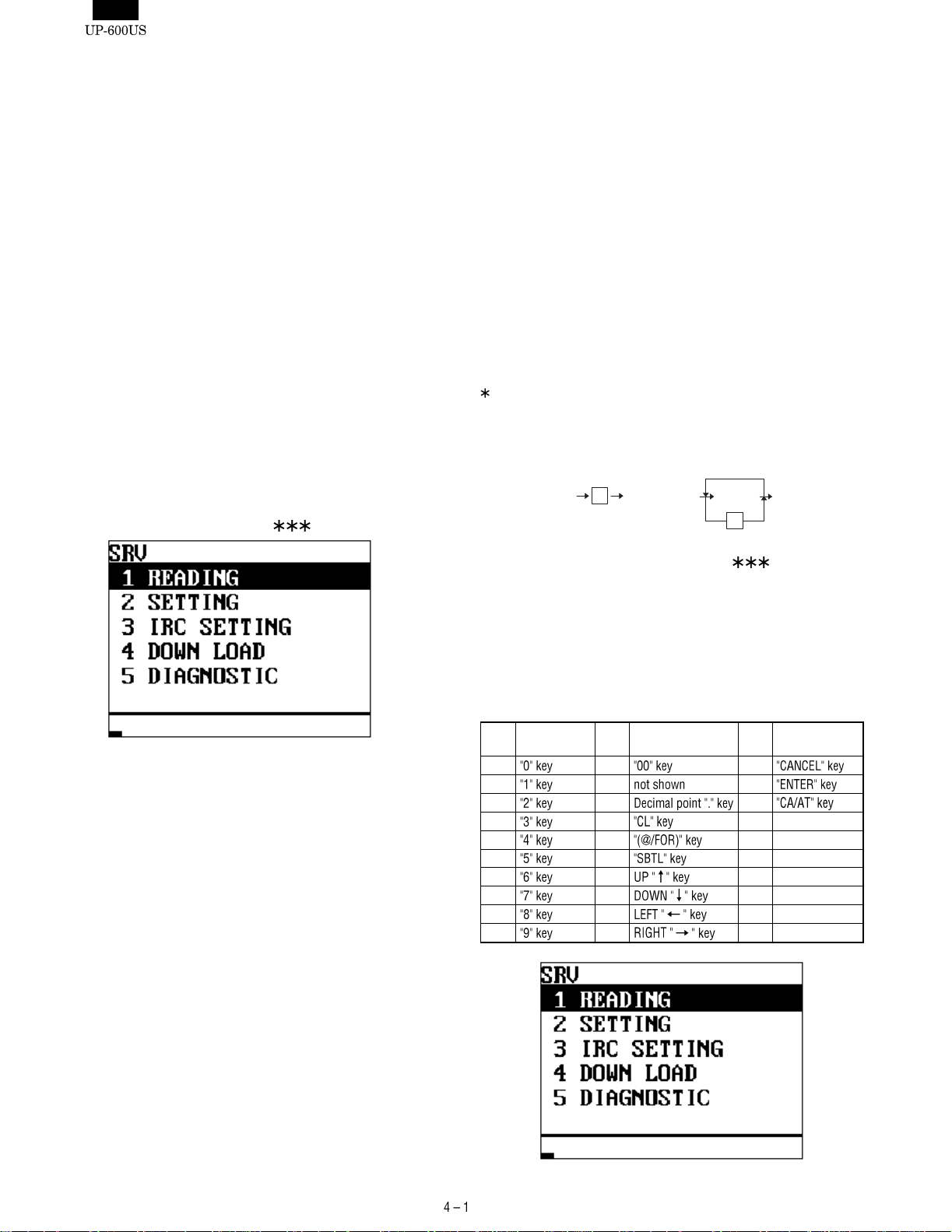

CHAPTER 4. SRV. RESET AND MASTER RESET

The SRV key is used for operating in the SRV mode.

1. SRV. RESET (Program Loop Reset)

Procedure

• Method 1

1) Turn off the AC switch.

2) Set the mode switch to (SRV’) position.

3) Turn on the AC switch.

4) Turn to (SRV) position from (SRV’) position.

• Method 2

1) Set the mode switch to PGM2 position.

2) Turn off the AC switch.

3) While holding down the JOURNAL FEED and RECEIPT FEED

keys, turn on the AC switch.

Note: When disassembling and reassembling always power up us-

ing method 1 only. Method 2 will not reset the CKDC9.

Note: SRV programming job#926-B must be set to a "4" to allow the

PGM program loop reset.

PRG. RESET

MRS-2 (Master resetting 2)

Used to clear all memory and keyboard contents.

This reset returns all programming back to defaults. The keyboard

must be entered by hand.

This reset is used if an application needs a different keyboard layout

other than that supplied by a normal MRS-1.

Procedure

1) Turn off the AC switch.

2) Set the MODE switch to the (SRV’) position.

3) Turn on the AC switch.

4) While holding down the JOURNAL FEED and RECEIPT FEED

keys, turn to the (SRV) position from the (SRV’) position.

5) Key position assignment:

After the execution of a MRS-2, only the RECEIPT FEED and

JOURNAL FEED keys can remain effective on key assignment.

Any key can be assigned on any key position on the main keyboard.

[key setup procedure]

0

Disable

*2

Free key setup

complete.

*1

MRS-2 executed Key position set Free key

0

2. MASTER RESET (All memory clea r)

There are three possible methods to perform a master reset.

MRS-1 (Master resetting 1)

Used to clear all memory contents and return the machine back to its

initial setting s .

Returns the keyboard to the default layout.

Procedure

1) Turn off the AC switch.

2) Set the MODE switch to the (SRV’) position.

3) Turn on the AC switch.

4) While holding down the JOURNAL FEED key, turn to the

(SRV) position from the (SRV’) position.

MASTER RESET

NOTES:

*1: When the 0 key is pressed, t he key of the key number on the

display is disabled.

*2: Push the key on the position to be assigned. With this, the key of

the key number on the display is assigned to that key position.

*3: When relocating the keyboard, the PGM 1/2 modes use the

standard key layout.

Key

No.

001

002 012 022

003 013 023

004 014

005 015

006 016

007 017

008 018

009 019

010 020

Key

name

Key

No.

011 021

Key

name

Key

No.

Key

name

Page 17

Symbol/PartsCod)

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

MRS-3 (Master resetting 3)

Master resetting 3 requires the entry of Seri al No. data in addition to

Master resetting 2.

After completion of the MRS-3, the following operations and programming will be inhibited.

1. GT programming.

2. All memory download via RS-232.

3. GT resets with Z report. (Z report can be made, but the GT will not

be reset.)

Procedure

1) Turn off the AC switch.

2) Set the reset switch to the "SRV" position.

3) Turn on the AC switch.

4) While holding down the JOURNAL FEED key and MRS-3 key,

turn to the (SRV) position from the (SRV’) position.

MRS-3 key : UP-600=[CANCEL] key

UP-700=[PLU72] key

5) The product serial No. input window is displayed as shown

below.

DISPLAY:

SERIAL No. 00000000

Enter the product serial No. of this POS and enter the [CA/AT]

key.

6) Key position assignment:

After the execution of MRS-3, only the RECEIPT FEED and

JOURNAL FEED keys can remain effective on key assignment.

Any key can be assigned on any key position on the main keyboard.

[key setup procedure]

0

Disable

*2

Free key setup

complete.

*1

MRS-2 executed Key position set Free key

0

MASTER RESET

NOTES:

*1: When the 0 key is pressed, t he key of the key number on the

display is disabled.

*2: Push the key on the position to be assigned. With this, the key of

the key number on the display is assigned to that key position.

*3: When relocating the keyboard, the PGM 1/2 modes the use

standard key layout.

Key

No.

001

002 012 022

003 013 023

004 014

005 015

006 016

007 017

008 018

009 019

010 020

Key

name

Key

No.

Key

name

Key

No.

011 021

Key

name

Page 18

CHAPTER 5. DIAGNOSTICS SPECIFICATIONS

1. GENERAL DESCRIPTION

This Diag Program consists of a number of Diag. programs for the

UP-600, which facilitate the PWB check, process check and the operation check of the system during servicing.

The Service Diag. programs are all contained in the standard ROM.

2. SYSTEM COMPOSITION

UP-600 only

UP-600

Fig 2-1. Service

3. DIAG.

Starting the Diag. Program

The Diag. Program is written on the external ROM, which is executed

by the CPU (H8/510) and runs on the following conditions:

The logic power supply is normal.

(+5V, VCKDC, POFF, +24V)

Both the I/O pins of the CPU and the CPU internal logic are

normal, and the CKDC9 and MPCA9, system bus, and standard

ROM/RAM are normal.

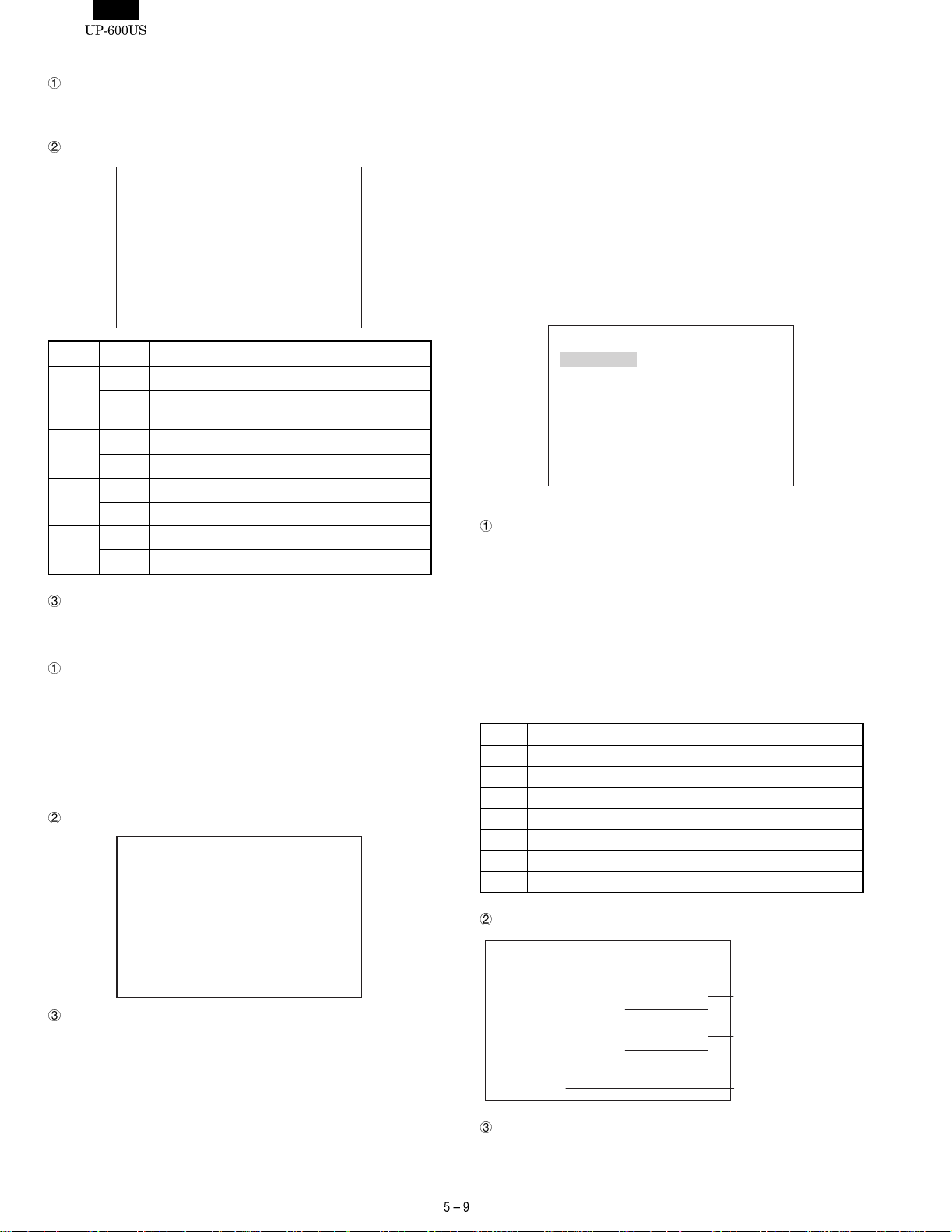

1) EXECUTING DIAG PROGRAM

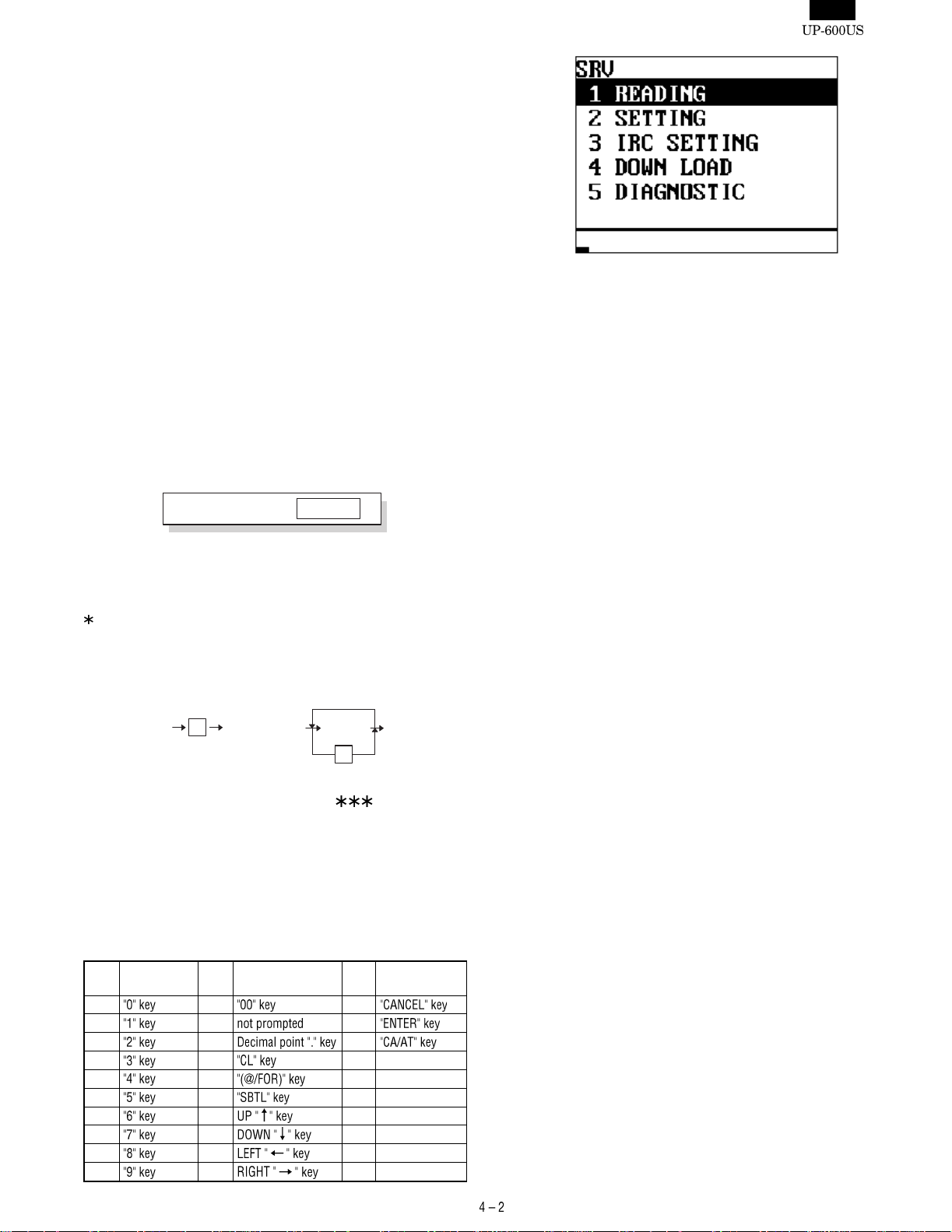

To start the Diag. Program, enter the SRV mode. Select the option

item DIAGNOSTICS from the MENU using the cursor keys and press

the ENTER key.

The DIAG. MAIN MENU appears on the screen as shown below. The

cursor is displayed in reverse video and can be moved using the

up/down arrow keys. Move the cursor to the menu item you want and

press the ENTER key to execute the corresponding Diag. program.

When each Diag. program is completed, the screen returns to the

DIAG. MAIN MENU. Press the CANCEL key to exit the Diag. Program and the screen returns to the SRV mode menu screen.

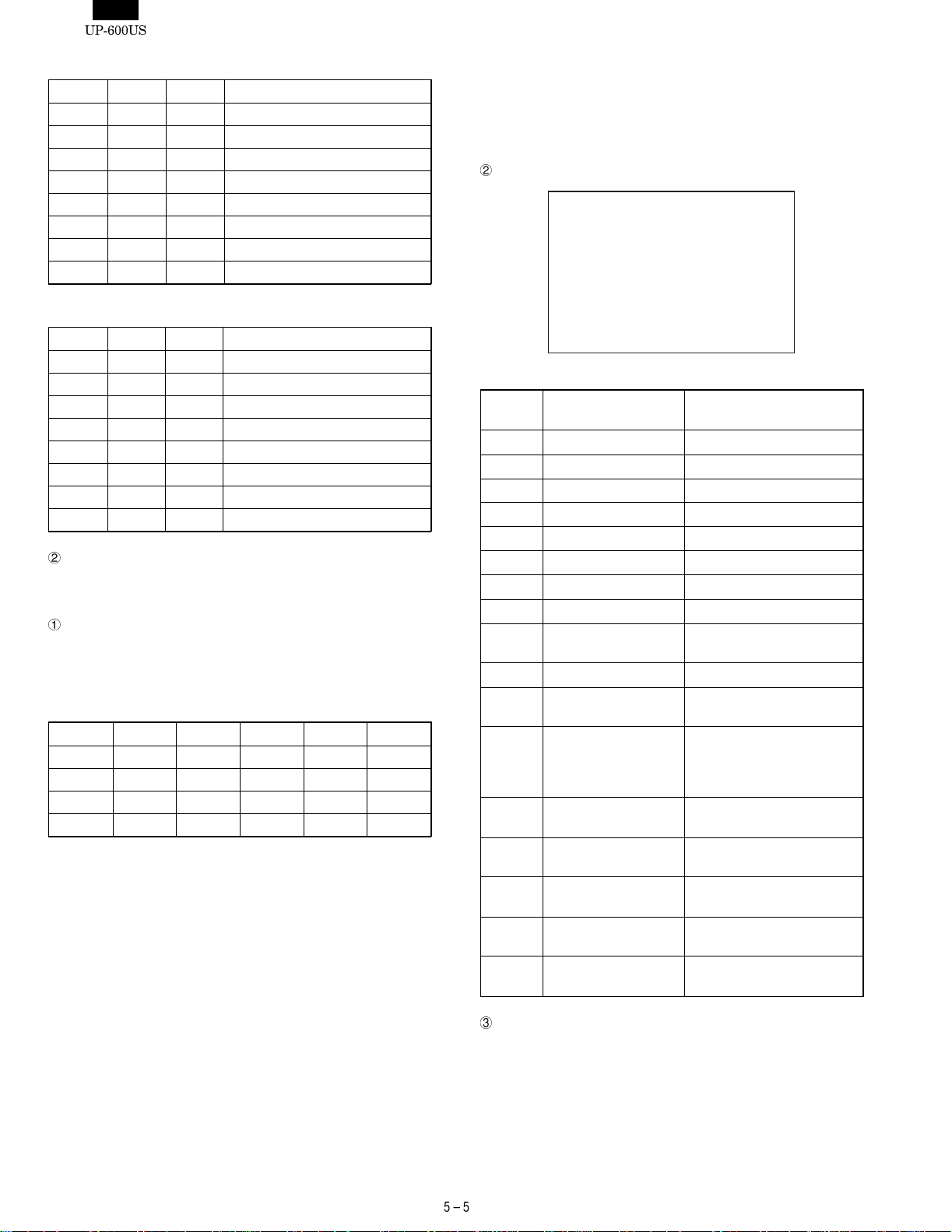

UP-600 DIAG V1.0A

PRODUCT&TEST

RAM&ROM&SSP

CLOCK&KEY&SWITCH

SERIAL I/O

DISPLAY&PRINTER

MCR&DRAWER

TCP/IP

2) RAM & ROM & SSP DIAGNOSITCS

This program tests the standard RAM, expanded RAM, standard and

service ROMs, and SSp circuit. RAM&ROM&SSP is selected on the

MAIN MENU, the following sub-menu screen appears. The cursor

shown in reverse video can be moved using the up/down arrow keys.

Move the cursor to the menu item you want and press the ENTER

key to execute the corresponding program. Press the CANCEL key to

return the screen to this submenu.

RAM&ROM&SSP DIAG

Standard RAM Check

UP-S04MB Check

UP-S02MB Check

Standard ROM Check

Service ROM Check

SSP Check

2)-1. Standard RAM check

Checking

The program performs the following checks on the standard

512KB of RAM. Data in memory remains unchanged before and

after the checks.

The following operations are performed for the memory addresses

to be checked (780000H - 7FFFFFH).

PASS1 : Save data in memory

PASS2 : Write data "0000H"

PASS3 : Read and compare data "0000H" and write data "5555H".

PASS4 : Read and compare data "5555H" and write data "AAAAH"

PASS5 : Read and compare data "AAAAH"

PASS6 : Return data into memory

If any comparison is not normal during the check sequence from

PASS 1 through 6, the error message appears.

If any error is not found up to the final address, the sequence

ends normally.

Then, another round of address checks is carried out using the

above check sequence

If an error occurs, the error message appears and the check

stops. The read/write of the address where the error occurs is

repeated.

Check point address = 780000H, 780001H

780002H, 780004H

780008H, 780010H

780020H, 780040H

780080H, 780100H

780200H, 780400H

780800H, 781000H

782000H, 784000H

788000H, 790000H

7A0000H, 7C0000H

Page 19

Symbol/PartsCod)

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

Display

The capacity checked is displayed in units of 64KB.

Standard RAM Check

512KB:PASS!!(or ERROR!!)

Error:XXXXXXH

Write:XXXXH

Read:XXXXH

The error address and bit are displayed only when an error occurs

(They are not displayed if there is no error.)

How to exit the program

You can exit the program by pressing the CANCEL key after the

results are displayed.

2)-2. UP-S02MB Check

Checking

The program checks for the presence of the UP-S02MB in the

following procedure.

Data in memory remains unchanged before and after checking.

i. Write 55AAH in 9FFFFEH.

ii. Read 9FFFFEH and compare the data with 55AAH. If both

data are correct and BFFFFEH is the same as 55AAH, the

following tests are performed. If not correct, the message

"0KB: ERROR!!" appears and checking ends.

The following checks are performed on the UP-S02MB.

The following operations are performed for the address space to

be checked (800000H - 9FFFFFH).

PASS1 : Save data in memory.

PASS2 : Write data "0000H".

PASS3 : Read and compare data "0000H" and write data "5555H".

PASS4 : Read and compare data "5555H" and write data "AAAAH".

PASS5 : Read and compare data "AAAAH".

PASS6 : Return data into memory.

If any comparison is not normal during the check sequence from

PASS 1 through 6, the error message appears.

If any error is not found up to the final address, the sequence

ends normally.

Then, another round of address checks is carried out using the

above check sequence.

If an error occurs, the error message appears and the checking

stops. The read/write of the address where the error occurs is

repeated.

Check point address = 800000H, 800001H

800002H, 800004H

800008H, 800010H

800020H, 800040H

800080H, 800100H

800200H, 800400H

800800H, 801000H

802000H, 804000H

808000H, 810000H

820000H, 840000H

880000H, 900000H

Display

The capacity checked is displayed in units of 64KB.

UP-S02MB Check

2048KB:PASS!!(or ERROR!!)

Error:XXXXXXH

Write:XXXXH

Read:XXXXH

The error address and bit are displayed only when an error occurs

(They are not displayed if there is no error.)

How to exit the program

You can exit the program by pressing the CANCEL key after the

results are displayed..

2)-3. UP-S04MB Check

Checking

The program checks for the presence of the UP-S04MB in the

following procedure. Data in memory remains unchanged before

and after checking.

i. After writing 55AAH in BFFFFEH, write AA55H in 9FFFFEH.

ii. Read BFFFFEH and compare the data with 55AAH. Data in

BFFFEH is correct, the following checks are perf ormed. Data

read is AA55H, the message "UP-S02MB!!" appears and the

check ends. If the data read is not either 55AAH or AA55H, the

message "0KB:ERROR!!" appears and the check ends.

The following checks are performed on the UP-S04MB.

The following operations are performed for the address space to

be checked (800000H - BFFFFFH).

PASS1 : Save data in memory.

PASS2 : Write data "0000H".

PASS3 : Read and compare data "0000H" and write data "5555H".

PASS4 : Read and compare data "5555H" and write data "AAAAH".

PASS5 : Read and compare data "AAAAH".

PASS6 : Return data into memory.

If any comparison is not normal during the check sequence from

PASS 1 through 6, the error message appears.

If any error is not found up to the final address, the sequence

ends normally.

Then, another round of address checks is carried out in the above

check sequence.

If an error occurs, the error message appears and the checking

stops. The read/write of the address where the error occurs is

repeated.

Check point address = 800000H, 800001H

800002H, 800004H

800008H, 800010H

800020H, 800040H

800080H, 800100H

800200H, 800400H

800800H, 801000H

802000H, 804000H

808000H, 810000H

820000H, 840000H

880000H, 900000H

A00000H

Page 20

Display

The capacity checked is displayed in units of 64KB.

UP-S04MB Check

4096KB:PASS!!(or ERROR!!)

Error:XXXXXXH

Write:XXXXH

Read:XXXXH

The error address and bit are displayed only when an error occurs

(They are not displayed if there is no error.)

How to exit the program

You can exit the program by pressing the CANCEL key after the

results are displayed.

2)-4. Standard ROM Check

Checking

The standard ROM area (200000H - 3FFFFFH) is added in units

of bytes. When the lowest 2 digits of the result is 20H, it is regarded as normal.

In addition, the ROM version and model name code stored in the

addresses 31FFE0H - 31FFFFH where the ROM version and

checksum correction data are stored are displayed. Data (ASCII)

is stored in the following formats:

31FFE0H~31FFEFH : Model name CODE (Example: "UP-600",

to be displayed until DATA becomes 00H.)

31FFF0H~31FFF9H : 27801R****(****=PROGRAM VERSION)

31FFFAH~31FFFBH : BLOCK NO.("20"~"3F")

31FFFCH : TERMINATOR ("=")

31FFFDH~31FFFEH : BLOCK VERSION (Example: "00")

31FFFFH : CHECK SUM correction DATA

FLASH ROM used as the standard ROM has 64K-byte-unit rewrite BLOCKs. To perform VERSION management in the BLOCK

unit, these BLOCKs have the same 16 byte organizati on as those

after the previous 31FFF0H and arranged every 64KBYTE. At this

time, the checksum for each BLOCK is corrected to be 01H so

that the entire 2MBYTE become a total of 20H.

Regarding the display of the PROGRAM VERSION, the FLASH

write MASTER EPROM has 8Mbits chips to allow management of

the block units of the chip. The PROGRAM VERSION stored in

blocks at 21H and 31H are displayed.

0 PAGE (BLOCK) where the IPL is stored, displays the PROGRAM VERSION of the IPL to make it possible to manage individual programs.

Display

The capacity checked is displayed in units of 64KB.

Service ROM Check

PASS!!(or ERROR!!)

APL: 27801R****

27801R****

IPL:**

JOURNAL print

BLOCK Version.

20=** 21=** 22=** 23=**

24=** 25=** 26=** 27=**

. . . . . . . . . . .

3C=** 3D=** 3E=** 3F=**

How to exit the program

You can exit the program by pressing the CANCEL key after the

result of checking is displayed.

2)-5. SERVICE ROM Check

Checking

The SERVICE ROM area composed of two EPROMs (D00000H -

EFFFFFH) is added in units of bytes for each chip. If the lowest 2

digits are 10H, it is regarded as normal.

In addition, the ROM version and model name code stored in the

addresses D1FFE0H - D1FFFFH where the ROM version and

checksum correction data are stored are displayed. Data (ASCII)

is stored in the following formats:

D1FFE0H~D1FFEFH : Model name CODE(Example: "UP-600",

to be displayed until data is 00H.)

D1FFF0H~D1FFF9H : 27801R****(****=PROGRA M VERS I ON)

D1FFFAH~D1FFFBH : BLOCK NO.("20"~"2F")

D1FFFCH : TERMINATOR("=")

D1FFFDH~D1FFFEH : BLOCK VERSION(Example:"00")

D1FFFFH : CHECK SUM correction DATA

This SERVICE ROM is used to write data into FLASH ROM and if

any error occurs during rewriting of the FLASH ROM, it is not

possible to resume operations. Its configuration is the same as the

standard ROM.

0 PAGE (BLOCK) where the IPL is stored displays the PROGRAM VERSION of the IPL to make it possible to manage individual programs.

Display

The capacity checked is displayed in units of 64KB.

Service ROM Check

ROM1:PASS!!(or ERROR!!)

ROM2:PASS!!(or ERROR!!)

APL: 27801R****

27801R****

IPL:**

JOURNAL print

BLOCK Version.

20=** 21=** 22=** 23=**

24=** 25=** 26=** 27=**

. . . . . . . . . . .

3C=** 3D=** 3E=** 3F=**

How to exit the program

You can exit the program by pressing the CANCEL key after the

result of checking is displayed.

Page 21

2)-6. SSP Check

Checking

When started, this check program automatically sets the test SSP,

performs the SSP check and displays the results.

The SSP check sets check d ata in the empty space in t he SSP

entry register. After checking is completed, only the check data is

erased. Any setting remains intact before and after this check

program is executed.

Display

SSP Check

PASS!!(or ERROR!!)

How to exit the program

You can exit the program by pressing the CANCEL key after the

results are checking is displayed.

3) TIMER & KEYBOARD & CLERK SWITCH

DIAGNOSTICS

This program checks the operation of t he CKDC’s clock crystal, keyboard and tests the clerk switch and mode switch.

You can return to the Diag menu screen by pressing the CANCEL

key.

3)-4. Mode Switch Check

Checking

The mode switch position code is displayed in a hexadecimal

number.

SRV:0, PGM2:1, PGM1:2, OFF:E, OP X/Z:3, REG:4, MGR:5,

X1/Z1:6, X2/Z2:7

Intermediate code:E, Multiple error F

4) RS232 I/F DIAGNOSTICS

The program tests the RS232 interface for the main PWB and the

optional board ER-A5RS. Attach a 9-pin D-sub loop back connector

(UKOG-6717RCZZ) wired as shown in Fig. 3-11, to the port you are

going to test.

1pinCD

2pinRD

3pinSD

4pinER

5pinGND

6pinDR

7pinRS

8pinCS

9pinCI

Fig. 3-11. Wiring diagram of loop back connector (UKOG-6717RCZZ)

The following menu appears on the screen. The cursor shown in

reverse video can be moved using the up/down arrow keys. Move the

cursor to the menu item you want to execute and select by pressing

the Enter key to the corresponding Diag. Program. Press the CANCEL key to return the screen to this submenu.

When setting the channel for the RS232 interface, do not set more

than two ports to the same channel . The UP-600 accommodates up

to one ER-A5RS board, but use caution not to allow each port to

have the same channel; otherwise the hardware might be destroyed.

3)-1. Timer Check

Checking

Check the operation of the CKDC9’s clock crystal.

The area showing "YY/MM/DD & MM:HH" is continuously dis-

played. Check whether the display blinks in black and white every

0.5 seconds and the time shown is updated.

3)-2. Keyboard Check

Checking

The program checks the input through the keyboard of the UP-

600.

A 3-digit position code corresponding to a key pressed appears on

the screen, along with a catch sound.

3)-3. Clerk SW Check (Not for U version)

Checking

The code of the key inserted into t he cl erk key switch appears in a

decimal number.

RS232 I/F DIAG

CH1 Check

CH8 Check

When Diag. is started, the channel check is performed and only the

channels already set appear on screen.

Note: The channel numbers displayed are logical numbers on soft-

ware, In practical terms, CH1 means the CH1 of the rear connector of the POS and CH8 means the CH2 of the rear connector of the POS. If options are installed, only the ones (CH2

- CH7) which have been set will be added and displayed.

4)-1. CHANNEL Check

Checking

The screen shows only the channels for which have been set and

are connected to the ECR. Compare the channels shown on the

screen and the settings of the channel setting DIP SW of the

RS232 interface board.

The RS232 on the main PWB of the UP-600 is fixed to CH1 and

CH8. It is therefore necessary for the ER-A5RS to set the channel

to CH2 - CH7.

(Ref) ER-A5RS channel settings ("1" = SW OFF, "0" = SW ON)

Page 22

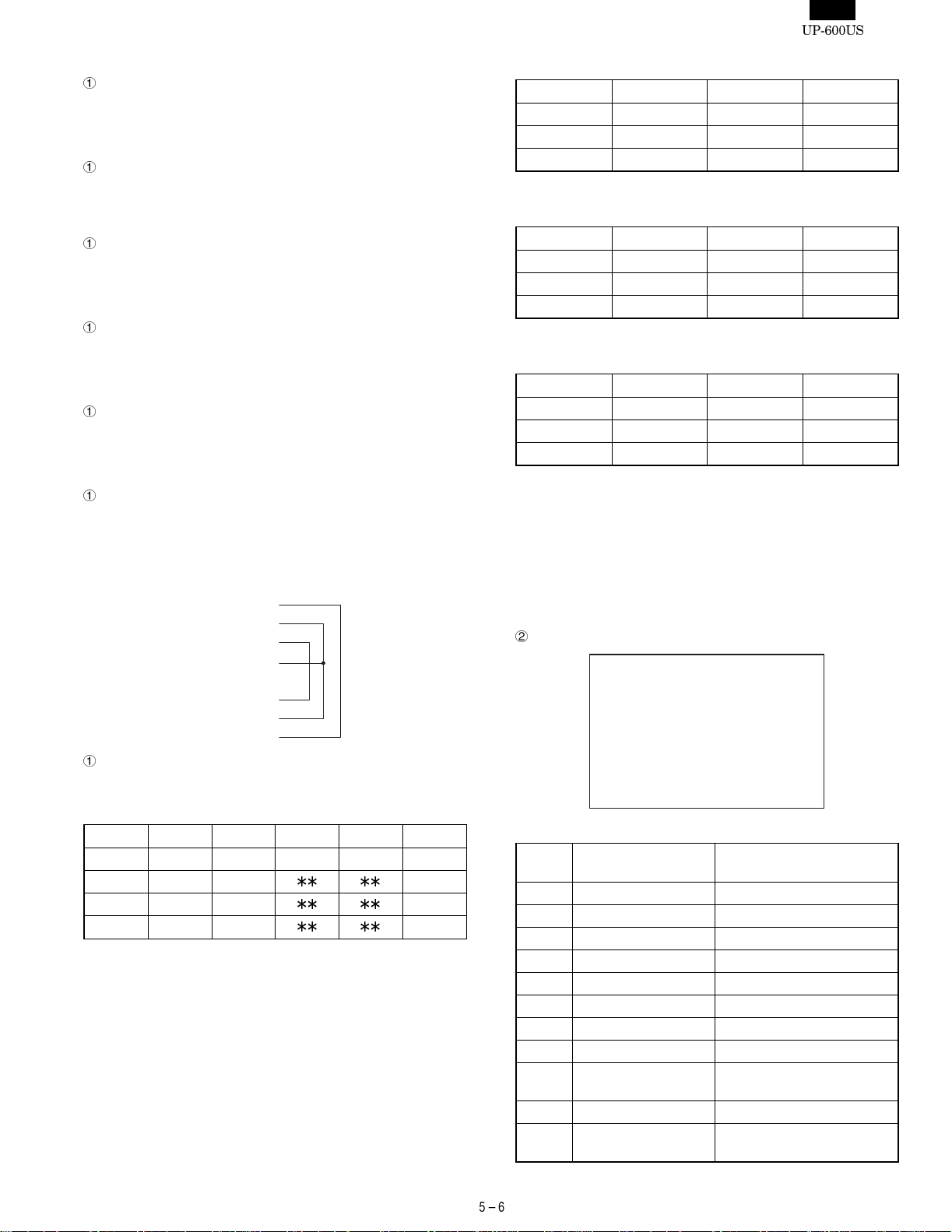

ER-A5RS CON3 (RSCN1)

S1-1 S1-2 S1-3 CHANNEL

0 0 0 Disabled

0 0 1 No setting allowed (Standard RS)

0 1 0 CHANNEL 2

0 1 1 CHANNEL 3

1 0 0 CHANNEL 4

1 0 1 CHANNEL 5

1 1 0 CHANNEL 6

1 1 1 CHANNEL 7

ER-A5RS CON4 (RSCN2)

S1-4 S1-5 S1-6 CHANNEL

0 0 0 Disabled

0 0 1 No setting is allowed (Standard RS)

0 1 0 CHANNEL 2

0 1 1 CHANNEL 3

1 0 0 CHANNEL 4

1 0 1 CHANNEL 5

1 1 0 CHANNEL 6

1 1 1 CHANNEL 7

How to exit the program

Press the CANCEL key to exit the program.

4)-2. CH1 Check

Checking

If any channel is not set, the error message (ERROR: CHx) ap-

pears. When the channel is set, the following checks are performed.

i. Control signal check

ERn RSn DRn Cin CDn CSn

OFF OFF OFF OFF OFF OFF

OFF ON OFF OFF ON ON

ON OFF ON ON OFF OFF

ON ON ON ON ON ON

The program performs the read checks of the above inputs and

interrupt checks of CS, CI, and CD.

During the read check, ER and RS are changed over in the above

order, checking the logic of DR, CI, CD and CS.

If the check result does not agree with the logic in the table, the

error message appears. "ON" in the table means active low and

"OFF" means active high.

In the interrupt check, the CS, CI and CD interrupts are permitted

one by one (The mask is canceled.).

The error message appears if an interrupt does not occur when

each signal is active or if an interrupt occurs when each signal is

not active.

Four cycles of the above check is performed.

ii. Data transfer check

As check data, loop back data transfer of 256 bytes of 00H - 0FFH

is performed. The baud rate is 38400 bps.

iii. TIMER CHECK (RS232 ON BOARD TIMER)

Before starting the check ii, perform the RCVDT start of the timer

you want to check and set to 5 ms. Make sure::

• No TRQ- is generated during the implementation of check ii.

• TRQ- is generated at 5 ms after check ii is completed.

Display

RS232 CH1 Check

PASS!!(or ERROR!!)

Details of the errors are printed on the journal.

ERROR

No.

1 ER-DR : ERROR ER-DR LOOP ERROR

2 ER-CI : ERROR ER-CI LOOP ERROR

3 RS-CD : ERROR RS-CD LOOP ERROR

4 RS-CS : ERROR RS-CS LOOP ERROR

5 CI INT : ERROR No CI interrupt occurs.

6 CD INT : ERROR No CD interrupt occurs.

7 CS INT : ERROR No CD interrupt occurs.

8 TXEMP : ERROR TXEMP is not set.

9 TXEMP INT : ERROR TXEMP interrupt does not

10 TXRDY : ERROR TXRDY is not set.

11 TXRDY INT : ERROR TXRDY interrupt does not

12 RCVRDY : ERROR RCVRDY is not set.

13 RCVRDY INT : ERROR RCVRDY interrupt does not

14 SD-RD : ERROR SD-RD LOOP ERROR

15 SD-RD : ERROR SD-RD LOOP ERROR

16 TIMER : ERROR TIMER ERROR

17 TIMER INT : ERROR TRQ1- interrupt does not

How to exit the program

Press the CANCEL key to exit the program.

ERROR print Details of ERROR

occur.

occur.

(Not possible to receive.

TRQ- occurs during the

implementation of check ii.)

occur.

(DATA ERROR)

(DATA ERROR)

(After check ii is completed)

occur.

Page 23

4)-3. CH2 Check

Checking

The procedure for checking, display and the method of exiting the

programs are the same as for the CH1 check.

4)-4. CH3 Check

Checking

The procedure for checking, display and the method of exiting the

program are the same as for the CH1 check.

4)-5. CH4 Check

Checking

The procedure for checking, display and the method of exiting the

program are the same as for the CH1 check.

4)-6. CH5 Check

Checking

The procedure for checking, display and the mothod of exiting the

programs are the same as for the CH1 check.

4)-7. CH6 Check

Checking

The procedure for checking, display and the method of exiting the

programs are the same as for the CH1 check.

4)-8. CH7 Check

Checking

The procedure for checking, display and the method of exiting the

programs are the same as for the CH1 check.

4)-9. CH8 Check

For checking CH8, the following loop-back connector is used.

1pinRS

2pinER

3pinSD

4pinCI/CD

5pinGND

6pinRD

7pinDR

8pinCS

Checking

The following checks are performed.

i. Control signal check

ER8 RS8 DR8 Ci8 CD8 CS8

OFF OFF OFF OFF OFF OFF

OFF ON OFF

ON OFF ON

ON ON ON

The program performs the read checks of the above inputs.

During the read check, ER and RS are changed over in the above

order, checking the logic of DR, CI, CD and CS.

If the logic is different from those listed in the table, the error

message appears.

ON

OFF

ON

PATTERN 1

ER8 RS8 CI 8 CD8

OFF ON OFF OFF

ON OFF OFF OFF

ON ON OFF OFF

"No Connect" is displayed on the next line of PASS!!.

PATTERN 2

ER8 RS8 CI 8 CD8

OFF ON OFF OFF

ON OFF ON OFF

ON ON ON OFF

"CI Connect is displayed on the next line of PASS!!

PATTERN 3

ER8 RS8 CI 8 CD8

OFF ON OFF OFF

ON OFF OFF ON

ON ON OFF ON

"CD Connect! is displayed on the next line of PASS!!

If the logic is different from t hose in PATTERN 1 - 3, the error

message appears.

"ON" means active low and "OFF" active high.

The above checks are repeated for four cycles.

ii. Data transfer check

As check data, loop back data transfer of 256 bytes of 00H - 0FFH

is performed, the baud rate is set for115200 bps.

Display

RS232 CH8 Check

PASS!!(or ERROR!!)

CD Connect(or CI

Details of the errors are printed on the journal.

ERROR

No.

1 ER-DR : ERROR ER-DR LOOP ERROR

2 ER-CI : ERROR ER-CI LOOP ERROR

3 RS-CD : ERROR RS-CD LOOP ERROR

4 RS-CS : ERROR RS-CS LOOP ERROR

5

6

7

8 TXEMP : ERROR TXEMP is not set.

9 TXEMP INT : ERROR TXEMP interrupt does not

10 TXRDY : ERROR TXRDY is not set.

11 TXRDY INT : ERROR TXRDY interrupt does not

ERROR print Details of ERROR

Connect, No Connect

occur.

occur.

)

Page 24

ERROR

No.

ERROR print Details of ERROR

12 RCVRDY : ERROR RCVRDY is not set.

(Not possible to receive. TRQoccurs during the

implementation of check ii.)

13 RCVRDY INT : ERROR RCVRDY interrupt does not

occur.

14 SD-RD : ERROR SD-RD LOOP ERROR

(DATA ERROR)

15 SD-RD : ERROR SD-RD LOOP ERROR

(DATA ERROR, FRAMING

ERROR, and others)

16

17

18 CI : ERROR The logic of C1 is ON, but

different from those in 1~3.

19 CD : ERROR The logic of CD is ON, but

different from those in 1~3.

How to exit the program.

Press the CANCEL key to exit the program.

5) LCD/POPUP/POLE DISPLAY & PRINTER

DIAGNOSTICS

The program tests the LCD, popup and pole displays of the UP-600.

The following menu appears on the screen. The cursor shown in

reverse video can be moved using the up/down arrow keys. Move the

cursor to the menu item you want to execute and select by pressing

the Enter key to execute the corresponding Diag. program. You can

return the screen to this submenu by pressing the CANCEL key.

ii. Reverse-videoed test pattern of i

iii. Vertical stripe pattern with 1-dot spacing

iv. Reverse-videoed test pattern of iii

v. Horizontal stripe pattern with 1-dot spacing

DISPLAY&PRINTER DIAG

LCD Check

POPUP Check

POLE Check

PRINTER Check

PRINTER CG Check

PES&NES SENSOR Check

Dot pulse adjustment

The test program displays the following test patterns in the order

shown. You can move to the next pattern by pressing the ENTER

key.

You can return the screen to this submenu by pressing the ENTER

key when the final test pattern is shown on the screen or by pressing

the CANCEL key during the implementation of the check.

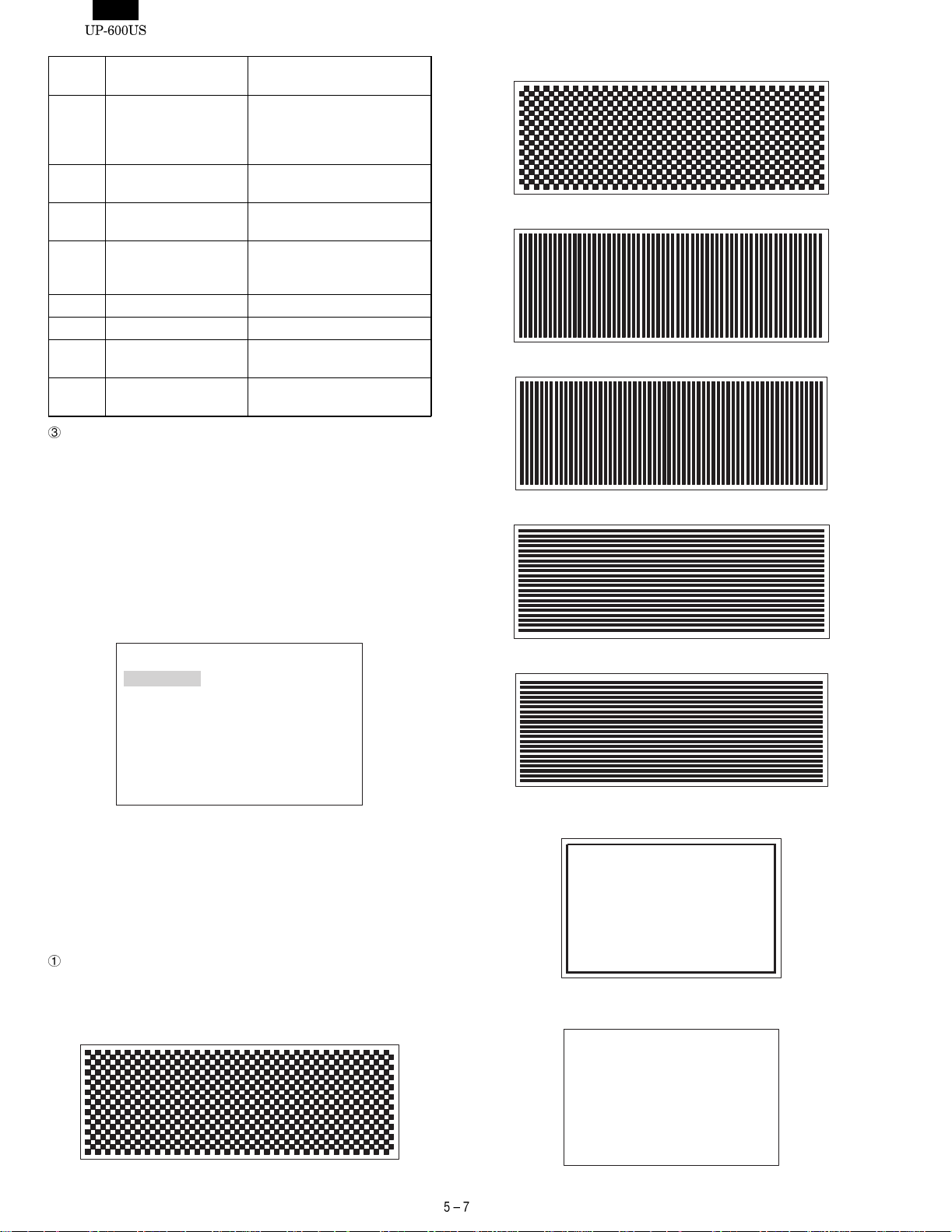

5)-1. Liquid Crystal Display Check

Checking

The screen shows the following test patterns. Press the ENTER

key to move to the next test pattern.

i. Black and white checkered pattern with 1-dot spacing.

vi. Reserve-videoed test pattern of v

vii. The outermost periphery of LCD’s active area is displayed in

1-dot line.

viii. "H" pattern. "H" is displayed in 20 digits and 8 lines.

"H" is displayed in 19 digits only in the 8th line.

HHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHH

Page 25

How to exit the program.

You can exit the program by pressing the ENTER key when the

final test pattern is shown on the screen or by pressing the CANCEL key during checking.

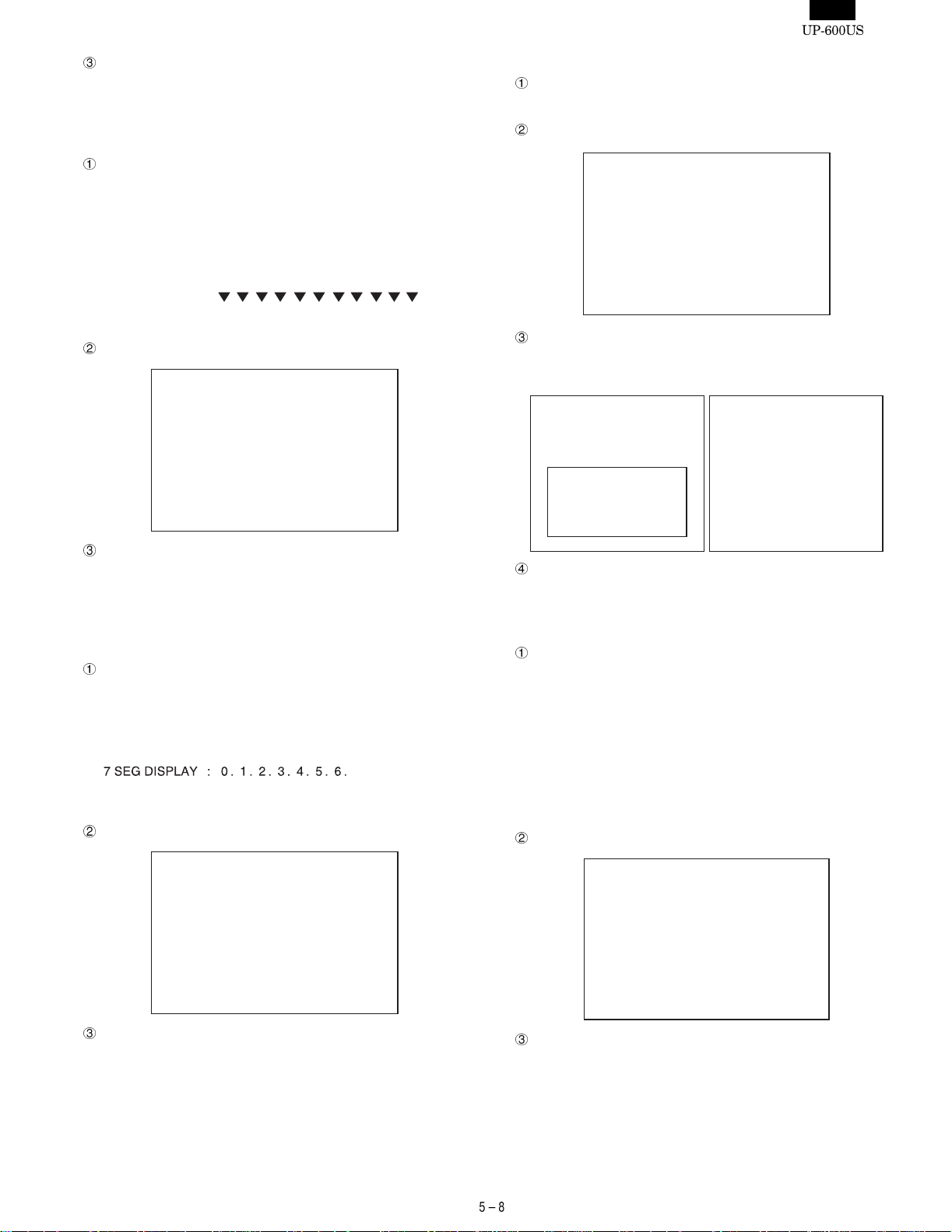

5)-2. Pole Display Check

Checking

The screen shows the following test patt erns in the order given

below. Press the ENTER key to move to the next pattern.

i. The following test patterns are displayed.

5)-4. PRINTER Check

Checking

The printer prints on the RECEIPT/JOURNAL PRINTER.

Display

PRINTER Check

DOT DISPLAY

7SEG DISPLAY::

0123456789;AaBbC

0. 1. 2. 3. 4. 5. 6. 7. 8. 9. -.

ii. The test pattern where all digits are turned ON is displayed.

Display

POLE Display Check

How to exit the program.

You can return to the Diag. submenu by pressing t he ENTER key

after the 2nd test pattern where all digits are turned ON and are

displayed. Or press the CANCEL key to erase the screen to exit

the program.

5)-3. Popup Display Check

Checking

The screen shows the following test patt erns in the order given

below. Press ENTER to move to the next pattern.

i. The following test patterns are displayed.

ii. The test pattern where all digits are turned ON is displayed.

Display

JOURNAL/RECEIPT print

"Z" 24 digits are printed in 5 lines.

RECEIPT

ZZZZZZZZZZZZZZZZZZZZZZZZ

ZZZZZZZZZZZZZZZZZZZZZZZZ

ZZZZZZZZZZZZZZZZZZZZZZZZ

ZZZZZZZZZZZZZZZZZZZZZZZZ

ZZZZZZZZZZZZZZZZZZZZZZZZ

LOGO

ZZZZZZZZZZZZZZZZZZZZZZZZ

ZZZZZZZZZZZZZZZZZZZZZZZZ

ZZZZZZZZZZZZZZZZZZZZZZZZ

ZZZZZZZZZZZZZZZZZZZZZZZZ

ZZZZZZZZZZZZZZZZZZZZZZZZ

JOURNAL

How to exit the program

One second after printing is completed, the screen returns to the

PRINTER Check of the DISPLAY & PRINTER MENU.

5)-5. PRINTER CG Check

Checking

The printer prints the built-in CG onto the RECEIPT/JOURNAL

PRINTER.

Standard characters are printed in 16 characters/line and ex-

tended ASCII characters (enlarged characters) are printed in 8

characters/line.

The standard characters are printed first, followed by the extended ASCII characters.

Check the outputted print to see if CG is correctly printed.

Display

POPUP Display Check

How to exit the program

You can return to the Diag. submenu by pressing t he ENTER key

after the 2nd test pattern where all digits are turned ON and are

displayed. Or press the CANCEL key to erase the screen to exit

the program.

PRINTER CG Check

How to exit the program.

Press the CANCEL key to exit the program after 1 cycle of printing

is completed.

Page 26

5)-6. PES & NES SENSOR Check

Checking

The screen displays the operating status of the paper end sensor

and paper near end sensor of the receipt/journal printer.

Display

PES&NES SENSOR Check

NES : 0 (or 1)

RPES : 0 (or 1)

JPES : 0 (or 1)

OPBS : 0 (or 1)

6) TCP/IP STACK NETWORK DIAGNOSTICS

The program performs the TCP/IP stack test.

The test requirements are as follows:

• UP-600

• 10BASE-T cable (for d a ta tra n sfer testing)

• HUB (for loop back test and data transfer test where 2 or more

units are used.)

The following menu appears. The cursor shown in reverse video can

be moved using the up/down arrow keys. Move the cursor to the

menu item you want to execute and press t he ENTER key to execute

the corresponding check program. After the selected Diag. program is

completed, the screen returns to this menu.

Press the CANCEL key to return the screen to the Diag. submenu.

Display Status Description

NES 0 Senses the near end of the journal paper roll.

Does not sense the near end of the journal

1

paper roll.

RPES 0 Senses the end of the receipt paper roll.

1 Does not sense the end of the receipt paper roll.

JPES 0 Senses the end of the journal paper roll.

1 Does not sense the end of the journal paper roll.

OPBS 0 IPL ROM PWB connected

1 IPL ROM PWB not connected

How to exit the program

Press the CANCEL key to exit the program.

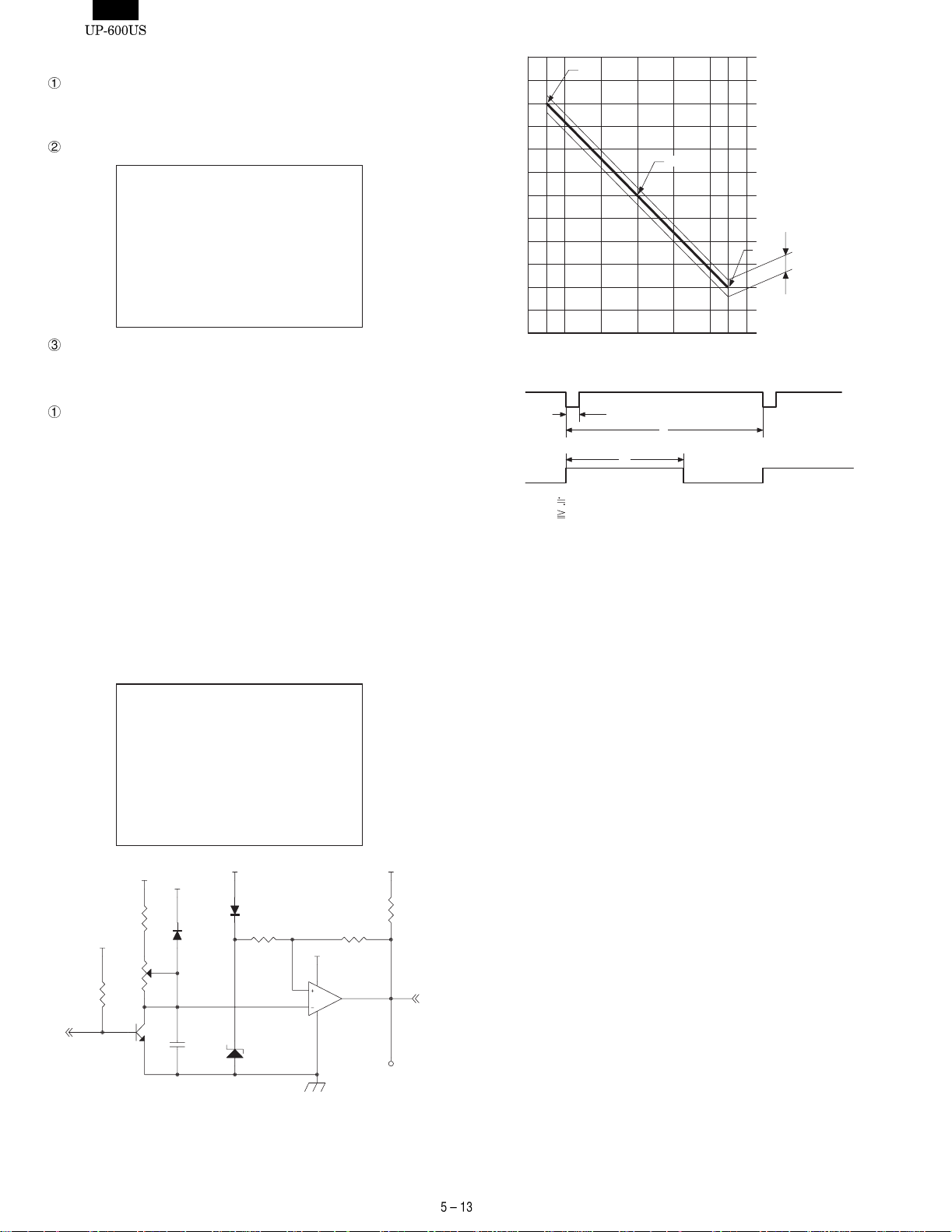

5)-7. DOT PULSE Adjustment

Checking

The dot width adjustment circuit controls the pulse width of the

current which is added to the printer dot head in response to

fluctuations n supply voltage. If the circuit is replaced with a new

one for any reason such as repair, the dot pulse width needs to be

adjusted using the 200K’s knob VR1. When the DOT PULSE

Adjustment is executed, the dot pulse "PE" is outputted without

printing.

Display

DOT PULSE Adjustment

TCP/IP DIAG

SELF Check

LOOPBACK Check

MAC ADDR&FIRM Ver. Read

MAC ADDR&FIRM WRITE

DATA Trans.(MA)

DATA Trans.(SA)

6)-1. SELF Check

Checking

The program executes Diag’s built in TCP/IP stack board and

displays the results.

i. Execute the flash memory test command and display the re-

sult.

ii. Execute the SRAM test command and display the result.

iii. Execute the dual-port RAM test and display the result.

iv. Execute the interrupt test command and display the result.

The information inside the error status is as follows:

b7 Reserved ("0" is always displayed)

b6 Reserved ( "0" is always displayed)

b5 Reserved ("0" is always displayed)

b4 Reserved ( "0" is always displayed)

b3 HR_RST : If /INTHR cannot be canceled

b2 HR_ACK:If /INTHR does not enter after waiting for 10 ms

b1 HW_RST : If /INTHW cannot be canceled

b0 Reserved ("0" is always displayed)

How to exit the program

Press the CANCEL key to exit the program.

Display

SELF Check

FLASH : PASS (or ERROR)

SRAM : PASS (or ERROR)

XXXXXXXX : XX : XX

DPRAM : PASS (or ERROR)

XXXXXXXX : XX : XX

INTERRUPT : PASS (or ERROR)

XXXXXXXX

How to exit the program.

Press the CANCEL key to exit the program.

When an error occurs,

the address and data

are displayed.

When an error occurs,

the address and data

are displayed.

When an error occurs,

the data is displayed.

Page 27

6)-2. LOOPBACK Check

Checking

Install a straight cable between the RJ45 connector and the HUB

and execute the loop back test command to send and receive 1

packet of data.

Display

LOOPBACK Check

LOOPBACK : PASS (or ERROR)

LOOPBACK ERROR

LANC ERROR

How to exit the program

Press the CANCEL key to exit the program.

Displayed when an

error occurs.

Displayed when an

error occurs.

Input : DUAL PORT RAM (800000H‘)

08 00 1F XX YY ZZ

MAC ADDRESS (XX, YY, ZZ are converted to 16 hexadecimal

numbers.)

Output : DUAL PORT RAM (800800H‘)

During writing

I P L 0 0 0 7 0 0

When writing is completed (The same applies when the copy is

skipped at the first verification.)

I P L 0 0 0 7 O K

When the writing process ends with an error.

I P L 0 0 0 7 N G

6)-3. MAC ADDRESS&FIRM Ver. read Check

Checking

The program reads the version of the MAC address and firmware

and displays the result.

Display

MAC ADDR&FIRM Ver. Read

MAC ADDRESS :

XX XX XX XX XX XX

FIRMWARE VERSION :

XXXXXXXXXX

How to exit the program

Press the CANCEL key to exit the program.

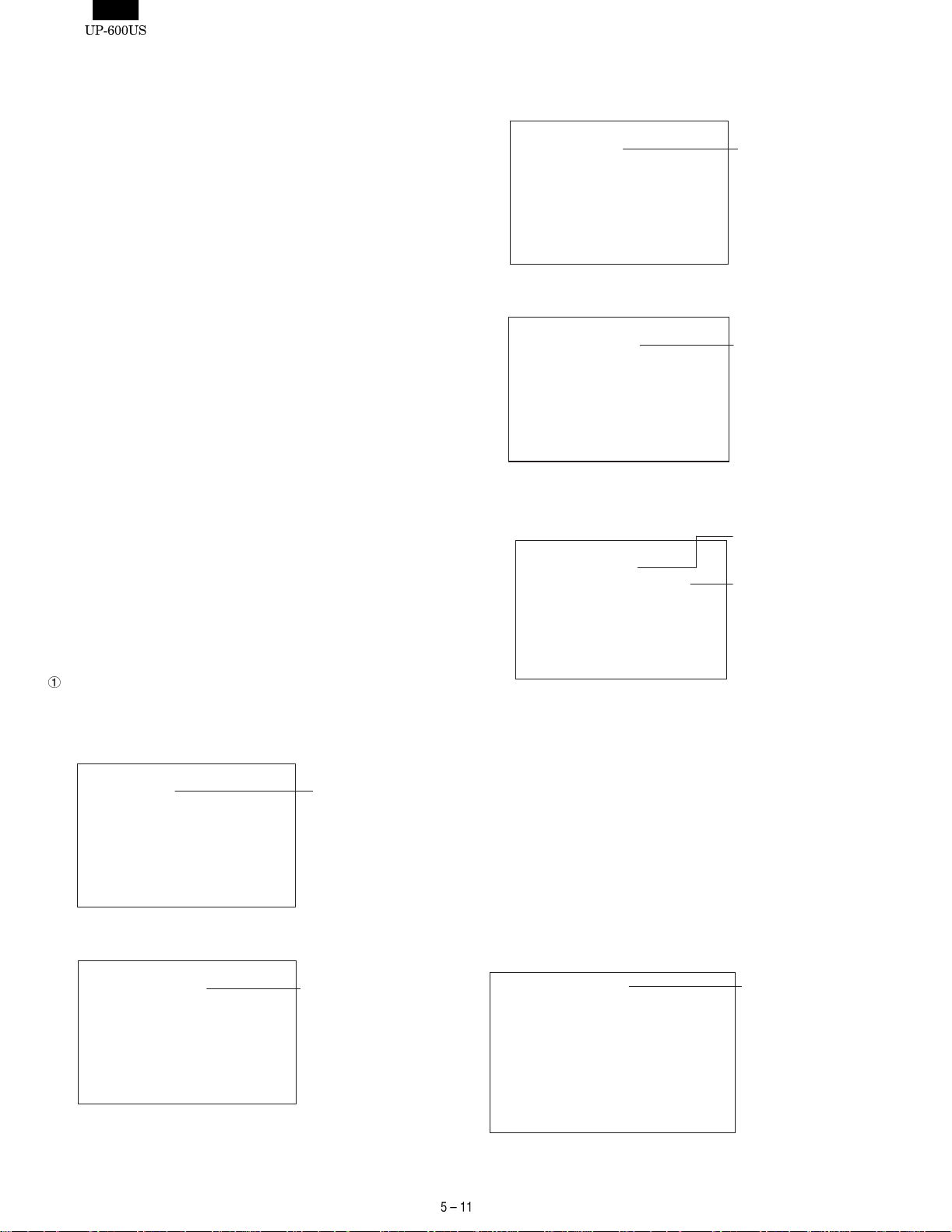

6)-4. MAC ADDRESS&FIRM write UTILITY

Operation

This utility writes the MAC address and firmware.

(Procedure)

Install the master EPROM on the TCP/IP board and turn the IPL

switch on the board to the "program write mode."

Turn on the ECR.

The IPL program on the TCP/IP board starts.

Input 3 sets of 3-digit decimal num bers through the keyboard of

the ECR and press the ENTER key.

Following the SHARP maker code (08, 00, 1F), the 3 sets of

numbers input through the keyboard are converted into hexadecimal numbers. The program then writes a total of 6 bytes of MAC

address into dual port RAM (800000H - ).

Turn off the power supply.

Remove the EPROM from the TCP/IP board and turn the IPL

switch to the "normal mode."

Data of 6 bytes is

displayed.

10 digits are

displayed.

Display

MAC ADDR&FIRM Write

MAC ADDRESS

Decimal numbers are

input through

keyboard.

AAA BBB CCC

08 00 1F XX YY ZZ

TCP/IP FIRM CHANGE

Data of 6 bytes is

displayed as

hexadecimal numbers

IPL 00-07 XX (XX : 00~07 OK or NG)

TCP/IP FIRM CHANGE :

ERASE 00-07 00

A

COPY 00-05 00

B

FIRM CHANGE PASS!!

C

While the address and firmware are being rewritten, the message

A and then B appears.

When the address and firmware have been rewritten, the message C is displayed.

The following screen appears when the IPL switch is not turned to

the write mode.

MAC ADDR&FIRM Write

CHANGE IPL SW!!

How to exit the program.

Press the CANCEL key to exit the program.

After rewriting, make sure to turn the power off and then turn it

on again.

Page 28

6)-5. Data Transmission Check

The program performs a data transfer test using an actual established system.

The system consists of 1 master machine and up to 63 satellite

machines.

Cautions to be taken when starting the test.

• If this test is performed on the ECRs set for LAN, cancel the

settings before starting the test.

• If this test is performed using an established system, disconnect

the LAN cables from the ECRs you do not want to test or cancel

their LAN settings. If the test is performed with those ECRs set for

LAN, their data might be destroyed.

• After canceling the LAN settings of all ECRs on the system, set

them for the data transfer test.

Set the satellite machines first, and then set the master machine.

• The Diag of the UP-600 uses a private IP address. Each IP ad-

dress is unique on the Internet. When building a private network,

you should be careful not to allow your internal packet used for

your own network to leak to t he Internet, because it might cause

confusion. The Internet Assigned Numbers Authority (IANA) specifies IP addresses that can be used without registration. These

addresses can only be used within a private network and are not

route controlled between sites of the Internet.

Class A : 10.x.x.x

Class B : 172.16.x.x 172.31.x.x

Class C : 192.168.0.x?192.168.255.x

It is strongly recommended to use addresses within the above

range when building a private network.

In this Diag. program, the following private IP addresses are assigned to the terminal Nos. (1 - 64).

TERMINAL NO.1 = 192.168.0.1

TERMINAL NO.2 = 192.168.0.2

......

TERMINAL NO.31 = 192.168.0.63

TERMINAL NO.32 = 192.168.0.64

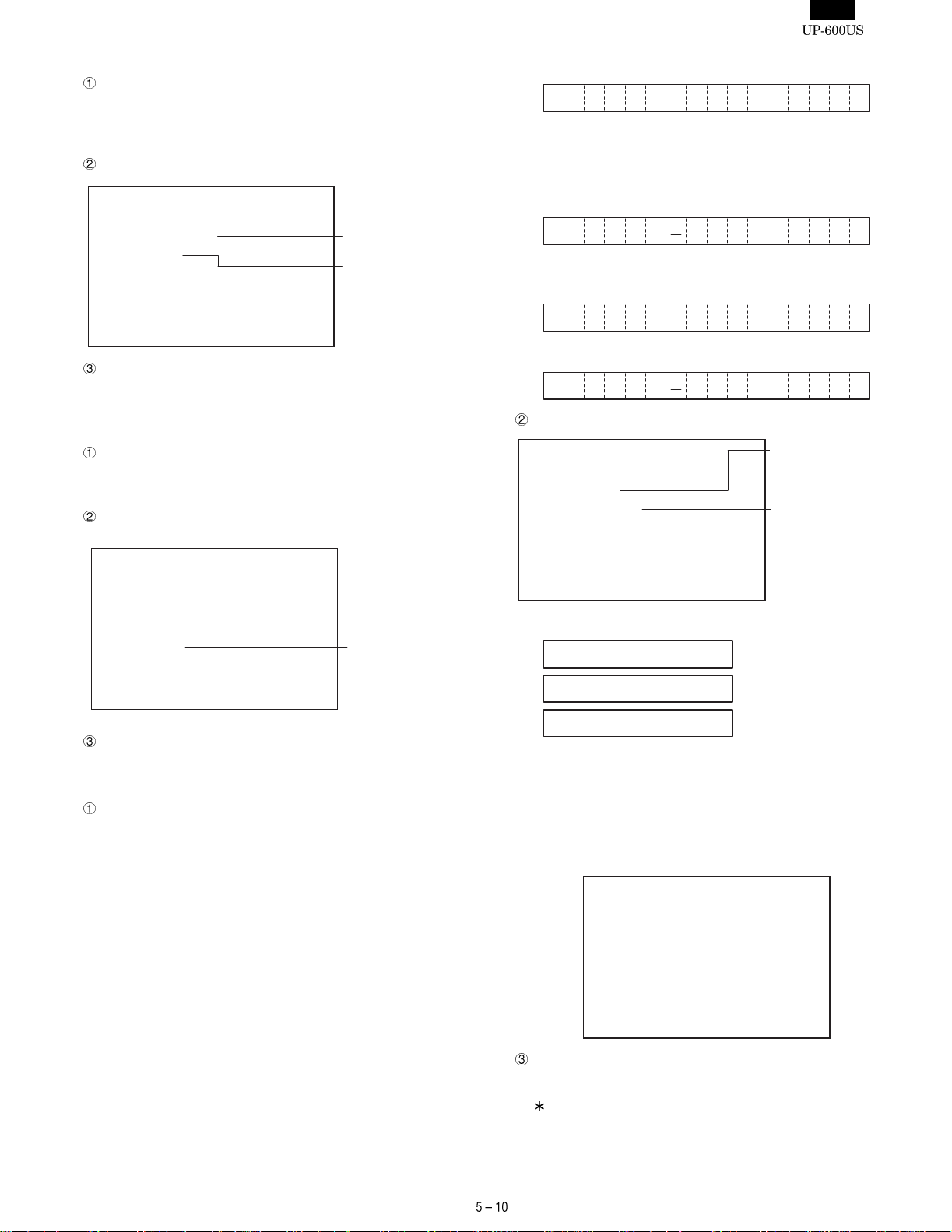

Setting

i. Setting satellite machines.

On the menu screen, select DATA Trans. (SA). The screen is

shown below.

DATA Trans.(SA)

INPUT SA T-NO.

Enter the terminal No. of the machine you are going to test (a

2-digit number from 1 - 32) + Enter. The screen looks like this:

DATA Trans.(SA)

INPUT SA T-NO. : XX

DATA SEQ.NO. : 0000

Enter a number

within the range

from 1 64.

The terminal No. you

entered is displayed.

i. Setting the master machine.

On the menu screen, select DATA Trans. (MA). The screen

looks like this:

DATA Trans.(MA)

INPUT MA T-NO. :

Enter a number

within a range

from 1~64.

Enter the terminal No. of the machine you want to test (a

2-digit number from 1 - 64)+ Enter. The screen looks like this:

DATA Trans.(MA)

INPUT MA T-NO. : XX

INPUT SA T-NO. :

The terminal No. you

entered is displayed.

Enter the terminal No. (a 2-digit number from 1 -64) of the

satellite machines which are connected to the test machine +

Enter. The screen looks like this:

The terminal No. of

DATA Trans.(MA)

INPUT MA T-NO. : XX

INPUT SA T-NO. : XX( or XXXX)

the master machine

you entered is

displayed.

The terminal No. of

the satellite machine

you entered is

displayed.

When performing the test with multiple satellite machines, type their

terminal numbers (2-digit numbers within the range from 1~64) and

press Enter. In addition, you specify the satellite machines using the

area specification function without typing terminal numbers. This is

achieved by typing the first terminal number (2 digits) and the last

terminal number (2 digits) of the satellite machines and then press

Enter. For example, if you want to specify the terminal numbers of

satellite machines from 5 to 15, type "0515" for T-No. and press Enter.

When executing, press the Enter key without typing the terminal

numbers.

The display appears like this:

Note that the terminal numbers of the master machine and satellite machines should not be the same. When the terminal numbers

are to be specified using the area specification function, any terminal number that is used for the master machine will be excluded

from the specification of satellite machine terminal numbers.

INPUT MA T-NO. : XX

The terminal No. of

the master machine

you entered is

displayed.

DATA SEQ.NO. : 0000

With the above setting, data transfer is performed bet ween the

master machine and the satellite machines.

Page 29

Checking

i. The master machine sends data of the following form at con-

sisting of 2-byte sequence No. and 254-byte AAH data to the

satellite machine. The master machine displays the sequence

Nos.

Test data format (1 packet: 256 bytes)

12345 254255256byte

XX XX AA AA AA AA AA AA

7) MCR & DRAWER Diagnostics

The program checks the MCR and drawer.

The following menu appears on screen.

The cursor shown in reverse video can be moved using the up/down

arrow keys. Move the cursor to the m enu item you want to execute

and select by pressing the ENTER key to execute the corresponding

program. Press the CANCEL key to return the screen to this submenu.

XXXX : Sequence No. 2 bytes (4-digit binary coded decimal

number)

AA : Transfer (AAH) ~ 254 bytes

ii. The satellite machine returns the data it has received, to the

master machine as it is. The satellite machine displays the

sequence No. on the screen.

iii. The master machine receives the data and then checks the

sequence Nos. and 254-byte AAH data. If an error occurs, the

master machine displays an error code and ends the test. If

there are multiple satellite machines, steps i and ii are repeated.

The master machine advances the sequence No. when data is

transferred successfully between it and the satellite machines.

Steps i - iii are repeated.

Error display

The following error codes are used (same as for TCP/IP HANDLER)

01 Command error (excluding the time when data is sent)

02 No data received

03 Received data size present

Received data left

04 Receiving station not ready for receiving (when sending)

"NRDY" is returned because the receiving station is not

ready for receiving.

05 Receiving buffer full(when sending)

The receiving side’s controller receive buffer is full.

06 Resend error(When sending)

The number of retries exceeds the setting (5 times) when

no response is obtained.

07 Collision error (When sending)

If a collision occurs

08 Line busy time out

Data cannot be sent due to multiple stations communicating

09 Receiving data size over (when receiving)

Insufficient size of receiving buffer.

0A Hardware error

Interface error (No SRN interface or defective SRN

controller)

MCR&DRAWER Check

MCR Check

DRAWER 1 Check

DRAWER 2 Check

7)-1. Magnetic Card Reader Check

The program performs the read test of an optional UP-E13MR.

The test program reads a magnet card using the ISO7811/1-5 stand-

ard and prints data on the journal.

Press the CANCEL key to return the screen to the submenu.

Checking

The program reads tracks 1 - 3 of a magnet card using the

ISO7811/1‘5 standard and prints the data using ASCII codes.

JOURNAL print

MCR Check

TRACK1:

XXXXXXXXXXXXXXXXXXXXXXXXXXX

XXXXXXXXXXXXXXXXXXXXXXXXXXX

XXXXXXXXXXXXXXX

TRACK2:

XXXXXXXXXXXXXXXXXXXXXXXXXXX