Page 1

SERVICE MANUAL

POS TERMINAL

MODEL UP-5700

("U" & "A" version)

CONTENTS

WIRING DIAGRAM

CHAPTER 1. SPECIFICATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

CHAPTER 2. OPTIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

CHAPTER 3. SERVICE PRECAUTION. . . . . . . . . . . . . . . . . . . . . . 3-1

CHAPTER 4. DIAGNOSTICS SPECIFICATIONS . . . . . . . . . . . . . . 4- 1

CHAPTER 5. CIRCUIT DESCRIPTION. . . . . . . . . . . . . . . . . . . . . . 5-1

CHAPTER 6. POWER SUPPLY UNIT. . . . . . . . . . . . . . . . . . . . . . . 6-1

CHAPTER 7. BIOS SET UP UTILITY . . . . . . . . . . . . . . . . . . . . . . . 7-1

CHAPTER 8. ABOUT UTILITY SOFTWARE AND OTHERS . . . . . 8-1

CHAPTER 9. CIRCUIT DIAGRAM. . . . . . . . . . . . . . . . . . . . . . . . . . 9-1

CHAPTER 10. PWB LAYOUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-1

PARTS GUIDE

Parts marked with " " is important for maintaining the safety of the set. Be sure to replace these parts with specified

ones for maintaining the safety and performance of the set.

This document has been published to be used

SHARP CORPORATION

for after sales service only.

The contents are subject to change without notice.

Page 2

THE FOLLOWING CAUTION IS APPLICABLE IN THE UNITED STATES ONLY.

“B A T T E R Y D I S P O S A L”

“CONTAINS NICKEL-CADMIUM RECHARGEABLE BATTERY MUST BE RECYCLED OR DISPOSED OF

PROPERLY. REMOVE THE BATTERY FROM THE PRODUCT AND CONTACT FEDERAL OR STATE

ENVIRONMENTAL AGENCIES FOR INFORMATION ON RECYCLING AND DISPOSAL OPTIONS.”

The RBRCTM Seal

TM

The RBRC

Seal on the easily removabl e nick el-cadmium battery pack contained

in our product indicates that SHARP is voluntarily participating in an industry program to

collect and recycle these battery pac ks at the end of their useful life, when taken out of

TM

service within the United States. The RBRC

program provides a convenient alternative to

placing spent nickel-cadmium battery packs into the trash or municipal waste stream,

which is illegal in some areas.

TM

SHARP’s payments to RBRC

makes it easy for you to drop off the spent battery pack at local retailers

of replacement nickel-cadmium batteries, or at authorized SHARP product service centers. You may also contact

your local recycling center for information on where to return the spent battery pack. SHARP’s involvement in this

program is part of its commitment to protecting our environment and conserving natural resources.

TM

(RBRC

is a trademark of the Rechargeable Battery Recycling Corporation.)

Page 3

CHAPTER 1. SPECIFICATIONS

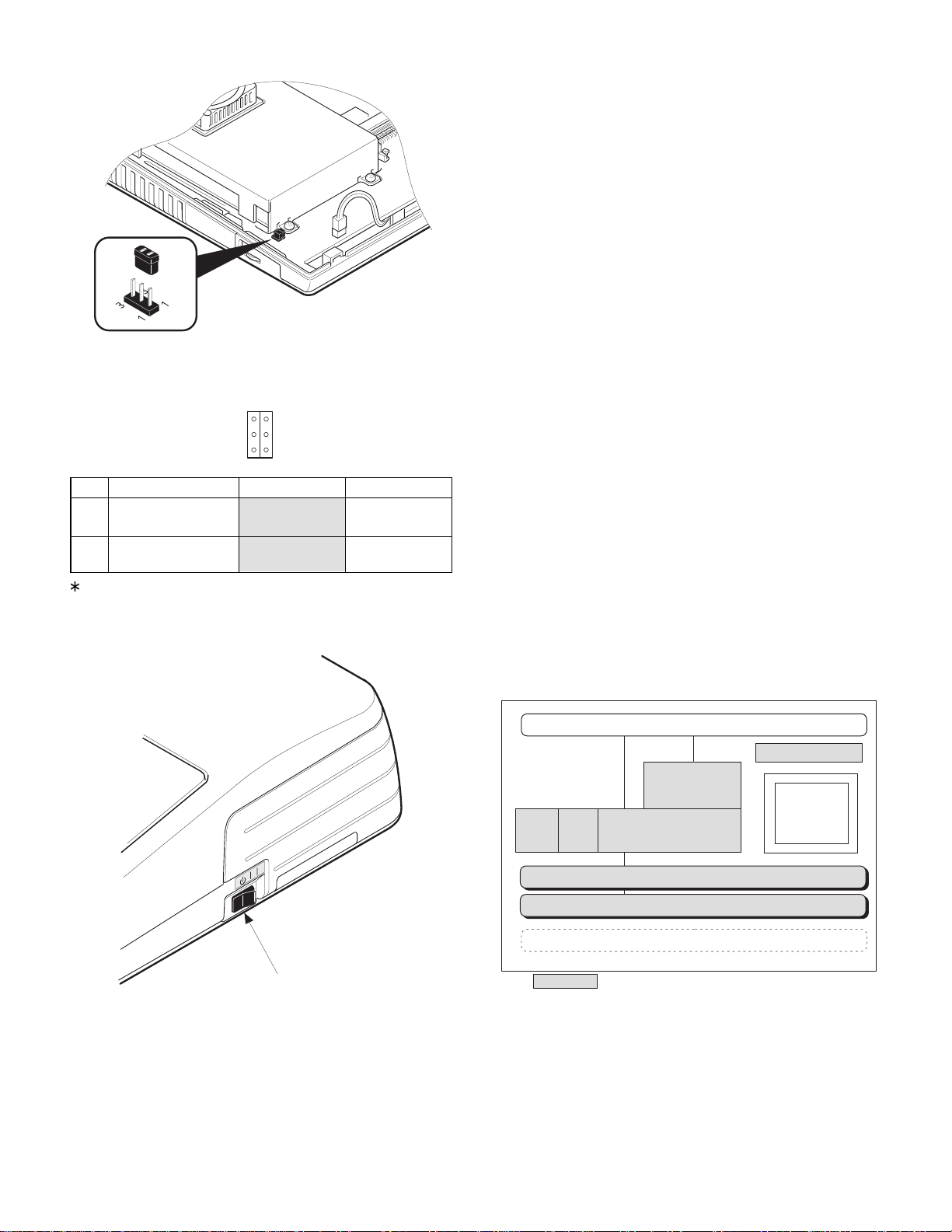

1. Appearance

Flat-panel LCD display

with touch-sensitive overlay

Power switch

AC cord

Plug your POS terminal into a wall outlet before using.

Power switch

Set the power switch to the ON ( I ) position after plugging your POS

terminal.

2. Rating

ITEM SPECIFICATIONS

External dimensions 290 (W) ´ 365 (D) ´ 131 (H) mm

Weight 5.5 kg

Power source Official (normal) voltage and

Power consumption Operating: 43 W

Working temperature and

humidity

frequency

0 to 40°C (32 to 104°F)

10 to 90%

3-3. PC system

ITEM SPECIFICATIONS NOTE

CPU Pentium processor

Chip set OPTI 82C700

VGA chip C&T T65550B

Main memory

(for executing MS-DOS,

Application software)

Video RAM 1 Mbytes EDO type

BIOS ROM 512 Kbytes Flash ROM

OS (MS-DOS) ROM 4 Mbytes Mask ROM

ROM disk memo r y

(for stored Application

software)

RAM disk memory

(for POS data)

Key controller M38802

Super I/O M5113

Standard: 8 Mbytes EDO type

Max.: 40 Mbytes adding S.O.DIMM

Standard: 2 Mbytes Flash ROM

Max.: 6 Mbytes adding UP-F04RB

Standard: 1 Mbytes

Max.: 3 Mbytes adding UP-P02MB

3-4. Serial port

D-SUB 9-pin connector COM1 and COM2 are equipped.

In order to supply +5V power, CI signal and +5V power supply of

COM1 and COM2 can be switched.

2 channels of RJ45 Connector COM port are equipped.

COM3 and COM4 or original I/O address (COM5 and COM6) can be

selected as the 2 channels of RJ45 COM port.

COM1 & COM2: D-sub 9 pin

Pin No. Signal Function I/O

1 CD Data Carrier Detect I

2 RD Receive Data I

3 SD Send Data O

4 ER Data Terminal Ready O

5 SG Signal Ground —

6 DR Data set Ready I

7 RS Request to Send O

8 CS Clear to Send I

9 CI/+5V Ring Indicate / +5V I/–

3. Hardware

3-1. Display

ITEM SPECIFICATIONS NOTE

Type TFT color LCD with back

Screen size 10.4" Full screen

Dot format 640 (W) ´ 480 (H) dots

Dot size 0.33 ´ 0.33 mm

Control VGA

3-2. Keyboard

ITEM SPECIFICATIONS NOTE

Type Touch key

Number of key

positions

Control Mouse emulation

light

(Analog touch panel)

4096 (W) ´ 4096 (H)

positions

With 256 colors

COM3 or COM5: Modular jack RJ45 8 pin

Pin No. Signal Function I/O

1 RS Request to Send O

2 ER Data terminal Ready I

3 SD Send Data O

4 SG/(+5V) Signal Ground/(+5V) —

5 SG Signal Ground –

6 DR Receive Data I

7 DR Data set Ready I

8 CS Clear to Send I

1 – 1

Page 4

COM4 or COM6: Modular jack RJ45 8 pin

Pin No. Signal Function I/O

1 RS Request to Send O

2 ER Data terminal Ready I

3 SD Send Data O

4 SG Signal Ground —

5 SG Signal Ground –

6 RD Receive Data I

7 DR Data set Ready I

8 CS Clear to Send I

3-5. Expansion slot

ITEM SPECIFICATIONS NOTE

Type ISA bus Half size PC board

Number of slots 2 slots

Power consumption +5V/max. 1.0A

+12V/max. 0.05A

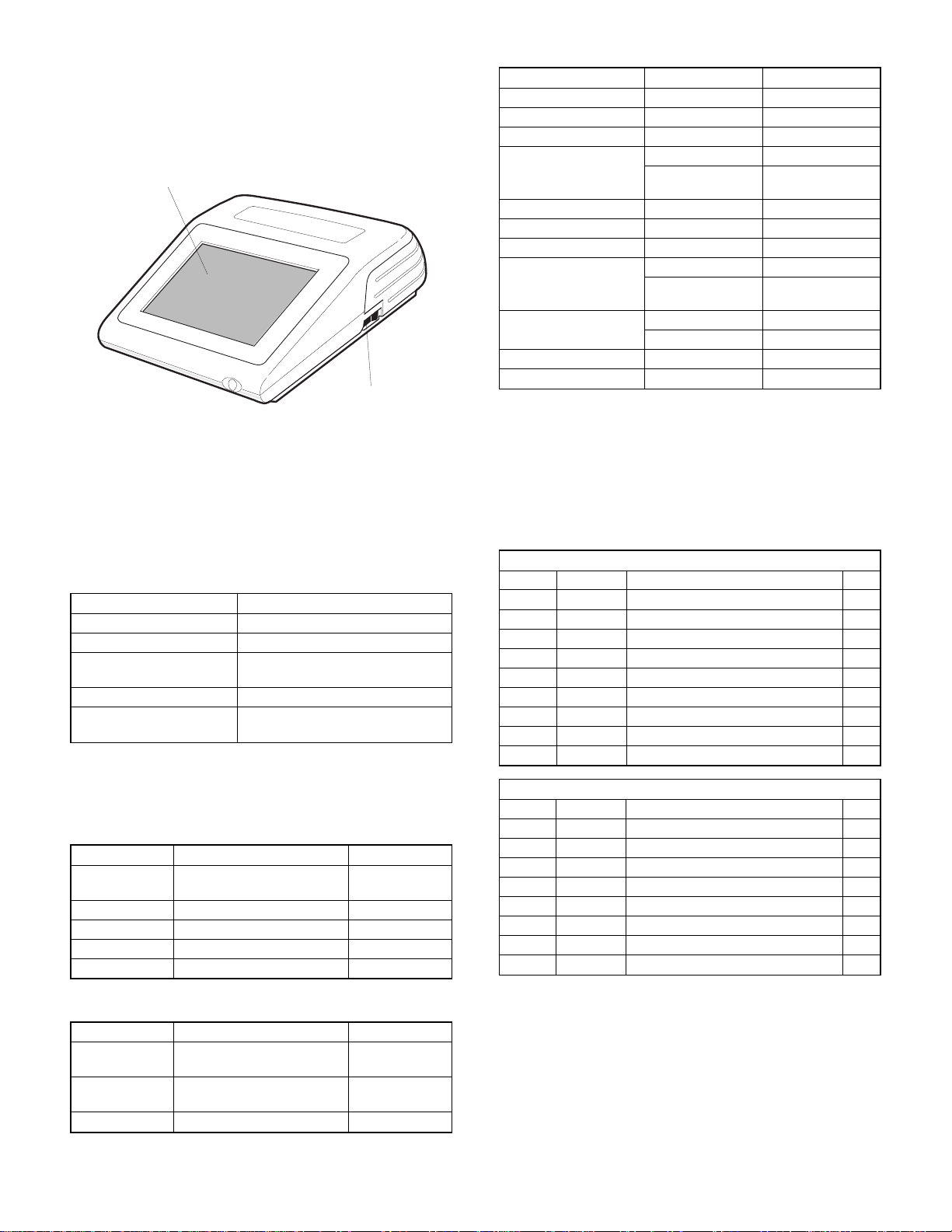

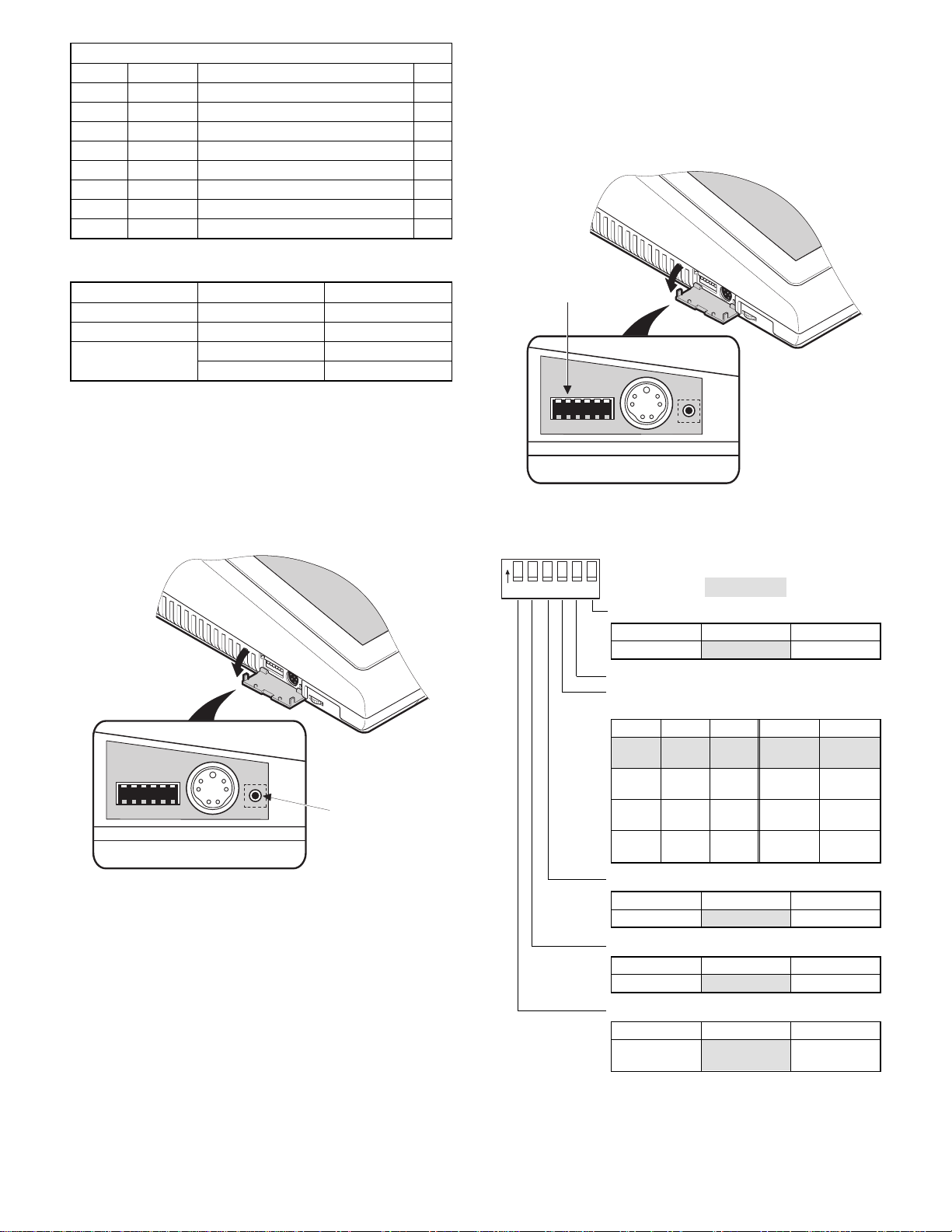

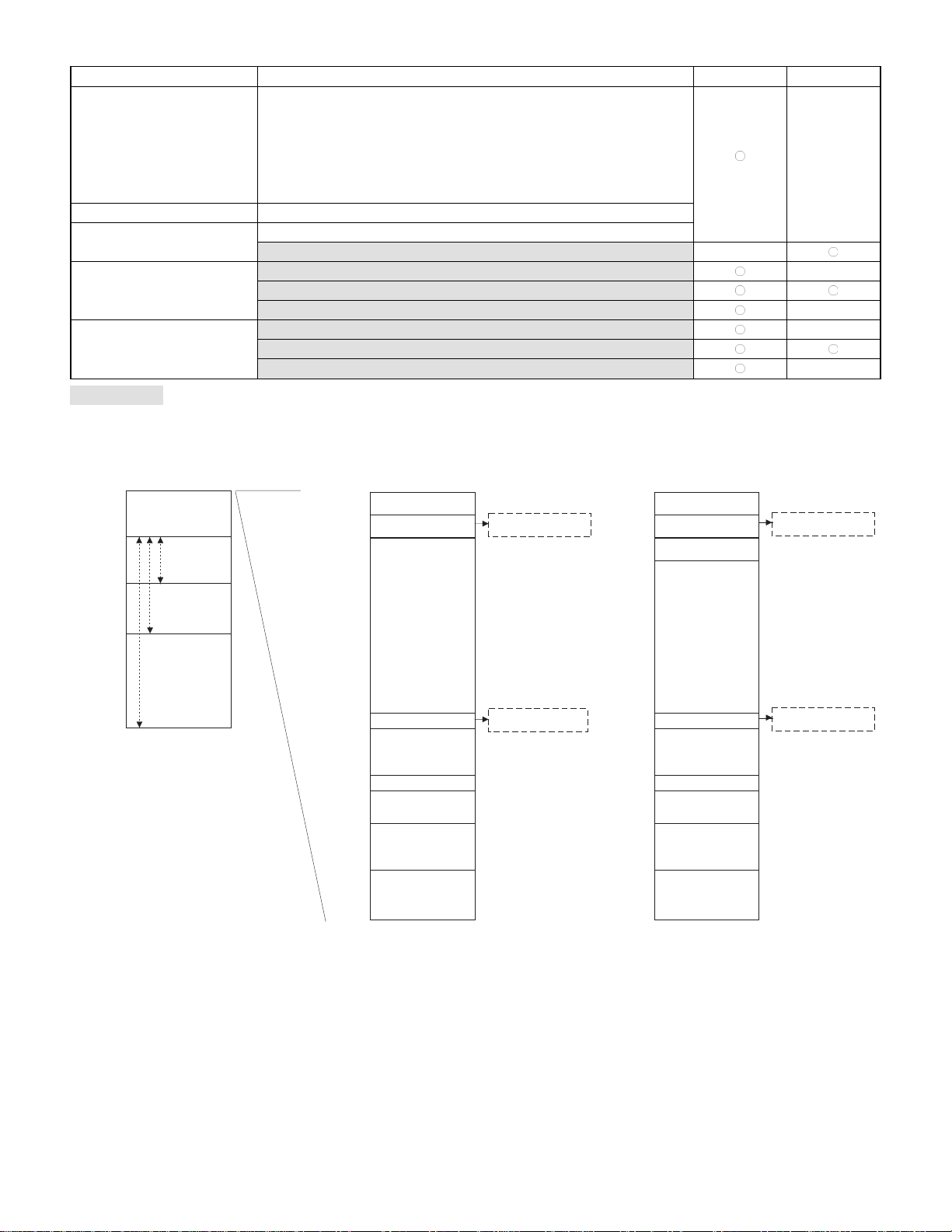

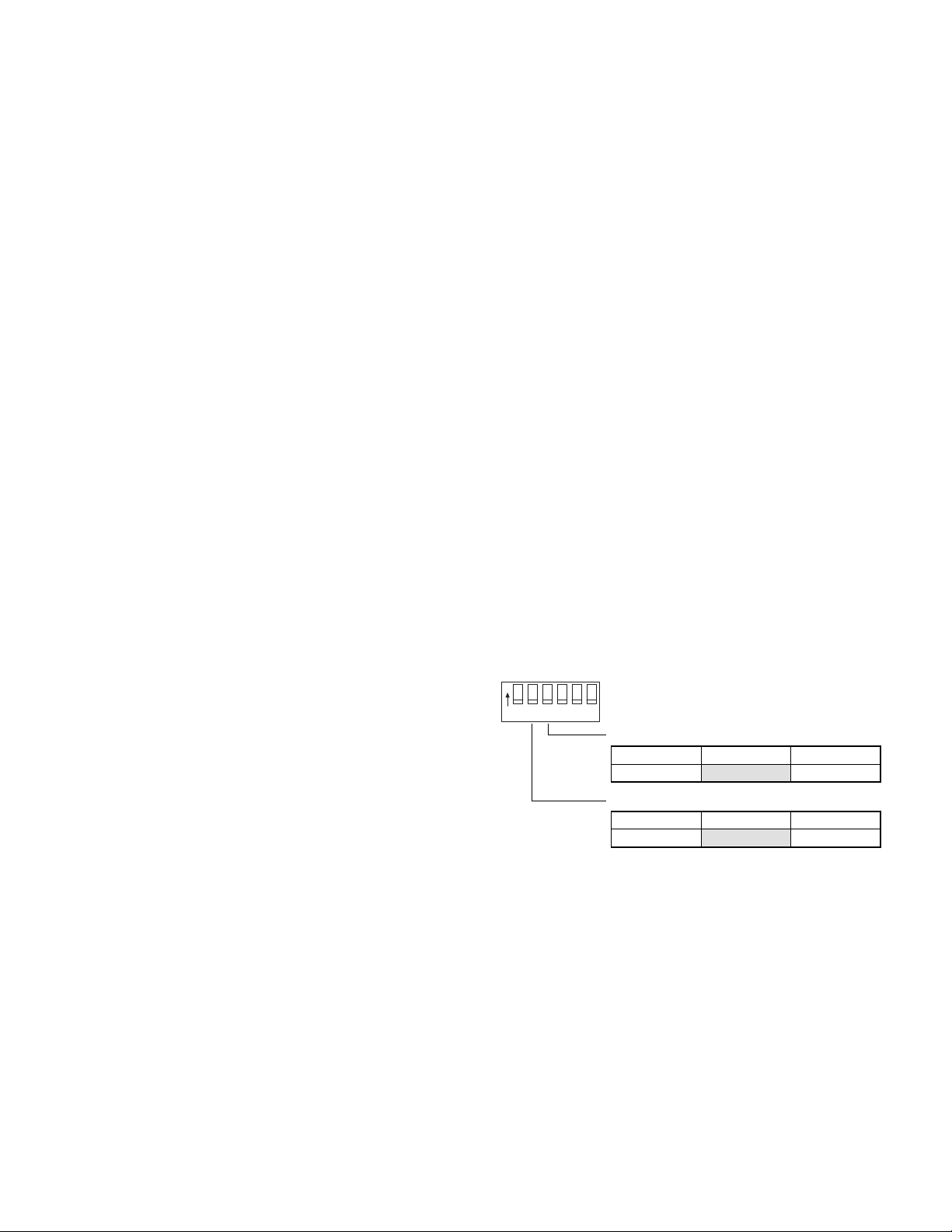

3-7. System switch

The system switch is used to preset for system configuration.

[Out line]

The system switch is consist of DIP switch and Jumper switch.

[DIP switch]

System switch

3-6. Shutdown switch

Shutdown switch used when the OS or application programs are

straying and the system can not return to the normal state.

You must not use this shutdown switch when t he UP-5700 is running

normally. Use this switch only when the main power source is not cut

off even if the main unit power switch is set to OFF position. UP-5700

is turned OFF and the hardware is reset by turning the main power

switch OFF and then pressing the shutdown switch.

123456

Shut down switch

123456

The PSC2 simply reads switched signals from the DIP switch as

hardware. The meaning of DIP switch wholly depends on the software.

ON

123456

ON

OFF

: Default setting

DSW-6

Function OFF (value = 1) ON (value = 0)

CMOS Initialize Not Initialize Initialize

DSW-5

DWS-4

Drive C:, D: & E: Setting

Drive C: Drive D: Drive E: SW-4 SW-5

Flash

PS RAM HDD

ROM

HDD — —

HDD PS RAM

PS RAM

Flash

ROM

Flash

ROMON(value = 0)

HDD

OFF

(value = 1)

ON

(value = 0)ON(value = 0)

OFF

(value = 1)ON(value = 0)

OFF

(value = 0)

OFF

(value = 1)

[Out line]

The shutdown switch is single shot type. (Normally OFF position)

Push ON: This position is used to reset stand-by mode for power

supply unit when software hang up.

Release OFF: Usually the shutdown switch needs to be set to this

position when the UP-5700 is operated.

[Operating method]

The shutdown switch is a push switch. If it is push ON, UP-5700

performs to stop supplying the power when t he power switch is set

into stand-by mode.

NOTE: The shutdown operation will be ignore when te power switch

is set into power-on position.

1 – 2

DSW-3

Function OFF (value = 1) ON (value = 0)

Boot Drive Drive A: Drive C:

DSW-2

Function OFF (value = 1) ON (value = 0)

Drive A: Device Mask ROM FDD

DSW-1

Function OFF (value = 1) ON (value = 0)

Floppy Disk

Controller

Not Exit Exit

Page 5

[Jumper switch]

Jumper switches the following functions for UART1 and UART2 in the

PSC2.

8 7

ON

OFF

SW Function OFF (value = 1) ON (value = 0)

7COM3 & COM4 IRQ

assign

8 G/A UART1&2

decode mode

COM3 = IRQ11 COM3 = IRQ4

COM4 = IRQ10 COM4 = IRQ3

COM3 & COM4 COM5 & COM6

When SW8 is set to ON, the setting of SW7 is not valid.

3-8. Power switch

[Out line]

The power switch has the positions ON and OFF (Stand-by)

ON position: Usually the power switch needs to be set to t his posi-

tion when the POS-terminal is operated.

OFF position: This position is used to turn the stand-by mode. When

the power switch is set to this position, power supply

stops automatically. But if the soft ware program control the power supply to hold, even if the power switch

is set into this position, power supplying will be kept

until an software program allows power supply no to

hold.

[Operating method]

The power switch is a seesaw switch, and it can be tipped toward the

ON or OFF.

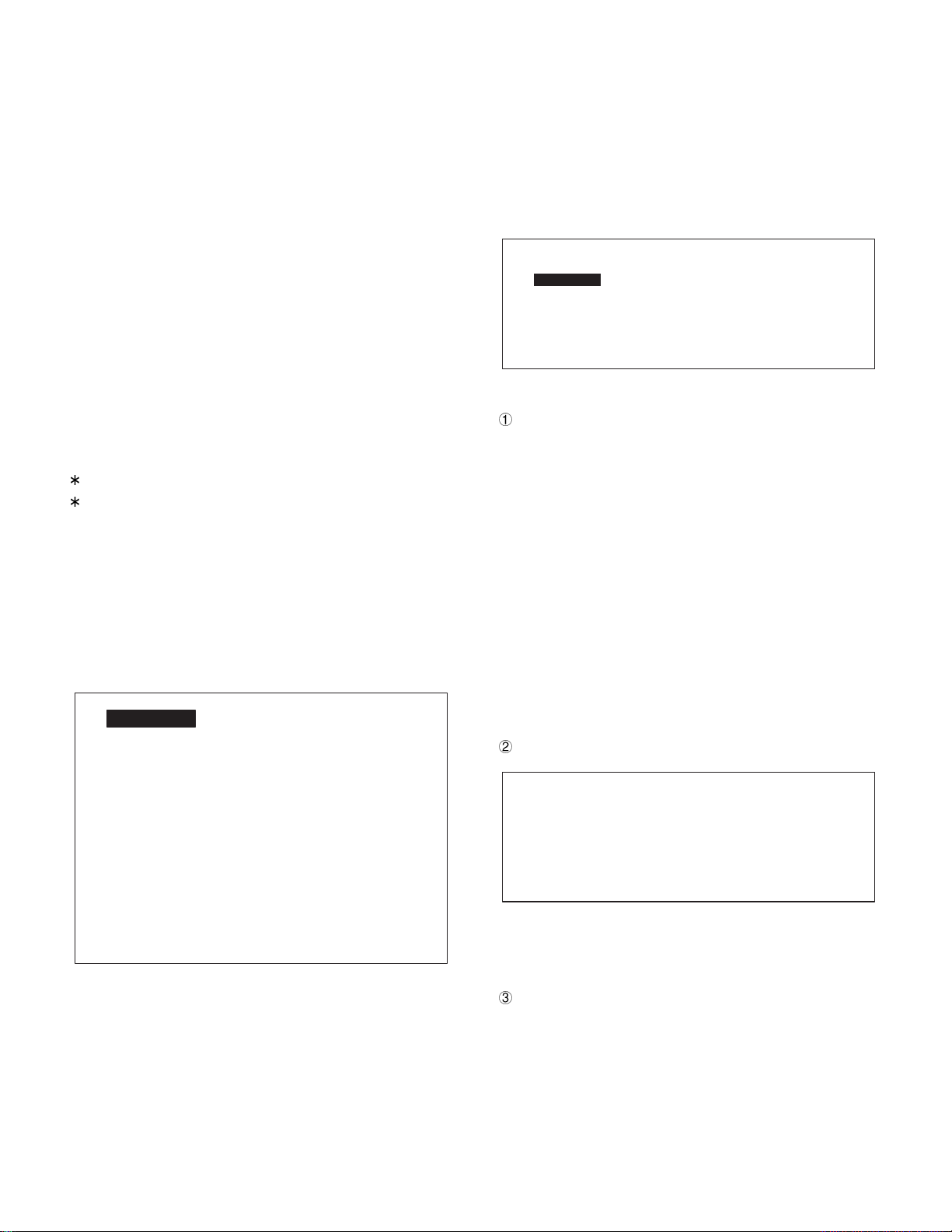

4. Software

4-1. Software Structure

The basic system software is mainly consisted of the following 3

modules.

(1) MS-DOS Version 6.22

The operating system (MS-DOS Version 6.22) is stored in MROM

disk.

(2) Drivers

There are following types of drivers

· POS Device Driver (for Clerk, Buzzer, Drawer, Timer, MCR, Line

Display, Serial Port) POS device drivers adopt same control

method as the control of former (ER-A850/A880) software.

· SRN Driver

· Touch Panel Driver

(3) POS Device Middleware

Middleware helps improve development of applications.

(4) Software Structure

Power switch

The power switch is used to turn the POS terminal on or stand-by

If the communication function is used, the AC power can be turned off

by software operation for power saving after communication.

SRN

Driver

Touch

Panel

Driver

Application

POS Device

Mifddle Wsre

DOS Devlce Driver

MS-DOS Version 6.22

BIOS

Hardware

Provided from SHARP

POS Utillty

Standard PC

Device Driver

(Local production)

SCSI

Ethernet

.......etc

1 – 3

Page 6

4-2. Basic system software list

ITEM CONTENTS for UP-5700 for PC

BIOD (FROM)

· AT compatible system BIOS

· VGA BIOS for C&T65550 VGA LSI

· Standard SETUP program

· Flash Disk/MROM Disk/PSRAM Disk built-in control program

· Memory size/HDD type auto detect function

· No APM/PnP support

OS (MROM disk) MS-DOS Version 6.22 (Subset)

Install program (MROM disk)

· System Install program

· APL Install program (for MS-DOS/Windows 95) —

POS device driver · POS device driver —

· SRN driver

· Touch panel driver (mouse emulation I/F only) —

Middleware soft and

application development tools

· POS device MiddleWare —

· R/J Logo image loading utility program (MS-DOS/Windows 95)

· Touch panel calibration utility program (MS-DOS) —

... These software are provided with FD from SHARP.

Please copy contents of FD provided from department to development PC. Install to UP-5700 by using APL Install Program from PC.

4-3. Memory map

—

0000000h

STD. 8MB

0800000h

+8MB

1000000h

1800000h

2800000h

(16MB)

+8MB

(24MB)

+32MB

(40MB)

Memory is expandable up to

32MB using EMM386 in DOS.

00000h

9F4000h

A0000h

C0000h

CB000h

E8000h

100000h

MS-DOS

(25K)

Sharp Driver

(32K)

Free

Conventional

(580K)

EBDA : 3K

VRAM

128K

VGA BIOS(40K)

UMB

(116K)

System BIOS

(96k)

HMA

64K

Not Use Middleware

POS Device 20K

Touch Key 12k

(External BIOS

Data Area)

00000h

9F4000h

A0000h

C0000h

CB000h

E8000h

100000h

MS-DOS

(25K)

Sharp Driver

(32K)

Middleware

(15K)

Free

Conventional

(565K)

EBDA:3K

VRAM

128K

VGA BIOS(40K)

UMB

(116K)

System BIOS

(96k)

HMA

64K

Use Middleware

POS Device 20K

Touch Key 12k

(External BIOS

Data Area)

1 – 4

Page 7

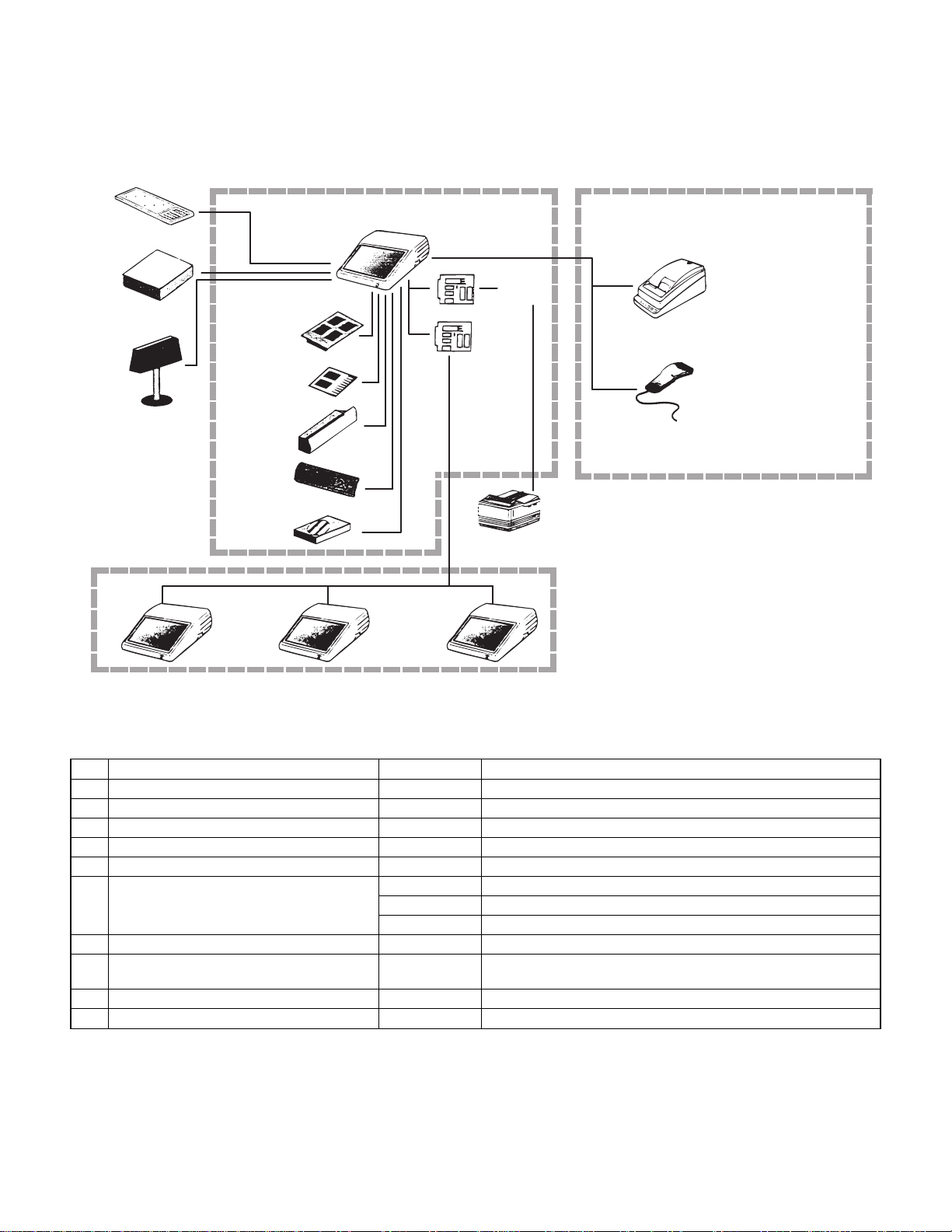

CHAPTER 2. OPTIONS

1. System configuration

AT Keyboard

<supplied on site>

Drawer

<Option>

ER-03DW/

04W/05DW

Customer

Poll Display

<Option>

UP-P20DP

In-line Communication

Connection

Incorporated in Main Unit

max.2

Additional

RAM Memory

<Option>

UP-P02MB

Additional

ROM Memory

<Option>

UP-F04RB

Additional DRAM

Memory

<supplied on site>

Magnetic

Card Reader

<Option>

UP-E12MR

Customer

Display

<Option>

ER-A8DP

HDD Unit

<supplied on site>

Master Machine

UP-5700

(RS-232)

RS232 Board

<Option>

ER-A8RS

SRN Board

<Option>

ER-01IN-PC

Ethernet Board

<supplied on site>

Centronics Printer

<supplied on site>

RS-232 Communication Connection

max.6

Hand Scanner

Remote Printer

<Option> ER-01PU

<supplied on site> TM-T80/85/295

ER-FBT40

<Option>

ER-A6HS1

Satellite Machine

UP-5700

2. Options

No. NAME MODEL NAME DESCRIPTION

1 Expansion RAM disk board UP-P02MB 2 Mbytes RAM board

2 Expansion ROM disk board UP-F04RB 4 Mbytes ROM board

3 Customer display ER-A8DP 1 line 7-segments display

4 Customer pole display UP-P20DP 2 line 20 digits dot display

5 MCR (Magnetic Card Reader) UP-E12MR for ISO 1 & 2 stripe card

6 Remote drawer ER-03DW

ER-04DW

ER-05DW

7 PC-SRN board ER-01IN-PC SRN communication board for ISA bus slot

8 RS232 & CENTRO I/F board ER-A8RS RS232 9 pins connector: 2 ports

CENTRONICS 25 pins connector: 1 port

9 Receipt/Journal printer ER-01PU 2 station (R/J) printer

10 Hand scanner ER-A6HS1 for reading bar code

2 – 1

Page 8

3. Service options: None

No. NAME PARTS CODE

1 HDD kit

4. Service tools

No. NAME PARTS CODE PRICE DESCRIPTION

1 Service tool kit

2 Printer connector signal loop back connector

3 MCR test card

4 RS232 loop back connector

5 CPU/VGA PWB relay PWB

6 BIOS loading board

7 RS232 modular jack loop back connector

8 BIOS MASTER ROM

9 TOUCH PEN

*

1 Always use this pen for the TOUCH PANEL POSITION ADJUSTING UTILITY PROGRAM.

This pen is for K-PDA (ZR-xxxx series).

If you use a ball-point pen or other pens whose point is hard, the surface of TOUCH PANEL may be damaged.

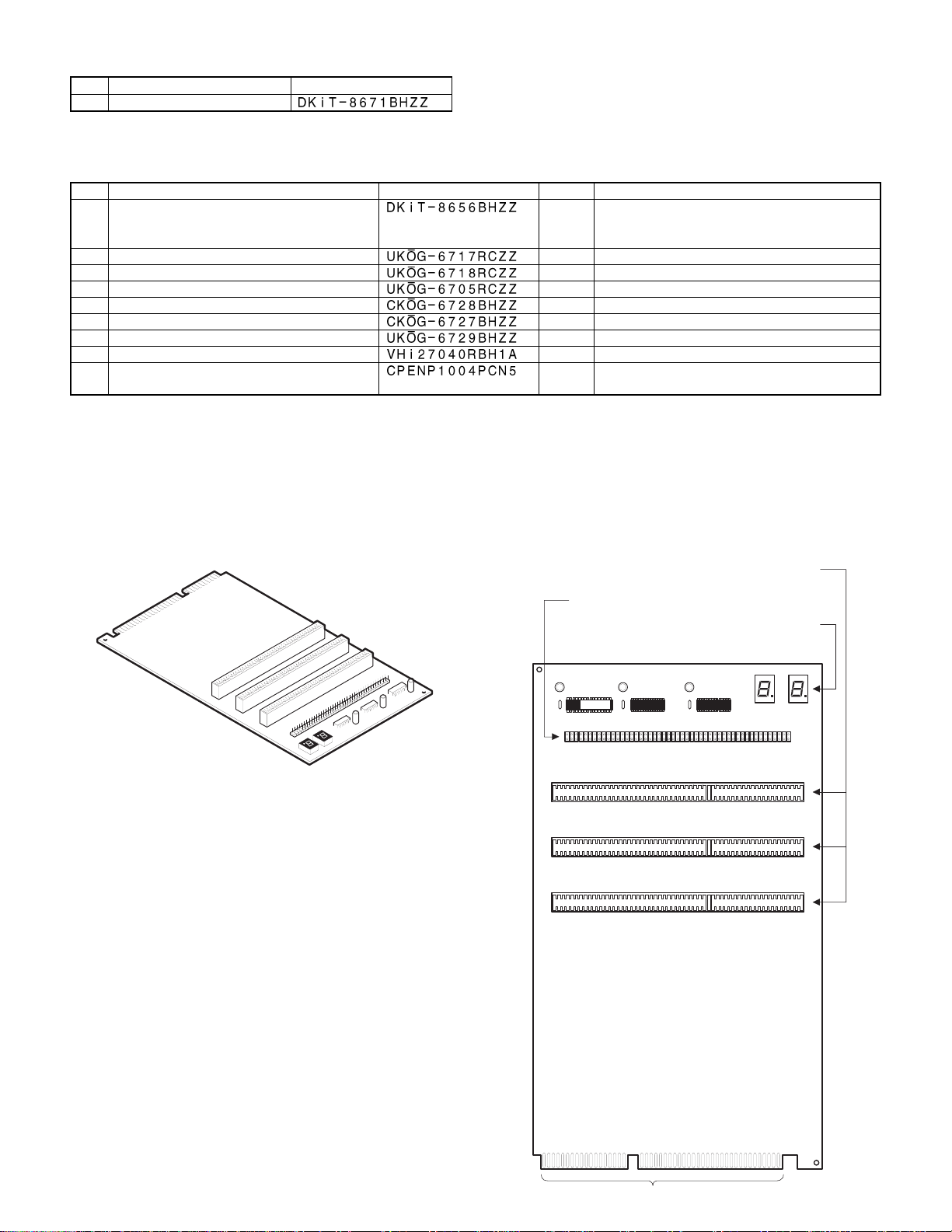

4-1. Service tool kit: DKIT-8656BHZZ

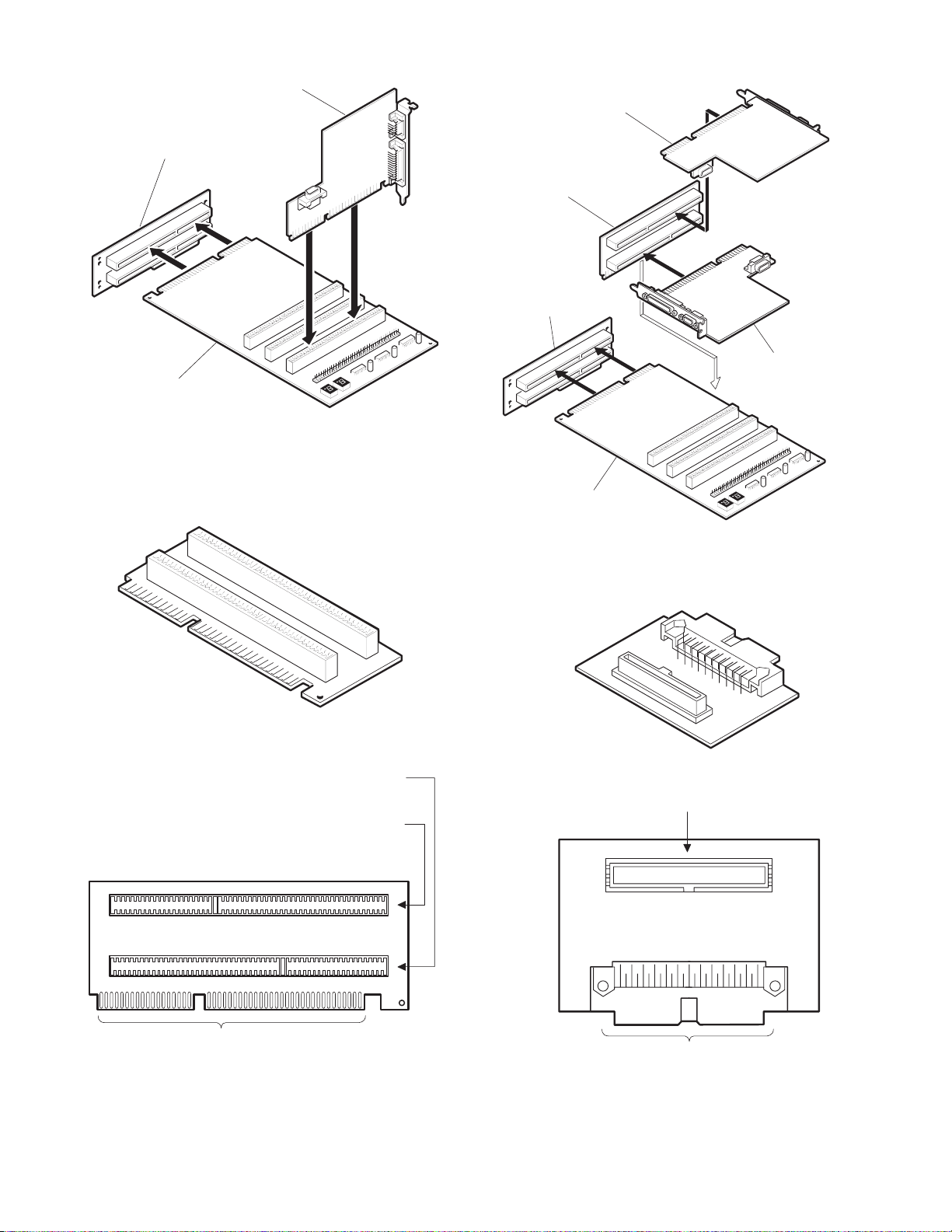

1) ISA checker

Used to repair or check the operation of the optional I/F.

· External view · Plan view

CW ISA checker

ISA relay board

RAM relay board (Not used for UP-5700)

BR for ER-A8RS CENTRONICS connector

BE for UP-E12MR

BC for RS232 connector

CQ

CS for overwriting BIOS

AZ for RJ45 connector

(P) EP-ROM for overwriting BIOS

AG For TOUCH PANEL POSITION ADJUSTING

UTILITY PROGRAM *1

ISA bus connectors:

Used to connect with the I/F PWB of ER-A8RS,

ER-01IN-PC etc.

Test pins: Used to check the ISA bus signal.

LED circuit: Not used currently.

RAM1A

2 – 2

Connected to the ER-A850/A880 ISA bus connectors.

Page 9

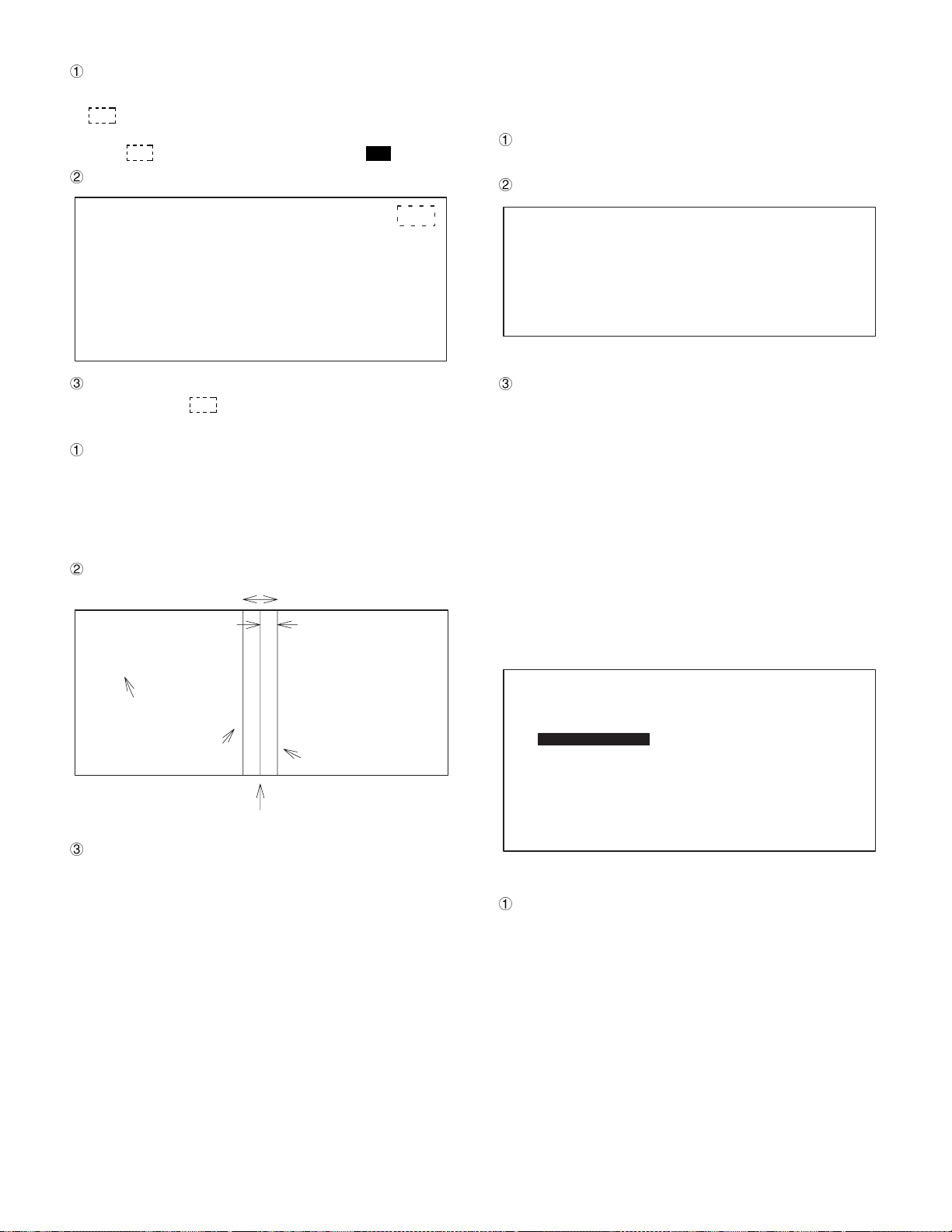

· Connection diagram

· Connection diagram

ER-A8RS

(or ER-01IN-PC)

UP-5700

ISA bus connector

ISA checker

2) ISA relay board

Connected to the ISA checker for installation of the optional I/F horizontally and for repairing and checking the operation .

· External view

ER-A8RS (or ER-01IN-PC)

solder side

ISA relay board

ISA PWB

ER-A8RS (or ER-01IN-PC)

parts side

ISA checker

· Plan view

ISA bus connector:

Used to check the ER-A8RS (or ER-01IN-PC)

parts side.

ISA bus connector:

Used to check the ER-A8RS (or ER-01IN-PC)

solder side.

3) RAM PWB relay board (UP-5700: Not used)

· External view

· Plan view

Connected to the ISA bus connector of ISA checker.

2 – 3

Page 10

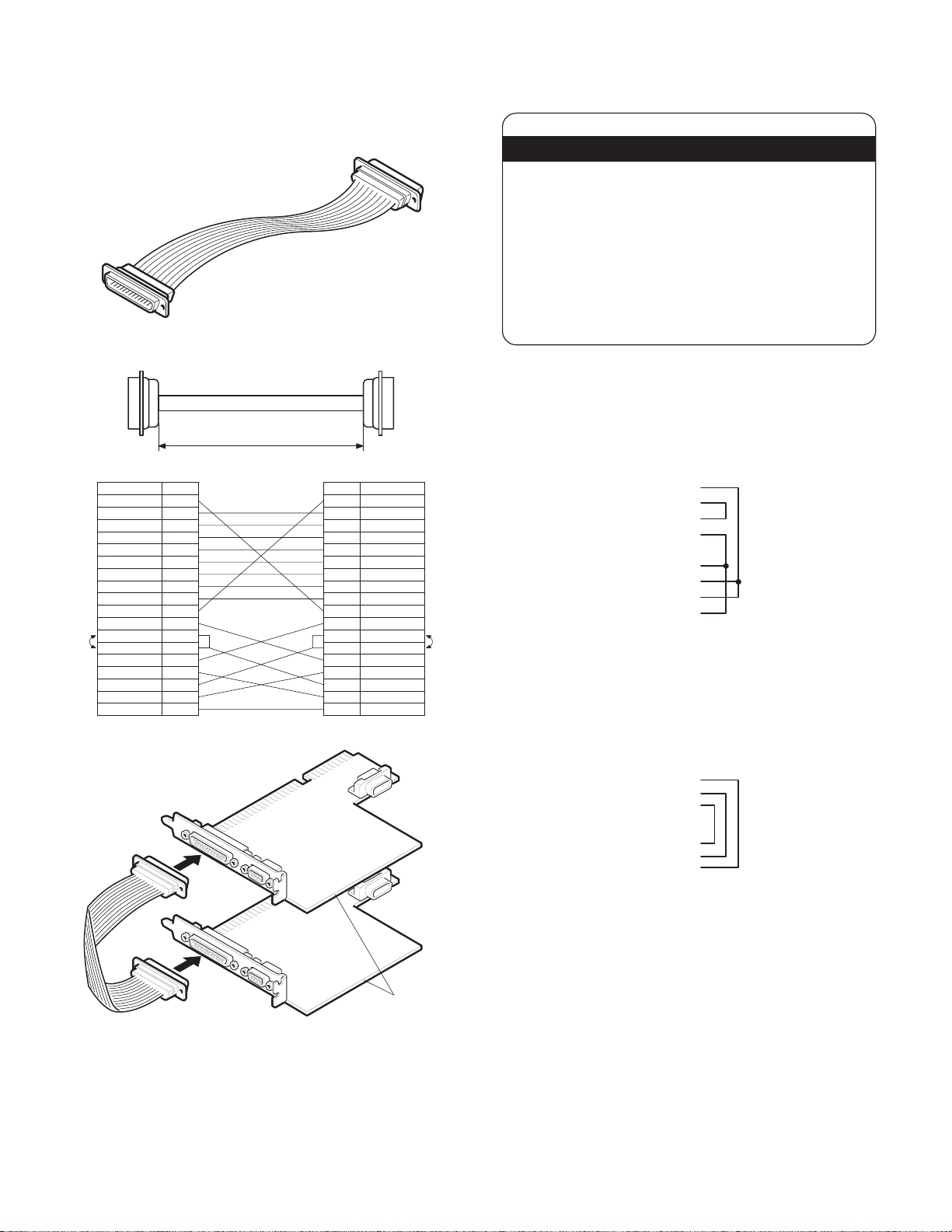

4-2. Printer connector signal loop check cable:

UKOG-6717RCZZ

Connected to the centronics connector (25 pin) of the ER-A8RS, and

used to check loop signals when executing diagnostics.

· External view

· Plan view and connection diagram

150±8

4-3. MCR test card: UKOG-6718RCZZ

Used when executing the diagnostics of the UP-E12MR.

·

· External view

4-4. RS232 loop back connector: UKOG-6705RCZZ

Connected to the RS232 connector (D-SUB 9 pin: COM1, COM2,

COM3, COM4) of the UP-5700 and ER-A8RS, and used to check

loop signals when executing diagnostics.

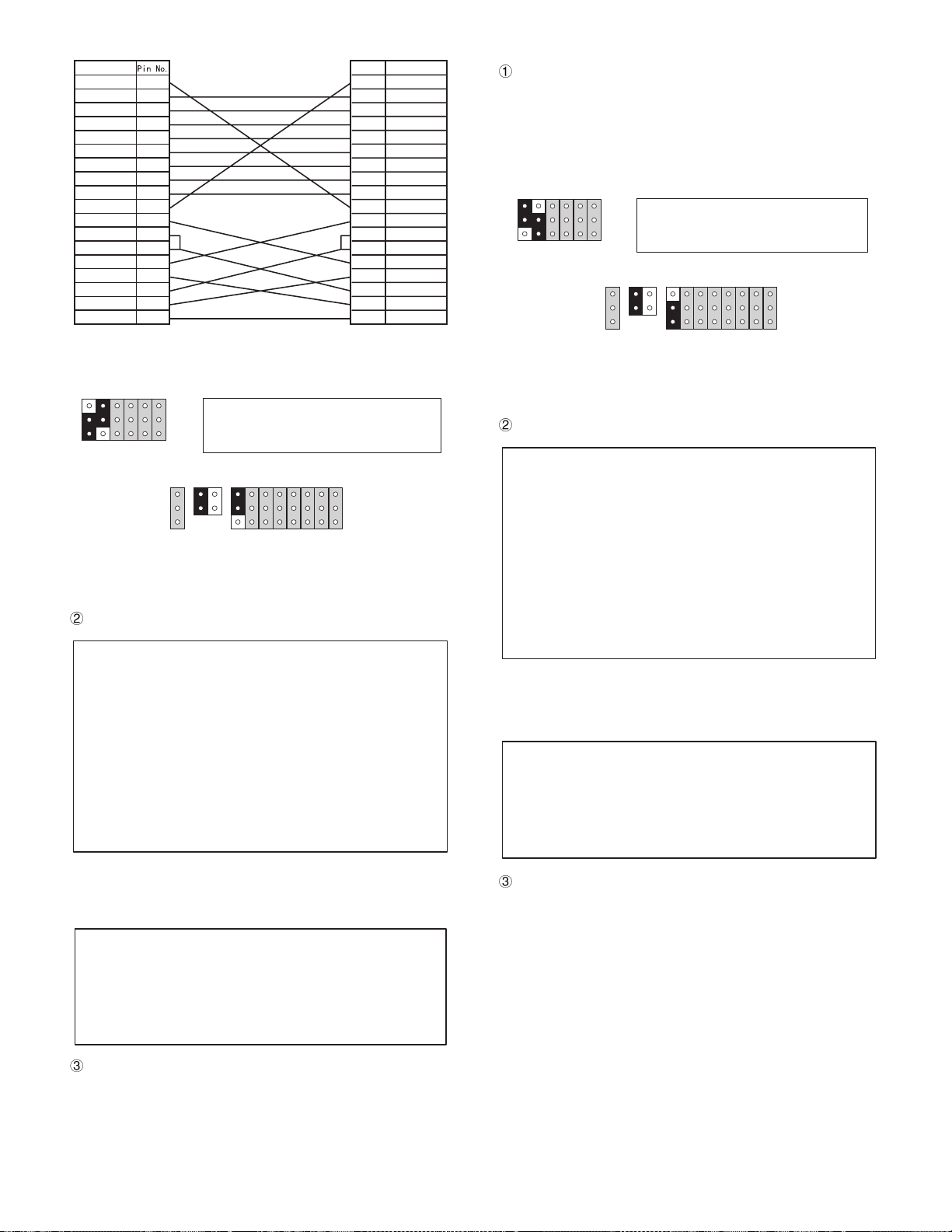

· Connection diagram

Signal name Pin No.

1STROBE2DB0

3DB1

4DB2

5DB3

6DB4

7DB5

8DB6

9DB7

10ACK11BUSY

12PE

13SLCT

14AUTOFD15ERROR16INIT17SLCTIN-

18~25PE

· Connection diagram

Signal namePin No.

1 STROBE2DB0

3DB1

4DB2

5DB3

6DB4

7DB5

8DB6

9DB7

10 ACK11 BUSY

12 PE

13 SLCT

14 AUTOFD15 ERROR16 INIT17 SLCTIN-

18~25 PE

CD 1pin

RD 2pin

TD 3pin

DTR 4pin

GND 5pin

DSR 6pin

RTS 7pin

CTS 8pin

RI 9pin

4-5. RS232 modular jack loop back connector:

UKOG-6729BHZZ

Connected to the RS232 connector (RJ45: COM5, COM6) of the

UP-5700 and ER-A8RS, and used to check loop signals when executing diagnostics.

· Connection diagram

RTS

1pin

DTR

2pin

TD

3pin

GND

4pin

GND

5pin

RD

6pin

DSR

7pin

CTS

8pin

ER-A8RS

2 – 4

Page 11

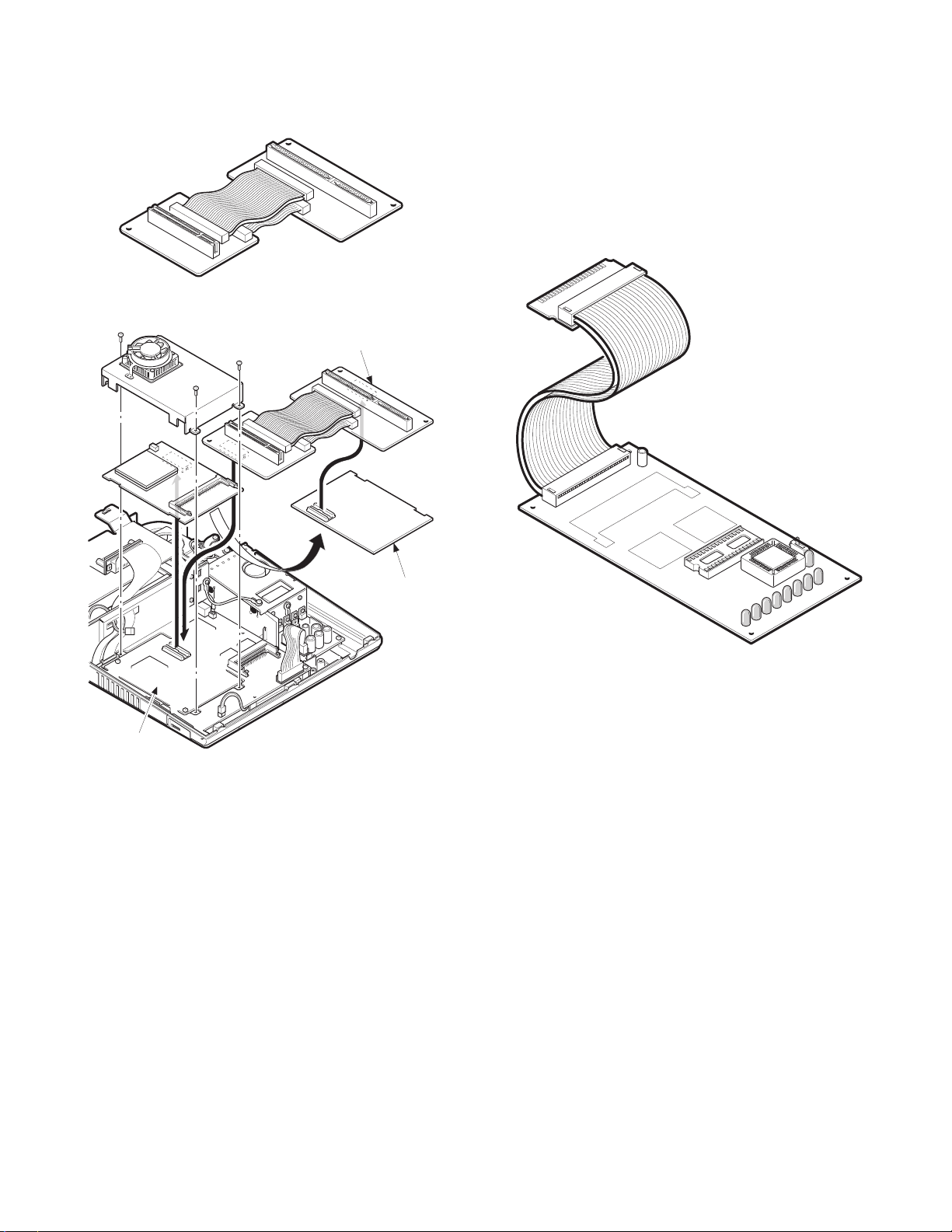

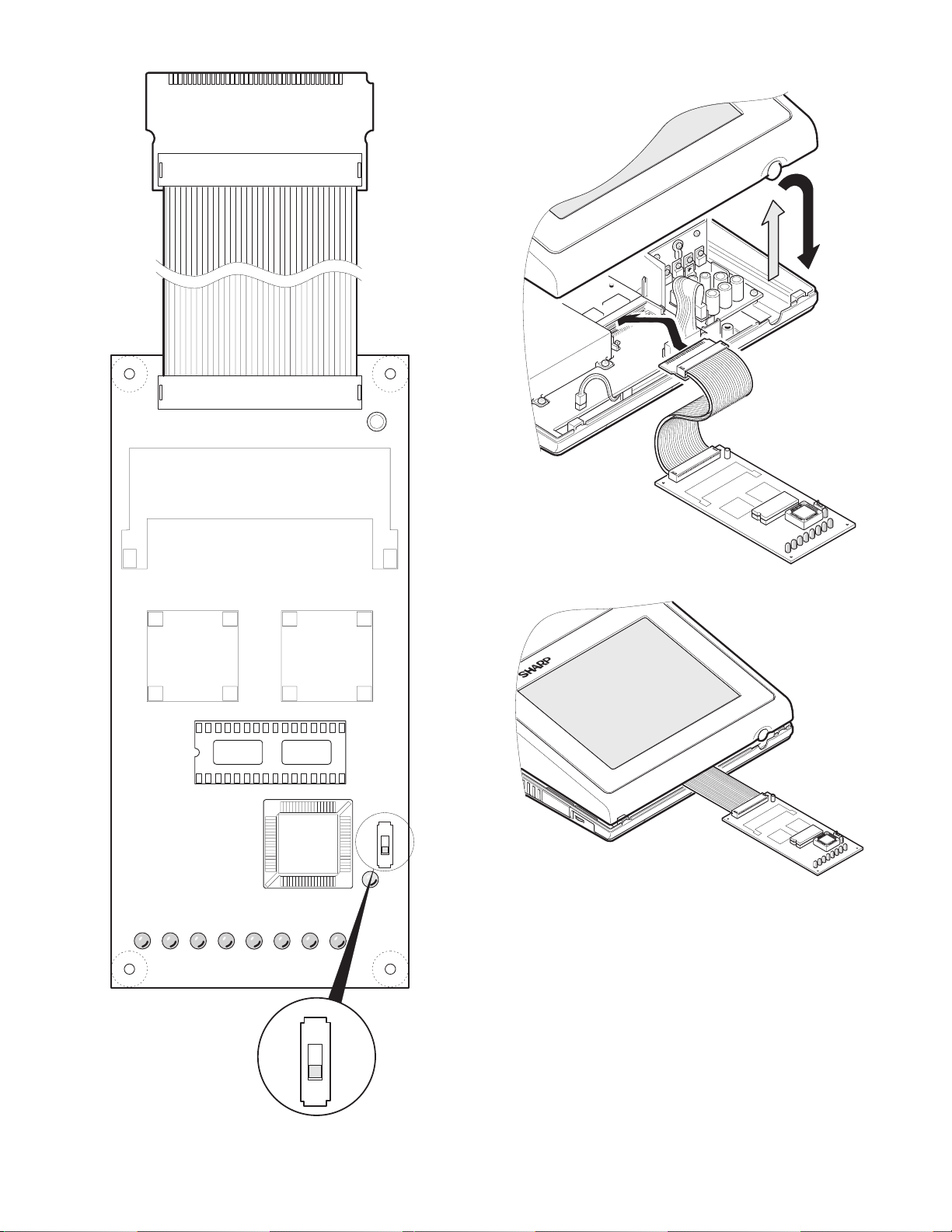

4-6. CPU/VGA PWB relay PWB: CKOG-6728BHZZ

The CPU PWB, you can check the soldered face of the CPU PWB by

connecting the CPU PWB to the VGA PWB.

· External view

· Connection diagram

CPU/VGA PWB relay PWB

4-7. BIOS loading board: CKOG-6727BHZZ

The BIOS loading board: CKOG-6727BHZZ is a tool to write a BIOS

ROM program in the F-ROM on the UP-5700’s main board. Use this

PWB in the following cases:

· The F-ROM on the UP-5700’s main board is changed due to some

defect and a BIOS ROM program is written in the F-ROM.

· The BIOS ROM program in the F-ROM is overwritten due to the

version up of BIOS ROM program, etc.

Connected to the Option ROM/RAM disk connector (CN19) of the

Main PWB.

· External view

Main PWB

CPU PWB

2 – 5

Page 12

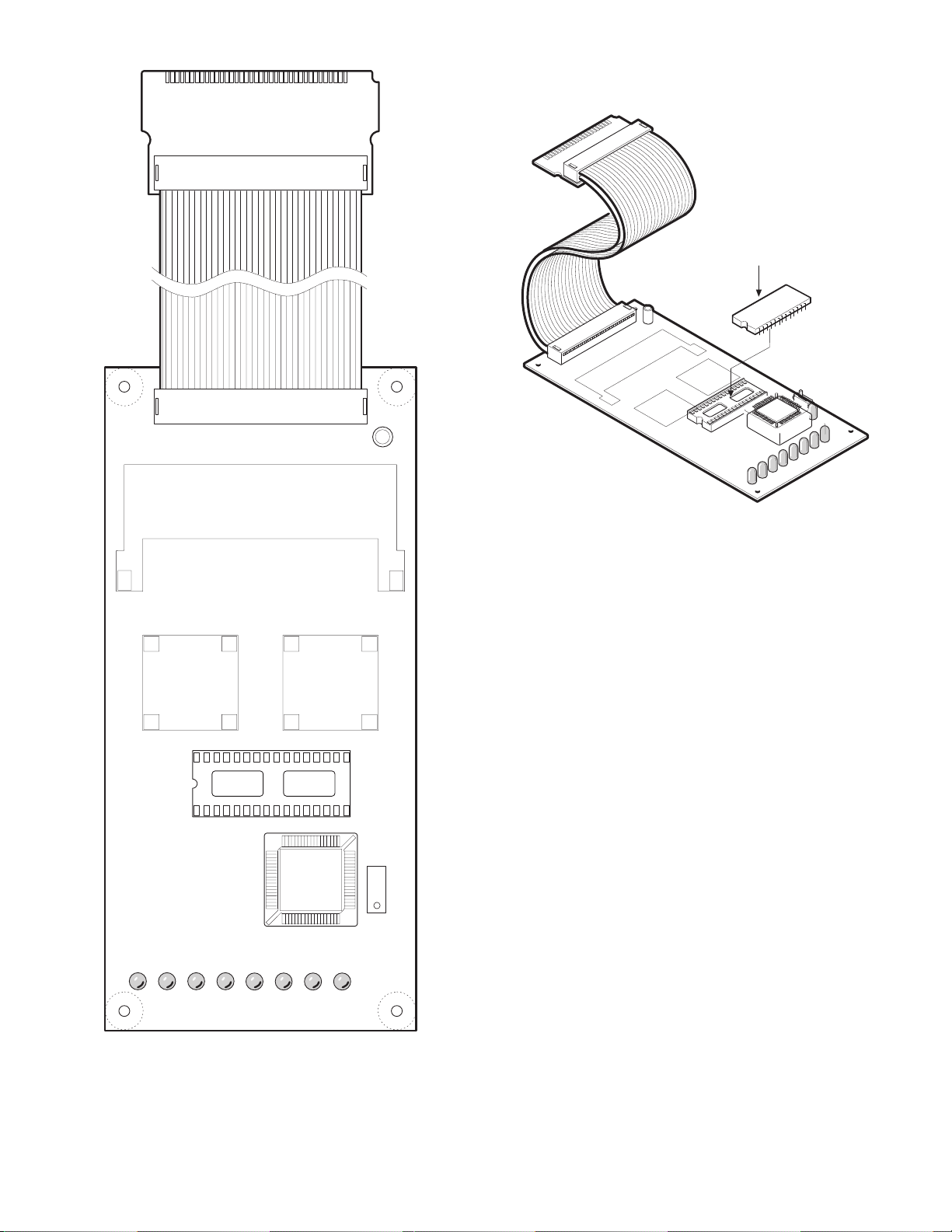

· Plan view

Writing BIOS ROM Program

1. Install the EP-ROM (master ROM): VHI27040RBH1A containing a

BIOS program on the BIOS loading board: CKOG-6727RCZZ.

BIOS MASTER ROM

LED1 LED2 LED3 LED4 LED5 LED6 LED7 LED8

· Connection diagram

SW1

13

2 – 6

Page 13

2. Set SW1 on the BIOS loading board to the side of pin 3.

4. Connect the BIOS loading board to the option ROM/RAM connector CN19 on the main PWB, and then close the cabinet.

LED1 LED2 LED3 LED4 LED5 LED6 LED7 LED8

3. Open the upper cabinet.

SW1

SW1

1

3

LED9

5. Writing the BIOS ROM program starts by turning on the power

switch on the right side.

For the status of LED on the special service PWB when a BIOS

ROM program is being written, see the following table.

Writing is complete (automatic completion) when the green LED

(LED9) on the BIOS loading board lights up.

SW1

1

3

6. After writing is complete, turn off the power switch on the right

side to remove the BIOS loading board, and turn on the power

switch on the left side again to check whether the BIOS program

starts up normally or not.

2 – 7

Page 14

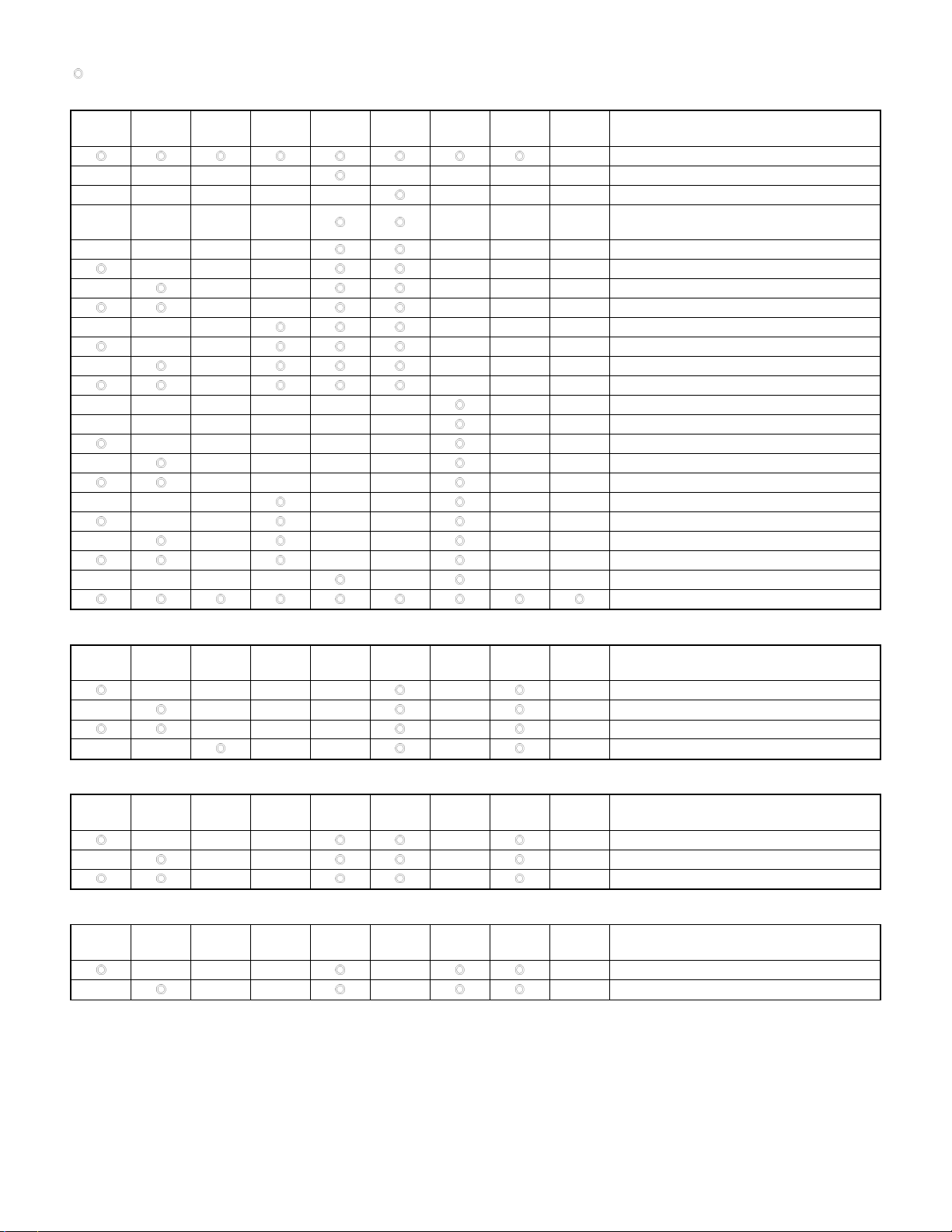

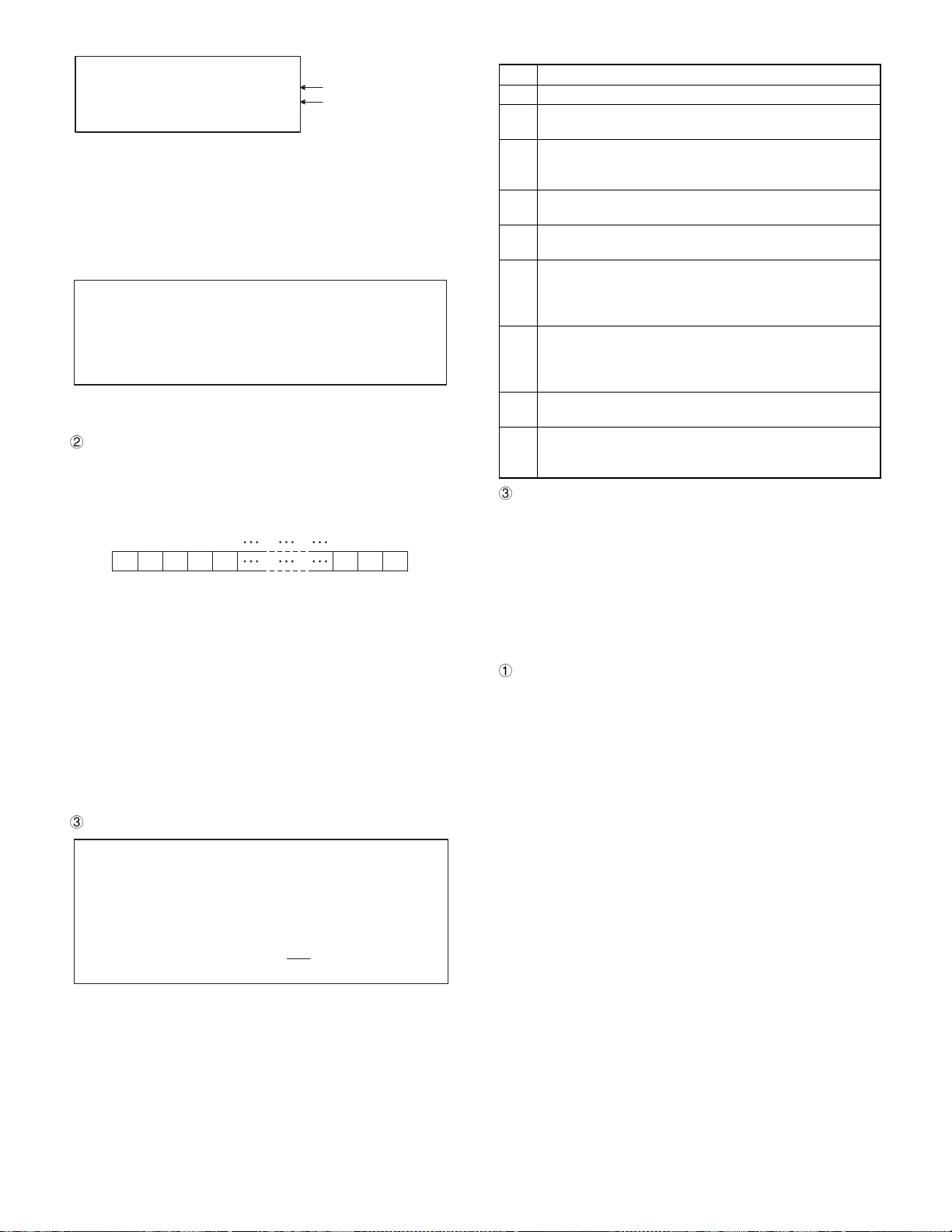

LED DISPLAY STATUS

[ : ON (Lighting) — : OFF]

<In normal operation>

LED1

(RED)

————

—————

————

————

—

———

—

——————

——————

—

———

—

————

LED2

(RED)

——— — — — Programming: Bank0 D0000 h (64KB)

—— — — — Programming: Bank1 D0000 h (64KB)

————— — — Verifying: Bank0 D0000 h (64KB)

—— —— — — Verifying: Bank1 D0000 h (64KB)

LED3

(RED)

—— — — — Programming: Bank0 E0000 h (64KB)

—— — — — Programming: Bank0 F0000 h (64KB)

— — — — Programming: Bank1 E0000 h (64KB)

— — — — Programming: Bank1 F0000 h (64KB)

———— — — Verifying: Bank0 E0000 h (64KB)

———— — — Verifying: Bank0 F0000 h (64KB)

— —— — — Verifying: Bank1 E0000 h (64KB)

— —— — — Verifying: Bank1 F0000 h (64KB)

LED4

(RED)

LED5

(RED)

—— — — Verifying: Bank1 C0000 h (64KB)

LED6

(RED)

LED7

(RED)

————Start initializing

— — — Erasing F-ROM (LED6: RED is blinking)

———

— — — Programming: Bank0 C0000 h (64KB)

— — — Programming: Bank1 C0000 h (64KB)

— — — Setting protection the F-ROM

LED8

(RED)

— — Start verifying the program in the F-ROM

— — Verifying: Bank0 C0000 h (64KB)

LED9

(GREEN)

— Start of COPY FUNCTION

Start copy programming to F-ROM from EPROM

END of complete COPY FUNCTION

FUNCTION

<Erase ERROR in F-ROM>

LED1

(RED)

—

——

<Programming ERROR in F-ROM>

LED1

(RED)

—

<Verifying ERROR in F-ROM>

LED1

(RED)

—

LED2

(RED)

———— — — Device not ready

LED2

(RED)

——— — — Device not ready

LED2

(RED)

——— — — Device not ready while release the protection

LED3

(RED)

——— — — VPP error

——— — — Command sequence error

LED3

(RED)

—— — — VPP error

—— — — Command sequence error

LED3

(RED)

—— — — Can not release the protection

LED4

(RED)

—— — —

LED4

(RED)

LED4

(RED)

LED5

(RED)

LED5

(RED)

LED5

(RED)

LED6

(RED)

LED6

(RED)

LED6

(RED)

LED7

(RED)

LED7

(RED)

LED7

(RED)

LED8

(RED)

LED8

(RED)

LED8

(RED)

LED9

(GREEN)

LED9

(GREEN)

LED9

(GREEN)

FUNCTION

FUNCTION

FUNCTION

2 – 8

Page 15

CHAPTER 3. SERVICE PRECAUTION

1. Conditions for soldering circuit parts

To solder the following parts manually, follow the conditions described below.

PARTS NAME PARTS CODE LOCATION CONDITIONS FOR SOLDERING

Ceramic oscillator

DIP SWITCH

MAIN PWB: X1 (8M) 270°/3sec.

MAIN PWB: X2 (24M)

MAIN PWB: X2 (7.37M)

MAIN PWB: S3 3000°/3sec.

2. Cautions on handling CPU and POWER

FAN

When removing or performing any other operation on the CPU and

POWER FAN, be sure to handle them with care, because it may

cause abnormal sound or deteriorate the performance while the CPU

FAN is rotating if they are dropped or given heavy impact.

3. Note for handling of Touch panel

· The transparency of the touch panel should be vitally important.

Do not put finger prints or wat er print on the surface. Use clean

finger such or gloves and masks.

· For handling, do not hold the transparent are, and do not hold the

heat seal connector section to assure reliability.

· Do not overlay touch panels. The edge may damage the surface.

· Do not put a heavy thing on the touch panel.

· Do not apply a strong shock, and do not drop it.

· When attaching the protection film again, carefully check for no

dirt. If there is any dirt, it is transferred.

· To clean dirt on the surface, use dry, soft cloth or a cloth immersed

in ethyl alcohol.

· Check that the housing does not give stress to the touch panel.

· Be careful not to touch the touch panel with tools.

· The heat seal section is easily disconnected. Be careful not to give

a stress to the heat seal section when installing.

· The touch panel is provided with an air groove to make the exter-

nal and the internal air pressure equal to each other. If water or oil

is put around the air groove, it may penetrate inside. Be careful to

keep the air groove away from water and oil.

· Input is performed with fingers. Do not use a hard thing for input-

ting.

4. Note for handling of LCD

· The LCD elements are made of glass. BE careful not to give them

strong mechanical shock, or they may be broken. Use extreme

care not to break them.

· If the LCD element is broken and the liquid is leaked, do not lick it.

If the liquid is attached to your skin or cloth, immediately clean with

soap.

· Use the unit under the rated conditions to prevent against damage.

· Be careful not to drop water or other liquid on the display surface.

· The reflection plate and the polarizing plate are easily scratched.

BE careful not to touch them with a hard thing such as glass,

tweezers. Never hit, push, or rub the surface with hard things.

· When installing the unit, be careful not to apply stress to the LCD

module. If an excessive stress is applied, abnormal display or

uneven color may result.

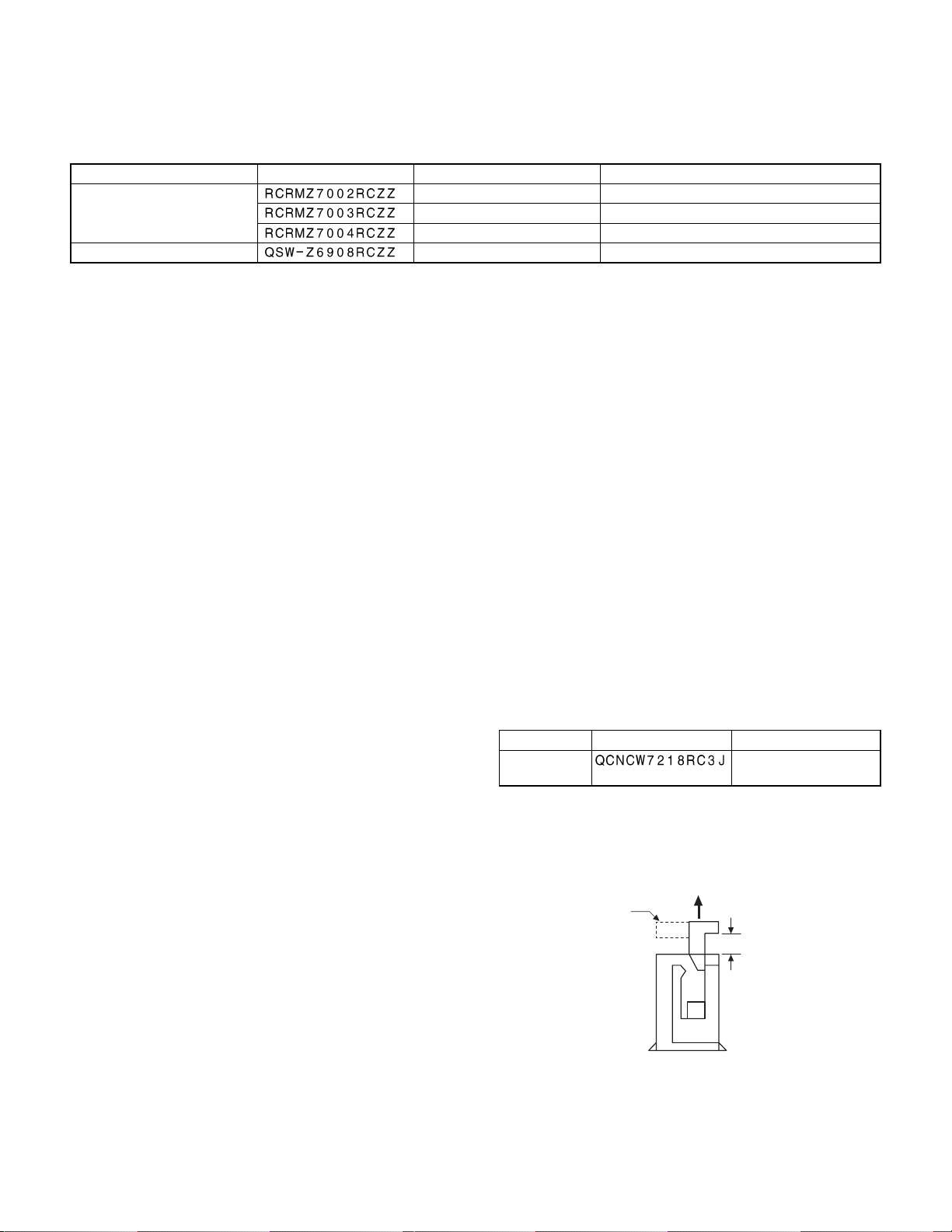

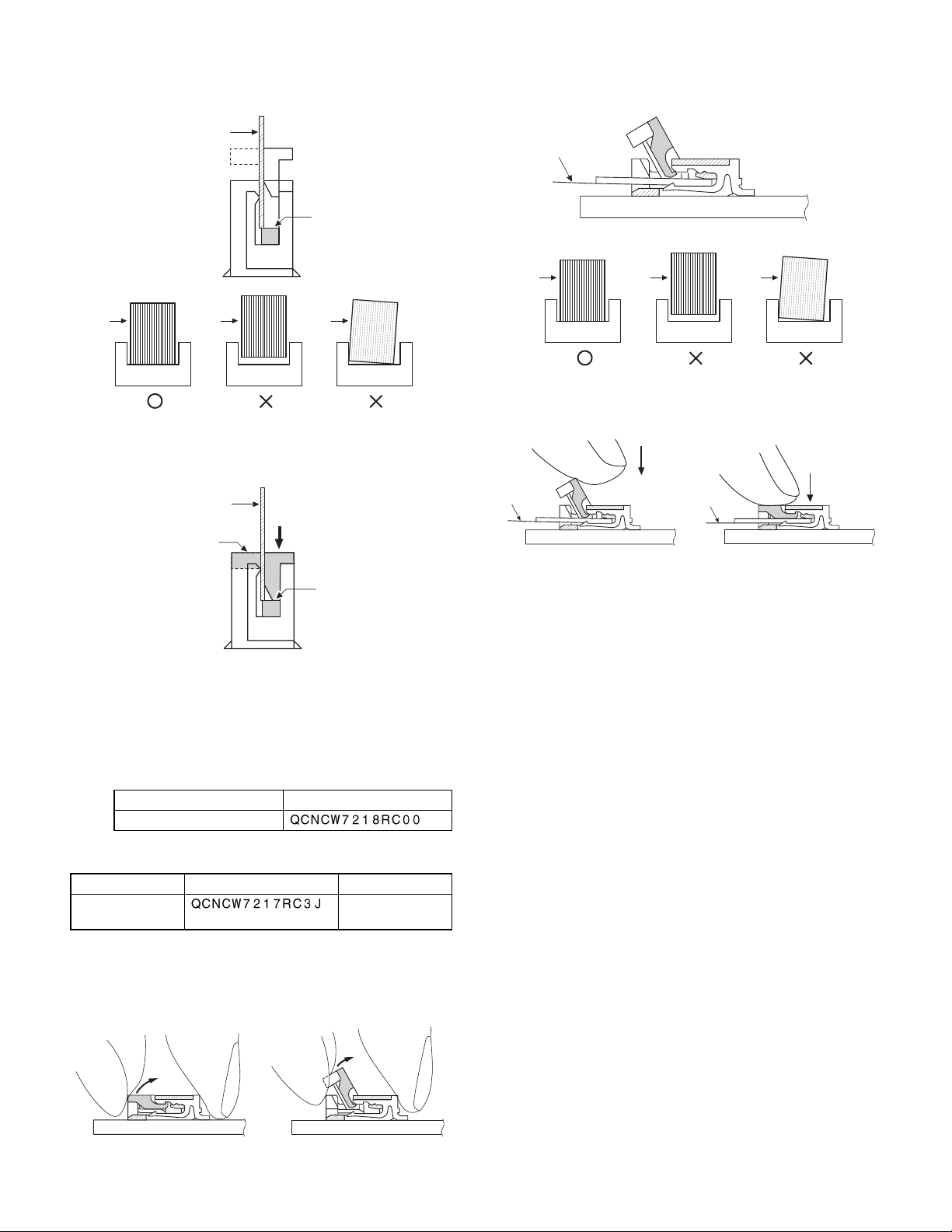

5. Cautions on handling connectors

When connecting or disconnecting the following connectors, follow

the procedures below.

1)

PARTS NAME PARTS CODE LOCATION

FFC

CONNECTOR

· How to Connect or Disconnect FFC

(1) Open the slider to unlock position

The slider will open only up to a fixed height (about 1.2mm). If

you forcibly pull up the slider further, it may be dropped.

UNLOCK

Slider

MAIN PWB: CN12

KEY I/F PWB: CN8/CN10

3 – 1

1.2mm

Page 16

(2) Insert the FFC

Insert the FFC firmly untill the FFC hits the bottom of the connector’s insulator.

FFC

(2) Insert the FFC

Insert the FFC firmly until the FFC hits the bottom of the connector’s insulator.

FFC

FFC

CONNECTOR

FFC

CONNECTOR

FFC

CONNECTOR

(3) Close the slider to lock position

Insert the FFC and then push the slider downward.

FFC

Slider

LOCK

(4) To pull out the FFC, unlock the slider to pull it out in the same

procedures as (1).

· Replacement parts required when the OCNCW7218RC3J’s

slider is broken

Forcibly pulling up the slider further may cause the slider to

drop and to be broken in the worst case. You can change this

slider part only .

PARTS NAME PARTS CODE

SLIDER

2)

PARTS NAME PARTS CODE LOCATION

FFC

CONNECTOR

LCD RELAY

PWB: CN1

FFC

CONNECTOR

FFC

CONNECTOR

FFC

CONNECTOR

(3) Close the slider to lock position

Insert the FFC and then push the slider downward.

FFC

FFC

(4) To pull out the FFC, unlock the slider to pull it out in the same

procedures as (1).

6. AT Keyboard usable for UP-5700

Do not use the following keyboards because they do not work when

connected to the UP-5700.

The UP-5700 can be externally connected to a keyboard.

The UP-5700’s key BIOS conforms to the PC standard, but this

BIOS’s operation is not assured for some keyboards.

Some keyboards may cause operation errors due to delicate timing.

It is currently found out that t he following models of keyboards may

malfunction.

When selecting a keyboard to be connected, operate the keyboard in

advance to check that it correctly works.

· Japanese keyboard (106 keys)

Manufactured by IBM: TYPE/MODEL5576-B01 FRUPN66G0507

· English keyboard (101 keys)

Manufactured by NMB Technologies Inc.: Model: RT6651T+

· How to Insert FFC

(1) Open the slider to unlock position

Open the slider upwards up to an angle of 60 degrees. If the

slider does not fully open, the FFC can not be smoothly inserted.

3 – 2

Page 17

CHAPTER 4. UP-5700

DIAGNOSTICS SPECIFICATIONS

CONTENT

1. General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2. System configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

3. Service diagnostics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

3-1. Service diagnostics getting started . . . . . . . . . . . . . . . . . . 1

3-2. Selection menu. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

3-3. RAM Diagnostics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

1) D-RAM Check . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

2) Standard RAM Disk Check . . . . . . . . . . . . . . . . . . . . 2

3) OPTION RAM DISK Check . . . . . . . . . . . . . . . . . . . . 3

3-4. ROM Diagnostics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

1) DOS ROM Check. . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2) BIOS ROM Check . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3) Standrad FLASH ROM Check . . . . . . . . . . . . . . . . . . 4

4) Option FLASH ROM Check . . . . . . . . . . . . . . . . . . . . 4

3-5. Real time clock & CMOS RAM Diagnostics . . . . . . . . . . . 4

1) Real time clock Check . . . . . . . . . . . . . . . . . . . . . . . . 4

2) CMOS RAM Check . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3-6. Touch Panel Diagnostics . . . . . . . . . . . . . . . . . . . . . . . . . 5

1) Controller Diag Test . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2) Touch Key Pad Test . . . . . . . . . . . . . . . . . . . . . . . . . 5

3) Linearity Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3-7. Clerk Key Diagnostics. . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1) Clerk Key Check . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3-8. Printer Diagnostics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1) PARALLEL1 Loop Check. . . . . . . . . . . . . . . . . . . . . . 6

2) PARALLEL2 Loop Check. . . . . . . . . . . . . . . . . . . . . . 7

3) PARALLEL3 Loop Check. . . . . . . . . . . . . . . . . . . . . . 7

4) PARALLEL1 Print Check . . . . . . . . . . . . . . . . . . . . . . 8

5) PARALLEL2 Print Check . . . . . . . . . . . . . . . . . . . . . . 8

6) PARALLEL3 Print Check . . . . . . . . . . . . . . . . . . . . . . 8

3-9. Serial I/O Diagnostics . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1) COM1 Check . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2) COM2 Check . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

3) COM3 Check . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

4) COM4 Check . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

5) COM5 Check . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

6) COM6 Check . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

3-10. Liquid Crystal Display Diagnostics . . . . . . . . . . . . . . . . . . 9

1) Liquid Crystal Display Check . . . . . . . . . . . . . . . . . . . 9

3-11. Rear Display Diagnostics . . . . . . . . . . . . . . . . . . . . . . . . 10

1) Rear Display Check . . . . . . . . . . . . . . . . . . . . . . . . . 10

3-12. SHARP Retail Network Diagnostics . . . . . . . . . . . . . . . . 11

1) SRN Self Check . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2) SRN Flag Send Check. . . . . . . . . . . . . . . . . . . . . . . 12

3) SRN Data Send Check . . . . . . . . . . . . . . . . . . . . . . 12

4) Data Transmission Check . . . . . . . . . . . . . . . . . . . . 12

3-13. Magnetic Card Reader Diagnostics . . . . . . . . . . . . . . . . 13

1) Magnetic Card Reader Check . . . . . . . . . . . . . . . . . 13

3-14. System Switch Diagnostics. . . . . . . . . . . . . . . . . . . . . . . 14

1) System Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3-15. Drawer Diagnostics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

1) Drawer 1 Check . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2) Drawer 2 Check . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3-16. Pole Display Diagnostics . . . . . . . . . . . . . . . . . . . . . . . . 14

3-17. IDE I/F & HARD DISK Diagnostics. . . . . . . . . . . . . . . . . 15

[READ MODE TEST] . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1) Drive Status display. . . . . . . . . . . . . . . . . . . . . . . . . 15

2) Sequential Seek Test. . . . . . . . . . . . . . . . . . . . . . . . 15

3) Random Seek Test . . . . . . . . . . . . . . . . . . . . . . . . . 16

4) Seek&Read Test . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

5) Target Sector Read Test . . . . . . . . . . . . . . . . . . . . . 16

6) HD Dump Test. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

7) Error lnformation Display . . . . . . . . . . . . . . . . . . . . . 17

8) Contoroller check Test. . . . . . . . . . . . . . . . . . . . . . . 18

[WRITE MODE TEST] . . . . . . . . . . . . . . . . . . . . . . . . . . 18

9) Seek&Write/Read-Verify Test . . . . . . . . . . . . . . . . . 18

10) Target Sector Write/Read-Verify Test . . . . . . . . . . . 19

11) HDPatch Test (Utility) . . . . . . . . . . . . . . . . . . . . . . . 19

12) Error Logging Area Clear. . . . . . . . . . . . . . . . . . . . . 19

13) Error table display . . . . . . . . . . . . . . . . . . . . . . . . . . 19

14) Other Supplemental Items. . . . . . . . . . . . . . . . . . . . 19

15) Error Content. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

16) Error Information Storing Area Description . . . . . . . 20

3-18. FAN & LCD ON/OFF Diagnostics. . . . . . . . . . . . . . . . . . 20

1) FAN & LCD ON/OFF Check . . . . . . . . . . . . . . . . . . 20

3-19. Power Hold Diagnostics . . . . . . . . . . . . . . . . . . . . . . . . . 20

1) Power Hold Check. . . . . . . . . . . . . . . . . . . . . . . . . . 20

Cautions:

The diagnostic program has been installed on the F-ROM disk when

it is shipped from the factory.

Application software is also installed on the F-ROM disk. Therefore,

the application software must be installed along with the diagnostic

program.

Starting up the diagnostic program with application software installed

(1) Executing the di agnostic program by starting up the BIOS-ROM

(MASK ROM)

1) Switch the system switch DSW-2 and DSW-3 as follows:

ON

123456

ON

OFF

DSW-3

Function OFF (value = 1) ON (value = 0)

Boot Drive Drive A: Drive C:

DSW-2

Function OFF (value = 1) ON (value = 0)

Drive A: Device Mask ROM FDD

(Set these switches to start-up from the BIOS-ROM (MASK

ROM).)

2) Connect the AT keyboard.

3) Turn the main power ON to start up the BIOS-ROM (MASK

ROM). Then, the incorporated system installer utility will start

up.

4) Press the "ESC" key of AT key, and then select the "EXIT"

from the menu display to end the system installer utility.

5) "C<" (DOS prompt) is displayed. Input "C<" to start up the

service diagnostic.

(2) Executing t he diagnostic program when start ing up an application

software

1) Connect the AT keyboard.

2) Turn the main power ON to press "F8" AT key, and then start

up the system without executing the content of "CONFIG.SYS"

and "AUTOEXEC.BAT".

3) "C<" (DOS prompt) is displayed. Input "C<" to start up the

service diagnostic.

4 – 1

Page 18

1. General

This diagnostic program is used to check the PWB’s, the process,

and the machine of UP-5700 series in a simplified manner.

This test program is supplied with floppy disks.

Parts code: UKOG-6731BHZZ

2. System configuration

The system requires the UP-5700 body, HDD or FDD, and the AT

keyboard for diagnostic operations.

3. Service diagnostics

3-1. Service diagnostics getting started

Getting start e d:

Execute "SRV.BAT" by entering the command with the AT key as

follows:

C > SRV ¿

"C >" is the DOS prompt. (when the diagnostic program is on C

drive.)

Do not use other device drivers when using this program.

To operate other applications after performing this program, restart

the machine.

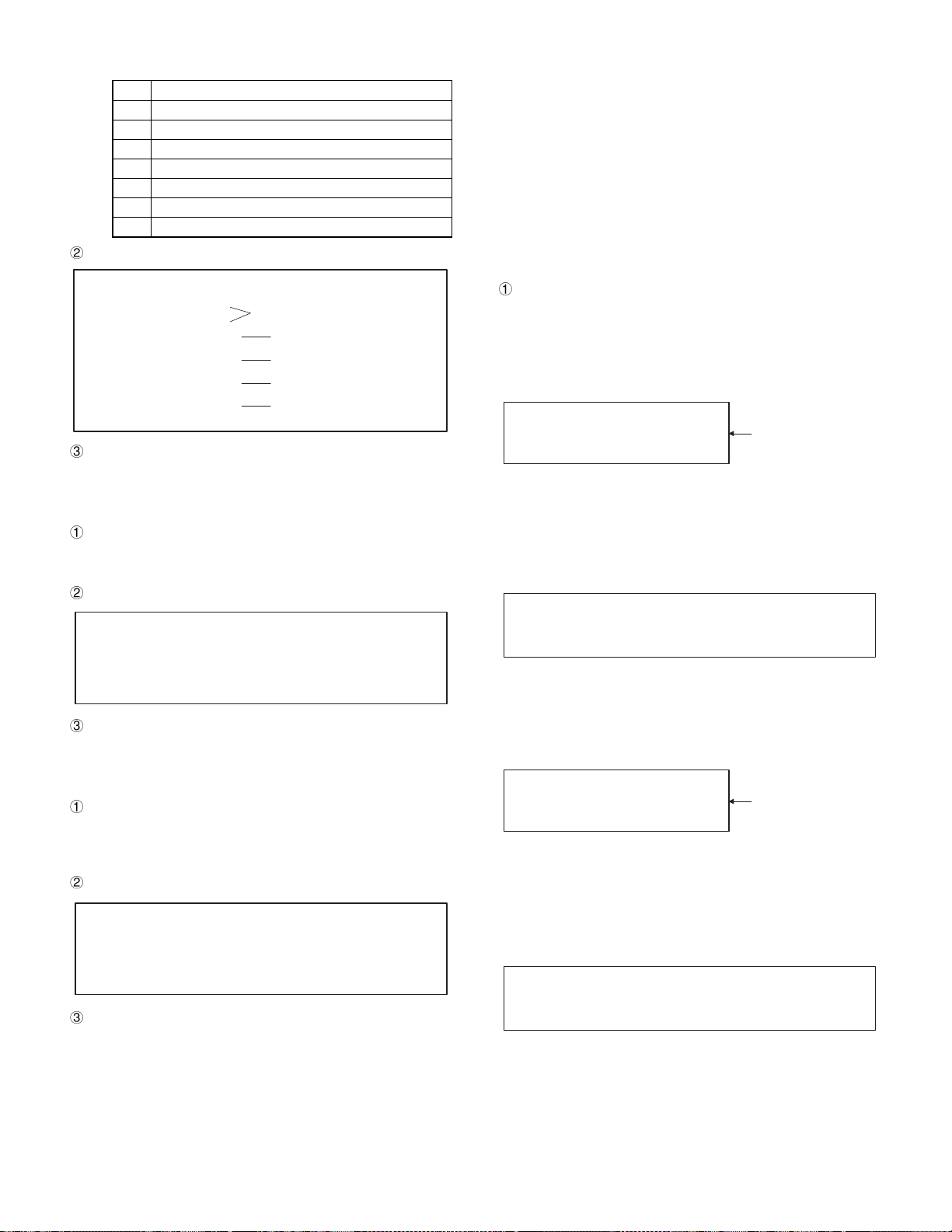

3-2. Selection menu

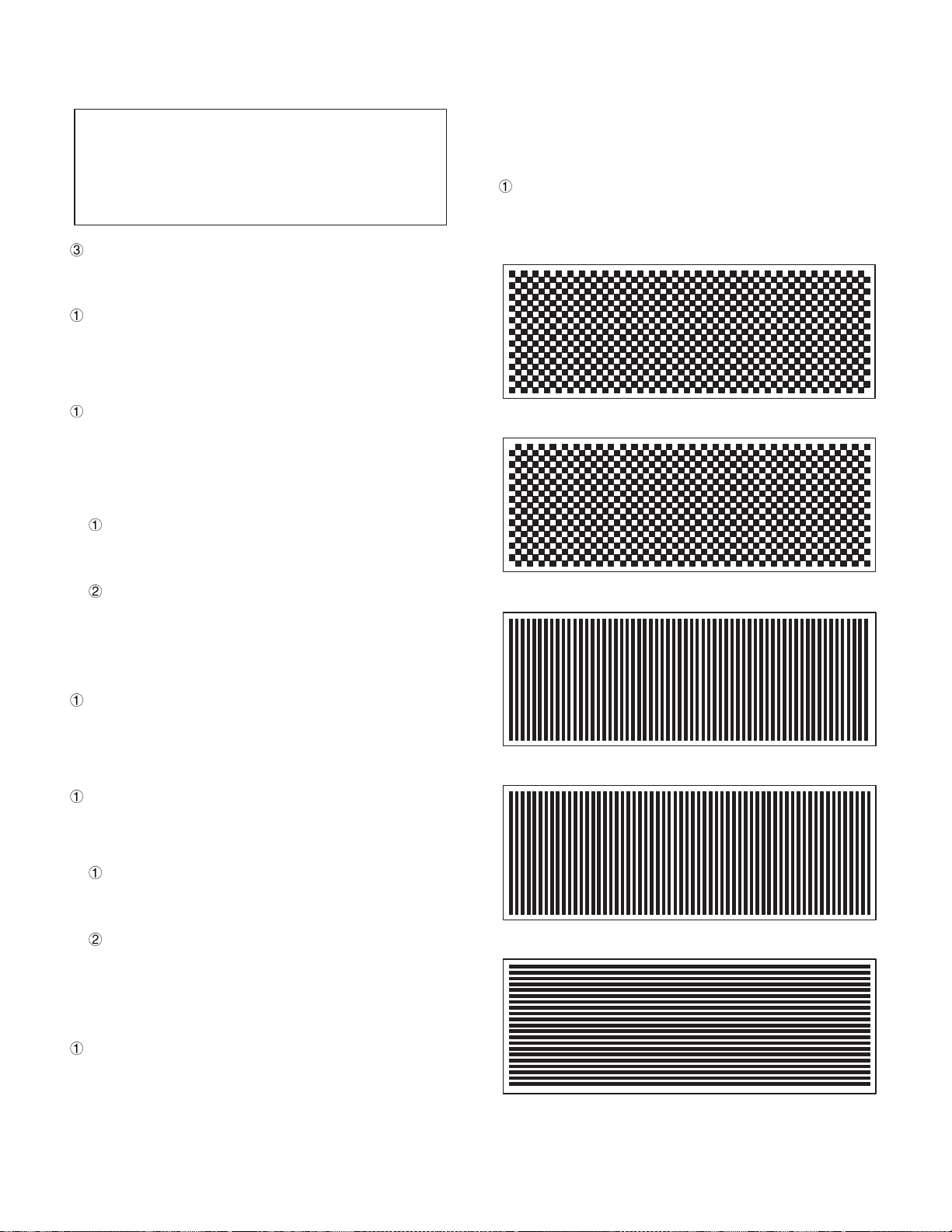

The diagnostics menu is started and the following menu is displayed.

The highlighted cursor is moved by the cursor keys (UP and DOWN

¯) of the AT keyboard. Move the cursor to the desired item, and press

Enter key to execute the selected diagnostics program. When the

selected diagnostics program is completed, the display returns to the

menu screen. Select "Diagnostics End" and press Enter key to terminate the diagnostics.

UP-5700 Service-man Diagnostics

RAM Diagnostics

ROM Diagnostics

Real time clock & CMOS RAM Diagnostics

Touch Panel Diagnostics

Clerk Key Diagnostics

Printer Diagnostics

Serial I/O Diagnostics

LCD (Liquid Crystal Display) Diagnostics

Rear Display Diagnostics

SRN (SHARP Retail Network) Diagnostics

MCR (Magnetic Card Reader) Diagnostics

System Switch Diagnostics

Drawer Diagnostics

Pole Display Diagnostics

IDE I/F & Controller Diagnostics

FAN&LCD ON/OFF Diagnostics

Power Hold Diagnostics

Diagnostics End

Version 1.00d

3-3. RAM Diagnostics

This program is used to test the standard memory, the extension

memory, and the RAM disk.

When this program is selected, the following menu is displayed.

The highlighted cursor is moved by the cursor keys (UP and DOWN

¯) of the AT keyboard. Move the cursor to the desired item, and press

Enter key to execute the selected diagnostics program.

When the selected diagnostics program is completed, the display

returns to the menu screen. Pressing Esc key returns to the service

diagnostics menu.

RAM Diagnostics

D-RAM Check

Standard RAM Disk Check

Option RAM Disk Check

1) D-RAM Check

Check content

All memory areas are checked in the unit of 64KB. The check

procedures are as follows:

i. Test data 5555H is written to all the test areas.

ii. Test data and read data are compared for each word, If it is

O.K., test data AAAAH is written to the test area.

iii. Test data and read data are compared for each word, If it is

O.K., test data 5555H is written to the test area.

iv. Test data 0000H is written to all the test areas.

v. Test data and read data are compared for each word, If it is

O.K., test data FFFFH is written to the test area.

vi. Test data and read data are compared for each word, If it is

O.K., test data 0000H is written to the test area.

When an error occurs during the test, the error address and data

are displayed and the test is stopped.

For the extension memory test, the value set in the setup are read

and test is made to the area in the increment of 64KB.

Display

D-RAM Check

Main memory size : 640KB PASS !!(or ERROR !!)

Extended memory size : xxxxKB PASS !!(or ERROR !!)

Error Address xxxxxxH Write Data xxxxH Read Data xxxxH

As the extension memory size, the value set in the setup is displayed. The error address and the error data are displayed only

when an error occurs. (When no error occurs, they are not displayed.)

Terminating method

After completion of the test, press Esc key to terminate the test.

4 – 2

Page 19

2) Standard RAM Disk Check

Check content

For the standard RAM disk area (BANK 000H ~ 03FH), each test

area of bank size 16KB is checked. The bank base address of

RAM is set to 0D4000H and after. The check procedures are as

follows:

i. Write different data to the following address with Word. After

completion of writing, BANK 03FH 0D4000H data read verify

check is made. (Data in the written area are saved in the main

memory.) If it is OK, the following t est is executed. In case of

an error, the error display is made and the test is terminated.

Write address Write data

BANK BFH (extension) 0D4000H BF40H

BANK 7FH (extension) 0D4000H 7F80H

BANK 3FH (standard) 0D4000H 3FC0H

ii. The test area data is saved to the main memory.

iii. Test data 5555H is written to all the test areas.

iv. Test data and read data are compared for each word, If i t is

O.K., test data AAAAH is written to the te st area.

v. Test data and read data are compared for each word, If it is

O.K., test data 5555H is written to the test area.

vi. Test data 0000H is written to all the test areas.

vii. Test data and read data are compared for each word, If it is

O.K., test data FFFFH is written to the test area.

viii. Test data and read data are compared for each word, I f it is

O.K., test data 0000H are written to the test area.

ix. The saved data are written to the test areas.

When an error occurs during the test, the error address and dat a

are displayed and the test is stopped.

Display

Standard RAM Disk Check

Standard RAM Disk size : 1024KB PASS !!(or ERROR !!)

Error Address xxxxxxH Write Data xxxxH Read Data xxxxH

v. Test data 5555H is written to the test area.

vi. Test data and read data are compared. If is OK, test data

AAAAH is written to the test area.

vii. Test data and read data are compared for each word, If it is

O.K., test data 5555H is written to the test area.

viii. Test data and read data are compared for each word, If it is

O.K., test data 0000H is written to all the test areas.

ix. Test data and read data are compared for each word. If it is

OK, test data FFFFH is written to the test area.

x. Test data and read data are compared for each word. If it is

OK, test data 0000H is written to the test area.

xi. The saved data is written to the test areas.

When an error occurs during the test, the error address and data

are displayed and the test is stopped.

Display

Option RAM disk Check

Extended RAM Disk size : 1024KB PASS !!(or ERROR !!)

Error Address xxxxxxH Write Data xxxxH Read Data xxxxH

The error address and the error data are displayed only when an

error occurs. (If no error occurs, they are not displayed.)

Terminating method

After the test result is displayed, press Esc key to terminate the

test.

3-4. ROM Diagnostics

DOS ROM, BIOS ROM, standard flash ROM, and option flash ROM

are tested.

The following menu is displayed. The highlighted cursor is moved by

the cursor keys (UP and DOWN ¯) of the AT keyboard. Move the

cursor to the desired item, and press Enter key to execute the selected diagnostics program. When the selected diagnostics program

is completed, the display returns to the menu screen. Pressing Esc

key returns to the service diagnostics menu.

The error address and the error data are displayed only when an

error occurs. (If no error occurs, they are not displayed.)

Terminating method

After the test result is di splayed, press Esc key to terminate the

test.

3) OPTION RAM Disk Check

Check content

For the standard RAM disk area (BANK 040H ~ BANK 0BFH),

each test area of bank size 16KB is checked. The bank base

address of RAM is set to 0D4000H and after. The check procedures are as follows:

i. Write different data to each address with Word similarly to the

Standard RAM Disk Check. After completion of writing, BANK

0BFH 0D4000H data read verify check is made. (Data in the

written area are saved in the main memory.) If it is OK, the

following test is executed. In case of an error, the error display is made and the test is terminated.

ii. Test data 55AAH is written to BANK 040H 0D4000H.

iii. BANK 040H 0D4000H is read and compared with 55AAH. If

both data are correct, the following test is executed. If not,

"Extended RAM Disk size: 0KB" is displayed and the test is

terminated.

iv. The test area data is saved to the main memory.

ROM Diagnostics

DOS ROM Check

BIOS ROM Check

Standard FLASH ROM Check

Option FLASH ROM Check

1) DOS ROM Check

Check content

Sum check is made for DOS ROM (BANK 000H ~ 0FFH). All data

bytes are added. If the check sum is 10H, it is normal.

The ROM version is displayed.

Display

DOS ROM Check

Sum Check : PASS !!(or ERROR !!)

ROM Version : VHILH****

The version is displayed.

Terminating method

After the test result is displayed, press Esc key to terminate,

4 – 3

Page 20

2) BIOS ROM Check

Check content

The BIOS ROM version is displayed.

Display

BIOS ROM Check

Version - ROM : SHUP****

The version is displayed.

Terminating method

After the test result is displayed, press Esc key to terminate,

3) Standard FLASH ROM Check

Check content

Write and read are performed for the standard FLASH ROM area

(BANK 200H ~ 27FH) to make verify check. The check procedures are as follows:

· The ID code, the manufacture, and the device signature code

are read and displayed.

· The ROM size is specified and the following display is made to

allow the user to select whether to perform verify check or not.

Terminating method

After the test result is displayed, press Esc key to terminate,

4) Option FLASH ROM Check

Check content

Write read verify check or read check is performed for the option

FLASH ROM area (BANK 280H – 3FFH). The check procedures

are as follows:

· The ID code, the manufacture, and the device signature code

are read in BANK 280H ~ 2FFH, BANK 300H ~ 37FH, and

BANK 380H ~ 3FFH to check that the proper value is read or

not.

· If the proper value is read, the ROM size is specified and the

following display is made to allow the user to select whether to

perform verify check or not.

Option Flash ROM Check

Option Flash ROM Size : 4096KB

Write Read Verify chek YESNO<- CAUTION!!

Device ID = **** Manu facture ID = ****

All filesin Option Flash ROM Disk will be destroyed.

Are you sure?

If the proper value is not read, the following display is made. (Esc

key)

Changed depending on the capacity.

<-(Read Only)

The cursor is on this side

(Default).

Standard Flash ROM Check

Standard Flash ROM Size : 2048KB

Write Read Verify chek YES

Device ID = **** Manu facture ID = ****

All filesin Standard Flash ROM Disk will be destroyed.

Are you sure?

NO

<- CAUTION!!

The cursor is on this side

(Default).

If the proper value is not read, the f ollowing display is made. (Esc

key)

Standard Flash ROM Check

ERROR!

Device is not installed or not work properly.

· Move cursor to select "YES", and the message in ( ) will be

displayed.

· If the verify check is made, the test area is first erased.

· Increment data for each byte is written to all the test areas.

· (Example: "0001h", "0202h", "0405h", --- "0E0Fh", --- "FEFFh"

The two left digits are the lower address, and t he two right

address are the upper address.)

· Read verify check is performed.

Final display

Standard Flash ROM Check

Standrd Flash ROM Size : 2048KB

Write Read Verify chek : PASS!! (or ERROR!!)

ERROR ADDRESS BANK XXXH,XXXXXXH WRITE DATA XXXXH READ DATA XXXXH

Device ID = **** Manu facture ID = ****

Option Flash ROM Check

ERROR!

Device is not installed or not work properly.

When "YES" is selected

· Move cursor to select "YES", and the message in ( ) will be

displayed.

· If the verify check is made, the test area is first erased.

· Increment data for each byte is written to all the test areas.

· (Example: "0001h", "0203h", "0405h", ××× "0E0Fh", ××× "FEFFh"

The two left digits are the lower address, and the two right

address are the upper address.)

· Read verify check is performed.

When "NO" is selected

· When "NO" is selected, read check is performed for the above

increment data. Therefore, the option FLASH ROM to be tested

must be passed by write read verify check once.

Final display

Option Flash ROM Check

Option Flash ROM Size : 2048KB

Write Read Verify chek : PASS!! (or ERROR!!)

ERROR ADDRESS BANK XXXH,XXXXXXH WRITE DATA XXXXH READ DATA XXXXH

Device ID = **** Manu facture ID = ****

Terminating method

After the test result is displayed, press Esc key to terminate.

4 – 4

Page 21

3-5. Real time clock & CMOS RAM Diagnostics

RTC and CMOS RAM check is performed.

The following menu is displayed. The highlighted cursor is moved by

the cursor keys (UP and DOWN ¯) of the AT keyboard. Move the

cursor to the desired item, and press Enter key to execute the selected diagnostics program. When the selected diagnostics program

is completed, the display returns to t he menu screen. Pressing Esc

key returns to the service diagnostics menu.

Real time clock & CMOS RAM Diagnostics

Real time clock Check

CMOS RAM Check

1) Real time clock Check

Check content

RTC timer function and RTC clock function are tested.

In RTC timer check, the RTC timer is set so that an interrupt is

generated after 2 sec and check that the interrupt is performed

properly. In RTC clock check, the RTC clock is set to 23:59;58,

31/Dec/1989, and check that the clock shows 0:0:0, 1/Jan/ 1990

after 2 sec.

Display

Real time clock Check

RTC Timer Check : PASS !!(or ERROR !!)

RTC Clock Check : PASS !!(or ERROR !!)

Terminating method

After the test result is displayed, press Esc key to terminate,

2) CMOS RAM Check

Check content

Read/write check is performed for CMOS-RAM when setting up.

The check procedures are as follows:

i. Test address data is saved to the main memory.

ii. Test data 55H is written to the test address.

iii. Test data and read data are compared, and test data AAH is

written to the test address.

iv. Test data and read data are compared.

v. The saved test data is written to the test area.

vi. The address is incremented until it becomes 3FH.

If POFF interruption is generated during the test, the test is

stopped and the saved data is written to the test area within 50ms.

Display

The error address and the error bit are displayed only when an

error occurs. (When no error occurs, they are not displayed.)

Terminating method

After the test result is displayed, press Esc key to terminate.

3-6. Touch Panel Diagnostics

The touch panel and its controller are checked. Communication with

the controller is performed by 8250 built in the gate array PSC2.

The controller diag check, the touch keypad test, and the linearity test

are performed.

The initial disp la y is as fo ll o w s :

Touch Panel Diagnostics

Controller Diag Test

Touch Key Pad Test

Line arity

1) Controller Diag Test

Check content

After initializing the controller, the diag command is executed. The

procedures are as follows:

· One byte of dummy data (FFh) is sent and waiting of 100ms is

made.

· The reset command (80h) is sent and waiting for the end code

(2 bytes: 90h and 00h) from the controller is made.

· The diag command (2 bytes: 89h, any one-byte data) is exe-

cuted, and waiting for the end code (3 bytes: 90h, return code,

any one-byte data) is made.

· The error display is made with the return code.

To exit from the controller diag test. press Esc key during waiting for the end code response.

Return code Content

0Ah ROM error

0Bh RAM error

0Ch Panel voltage error

0Dh Reserve

0Eh E

0Fh E

10h E

Display

Controller Diag Test

Pass!!

ROM Error!!

or

RAM Error!!

PANEL Voltage Error!!

2

E PROM Write Error!!

2

E PROM Read Error!!

2

E PROM SUM Error!!

2

PROM write error

2

PROM read error

2

PROM check sum error

Error!!

Error!!

CMOS-RAM Check

RTC RAM Check : PASS !!(or ERROR !!)

Error Address xxxxxH Write Data xxH Read Data xxH

Terminating method

After the test result is displayed, press Esc key to terminate,

4 – 5

Page 22

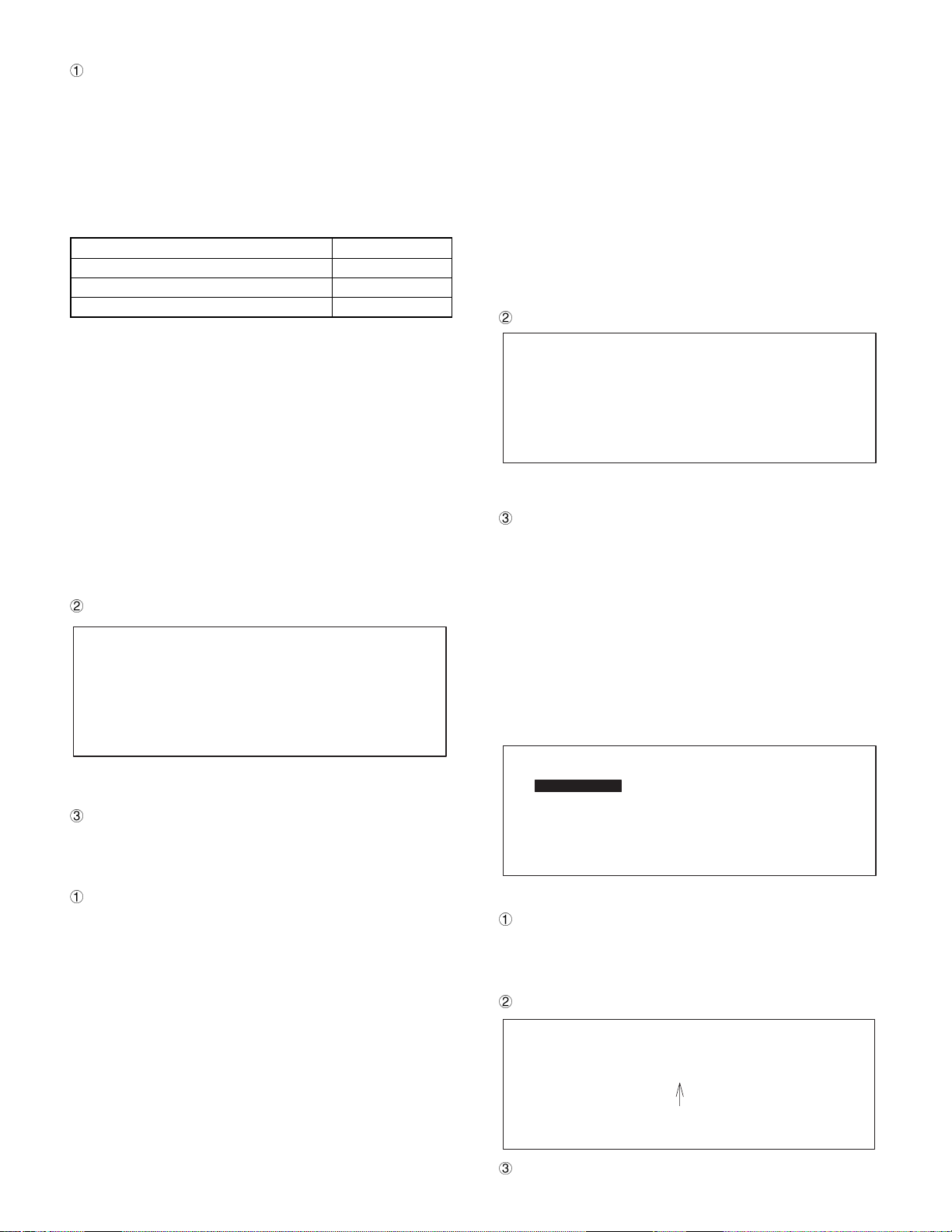

2) Touch Key Pad Test

Check content

The driver function call is used.

is displayed at the four corners of the LCD sequentially.

(In the sequence of upper right, upper left, lower left, lower right.)

When

is touched by the operator, it turns to .

Display

3-7. Clerk Key Diagnostics

The clerk key input test is performed.

Pressing Esc key returns to the serviceman diagnostics menu.

1) Clerk Key Check

Check content

Key code inserted to the clerk key switch is displayed in decimal.

Display

Touch Key Pad Test

Touch Cursor !!

Terminating method

Touch all the four

or press Esc key to terminate.

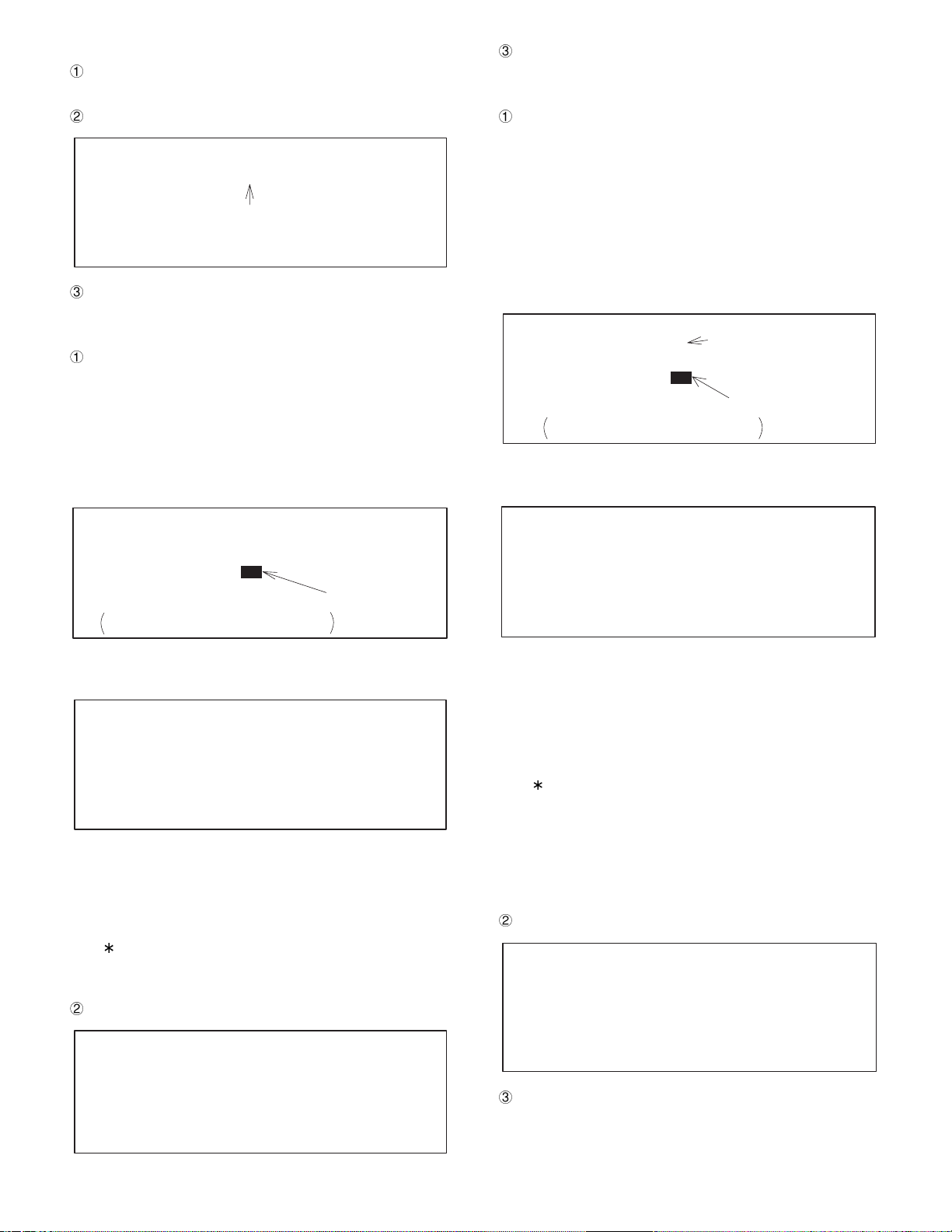

3) Linearity test

Check content

Red lines are displayed at the both sides of the blue line at the

center. The operator must touch the blue l ine without t ouching the

red lines.

The touched part of the blue line is changed to white.

If the red line is touched, an error message is issued.

Display

About 2cm

Linearity

Test

Complete!

(Error!!)

Displayed after termination.

About 1cm

Clerk Key Check

Clerk Key Code : xx

The clerk code is displayed at XX.

Terminating method.

Press Esc key to terminate.

3-8. Printer Diagnostics

Parallel interface (standard) and ER-A8RS parallel interface (option)

are tested.

Here, parallel interface on the main body is mentioned as PARALLEL1, and parallel interface on ER-A8RS as PARALLEL 2/3.

The following menu is displayed.

The highlighted cursor is moved by the cursor keys (UP and DOWN

¯) of the AT keyboard. Move the cursor to the desired item, and press

Enter key to execute the selected diagnostics program.

When the selected diagnostics program is completed, the display

returns to the menu screen. Pressing Esc key returns to the serviceman diagnostics menu.

Printer Diagnostics

Standard Option(ER-A8RS)

Red line

Terminating method

Press Esc key to terminate,

Blue line

Red line

PARALLEL 1 Loop Check

PARALLEL 1 Print Check

PARALLEL2 Loop Check

PARALLEL3 Loop Check

PARALLEL2 Print Check

PARALLEL3 Print Check

1) PARALLEL1 Loop Check

Check content

Loop check is made for the standard I/O address 378H ~ 37FH.

(PARALLEL1)

In the loop check, a normally-operating ER-A8RS is inserted and

the loop cable (UKOG-6717RCZZ) of the following wiring diagram

is connected with PARALLEL1 and PARALLEL3 (ER-A8RS) for

testing. Set the jumper on the PWB during test as follows:

4 – 6

Page 23

Signal name

STROBE-

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

ACKBUSY

PE

SLCT

AUTOFD-

ERROR-

INIT-

SLCTIN-

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18~2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18~2

Loop cable (UKOG-6717RCZZ) wiring diagram

Signal namePin No.

STROBE-

ACKBUSY

SLCT

AUTOFD-

ERROR-

INIT-

SLCTIN-

GND

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

PE

2) PARALLEL2 Loop Check

Check content

The loop check is performed for ER-A8RS I/O address 278H ~

27FH (PARALLEL2), In the loop check, the loop cable shown in

Fig, 3-4 is connected with PARALLEL2 (ER-A8RS) and PARALLEL1 for testing. Set the jumper on the PWB during the test as

shown in Fig. 3-6.

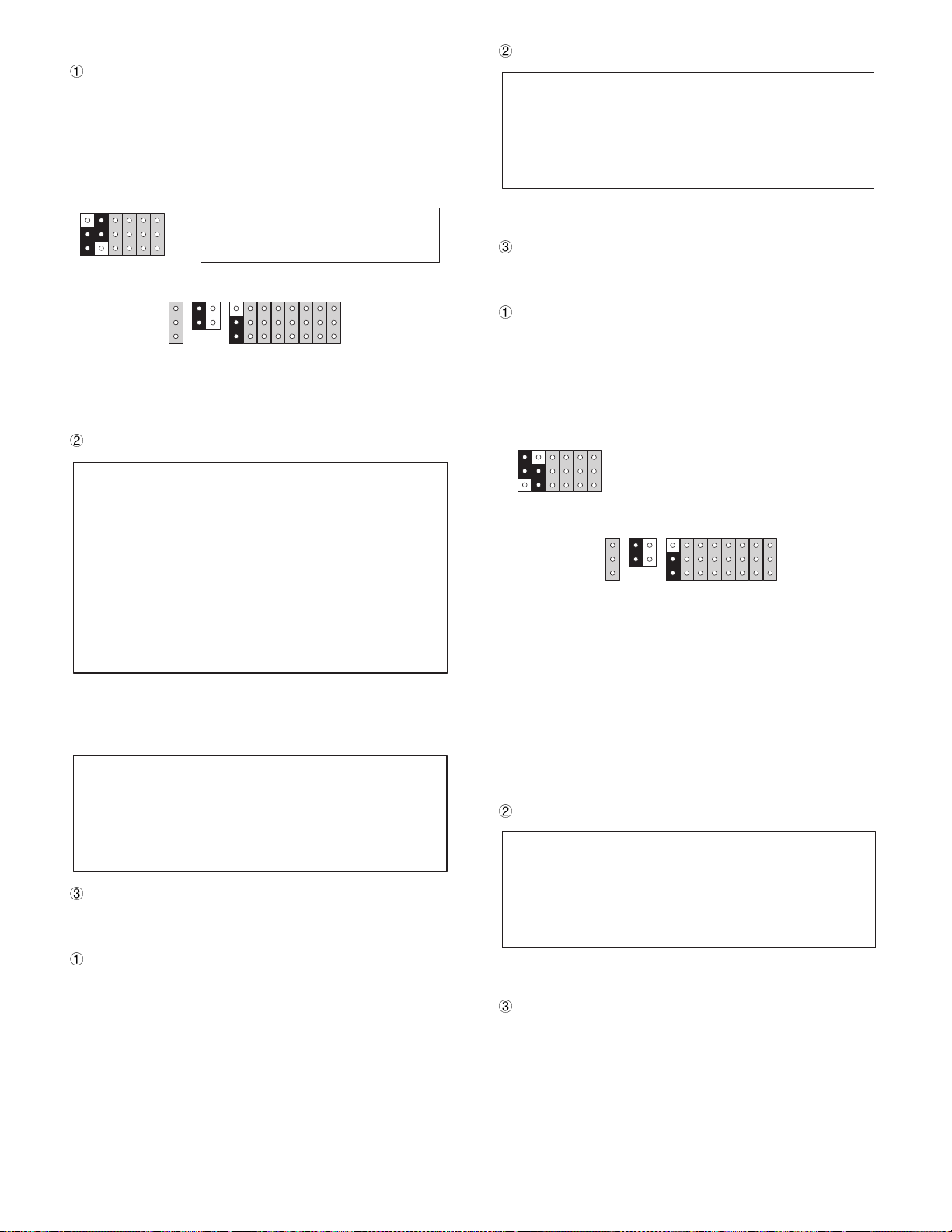

J3J8J4J5J6

J7

10

UP-5700 : PARALLEL1 INPUT MODE

A8RS : PARALEL2 OUTPUT MODE

J9

L

H

J10

57

I

12

O

J18

J11

J12

J13

J14

J15

J16

J17

J3J8J4J5J6

J7

10

UP-5700 : PARALLEL1 OUTPUT MODE

A8RS : PARALLEL3 INPUT MODE

J9

J10

I

L

H

57

O

J18

J11

Opposite ER-A8RS setting

Jumper pin setting diagram

Display

PARALLEL1 Loop Check

ACK- Signal : PASS !!(or ERROR !!)

BUSY Signal : PASS !!(or ERROR !!)

PE Signal : PASS !!(or ERROR !!)

SLCT Signal : PASS !!(or ERROR !!)

ERROR- Signal : PASS !!(or ERROR !!)

STROBE- Signal : PASS !!(or ERROR !!)

AUTOFD- Signal : PASS !!(or ERROR !!)

INIT- Signal : PASS !!(or ERROR !!)

SLCTIN- Signal : PASS !!(or ERROR !!)

INTERRUPT : IRQ X (or ERROR !!)

DATA Bus : PASS !!(or ERROR !!)

J12

J13

J14

J15

J16

J17

Setting of ER-A8RS to be tested

Fig. 3-6 Jumper pin setting

Display

PARALLEL2 Loop Check

12

ACK- Signal : PASS !!(or ERROR !!)

BUSY Signal : PASS !!(or ERROR !!)

PE Signal : PASS !!(or ERROR !!)

SLCT Signal : PASS !!(or ERROR !!)

ERROR- Signal : PASS !!(or ERROR !!)

STROBE- Signal : PASS !!(or ERROR !!)

AUTOFD- Signal : PASS !!(or ERROR !!)

INIT- Signal : PASS !!(or ERROR !!)

SLCTIN- Signal : PASS !!(or ERROR !!)

INTERRUPT : IRQ X (or ERROR !!)

DATA Bus : PASS !!(or ERROR !!)

The interruption level is displayed at XX.

If no access is allowed to PARALLEL2, the following display is

made.

PARALLEL2 Loop Check

PARALLEL2 Channel Disabled

The interruption level is displayed at X.

When no access is allowed to PARALLEL1, the following display

is made.

PARALLEL1 Loop Check

PARALLEL1 Channel Disabled

Terminating method.

Press Esc key to terminate.

Terminating method.

Press Esc key to terminate.

4 – 7

Page 24

3) PARALLEL3 Loop Check

Check content

The loop check is performed for ER-A8RS I/O address 3BCH ~

3BEH (PARALLEL3), In the loop check, the ER-A8RS to be connected is connected to the extension slot and the loop cable

shown in Fig. 3-4 is connected with PARALLEL3 (ER-A8RS) and

PARALLEL1 for testing. Set the jumper on the PWB during the

test as shown in Fig. 3-6.

Display

PARALLEL1 Print Check

PARALLEL1 Channel Disabled

J3J8J4J5J6

J7

10

UP-5700 : PARALLEL1 OUTPUT MODE

A8RS : PARALEL3 INPUT MODE

J10

J9

L

H

57

I

12

O

J18

J11

J12

J13

J14

J15

J16

J17

Setting of ER-A8RS to be tested

Fig. 3-6 Jumper pin setting

Display

PARALLEL3 Loop Check

ACK- Signal : PASS !!(or ERROR !!)

BUSY Signal : PASS !!(or ERROR !!)

PE Signal : PASS !!(or ERROR !!)

SLCT Signal : PASS !!(or ERROR !!)

ERROR- Signal : PASS !!(or ERROR !!)

STROBE- Signal : PASS !!(or ERROR !!)

AUTOFD- Signal : PASS !!(or ERROR !!)

INIT- Signal : PASS !!(or ERROR !!)

SLCTIN- Signal : PASS !!(or ERROR !!)

INTERRUPT : IRQ X (or ERROR !!)

DATA Bus : PASS !!(or ERROR !!)

The interruption level is displayed at XX.

If no access is allowed to PARALLEL3, the following display is

made.

PARALLEL3 Loop Check

PARALLEL3 Channel Disabled

"PARALLEL1 Channel Disabled" is displayed only when no access to PARALLEL1 is allowed.

Terminating method.

Press Esc key to terminate.

5) PARALLEL2 Print Check

Check content

The print check is performed for PARALLEL2 at I/O address 278H

~ 27Fh on the ER-A8RS.

In the print check, set the short pin of the ER-A8RS to be tested

as shown in Fig. 3-9, and connect D-Sub 25 pin connector to the

printer to allow to print for test.

J3J8J4J5J6

The test procedures are as follows:

i. Data of 55H is written to I/O address 278H, and the same

ii. Characters of 20H ~ 7FH (ASCII code) are printed and the

Display

J7

10

J10

J9

L

H

57

I

12

O

J18

J11

J12

J13

J14

J15

J16

J17

Fig. 3-9 Jumper pin setting

address is read. If the read data is not 55H, "PARALLEL2

Channel Disabled" is displayed and the following check is not

performed.

line is changed.

This procedure is repeated for 5 times.

Terminating method.

Press Esc key to terminate.

4) PARALLEL1 Print Check

Check content

The print check is performed for the standard port PARALLEL1 at

I/O address 378H ~ 37FH. In the print check, D-Sub 25 pin connector is connected with the printer to allow to print for test.

The test procedures are as follows:

i. Data of 55H is written to I/O address 378H, and the same

address is read. If the read data is not 55H, "PARALLEL1

Channel Disabled" is displayed and the following check i s not

performed.

ii. Characters of 20H ~ 7FH (ASCII code) are printed and the

line is changed.

This procedure is repeated for 5 times.

PARALLLEL2 Print Check

PARALLEL2 Channel Disabled

"PARALLEL2 Channel Disabled" is displayed only when no access to PARALLEL2 is allowed.

Terminating method.

Press Esc key to terminate.

4 – 8

Page 25

6) PARALLEL3 Print Check

Check content

The print check is performed for PARALLEL3 at I/O address

3BCH ~ 3BEh on the ER-A8RS.

In the print check, set the short pin of the ER-A8RS to be tested

as shown in Fig. 3-10, and connect D-Sub 25 pin connector to the

printer to allow to print for test.

J3J8J4J5J6

The test procedures are as follows:

i. Data of 55H is written to I/O address 3BCH, and the same

ii. Characters of 20H ~ 7FH (ASCII code) are printed and the

Display

J7

10

J10

J9

L

H

57

I

12

O

J18

J11

J12

J13

J14

J15

J16

J17

Fig. 3-10 Jumper pin setting

address is read. If the read data is not 55H, "PARALLEL3

Channel Disabled" is displayed and the following check i s not

performed.

line is changed.

This procedure is repeated for 5 times.

RTS

1pin

DTR

2pin

TD

3pin

GND

4pin

GND

5pin

RD

6pin

DSR

7pin

CTS

8pin

Loop back connector (UKOG-6729BHZZ) wiring diagram

The UP-5700’s 9-pin D-sub ports are used as COM1 and 2. In addition, the UP-5700’s RJ45 ports are used as COM3 and 4 or COM5

and 6 according to the setup. On the other hand, ER-A8RS is used

by selecting either COM1 and 2 or COM3 and 4 according to the

setup.

Therefore, when an ER-A8RS is used, you must set COM1, 2, 5, and

6 on the UP-5700 side, and set COM3 and 4 on the ER-A8RS side.

The following menu is displayed.

The highlighted cursor is moved by the cursor keys (UP and DOWN

¯) of the AT keyboard. Move the cursor to the desired item, and press

Enter key to execute the selected diagnostics program.

When the selected diagnostics program is completed, the display

returns to the menu screen. Pressing Esc key returns to the serviceman diagnostics menu.

Serial I/O Diagnostics

COM1 Check

COM2 Check

COM3 Check

COM4 Check

COM5 Check

COM6 Check

PARALLEL3 Print Check

PARALLEL3 Channel Disabled

"PARALLEL3 Channel Disabled" is displayed only when no access to PARALLEL3 is allowed.

Terminating method.

Press Esc key to terminate.

3-9. Serial I/O Diagnostics

The serial interface of UP-5700 and the option PWB ER-A8RS is

performed. To test the 9pin D-Sub port, connect the D-Sub loop back

connector (UKOG-6705RCZZ).

To test the RJ45 port, connect the loop back connector (UKOG6729BHZZ).

CD 1pin

RD 2pin

TD 3pin

DTR 4pin

GND 5pin

DSR 6pin

RTS 7pin

CTS 8pin

RI 9pin

Loop back connector (UKOG-6705RCZZ) wiring diagram

1) COM1 Check

Content

The loop back check is performed for UART at I/O address 3F8H

~ 3FFH. The test procedures are as follows:

i. UART setting is made. If access is denied to UART at that

time, "COM1 Disabled" is displayed and the following check is

not performed.

ii. RTS signal is turned on/off t o check that CD, CTS signal is

normally operating. In case of any abnormality, ERROR is

displayed.

iii. DTR signal is turned on/off to check that DSR, RI signal is

normally operating. In case of any error, ERROR is displayed.

When an error occurs in procedure i or ii, the following test is

not performed.

iv. Set the baud rate to 19200bps asynchronous. 256 byte data

of 00H ~ FFH is transmitted from SD signal. Data received at

RD signal is compared to check that the both are the same. If

the outputted data is not returned for 5 sec or more, ERROR

is displayed and the test is terminated.

v. An interruption signal is issued f rom UART and the number of

generated interruption request signal is displayed.

Display

Serial I/O COM1 Check

RTS - CD : PASS !!(or ERROR !!)

RTS - CTS : PASS !!(or ERROR !!)

DTR - DSR : PASS !!(or ERROR !!)

DTR - RI : PASS !!(or ERROR !!)

TD - RD : PASS !!(or ERROR !!)

INTERRUPT : IRQ XX

4 – 9

Page 26

The number of the interruption request signal is displayed at XX.

If no access is allowed to COM1 UART, the following display is

made.

Serial I/O COM1 Check

COM1 Channel Disabled

Terminating method.

Press Esc key to terminate.

2) COM2 Check

Check content

The loop back check is performed for UART at I/ O address 2F8H

~ 2FFH. The check procedure, the display, and the terminating

method are the same as COM1 Check.

3) COM3 Check

Check content

The loop back check is performed for UART at I/ O address 3E8H.

When the ER-A8RS is assigned to COM3, the check procedure,

display and terminating method are the same as COM1.

When the RJ-45 port of the UP-5700 main unit is assigned to

COM3, the following points are different from COM1 Check :

Content

· RTS-CTS is not checked.

· DTR-RI is not checked.

Display

· RTS-CTS is not displayed.

· DTR-RI is not displayed.

COM3 is checked as well as COM1 except the above 2 points.

4) COM4 Check

Check content

The loop back check is performed for UART at I/O address 2E8H

~ 2EFH. The check procedure, the display, and the terminating

method are the same as COM3 Check.

5) COM5 Check

Check content

The loop back check is performed for UART at I/O address (PSC2

base address) + (410H ~ 417H). The following points are different

from COM1 Check:

Content

· RTS-CTS is not checked.

· DTR-RI is not checked.

Display

· RTS-CTS is not displayed.

· DTR-RI is not displayed.

COM5 is checked as well as COM1 except the above 2 points.

6) COM6 Check

Check content

The loop back check is performed for UART at I/O address (PSC2

base address) + (418H ~ 41FH). The check procedure, the display, and the terminating method are the same as COM5 Check.

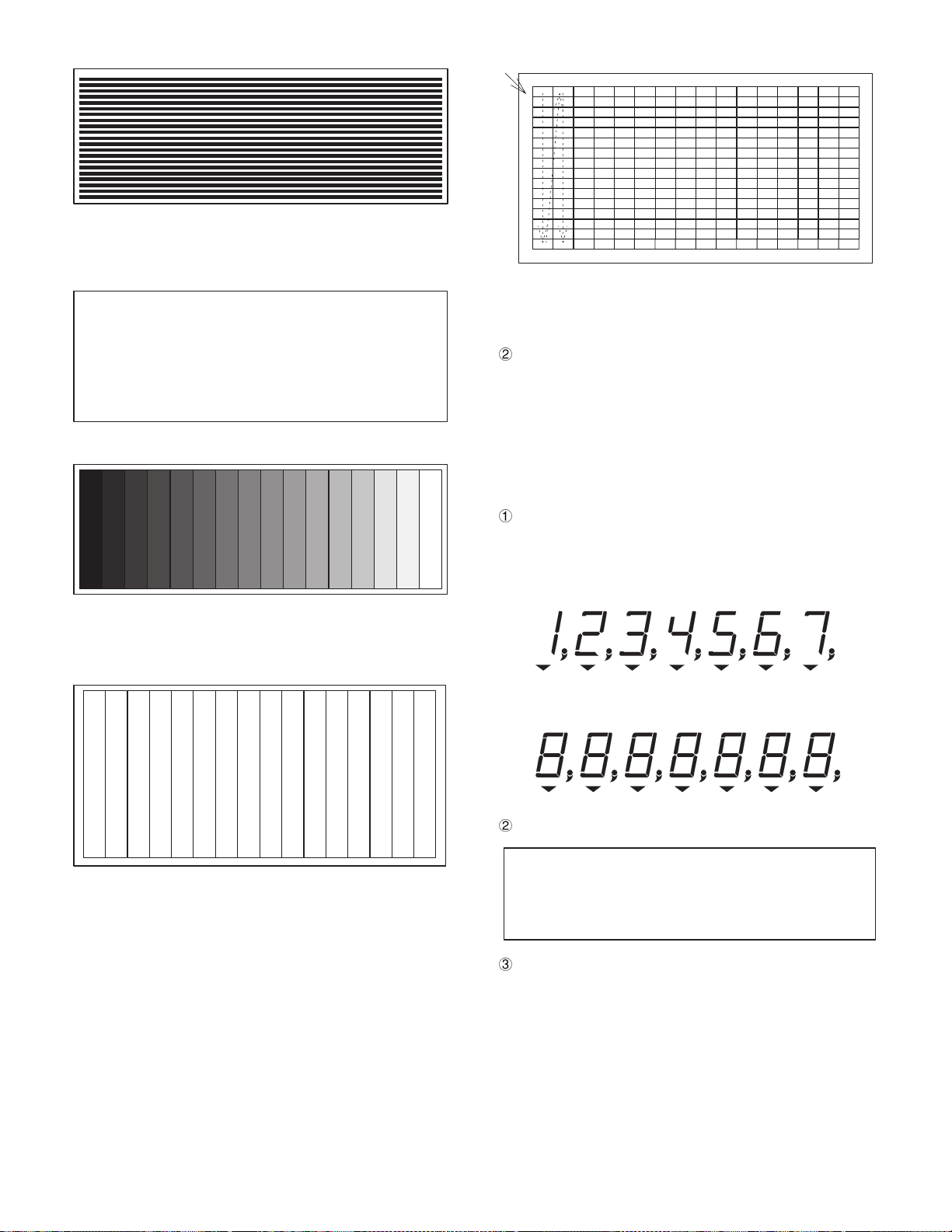

3-10. Liquid Crystal Display Diagnostics

LCD test is performed.

The following patterns are displayed in sequence. Pressing the space

bar proceeds the display. Pressing the space bar at the final pattern

or pressing Esc key during the test, the display returns to the service

diagnostics menu.

1) Liquid Crystal Display Check

Check content

The test patterns are displayed in the following test procedures.

Pressing the space bar moves to the next pattern.

i. Black-and-white pattern in 1 dot interval

ii. Reversed pattern of pattern i.

iii. Vertical stripe pattern in 1 dot interval

iv. Reversed pattern of pattern iii.

v. Horizontal stripe pattern in 1 dot interval

4 – 10

Page 27

vi. Reversed pattern of pattern v.

vii. "H" pattern (80 digits ´ 35 lines) In the 35th line, only 78 digits

of "H" are displayed.

(The actual display range is 25 lines. Scroll for 10 lines to

check.)

HHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHH

viii. Gradation pattern from black to white in 16 gradations

Arrange RAMDAC register No. 0 ~ 255 from the upper left.

xii. Backlight OFF

The backlight is turned off without turning off the display.

xiii. Backlight ON

Terminating method

Press the space bar or Esc key to terminate.

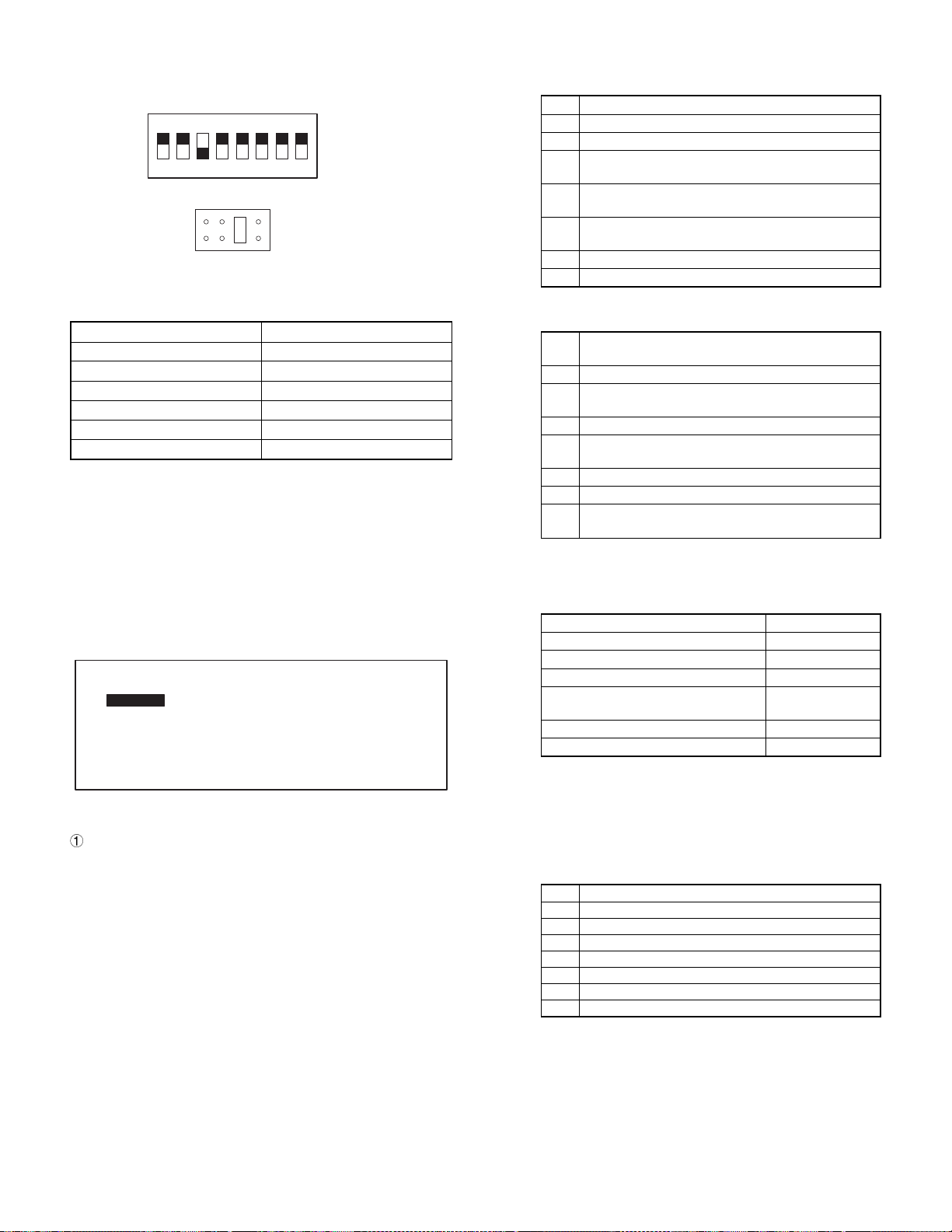

3-11. Rear Display Diagnostics

The display test of the option display ER-A8DP.

The following patterns are displayed. Pressing Esc key returns to the

service diagnostics menu.

1) Rear Display Check

Check content

The test patterns are displayed in the following procedures.

Pressing the space bar moves to the next pattern.

i. The following test pattern is displayed.

ix. All white pattern

x. Color bar (16 colors)

Color bars of 16 colors are displayed.

Black

Blue

Green

Cyan

Red

Brown

White

Magenta

Gray

Light green

Light blue

Light cyan

Light red

Light magenta

xi. Color pattern (256 colors)

Color pattern of 256 colors is displayed. The displayed colors

are default pallet.

Light yellow

ii. The test pattern of all digits ON is displayed.

Light white

Display

Rear Display Check

Terminating method

Pressing Esc key clears the rear display and terminates the test.

4 – 11

Page 28

3-12. SHARP Retail Network Diagnostics

The SRN interface option ER-01N-PC is tested.

Set the ER-01IN-PC DIP switch and jumpers as shown below.

1 2 3 4 5 6 7 8

SW2-3 OFF

OFF

SW2

IRQ12

IRQ 10

111215

I/O address is different from ER-A850/880 SRN as shown in the table

below.

Register (R/W) ER-01IN-PC

DRR/DWR 200

STR/ENR 201

___/WCF 202

HEND/SYSF 203

___/SRCR 205

TNO/___ 204

The following composition is required for the test.

· ER-01N-PC

· Terminal resistor

· Branch (Main line) cable (only for data transmission)

The following menu is displayed.The highlighted cursor is moved by

the cursor keys (UP and DOWN ¯) of the AT keyboard. Move the

cursor to the desired item, and press Enter key to execute the selected diagnostics program. When the selected diagnostics program

is completed, the display returns to t he menu screen. Pressing Esc

key returns to the service diagnostics menu.

SRN (SHARP Retail Network) Diagnostics

Self Check

Flag Send Check

Data Send Check

Data Transmission Check (Satellite Machine)

Data Transmission Check (Master Machine)

1) SRN Self Check

Check content

The ROM check for SRN, the interruption by CTC, and carrier

sense are checked. In addition, ADLC functions and send/receive

DMA check are made by means of the self l oop function of ADLC

(MC6854). The other signals are also checked. The check procedures are as follows:

i. Diag 2 command is executed and the number of resending is

displayed.

ii. Diag 0 command is executed and the error status is dis-

played. The error status is as shown in the table below. When

an error occurs in this test, the following test is not executed.

b7 An error is generated. (Error print is always "1.")

b6 An unexpected interruption is made.

b5 A collision occurs.

The interruption of transmission end (interruption of

b4

DMAC TC-UP) is not made.

The interruption of carrier OFF is not made. The

b3

mirror image of carrier OFF shows carrier ON.

The interruption of CTC. CH2, or CH3 (timer

b2

interruption) is not made.

b1 ROM SUM CHECK ERROR

b0 RAM ERROR

iii. Diag 1 command is executed and the error status is dis-

played. The error status is as shown in the figure below.

An error is generated. (Always 1 in case of error

b7

print.)

b6 An unexpected interruption is made.

Data transmitted by DMA is different from date

b5

received.

b4 The number of data received by DMA is abnormal.

The number of data transmitted by DMA is

b3

abnormal.

b2 An overrun error is generated.

b1 An underrun error is generated.

An interruption of transmission end (interruption of

b0

DNAC TC.UP) is not made.

iv. Diag command 5 is executed and the error status is dis-

played.The names of signals which are subject to t he check

by diag 5 command and their directions are as shown in the

table below.

Signal name Direction

Power OFF interruption notice Host ® Controller

Power ON intial iz i n g Host ® Controller

Power ON continuation Host ® Controller

Power OFF interruption process com-

plete

Host ¬ Controller

CH1 received data present Host ¬ Controller

CH2 received data present Host ¬ Controller

Check that the target byte of two status (ST1 and ST2) obtained by diag 5 command is "0" for ST1 and "1" for ST2. (The

other bits must be masked.) In the other cases, the error

occurrence bit is "1" and the error status is displayed.The

normal bits are "0."

The error status from the host to the controller is as shown in

the table below.

b7 NC (Always displays "0.")

b6 Service interruption notice

b5 NC (Always displays "0.")

b4 NC (Always displays "0.")

b3 NC (Always displays "0.")

b2 NC (Always displays "0.")

b1 Power ON continuation

b0 Power ON initializing

4 – 12

Page 29