Page 1

SERVICE MANUAL

POS TERMINAL

MODEL UP-5350

"U" Version "UB" Version

Color of Cabinet parts Gray 282 (light gray) Gray 35 (dark gray)

CONTENTS

■INTRODUCTION

Explanation of modifications

CHAPTER 1. SPECIFICATIONS..................................................................1 - 1

CHAPTER 2. OPTIONS................................................................................2 - 1

CHAPTER 3. SERVICE P RE CA UT ION........................................................3 - 1

CHAPTER 4. UP-535 0 D IAGNOSTICS SPECIFIC ATIONS.........................4 - 1

CHAPTER 5. CIRCUIT DE SC RIPTION........................................................5 - 1

CHAPTER 6. BIOS SETU P UTILITY............................................................6 - 1

CHAPTER 7. ABOUT UTILITY SOFTWARE AND OTHER S.......................7 - 1

CHAPTER 8. CIRCUIT DIA GR AM................................................................8 - 1

CHAPTER 9. PWB LAYOU T.........................................................................9 - 1

PARTS GUIDE

Parts marked with " " are important for maintaining the safety of the set. Be sure to replace these parts with specified

ones for maintaining the safety and performance of the set.

This document has been published to be used

SHARP CORPORATION

for after sales service only.

The contents are subject to chang e w ithout notice.

Page 2

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

-->

BATTERY DISPOSAL

Contains Nickel Metal Hydride Battery. Must be Disposed of Properly.

Contact Local Environmental Officials for Disposal Instructions.

Page 3

■INTRODUCTION

Explanation of modifications

Changes in association with production discontinuance of NeoMagic Graphics Controller

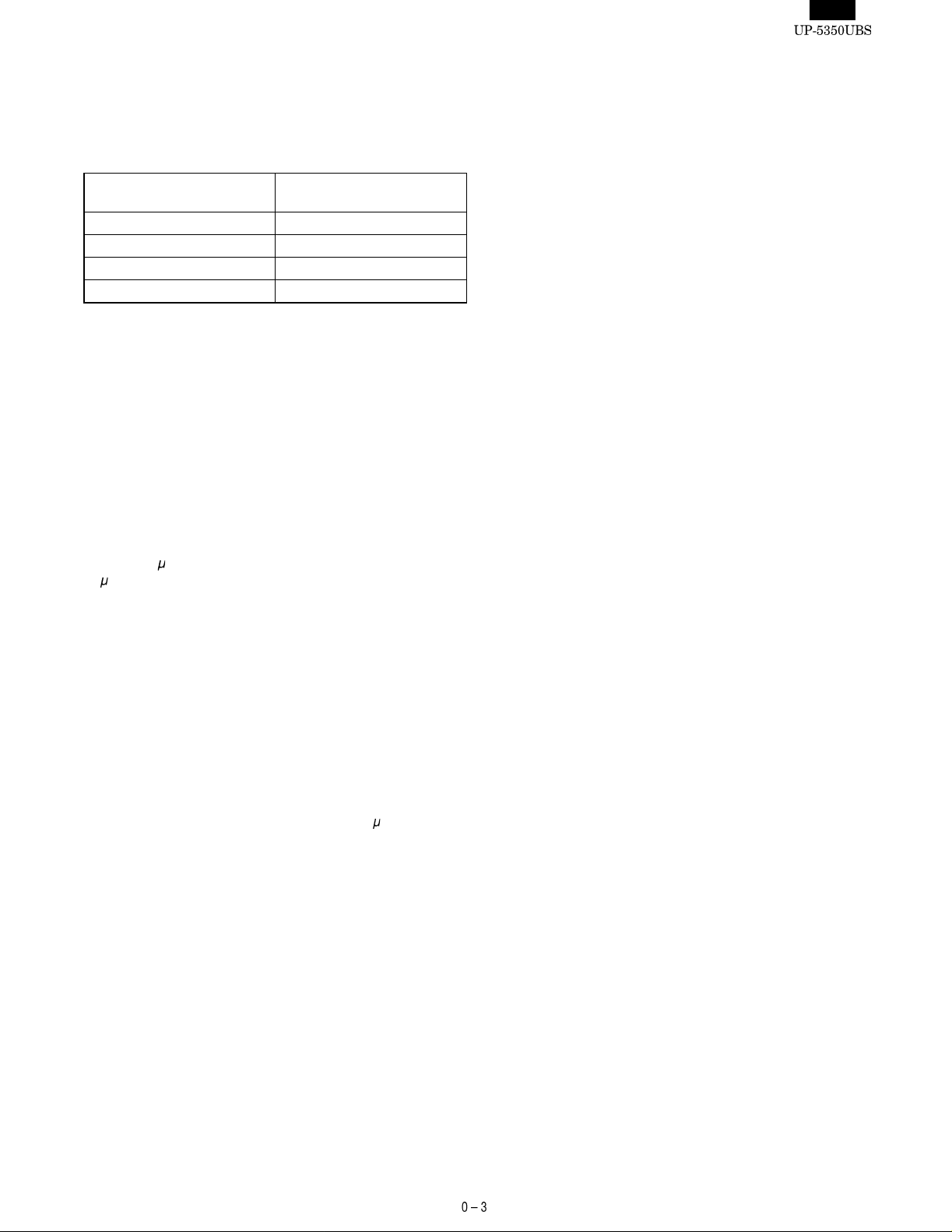

1. APPLICABLE MODELS

MODEL NAME VERSION:CABINET COLOR PRODUCTION PERIOD

UP-5350 U : Gray282 (Light gray) From Oct. 2000

UP-5350 UB : Gray3.5 (Dark gray) New products (1st lot produced in Oct.)

2. OUTLINE

In association with production di scontinuance of NeoMag ic Grap hi cs Controllers,

Silicon Motion Inc. Graphics Controllers will be incorporated.

OLD NEW

PARTS CODE

SOURCE MAKER NeoMagic Silicon Motion Inc

Along with this change, a new function is also add ed so th at th e sta nd ard intern al FDD may become detachable.

For this new function, refer to item 3-4 ).

3. DESCRIPTIONS OF CHANGE

As a result of the Graphics Controller change, those changes described in items 1) - 5) will also be im pl emented.

1) VGA PWB UNIT change

As a result of the Graphics Controller change, the VGA PWB UNIT will

also be changed.

PARTS NAME OLD NEW

VGA PWB UNIT

2) MAIN PWB UNIT change

In parallel with the VGA PWB unit change, the Main PWB unit will also

be changed as follows:

PARTS NAME OLD NEW

MAIN PWB UNIT

• IRQ5 will be assign ed to the new Graphics Controller,

CHIPSET signal (PIRQ5) and No. 77 pin of VGA PWB UNIT connector (CN11) will be conn ecte d.

3) BIOS ROM Change

Since the BIOS PROGRAM must be updated from Version 1.0A to

Version 1 .0B to sup port the new Grap hics Cont roll er, the BI OS MASTER ROM will be change d a s fol lo ws:

PARTS NAME OLD NEW

BIOS MASTER

ROM

You can check the BIOS version in the following system start up

screen, which is displayed when unit is powered on.

(Version 1.0A) (Version 1.0B)

Old BIOS Version 1.0A

Phoenix NoteBIOS

Copyright 1985-1997 Phoenix Technologies Ltd, All Rights Reserved.

SHARP POS Terminal Firmware Version 1.0A

0000640K System RAM Passed

0031744K Extended RAM Passed

0512K Cache SRAM Passed

Fixed Disk 0 : Identified

4.0.0

New BIOS Version 1.0B

Phoenix NoteBIOS

Copyright 1985-1997 Phoenix Technologies Ltd, All Rights Reserved.

SHARP POS Terminal Firmware Version 1.0B

0000640K System RAM Passed

0031744K Extended RAM Passed

0512K Cache SRAM Passed

Fixed Disk 0 : Identified

4.0.1

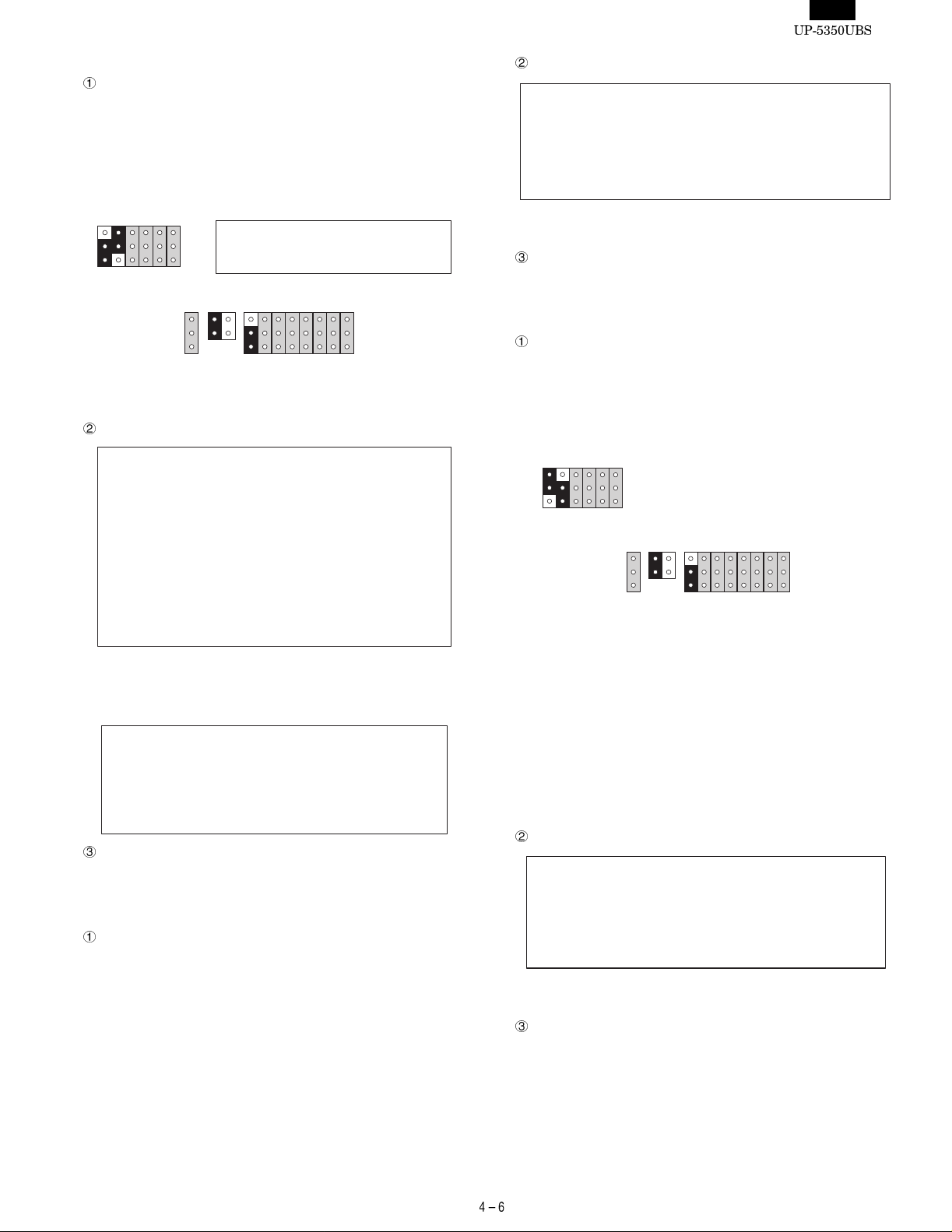

4) The SYSTEM SWITCH-1, will be enhanced.

The new BIOS al lows the standar d internal FDD to become detatchable, "FDD: Exist/Not Exist" will become selectable with SYSTEM

SWITCH: DSW-1.

SYSTEM SWITCH:DSW-1

Function

FDD Exist Not exist

To detach the FDD drive, turn ON this SWITCH.

*Important:The new BIOS may only be used on units using the Silicon

Motion video controller (Since Oct. production)

OFF

(value=1)

ON

(value=0)

Page 4

5) Software

A new Display driver will be released to support the Graphics Controller.

Windows 98 Second Edition

OLD NEW

FILE NAME DESCRIPTION FILE NAME DESCRIPTION

NMGC5VD2.VxD VGA Virtual Device Driver SMVD D.VxD VG A Virtual Device Driver

NMGC5VDD.VxD VGA Virtual Device Driver SMDRV.DRV VGA Device Driver

NMGC5.DRV VGA Device Driver SMI.INF VGA Driver information file

NMGC5VPM.DRV VGA Device Driver SMDD32.DLL VGA Driver library

NMGC5.INF VGA Driver information file SMI.CAT VGA Driver catalog file

NEOMAGIC.HLP VGA Driver help file NEOMAGIC.DLL VGA Driver library

NMGC5_16.DLL VGA Driver library NMGC5_32.DLL VGA Driver library

NMGCDD5.DLL VGA Driver library TSB.DLL VGA Driver library

Windows NT Workstation 4.0

OLD NEW

FILE NAME DESCRIPTION FILE NAME DESCRIPTION

NEO20XX.SYS VGA Device Driver SMIMINI.SYS VGA Device Driver

NEOMAFIC.INF VGA Driver information file SMISETUP.INF VGA Driver information file

NEOMAGIC.HLP VGA Driver help file SMIDISP.DLL VGA Driver library

NEO20XX.DLL VGA Driver library FRAMEBUF.DLL VGA Driver library

NEOMAGIC.DLL VGA Driver library TSB.DLL VGA Driver library

4. COMPATIBILITY

1) Compatibility between new and old parts

The following parts must be used on ly in the fo llow in g co mbina t ions a s follo ws. N ew and Old parts can not to coexist in the sam e unit.

ITEM OLD NEW Remarks

VGA PWB UNIT

MAIN PWB UNIT

(BIOS Version ) Version 1.0A Version 1.0B Refer to item 3-3).

(SYSTEM SWITCH-1 function) Don’t care FDD:Exist / Not Exist Refer to item 3-4)

Display driver OLD NEW Refer to item 3-5)

IRQ restriction IRQ5 is availab le. IRQ 5 is use d b y System Refer to item 4-2)

When you service the units in the field, take special care not to install the combination of an old Main PWB and a new VGA PWB or a new Main PWB

and an old VGA PWB.

Please modify Main PWB’s in the following methods:

To modify Main PWB’s from old to new,

please refer to item 5-1) please refer to item 5-1) How to modify old Main PWB’s to new Main PWB’s.

With this modification implemented, old Main PWB’s function as new Main PWB’s.

To modify Main PWB’s from new to old,

please refer to item 5-2) How to modify new Main PWB’s to old Main PWB’s

With this modification implemented, new Main PWB’s function as old Main PWB’s.

Important: The old VGA PWB’s cannot be modified to the new VGA PWB’s, or vice ve rsa.

Refer to items 2 and 3-1).

Refer to item 3-2).

Page 5

2) IRQ signal compatibility

The old Graphics Controller does not use an IRQ, while the new

Graphics Controller uses IRQ5.

To avoid IRQ collisions, Please assign IRQ’s other than IRQ5 to the

other devices.

The following chart shows IRQ’s available to optional devices.

IRQ’s available to optional

devices.

IRQ7 LPT1

IRQ10 COM4

IRQ11 COM3

IRQ12 Ethernet/SCSI

Recommended devices for

UP-5350

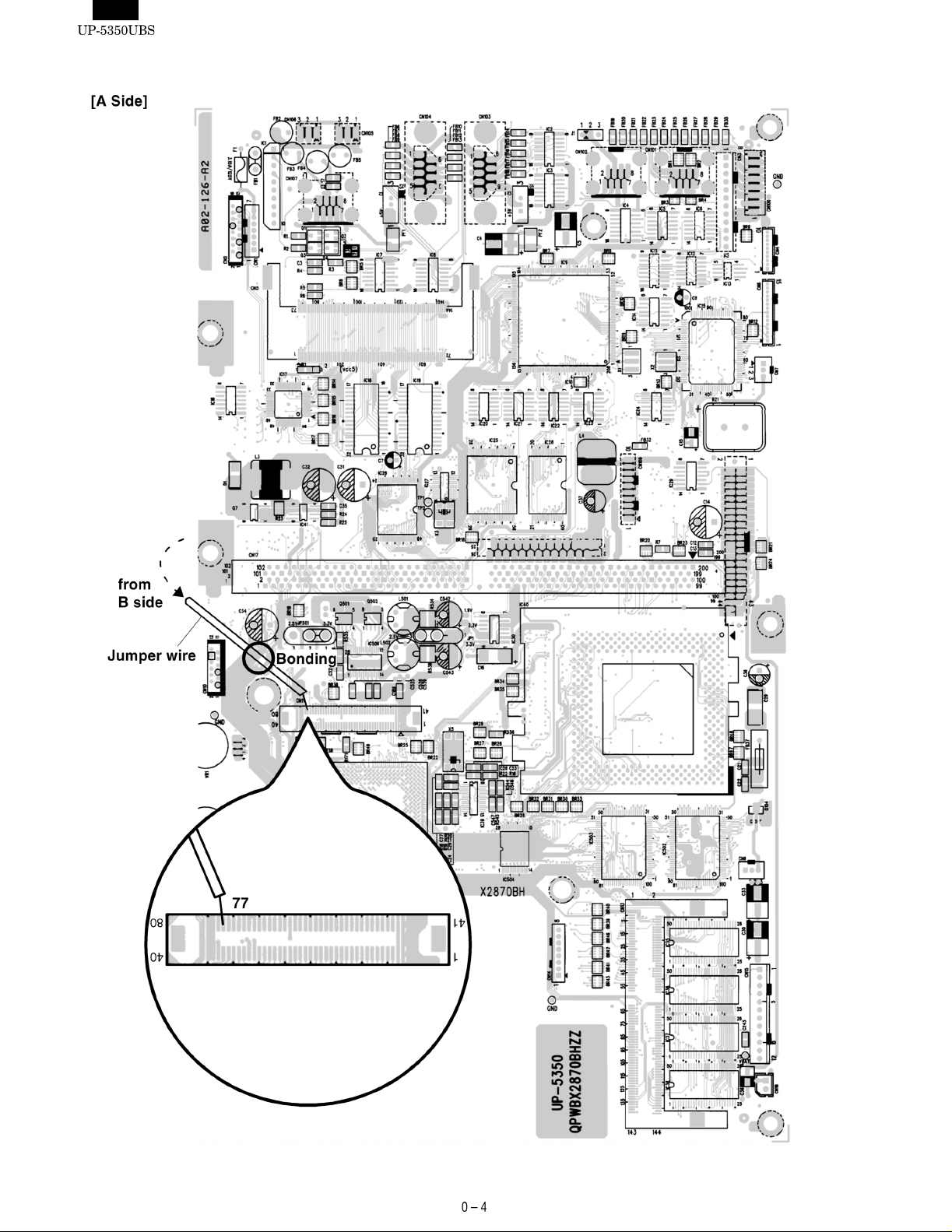

5. HOW TO MODIFY MAIN PWB’s

1) How to modify old Main PWB’s to new MAIN

PWB’s

A) Connect a jumper w ir e .

Connect the No. 77 pin of VGA Connector (CN11) on Main PWB side

A to the solder pad (PAD2 in JR100) supplying IRQ5 on Main PWB

side B by soldering a jumper wire. (For more information, refer to the

PWB layout.)

B) Change a capaci tor.

Change the capacitance of the Capacitor C536 on the Main PWB B

side from 0.1

0.1

F : VCKYTV1HF104Z -> 1000Pf VCKYTV1HB102K

C) Update the BIOS version.

Rewrite the BIOS to update the version to 1.0B to support the new

Graphics Controller.

To rewrit e t he B IO S p rog r am, pl ea se ref e r t o p ag es 2-6 "W r iti ng BI OS

ROM Program".

F to 1000 pF.

2) How to modify new Main PWB’s to old Main

PWB’s

A) Modify BIOS program

Rewrite the BIOS to modify the version to 1.0A to support the old

Graphics Controller.

There is no need to change the capacitor C536 to 0.1

To rewrite the BIOS program, refer to pages 2-6 "Writing BIOS ROM

Program".

F.

Page 6

3) PWB LAYOUT

Page 7

Page 8

12345678

(5/21)

D

VCC3

VCC2R5

1 3

JP501

FB560

2

BFD3580R2F

VCC3_GC

VCC5

A

2 1

IC34F

4069

13 12

10

IC34E

4069

11

IC34D

4069

9 8

IC34C

4069

5 6

14PIN --- VCC3

3

PCICLK2

33

R544

1

R14

10k

23

GND4GND11GND17GND

14

VCC5

PERR#

STOP#

RSTDRV#

VCC3_GC

PERR#

RSTDRV#

C546

120p

2

MK1492-04

R208

VCON

RXD7

B

22k

RXD7

PCICLK3

33

R545

C547

120p

2

1

FS32K

OSC32K

47

R1147R13

C20

27p

IC34B

4069

3 4

IC34A

VCC3

VR2

20k VR

BLON

PIRQ5

+12V

VR2-2

VR1

R580

20k VR

22.1kF

X4

32.768KHz

C18

R209

1 2

18p

8.2k

Add

R207

4069

2.32kF

R9 10M

R12 470k

C19

15p

C

FS14M

FSCLK

CPUCLK

CLK_L2

R527

OSC14M

R18 33

R17 33

R15 33

R19 33

5

28

8

13

HOST210HOST312HOST4

F1(PEN)

EHOST1

14.3(OE)

XI2XO

IC39

R22

10M

C28

22p

1

1

1

2

B

F

FB133

BLM21

1

VCC3

C/BE#0

C/BE#2

AD30

AD28

AD26

AD24

SDCLK6SDATA7PCISTP#16CPUS#15VDD1VDD20VDD26VDD_HOST1,29VDD_HOST3,4

3

0

R21

R20

1M

X5

MA-406

14.3181MHz

C27

22p

2

C221

1000p

2

C224

0.1u

2

2

C225

10u

B

F

FB132

1

VCC_CPIO

VCC5

AD22

AD20

AD18

AD16

AD14

AD12

33

1

1

1

10k

R210

1

1

C25

C523

18

HOST5,7

BLM21

AD10

PCICLK

33

R16

C23

10p

10p

HOST6,8(DS)

1000p

0.1u

120p

2

1

27

25

24

22

21

PCI(FS)

PCIF(LE)

PCI(SEL1)

PCI(CSSS)

48M/14M(SEL0)

TRDY#

FRAME#

BR36

10kX4

4

3

2

1

AD4

AD2

AD0

OSC14M

FRAME#

TRDY#

STOP#

10p

2

2

C24

2

C26

10p

19

R211 10k

2

C223

2

C220

5

6

7

8

AD8

AD6

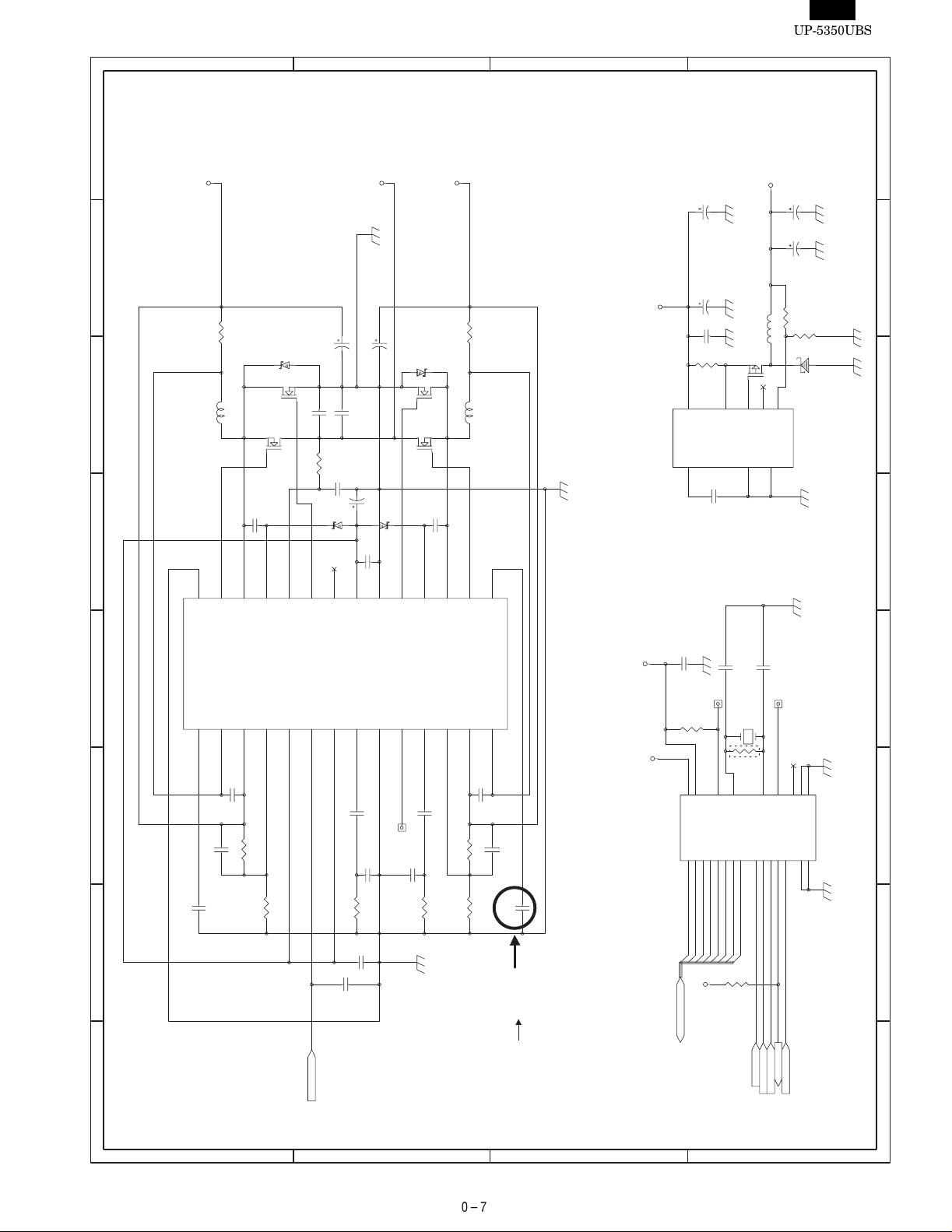

4) CIRCUIT DIAGRAM

BR49

10kX4

4

VCC5

5

6

7

8

C/BE#

3

C/BE#

2

C/BE#

1

C/BE#

3

2

1

0

C/BE#[0..3]

1-1-5. VGA CONNECTOR

D

414243444546474849505152535455565758596061626364656667686970717273

123456789101112131415161718192021222324252627282930313233343536373839

CN11

VCC5

C/BE#3

C/BE#1

AD31

AD29

AD27

AD25

AD23

AD21

AD19

AD17

AD[0..31]

AD15

VCC5

AD13

AD11

AD5

AD3

AD1

OSC32K

BR38

10kX4

IRDY#

DEVSEL#

PCICLK2

4

3

2

1

IRDY#

DEVSEL#

AD9

AD7

5

6

7

8

C

CPAR

CPAR

SERR#

SERR#

VCC3

FANON

TXD7

FANON

74

7576777879

VR2-1

BGNT#

TXD7

BGNT#

B

BREQ#

BREQ#

+12V

80

40

R541

R540

IC34 : 7PIN --- GND

53489-0809

10k

10k

VCC5

8 7 6 5 4

A

Page 9

12345678

(6/21)

D

C

B

A

CS

C548

X1 2X2

AD0

AD1

AD2

4

5

1,2,3

7

3

3p

X3

R581

4Q7Si9430

EXT

SHDN

32.768kHz

VCC2R5

C31

150u/6.3V OS(SL)

C32

OS(SL)

150u/6.3V

R25

100KF

R24

L3 39uH

1

OUT

3

150KF

12

D1

5,6

7,8

SFPB72

2

FB

GND

MAX1651

8

C549

2p

TP2

12

23

22

16

GND

GND

SQW

EXTRAM

MOT

INT#

RST#

R/W#

CS#

BQ3285ESS

1

19

18DS 17

15AS 14

13

2 1

3

RTC

VCC2

(VOUT1=1.9V)

R534

0.010

1/2W(RL3720W)

D501

SFPB54

L501

10uH

RCH-108

28

27

TG1

FLTCPL

RUN/SS1

SENSE+

IC506

1

2

C526

1000p

C525

180p

Q501B

10u/6.3V

(GRM225)

FDS8963A

Q501A

FDS8963A

C537

0.1u

26

25

SW1

BOOST1

SENSE-

VOSENSE1

3

4

R528

49.9kF

10

R535

23

24

VIN

BG1

FREQSET

STBYMD

5

6

VCC5

(VIN=5V)

C542

C543

220uF/4V OS(SP)

150uF/6.3V OS(SP)

C551

C552

10u/6.3V

(GRM225)

C539

0.1u

C540

4.7u/16V

GRM230

D503

RB501V-40

D504

RB501V-40

C541

1u

21

22

20

19

BG2

PGND

INTVCC

EXTVCC

FCB

ITH1

SGND

3.3VOUT

7

8

9

10

TP504

C530

1000p

C531

33p

VCC3

(VOUT2=3.3V)

R536

0.010

D502

SFPB54

Q502B

FDS8963A

Q502A

FDS8963A

C544

0.1u

18

BOOST2

ITH2

11

C533

TP

C532

33p

1/2W(RL3720W)

L502

10uH

RCH-108

17

16

15

TG2

SW2

RUN/SS2

VCC5

VOSENSE2

SENSE2-

SENSE+

LTC1628CG

12

13

14

VRAM

C535

1000p

1000p

2 1

C534

R533

180p

63.4kF

C550

22u/10V

GRM235

C14

100u/10V OS(SA)

VCC5

C160

0.1u

R23

0.22F

5

6

V+

REF

IC41

4

C35

0.1u

C242

1u

TP1

R166

10k

RCL#

24

21

20

BC

VCC

RCL#

AD3

AD4

AD5

AD6

AD7

IC27

6

7

8

9

10

11

1-1-6. RTC

36kF

C524

R529

0.1u

PWRGOOD

15k

R530

C529

0.01u

C528

0.01u

D

15k

20kF

C536

R531

C

0.1u

R532

SD7

SD6

SD5

SD4

SD3

SD2

SD1

SD0

VCC5

R165

New

Old

1000pF

SD[0..7]

0.01µF

B

10k

RTCAS

RTCRD#

RTCWR#

IRQ8#

RSTDRV#

IRQ8#

RTCAS

RTCRD#

RTCWR#

RSTDRV#

8 7 6 5 4

A

Page 10

CHAPTER 1. SPECIFICATIONS

1. APPEARANCE

Brightness

control

Contrast control

Power switch

Operator display

(touch panel)

Power indicator

Money checking

space

Floppy disk drive

3-2. KEYBOARD

TOUCH PANEL

ITEM SPECIFICATIONS NOTE

Type Touch key (Analog touch panel)

Number of

key positions

Control Mouse emulation

4096 (W) x 4096 (H) positio ns

POS KEY PAD

Option (UP-C30PK)

ITEM SPECIFICATION NOTE

Type POS rising ke ybo ard

Number of

keys

Key layout

Standard 27 keys

Numeric keys : 11 keys ( 1 to 9,0 an d 0 0)

Capped keys : 16 keys (Key labels are local ly

purchased.)

Maximum 30 keys (6x5 matrix)

(Changing key layout by using

ER-11KT7/12KT7/22KT7)

789

AC cord

AC CORD

Plug your POS terminal into a wall outlet before using.

POWER SWITCH

Set the power switch to the ON ( I ) position after plugging your POS

terminal.

2. RATING

ITEM SPECIFICATIONS

External dimensions 11.8 (W) x 16.3 (D) x 13.3 (H) in. approximately

(298.5 (W) x 415 (D) x 337 (H) mm )

Weight Approximately 15.5lb. (7.0 kg)

Power source 100 - 120V AC

Power consumption Operating : 74W

Working temperature

and humidity

32 to 104 °F (0 to 40°C)

10%, 60 Hz

3. HARDWARE

3-1. DISPLAY

ITEM SPECIFICATION NOTE

Type DSTN color LCD with back light High color(16bit)

display

Screen size 12.1" full screen

Dot format 800(W) x 3(RGB) x 600 (H) dots

Dot size 0.0825 x RGB(W) x 0.28 25 (H) m m

Control SVGA With 4MB

video RAM

456

123

000

3-3. PC SYSTEM

ITEM SPECIFICATIONS NOTE

CPU MMX Pentium

Chip set FireStar Plus:

Graphic controller VGAC:

Main memory

(for executing MS-DOS,

Application software)

Video RAM 4 Mbytes VGAC Embedded

BIOS ROM 512 Kbytes Flash ROM

Keyboard controller M38802M270

Super I/O M5113 A2

POS system controller PSC2 : LZ9AM22

processor

82C700U3.2

SM712GM04

Standard : 32

Mbytes

Max. : 96 Mbytes adding S.O.DIMM

266MHz

EDO type

SGRAM

Page 11

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

-->

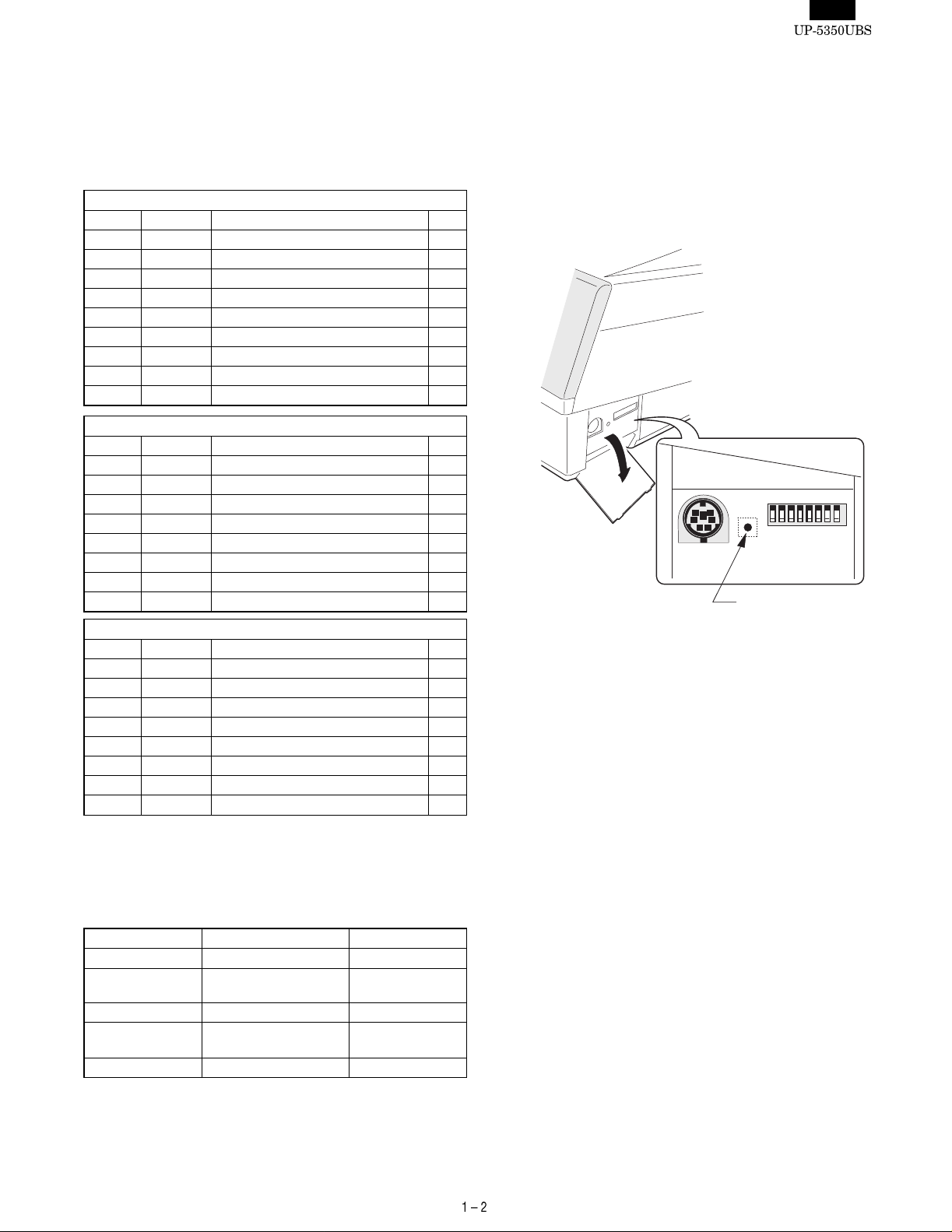

3-4. SERIAL PORT

D-SUB 9-pin connector COM1 and COM2 are eq ui pped.

In order to supply +5V power, CI signal and +5V power supply of

COM1 and COM2 can be switched.

2 channels of RJ45 Connector COM port are equipped.

COM3 and COM4 or original I/O address (COM5 and COM6) can be

selected as the 2 channels of RJ45 COM port.

COM1 & COM2: D-sub 9 pin

Pin No. Signal Function I/O

1 CD Data Carrier Detect I

2 RD Receive Data I

3 SD Send Data O

4 ER Data Terminal Ready O

5 SG Signal Ground —

6 DR Data set Ready I

7 RS Request to Send O

8 CS Clear to Send I

9 CI/+5V Ring Indicate / +5V I/–

COM3 or COM5: Modular jack RJ45 8 pin

Pin No. Signal Function I/O

1 RS Request to Send O

2 ER Data terminal Ready I

3 SD Send Data O

4 SG/(+5V) Signal Ground/(+5V) —

5 SG Signal Ground —

6 RD Receive Data I

7 DR Data set Ready I

8 CS Clear to Send I

COM4 or COM6: Modular jack RJ45 8 pin

Pin No. Signal Function I/O

1 RS Request to Send O

2 ER Data terminal Ready I

3 SD Send Data O

4 SG Signal Ground —

5 SG Signal Ground —

6 RD Receive Data I

7 DR Data set Ready I

8 CS Clear to Send I

3-5. EXPANSION SLOT

ISA PC board can built in UP-5350 up to two.

5V PCI board can built in UP -5 350 instead of an ISA PC bo ard .

This has to satisfy the power consum pti on .

3-6. SHUTDOWN SWITCH

The shutdown switch is used when the OS or applica tion programs

are straying and the system can not return to the normal state.

You must not use this sh utdown s witch whe n the UP- 5350 is r unning

normall y. Use th is swit ch only wh en the mai n power sour ce is n ot cut

off even if the main unit power switch is set to OFF position. The

UP-5350 is turned OFF and the hardware is reset by turning the main

power switch OFF and th en pressing the shutdown sw itch .

12345678

Shut down switch

[OUT LINE]

The shutdown switch is a si ng le shu t type . (Normally OFF position)

Push ON: This position is used to reset the stand-by mode for

power supply unit during softw are hang ups.

Release OFF: Usually the shutdown switch needs to be set to this

position when the UP-5350 is operating.

[OPERATING METHOD]

The shutdown switch is a push switch. If it is pushed to ON, the

UP-5350 stops supplying the power when the power switch is set into

stand-by mode.

NOTE:The shutdown operation will be ignored when the power switch

is set to power-on position.

ITEM SPECIFICATION NOTE

Type ISA bus & PCI bus

Power

consumption

ISA board size Half size PC board ER-A8R S, etc.

5V PCI board size Short size PC board (Local

Quantity 2 slots 2 ISA or ISA + PCI

+5V max. 1.0A

+12V max. 0.05A

procurement item)

Page 12

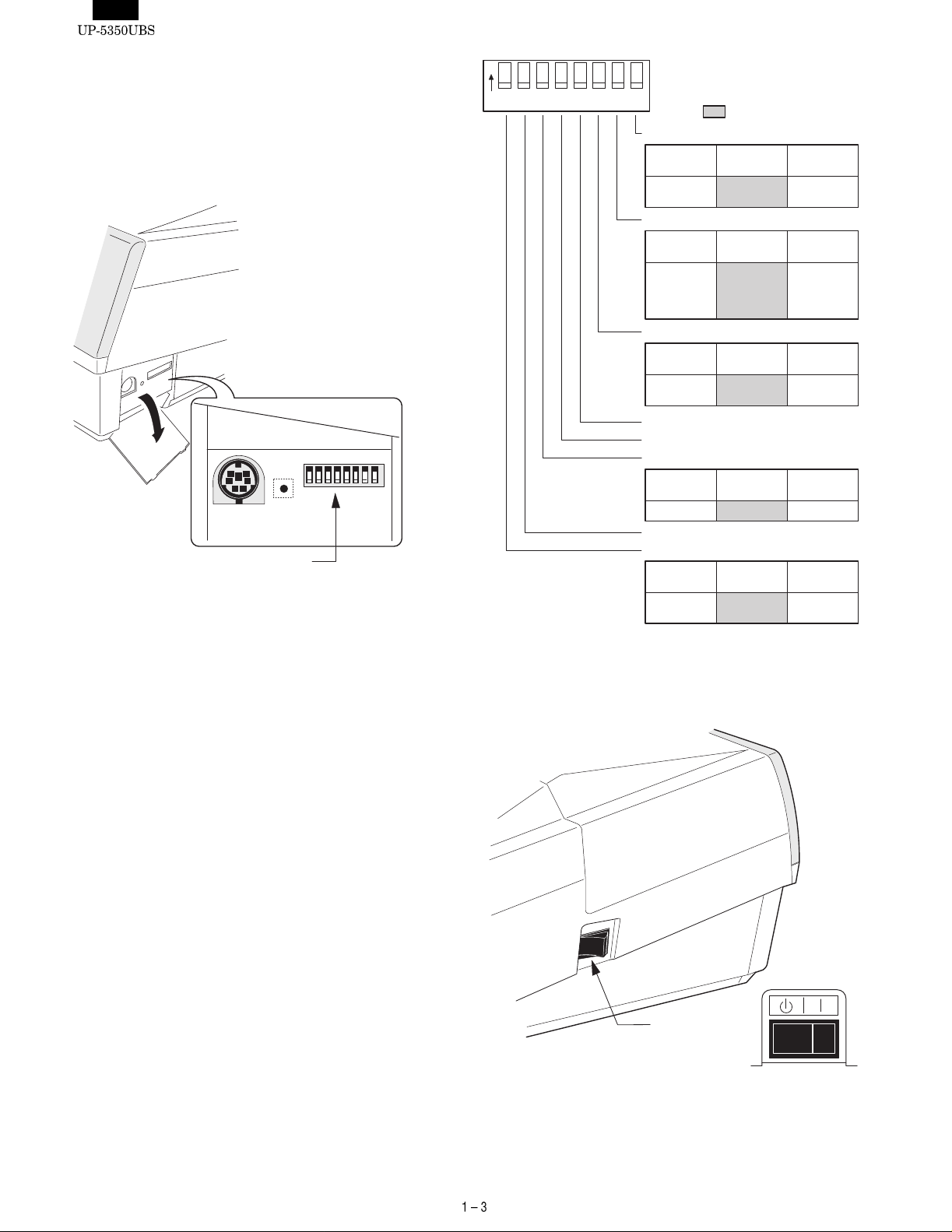

3-7. SYSTEM SWITCH

The system switches are used to preset various system configurations.

[OUT LINE]

The system switches consists of DIP switche s.

[DIP SWITCH]

12345678

System switch

The PSC2 simply reads the switched signals from the DIP switch as

hardware. The meaning of the switch settings are shown at the right.

ON

1234567 8

ON

OFF

: Default setting

DSW-8

Function

Serial3 & 4

decode mode

OFF

(value=1)

COM3 &

COM4

DSW-7

Function

COM3 &

COM4 IRQ

assign

(Serial 3 & 4)

OFF

(value=1)

COM3=

IRQ11

COM4=

IRQ10

DSW-6

Function

CMOS

Initialize

OFF

(value=1)

Not Initialize

DSW-5 : Reserved (OFF)

DSW-4 : Reserved (OFF)

DSW-3

Function

Boot Drive

OFF

(value=1)

Drive A:

DSW-2 : Reserved (OFF)

DSW-1

Function

Floppy Disk

Drive

OFF

(value=1)

Exit

ON (value=0)

COM5 &

COM6

ON (value=0)

COM3=

IRQ4

COM4=

IRQ3

ON (value=0)

Initialize

ON (value=0)

Drive C:

ON (value=0)

Not exit

Note : On the UP-5350, DSW-1, -2, -4, and -5 are ig no red .

3-8. POWER SWITCH

Power switch :

Page 13

[OUT LINE]

The power switch has the positions ON and OFF (Stand-by)

ON position: Usually the power switch needs to be set to this posi-

tion when the POS-terminal is operated .

OFF position: This position can be used to for the stand-by mode.

When the power switch is set to this position, the

power supply stops automatically. But if the software

program co ntrols the power supply t o hold, ev en if the

power switch is set into this position, the power supply

will stay on until the software program allows a power

supply to turn OFF.

[OPERATING METHOD]

The power switch is a see-saw switch, and it can be tipped toward the

ON or OFF position.

4. SOFTWARE

ITEM SPECIFICATION NOTE

OS provision The OS may be pre-installed.

Available OS Windows 98 Second Edi tio n

Windows NT Work station 4 . 0

Device drivers POS drivers POS device driver Provided from SHARP

Touch panel driver

VGA device driver

Additional device driver

BIOS Written to the Flash ROM on the

Main PWB.

Utility software Touch panel calibration utility program Provided from SHARP

Double t a p setup u t il ity progra m

POS print e r utility pro gram

Application software

Page 14

CHAPTER 2. OPTIONS

1. SYSTEM CONFIGURATION

Additional DRAM

Memory

<Local item>

Magnetic

Card Reader

<Option>

UP-E12MR2

Customer Display

<Option>

UP-I20DP

HDD Unit

<Local item>

PC Keyboard

<Local item>

Drawer

<Option>

ER-03DW/04W

Host

UP-5350

max.2

Incorporated in Main Unit

(Ethernet)

(RS-232)

RS232 Board

<Option>

ER-A8RS

Built-in printer

<Option>

UP-T80BP

In-line Communication Connection

Sub

UP-5350

RS-232 Communication Connection

max.6

Remote Printer

<Local item>

Local Printer

<Option> ER-01PU

<Local item>

Hand Scanner

<Option>

ER-A6HS1

PC server

<Local item>

Kitchen video monitor

<supplied on site>

CAT/EFT

<Local item>

Scale

<Local item>

Customer

Poll Display

<Option>

UP-P20DP

2. OPTIONS

No. NAME MODEL NAME DESCRRIPTION

1 Customer display UP-I20DP 2 line 20 digits dot display

2 Customer pole display UP-P20DP 2 line 20 digits dot display

3 MCR (Magnetic Card Reader) UP-E12MR2 for ISO 1 & 2 stripe card

Remote drawer ER-03DW 7B/5C

4

5 Receip t/Jou rnal printer ER-01PU 2 station (R/J) the rm al pri nte r 45mm width

6 Built-in printer UP-T80BP 1 station thermal printer 80mm width

RS232 & CENTRO I/F board ER-A8RS RS232 9 pins connector:2 ports

7

8 Han d sca nn er ER-A6HS1 for reading bar co de

9 Key pad UP-C30PK Std. 27 keys, Max. 30 keys

Key kit (Used for key pad : UP-C30PK) ER-11KT7 1 x 1 key top kit

10

ER-04DW 5B/5C

Centronics 25 pins connector : 1 port

ER-12KT7 1 x 2 key top kit

ER-22KT7 2 x 2 key top kit

Coin dispenser

<supplied on site>

Page 15

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

-->

3. LOCALLY SUPPLIED OPTIONS

No. NAME DESCRIPTION NOTE

1 S.O.DIMM 144pin Small Outline DIMM Max. 64Mbytes *1

2 Hard disk drive 2.5 inch type *2

3 Ethernet Ethernet adapter *3

4 PC keyboard PS/2 type PC keyboard

5 Application softw are

6 Addition al de vice dri vers

*1 Extension RAM module

[Device] 144pin Small Outline DIMM (8Mbytes/16Mbytes/32Mby-

tes/64Mbytes)

[Outline] UP-5350 has a socket as Small Outline DIMM.

The following S.O.DIMM memory specification must be

adhered to.

[Specification]

144pin S.O.DIMM

8 Mbytes 16 Mbytes 32 M byte s 64 Mbytes

Type EDO type

Access time 60 nsec.(or less)

Power 3.3V

Refresh cycle 1024/16 msec 2048/32 msec. 4096/64 msec. 4096/64 msec.

Refresh type CBR

Power consumption 700 mA (or less)

Other 4 chips x 16Mbits

(1 Mwords x 16 bits)

8 chips x 16Mbits

(2 Mwords x 8 bits)

4 chips x 64Mbits

(4 Mwords x 16 bits)

8 chips x 64Mbits

(8 Mwords x 8 bits)

*2 Hard disk drive

[Device] 2.5 inch type Hard disk drive

[Outline] It is necessary to satisfy with 2.5 inch Hard disk drive

specification as follows.

[Specification]

2.5 inch Hard disk drive

Type 1 Type 2

Maker Fujitsu Toshiba

Model MHD2021AT MK4313MAT

Capacity 2167 Mbytes 4327 Mbytes

Interface ATA-4 ATA-4

*3 Ethernet

[Device] Ethernet adapter

[Outline] It is necessary to satisfy the Ethernet adapter specifica-

tion as follows.

[Specification]

Ethernet adapter

Type 1 Type 2

Maker 3 Com 3Com

Model EtheLink III ISA EtheLink III XL

Speed 10 Mbps 10 Mbps, 100 Mbps

Interface 16-Bit ISA 5V 32-Bit PCI

Page 16

4. SERVI C E OP TIO N S

No NAME PARTS CODE PRICE DESCRIPTION

1 Connector cable for Dongle (LPT-1)

BL Relay line from Terminal to Dongle

5. SERVICE TOOLS

No. NAME PARTS CODE PRICE DESCRIPTION

1 Service tool kit

2 Printer con ne c tor signal loop back connector

3 MCR test card

4 RS232 loop back connector

5 BI OS loadin g board

6 RS232 mo du la r jack loop back connector

7 BIOS MASTER ROM

8 TOUCH PEN

CW ISA checker

ISA relay board

BR for ER-A8RS CENTRONICS connector

BE for UP-E12MR2

BC for RS232 connector

CS for overwriting BIOS

AZ for RJ45 connector

— EP-ROM for overwriting BIOS

AG

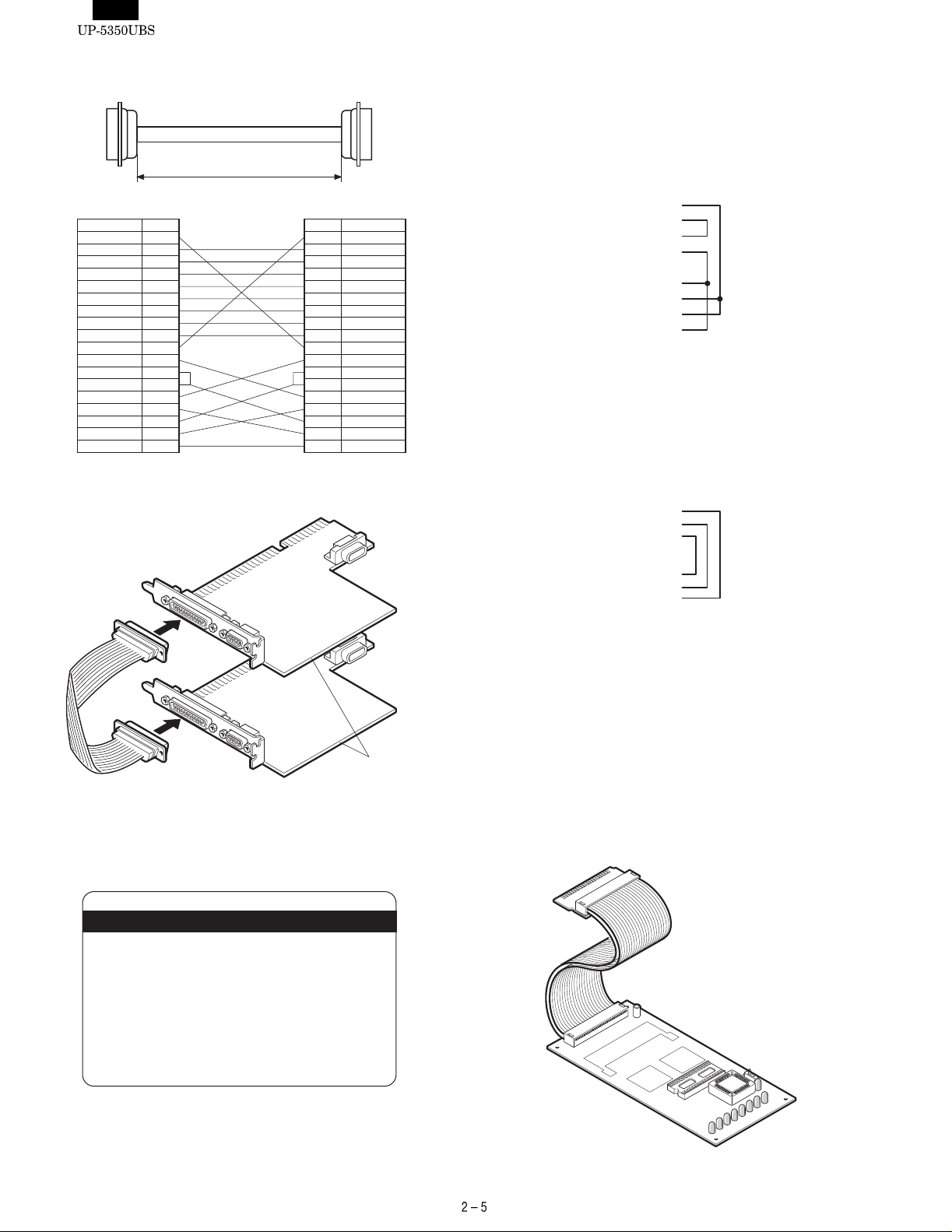

5-1. SERVICE TOOL KIT: DKIT-8656BHZZ

1) ISA CHECKER

Used to repair or check the operation of th e o ption al I/F.

• Externa l view

• Plai n view

ISA bus connectors:

Used to connect with the I/F PWB of ER-A8RS etc.

Test pins: Used to check the ISA bus signal.

LED circuit: Not used currently.

RAM1A

Connected to the UP-5350 ISA bus connectors.

Page 17

• Connection diagram

• Connection diagram

ER-A8RS

UP-5350

ISA bus connector

ISA checker

2) ISA RELAY BOARD

Connected to the ISA checker for installation of the optional I/F horizontally and for repairing and checking the opera tio n .

• Externa l view

ER-A8RS solder side

ISA relay board

ISA PWB

ER-A8RS parts side

ISA checker

• Plai n view

ISA bus connector:

Used to check the ER-A8RS parts side.

ISA bus connector:

Used to check the ER-A8RS solder side.

Connected to the ISA bus connector of ISA checker.

5-2. PRINTER CONNECTOR SIGNAL LOOP CHECK

CABLE: UKOG-6717RCZZ

Connected to the centronics connector (25 pin) of the ER-A8RS, and

is used to check loop signals wh en executing diagnostics.

• Externa l view

Page 18

• Plan view and connection diagram

150±8

Signal name Pin No.

1STROBE2DB0

3DB1

4DB2

5DB3

6DB4

7DB5

8DB6

9DB7

10ACK11BUSY

12PE

13SLCT

14AUTOFD15ERROR16INIT17SLCTIN-

18~25PE

• Connection diagram

Signal namePin No.

1 STROBE2 DB0

3 DB1

4 DB2

5 DB3

6 DB4

7 DB5

8 DB6

9 DB7

10 ACK11 BUSY

12 PE

13 SLCT

14 AUTOFD15 ERROR16 INIT17 SLCTIN-

18~25 PE

5-4. RS232 LOOP BACK CONNECTOR:

UKOG-6705RCZZ

Connected to the RS232 connector (D-SUB 9 pin: COM1, COM2,

COM3, COM4 ) of the UP-5350 and ER-A8RS, and used to check loop

signals when executing diagnostics.

• Connection diagram

CD 1pin

RD 2pin

TD 3pin

DTR 4pin

GND 5pin

DSR 6pin

RTS 7pin

CTS 8pin

RI 9pin

5-5. RS232 MODULAR JACK LOOP BACK

CONNECTOR: UKOG-6729BHZZ

Connected to the RS232 connector (RJ45: COM3, COM4, COM5,

COM6) of the UP-5350, and used to check loop signals when executing diagnostics.

• Connection diagram

RTS

1pin

DTR

2pin

TD

3pin

GND

4pin

GND

5pin

RD

6pin

DSR

7pin

CTS

8pin

5-3. MCR TEST CARD: UKOG-6718RCZZ

•

Used when executing the di agnostics of the UP-E12MR2.

• Externa l view

ER-A8RS

5-6. BIOS LOADING BOARD: CKOG-6727BHZZ

The BIOS load ing board: CKOG -6727BHZZ is a t ool to write a B IOS

ROM progra m in the F-RO M on the UP-5 350’s main b oard. Use thi s

PWB in the following cases:

• The F-ROM on the UP-5350’s main board becomes unreadable

and a BIOS ROM program must be written in the F-RO M.

• The BIOS ROM program in the F-ROM is overwritten due to the

BIOS ROM program of the version up, etc.

The BIOS load ing board is connecte d to the Option ROM/RAM dis k

connector (CN5) of the Main PWB.

• Externa l view

Page 19

• Plai n view

Writing BIOS ROM Program

NOTE: Remove all option boards from the ISA slots before writing on

the BIOS ROM.

1. Install the EP-ROM (master ROM): containing a BIOS program on

the BIOS loading board: CKOG-6727RCZZ.

BIOS MASTER ROM

LED1 LED2 LED3 LED4 LED5 LED6 LED7 LED8

SW1

13

Caution: The AC power must be removed prior to installing the

BIOS loading board.

• Connection diagram

Page 20

2. Set SW1 on the BIOS loading b oa rd to the side of pin 3. 3. Open the upper cabin et.

4. Connect the BIOS loading board to the option ROM/RAM connector CN5 on the main PWB , an d then close the cabinet.

LED1 LED2 LED3 LED4 LED5 LED6 LED7 LED8

SW1

5. Writing the BIOS ROM program starts by turning on the power

switch on the right side.

To determi ne the status of t he LED lights on the special serv ice

PWB when a BIOS ROM program is being written, see the table on

the next page.

Writing is complete (automatic completion) when the green LED

SW1

1

3

(LED9) on the BIOS load ing board lights up.

6. After writing is complete, turn off the power switch on the right side

to remove the BIOS loading board, and turn on the power switch

on the left si de ag ai n to c he ck whe the r th e BI OS pr o gra m st art s up

LED9

normally or not.

SW1

1

3

Page 21

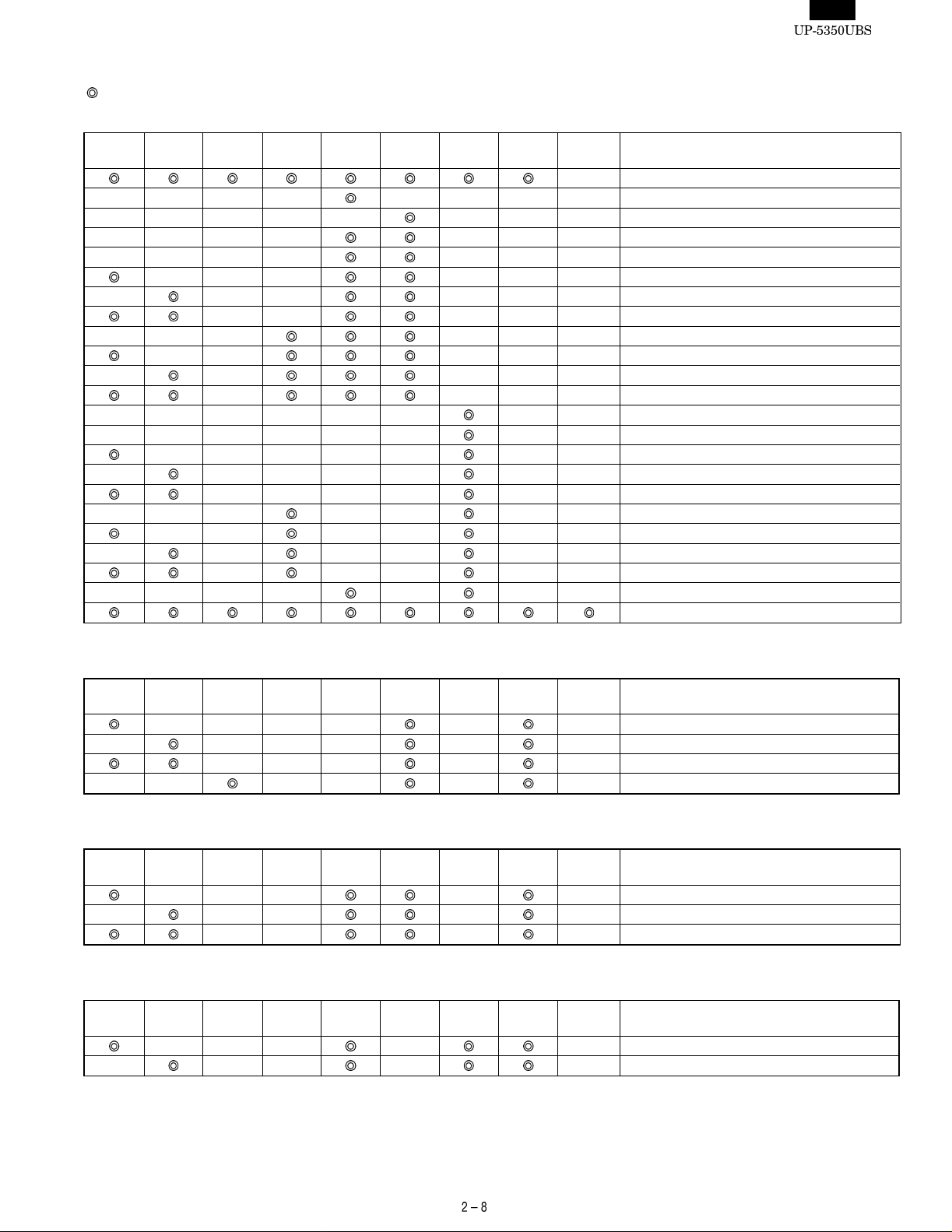

LED DISPLAY STATUS

[ : ON (Lighting) — : OFF]

<In normal operation>

LED1

(RED)

————

—————

————

————

—

———

—

——————

——————

—

———

—

————

LED2

(RED)

——— ———

—— — — — Programming: Bank1 D0000 h (64KB)

————— ——

—— —— — — Verifying: Bank1 D0000 h (64KB)

LED3

(RED)

—— — — — Programming: Bank0 E0000 h (64 K B)

—— ———

— ———

— ———

———— — — Verifying: Bank0 E0000 h (64KB)

———— — — Verifying: Bank0 F0000 h (64KB )

— —— — — Verifying: Bank1 E0000 h (64KB)

— —— ——

LED4

(RED)

LED5

(RED)

—— ——

LED6

(RED)

————

— ——

LED7

(RED)

— — — Erasing F-ROM (LED6: RED is blinking)

— — — Start copy programming to F-ROM from EP-ROM

———

———

LED8

(RED)

— — Start verifying the program in the F-ROM

— — Verifying: Bank0 C0000 h (64KB)

LED9

(GREEN)

— Start of COPY FUNCTION

Start initializing

Programming: Bank0 C 0000 h (64KB)

Programming: Bank0 D 0000 h (64KB)

Programming: Bank0 F 0 000 h (64KB)

Programming: Bank1 C 0000 h (64KB)

Programming: Bank1 E0000 h (64KB)

Programming: Bank1 F 0 000 h (64KB)

Verifying: Bank0 D0000 h (64 K B)

Verifying: Bank1 C0000 h (64 KB )

Verifying: Bank1 F0000 h (6 4KB )

Setting protection for F-ROM

END of complete COPY FUNCTION

FUNCTION

<Erase ERROR in F-ROM>

LED1

(RED)

—

——

<Programming ERROR in F-ROM>

LED1

(RED)

—

<Verifying ERROR in F-ROM>

LED1

(RED)

—

LED2

(RED)

———— — —

LED2

(RED)

——— — — Device not ready

LED2

(RED)

——— — —

LED3

(RED)

——— — — VPP error

——— — —

LED3

(RED)

—— — —

—— — — Command sequen ce error

LED3

(RED)

—— — — Can not release the protection

LED4

(RED)

—— — —

LED4

(RED)

LED4

(RED)

LED5

(RED)

LED5

(RED)

LED5

(RED)

LED6

(RED)

LED6

(RED)

LED6

(RED)

LED7

(RED)

LED7

(RED)

LED7

(RED)

LED8

(RED)

LED8

(RED)

LED8

(RED)

LED9

(GREEN)

LED9

(GREEN)

LED9

(GREEN)

FUNCTION

Device not ready

Command sequence e rror

FUNCTION

VPP error

FUNCTION

Device not ready while releasing the protection

Page 22

CHAPTER 3. SERVICE PRECAUTION

1. CONDITIONS FOR SOLDERING

CIRCUIT PARTS

To solder the fo ll ow ing pa rt s m anu al ly , fol lo w the co ndi ti on s d esc ri be d

below.

PARTS NAME PARTS CODE LOCATION CONDITIONS FOR SOLDERING

Ceramic oscillator

DIP SWITCH

TOUCH PANEL CONTROL PWB: X1 (8M) 270°C/3sec.

MAIN PWB: X2 (24M)

MAIN PWB: X2 (7.37M)

SWITCH PWB: S2 300°C/3sec.

2. CAUTIONS ON HANDLING CPU AND

POWER FAN

When removing or performing maintenance activities on the CPU and

POWER FAN, be sure to handle them with care, because it may

cause abnormal sounds or deteriorate th eir performance if th ey are

dropped or exposed to a heavy impact.

3. NOTE FOR HANDLING OF TOUCH

PANEL

• The transparency of the touch panel should be vitally important.

Use clean gloves and masks.

• For handling, do not hold the transparent area, and do not hold the

heat seal connector section to assure reliability.

• Do n ot o verl ay to uch panels. The edge ma y damage the surface.

• Do not place heavy things on the touch panel.

• Do not apply a strong shock, and do not drop it.

• When attaching the protection film again, carefully check for dirt. If

there is any dirt, it is transferred.

• To clean dirt on the surface, use a dry, soft cloth or a cloth im-

mersed in ethyl alcohol.

• Check that the housing does not give stress to the touch panel.

• Be care ful no t to to uch the touch panel with tools.

• Th e he at sea l se ctio n is easily disconnected. Be carefu l not to pl ace

stress to the heat seal section wh en installing.

• The touch panel is provided with an air groove to make the external

and the internal air pressure equal to each other. If water or oil is

put around the air groove, it may penetrate inside. Be careful to

keep the air groove away from water and oil.

• Do n ot u se sharp objects when making in pu t entrees.

4. NOTE FOR HANDLING OF LCD

• The LCD elements are made of glass. BE careful not to expose

them to strong mechanical shock, or they may be broken. Use

extreme care not to break them.

• If the LCD element is broken and the liquid leaks, avoid contact with

your mouth or eyes . If th e liq uid co mes in c ontac t with y our s kin or

clothes, immediately clean w ith soap.

• Use the unit under the rated conditions to prevent against damage.

• Be careful not to place water or o the r liquids on the display surface.

• The reflection plat e and the polarizing pl ate are easily scra tched.

BE careful not to touch them with a hard object such as glass,

tweezers etc. Never hit, push, or rub the surface with hard objects.

• When installing the unit, be careful not to apply stress to the LCD

module. If excessive stress is applied, abnormal display or uneven

color may result.

5. CAUTIONS ON HANDLING

CONNECTORS

When connec ti ng or d is c onn ec ti ng the fol l owi ng co nnec to r s, fol l ow th e

procedures below.

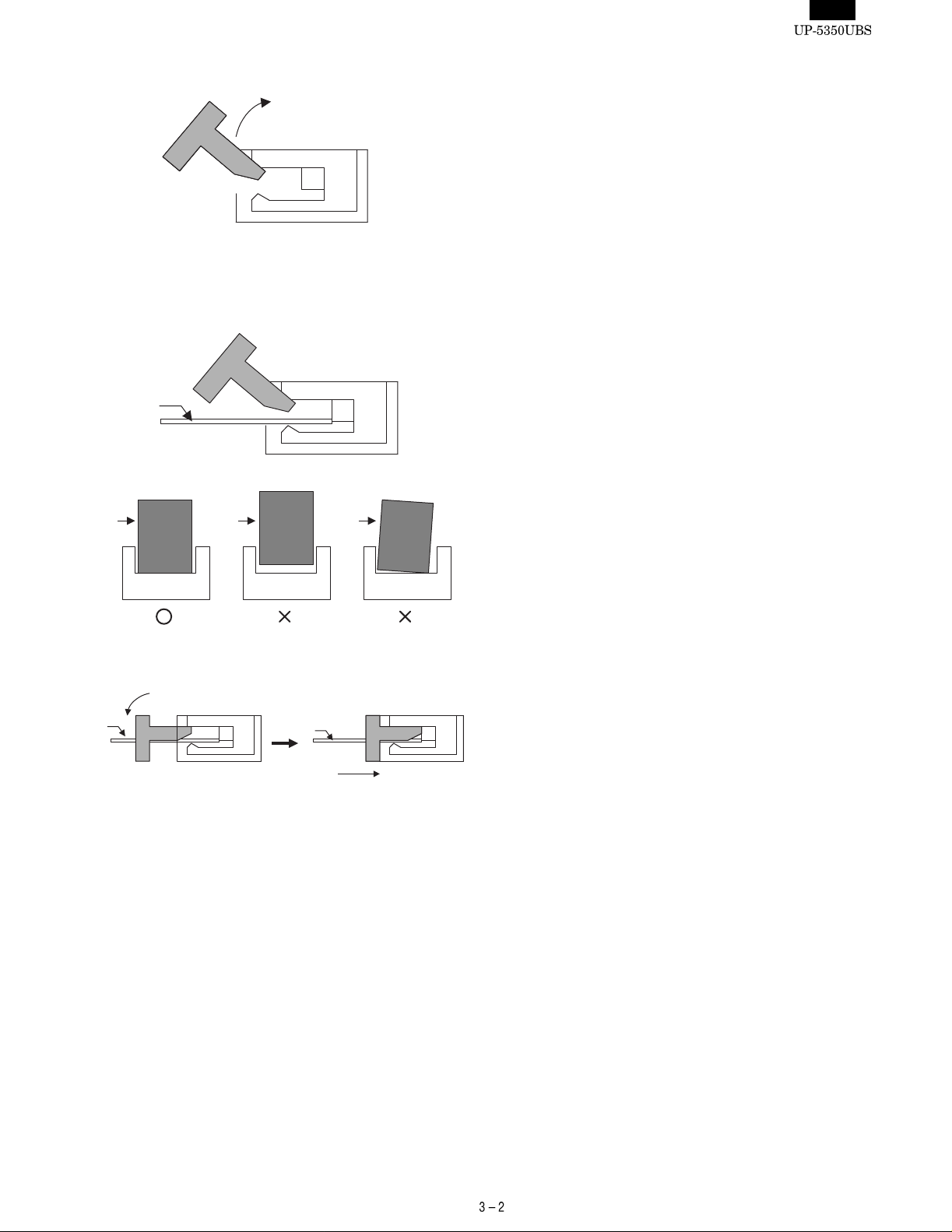

1)

PARTS NAME PARTS CODE LOCATION

FFC

CONNECTOR

How to insert FFC

(1) Pull the slider to the unlock position.

LCD RELAY

PWB: CN6

Page 23

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

-->

(2) Open the slider upwards.

(3) Inserting the FFC

Insert the FFC firmly until the FFC hits the bottom of the connector’s insulator.

FFC

FFC FFC FFC

CONNECTOR CONNECTOR CONNECTOR

(4) Close the slider to the lock position

FFC

FFC

6. PS2 Keyboard usable f or UP- 5 35 0

The UP-5350 can be e xtern al ly co nn ected to a keyboard.

The UP-5350’s key BIOS conforms to the PC standard, but this

BIOS’s operation is not compatible for some keyboards.

Some keyboards may cause operation errors due to delicate timing

and conflicts.

It is currently found that the following models of keyboards may malfunction.

When selecting a keyboard to be connected, test the keyboard in

advance to check that it correctly wo rks.

• Japa nese keyboard (106 keys)

Manufactured by IBM: TYPE/MODEL5576-B01 FRUPN66G0507

• English keyboard (101 keys)

Manufactured by NMB Technologies Inc.: Model: RT6651T+

Page 24

CHAPTER 4. UP-5350 DIAGNOSTICS SPECIFICATIONS

CONTENT

1. General ...................................................................................... 4-1

2. System configura tion .................................................................4-1

3. Service diagnostics ...................................................................4-1

3-1. Service diagnostics getting started .................................4-1

3-2. Selection menu ................................................................ 4-2

3-3. RAM Diagnostics ............................................................. 4-2

1) D-RAM Check ......................................................... 4-2

3-4. ROM Diagnostics ............................................................ 4-2

1) BIOS ROM Check ................................................... 4-2

3-5. Real time clock & CMOS RAM Diagnostics .................... 4-2

1) Real time clock Check ............................................4-2

2) CMOS RAM Check ................................................. 4-3

3-6. Touch Panel Diagnostics ................................................ 4-3

1) Controller Diagnostics Test .....................................4-3

2) Touch Key Pad Test ...............................................4-3

3) Linearity Test ........................................................... 4-3

3-7. Key Pad Diagnostics ....................................................... 4-4

1) Key Pad Check ....................................................... 4-4

3-8. Clerk Key Diagnostics ..................................................... 4-4

1) Clerk Key Check ..................................................... 4-4

3-9. Printer Diagnostics .......................................................... 4-4

1) PARALLEL1 Loop Check ....................................... 4-5

2) PARALLEL2 Loop Check ....................................... 4-5

3) PARALLEL3 Loop Check ....................................... 4-6

4) PARALLEL1 Print Check ........................................ 4-6

5) PARALLEL2 Print Check ........................................ 4-6

6) PARALLEL3 Print Check ........................................ 4-7

7) UP-T80BP Test ....................................................... 4-7

3-10. Serial I/O Diagnostics ......................................................4-7

1) COM1 Check .......................................................... 4-8

2) COM2 Check .......................................................... 4-8

3) COM3 Check .......................................................... 4-8

4) COM4 Check .......................................................... 4-8

5) COM5 Check .......................................................... 4-8

6) COM6 Check .......................................................... 4-8

3-11. Liquid Crystal Display Diagnostics .................................. 4-8

1) Liquid Crystal Display Check .................................. 4-9

3-12. Magnetic Card Reader Diagnostics .............................. 4-10

1) Magnetic Card Reader Check .............................. 4-10

3-13. System Switch Diagnostics ........................................... 4-10

1) System Switch ...................................................... 4-10

3-14. Drawer Diagnostics ....................................................... 4-10

1) Drawer 1 Check .................................................... 4-10

2) Drawer 2 Check .................................................... 4-11

3-15. Option Display Diagno stics ........................................... 4-11

3-16. IDE I/F & HARD DISK Diagnostics ............................... 4-11

[READ MODE TEST] .................................................... 4-11

1) Drive Status display .............................................. 4-11

2) Sequential Seek Test ............................................ 4-11

3) Random Seek Test ............................................... 4-12

4) Seek & Read Test ................................................. 4-12

5) Target Sector Read Test ...................................... 4-13

6) HD Dump Test ...................................................... 4-13

■ DIAGNOSTICS PROGRAM: CREATING AN

Before ex e cut i ng t he Di ag no st ic pr o gra m, cr e ate th e MS- DO S s ta r tin g

media and copy the Diagnostics program onto it.

How to create an MS-DOS starting media

1. GENERAL

This diagnostic program is used to check the PWB’s, the process, and

the machine of UP-5350 series in a simplified manner.

This test program is supplied with floppy di sks.

2. SYSTEM CONFIGURATION

The system requires the UP-5350, and a PS2 keyboard for diagnostic

operations.

3. SERVICE DIAGNOSTICS

3-1. SERVICE DIAGNOSTICS GETTING STARTED

Getting started:

Execute "S RV.BA T" by en teri ng the c ommand with th e PS2 keyb oard

as follows:

"A:\>" is the DOS prompt. (Used by the FD : Floppy disk based on the

settings of the system switches.)

7) Error lnformation Display .......................................4-14

8) Controller check Test ............................................4-14

[WRITE MODE TEST] ...................................................4-14

9) Seek&Write/Read-Verify Test ...............................4-14

10) Target Sector Write/Read-Verify Test ...................4-15

11) HD Patch Test (Utility) ...........................................4-15

12) Error Logging Area Clear ......................................4-15

13) Error table display ..................................................4-16

14) Other Supplemental Items .....................................4-16

15) Error Content .........................................................4-16

16) Error Information Storing Area Description ...........4-16

3-17. FDD Diagnostics ............................................................4-16

3-18. FAN & LCD ON/OFF Diagnostics ..................................4-17

1) FAN & LCD ON/OFF Check ..................................4-17

3-19. Power Hold Diagnostics .................................................4-17

1) Power Hold Check .................................................4-17

MS-DOS STARTING MEDIA (FD)

1) Execute the command given below on the PC where the MS-

DOS Ver. 6.22 is running and create an MS-DOS starting media (FD).

MS-DOS (Command) format a: /s

2) Copy the Diagnostics program onto the MS-DOS starting media

(FD).

A:\> SRV

Do not load any device drivers when using this program.

To operate other ap pl ic at io ns af te r perf o rm in g thi s prog r am, re - boot

the machine.

Page 25

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

-->

3-2. SELECTION MENU

The diagnost ics menu is s tarted and t he followin g menu is dis played.

The highlighted cursor is moved by the cursor keys (UP

) of the PS2 keyboard. Move the cursor to the desired item, and

press the Enter key to execute the selected diagnostics program.

When the selected diagnostics program is completed, the display returns to t he menu scr een by pre ssing the E SC key. Se lect "Dia gnostics End" and press the Enter ke y to te rm inate the diagnostics.

SHARP PC-POS System Diagnostic Series III

Diagnostics for Service

RAM Diagnostics

ROM Diagnostics

Real time clock & CMOS RAM Diagnostics

T ouch Panel Diagnostics

Key Pad Diagnostics

Clerk Key Diagnostics

Printer Diagnostics

Serial I/O Diagnostics

LCD (Liquid Crystal Display) Diagnostics

MCR (Magnetic Card Reader) Diagnostics

System Switch Diagnostics

Drawer Diagnostics

Option Display Diagnostics

IDE I/F & Controller Diagnostics

FDD Diagnostics

FAN&LCD ON/OFF Diag nos tics

Power Hold Diagnostics

Diagnostics End

and DOWN

Version 1.00B

are not displayed.)

Terminating method

After completion of the test, press Esc key to terminate and return

to the service diagnostics menu .

3-4. ROM DIAGNOSTICS

The BIOS ROM, is tested.

1) BIOS ROM CHECK

Checking content

The BIOS ROM version is displayed.

Display

BIOS ROM Check

Version - ROM : SHPUP****

The version is displayed.

Terminating method

After the test result is displayed, press Esc key to terminate and

return to the service diagnostics menu.

3-3. RAM DIAGNOSTICS

This progr am is used to test t he standard memory and t he extensi on

memory.

1) D-RAM CHECK

Checking content

All memory areas are checked in blocks of 64KB. The checking

procedures are as follows:

i. Test data 5555H is written to all the test areas.

ii. Test data and read data are compared by each word, If it is

O.K., test data AAAAH is written to the test area.

iii. Test data and read data are compared by each word, If it is

O.K., test data 5555H is written to the test area .

iv. Test data 0000 H is written to all the test areas.

v. Test data and read data are compared by each word, If it is

O.K., test data FFFFH is written to the test area.

vi. Test data and read data are compared by each word, If it is

O.K., test data 0000H is written to the test area .

When an error occurs during the test, the error address and data

are displayed and the test is stop pe d.

For the extended memory test, the value set in the setup of read

and test and is made to the area in incre m en ts of 64KB.

Display

D-RAM Check

Main memory size : 640KB PASS !!(or ERROR !!)

Extended memory size : xxxxKB PASS !!(or ERROR !!)

Error Address xxxxxxH Write Data xxxxH Read Data xxxxH

3-5. REA L TIME C L OCK & CMOS RAM DIAG NOSTIC S

RTC and CMOS RAM check is performed.

The followin g menu is disp layed. The hi ghlighted cur sor is moved by

the cursor keys (UP

cursor to the desired item, and then press the Enter key to execute the

selected diagnostics program. When the selected diagnostics prog ram

is completed. Pressing Esc key again returns to the service diagnostics menu.

Real time clock & CMOS RAM Diagnostics

Real time clock Check

CMOS RAM Check

1) REAL TIME CLOCK CHECK

Checking content

RTC timer function and RTC clock function are tested.

In RTC timer check, the RTC timer is set so that an interrupt is

generated after 2 sec and checked that the interrupt is performed

properly. In RTC clock check, the RTC clock is set to 23:59:58,

31/Dec/1989, and checks that the clock shows 0:0:0, 1/Jan/1990

after 2 sec.

Display

Real time clock Check

RTC Timer Check : PASS !!(or ERROR !!)

RTC Clock Check : PASS !!(or ERROR !!)

and DOWN ) of the PS2 keyboard. Move the

When testi ng the exte nsion me mory siz e, the val ue of the exi sting

memory is displayed. The error address and the error data are

displayed only when an error occurs. (When no errors occur, they

Terminating method

After the test result is displayed, press Esc key to terminate and

return to the RTC and C M OS RAM diagnostics menu.

Page 26

2) CMOS RAM CHECK

Checking content

The read/wri te check is performed for CMOS-RAM wh en setting

up. The checking procedure is as follows:

i. Test address data is saved to the main memory.

ii. Test data 55H is written to the test address.

iii. Te st data and read data are compared , and test data AAH is

written to the test address.

iv. Test data an d re ad data are compared.

v. The saved test data is written to th e test area.

vi. The addre ss is incre m ented until it becomes 3FH.

If POFF interruption is generated during the test, the test is

stopped and the saved data is w ritten to the test area within 50ms.

Display

CMOS-RAM Check

RTC RAM Check : PASS !!(or ERROR !!)

Error Address xxxxxH Write Data xxH Read Data xxH

The error address and t he error bit are di splayed only when an

error occurs. (When no error occu rs, they are not displayed.)

Terminating method

After the test result is displayed, press Esc key to terminate and

return to the RTC and C M OS RAM diagnostics menu.

3-6. TOUCH PANEL DIAGNOSTICS

The touch pane l and its contr oller are chec ked. Communicat ion with

the controller is performed by 8250 built in the gate array PSC2.

The controller diag check, the touch keypad test, and the linearity test

are performed.

The initial display is as follows:

Return code Content

0Ah ROM error

0Bh RAM error

0Ch Panel voltage error

0Dh Reserve

0Eh EPROM write error

0Fh EPROM read error

10h EPROM check sum erro r

Display

Controller Diag Test

Pass!!

ROM Error!!

or

RAM Error!!

PANEL Voltage Error!!

EPROM Write Error!!

EPROM

EPROM SUM Error!!

Error!!

Error!!

Read Error!!

Terminating method

After the test result is displayed, press the Esc key to terminate

and return to the Touch pa nel diagnostics menu.

2) TOUCH KEY PAD TEST

Checking content

The driver function call is used.

ners of the LCD sequentially.

(In the sequence of uppe r right, u pp er left, low er left, low er righ t.)

When the

the screen turns to

is touched by the operator, the buzzer sounds and

.

Display

Touch Key Pad Test

Touch Cursor !!

is displayed at the four cor-

Touch Panel Diagnostics

Controller Diag Test

Touch Key Pad Test

Linearity

1) CONTROLLER DIAGNOSTICS TEST

Checking content

After initializing the controller, the diagnostic command is exe-

cuted. The procedures are as follows:

• One byte of sample data (FFh) is sent and a wait state of 100ms

is made.

• The re set command ( 80h) is sen t and a wait stat e for the end

code (2 bytes: 90h and 00h) fro m the controller is made.

• The di agnostic command ( 2 bytes: 89h, any o ne-byte data) is

executed, and a wait state f or the end code (3 bytes: 90h, return

code, any one-byte data) is made.

• If an error occurs the error display is made with the return cod e.

To exit from the controller diagnostic test, press the Esc key

during the wait state for the end code response.

Terminating method

Touch all four

or press the Esc key to terminate and return to

the Touch panel diagnostics menu.

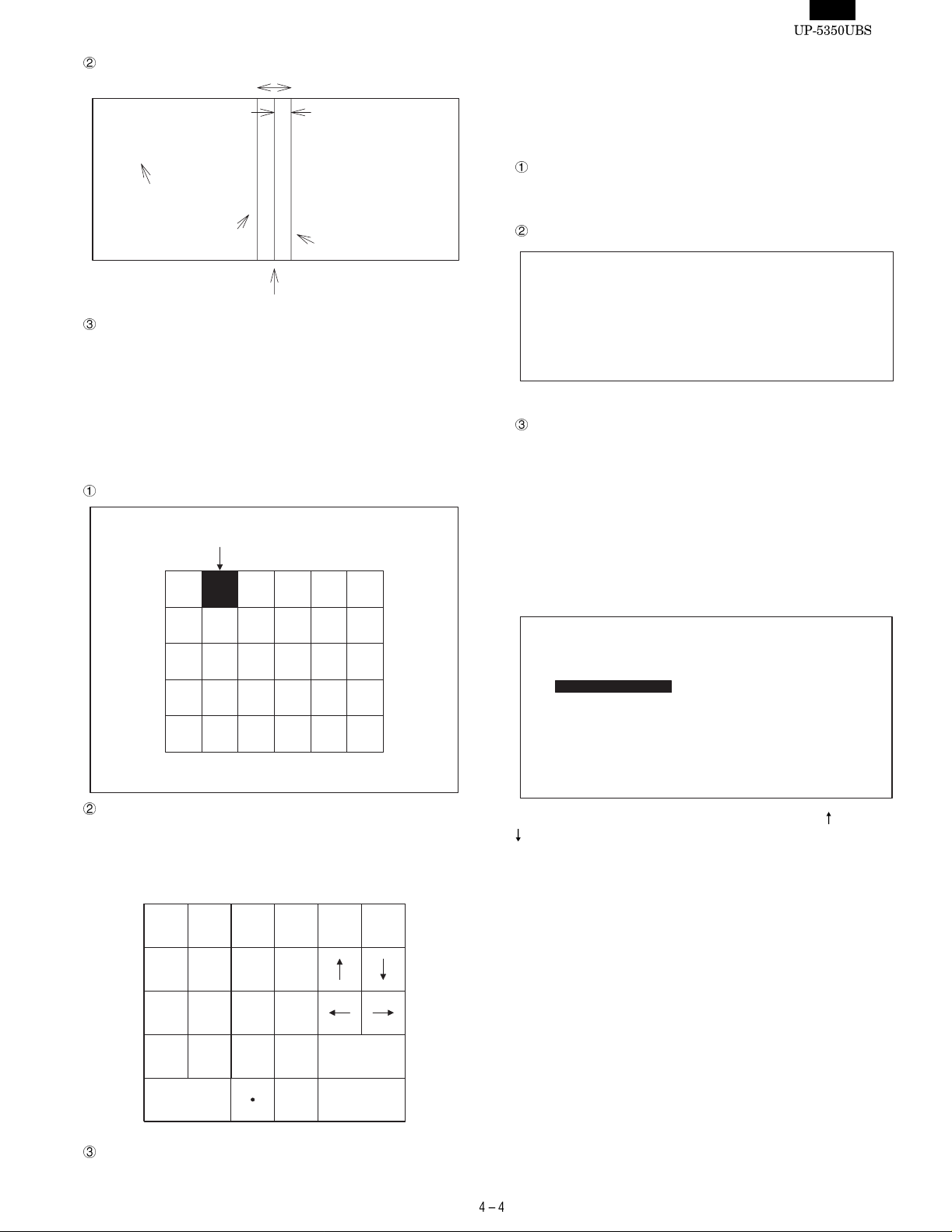

3) LINEARITY TEST

Checking content

Red lines ar e di spl aye d at bo th si des of th e blu e li ne at th e cent er.

The operator must touch the blue line without touching the red lines

and drag from top to bo ttom.

The touched part of the bl ue line is ch anged to white.

If the red line is touched, an erro r messa ge is issued.

Page 27

Display

About 2cm

Linearity

Test

Complete!

(Error!!)

Displayed after termination.

Red line

Blue line

About 1cm

Red line

Terminating method

Press Esc k ey to t e rmi nat e an d r et urn to t h e Touc h pa ne l d ia gnos -

tics menu.

3-8. CLERK KEY DIAGNOSTICS

(Not used for "U/B" models)

The clerk key input test is performed.

Pressing the Esc key returns to the se rvicem an diagnostics menu.

1) CLERK KEY CHECK

Checking content

Key code inserted to the clerk key switch which is then displayed in

a decimal value.

Display

Clerk Key Check

Clerk Key Code : xx

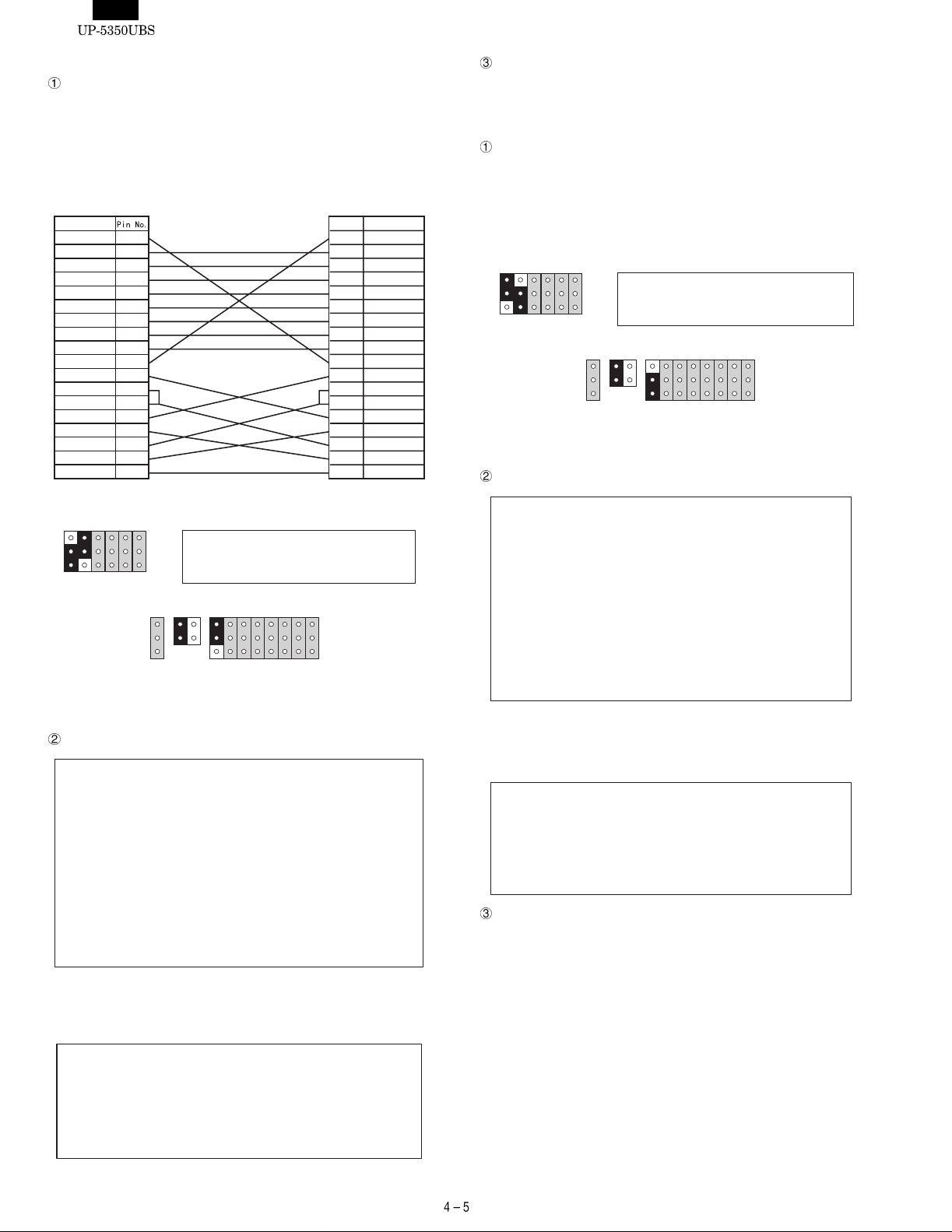

3-7. KEY PAD DIAGNOSTICS

1) KEY PAD CHECK

The UP-C30PK k ey test is per formed. I n the UP-C30 PK, key s are

detected by matrix scan of KBC (M 38 80 2M 270).

Display

Key Pad Diagnostics

When this is pressed, the buzzer sounds

and the color changes.

ESC

Press ESC key to exit.

Content

When a key is pressed, its color changes and the key catch sound

is made.

The keys to be checked an d th ei r po sitions are as shown below.

ESC

F4

F5

F10 Delete

Back

Space

The clerk code is displayed at XX.

Terminating method.

Press the Esc key to terminate and return to the service diagnos-

tics menu.

3-9. PRINTER DIAGNOSTICS

The parallel interface (standard) and ER-A8RS parallel interface (option) are tested.

Here, the parallel interface on the main body is mentioned as PARALLEL1, and the parallel interface on ER-A8RS as PARALLEL 2/3.

The following menu is displayed.

Printer Diagnostics

Standard Option(ER-A8RS)

PARALLEL 1 Loop Check

PARALLEL 1 Print Check

Option(UP-T80BP)

Print Check ALLEL3 Print Check

The highlighted cursor is moved by the cursor keys (UP

) on the PS2 keyboard. Move the cursor to the desired item and

press the Enter key to execute the selected diagnostics program.

When the selected diagnostics program is completed, the display re-

turns to the menu screen. Pressing the Esc key returns to the service

diagnostics menu.

P ARALLEL2 Loop Check

P ARALLEL3 Loop Check

P ARALLEL2 Print Check

PAR

and DOWN

Tab

9

8

7

L-Shift

6

5

4

L-Ctrl

3

2

1

0

L-Alt

End

Press the ESC key to terminate the test.

Space

Enter

Page 28

1) PARALLEL1 LOOP CHECK

Checking content

A loop check is made for the standard I/O address 378H ~ 37FH.

(PARALLEL1)

In the lo op check, a nor mally-oper ating ER-A8R S is inserted and

the loop c able (U KOG-6717 RCZZ) is c onnecte d between P ARALLEL1 and PAR ALLEL3 ( ER-A8 RS) for testing . Set th e jumper s on

the PWB prior to the test as follows:

Signal name

STROBE-

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

ACKBUSY

PE

SLCT

AUTOFD-

ERROR-

INIT-

SLCTIN-

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18~2

Loop cable (UKOG-6717RCZZ) wiring diagram

J3J8J4J5J6

J7

10

UP-5350 : PARALLEL1 OUTPUT MODE

A8RS : PARALLEL3 INPUT MODE

J9

J10

I

L

H

57

O

J18

Opposite ER-A8RS setting

Jumper pin setting diagram

Display

PARALLEL1 Loop Check

ACK- Signal : PASS !!(or ERROR !!)

BUSY Signal : PASS !!(or ERROR !!)

PE Signal : PASS !!(or ERROR !!)

SLCT Signal : PASS !!(or ERROR !!)

ERROR- Signal : PASS !!(or ERROR !!)

STROBE- Signal : PASS !!(or ERROR !!)

AUTOFD- Signal : PASS !!(or ERROR !!)

INIT- Signal : PASS !!(or ERROR !!)

SLCTIN- Signal : PASS !!(or ERROR !!)

INTERRUPT : IRQ X (or ERROR !!)

DATA Bus : PASS !!(or ERROR !!)

J11

J12

J13

J14

J15

J16

J17

18~2

12

Signal namePin No.

1

STROBE2

3

4

5

6

7

8

9

10

11

12

13

14

AUTOFD-

15

ERROR-

16

INIT-

17

SLCTIN-

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

ACKBUSY

PE

SLCT

GND

Terminating method.

Press the Esc key to terminate and return to the Printer diagnostics

menu.

2) PARALLEL2 LOOP CHECK

Checking content

A loop check is perf orme d for E R-A8RS I/O ad dres s 278H ~ 27 FH

(PARALLEL2).

In the loop check, the loop cable shown in Fig, 3-4 is connected

between PARALLEL2 (ER-A8RS) and PARALLEL1 for testing. Set

the jumpers on the PWB prior to the te st as sh own in Fig. 3-6.

J3J8J4J5J6

Display

PARALLEL2 Loop Check

ACK- Signal : PASS !!(or ERROR !!)

BUSY Signal : PASS !!(or ERROR !!)

PE Signal : PASS !!(or ERROR !!)

SLCT Signal : PASS !!(or ERROR !!)

ERROR- Signal : PASS !!(or ERROR !!)

STROBE- Signal : PASS !!(or ERROR !!)

AUTOFD- Signal : PASS !!(or ERROR !!)

INIT- Signal : PASS !!(or ERROR !!)

SLCTIN- Signal : PASS !!(or ERROR !!)

INTERRUPT : IRQ X (or ERROR !!)

DATA Bus : PASS !!(or ERROR !!)

The inter r uption le v e l is displa y e d at XX.

If no access is allowed to PARALLEL2, the following display is

made.

PARALLEL2 Loop Check

Terminating method.

Press the Esc key to terminate and return to the Printer diagnostics

menu.

J7

10

UP-5350 : PARALLEL1 INPUT MODE

J9

J10

L

H

57

O

Setting of ER-A8RS to be tested

Fig. 3-6 Jumper pin setting

PARALLEL2 Channel Disabled

A8RS : PARALLEL2 OUTPUT MODE

I

12

J18

J11

J12

J13

J14

J15

J16

J17

The inter r uption le v e l is displa y e d at X.

When no ac cess is allo wed to PARALLEL1, the following display is

made.

PARALLEL1 Loop Check

PARALLEL1 Channel Disabled

Page 29

3) PARALLEL3 LOOP CHECK

Checking content

A loop check is performed for ER-A8RS I/O address 3BCH ~

3BEH (PARALLEL3).

In the loop check the ER-A8RS is connected to the extension slot

and the loop cable shown in Fig. 3-4 is connected between PARALLEL3 (ER -A8RS) and PAR ALLEL1 for te sting. Set t he jumpers

on the PWB prior to the test as show n in Fig. 3 -6.

J3J8J4J5J6

Display

J7

10

UP-5350 : PARALLEL1 OUTPUT MODE

A8RS : PARALLEL3 INPUT MODE

J10

J9

I

L

H

57

O

J18

J11

J12

J13

Setting of ER-A8RS to be tested

Fig. 3-6 Jumper pin setting

J14

J15

J16

12

J17

Display

PARALLEL1 Print Check

PARALLEL1 Channel Disabled

"PARALLEL1 Channel Disabled" is displayed only when no access

to PARALLEL1 is allowed.

Terminating method.

Press the Esc key to terminate and return to the Printer diagnostics

menu.

5) PARALLEL2 PRINT CHECK

Checking content

The print check is performed for PARALLEL2 at I/O address 278H

~ 27Fh on the ER-A8RS.

In the print check, set the short pin of the ER-A8RS to be tested as

shown in Fig. 3-9, and connect the D- Sub 25 pin connector to a

printer to allow a print pattern test.

PARALLEL3 Loop Check

ACK- Signal : PASS !!(or ERROR !!)

BUSY Signal : PASS !!(or ERROR !!)

PE Signal : PASS !!(or ERROR !!)

SLCT Signal : PASS !!(or ERROR !!)

ERROR- Signal : PASS !!(or ERROR !!)

STROBE- Signal : PASS !!(or ERROR !!)

AUTOFD- Signal : PASS !!(or ERROR !!)

INIT- Signal : PASS !!(or ERROR !!)

SLCTIN- Signal : PASS !!(or ERROR !!)

INTERRUPT : IRQ X (or ERROR !!)

DATA Bus : PASS !!(or ERROR !!)

The inter r uption le v e l is displa y e d at XX.

If no access is allowed to PARALLEL3, the following display is

made.

PARALLEL3 Loop Check

PARALLEL3 Channel Disabled

Terminating method.

Press the Esc key to terminate and return to the Printer diagnostics

menu.

4) PARALLEL1 Print Check

Checking content

The print check is performed for the standard port PARALLEL1 at

I/O address 378H ~ 37FH. In the print check mode the D-Sub 25

pin connector is connected with a printer to allow a print pattern

test.

The test procedures are as follows:

i. Data of 55H is written to I/O address 378H, and the same

address is read. If the read data is not 55H, "PARALLEL1

Channel Disa bled" is displ ayed and the followi ng check is not

performed.

ii. C harac ters of 20H ~ 7FH (AS CII co de) are pr inte d and the l ine

is changed.

This procedure is repeate d fo r 5 ti m es.

J3J8J4J5J6

J7

10

J10

J9

L

H

57

I

O

J18

J11

J12

J13

J14

J15

J16

12

J17

Fig. 3-9 Jumper pin setting

The test procedures are as follows:

i. Data of 55H is written to I/O address 278H, and the same

address is read. If the read data is not 55H, "PARALLEL2

Channel Disa bled" is displ ayed and the followi ng check is not

performed.

ii. C harac ters of 20H ~ 7FH (AS CII co de) are pr inte d and the l ine

is changed.

This procedure is repeate d fo r 5 ti m es.

Display

PARALLLEL2 Print Check

PARALLEL2 Channel Disabled

"PARALLEL2 Channel Disabled" is displayed only when no access

to PARALLEL2 is allowed.

Terminating method.

Press the Esc key to terminate and return to the Printer diagnostics

menu.

Page 30

6) PARALLEL3 PRINT CHECK

Checking content

The print check is performed for PARALLEL3 at I/O address 3BCH

~ 3BEh on the ER-A8RS.

In the print check, set the short pin of the ER-A8RS to be tested as

shown in Fig. 3-10, and connec t the D-Sub 25 pin c onnector to a

printer to allow a print pattern test.

Testing

The followin g patterns are p rinted and the p aper cut command is

sent by th e specified number of times to the Se rial output of I/O

address 980H to 987H.

J3J8J4J5J6

J7

10

J10

J9

L

H

57

I

12

O

J18

J11

J12

J13

J14

J15

J16

J17

Fig. 3-10 Jumper pin setting

The test procedures are as follows:

i. Data of 55H is written to I/O address 3BCH, and the same

address is read. If the read data is not 55H, "PARALLEL3

Channel Disa bled" is displ ayed and the followi ng check is not

performed.

ii. C harac ters of 20H ~ 7FH (AS CII co de) are pr inte d and the l ine

is changed.

This procedure is repeate d fo r 5 ti m es.

Display

PARALLEL3 Print Check

PARALLEL3 Channel Disabled

"PARALLEL3 Channel Disabled" is displayed only when no access

to PARALLEL3 is allowed.

Terminating method.

Press the Esc key to terminate and return to the Printer diagnostics

menu.

7) UP-T80BP TEST

Display

Print Check

Count ? = 01 (00-99)

Pass Count = XX

Hit ESC Key to Stop

On the above screen the setting appears in the box.

The Count can be set from "01" up to "99". If "00" is set, printing

does not stop until the ESC key is pressed.

YOUR RECEIPT

THANK YOU

Error message

The following error message appears if a communication error

occurs with the UP-T80BP.

Print Check

CD 1pin

RD 2pin

TD 3pin

DTR 4pin

GND 5pin

DSR 6pin

RTS 7pin

CTS 8pin

RI 9pin

RTS

1pin

DTR

2pin

TD

3pin

GND

4pin

GND

5pin

RD

6pin

DSR

7pin

CTS

8pin

********************

UP-T80BP I/F ERROR

Hit ESC Key to Stop

End of testing

The testing is fi nishe d afte r pri nting is made by the s pecif ied num-

ber of times or by pressing the ESC ke y.

3-10. SERIAL I/O DIAGNOSTICS

The serial interface of UP-5350 and the option PWB ER-A8RS is

performed. To test the 9pin D-Sub port, connect the D-Sub loop back

connector (UKOG-6705RCZZ).

To test the RJ45 port, connect the loop back connector (UKOG6729BHZZ).

Loop back connector (UK OG-6705RCZZ) wiring diagra m

Loop back connector (UKOG-6729BHZZ) wiring diagram

The UP-535 0’s 9-pin D-sub port s are used as COM1 and 2. In a ddition, th e UP-5350’s RJ45 ports are use d as COM3 and 4 or CO M5

and 6 accor di ng t o t he set up. O n th e o the r ha nd , E R-A 8RS i s us e d by

selecting either COM1 and 2 or COM3 and 4 according to the setup.

Therefore , when an ER-A8 RS is us ed, yo u must s et COM1 , 2, 5, an d

6 on the UP-5350 side, and set COM3 and 4 on the ER-A8RS side.

Page 31

The following menu is displayed.

The highlighted cursor is moved by the cursor keys (UP

and DOWN

) of the PS2 keyboard. Move the cursor to the desired item, and

press the Enter key to execute the selected diagnostics program.

When the selected diagnostics program is completed, the display re-

turns to the menu screen. Pressing the Esc key returns to the service

diagnostics menu.

Serial I/O Diagnostics

COM1 Check

COM2 Check

COM3 Check

COM4 Check

COM5 Check

COM6 Check

1) COM1 Check

Content

The loop back check is performed for the UART at I/O address

3F8H ~ 3FFH. The test procedures are as follows:

i. UART setting is made. If access is denied to UART at that time,

"COM1 Disa bled" is displayed a nd the following check is not

performed.

ii. RTS signal is turned on/off to check that CD, CTS signal is

normally operating. In case of any abnormality, ERROR is displayed.

iii. DTR signal is turned on/off to check that DSR, RI signal is

normally operating. In case of any error, ERROR is displayed.

When an error occurs in procedure i or ii, the following test is

not performed.

iv. Set the baud rate to 19200bps asynchronous. 256 byte data of

00H ~ FFH is transmitted from SD signal. Data received at RD

signal is compared to check that the both are the same. If the

output data is not returned for 5 sec or more, an ERROR is

displayed and the test is terminated.

v. An interruption signal is issued from UART and the number of

generated interruption re quest signal is displayed.

Display

Serial I/O COM1 Check

RTS - CD : PASS !!(or ERROR !!)

RTS - CTS : PASS !!(or ERROR !!)

DTR - DSR : PASS !!(or ERROR !!)

DTR - RI : PASS !!(or ERROR !!)

TD - RD : PASS !!(or ERROR !!)

INTERRUPT : IRQ XX

The number of the interruption request signal is displayed at XX.

If no access is allowed to COM1 UART, the following display is

made.

Serial I/O COM1 Check

COM1 Channel Disabled

Terminating method.

Press the Esc key to terminate and return to the Se rial I/O diag nos-

tics menu.

2) COM2 CHECK

Checking content

The loop back check is performed for the UART at I/O address

2F8H ~ 2FFH. The ch eck p roc edu r e, t he d is pl ay , an d the ter min at ing method are the same as COM1 Check.

3) COM3 CHECK

Checking content

The loop back check is performed for the UART at I/O address

3E8H. When t he E R-A 8 RS i s as s i gned t o COM 3, t he ch eck pr oc edure, display and terminating m eth od are the same as COM1.

When the RJ-45 port of the UP-5350 main unit is assigned to

COM3, the following points are different from COM1 Check :

Content

• RTS-CTS is not checked.

• DTR-RI is not checked.

Display

• RTS-CTS is not displayed.

• DTR-RI is not displayed.

COM3 is checked as well as COM1 except at the above 2 points.

4) COM4 CHECK

Checking content

The loop back check is performed for the UART at I/O address

2E8H ~ 2EFH. The check procedu re, the display, and the terminating method are the same as COM3 Check.

5) COM5 CHECK

Checking content

The loop back check is performed for the UART at I/O address

(PSC2 base address) + (410 H ~ 417H). The foll owing points are

different from the COM1 Check:

Content

• RTS-CTS is not checked.

• DTR-RI is not checked.

Display

• RTS-CTS is not displayed.

• DTR-RI is not displayed.

COM5 is checked as well as COM1 except at the above 2 points.

6) COM6 CHECK

Checking content

The loop back check is performed for the UART at I/O address

(PSC2 base address) + (418H ~ 41FH). The checking procedure,

the displa y, and the terminati ng method are the same as CO M5

Check.

3-11. LIQUID CRYSTAL DISPLAY DIAGNOSTICS

LCD test is performed.

The following patterns are displayed in sequence. Pressing the space

bar proceeds to the next display. Pressing the space bar at the final

pattern or pressing the Esc key during the test, will return the display

to the service diagnostics menu .

Page 32

1) LIQUID CRYSTAL DISPLAY CHECK

Checking content

The test patterns are displayed in the following test procedures.

Pressing the space bar moves to the next pattern.

i. Black-and-white pattern in 1 dot interval

ii. Reversed pattern of pattern i.

iii. Vertical stripe pattern in 1 dot interval

vii. " H" pattern (80 digits x 35 lines) In the 35th line, only 78 digits

of "H" are displayed.

(The actual display range is 25 lines. Scroll for 10 lines to

check.)

HHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHH

HHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHHH

viii.Gradation pattern fro m black to white in 16 gradations

iv. Reversed pattern of pattern iii.

v. Horizontal stripe pattern in 1 d ot inte rval

vi. Reversed patte rn of pattern v.

ix. All white patter n

x. Color bar (16 colors)

Color bars of 16 colors are displ aye d.

Black

Blue

Green

Cyan

Red

Brown

White

Magenta

Gray

Light green

Light blue

Light cyan

Light red

Light magenta

Light yellow

xi. Color pattern (256 colors)

Color pattern of 256 colors is displayed. The displayed colors

are the default pallet.

Arrange RAMDAC register No. 0 ~ 255 from the upper left.

Light white

xii. Backlight OFF

The backlight is turned off without turning off the display.

xiii.Backlight ON

Page 33

Terminating method

Press the space bar or Esc key to terminate and return to the

service diagnostics menu.

Terminating method

Press the Esc key to terminate the test and return to the service

diagnostics menu.

3-12. MAGNETIC CARD READER DIAGNOSTICS

This test progr am r ead s the m agnet ic card based on the ISO7 811/1 -5

standard and displays the d ata .

Pressing the Esc key returns to the se rvice di agnostics menu.

1) MAGNETIC CARD READER CHECK

Checking content

The test program reads tracks 1 and 2 of the magnetic card

(UKOG-6718RCZZ) based on the ISO7811/1 ~ 5 standard, and

displays the data in ASCII code. There are two kinds of data patterns to be read.

TRACK 1: IATA pattern