Page 1

CONFIDENTIAL DRAFT

q

SERVICE MANUAL

by Toko (toko@gsm-free.org)

MOBILE PHONE

MODEL

(INTERNAL MODEL NAME:

G : For Germany

E : For U.K.

AT : For Austria

• In the interests of user-safety the set should be restored

to its original condition and only parts identical to those

specified should be used.

Caution:

Risk of explosion if batter y is rep laced by an i ncorr ect typ e,

dispose of used batteries ac cording t o the inst ructi on.

TM100

TM100G/E/AT/CZ/H/B)

CZ : For Czechoslovakia

H : For Netherlands

B : For Hungary

CONTENTS

SERVICING CONCERNS

CHAPTER 1. GENERAL DESCRIPTION

[1] Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

[2] Names of parts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

[3] Operation manual . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

CHAPTER 2. ADJUSTMENTS, PERFORMANCE CHECK,

AND FIRMWARE UPGRADE

[1] SHARP Program Support Tool (SPST) . . . . . . . . . . . . . . . . . . . 2-1

[2] Test points . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-22

[3] Trouble shooting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-27

CHAPTER 3

CHAPTER 4. DIAGRAMS

CHAPTER 5. CIRCUIT DIAGRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

CHAPTER 6. WAVEFORMS OF CIRCUIT

CHAPTER 7. OTHERS

Parts Guide

. DISASSEMBLY AND REASSEMBLY

[1] Disassembly and reassembly . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

[1] BLOCK DIAGRAM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

[1] WAVEFORMS OF CIRCUIT . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

[1] IC/LSI PIN LIST AND CONNECTOR PIN LIST. . . . . . . . . . . . . 7-1

Parts mark ed w ith "!" are important for maintaining the safety of the set. Be sure to replace these parts with specified

ones for maintaining the safety and performance of the set.

This document has been pub lished to be used

SHARP CORPORATION

for after sales service only.

The contents are subject to change without notice.

Page 2

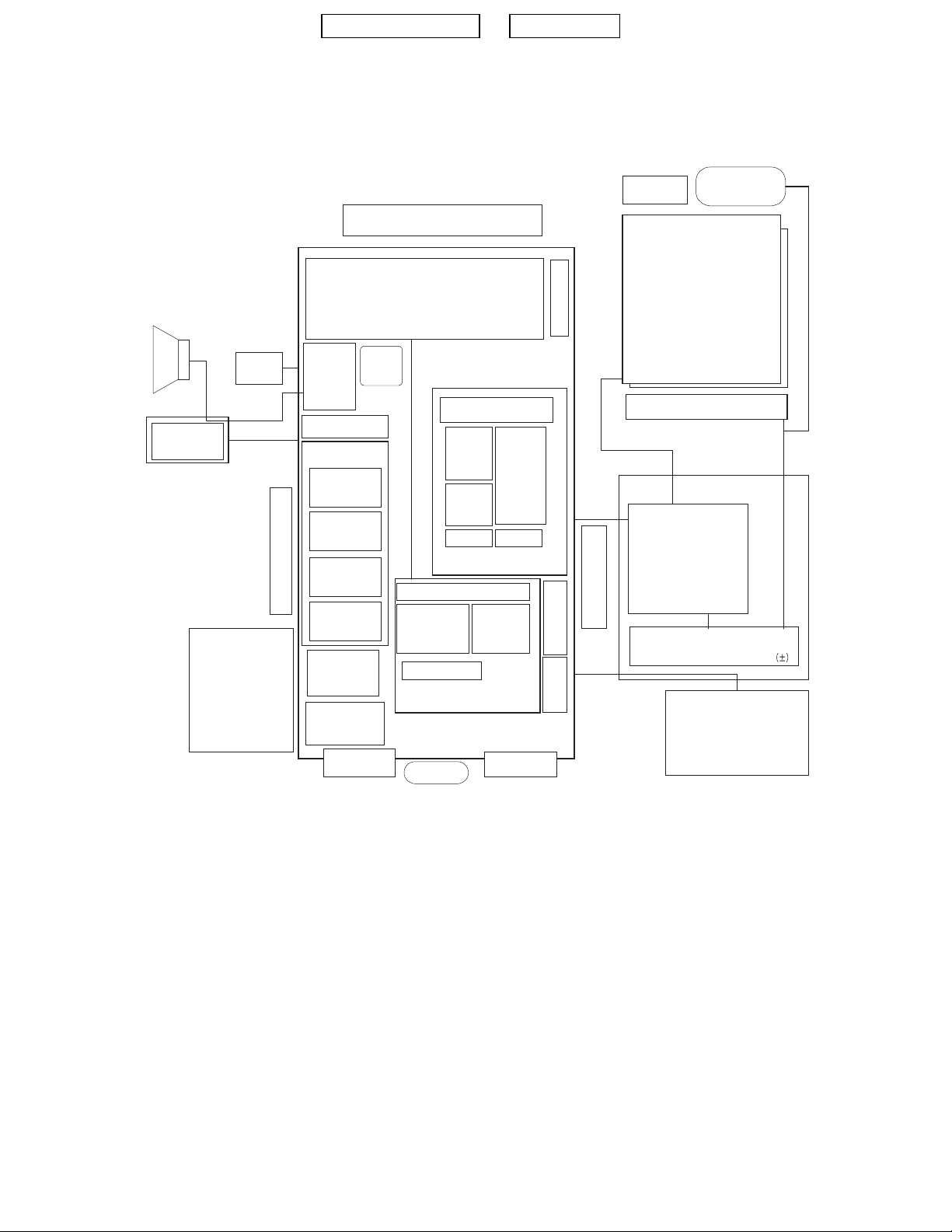

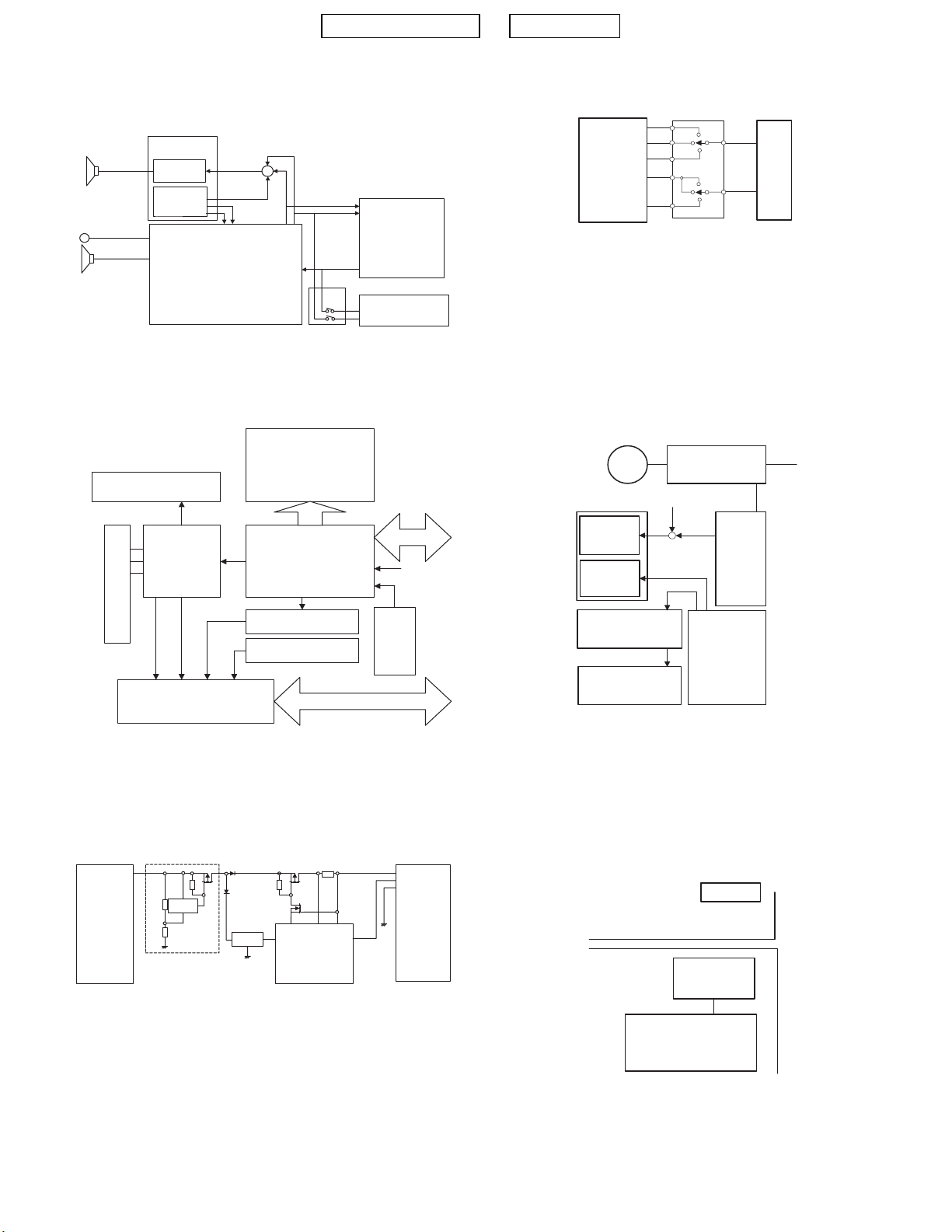

CHAPTER 4. DIAGRAMS

[1] BLOCK DIAGRAM

CONFIDENTIAL DRAFT

CCD Camera

Vib

motor

Lithum Ion

Battery

Pack

Sound

Audio

YM762

SIM Card

Memory IC

LRS1B27

Super AND

Flash-ROM

128Mbit

NOR Flash-ROM

128Mbit

PS-RAM

UP/Down SW

64M+32Mbit

SRAM

4Mbit

Interface

IC

BU7870KN

12 Key

Interface

Connector

ANT FPC

RF, PowerAMP, Filter, Mix

Backup

Bat

DSP

CPU

PLL

Hermes

AD6529

AD/DA

Audio

AMP, Filter

Mix

Controller

Typhoon

AD6535

MIC

BIU(bus)

ROM/

RAM

RTC

Power

Audio

Connector

Hall IC

IR Module

Power

Magnet

Shutter SW

Receiver

LCD

QVGA

240x320

2.2Type

WhiteLED BackLight

LCD Disp

Controller

LR38863

BD6015

Power IC

for BackLight and Camera

Cursol Key Matrix

&

Key Light_LED

TM100 DIAGRAMS

4 – 1

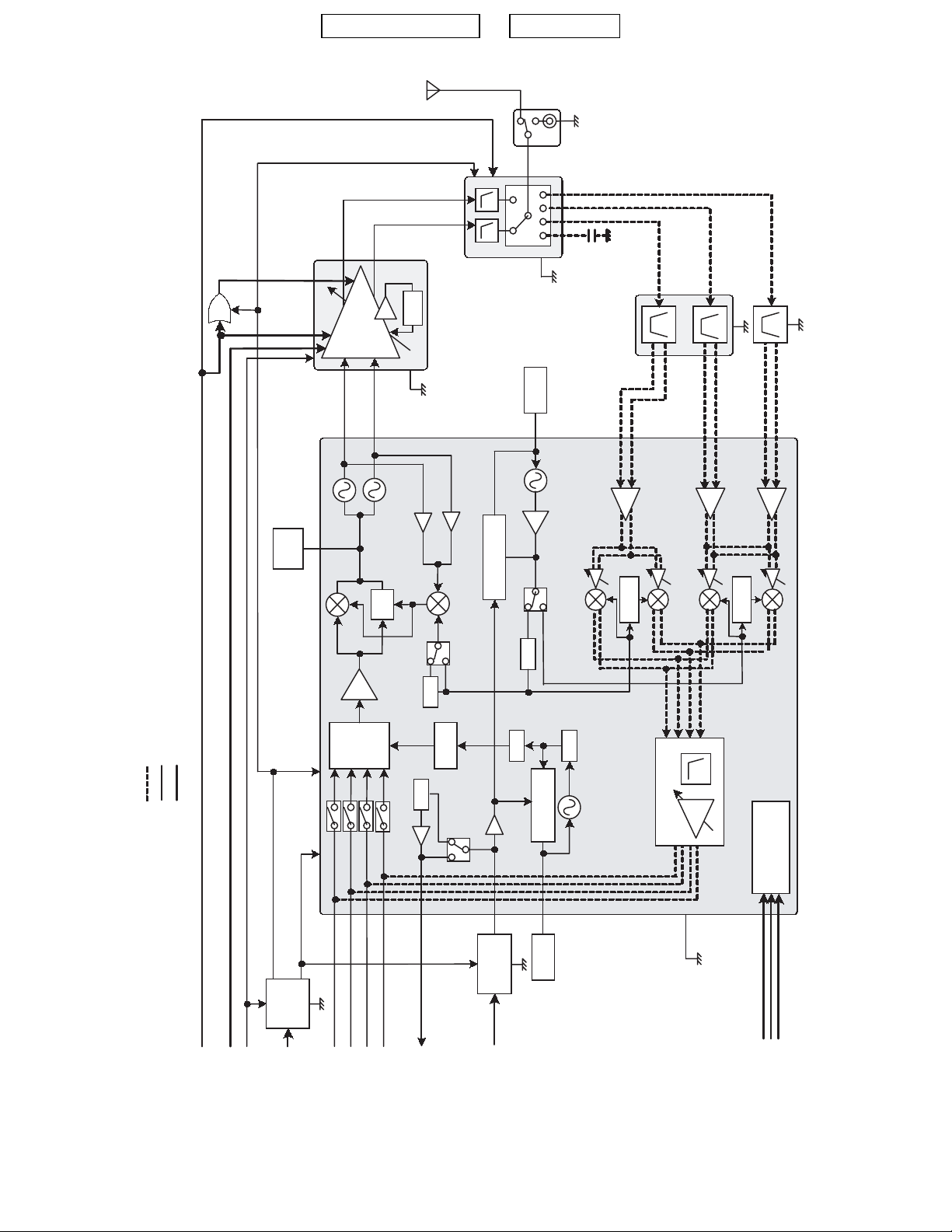

Page 3

CONFIDENTIAL DRAFT

BS1

BS2

BS3

BS4

1800 / 1900

900

Antenna

IC803

J801

Test Connector

RFSW

GSM900 RX

SAW Filter

DCS RX

PCS RX

SAW Filter

IC805

(PF08141BS)

APC

FL902

filter

Loop

LNA

LNA

FL903

4

LNA

BS2

BS2

BS3

VBAT

PA

IC802

RX Line

TX Line

filter

Loop

RF"Synthesizer

DPD

1/2

1/2

I&Q

Control Line

(D):"Digilal,"(A): Anal og

VRF

VTCXO

MOD

1/2

90deg

shift( )

1/2

IC804

Voltage

Regulator

TCX801

1/2

26MHz

VCTCXO

1/2

IF"Synthesizer

filter

Loop

1/2

90deg

Shift( )

PGA Part

PGA

1/2

90deg

Shift( )

RFIC

IC801

(HD155155)

interface

Serial data

BS3 (D)

BS4 (D)

BS1 (D)

BS2 (D)

VBAT

PA (A)

RF BLOCK DIAGRAM

QN (A)

IP (A)

IN (A)

TCXOEN (D)

QP (A)

TCXOOUT (D)

TM100 DIAGRAMS

AFCDAC (A)

""SYNTHEN""""""(D)

""SYNTHDATA"(D)

""SYNTHCLK""""(D)

4 – 2

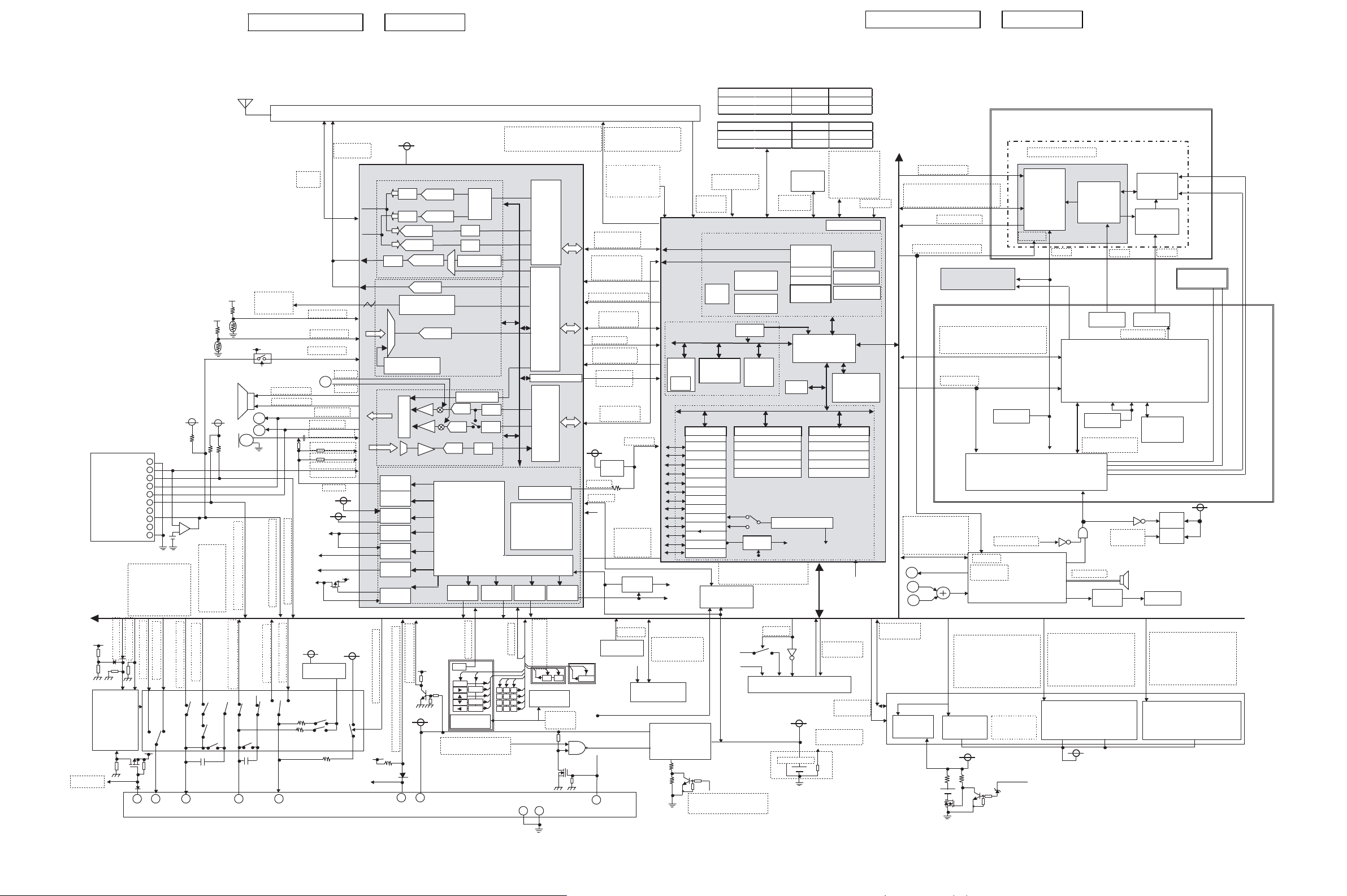

Page 4

CONFIDENTIAL DRAFT

O

S

)

)

y

W

D

G

)

■ Baseband Block Diagram Ver1.0 (TM100)

AFCDAC,

PA

GPIO_09

Headset Jack

JEARL(MONO)

MONO/ST

VUSB

GPO_04

M

DE

EL1

logic

MODE SEL2

1

AGND

2

JMIC

3

JACK

JEARR

4

5

6

NC

7

RCS

8

NC

9

DGN

10

Functions of

Accessary Connector

ƦRS232C Cabel

ƦUSB

ƦGenie

ƦAC/DC Charger

ƦHands Free

GPO_19

USB D-

USC[2](TXD)

MODE SEL3

VINT

Pch

6 7

For batter

VREF

For Camera

RECEIVER

VCORE

VVCXO

MIC

GPIO_2(MODESEL1)

GPIO_36(MODESEL2)

GPO_19(MODESEL3)

USC[0](Genie_TX)

USC[5](CTS/Genie_TX)

VREF

LIGHT1

LIGHT2

LIGHT3

VINT

VABB

AOUT1P

AOUT1N

E

D

GPIO_48(Remote control SW)

GPIO_8(Stereo / MONO DEC)

USC[1](RXD)

USC[4](RTS/Genie_RX)

9 23

IP, IN

QP, QN

TEMP2

TEMP1

AUXADC2

A

AOUT3R

AOUT3L

AIN1P

AIN1N

AIN2N

AIN2P

AIN2N

USB_VBUS

VUSB

VBACK

VRTC

VSIM

VAPP

GPIO_7(Headset SW detect)

VBAT

USB D+

Reg 3V

BU7870KN

AD6535 (Typhoon

x 3

AIN3L

AIN3R

VBAT

VUSB

GPIO_39(USB_PU_Control)

VINT

Test C

Accessary Connector

RF I/F ( BRIGHT5E )

VBAT

ADC

ADC

RAMP DAC

AFC DAC

Light Controller

AUX ADC

PGA

PGA

Analog SW

PGA

VINT

GPIO_10( DETECT)

4

BASEBAND SECTION

DAC

DAC

GMSK

MOD

Filter

Filter

Ramp RAM

AUXRILY SECTION

Tone Generator

DAC

DAC

ADC Filter

AUDIO SECTION

REGULATOR

CONTOROL

VCXO

LDO

KEYON

Power

MENU

Soft2

SEND

Soft1

Cursor key

BACKLIGHT

USB CHARGE ENABLE

LIGHT2(Typhoon)

Filter

Filter

POWER MANAGEMENT SECTION

Filter

Filter

Filter

Voltage Reference

BUFFER

VMIC

LDO

VABB

LDO

VUSB

LDO

VBACK

LDO

VRTC

LDO

SIM

LDO

VAPP

LDO

USB_VBUS

USC[6](GPIO_31/Genie_RX/RTC_monitor)

8

CLKON,ȁGPO_1 (TXON),

GPO_9 (BS3), GPO_11(BS4)

GPO_16 (BS1) GPO_17(BS2)

Baseband

Serial

Port

Control

Serial

Port

INTERRUPT LOGIC

Audio

Serial

Port

POWER ON

RESET GENERATOR

BATTERY

CHARGER

VMEM

VEXT

LDO

LDO

KEYOUT

KEYPADROW[4:0]

* #0

1 32

4 6Up5

7 98

Keypad:4x 3

1

KEY PAD

BACKLIGHT

10

VCORE

LDO

KEYPADCOL[4:0]

Dn

Shutter

LIGHT3

(Typhoon)

GPO_18 (SYNTHEN)

GPO_20 (SYNTHDATA)

GPO_21 (SYNTHCLK)

HardwearID for MP

GPIO_04:"L"

GPIO_16:"L"

GPIO_34:"H"

BSIFS BSDI

BSOFS BSDO

GPO_1 (TXON),

GPO_0 (RXON),

GPO_5 (ASM)

GPO_29(RESETABB

CSFS CSDI

CSDO

MCLKEN

CLKOUT

(13MHZ)

GPIO_37

(Interrupt)

ASFS ASDI

ASDO

2.6V

detect

nRESET

VINT

RESET

VCHG

PWRON

(DBBON),

CLKON

(VCXOEN)

VINT

VBAT

GPIO_11

Flip-SENSE

HoleIC

VSIM

5.2V/600mA

from AC/DC

5

LDO

3.0V / (1.8V)

CARD

SIMDATAIO

SIMCLK

GPIO_23(RESET)

SIM

VIN

EN

BOOTCTRL[1]

BOOTCTRL[0]

CLKIN

(13MHz)

AD6529 (Hermes)

BSPORT

ASPORT

HSL/

Trace

MCU Subsystem

SBUS

BOOT

ROM

Serial

number

VINT

VCORE

Reg15 for

loader

ACL

MCU

ARM7TDMI

58.5MHz

GPIO

DISPLAY

RTC

KEYPAD

BMC

SIM

USC

UART

USB 1.1

Fast IrDA

I2C

Backlight

SPI(MMC)

External Circuit

For Charging

USB_CURRENT_CONTROLL

MP4_P0((LCDC port)

Genie I/F (For debugging)

Inter face IC MODE MODE1 MODE2/ 3 / 5

Genie_TX USC[0] USC[5]

Genie_RX USC[6] USC[4]

Genie I/F (For Production)

Inter face IC MODE MODE1 MODE2 / 3 / 5

Genie_TX USC[5] USC[0]

Genie_RX USC[3] USC[3]

When JTAG=H,

automaticaly

GPO_183TCK

32kHz

GPO_193TMS

Crystal

GPIO_203TDI

OSCIN

OSCOUT

GPIO_213TDO

JTAG I/F

DSP Subsystem

Cipher

Coprocessor

Viterbi

Coprocessor

Cache

(16k byte)

CLK

&

BS GEN

HOUSE-KEEPING

System DMA

WDT

General Timers

IRQ-CTRL & RAU

SPORT-0

SPORT-1

PLL

IDMA

DSP

ADSP-218x

78MHz

DMA and BUS

ARBITRATION

PBUS

Cipher

Engine

Cache RAM

(4k word)

PM (16k word)

DM (16k word)

Internal

SRAM

(2Mbit x 2)

GSM-SYSTEM

MicroSM

Slow Clocking

CSPORT

Synth i/f

RBUS

Peripheral Subsystem

Peripheral PLL

VINT

VBAT

LDO

VHGOSC, GATEDRIVE,

CHGDACREF, ISENSE(ADC)

REFCHG, VBATSENSE(ADC)

Vmem

2.8V

VINT

GPO_8

VBAT

VINT

Shut

Down

IrDA module

(GP2W0116)

Protection

VCORE,ȁVINTȒABB

VMEM, VEXT

VRTC, VSIM

VUSB, VMC

GPIO_0 (TXD)

GPIO_1(RXD)

ADD[1..23]

BATTYPE

(Typhoon ADC)

Li-ION

Battery

700mAh

TYPE R=4.7K

CONFIDENTIAL DRAFT

JTAGEN

EBUS

GPIO_47 (RESET

ADD[2:1], ADD[19:17],

DATA[15:0], nDISPLAYCS2 ,

nWR, nRD,

PIO_13(CINT)

GPIO_40(13M CLKOUT)

CGS module

nRD, GPO_10(BUFOFF) nWR,

nDISPLAYCS1,nWAIT,GPIO_22(RSP)

DATA[15:0],GPIO_6(LCDINT)

GPIO_12

RESET

GPIO_38(INT),

nWR,nRD

ADD[1],DATA[15:0]

GPIO_24(RESET),

nAUXCS2

A

D

E

EQ

ADDRESS & DATA BUS / GPIO (INT)

DATA[0..15]

OE#:NRD(Hermes)

WE#:NWE(Hermes)

CE#:NROMCS1(Hermes)

WP#:GPO_02(Hermes)

RST#:NRESET(VINT_Detector)

VPP:GPO_22(Hemes)

RY:NC

Memory

SRAM

4Mbit (x16)

nGPCS2

Back-up

Battery

P-SRAM 1

64Mbit (x 16)

nRAMCS1

VBACK

controlled by VCORE

CLKI

HP_OUTL

HP_OUTR

RESET

AVDD

EXCKI

VINT 3.0V

Reg8

3.0V

Power management IC

(BD6015)

GPO_1(TX_ON)

Sound IC

(MA3)

P-SRAM 2

32Mbit (x 16)

nRAMCS2

TestC

350Kpcs CCD

DSP part

IP part

LED ON/OFF

LED

OE#:NRD(Hermes)

WE#:NWE(Hermes)

CE#:NROMCS1(Hermes)

WP#:GPO_02(Hermes)

RST#:NRESET(VINT_Detector)

VPP:GPO_22(Hemes)

RY:NC

VDD2

RESET

Motor

ON/OFF

ALEOE# CLE WP#

128Mbit (x 16)

Camera LSI

(LR38604)

controlled by VCORE

SE_D0, SE_LD2

SE,CK, PWM_LCD

CAMN

CAMP

SPOUT1/2

Nor Flash

nROMCS1

VINT

3.0V

Camera module (LZ0P371J)

sensor

V-Driver

VDD

controlled by VCORE

Reg 7

2.5V

Reg9

3.1V

MP4RESET_B

LCD Controller

(LR38863)

VDDCORE

VDDPLL

Reg 11

1.8V

LIGHT1

(Typhoon)

Speaker

Reg13

3.0V

RE# WE#

CCD

-8V

VDD6

15V

LCD

BACKLIGHT

5.45MHz

Ceramic

Resonator

Green

LED

Red

LED

Vibrator

RE#:NRD(Hermes)

WE#:NWE(Hermes)

CE#:NGPCS1(Hermes)

WP#:ADD_0(Hermes)

ALE:NADV(VINT_Detector)

CLE:NAUXCS1(Hermes)

R/#B:NC

Super AND Flash

128Mbit (x 16)

nGPCS1

VBAT

TM100 DIAGRAM

4 - 3

TM100 DIAGRAM

4 - 4

Page 5

CONFIDENTIAL DRAFT

(1) Sound signal system

䇭

Speaker

Internal

microphone

Receiver

YM762

Amplifier

unit

Sound

source

unit

AIN1

OUT1

Monophonic

AIN3R

AIN3L

AD6535

(2) LCD & camera system

Backlight LED

OUT3R

OUT3L

AIN2

LCD

External

headphone

External

Microphone

External headphone

External Microphone

(4) Interfac e

Interface SW

UART

Analog

Serial

UART

USB

BU7870

(5) Vibration Motor & LED Driver

LDOM

Vibration Motor

ON/OFF

I/F CN

Power

Cherge Pump

souceIC

BD6015

15V

8V

3.1V

2.5V

CCD camera I/F

LCD controler

Series regulator

Series regulator

(3) Battery charge system

Constant voltage

Constant current

AC charger

VDT

reg

OVP

AD6538

I/F

㧗3.0V

㧗1.8V

Series

regulator

Lithium ion

Battery pack

LED

Green

LED

Red

LED-Light

Cursor-Key

LED-Light

(6) Sense Slide

Slide Sense

12Key

TAPE SIDE

Polar"S"

Upper CAB

Lower

CAB

YM762

AD6535

Typhoon

N

Magnet

S

Hall IC

EW6671

TM100 DIAGRAMS

4 – 5

AD6529

Hermes

Page 6

CONFIDENTIAL DRAFT

B

B

B

D

D

D

D

1/1

12345678

12345678

12345678

12345678

C

C

C

C

B

A

21

21

21

21

3

3

3

3

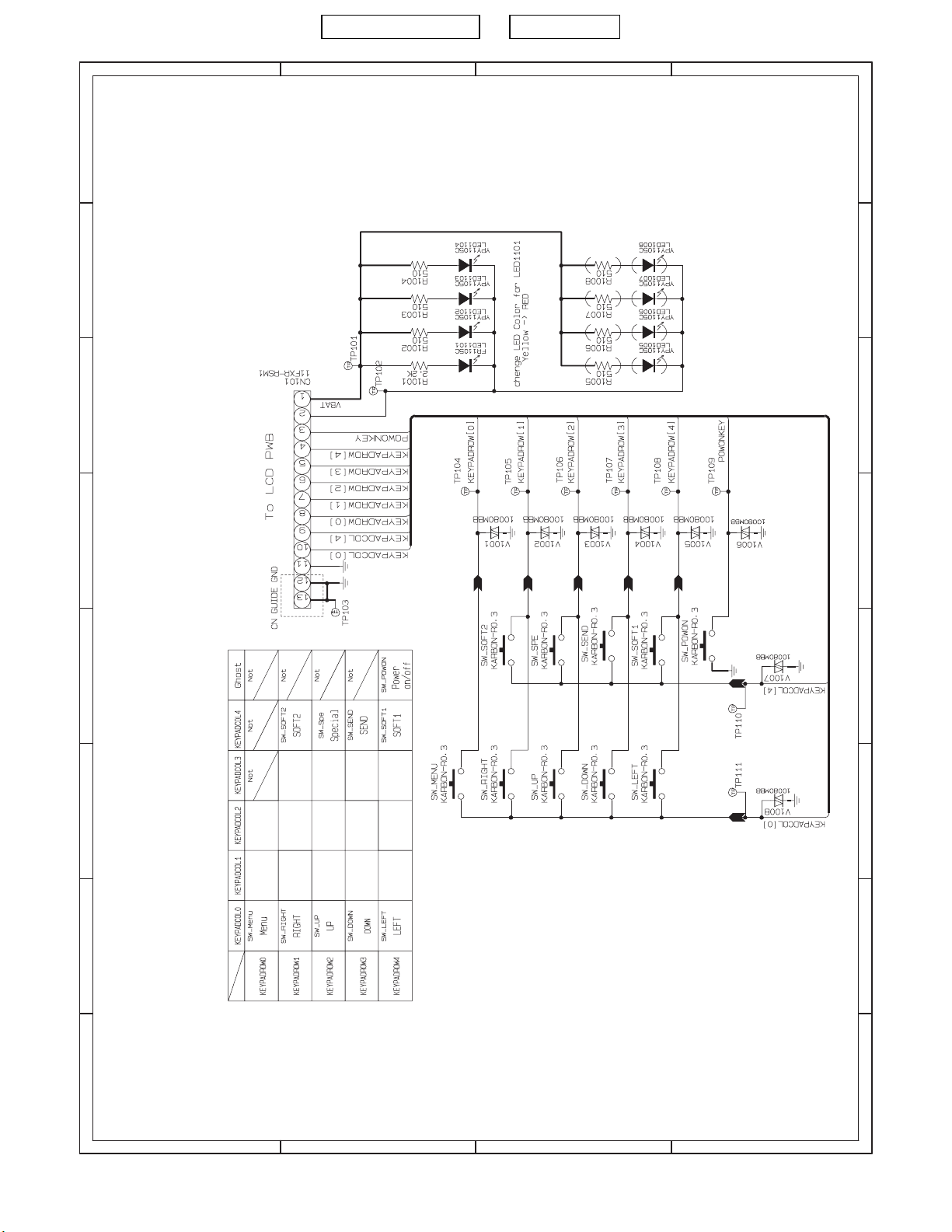

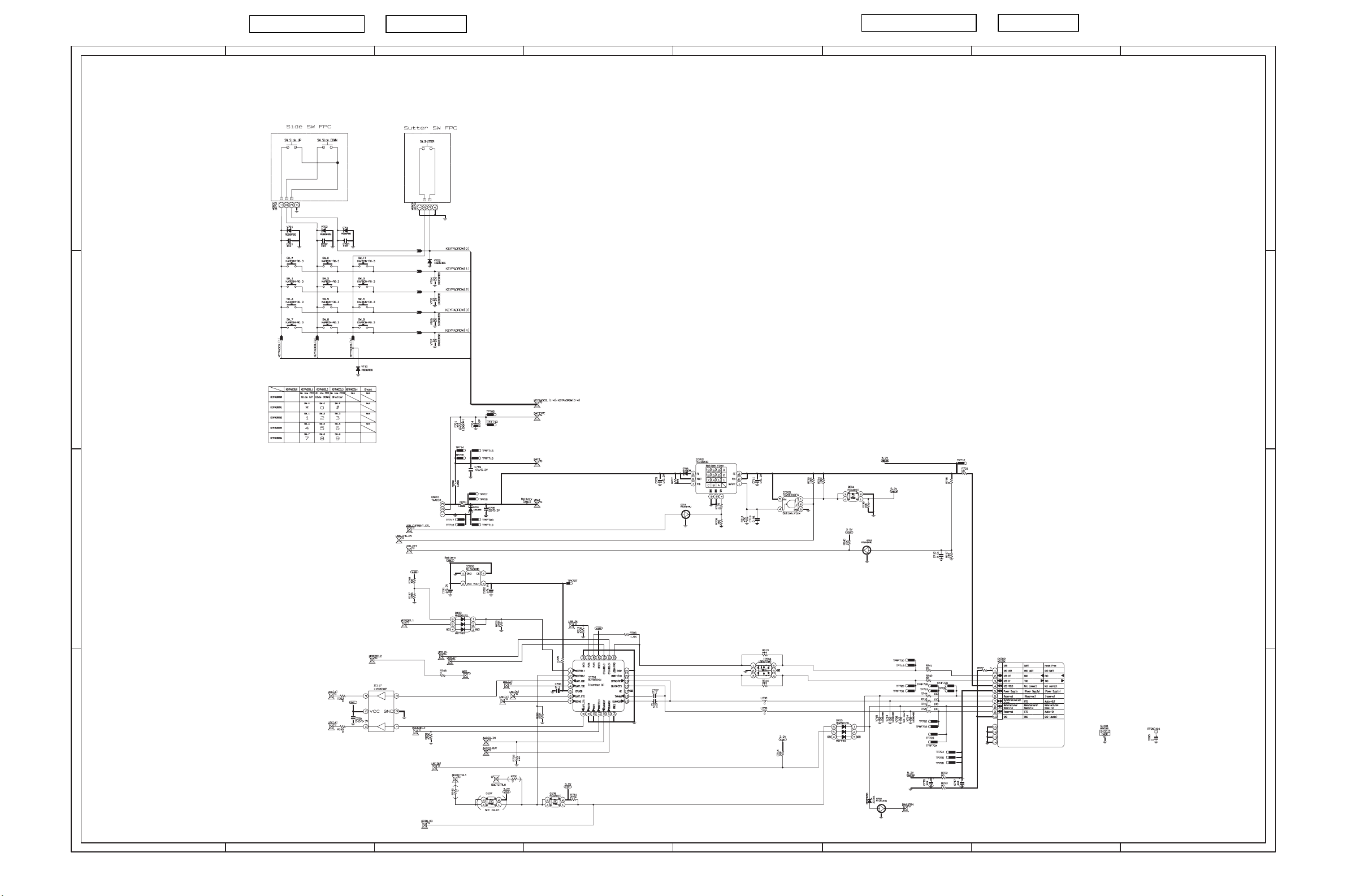

CHAPTER 5. CIRCUIT DIAGRAM

TM100 PRE PRODUCTION/KEY

D

D

D

D

C

C

C

C

TM100 CIRCUIT DIAGRAM AND PWB LAYOUT

5 – 1

87654

87654

87654

87654

B

B

B

B

A A

A A

A A

A

Page 7

CONFIDENTIAL DRAFT

B

B

B

D

D

D

D

1/1

12345678

12345678

12345678

12345678

C

C

C

C

B

A

21

21

21

21

3

3

3

3

CHAPTER 5. CIRCUIT DIAGRAM

TM100 PRE PRODUCTION/KEY

D

D

D

D

C

C

C

C

TM100 CIRCUIT DIAGRAM AND PWB LAYOUT

5 – 1

87654

87654

87654

87654

B

B

B

B

A A

A A

A A

A

Page 8

CONFIDENTIAL DRAFT

TM100 PRE PRODUCTION / LCD

CONFIDENTIAL DRAFT

12345678

D

C

5

6

D

C

B

A

87654

TM100 CIRCUIT DIAGRAM AND PWB LAYOUT

5 - 2

3

TM100 CIRCUIT DIAGRAM AND PWB LAYOUT

5 - 3

21

B

A

Page 9

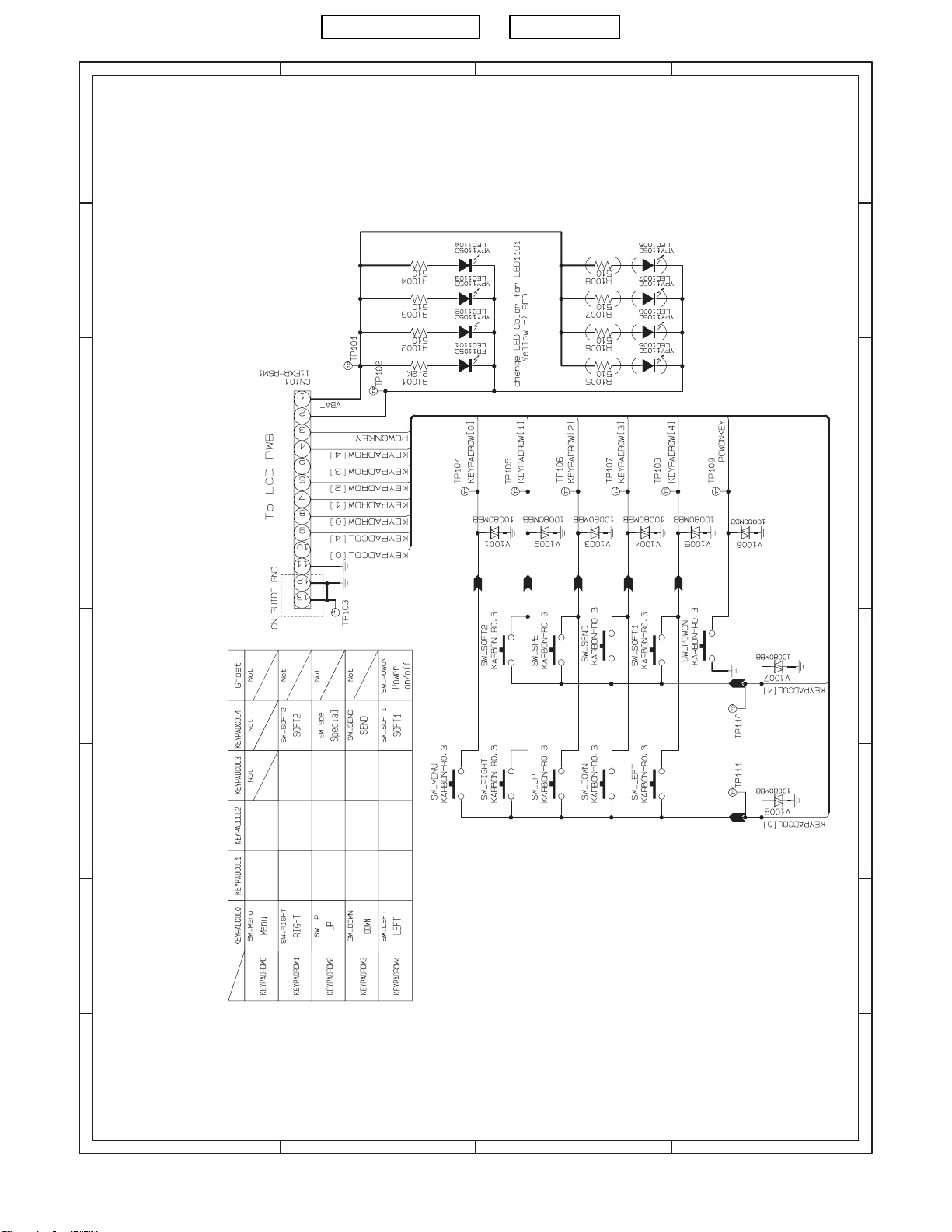

CONFIDENTIAL DRAFT

TM100 PRI PRODUCTION / MAIN

CONFIDENTIAL DRAFT

12345678

D

C

D

C

B

2

1

A

87654

TM100 CIRCUIT DIAGRAM AND PWB LAYOUT

5 - 4

3

3

TM100 CIRCUIT DIAGRAM AND PWB LAYOUT

5 - 5

21

B

A

Page 10

CONFIDENTIAL DRAFT

PRI PRODUCTION/MAIN

CONFIDENTIAL DRAFT

12345678

D

C

D

C

B

A

87654

TM100 CIRCUIT DIAGRAM AND PWB LAYOUT

5 -6

3

TM100 CIRCUIT DIAGRAM AND PWB LAYOUT

5 - 7

21

B

A

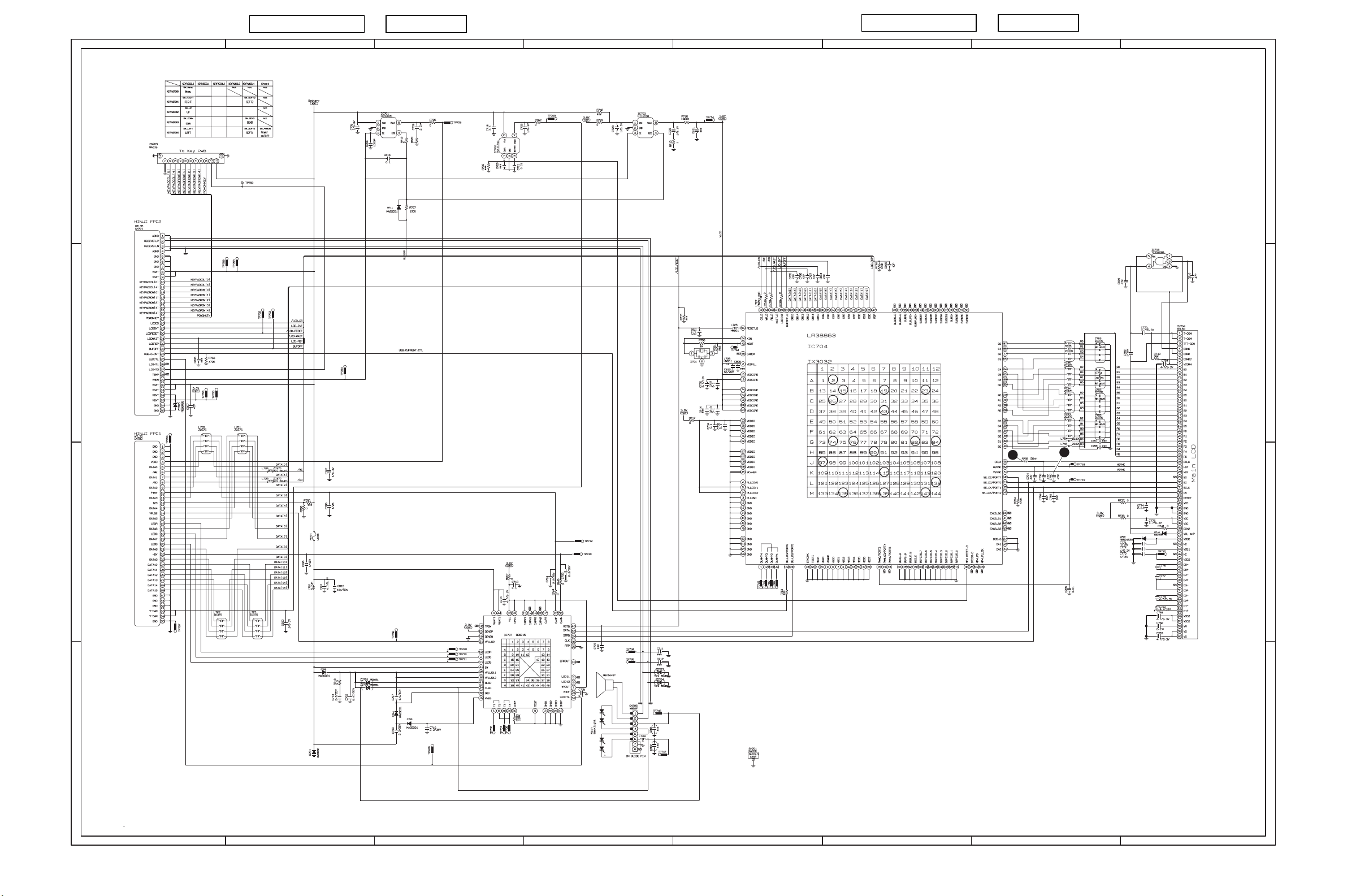

Page 11

CONFIDENTIAL DRAFT

A

A

A

B

B

B

D

D

D

D

1/1

1

1

1

1

C

C

C

C

B

A

2

2

2

2

14

3

3

3

3

4567

4567

4567

4567

11

12

21

21

21

21

3

3

3

3

54

54

54

54

6

6

6

6

7

8

9

10

4

8

8

8

8

16

15

17

87

87

87

87

TM100 PRE PRODUCTION / RF PART

B

B

B

D

D

D

D

C

C

C

C

TM100 CIRCUIT DIAGRAM AND PWB LAYOUT

5 – 8

B

A

A

A

A

Page 12

CONFIDENTIAL DRAFT

D108

C230

R711

C718

R709

C112

R297

R265

R296

C158

R287

R735

C231

R131

IC705

C225

R294

C122

C228

C108

R280

C121

C163

R728

IC115

Q504

R284

IC702

C162

R734

C116

C133

R295 R126

R124

R147

IC118

R115

C155

IC116

C711

R732

R285

R259

V102

R286

R125

Q701

R132

C146

R299

R255

R283

C103

R741

C218

R195

R277

CN702

R722

R718

V713

R720

L838

L839

V714

R721

R723

CN106

C219

IC117

R193

R745

R164

R752

R205

R204

C182

R172

C207

R262

R180

IC112 IC113

C215

C721

IC505

C722

IC101

R714

R186

C143

R727

R744

IC108

C205

IC109

C139

C720

C200 C198 C199

L113

D705

1

R278

D105

R719

V715

UN101

1

D109

R753

R747

R746

SH101

C142

JK101

C173

C105

V103

C166

R143

C141

R246

R192

R169

C153

R166 R144

C191

R128

L104

R113

V101

32.768 KHz

3

X101

R174

C187

R152

R167

C164

R148

C221

FS702

FS701

C705

R258

C176

C151

R237

R141

R257

C222

R748

TH101

C223

C216

R740

C217

R256

C189

L112

Q503

IC114

TH001

R269

C234

ZD101

R267

C179

R179

C177 C178 R272 C188

C184 C185

C235

CN701

C220

C137 R117

IC504

C704

R207

R194

R261

C210

R163

13MHz IN

1

C183

R742

C186

C715

R249

R716

R206

R175

R181

R173

C101

L101

L102

C192

R170

C180 C190

IC106

L111

R244

R245

L103

L105

C110

R191

C107

D103

R133

Q101

D703

R751

Q108

C709

C145

R168

C144

C213

R238

C214

IC111

R162

R239

R209

C208

C181

R177

C161

C160

C159

R171

C165

R248 R140

IC103

C150

Q103

R127

R138

C118

C206

C719

R153

13MHz OUT

2

R134

■ MAIN PWB

ANT801

C894

R894

C893

R892R897

R895

FL905

LED125

J801

GND1

TM100 CIRCUIT DIAGRAM AND PWB LAYOUT

5 – 9

Page 13

CONFIDENTIAL DRAFT

C120

R234

C113

L108

CN105

R137

L107

R122

R273

C233

C226

CN704

C147

R233

BS3

13

R279

CN103

C115

C132

BS1

R266

C892

C866C865

C864

SH801

L806

L805

L804

C845

C852

L803

L892

L891

C860

C850

C867

L823

TCXOEN

IC805

4

C843

C844

SYNTHEN

15

C851

R807

C801

FL102FL103FL104FL105

L802

SYNTHDAT

17

IC801

SYNTHCLK

16

IN

8

C810

L822

L801

C807

C806

C802

IC804

CN101

R275

R805

C842

C830

C836

L821

R810

R811

C803

R804

C149

C841

C840

C812

C811

TCX801

C834C835

C152

C723

C707

R165

R806

C831

IP

7

R139

IC105

R293

V703

C837

L837

C833

L836

L835

C832

R802

V710

R706

C193

R182

IC107

C194

QN

10

QP

9

Q106

R253

R252

C895

R282

C227

R281

C148

R142

R145

R146

C157

C154

R120

R116

C169

C167

C171

R159

R161

C170

R160

C232

C168

R158

R705

C706

R289

IC701

R288

R713

CN703

R276

BS2

12

C881

C885

C870

C873

11

C872

IC803

L872

C874

C876

C875

ZD701

Q109

C239

R228

R227

R210

C238

R217

R189

FL107

FL106

V701

V702

C240

V707

V705

R225

L871

FL109

Q702

R298

C134

C236

C117

BS4

14

D701

R260

R292

R187

R224

FL101

R222

C862

C863

C861

R812R861

FL108

IC802

CN102

C241

R221

R274

C856

C855

C871

V706

C857

V704

FL903

FL902

R891 C854

L110

■ MAIN PWB_REAR

R103

R101

R102

LED113

LED101

LED102

LED103

LED114

R104

LED104

R105

LED105

R106

LED106

ZD104

ZD103

ZD105

TM100 CIRCUIT DIAGRAM AND PWB LAYOUT

5 – 10

R107

R108

R109

LED115

LED107

LED108

LED109

LED111

LED112

R110

R111

R112

LED116

LED110

C197

C196

R185

R184

R183

Q104

Page 14

■ LCD PWB_F

R713

IC703

C728

R743

C729

R716

R712

L729

CN703

CONFIDENTIAL DRAFT

R740

CN704

D710

CN705

C770

C809

C810

C721

IC706

C784

IC701IC702

C769

C722

C709

R705

C706

C797

R720

C705

C718C800R762

C766

C701

D705

R741

C771

L701

C708

D704

C772

D709

C707

R718

D701

C713

SH701

D702

C702

C714

R708

C710

R745

R737

C774

R738

ZD705

C775

C782

C781

C783C779C773

C780C777C776

C719R707

IC707

R744

C725

C795

C726

C724

C796

■ LCD PWB_REAR

C785

C786

C804

C787

C734

L727

C761

C737

C736

CN702

L726

R732

C805

R746

R748

R747

C759

R764

CN701

L723L722L721L720

C758

C794

IC704

X701

6

R750R751

C760

VSYNC

R759

C732

R717

DCLK

5

R736

R735

R733

L728

C813

C812

L714

L715

C739

R763

C807

R766

R734

FS701

C815

D711

R767

C816

TM100 CIRCUIT DIAGRAM AND PWB LAYOUT

5 – 11

Page 15

■ KEY PWB_REAR

CONFIDENTIAL DRAFT

■ KEY PWB

R1003

LED1103

R1002

LED1102

LED1104

R1004

LED1101

R1001

V1005

V1003

V1001

V1008

V1002

V1007

CN101

V1006

V1004

TM100 CIRCUIT DIAGRAM AND PWB LAYOUT

5 – 12

Page 16

CONFIDENTIAL DRAFT

L102

F

F

IC1001

C1001 C1002

L101

■ CAMERA FPC

F

TM100 CIRCUIT DIAGRAM AND PWB LAYOUT

5 – 13

F

F

Page 17

CHAPTER 6. WAVEFORMS OF CIRCUIT

[1] WAVEFORMS OF CIRCUIT

IP

(talking)

C811

(IC801 23Pin)

2

IN

(talking)

C811

(IC801 24Pin)

QP

3

(talking)

C812

(IC801 25Pin)

QN

4

(talking)

C812

(IC801 26Pin)

IP

(talking)

C811

(IC801 23Pin)

2

IN

(talking)

C811

(IC801 24Pin)

3

QP

(talking)

C812

(IC801 25Pin)

4

QN

(talking)

C812

(IC801 26Pin)

RF T est Tool

Tx test

Data pattern

RF T est Tool

Rx test

channel_62, Gain 62dB, SniffOff

...

TSC5

8

BS1

(talking)

C870

(IC803 10Pin)

9

BS2

(talking)

C871

(IC803 6Pin)

10

BS3

(talking)

C872

(IC803 12Pin)

11

BS4

(talking)

C874

(IC803 14Pin)

8

BS1

(talking)

C870

(IC803 10Pin)

9

BS2

(talking)

C871

(IC803 6Pin)

10

BS3

(talking)

C872

(IC803 12Pin)

11

BS4

(talking)

C874

(IC803 14Pin)

RF T est Tool

Tx test

GSM900 Band

RF T est Tool

Tx test

DCS1800, PCS1900 Band

5

SYNTHEN

(STAND-BY)

L835

(IC801 29Pin)

6

SYNTHCLK

(STAND-BY)

L836

(IC801 30Pin)

7

SYNTHDATA

(STAND-BY)

L837

(IC801 32Pin)

RF T est Tool

Rx test

GSM900 Band (channel 62)

TM100 WAVEFORMS OF CIRCUIT

6 – 1

Page 18

8

BS1

(talking)

C870

(IC803 10Pin)

9

BS2

(talking)

C871

(IC803 6Pin)

10

BS3

(talking)

C872

(IC803 12Pin)

11

BS4

(talking)

C874

(IC803 14Pin)

8

BS1

(talking)

C870

(IC803 10Pin)

9

BS2

(talking)

C871

(IC803 6Pin)

10

BS3

(talking)

C872

(IC803 12Pin)

11

BS4

(talking)

C874

(IC803 14Pin)

RF T est Tool

Rx test

GSM900, DCS1800 Band

RF T est Tool

Rx test

PCS1900 Band

13MHz IN (Point R261) To Digital Base Band LSI Pin142

12

13MHz OUT (Point R166) from Digital Base Band LSI Pin84

13

32.768KHz IN (Point-R152) To Digtal Base Band LSI Pin49

14

TM100 WAVEFORMS OF CIRCUIT

6 – 2

Page 19

DCLK (Point-R759 on LCDC_PCB) To LCD Unit pin26

15

VSYNC (Point-C760 on LCDC_PCB) To LCD Unit pin28

16

TCXOEN (Point-IC804 pin 1) From Analog Base Band LSI Pin 2

17

TM100 WAVEFORMS OF CIRCUIT

6 – 3

Page 20

CONFIDENTIAL DRAFT

CHAPTER 7. OTHERS

[1] IC/LSI PIN LIST AND CONNEC TOR PIN LIST

1. MAIN PWB

IC101 (LRS1B27): Memory LSI

PIN No. Name I/O Discription of Terminal

1A1NC −

2 A3 A20 I Address A20

3 A4 A11 I Address A11

4 A5 A15 I Address A15

5 A6 A14 I Address A14

6 A7 A13 I Address A13

7 A8 A12 I Address A12

8A9GND −

9A10NC −

10 A11 NC −

11 A12 NC −

12 B1 NC −

13 B2 SF-RY O

14 B3 A16 I Address A16

15 B4 A8 I Address A8

16 B5 A10 I Address A10

17 B6 A9 I Address A9

18 B7 DQ15 I/O

19 B8 S/SC-WE# I NOR Flash/Smart Combo

20 B9 DQ14 I/O DATA DQ14

21 B10 DQ7 I/O DATA DQ7

22 B11 NC −

23 B12 NC −

24 C2 SF-RE# I Smart Combo Flash Read

25 C3 F-WE# I S mart Combo Flash Write

26 C4 F-RY O NOR Flash Ready

27 C5 A21 I Address A21

28 C6 SC-CE2 I Smart Combo RAM

29 C7 DQ13 I/O DATA DQ13

30 C8 DQ6 I/O DATA DQ6

31 C9 DQ4 I/O DATA DQ4

32 C10 DQ5 I/O DATA DQ5

33 C11 NC −

34 D2 F/SF/SC-VCC

35 D3 GND

36 D4 F-RST# I NOR Flash Reset

37 D5 A22 I Address A22

38 D6 SC2-CE1# I Smart Combo RAM2 Chip

39 D7 DQ12 I/O DATA DQ5

40 D8 S/SC1-CE2 I SRAM Chip Enable, Smart

41 D9 S-VCC

Smart Co mbo F l as h Rea dy (O D)

RAM/SRAM Write Enable

Sleep State Input

NOR Flash/Smart Combo

Power

RAM/Smart Combo Flash Power

Power

GND

Enable

Combo RAM Sleep State

Power

SRAM Power

PIN No. Name I/O Discription of Terminal

42 D10 F/SF/SC-VCC

43 D11 NC −

44 E2 CLE I Smart Combo Flash

45 E3 F-WP# I NOR Flash Write Protect

46 E4 VPP I NOR Flash Voltage Sense

47 E5 A19 I Address A19

48 E6 DQ11 I/O DATA DQ11

49 E7 F/SF/SC-VCC

50 E8 DQ10 I/O DATA DQ10

51 E9 DQ2 I/O DATA DQ2

52 E10 DQ3 I/O DATA DQ3

53 E11 NC −

54 F2 ALE I Smart Combo Flash Address

55 F3 LB# I Smart Combo RAM

56 F4 UB# I Smart Combo RAM

57 F5 NC −

58 F6 NC −

59 F7 DQ9 I/O DATA DQ9

60 F8 DQ8 I/O DATA DQ8

61 F9 DQ0 I/O DATA DQ0

62 F10 DQ1 I/O DATA DQ1

63 F11 NC −

64 G1 NC −

65 G2 SF-WE# I Smart Combo Flash

66 G3 A18 I Address A18

67 G4 A17 I Address A17

68 G5 A7 I Address A7

69 G6 A6 I Address A6

70 G7 A3 I Address A3

71 G8 A2 I Address A2

72 G9 A1 I Address A1

73 G10 SC1-CE1# I Smart Combo RAM1

74 G11 NC −

75 G12 NC −

76 H1 NC −

77 H2 SF-WP# I Smart Combo Flash

78 H3 SF-CE# I Smart Combo Flash

79 H4 A5 I Address A5

80 H5 A4 I Address A4

81 H6 A0 I Address A0

NOR Flash/Smart Combo

Power

RAM/Smart Combo Flash Power

Command Latch Enable

NOR Flash/Smart Combo

Power

RAM/Smart Combo Flash Power

Latch Enable

Lower Byte Enable

Upper Byte Enable

Write Enable

Sleep State

Write Protect

Chip Enable

TM100 OTHERS

7 – 1

Page 21

CONFIDENTIAL DRAFT

PIN No. Name I/O Discription of Terminal

82 H7 F-CE# I NOR Flash Chip Enable

83 H8 GND

84 H9 OE# I NOR Flash/Smart Combo

85 H10 S-CE1# I SRAM Chip Enable

86 H11 NC −

87 H12 NC −

IC103 (AD6535): Analog BaseBand LSI

PIN No. Name I/O Discription of Terminal

1 A1 TD1 I TEST Port Data Input

2A2VCXOEN I

3 A3 VBAT3

4 A4 VEXT

5 A5 VCHG

6 A6 GATEDRIVE O Charge FET gate control signal

7 A7 ISENSE I Charge Current Sense

8 A8 TEMP2 I ADC Input (Temperature sen-

9 A9 AUXADC2 I Not used (ADC input)

10 A10 REFBB O Reference V oltage OUTPUT

11 A11 A GND 2 − Analog BaseBand GND

12 A12 IP I/O BASEBAND T&R I-Channel

13 A13 IN I/O BASEBAND T&R I-Channel

14 A14 QN I/O BASEBAND T&R Q-Channel

15 A15 QP I/O BASEBAND T&R Q-Channel

16 A16 RSVD_A16 - RESERVED

17 B1 TMS I TEST Port ModeSelect

18 B2 TCK I TEST Port Clock (Not Used)

19 B3 VBAT3

20 B4 VEXT

21 B5 CHGOSC I ChargeTimer Capacitor

22 B6 BATTYPE I Battery Type sense ADC input

23 B7 CHGDACREF I/O GA TE D ri v e C u r re n t s et t i ng

24 B8 VBATSENSE I

25 B9 TEM P1 I

26 B10 AUXADC1 I Not used (ADC input)

27 B11 REFOUT O Voltage Reference Output

28 B12 PA O RF Power AMP Control Out-

29 B13 A GND 0 − GND (Substrate GND)

Power

RAM/SRAM Output Enable

(Not Used)

VVCXO Regulator Control input

Power

VEXT Regulator Input

VEXT Regulator Output (2.8V

Power

200mA Not used /bypassing

by capacitor)

Power

Charge Block Power input

sor for Battery)

for BASEBAND T&R (1.2V)

Positive I/O (Connect RF port)

Negative I/O (Connect RF port)

Positive I/O (Connect RF port)

Negative I/O (Connect RF port)

(Not Used)

Power

VEXT Regulator Input

VEXT Regulator (Output 2.8V

Power

200mA Not used /b ypassing

by capacitor)

(4700pF set 32KHz)

register connect (Ful lscale set)

Battery Voltage sense ADC input

ADC Input (Temperature sensor

for Camera)

(1.2V) Use for CAMERA

Temp Thermistor

put

PIN No. Name I/O Discription of Terminal

30 B14 AFCDAC O Auto Freqency Control DAC

[0to2xVREF] (Connect RF

port)

31 B15 REF O Voltage Reference Output

(1.2V)

32 B16 AGND1 − GND for Voltage Reference

Block

33 C1 TDO O TEST DataOutput (Not Used)

34 C2 GPI I

Ring Tone input (Not used con-

nect to GND through Register)

35 C15 VBAT1

Power

VVCXO Regulator Input

36 C16 RSVD_C16 − RESERVED

37 D1 INT O Interrupt Request

(Charge state interrupt)

38 D2 ASDO O Aud i o Se r ia l Po r t D a ta O ut

(Connect Hermes ASDI)

39 D15 REFCHG O Voltage R eference Output

(1.2V) Use for BAT Temp &

Type

40 D16 VVCXO

VVCXO Regulator Output

Power

(2.75V 10mV Not used/

bypassing by capacitor)

41 E1 ASDI I Audio Serial Port Data In

(Connect Hermes ASDO)

42 E2 BSDO O Base Band Serial Port Data Out

43 E15 VUSB

VUSB Regulator Output

Power

(3.2V 15mA )

44 E16 VAPPGATE O VAPP FET Gate Contro l

45 F1 BSIFS I Base Band Serial Port Input

Framing Signal

46 F2 AS FS O Audio Ser ial Port Framing sig-

nal Out

(Connect Hermes ASDO)

47 F15 VUSBIN

VUSB Regulator Input

Power

(connect to VBAT)

48 F16 VAPP I VAPP Voltage FeedBack

(1.8V/3.0V set software)

49 G1 BSOFS O Base Band Serial Port Output

Framing Signal

50 G2 BSDI I Base Band Serial Port Data In

51 G15 VBAT2

Analog BaseBand Regulator

Power

Intput

52 G16 NC_G16 − RESERVED

53 H1 CSDO O Control serial Port Data Out

54 H2 CSDI I Control serial Port Data In

55 H15 VBAT2

56 H16 VABB

Analog BaseBand Regulator

Power

Intput

Analog BaseBand Regulator

Power

Output (2.75V use internal only)

57 J1 ASM I B.B T&R Advanced State

Machine

58 J2 MCLKEN O Master Clock (13MHz) GATE

59 J15 AOUT1P O Audio Output 1 (+) 32Ω

(for Receiver)

60 J16 AOUT3L I/O Audio Output 3 (Left Chan-

nel) 32Ω (for Ex Phone)

61 K1 RXON I Base Band Rx ON (Active)

62 K2 TXON I Base Band Tx ON (Active)

TM100 OTHERS

7 – 2

Page 22

CONFIDENTIAL DRAFT

PIN No. Name I/O Discription of Terminal

63 K15 A OUT1N O Audio Output 1 (-) 32Ω

64 K16 AOUT3R O Audio Output 3 (Right Chan-

65 L1 MCLK I Master Clock Input (13MHz)

66 L2 CSFS I Co nt r ol S er i a l P or t Fr a mi n g

67 L15 AGND3 − analog Audio GND

68 L16 LIGHT1 O LED Dr iv er Op en Dr ai n 3 0m A

69 M1 ABBRESET I RESET Input (active Low)

70 M2 DGND − Digital GND

71 M15 LIGHT2 O LED Driver OpenDrain 30mA

72 M16 LIGHT3 O LED Driver OpenDrain 90mA

73 N1 VCORE

74 N2 VCOREIN

75 N15 LGND − Light Driver GND

76 N16 VMIC

77 P1 VCORE

78 P2 VMEMIN

79 P15 A IN2P I AudioInput 2 (+) (Used for

80 P16 A IN1P I AudioInput 1 (+) (Used for

81 R1 CRST I/O Power on reset Delay capaci-

82 R2 VMEMIN

83 R3 VMEMESEL I VMEM R eg ula to r O utpu t Vol t-

84 R4 VBAT5

85 R5 VBAT4

86 R6 VRTCIN

87 R7 DBBON I Power ON Input

88 R8 SGND − GND (Return POWER SPWR)

89 R9 AOUT2N O Audio Output 1 (-) 8Ω Audio

90 R10 SPWR − POWER Supply For AOUT2

91 R11 AOUT2P O Audio Output 1 (+) 8Ω Audio

92 R12 NC_R12 − RESERVED

93 R13 AIN3L I AudioInput 3 Left Channel

94 R14 AIN3R I AudioInput 3 Right Channel

95 R15 AIN2N I AudioInput 2 (-) (Used for

(for Receiver)

nel) 32Ω (for Ex Phone)

signal In (Connect Hermes)

(Indicator RED LED)

(Use for USB_CHG

control Port)

(for KEY lighting)

Vcore Regulator Output

Power

(1.8V 80mA Supply for

Hermes VCC)

Vcore Regulator Inpit

Power

(Supply VBAT)

(for Light1,2,3)

VMIC Regulator Output (2.5V

Power

2mA Supply for Mic Bias)

Vcore Regulator Output (1.8V

Power

80mA Supply for Hermes VCC)

VMEM Regulator Inpit

Power

(Supply VBAT)

External Microphone signal)

Internal Microphone signal)

tor Terminal

VMEM Regulator Inpit

Power

(Supply VBAT)

age select (H:VMEM=1.8V

L:VMEM=2.8V set 2.8V)

Power

Vback Regulator Intput

Power

VSIM Regulator Intput

Power

VRTC Regulator Input

SemiPowerAMP (Not used)

(connect VBAT)

SemiPowerAMP (Not used)

(Connect Melody IC YMU765)

(Connect Melody IC YMU765)

External Microphone Bias)

PIN No. Name I/O Discription of Terminal

96 R16 AIN1N I AudioInput 1 (-) (Used for

Internal Microphone Bias)

97 T1 RESET O RESET Output

98 T2 VMEM

VMEM Regulator Output

Power

(1.8V/2.8V selectable 150mA

Supply for IrDA Module)

99 T3 VMEM

VMEM Regulator Output

Power

(1.8V/2.8V selectable 150mA

Supply for IrDA Module)

100 T4 VBACK

VBACK Regulator Output

(1.85V/2.85V set by "VBACK-

Power

SELL" pin 50mA Supply for

Memory)

101 T5 VBACKSEL I VBACK Regulator Output

select connect GND:2.85V

102 T6 VSIM

VSIM Regulator Output (1.8V/

Power

2.85V set by software 20mA

Supply for SIM Interface)

103 T7 VRTC

VRTC Regulator Output

Power

(1.8V 20uA Supply for RTC in

Hermes)

104 T8 SGND − GND

(Return POWER SPWR)

105 T9 AOUT2N O Audio Output 1 (-) 8Ω Audio

SemiPowerAMP (Not used)

106 T10 SPWR - POWER Supp ly For AOUT 2

(connect VBAT)

107 T11 AOUT2P O Audio Output 1 (+) 8Ω Audio

SemiPowerAMP (Not used)

108 T12 LDOEN O Regulator enable output

(Not Used)

109 T13 KEYOUT O Power-On Key Ou tp ut

(Open drain)

110 T14 KEYON I Power-On Key input

111 T15 IBIAS O Internal Bias setting register

(1.2KΩ between GND)

112 T16 AGND4 −

Power managiment Analog GND

113 E5 AGND0 − GND (Thermal/Analog GND)

114 E6 AGND0 − GND (Thermal/Analog GND)

115 E7 AGND0 − GND (Thermal/Analog GND)

116 E10 AGND0 − GND (Thermal/Analog GND)

117 E11 AGND0 - GND (Thermal/Analog GND)

118 E12 AGND0 − GND (Thermal/Analog GND)

119 F5 AGND0 − GND (Thermal/Analog GND)

120 F6 AGND0 − GND (Thermal/Analog GND)

121 F7 AGND0 − GND (Thermal/Analog GND)

122 F10 AGND0 − GND (Thermal/Analog GND)

123 F11 AGND0 − GND (Thermal/Analog GND)

124 F12 AGND0 − GND (Thermal/Analog GND)

125 G5 AGND0 − GND (Thermal/Analog GND)

126 G6 AGND0 − GND (Thermal/Analog GND)

127 G7 AGND0 − GND (Thermal/Analog GND)

128 G10 AGND0 − GND (Thermal/Analog GND)

129 G11 AGND0 − GND (Thermal/Analog GND)

130 G12 AGND0 − GND (Thermal/Analog GND)

131 K5 AGND0 − GND (Thermal/Analog GND)

132 K6 AGND0 − GND (Thermal/Analog GND)

TM100 OTHERS

7 – 3

Page 23

CONFIDENTIAL DRAFT

PIN No. Name I/O Discription of Terminal

133 K7 AGND0 − GND (Thermal/Analog GND)

134 K10 AGND0 − GND (Thermal/Analog GND)

135 K11 AGND0 − GND (Thermal/Analog GND)

136 K12 AGND0 − GND (Thermal/Analog GND)

137 L5 AGND0 − GND (Thermal/Analog GND)

138 L6 AGND0 − GND (Thermal/Analog GND)

139 L7 AGND0 − GND (Thermal/Analog GND)

140 L10 AGND0 − GND (Thermal/Analog GND)

141 L11 AGND0 − GND (Thermal/Analog GND)

142 L12 AGND0 − GND (Thermal/Analog GND)

143 M5 AGND0 − GND (Thermal/Analog GND)

144 M6 AGND0 − GND (Thermal/Analog GND)

145 M7 AGND0 − GND (Thermal/Analog GND)

146 M10 AGND0 − GND (Thermal/Analog GND)

147 M11 AGND0 − GND (Thermal/Analog GND)

148 M12 AGND0 − GND (Thermal/Analog GND)

IC105 (YMU762): Sound IC

PIN No. Name I/O Discription of Terminal

1 CLKI I Clock input

2 LED O LED Drive

3 /IRQ O Interrupt Request

4 /RST I Hardware Reset

5NC − No connection

6 PLLC − Capacitor for PLL

7VDD

8 VSS - Ground

9 VREF O Reference Voltage

10 HPOUT-L/MONO O Headphone out left channel

11 HPOUT-R O Headphone out right channel

12 EQ1 O equalizer

13 EQ2 O equalizer

14 EQ3 O equalizer

15 SPVDD − Power for Speaker Amp

16 SPVSS − GND for Speaker Amp

17 SPOUT1 O Speaker Out1

18 SPOUT2 O Speaker Out2

19 MTR O Motor Control

20 D7 I/O Data Bus Bit7 (CPU I/F)

21 D6 I/O Data Bus Bit6 (CPU I/F)

22 D5 I/O Data Bus Bit5 (CPU I/F)

23 D4 I/O Data Bus Bit4 (CPU I/F)

24 D3 I/O Data Bus Bit3 (CPU I/F)

25 D2 I/O Data Bus Bit2 (CPU I/F)

26 D1 I/O Data Bus Bit1 (CPU I/F)

27 D0 I/O Data Bus Bit0 (CPU I/F)

28 /WR I WR Enable (CPU I/F)

29 /CS − Chip Select (CPU I/F)

30 A0 O Address (CPU I/F)

31 /RD O RD Enable (CPU I/F)

Power

Power Supply

(monoral output)

PIN No. Name I/O D iscription of Terminal

32 IOVDD I I/O interface Power (3V)

IC106 (AD6529): Digital BaseBand LSI

PIN No. Name I/O Discription of Terminal

1 A1 ASDO O Audio Serial port Data Out-

2 A2 BSDI I Baseband Serial port Data

3 A3 BSOFS I Baseband Serial port Data

4 A4 GPIO_48 I GPIO (Input for Headset

5A5VINT

6 A6 GPO_29 O GPO (To Typhoon

7 A7 GPO_5 O GPO

8 A8 VDDRTC

9A9VSSRTC − RTC Power Return (GND)

10 A10 MC_DAT[0] I/O Multi-media Card Data[0]

11 A11 GPIO_22 O GPIO [Use for Output LCDC

12 A12 Boot control[0]/

GPIO_56

13 A13 KEYPADCOL[4] O Key Column STB

14 A14 KEYPADCOL[1] O Key Column STB

15 A15 KEYPADROW[4] I Key ROW Input

16 A16 KEYPADROW[2] I Key ROW Input

17 A17 IRQ/GPIO_38 I InterruptRequest from

18 A18 GPIO_36 O for feeding BIAS on Audio

19 B1 ASDI I Audio Serial port Data Intput

20 B18 GPIO_35 O Not used

21 C1 ADD[0] O Processor ADDress [0]

22 C3 ASFS I Audio Serial po rt Da ta Fram e

23 C4 BSIFS I Baseband Serial port Input

24 C5 BSDO O Baseband Serial port Data

25 C6 CSDI I Control Serial Data Input

26 C7 GPO_6 O Not used

27 C8 GPO_0 O GPO (To Tyohoon

28 C9 OSCOUT O 32KHz X'tal (for RTC clock)

29 C10 MC_DAT[2] I/O M ul t i - m e di a C a r d D at a [ 2 ]

30 C11 VMC

31 C12 VCC

put (to Typhoon ASDI)

Input (to Typhoon BSDO)

Frame Signal Input

(to Typhoon BSIFS)

Switch Monitor)

Power

Interface Power 1.8V

ABBRESET)

(To Tyohoon AM :B.B T&R

Advanced State Machine)

Power

RTC Power (1.8V)

(Not use)

Register Select (RSP)]

Use Boot contr o l [0]

I

(Connect to Logic level “H”)

YMU765 (sound)

AOUT3

(to Typhoon ASDIO)

Signal Input

(to Typhoon ASFS)

Frame Signal

(to Typhoon BSOFS)

Output (to Typhoon BSDI)

(to Typhoon CSDO)

RXON[Base Band Rx ON]

(Not use)

Power for Multi MediaCard

Power

(VAPP 3.0V supplied)

Power for Core

Power

(VCORE 1.8V supplied)

TM100 OTHERS

7 – 4

Page 24

CONFIDENTIAL DRAFT

PIN No. Name I/O Discription of Terminal

32 C13 KEYPADCOL[3] O Key Column STB

33 C14 KEYPADCOL[2] O Key Column STB

34 C15 GPIO_39 O GPIO

35 C16 IRQ/GPIO_37 I InterruptReques t from

36 C18 GPIO_34 I GPIO [Use for Reading

37 D1 ADD[4] O Processor ADDress [4]

38 D3 ADD[2] O Processor ADDress [2]

39 D4 GND − GND

40 D15 KEYPADROW[0] I Key ROW Input

41 D16 VEXT

42 D18 GPO_23 O GPO [Use for Smart Combo

43 E1 ADD[7] O Processor ADDress [7]

44 E3 VMEM

45 E5 ADD[1] O Processor ADDress [1]

46 E6 CSDO O Control Serial Data Output

47 E7 CLKOUT_GATE I Hardware CLK ON/OFF input

48 E8 GPO_1 O GPO [use for Base Band Tx

49 E9 OSCIN I 32KHz X'tal (for RTC clock)

50 E10 M C_CMD O Multi-media Card Command

51 E11 Boot control[1]/

GPIO_55

52 E12 GND − GND

53 E13 KEYPADROW[3] I Key ROW Input

54 E14 KEYPADROW[1] I Key ROW Input

55 E16 GPIO_33 O Not used

56 E18 GPIO_17 O Not used

57 F1 ADD[11] O Processor ADDress [11]

58 F3 ADD[9] O Processor ADDress [9]

59 F5 ADD[5] O Processor ADDress [5]

60 F6 ADD[3] O Processor ADDress [3]

61 F7 GND − GND

62 F8 VCC

63 F9 PWRON O Power ON/OFF control output

64 F10 MC_DAT[1] I/O Multi-media Card Data[1]

65 F11 GND − GND

66 F12 VEXT

67 F13 KEYPADCOL[0] O Key Column STB

68 F14 VEXT

69 F16 GPIO_15 O Not used

[Use for InterfaceIC USB

Pullup control (PUAEpin)]

Typhoon

Hardware REV.]

External I/O Power

Power

(VINT 3.0V)

RAM Sleep State Control SCCE2)

Memory I/F Power

Power

(VMEM 3.0V)

(to Typhoon CSDI)

[From Typhoon MCLKEN]

ON (Active)]

(Not use)

I Use Boot control[1]

(Connect to Logic level “L”)

Power for Core

Power

(VCORE 1.8V supplied)

[to Typhoon DBBON]

(Not use)

External I/O Power

Power

(VINT 3.0V)

External I/O Power

Power

(VINT 3.0V)

PIN No. Name I/O Discription of Terminal

70 F18 GPIO _16 I GPI O [U se f or Reading Hard-

ware REV.]

71 G1 ADD[13] O Processor ADDress [13]

72 G3 ADD[12] O Processor ADDress [12]

73 G5 ADD[8] O Processor ADDress [8]

74 G6 ADD[6] O Processor ADDress [6]

75 G13 GPO_22 O [Use for LCDC HOST I/F

Register Select]

76 G14 GPIO_14 O Not Used

77 G 16 G PI O _10 I GPIO [Us e for USB power

DETECT SENSE]

78 G18 GPIO_12 O GPIO [Use for LCDC RESET]

79 H1 VMEM

Memory I/F Power

Power

(VMEM 3.0V)

80 H3 ADD[14] O Processor ADDress [14]

81 H5 GND − GND

82 H6 VCC

Power for Core

Power

(VCORE 1.8V supplied)

83 H8 ADD[10] O Processor ADDress [10]

84 H9 CLKOUT O Clock out to Typhoon MCLK

85 H10 MC_DAT[3] I/O Multi-media Card Data[3]

(Not use)

86 H11 GND − GND

87 H13 GND − GND

88 H14 IRQ/GPIO_13 I Interrupt from Camera

89 H16 GPIO_7 I [Use for Headset detect

Sense]

90 H18 GPIO_9 O Not Used

91 J1 ADD[19] O Processor ADDress [19]

92 J3 ADD[17] O Processor ADDress [17]

93 J5 ADD[18] O Processor ADDress [18]

94 J6 ADD[15] O Processor ADDress [15]

95 J8 ADD[16] O Processor ADDress [16]

96 J9 CSFS I Control Serial Frame signal

(From Typhoon CSFS)

97 J10 MC_CLK O Multi-media Card Clock

(Not use)

98 J11 VCC

Power for Core

Power

(VCORE 1.8V supplied)

99 J13 GPIO_11 I GPIO[Used for Slide sense

Hall IC)

100 J14 GPIO_8 I GPIO[Use for sensing head-

set stero or monoral]

101 J16 G PI O_ 5 O Not Used

102 J18 IRQ/GPIO_6 I Interrupt from LCDC

103 K1 ADD[22] O Processor ADDress [22]

104 K3 ADD[21] O Processor ADDress [21]

105 K5 CLKOUTMUX1 /

GPIO_40

OCLKOUT

(13MHz Use for Camera)

106 K6 ADD[20] O Processor ADDress [20]

107 K8 GND − GND

108 K9 ADD[23] O Processor ADDress [23]

109 K10 GND −

110 K11 VEXT

External I/O Power

Power

(VINT 3.0V)

TM100 OTHERS

7 – 5

Page 25

CONFIDENTIAL DRAFT

PIN No. Name I/O Discription of Terminal

111 K13 GND − GND

112 K14 GPIO_4 I GPIO [Use for Reading Hard-

113 K16 GPIO_2 O GPIO [Use for USB power

114 K18 GPIO_3 O Not Used

115 L1 DATA[2] I/O Processor DATA [2]

116 L3 DATA[0] I/O Processor DATA [0]

117 L5 DATA[5] I/O Processor DATA [5]

118 L6 DATA[1] I/O Processor DATA [1]

119 L8 DATA[3] I/O Processor DATA [3]

120 L9 VCC

121 L10 DMINUS I/O USB Data [D-]

122 L11 TCK/GPIO_18 O JTAG test clock

123 L13 GND − GND

124 L14 IrDA Rx/GPIO_1 I Generic Serial Port for

125 L16 USC[5] O Use for external Serial I/F RTS

126 L18 IrDA Tx/GPIO_0 O Generic Serial Port for

127 M1 DATA[4] I/O Processor DATA [4]

128 M3 VMEM

129 M5 GND − GND

130 M6 VCC

131 M13 USC[6] I Use for sense Car kit

132 M14 VCC

133 M16 USC[2] O Use for external Serial I/F RTS

134 M18 USC[4] I Use for external Serial I/F CTS

135 N1 DATA[7] I/O Processor DATA [7]

136 N3 DATA[6] I/O Processor DATA [6]

137 N5 GND − GND

138 N6 DATA[9] I/O Processor DATA [9]

139 N7 DATA[13] I/O Processor DATA [13]

140 N8 NROMCS1 O Use for NOR Flash ROM

141 N9 Diplay_CS/

GPIO_42

142 N10 CLKIN I Clockinput 13MHz

143 N11 VSIM

144 N12 GND − GND

145 N13 USC[3] I Use for development tool

146 N14 USC[1] I Use for external Serial I/F Rx

147 N16 GND − GND

148 N18 USC[0] O

ware REV.]

regulator out put Current

Control signal]

Power for Core

Power

(VCORE 1.8V supplied)

IrDA[Used for IrDA Rx Input

(From IrDA Module)]

IrDA[Used for IrDA Tx Output

(From IrDA Module)]

Memory I/F Power

Power

(VMEM 3.0V)

Power for Core

Power

(VCORE 1.8V supplied)

Connect I/F connector

(CN702 6pin)

Power for Core

Power

(VCORE 1.8V supplied)

CE# (Chip Enable)

O Use for LCDC Chip Select

(connect to IC702 22pin)

(From RF Block TCXOUT)

Power for SIM I/F

Power

(VSIM 2.85V supplied)

only (Not used)

Use for external Serial I/F Bsync

PIN No. Name I/O Discription of Terminal

149 P1 DATA[0] I/O Processor DATA [ 0 ]

150 P3 DATA[8] I/O Processor DATA [ 8 ]

151 P5 NRD O Processor RD# (ReaD)

152 P6 DATA[14] I/O Processor DATA [8]

153 P7 GND − GND

154 P8 NRAMCS2 O Use for PSRAM1 CE1#

(Chip Enable)

155 P9 GPIO_44 I Not used (Connect to VINT

through Register)

156 P10 VSSUSB

power

GND for USB BLOCK

157 P11 GPIO_47 O Use for CAMERA Module

RESET

158 P12 TDI/GPIO_20 I Use for development tool

only (Not used)

159 P13 CLKON O OSC ON/OFF (Connect to

Typhoon VCXOEN)

160 P14 VCC

Power for Core

Power

(VCORE 1.8V supplied)

161 P16 GPO_18 O GPO

[Use for RF Serial control SYN]

162 P18 GPO_21 O Use RF_BLOCK SY NT HEN

163 R1 DATA[12] I/O Processor DATA [12]

164 R3 DATA[11] I/O Processor DATA [11]

165 R4 NWE O Processor WE#

(Write Enable)

166 R15 VEXT

External I/O Power

Power

(VINT 3.0V)

167 R16 GPO_11 O Use for RF_BLOCK

(BS4 Band Select)

168 R18 GPO_20 O GPO [Use for RF Serial

control SYNTHDATA]

169 T1 DATA[15] I/O Processor DATA [15]

170 T3 VMEM

Memory I/F Power

Power

(VMEM 3.0V)

171 T4 NADV O Address Latch Enable for

Super AND Flash ROM

(connect to Memory ALE)

172 T5 NGPCS1 O Chip Enable for Super AND

Flash ROM (connect to

Memory SF-CE#)

173 T6 VMEM

Memory I/F Powe

Power

(VMEM 3.0V)

174 T7 GPIO_45 O Use for SRAM CE1#

(Chip Enable)

175 T8 SOUND_CS/

GPIO_46

O Use for S ound LSI Chip

Select (YMU762 CS)

176 T9 DPLUS I/O USB Data [D+]

177 T10 SIMCLK O SiM Card Clock

178 T11 JTAGEN I JT AG Enable

(For development tool only)

179 T12 VEXT

External I/O Power

Power

(VINT 3.0V)

180 T13 GPO_3 O Not used

181 T14 GPO_4 O GPO [Use for Interface

Mode select 1 (MODSEL1)]

182 T15 GPO_7 O Not used

183 T16 GPO_16 O Use for RF_BLOCK

(BS1 Band Select)

TM100 OTHERS

7 – 6

Page 26

CONFIDENTIAL DRAFT

PIN No. Name I/O Discription of Terminal

184 T18 GPO_17 O Use for RF_BLOCK

185 U1 NHWR O Upper Byte Enable for

186 U18 GPO_19 O GPO [Use for Interface

187 V1 NLWR O LowerByteEnable for PSRAM

188 V2 NWAIT I Processor Bus Wait

189 V3 NRESET I Sy s t em R e s et ( F ro m V I NT

190 V4 BURSTCLK O Not used

191 V5 NRAMCS1 O Chip Enable for SPAM2

192 V6 NAUXCS1 O Command Latch Enable for

193 V7 CAMCS/GPIO_43 O Use for CAMERA Module

194 V8 VDDUSB

195 V9 GPIO_23 O Use for SIM I/F Reset

196 V10 SIMDATAIO I/O SIM I/F DATA

197 V11 GPIO_24 O Use for Sound IC (YMU762)

198 V12 TMS/GPIO_19 O Use for development tool

199 V13 TMDO/GPIO_21 O Use for development tool

200 V14 GPO_2 O GPIO[Use for NOR Flash

201 V15 GND − GND

202 V16 GPO_8 O Use for IrDA mod ule Pow er

203 V17 GPO_9 O Use for RF_BLOCK

204 V18 GPO_10 O

IC109 (NJ287130): Voltage Regulator

PIN No. Name I/O Discription of Terminal

1 CONT I ON/OFF Control

2GND − GND

3 NB O Noise Bypass

4 VOUT O Regulated Output

5 VIN I Unregulated Input Voltage

IC701 (BU7870): Interface IC

PIN No. Name I/O Discription of Terminal

1 MODESEL1 I Mode Select1

2 MODESEL2 I Mode Select2

3 UART_RXD O Host UART_RXD

4 UART_TXD I Host UART_TXD

5CPU_VDD

6 UART_RTS I Host UART_RST

(BS2 Band Select)

PSRAM (UB#)

Mode select 1 (MODSEL3)]

(LB#)

(Connect to LCDC WAIT)

Detector IC)

(connect to Memory SC-CE1#)

Super AND Flash ROM

(connect to Memory CLE)

Chip select

VUSB Block Power

Power

(VUSB 3.0V supplied)

Reset

only (Not used)

only (Not used)

Memory Write Protect (WP#)]

ON/OFF

(BS3 Band Select)

Use for LCDC Buffer OFF con-

Connect LCDC BUFOFF)

trol (

(CONT

1.6V--ON)

u

(3.0V CONT:on)

(appear Battey Voltage)

Power

Power for Host Interface

PIN No. Name I/O D iscription of Terminal

7 BSYNC I Host Serial Sync

8 UART_CTS O Host UART_CTS

9 BDATA I Host Serial DATA

10 BCNT I Host Serial Control

11 MODESEL2 I Mode Select3

12 TXANAOUT O Analog Output

(To Analog BaseBand Chip)

13 RXANAIN I Analog Input

(From Analog BaseBand C hip)

14 GND1 − GND

15 RXANAOUT O Analog Output

(To I/F Connector)

16 RXANAIN I Analog Input

(From I/F Connector)

17 NC − No Connection

18 BDATA/CTS I/O (I n:C T S O u t BDATA )

19 BSYNC/RTS O BSYNC RTS

(To I/F Connector)

20 USBD-/TXD I/O USB Data- /UART TXD

(To I/F Connector)

21 GND2 − GND

22 USBD+/RXD I/O USB Data+ /UART RXD

(To I/F Connector)

23 CPU_USB_D+ I/O USB Data+

(To Digital BaseBand Chip)

24 CPU_USB_D- I/O USB Data-

(To Digital BaseBand Chip)

25 REG3.3V

Power Supply For USB

Power

Config Register

26 PU15 O Switched Power Supply For

USB Config Register

27 PUAE I PU15 Controll

28 GND3 − GND

IC702 (TK73840B): Voltage Regulator

PIN No. Name I/O D iscription of Terminal

1 A1 VCONT I On/OFF Control

2 A2 Bin I Power for Internal circuit

Power

3A3Vin

Unregurated Input

4 B1 PCL I Output Current Control

5B2NC − No Connection

6B3GND − GND

7 C1 VFB I Feedback

8 C2 VSENSE I Output Voltage Sense

9 C3 Vout O Regurated Output

IC704 (LR38863): LCDC

PIN No. Name I/O D iscription of Terminal

1 A1 DUMMY4 − Soldering Check

2 A2 VDDPLL

3 A3 G NDPLL

4 A4 PLLDIV0 I SET PLL Divide code set [0]

5 A5 PLLDIV1 I SET PLL Divide code set [1]

6 A6 HSD0 I Hyper Serial Data Bus[0]

7 A7 HSD1 I Hyper Serial Data Bus[1]

Power

VDD for PLL Block (1.8V)

Power

GND for PLL Block

(Not used)

(Not used)

TM100 OTHERS

7 – 7

Page 27

CONFIDENTIAL DRAFT

PIN No. Name I/O Discription of Terminal

8 A8 HSD2 I Hyper Serial Data Bu s[2]

9 A9 HSWRD I Hyper Serial write/read

10 A10 HSEN I Hyper Serial Enable

11 A11 HSCK − Hyper Serial Clock (Not Used)

12 A12 DUMMY3 − Soldering Check

13 B1 P W M1/Port 8 O PWMOUT/Port8 (Not used)

14 B2 PLLDV2 O SET PLL Divide code set [ 2 ]

15 B3 VDDCORE

16 B4 GND

17 B5 SUBWR_B O Write for Driver (Not Used)

18 B6 GND

19 B7 VDDCORE

20 B8 PWM0 /Port3 O Port3 (To LCD Unit RESET)

21 B9 SUBCS_B O SUB LCD CS (Not used)

22 B10 CS_B I HOST I/F Chip Select

23 B11 VDDIO

24 B12 LCDINT O HOST I/F INTerrupt request

25 C1 GTDIO_B O MPEG4 ASIC I/F (Not used)

26 C2 VDDIO

27 C3 SUBDB1 I/O SUB LCD Data Bus[1]

28 C4 BDATA5 O LCD DATA Blue[5]

29 C5 BDATA4 O LCD DATA Blue[4]

30 C6 BDATA3 O LCD DATA Blue[3]

31 C7 GND

32 C8 TEST1 I LSI TEST (Connect to GND)

33 C9 BSH _ B I /O MPEG4 ASIC I/F

34 C10 WR_B I HOST I/F Write

35 C11 SUBRS O SUB LCD Reg sel (Not used)

36 C12 MP4RESET_B O For External Divice RESET

37 D1 HSD6 I/O Hyper Serial DATA [6]

38 D2 BDATA2 O LCD DATA Blue [ 2]

39 D3 BDATA1 O LCD DATA Blue [ 1]

40 D4 BDATA0 O LCD DATA Blue [ 0]

41 D5 EXCS_B1 O External Chip Select

42 D6 XOUT O X’tal

43 D7 VDDIO

44 D8 GND

45 D9 SCANEN I LSI TEST MODE SET

46 D10 RD_B I HOST I/F Read

47 D11 RSP I HOST I/F Register Select

48 D12 GND

49 E1 HSD3 I Hyper Serial Data Bus [3]

50 E2 DCLK O LCD Timing Clock

51 E3 VSYNC O LCD Timing VSYNC

52 E4 HSYNC O LCD Timing HSYNC

(Not used)

select (Not Used)

(Not Used)

Power

VDD for Core Block (1.8V)

Power

GND

Power

GND

Power

VDD for Core Block (1.8V)

Power

VDD for Host I/F Block (3.0V)

Power

VDD for Host I/F Block (3.0V)

(Not used)

Power

GND

(Not used, Connect to GND)

(Not Used)

Power

VDD for Host I/F Block (3.0V)

Power

GND

(Connect to GND)

Power

GND

(Not used)

PIN No. Name I/O D iscription of Terminal

53 E5 EXCS_B3 O External Chip Select

54 E6 XIN I X’tal

55 E7 SUBDB6 I/O SUB LCD Data Bus [ 6 ]

(Not used)

56 E8 RESET_B I LCDC master reset

57 E9 SUBDB0 I/O SUB LCD Data Bus [ 0 ]

(Not used)

58 E10 SUBDB2 I/O SUB LCD Data Bus [2 ]

(Not used)

59 E11 HSD5 I Hyper Serial Data Bus [5 ]

(Not used)

60 E12 DB 0 0 I /O Host Data Bus [0 0 ]

61 F1 HSD4 I Hyper Serial Data Bus [4 ]

(Not used)

62 F2 EXCS_B2 O External Chip Select

63 F3 GDATA5 O LCD DATA Green [5 ]

64 F4 GDATA4 O LCD DATA Green [4 ]

65 F5 GDATA3 O LCD DATA Green [3 ]

66 F6 SUBDB3 I/O SUB LCD Data Bus [3]

(Not used)

67 F7 SUBDB4 I/O SUB LCD Data Bus [4]

(Not used)

68 F8 HSD7 I Hyper Serial Data Bus [7 ]

(Not used)

69 F9 DB01 I/O Host Data Bus [01]

70 F 1 0 DB02 I/O Ho s t Data Bus [02]

71 F 1 1 DB03 I/O Ho s t Data Bus [03]

72 F 1 2 DB04 I/O Ho s t Data Bus [04]

73 G1 STKCHK I LSI TEST MODE SET

(Connect to GND)

Power

74 G2 VDDCORE

75 G3 GND

76 G4 VDDIO

VDD for Core Block (1.8V)

Power

GND

Power

VDD for Host I/F Block (3.0V)

77 G5 G DAT A 2 O LCD DATA Green [2 ]

78 G6 SUBDB5 I/O SUB LCD Data Bus [5]

(Not used)

79 G7 BSCLK O MPEG4 LSI Clock (Not used

and Connect to GND)

80 G8 SUBCLK O SUB LCD CLOCK (Not used)

81 G9 DB 05 I/O Host Data Bus [05]

Power

82 G10 VDDIO

83 G11 GND

84 G12 VDDCORE

VDD for Host I/F Block (3.0V)

Power

GND

Power

VDD for Core Block (1.8V)

85 H1 CAMCK O CAMERA CLOCK (Not used)

86 H2 GDATA1 O LCD DATA Green [1 ]

87 H3 GDATA0 O LCD DATA Green [0 ]

88 H4 RDATA5 O LCD DATA Red [5]

89 H5 RDATA4 O LCD DATA Red [4]

90 H6 VDDCORE

Power

VDD for Core Block (1.8V)

91 H7 PWMLCD O PWM (Not used)

92 H8 BSBLK_B I MPEG4 Data Enable

(Not used and Connect to GND)

93 H9 DB06 I/O Host Data Bus [06]

94 H10 DB07 I/O Ho st Data Bus [07]

TM100 OTHERS

7 – 8

Page 28

CONFIDENTIAL DRAFT

PIN No. Name I/O Discription of Terminal

95 H11 DB08 I/O Host Data Bus [08]

96 H12 DB09 I/O Host Data Bus [09]

97 J 1 VDDIO

98 J 2 RDATA3 O LCD DATA Red [3 ]

99 J 3 RDATA2 O LCD DATA Red [2 ]

100 J4 RDA TA1 O LCD DATA Red [1]

101 J5 RDA TA0 O LCD DATA Red [0]

102 J6 MP4_P0 O MP4 Power Control

103 J7 EXCS_B0 O External Chip Select

104 J8 BSPIXEL7 I γcompensation DATA [7 ]

105 J9 BSVS_B O MP4 Vsync

106 J10 DB 10 I/O Host Data Bus [10]

107 J11 DB 11 I/O Host Data Bus [11]

108 J12 DB 12 I/O Host Data Bus [12]

109 K1 MP4_PLLCK O MP4 CLK

110 K2 SUBDB7 I/O SUB LCD Data Bus [7]

111 K3 GND

112 K4 DA0 I

113 K5 BSPIXEL0 I γcompensation DATA

114 K6 DCS_B I Chip select Decode

115 K7 VDDIO

116 K8 BSPIXEL6 I γcompensation DATA

117 K9 SE_DO O Serial Data Out

118 K10 DB13 I/O Host Data Bus [13]

119 K11 DB14 I/O Host Data Bus [14]

120 K12 DB15 I/O Host Data Bus [15]

121 L1 WAIT_B O Host Wait

122 L2 SUBFLMIN I SUBLCD FLAME signal input

123 L3 SUBCKS O SUBLCD Clock Select s ignal

124 L4 DA1 I

125 L5 BSPIXEL1 I γcompensation DATA

126 L6 BSPIXEL4 I γcompensation DATA

127 L7 GND

128 L8 BSPIXEL5 I γcompensation DATA

129 L9 SE_CK O Serial Clock

130 L10 SE_LD2 O Serial Load [2] (BD6015 Load)

131 L11 BUFFOFF_B I Host I/F Buffer Gate

132 L12 VDDIO

133 M1 DUMMY2 − Soldering Check

134 M2 SE_LD3 O Out Port6

Power

VDD for Host I/F Block (3.0V)

(Not used)

(Not used and connect to GND)

(Not used and connect to GND)

(Not used Connect to GND)

(Not used)

Power

GND

Chip select Decode Address [0]

(Connect to GND)

(Not used and connect to GND)

(Connect to GND)

Power

VDD for Host I/F Block (3.0V)

(Not used and connect to GND)

(Not used)

input (Not used)

Chip select Decode Address [1]

(Connect to GND)

(Not used and connect to GND)

(Not used and connect to GND)

Power

GND

(Not used and connect to GND)

Power

VDD for Host I/F Block (3.0V)

[0]

[6]

[1]

[4]

[5]

PIN No. Name I/O D iscription of Terminal

135 M3 VDDIO

Power

VDD for Host I/F Block (3.0V)

136 M4 SUBLPIN I SUBLCD LP (Not used)

137 M5 BSPIXEL2 I γcompensation DATA

(Not used and connect to G ND)

138 M6 BSPIXEL3 I γcompensation DATA

(Not used and connect to G ND)

139 M7 VDDCORE

140 M8 SE_DI I

Power

VDD for Core Block (1.8V)

Serial Data In

(Not used and connect to GND)

141 M9 SE_LD1 O Serial Data Load [1]

(to LCD driver)

Power

142 M10 GND

143 M11 VDDCORE

GND

Power

VDD for Core Block (1.8V)

144 M12 DUMMY1 - Soldering Check

IC1001 (LZ6P3711): CCD CAMERA

PIN No. Name I/O Discription of Terminal

1GND − GND (Digital GND)

Power

2 VDD1

3 A19 I Address A19

4 A18 I Address A18

5 A17 I Address A17

6 A2 I Address A2

7 A1 I Address A1

8GND − GND (Digital GND)

9 OD15 I/O DATA DQ15

10 OD 14 I/O D AT A DQ14

11 OD 13 I/O D AT A DQ13

12 OD 12 I/O D AT A DQ12

13 OD 11 I/O D AT A DQ11

14 OD 10 I/O D AT A DQ10

15 OD9 I/O DATA DQ9

16 OD8 I/O DATA DQ8

17 OD7 I/O DATA DQ7

18 OD6 I/O DATA DQ6

19 OD5 I/O DATA DQ5

20 OD4 I/O DATA DQ4

21 OD 3 I/O DATA DQ14

22 OD2 I/O DATA D2

23 OD1 I/O DATA D1

24 OD0 I/O DATA D0

25 GN D − GND (Digital GND)

26 CTL3 O (Control 3) Not use

27 MO DE I Movie SELECT

28 CTL2 O (Control 2) Not use

29 TE ST 4 I Not use

30 +13V

31 -7V

32 AVDD

33 AGND − GND (Analog GND)

34 CBRE Q O DMA Request (Not used)

For DSP Core ( supplied 2.5V)

(Connect to GND)

Power

For sensor (supplied +13V)

Power

For sensor (supplied -7V)

Power

For V_Drive (supplied. 3.0V)

[2]

[3]

TM100 OTHERS

7 – 9

Page 29

CONFIDENTIAL DRAFT

PIN No. Name I/O Discription of Terminal

35 CINT O Interrupt Request

36 RSTN I Reset

37 RDB I READ Enable

38 WRB I Write Enable

39 CSB I Chip Select

40 PWCK I Clock out (Not use)

41 VDD2

42 EXCKI I Clock input

CN101 : Main-LCD Connector (LCD PWB)

PIN No. Name I/O Discription of Terminal

1GND − GND

2V-CAM

3V-CAM

4GND − GND

5GND − GND

6GND − GND

7 D[15] I/O Data Bus Bit15 (CPU I/F)

8 D[14] I/O Data Bus Bit14 (CPU I/F)

9 D[13] I/O Data Bus Bit13 (CPU I/F)

10 D[12] I/O Data Bus Bit12 (CPU I/F)

11 D[11] I/O Data Bus Bit11 (CPU I/F)

12 D[10] I/O Data Bus Bit10 (CPU I/F)

13 D[9] I/O Data Bus Bit9 (CPU I/F)

14 -7V

15 D[8] I/O Data Bus Bit8 (CPU I/F)

16 LEDB − Not used

17 D[7] I/O Data Bus Bit7 (CPU I/F)

18 LEDG − Not used

19 D[6] I/O Data Bus Bit6 (CPU I/F)

20 LEDR − Not used

21 D[5] I/O Data Bus Bit5 (CPU I/F)

22 VPUS2 − Not used

23 D[4] I/O Data Bus Bit4 (CPU I/F)

24 123 − Not used

25 D[3] I/O Data Bus Bit3 (CPU I/F)

26 +13V

27 D[2] I/O Data Bus Bit2 (CPU I/F)

28 /RD O RD Enable (CPU I/F)

29 D[1] I/O Data Bus Bit1 (CPU I/F)

30 /WE O WR Enable (CPU I/F)

31 D[0] I/O Data Bus Bit0 (CPU I/F)

32 VCCD

33 GND − GND

34 GND − GND

35 GND − GND

CN102 Main-LCD Connector (MAIN PWB)

PIN No. Name I/O Discription of Terminal

1 T-COM O COM for CS

2 T-COM O COM for CS

Power

For I/O (supplied 3.0V)

Power

AVDD for Vido Driver (3.0V)

Power

AVDD for Vido Driver (3.0V)

Power

-7V (for CAMERA sensor)

Power

+13V (for CAMERA sensor)

Power

VDD1 for DSP_Core (2.5V)

PIN No. Name I/O Discription of Terminal

3 TFT-COM O COM V

4COMC I

5COMC ICOM

6 COMDC I COM center

7VCOMH I

8B0 OBLUE[0]

9B1 OBLUE[1]

10 B2 O BLUE[2]

11 B3 O BLUE[3]

12 B4 O BLUE[4]

13 B5 O BLUE[5]

14 G0 O GREEN[0]

15 G1 O GREEN[1]

16 G2 O GREEN[2]

17 G3 O GREEN[3]

18 G4 O GREEN[4]

19 G5 O GREEN[5]

20 R0 O RED[0]

21 R1 O RED[1]

22 R2 O RED[2]

23 R3 O RED[3]

24 R4 O RED[4]

25 R5 O RED[5]

26 DCLK O Dot CLK

27 HSY O Hsync

28 VSYNC O Vsync

29 SO − NC

30 SI O Serial IN

31 SCLK O Serial CLK

32 CS O Chip select

33 RESET O RESET IN

34 VCC

Power

VCC 3.0V

35 GND − GND

36 GND − GND

37 VDC

38 VDC

Power

Power

VDC 3.0V

VDC 3.0V

39 COM2 I Common2

40 VCL AM P O VCL AMP

41 VSS2 −

42 NC −

43 VSS1 −

44 NC −

45 VDD2 −

46 C5- − CAP547 C5+ − CAP5+

48 C4- − CAP449 C4+ − CAP4+

50 C3- − CAP351 C3+ − CAP3+

52 C2- − CAP2-

TM100 OTHERS

7 – 10

Page 30

CONFIDENTIAL DRAFT

PIN No. Name I/O Discription of Terminal

53 C2+ − CAP2+

54 C1- − CAP155 C1+ − CAP1+

56 VDC2 −

57 VDC2 −

58 VR −

59 VS −

60 VS −

CN103 (CAMERA FPC Connector) (MAIN PWB)

PIN No. Name I/O Discription of Terminal

1GND − GND

2 SP1 O Speaker OUT1

3 SP2 O Speaker OUT2

4 D[8] I/O Processor DATA [8]

5 D[7] I/O Processor DATA [7]

6 D[6] I/O Processor DATA [6]

7 D[5] I/O Processor DATA [5]

8 D[9] I/O Processor DATA [9]

9 D[10] I/O Processor DATA [10]

10 D[11] I/O Processor DATA [11]

11 D[4] I/O Processor DATA [4]

12 D[3] I/O Processor DATA [3]

13 D[2] I/O Processor DATA [2]

14 D[1] I/O Processor DATA [1]

15 D[0] I/O Processor DATA [0]

16 D[12] I/O Processor DATA [12]

17 D[13] I/O Processor DATA [13]

18 D[14] I/O Processor DATA [14]

19 A1 O Processor Address [1]

20 D[15] I/O Processor DATA [15]

21 A2 O Processor Address [2]

22 A17 O Processor Address [17]

23 A18 O Processor Address [18]

24 A19 O Processor Address [19]

25 VDD_A − VDD1 for DSP_Core (2.5V)

26 CK O Clock 13M Hz

27 VINT − VDD2 for I/O (+3.0V)

28 CM_CS_N O Camera Chip select

29 -7V − -7V (sensor)

30 V_CAM − AVDD for Vido Driver (3.0V)

31 +13V − +13V (CCD DRIVER)

32 CINT I Interrupt Request

33 CM_RST_N O RESET

34 OE_N O Processor RD

35 WE_N O Processor WE

36 LEDG O Not used

37 123 O Not used

38 LEDB O Not used

39 LEDR O Not used

PIN No. Name I/O Discription of Terminal

40 VPUS2 − Not used

CN704 : UP-DOWN Switch Connector

PIN No. Name I/O Discription of Terminal

1 UP O KEYPADCOL[1]

2 Down O KEYPA DCOL[2]

3 COMMON I KEYPADROW[0]

4GND − GND

CN704 : Shutter Switch Connector (MAIN PWB)

PIN No. Name I/O Discription of Terminal

1GND − GND

2 SW1 O KEYPADCOL[3]

3 SW2 I/O KEYPADROW[0]

4GND − GND

CN101 Main-LCD Connector

PIN No. Name I/O Discription of Terminal

1GND − GND

2V-CAM

3V-CAM

4GND − GND

5GND − GND

6GND − GND

7 D[15] I/O Data Bus Bit15 (CPU I/F)

8 D[14] I/O Data Bus Bit14 (CPU I/F)

9 D[13] I/O Data Bus Bit13 (CPU I/F)

10 D[12] I/O Data Bus Bit12 (CPU I/F)

11 D[11] I/O Data Bus Bit11 (CPU I/F)

12 D[10] I/O Data Bus Bit10 (CPU I/F)

13 D[9] I/O Data Bus Bit9 (CPU I/F)

14 -7V

15 D[8] I/O Data Bus Bit8 (CPU I/F)

16 LEDB − Not used

17 D[7] I/O Data Bus Bit7 (CPU I/F)

18 LEDG − Not used

19 D[6] I/O Data Bus Bit6 (CPU I/F)

20 LEDR − Not used

21 D[5] I/O Data Bus Bit5 (CPU I/F)

22 VPUS2 − Not used

23 D[4] I/O Data Bus Bit4 (CPU I/F)

24 123 − Not used

25 D[3] I/O Data Bus Bit3 (CPU I/F)

26 +13V

27 D[2] I/O Data Bus Bit2 ( (CPU I/F)

28 /RD O RD Enable (CPU I/F)

29 D[1] I/O Data Bus Bit1 (CPU I/F)

30 /WE O WR Enable (CPU I/F)

31 D[0] I/O Data Bus Bit0 (CPU I/F)

32 VCCD

33 GND − GND

34 GND − GND

Power

AVDD for Vido Driver (3.0V)

Power

AVDD for Vido Driver (3.0V)

Power

-7V (for CAMERA sensor)

Power

+13V (for CAMERA sensor)

Power

VDD1 for DSP_Core (2.5V)

TM100 OTHERS

7 – 11

Page 31

CONFIDENTIAL DRAFT

PIN No. Name I/O Discription of Terminal

35 GND − GND

CN102 Main-LCD Connector

PIN No. Name I/O Discription of Terminal

1GND − GND

2GND − GND

3VINT

4VINT

5 VBAT

6 VBAT

7VCORE

8TEP − Not used

9 LIGHT3 O KEY LED DRIVE

10 NC − Not used

11 LEDG − Not used

12 USB_CCNT I USB_ Regulator Current

13 BUFOFF O To LCDC_BUF Control

14 LCDRSP O To LCDC_Register Select

15 LCDWAIT I From LCDC WAIT

16 LCDRESET O To LCDC_Reset

17 LCDINT I From LCDC Interrupt

18 LCDCS O To LCDC_Chip Select

19 PONKEY I Power ON_KEY

20 KEYP ADROW[4] I KEY MATRIX

21 KEYP ADROW[3] I KEY MATRIX

22 KEYP ADROW[2] I KEY MATRIX

23 KEYP ADROW[1] I KEY MATRIX

24 KEYP ADROW[0] I KEY MATRIX

25 KEYPADCOL[4] O KEY MATRIX

26 KEYPADCOL[0] O KEY MATRIX

27 VBAT_B L

28 GND − GND

29 GND − GND

30 GND − GND

31 AGND − GND

32 RECEIVER- O RECEIVER33 RECEIVER+ O RECEIVER+

34 GND − GND

35 GND − GND

Power

Power

Power

Power

Power

Power

3.0V

3.0V

Battery

Battery

VCORE 1.8V

Control

Request

Battery

CN703 Main-Key Connector (LCD PWB)

PIN No. Name I/O Discription of Terminal

1GND − GND

2 KEYPADCOL[0] O KEY MATRIX

3 KEYPADCOL[4] O KEY MATRIX

4 KEYPADROW[0] I KEY MATRIX

5 KEYPADROW[1] I KEY MATRIX

6 KEYPADROW[2] I KEY MATRIX

7 KEYPADROW[3] I KEY MATRIX

8 KEYPADROW[4] I KEY MATRIX

9 POWER_ON_KEY I POW ER O N KEY

10 LED O LED DRIVE [L IGHT3]

11 BAT

Power

Data Bus Bit11 (CPU I/F)

JK101 HEADSET CONNECTOR

PIN No. Name I/O Discription of Terminal

1AGND − ON/OFF Control

T1.6V--ON)

(CONT

u

2 JMIC I Microphone (with BIAS)

3 JAOK I Head-set sense (detect)

4 JEARR O Earphone Right ch (mono)

5 JEARL O Earphone Left ch (mono)

6 MON/ST I Stereo/monoral Sense

7NC − No connect

8 RCSW I Remote Control SW

9NC − No connect

10 DGND − GND

CN705 Main-Key Connector (LCDC PWB)

PIN No. Name I/O Discription of Terminal

1 RECEIVER_

2 RECEIVER_ + O RECEIVER_ +

3 BACK_LIGHT A[1] O Back light White

4 BACK_LIGHT K[1] I Back light White

5 BACK_LIGHT A[2] O Back light White LED

6 BACK_LIGHT K[2] I Back light White

-

O RECEIVER_

-

LED ANODE [1]

LED CATHODE [1 ]

ANODE [ 2 ]

LED CATHODE [2 ]

TM100 OTHERS

7 – 12

Page 32

CONFIDENTIAL DRAFT

CN101 Main-Key Connector (KEY PWB)

PIN No. Name I/O Discription of Terminal

1GND − GND

2 KEYPADCOL [ 0 ] O KEY MATRIX

3 KEYPADCOL [ 4 ] O KEY MATRIX

4 KEYPADROW [ 0 ] I KEY MA TRIX

5 KEYPADROW [ 1 ] I KEY MA TRIX

6 KEYPADROW [ 2 ] I KEY MA TRIX

7 KEYPADROW [ 3 ] I KEY MA TRIX

8 KEYPADROW [ 4 ] I KEY MA TRIX

9 POWER_ON_KEY I POWER ON KEY

10 LED O LED DRIVE [LIGHT3]

11 BAT

CN702 Interface Connector

Power

Data Bus Bit11 (C PU I/F)

USB Cable Connect

PIN

I/O I/O I/O

No.

1 − GND − GND − GND

2 I/O USBD+ I RXD I RXD

3I/OUSBD- ITXD OTXD

4 I USB Power I − I

5 I Power Supply −

6 I RESERVED I (RESERVED) I (RESERVED)

7 − SYNC O RTS O Audio Out

8 I Manufacture I Manufac ture I Manufacture

9 − I CTS I Audio in

10 − GND − GND − GND

Serial Cable

Connect

(Power S upp ly )

Car Kit Connect

(Power Supply)

−

TM100 OTHERS

7 – 13

Page 33

q

COPYRIGHT2004 BY SHARP CORPORATION

All rights reserved.

Printed in Japan.

No part of this publication may be reproduced,

stored in a retrieval system, or transmitted.

In any form or by any means,

electronic, mechanical, photocopying, recording, or otherwise,