Page 1

)

SHARP

SERVICE

MANUAL

PDSMX81013-MZ

ft'

In

Ill.

In

RS-232C

Serial Interface Card

MZ-SBI03

, "

•.•• " ...... , .... ~ ..

~I

.......

GP-IB Interface Card

MZ-SBI04

FEATURES

MZ·8BI03

•

A

serial

interface card

for

MZ·80B. capable

of

converting parallel 8-bits data

to

serial data

to

transmit

and

receive.

• Integrating

two

channeis

of

interface conforming

to

RS·232C (JIS·C·6361)

into

one board.

• Employment

of

Z·80SI0/0.

one

of

Z·80 famiiy, enabling

to

deal

with

various interrupts.

MZ·8BI04

• GP·IB

interface card

for

MZ·80B, capable

of

freely controlling measuring instrument groups

conforming

to I EC

standards

~

~E-488

and enabling

low

cost, automatic measuring system.

•

Capable

of

programming

by

improved BASIC .

~~

..................................................................

..

SHARP

CORPORATION

Page 2

~-------Contents--------

MZ·8BI03

Specifications.................................................

1

General information

.................................•...•.......

2

Description

of

circuit

...............................•............

3

Troubleshooting. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

• . . . . . . . . . . • . .

..

8

Test program

..................................................

10

PWB

and

circuit

diagram

..........................................

15

MZ-BBI04 Specifications

.................................................

18

Description

of

circuit

................................•....•••...•

19

Troubleshooting

..............................•.....•........•..

23

PWB

and

circuit

diagram

........................•..•.•....•.......

27

Packing method

........................

'

................•.•....•...••....

30

Replacement parts list

...........................................•.....••..

31

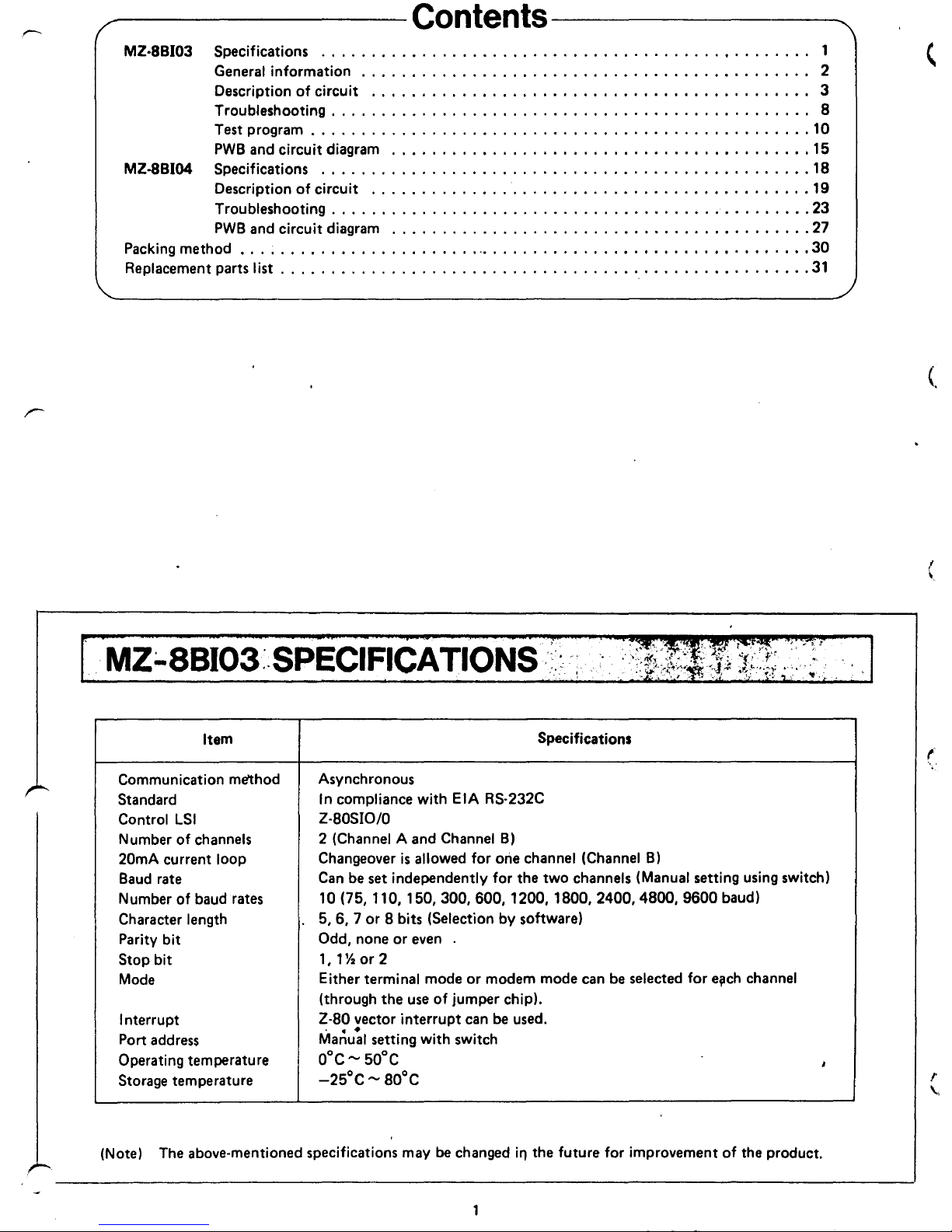

MZ:..8BI03:.SPECIFICATIONS

,~,~,

Item

Communication me'thod

Standard

Control

LSI

Number

of

channels

20mA current loop

Baud

rate

Number

of

baud

rates

Character length

Parity

bit

Stop

bit

Mode

Interrupt

Port

address

Operating temperature

Storage temperature

Specifications

Asynchronous

In compliance

with

EIA

RS·232C

Z·80SIO/0

2 (Channel A and Channel B)

Changeover

is

allowed

for

orie channel (Channel

B)

Can

be

set

independently

for

the

two

channels (Manual setting using switch)

10(75,110,

150,300,600,

1200,

1800,2400,4800,

9600 baud)

5,

6, 7

or

8 bits (Selection

by

software)

Odd, none

or

even

.

1,

1

Y.

or

2

Either terminal mode

or

modem mode

can

be

selected

for

ellch channel

(through the

use

of

jumper chip).

Z·80 vector

interrupt

can

be

used.

,

..

Manual setting

with

switch

O°C-

50°C

-25°C-

80°C

(Note) The above·mentioned specifications may be changed ir, the future

for

improvement

of

the product.

<.

f

" '

r

"

Page 3

)

)

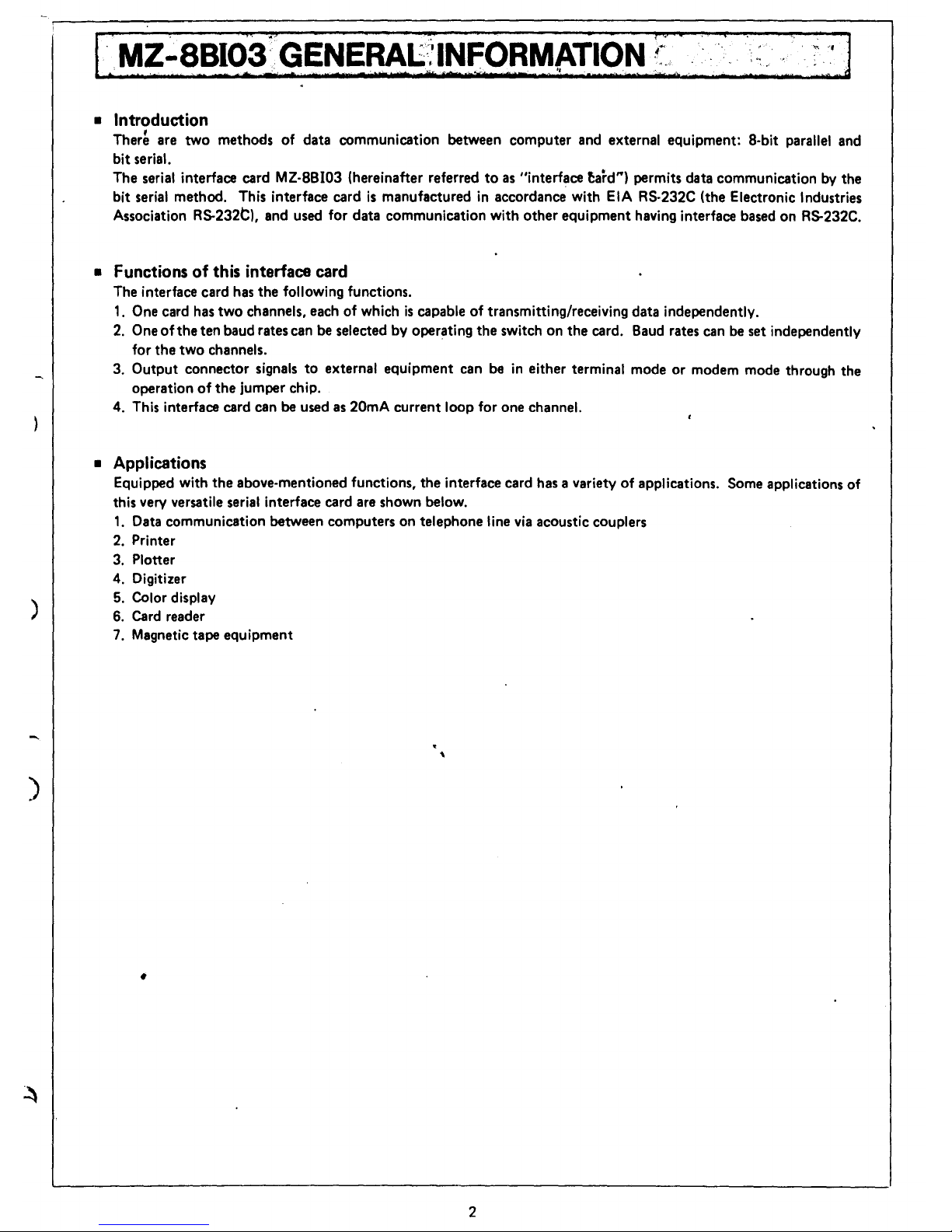

• Introduction

Ther~

are

two

methods

of

data communication between

computer

and external equipment: S-bit parallel and

bit

serial.

The serial interface card MZ-SBI03 (hereinafter referred

to

as "interface

~ard")

permits data communication by the

bit

serial method. This interface card

is

manufactured in accordance with EIA RS-232C (the Electronic Industries

Association RS-232t::), and used for data communication with

other

equipment having interface based

on

RS-232C.

•

Functions

of

this

interface

card

The interface card has

the

following functions.

1.

One card has

two

channels, each

of

which

is

capable

of

transmitting/receiving data independently.

2.

One

of

the

ten baud rates can be selected by operating

the

switch

on

the

card. Baud rates can be set independently

for

the

two

channels.

3.

Output

connector signals

to

external equipment can be

in

either terminal mode

or

modem mode through the

operation

of

the

jumper chip.

4. This interface card can be used as

20mA current loop for one channel.

•

Applications

Equipped with

the

above-mentioned functions,

the

interface card has a variety

of

applications. Some applications

of

this very versatile serial interface card are shown below.

1.

Data communication between computers on telephone line via acoustic couplers

2. Printer

3.

Plotter

4. Digitizer

5.

Color display

6.

Card reader

7. Magnetic tape equipment

.

\

•

2

Page 4

)

.~

)

•

n

3::

~

N

n

c

~

;+

I

D

....

~

~

TxDB

./

Current

~

0

ex»

RS-232CI

Loop

~

&.

e

ca

RxDB

Drive

~

Current Loop

Cl)

Select

3

0

DTRB

CA)

Co"",,'

••

' q

-)

Mode

Channel B

Select

Connector

C

(J-2)

v

m

RS-232C

~

en

~

Drive

/

0

Rml

I

..

CTSB

:D

..

-

DCDB

I (J-1)

"

....

-

H~~'Cb

0

furt

H

Z

Add'~~

Address -

Bus

Select

TxDA

.

',"~

.

:-

W

0

Circuit

..

RxDA

"

RS-232C

Mode

Channel A

• '.""',.1-,.

RTSA

Drive

Select

Connector

0

-

CTSA

DTRA I

(J-3)

I:D

0

DCDA

c:

-

+5V~

['m

~

Power

Chlnnel A

.~;~";

Supply

BR2

Baud Rate Setting

(SW-21

Blud

Rate

t',

Circuit

v..;..#

-12V

Oscillltion

f~";

Circuit

Channel B

.:\

BR1

14

Baud Rate Setting

(SW-31

.

'C

r·._

-

-

-

Page 5

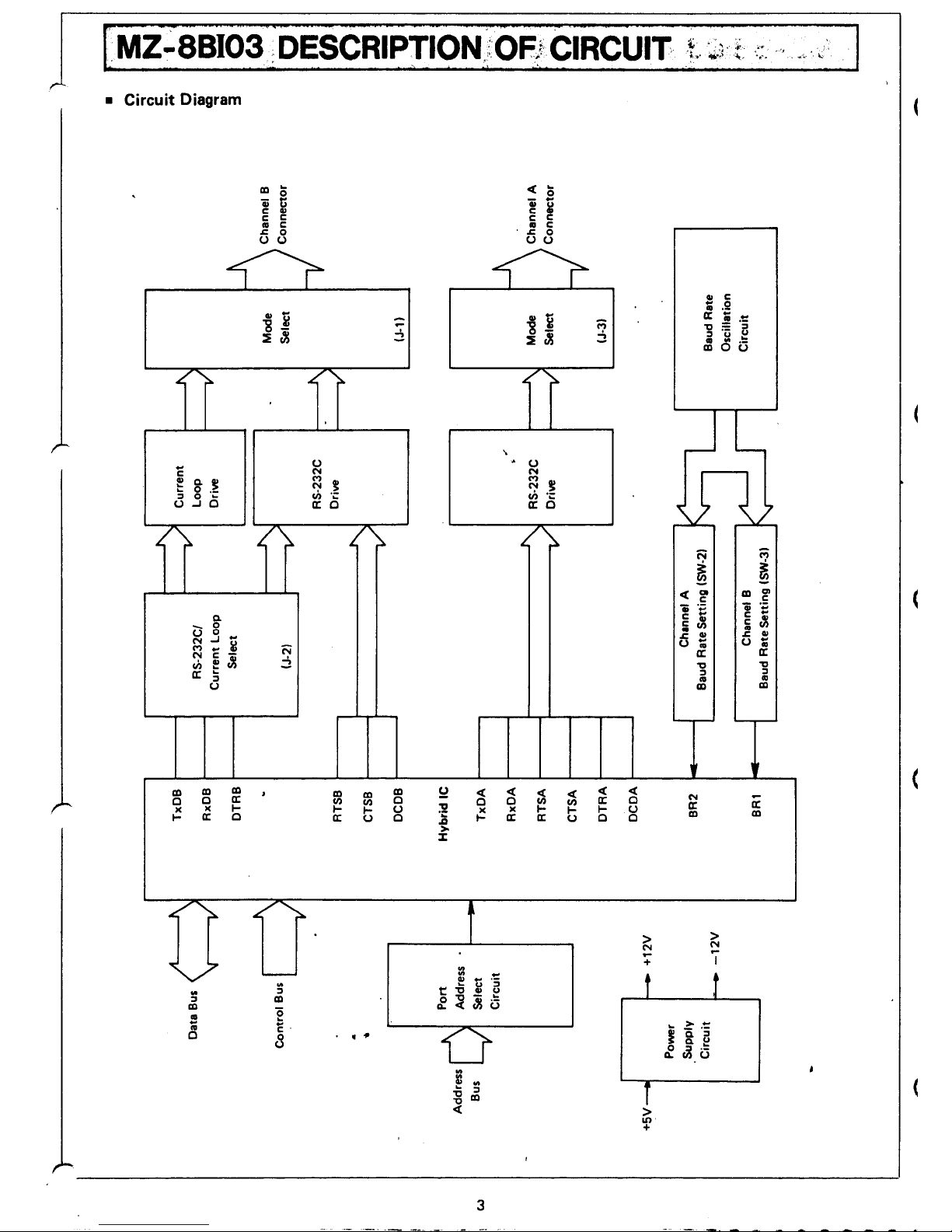

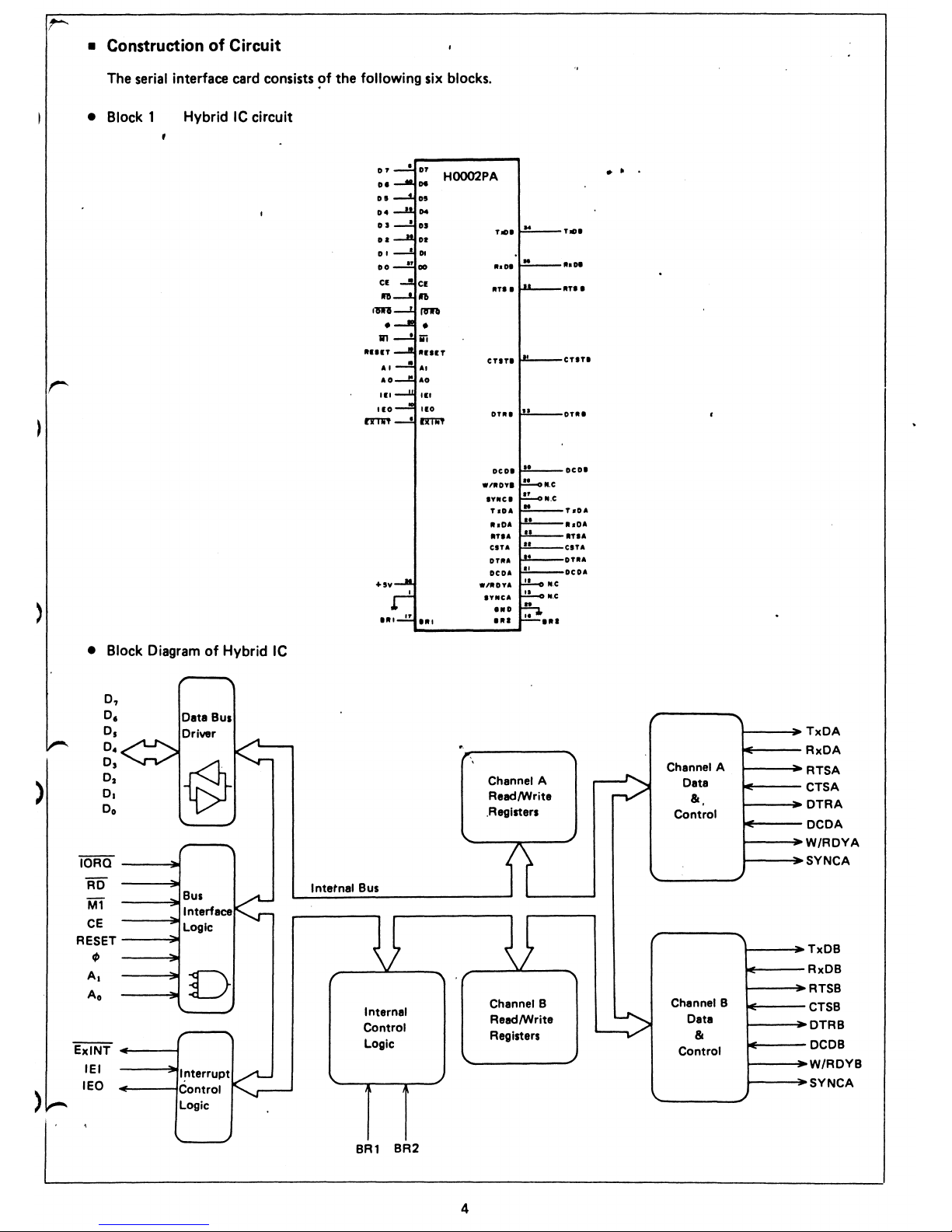

• Construction

of

Circuit

The

serial

interface

card

consists

?f

the following six blocks.

• Block

1

Hybrid

IC

circuit

D'

D'

HOOO2PA

01

D.

D'

D'

.

..,.

01

D'

00

IhO'

Cl

It"

•

1111

.1JII1i

rntI

• •

In

1t11'T

CTITI

A'

r

AD

'1'

'1'

'10

.10

DTItI

..

rnn

• RT1il

DCDI

••

.,.0

....

N.C

IY"CI

..

N.C

,.DA

H

••

0&

..

It'l.

CITA

DT

••

DCD"

+.v

.,,,oYA

'''''CA

)

IND

U.

U.

•

••

•

Block Diagram

of

Hybrid IC

0,

D.

Data BUI

0,

Driver

<:>

~

..

0

Channel A

Read/Writa

.Reglsters

D.

0,

)

O

2

D.

Do

lr

Bus

fG:

Intetnal Bus

Interface

Logic

U

U

D

Channel B

Internal

Read/Write

Control

Registers

Logic

IORO

RD

Ml

CE

RESET

~

A.

AD

ExlNT

~

I!"terrupt

Control

"-r--

Logic

IEI

IEO

)

I

BRl

BR2

4

•

•

.

..,

.

....

"TI'

C'I'I

DT.'

DCOI

'IDA

'hO&

ItTI"

CSTA

0'"''

DCO'

~

~

Channel A

Data

&

Control

Channel B

Data

&

Control

TxDA

RxDA

RTSA

CTSA

DTRA

DCDA

W/RDYA

SYNCA

TxDB

RxDB

RTSB

CTSB

DTRB

DCDB

W/RDYB

SYNCA

Page 6

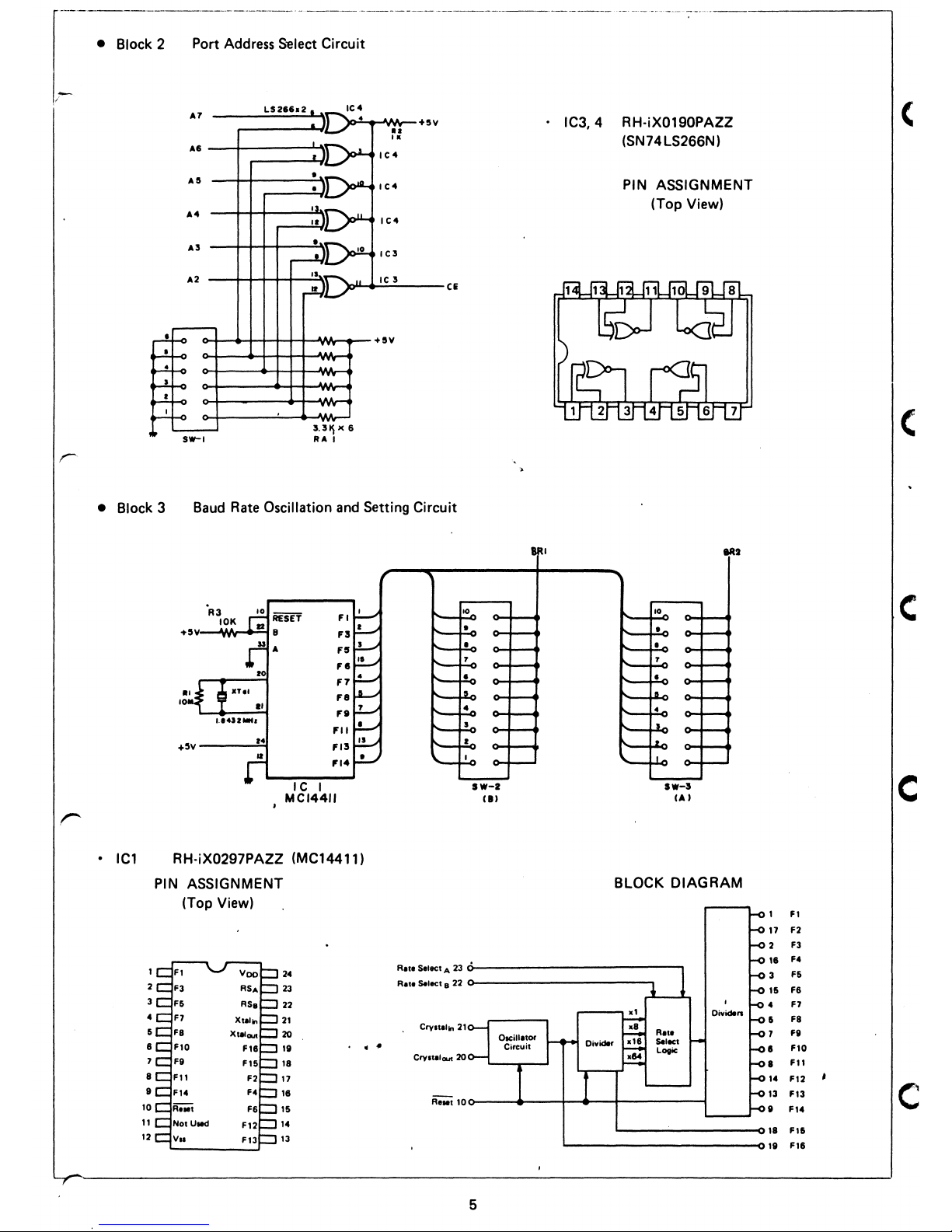

• Block 2

Port

Address

Select Circuit

147

A.

A'

144

145

142

SW-I

LS2&'h2

le4

5.51\"6

RA I

+5V

..

I.

I

e4

I

e4

le4

le5

le

5

CE

.SV

• Block 3

Baud

Rate

Oscillation

and

Setting Circuit

R~OK

10

REiE'f

.SV'-~""'+'"

B

II

I

.••

JI

....

+'V

___

---='.::j4

..

IC

I

MCI4411

ICl

RH·iX0297PAZZ

(MC144ll)

PIN

ASSIGNMENT

(Top View)

24

2

23

3

22

4

21

20

6

19

18

8

17

9

16

10

15

11

14

12

13

Rite

Sllect A 23

RI.I

Select 8

22

Cryltlljn 21

•

"

Cryltl1o..n:

20

R.Mt

10

sw-z

IBI

5

IC3,4

RH·iX0190PAZZ

(SN74LS266N)

PIN

ASSIGNMENT

(Top View)

1A2

BLOCK DIAGRAM

I

.1

Divide ...

Rill

Select

LotiC

(

(

c

c

Fl

11

f2

2

F3

16

F4

3

F5

15

f6

4

F7

5

F8

7

F9

e

Fl0

8

Fll

14

f12

13

FI3

C

11

F14

18 F16

19

F16

Page 7

)

)

)

)

)

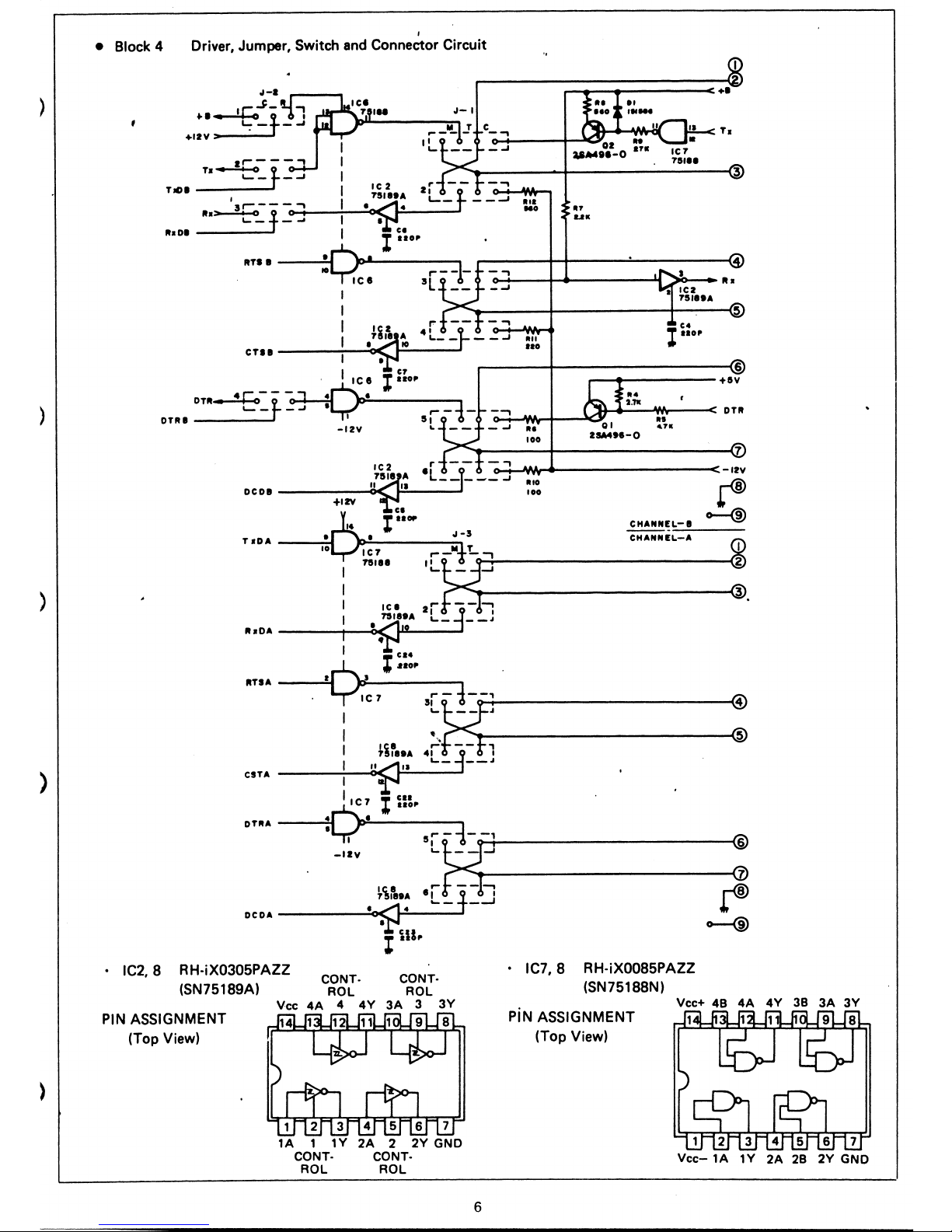

• Block 4

,

Driver, Jumper, Switch and Connector Circuit

./-1

L..

__

~

...

~.sf

1

+IIV"

TIDI

____

-.J

Ic2

, 751

..

"

It.

01

1

,....---...,

'<1

It.~

t

_000

~-iI--+-...:cO)(.~c:

I

..

o~

ItTlI

----=.~~..,..I'-----

...

-Y.:,

CTII

I

I

i

.~~~.;..-.

__

...

I

C1

.

IC'

l··o'

--,

-~

.,.

-

.

..

'.0

••

2.'111

+1

T.

6

+IIV

OTIt~-9-~'

•

'--r-...J

,--

-

OTltl

____

-.I

'

51

on

••

u •

-...,

-IIV

IC2

..

--'

..

'OO

DCDI

------c~1<

..

-'1----

...

~

"I'A

.10

100

+IZV

Cl

./-1

I··""

T

.DA

__

-:..,:

...

...

-

....

-IIV

r!>

CH"NNEL-I

~

CHANNEL-A

:.

~~II

I

r~-M

'L""1

ICI

,.. -:...,---------------

....

7511

..

21 , '

~

L._,

__

•

It.OA

----_.....c~;.c:-

...

.10

___

...

•

I

ca.

ItTIA

__

--It!.l~

:I;

••

01'

~C

7

I"

-

'1--

.... ' ___________

~~

:

~t::f-j------------------~@

I

~i~IIA

4r~1

:

~'.

L._ , __

•

I

,.

c

••

DTltA

___

.~.~II::

'"

..

01'

~

'[~

:

~'is~1A

'L_

j==~...,-,---------------r®

8

DCDA

-----....:.·OM~.

-

~

Iml'

CSTA

• IC2, 8 RH·iX0305PAZZ

(SN75189A)

CONT·

ROL

•

IC7,8

RH·iX0085PAZZ

(SN75188N)

PIN ASSIGNMENT

(Top View)

4A

4

4V

1

11

5

PiN ASSIGNMENT

(Top View)

Vcc+

48

1

38

1A

1

1V

CONT·

ROL

2A

2

2V

GND

CONT·

Vcc-

1A 1V

2A

28

2V

GND

ROL

6

Page 8

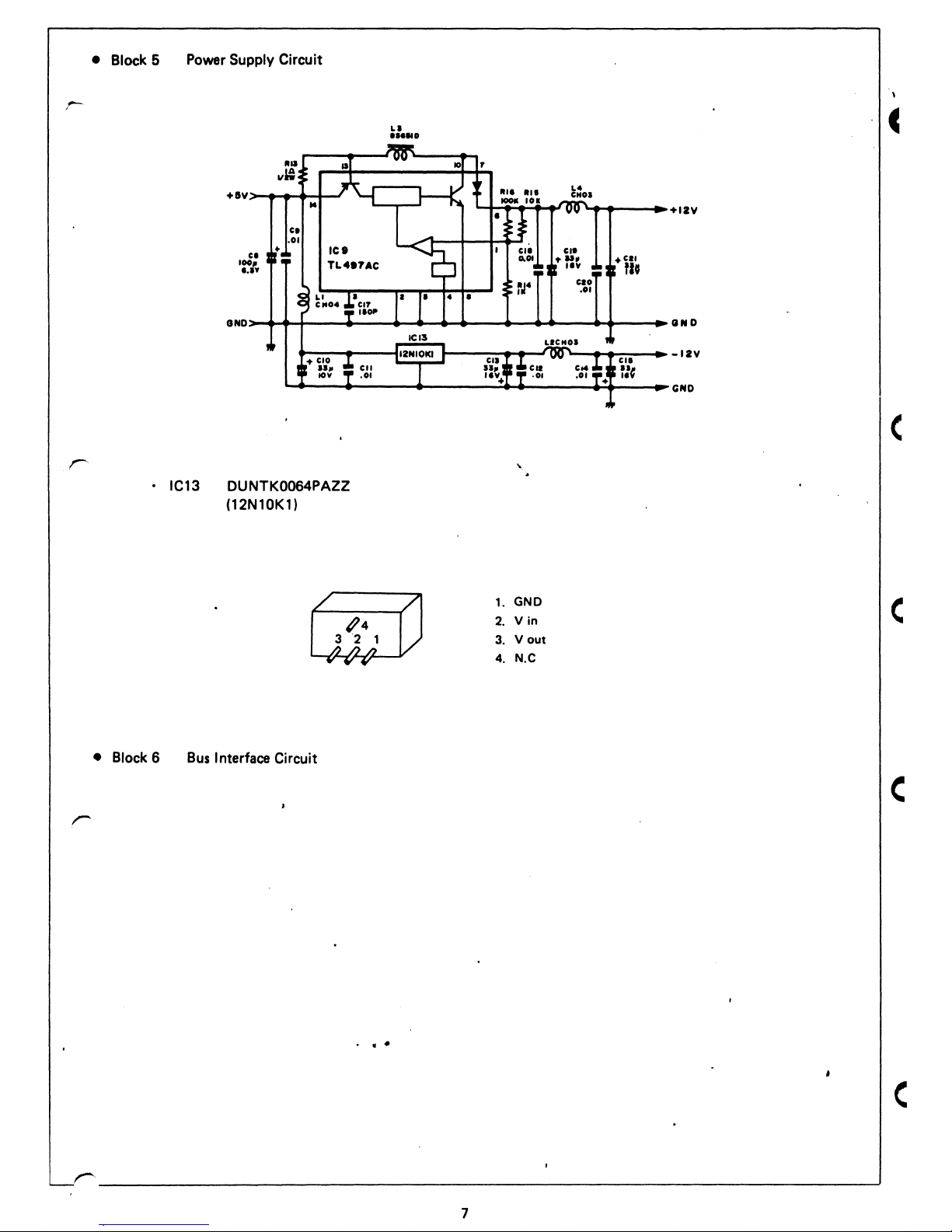

• Block 5

r

.

• Block 6

Power Supply Circuit

+

IV

ce

I~/.

aND

IC13

DUNTK0064PAZZ

(12N10K1)

LI

eH'"

~

LA1---V

Bus

Interface Circuit

.

..

+IIV

aND

cia

-IIV

U~

GND

,

1.

GND

2.

Vi"

3.

V out

4 .

N.C

~------------------------------------------------------------------------~

7

c

(

c

c

c

Page 9

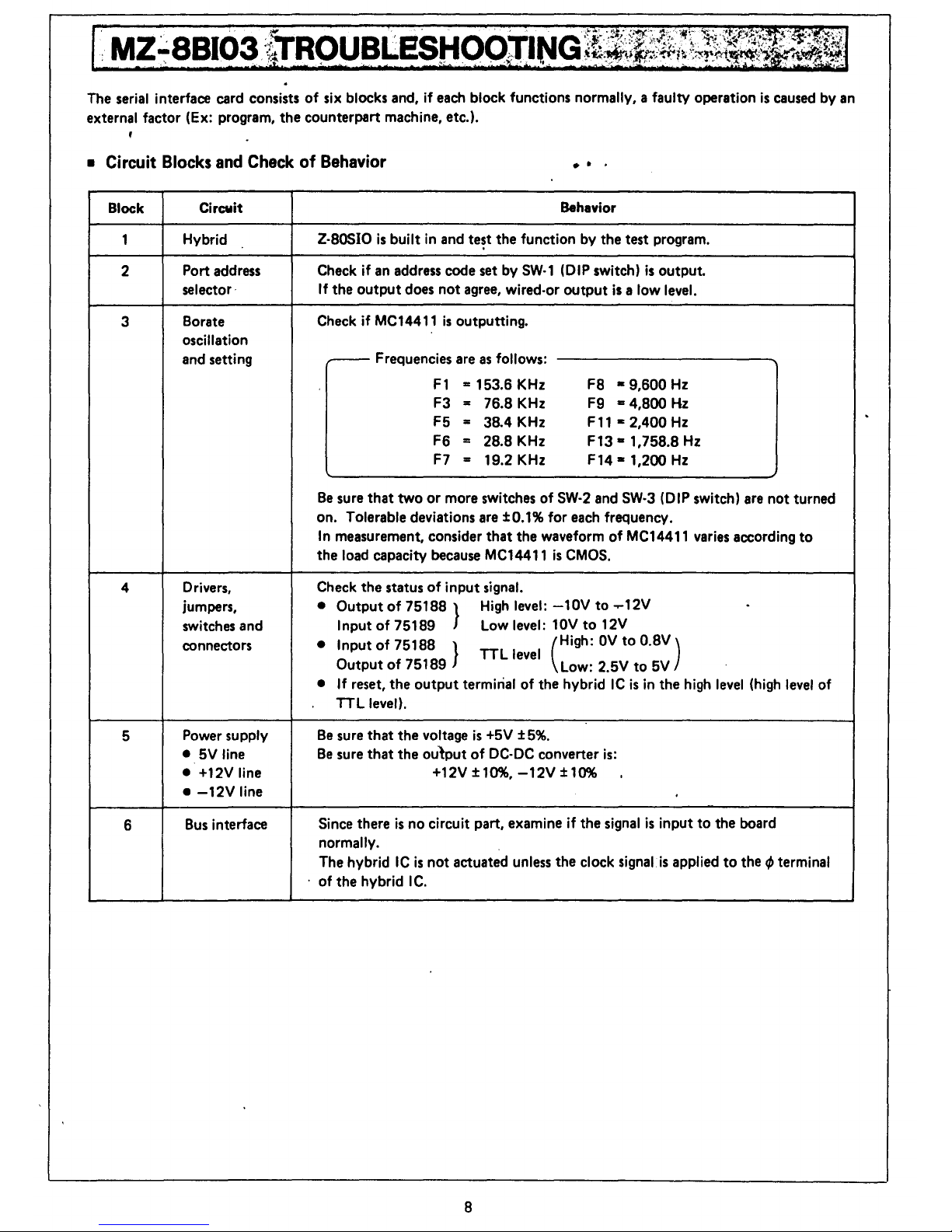

The

serial

interface card consists

of

six blocks and,

if

each

block functions normally, a faulty operation

is

caused

by

an

external factor (Ex: program, the counterpart machine, etc.) •

• Circuit Blocks and Check

of

Behavior

..

.

Block Circuit

Behavior

1

Hybrid

Z-80SIO

is

built

in

and

te~t

the function by the test program.

2

Port

address

Check

if

an

address

code

set

by

SW-1

(DIP switch)

is

output.

selector·

If

the

output

does

not

agree,

wired-or

output

is a low

level.

3

Borate

Check

if

MC14411

is

outputting.

oscillation

and

setting

r--

Frequencies

are

as

follows:

F1

.. 153.6 KHz

F8

• 9,600 Hz

F3

..

76.8 KHz F9

..

4,800 Hz

F5

..

38.4 KHz

F11

.. 2,400 Hz

F6

..

28.8 KHz

F13·

1,758.8

Hz

F7

..

19.2 KHz

F14·

1,200

Hz

Be

sure

that

two

or

more switches

of

SW-2

and

SW-3

(DIP switch)

are

not

turned

on.

Tolerable deviations

are

±0.1%

for

each

frequency.

In measurement, consider that the waveform

of

MC14411

varies

according

to

the load capacity

because

MC14411

is

CMOS.

4

Drivers,

Check the status

of

input

signal.

jumpers,

•

Output

of

75188 }

High

level:

-10V

to

....

12V

-

switches and

Input

of

75189

Low

level: 10V

to

12V

connectors

•

Input

of

75188 }

Ci9h:

OV

to

0.8V)

TTL

level

Output

of

75189

Low: 2.5V

to

5V

•

If

reset,

the

output

terminal

of

the hybrid

IC

is

in the high

level

(high

level

of

TTL

level).

5

Power supply

Be

sure

that the voltage

is

+5V ±

5%.

•

5V

line

Be

sure

that the

oulput

of

DC-DC converter

is:

• +12V line

+12V ±lO%,

-12V

±10%

0

•

-12V

line

6

Bus

interface

Since there

is

no circuit part, examine

if

the

signal

is

input

to

the board

normally.

The hybrid IC

is

not

actuated

unless

the clock signal

is

applied

to

the

q,

terminal

of

the hybrid I

C.

8

Page 10

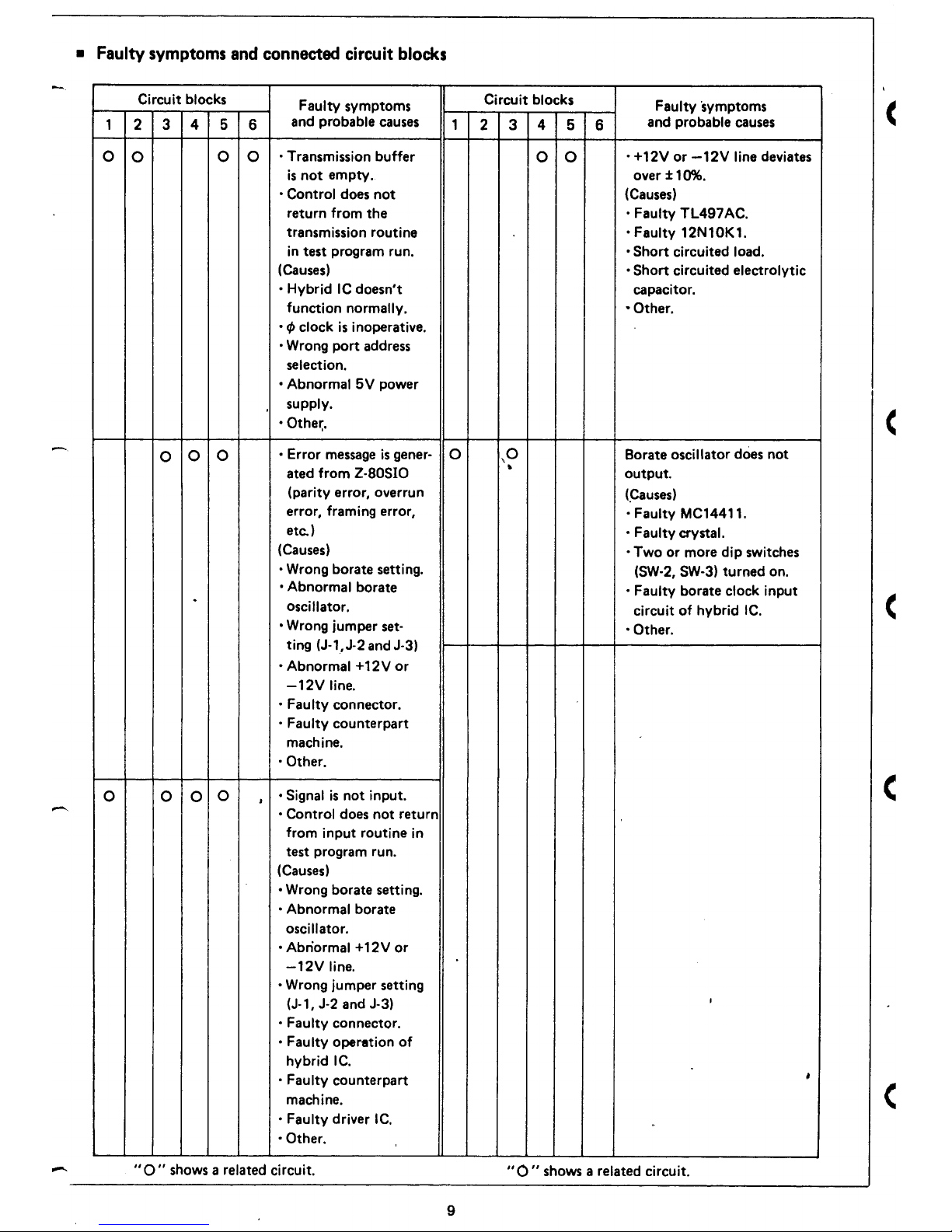

• Faulty

symptoms

and

connected

circuit

blocks

Circuit blocks

Faulty symptoms

Circuit blocks

Faulty 'symptoms

1

2

3 4 5

6

and

probable

causes

1

2 3 4 5

6

and

probable

causes

c

0

0

0 0

o Transmission buffer

0 0

o +12V or

-12V

line deviates

is

not

empty. over ±10%.

o Control

does

not

(Causes)

return from the o Faulty TL497 AC.

transmission routine

o Faulty 12N10K1.

in test program run.

o Short circuited load.

(Causes)

o Short circuited electrolytic

o Hybrid

IC

doesn't

capacitor .

function normally.

• Other.

o!p

clock

is

inoperative.

o Wrong port

address

selection.

• Abnormal

5V

power

supply.

o

Othe~.

(

0

0

0

o Error

message

is

gener-

0

,0

Borate oscillator

does

not

ated

from

Z·80SIO

•

output.

(parity error, overrun

(Causes)

error, framing error,

o Faulty MC14411.

etc.)

o Faulty crystal.

(Causes)

o Two or more

dip

switches

o Wrong borate setting.

(SW-2,

SW-3)

turned

on.

o Abnormal borate

o Faulty borate clock input

.

oscillator.

circuit

of

hybrid

IC.

o Wrong jumper

set-

o Other.

(

ting (J-1,J-2

and

J-3)

o Abnormal +12V

or

-12V

line.

o Faulty connector.

o Faulty counterpart

machine.

o Other.

0 0

0

0

•

• Signal

is

not input. c

-.

o Control

does

not return

from input routine in

test program run.

(Causes)

o Wrong borate setting.

o Abnormal borate

oscillator.

o Abnormal +12V

or

-12V

line.

o Wrong jumper setting

(J-1,

J-2

and

J-3)

,

o Faulty connector.

o Faulty opel'1ltion

of

hybrid

IC.

o FaUlty counterpart

,

machine.

(

• Faulty driver

IC.

o Other.

..

0"

shows

a related circuit.

..

0"

shows

a related circuit .

9

Page 11

MZ-SBI03 TEST

PROGRAM

• Self-diagnosis program

Let

~s

consider a program

for

self-diagnosis

of

this interface card and assume

that

data

are transmitted

from

Channel A are reCeived by Channel

A.

For

channel

B,

similar communication system shall

be

adopted. Self·

diagnosis

of

the

interface card can be made

by

examining whether

the

reoei.e

data

and transmit

data

are

the

same

at

the time

of

transmission/receiving.

• Setting jumper blocks

on

the

card

For'the

self-diagnosis as mentioned above,

set

the

jumper blocks

on

the

card as follows.

J-l

J-2

J-3

M

T

C

R C

M T

0

0

0

0

I,

0 0 0

0 0 0

0 0

0

0

0 0

0

0

0

0

0

0

0

0

0 0

0

0

0

,I

0

0

0

0

0

0 0 0 0

0

0

0

0

0

0

0

0···1

0

0

0

0

0

0

0-

0

III

Since

port

addresses

BOH,

B'

H, B2H and B3H are used

in

the

program, set

the

switch SW-'

in

the

following (factory

setting).

•

Switch segment

6 5

,

4

3 2 1

Switch position

OFF

ON

OFF

OFF

ON

ON

Set the switch for baud rate setting as desired. After setting each mode, install the card

in

MZ-aOB. On this occa-

sion, signal cable needs

not

to

be connected.

L_'

______

,

10

Page 12

•

Flow

Chart

of

Self-diagnosis

Program

Start testing Channel

A.

Stop

the

program when an error occurs. If Channel A

is

found normal, test Channel B then.

Set Z80-SIO

mode

Start checking

Channel A

Start checking

Channel B

"

Output test data

Output

tast data

from Channel A from Channel B

Contantl of arror Contents

or

error

displayed

displayed

No

No

....

.---<

11

Channel B

is

normal

_

...

_---

-------

..

-........--..-

...

-----

Page 13

•

Program

by BASIC

language

.,

Now, let

us

draw up

th~

program described

in

the above·mentioned flow chart, using tBASIC languages. The

program list

is

shown later.

In

the

BASIC

program,

the

routine

to

control the interface card

is

composed

of

machine language. The machine

language data are w.ritten into the memory by

POKE

statement and the routine

is

called by

USR

statement. The

routine

is

made by programming statement Nos. 1000 through 1990.

..

.

Statement

Nos.

1080 --1160

...........

Parameters

Clock rate

Stop bit

Parity

Odd/even

of

parity

Transmit/receive character

Auto enable

:·X

16

2 bits

Present

Even

8 bits

Set

Statement Nos.

1180""

1370

.•.........

Mode setting routine.

Statement Nos.

1550 --1610

...........

Channel A input routine.

Input data are stored

in

Address CHAR.

Error flags are stored

in

Address

INER@.

Statement Nos. 1630 --1740

...........

Channel B input routine.

Input data are stored

in

Address CAHR.

Error flags are stored

in

Address

INER@.

Statement Nos. 1780 --1840

...........

Channel A

output

routine.

Transmit data are stored

in

Address CHAR.

Statement

Nos.

1860 --1930

...........

Channel B

output

routine.

Transmit data are stored

in

Address CHAR.

Statement Nos.

1950 --1990

...........

Writes machine language data

in

the memory.

tBASIC Version: SB-6510, SB-5510

•

,

17

Page 14

~--------------------------------------------------------------~

13

Page 15

)

1630

1640

1650

1660

1670

1680

1690

1700

1710

1720

1730

1740

1750

1760

1770

1780

1790

1800

1810

1820

1830

1840

18S0

1860

1870

1880

1890

1900

1910

1920

1930

1940

1950

1960

1965

1970

1980

1990

3000

3010

3020

3030

3040

30S0

3060

3070

3080

3090

3100

3110

3120

3130

3140

3150

3160

3170

3180

3190

3200

3210

3220

3230

3240

3250

3260

REM

CH9IN

REM

REM

REM

REM

REM

REM

REM

REM

REM

REM

REM

REM

ENT

IN

A,

(CH9CT>

R'RCA

.JR

LD

OUT

IN

AND

LD

IN

LD

RET

NC,CH9IN

A,I

(CHBCT>

, A

A,(CHBCT)

70H

(INER@),A

A'(

CHBDT>

(C.HAR)

, A

REM

***

OUTPUT

ROUTINE

***

REM

REM

CHAOUT

ENT

REM

IN

REM

9IT

REM

JR

REM

LD

REM

OUT

REM

RET

REM

REM

CH90UT

ENT

REM

IN

REM

BIT

REM

JR

REM

LD

REM

OUT

REM

RET

REM

END

REM

A,

(CHACT>

2,A

Z,CHAOUT

A,(CHAR)

(CHADT>

, A

A,

(CHBCT>

2,A

Z,CHBOUT

A,(CHAR)

(CHBDT>

, A

; [

adr.='F04A

]

:DATA

DB,93

:DATA

OF

:DATA

30,FB

IDATA

3E,01

:DATA

D3,B3

:DATA

D9,B3

:DATA

E6,70

••

:DATA

32,32',FO

IDATA

D9,B2 '

:DATA

32,33,FO

:DATA

C9

[

adr.=SF060

]

IDATA

DB,91

:DATA

CB,S7

IDATA

28,FA

IDATA

3A,33,FO

:DATA

D3,BO

IDATA

C9

I [

adr

....

F06C ]

:DATA

DB,B3

:DATA

CB,S7

:DATA

28,FA

:DATA

3A,33,FO

:DATA

D3,B2

IDATA

C9

:DATA

END

DIM

X(30)ILIMIT

.FOOO

IP-15*4096

FOR

JaO

TO

9:X(J)-JINEXTIFOR

J-O

TO

SIX(17+J)-J+I0INEXT

PRINT"SIF

SUBROUTIN

LOADING"

READ

X'IIF

X'-"END"

THEN

3000

J-16*X(ASC(MIO.(X.,I,I))-48)+X(ASC(MID.(I',2,1))-48)

POKE

P,JIP=P+IIGOTO 1970

REM

**************************

REM

* *

REM

*

MAIN

PROGRAM

*

REM

* *

REM

**************************

REM

USR(.F009)IREM mod.

s.t

~,

PRINTIPRINT:PRINT

"*****

TEST

PROGRAM

(S.ri~l

I/F

M2-8BI03)

PRINT

PRINT

"Chann.l

A

TEST"

FOR

1-0

TO

2SS

POKE

.F033,I

:USR(.F060)IPOKE

.F033,O

:

REM

chann.l-A

output

USR(.F034)IA=PEEK(SF033):ER-PEEK(SF032) I

REM

chann.l-A

input

IF

ER<>O

THEN

PRINT"COMMUNICATION

ER

- ";ERISTOP

IF

I<>A

THEN

PRINT"COMPARA

ER":STOP

PRINT"."I:NEXT

PRINT"***

OK

***"

PRINT

PRINT"Chann.1 B

TEST"

FOR

1-0

TO

255

POKE

$F033,I:USR(.F06C):POKE

.F033,O

USR(.F04A):A=PEEK(.F033):ER=PEEK(SF032)

IF

ER<>O

THEN

PRINT

"COMMUNICATION

ER

'"'

IF

I<>A

THEN

PRINT

"COMPARA

ER"ISTOP

PRINT"'";

:NEXT

PRINT"***

OK

***"

END

14

:

REM

chann.I-9

output

:

REM

chann.l-B

input

";ERISTOP

***** "

Page 16

'"

1

. ~

2

•

3

10

1 1

•

A

B c o

E

F G

•

Z-SBI03

BAND

IT

DIA

Notes:

The

printed

wiring

board

circuit

diagram are

subject

to

change

without

prior notice .

• Printed Wiring Board

SERIAL

TERFA

•

•

••

•

•

•

15

•

•

•

I

Perspective' View

--"

Parts-fitted face

-,

'

Opposite

side

H

•

\

+ .

CD

-

o

•

Page 17

A

B

c

D

1 • Circuit

Diagram

.,

..

2

AS

••

3

AS

..

4

5

•

W-,

"'

....

ID

6

..

7

''',

.. "

B

9

••

NO

."UORAn

.!9.

• •

00

•

..

lOO

,

24

00

,

1.0

0

,

1200

•

,

..

,0

•

,

••

•

".

•

".

!L

"

"

16

E

F

G

.,

, "

, "

.,

, "

. ,

'"

. ,

••

•

'"

FlnlH

13Kx;S

...

hiNT

+

,

I

to.

H

JORQ

•

..

,

I

'C

5

HOOQ2PA

,~.

,,~

011

RTS 8

CTSTI

OT

RII

DeDI

W/ROT8

SYNC

B

T

.OA

I

hOA

IIlT,A

eSTA

OTA

...

DC

OA

W/ROYA

SYNCA

G

••

...

8.

- 3

,AI

J K

L

M

N

o

p

H

-,

"

,-,

t~

...

-r-J

+12'"

~

"

I

,

-

Z. ---

I

"

,

' 0

~-

I

".

•

I

7"88

•

"

I

~-

-

,

•

..

~

I

u.

I

-

.,

--

r

. ,

c

__

--

•

,

OTI'I •

.

,--

-

I 0

~

-~

"

~-

.,.

- 1

2V

"

'"

",

."

(ID

'"

•

®

CHANN~L-'

H

CHANNEL-A

, ,

"

~

r

"

I

~

I

I

•

-::r-:--------::::

~

"

~-

•

MZ-BBI03

17

Page 18

.

Item

Specifications

Interface standard

In

accordance with IEC Standard/TC66.

Interface funcion

Functions executable

in

MZ-,801rv"ersion-up BASIC language.

,

Function

Subset

Description

SH

SHl

All

functions

AH

AH1

All

functions

T

T6

Basic talker

Serial poll

Cancellation of talker by

MLA

L

L.

Basic listener

Cancellation

of

listener by MTA

C

Cl

System controller

C

2

IFC transmit. controller

in

charge

C

3

REN transmit

C.

Response

to

SRQ

C

6

Interface message transmit

Controller receive

Controller pass

Controll pass

to

itself

Parallel poll

SR

SRO

No function

RL

RLO

No function

PP

PPO

No function

OT

OTO

No function

DC

OCO

No function

Output

connector

(Male type)

connector

in

compliance with IEC Standard

•

,

Operating temperature

6°C"'"

35°C

Storage temperature

OOC"'"

50°C

Power source

DC

5V (supplied from MZ-80B)

Reference

The following specifications are

"reference"

specifications. since difference

is

caused by cable quality. connector

connection. noise and

other

environmental conditions.

1.

Number

of

Instruments per

system

2.

Full length

of

cable

per

system

15

max. including MZ-80B

20m

or

less

However.

length per instrument shall be

about

2m. If the number

of

instru-

ments exceed

11

in

one system. cables

of

2m

or

less shall be used between

instruments so

that

the

full length will be 20m

or

less.

(Note) The above-mentioned specifications may be changed in

the

future for improvement

of

the product.

18

Page 19

I MZ-SBI04 DESCRIPTION OF CIRCUIT

:

..

J

r--

• Block Diagram

MZ·80B

bus line

This interface circuit consists

of

a hybrid

le

(H0001 PAl

for

GP·IB, Z·80AP10

and

various logics

to

connect them

to

the extension I/O

of

MZ·80B.

Some

of

included logics

are

a waiting logic

and

a data buffer control logic

so

that the mode 2 interrupt

of

Z·80A

can

be

utilized by Z·80API0.

Data bus

1-

lE

lE

M

A

0-

1----

0-

A 7

8

0

I

0-

A

A

W

R_

.

1--

M

BUS4>

IORa

EXWAI T

T

lE

0

I

T

M

RESE

-

-

8

Buffer

control

logic

Address

decod·

ing logic

Waiting logic

•

Reset circuit

r---

....

DB7

tU

...

I

...

8

~

DBO

Dltl

b

ID

us

8

8

R1

W1

I--

W2 3

I-

HIC

Hind

07

Mlnlgemlnt

L...,.

I

line

line

GP·IB

sheke

DO

-

-

CE

5

TACS

5

Z·80A

Mlnage

PlO

LACS

line

-

ment

MI

8

CMAC

NBA

Command

ACCS

NBAW

-

INT

reed

IEO

l

-

IEI

iEi-

Timing circuit

MZ-8BI04 Block Diagram

.

..

~--------------------------------------------------------------------------------------~

19

Page 20

I

• Description

of

Hybrid

le

RMPTHOO01PAZZ

for

GP·IB,

The hybrid

IC

mounted, on the GP·IB interface MZ·8BI04

of

MZ·80B integrates the hand

shake

logic,

bus

driver/

receiver, etc. which

are

the proper circuits

of

GP·IB circuit,

into

one

package.

By connecting this HIC (hybrid IC)

to

the I/O ports

of

an

ordinary microcomputer, the functions

of

T

6

,

4,

SH

1

and

AHI

and

the inputting

and

CJutputting

of

the

l1'Ianagement

line

and

data line

are

enabled.

Data

line (

I nternal register (

read/write

pulse

DB,

I

DB.

Wl

R1

W2

I

nput

to

hand

shaka

line

and

management

line

OAV(R)

NRFO(R)

NOAC(R)

EOUR)

ATN(R)

SRO(R)

IFC(R)

REN(R)

Management ATN(O)

line

output

SRO(O)

[

EOHO)

IFC(O)

Enabling

manage.

REN(O)

ment

lines

other

ENABLE

than

EOI

Reporting

of

[T

ACS

Internal logic LACS

status

SPAS

Reset

.ignal

CLR

Waiting

time

~

NBA

setting

NBAW

Waiting

time

~

ACCS

setting

CMAC

• Block Diagram

of

Hybrid

le'

27

-~-

?g

19

16

2

3

4

lIE

5

-~-

7

-~

9

11

2

13

4

15

10

49

50

51

47

55

52

53

54

D7

De

D5

D4

D3

D2

D1

DO

DATA

LINE

DAV

R

NRFOR

NDACR

EOI

R

ATN

R

SRQ

R

IFC

R

REN

R

~§~

W2

GND(E)

..

.

30

HOOO1PA

31

32

33

34

35

36

37

3B

39

40

41

43

44

45

46

42

11

1171561~2~48

Vcc GNO

DATA

PORT

t--.-J

ClR

~~~~~~i~~~~~~~J

CMAC

Aces

NB':

LACS

TACS

SPAS

EOI

D

ATND

SROD

IFC

D

RENO

20

Driver

/Receiver

0108

0107

0106

0105

0104

0103

0102

0101

SRO

IFC

REN

ATN

OAV

NRFO

NOAC

EOI

SG

GP·IB line

Signal

groun"d

0108

0107

0106

0105

0104

0103

0102

0101

rr-

.......

==-=-

......

slgnal

GND

DAV

NRFD

NDAC

EOI

ATN

SRQ

IFC

REN

Page 21

• Description

of

Each Circuit

Each circuit will be described. The logic diagrams used for description are simplified schemata

of

logic.

1. Reset Circuit

RESET----I

)O----~

To

Pia

M1

MI------'

The circuit

is

intended

to

reset PlO by

the

RESET signal from MZ·80B

CPU

board. Z-80APIO

is

reset when MI

terminal

is

active for 2 clock cycles

or

over providing

that

both

"Fm

and

1U"RO"

signals are

not

active. The

RC

circiut

in

the

diagram

is

a low pass filter provided for preventing faulty operation

d~e

to

noise.

2.

Waiting Circuit

m1

MI---\

IDROW

MI----i

.;xl~--<2

LD

EXWAIT

BU&/>

--

Vcc

The waiting circuit corrects

the

timing

of

the interrupt vector transmitting from PlO

to

CPU

in

the interrupt

ac-

knowledge cycle. Thus, 10RQW develops a signal

of

reversedlORO

and EXWAIT

doesn't

develop pulse

in

other

cycle than the interrupt acknowledge cycle.

This waiting circuit does

not

correct

the

timing

of

the daisy chain. With

the

delay

of

the daisy chain, lED look

ahead

is

carried

out

on

the

extension I/O interface

of

MZ-80B.

The timing chart

in

the

interrupt acknowledge cycle

is

illustrated below.

Lalt M cycle

I

Interrupt

detection

-----""\

Ir---

------41-

~

--

T2

Tw·

. .

Wait line

.

detection

I

nterrupt

vector

T'i

Tw

input

c----,

EXWAIT

,)pROW

________________________________

----~I

\'----

21

c

(

Page 22

3. Addre •• Decoding Logic

A,

A.

-r---i.._

As

A.

--<I

A,

--<4

,--

__

Decoded

output

of

COH

to

C7H

to

PlO

~

(COH-C3H)

C

B

Ao

~A~~~----.

W, (C5H)'

W

I

(C4H)

RI

(C4H)

• ICg

AH·iX0303PAZZ

SN74LS138N

Pin Assignment (Top View)

Vcc

YO

Y1

("lA

•

V2

DATA

ENABLE

G28

5

Y3

OUTPUT

~1

6

V4

OUTPUT

V7

VS

V6

The address

decoding

logic forms ~ signal

of

PlO

and

A

I,

W I

and

W2 signals

of H IC

from

the

signals

Ao

to

A" AD,

WA

and

10POW.

The

decoded

output

of

COH

to

C7H

is

used

by

the

data

buffer

control

logic.

4. Data Buffer Control Logic

IEI

----I

IEO

-----0

MY

----0

RD

---d

Decoded

output

of

COH

to

C7H

IOROW

(lORO)

p----

To

No. 1

pin

of

IC6

(LS24S1

The

data

buffer

control

logic ,regulates

the

buffer

connecting

the

CPU

data

bus line

and

the

bus lines

of

PlO

and

HIC. CPU reads

data

when

the

No. 1 pin

of

ICS

is

in low level. CPU reads

data

when

the

10

addresses

of

COH

to

C7H

are

input

to

CPU

and

CPU reads

the

interrupt

vector

from PlO in

the

mode 2 interrupt

acknowledge cycle.

,

5. Timing Circuit

a

B

5/ols

The timing circuit forms pulses

of

about

500J,Jsec. and

about

5J,Jsec.

500J,Jsec.

determines

the

time for receiving

one

command

when

the

ATN signal

is

received

in

the

slave

mode

and

5J,Jsec.

determines

the

time

from

trans·

mitting

data

on

to

the

GP·IB

data

bus

to

outputting

DAV. It

is

so

designed

that

500J,Jsec. pulse

is

not

generated

untillEI

becomes high level, by considering

the

disposition

of

ATN

by

interrupt.

27

Page 23

MZ-SBI04 TROUBLESHOOTING

BASIC (Commands

other

than GP·IB) does

not

work

normally.

(N)

No

Fault

of

other

part

than GP·IB

interface.

(N):

Normal,

(A):

Abnormal

(With tha method

of

intarpretation, refer

to

paga

25,

26.)

(N):

Normal

>--~

Abnormal IDROW signal

23

(N)

"-

•

(A)

Abnormal

EXWAIT

signal

IC

connected

to

input

line

is

faulty.

Faulty

IC12

Page 24

(N)

>;"""':'-.j

Faulty

IC1

(A)

>;"""':'-1

Faulty

IC1

BASIC works

but

GP·IB commands

do

not

work.

Ves

Ves

No

•

,

Faulty address decoding

circuit

(lC11,

IC10and

IC3)

Faulty 1C9,

IC11

">N_°--lOOiCheck

abnormal signal.

24

·1

The R

EN

line of GP·IB becomes low level by

the

command

REN

and

high level by

the

command

LCL

·2

Pin @

outputs

negative pulse by reading

1/0

address

C4H

(1961.

Pin

([\)

Pin

(j)

outputs

negative pulse by writing on

to

1/0

address C4H (1961.

outputs

negative pulle by writing

on

to

1/0

address C5H (1971.

Page 25

•

Methods

of Interpreting

Whether

Normal

or

Abnormal

Each terminal

is

normal if it

is

in

the

following

status

in

the

"READY"

condition

after

run

by

BASIC.

Pin No.

of

IC

Normal

condition

ICl

®

Negative pulse

Same

as

MI

(CPU bus)

ICl

CID

Positive pulse

Reversed

MI

(CPU bus)

ICl

@

Constant

L level

IC2

(j))

Positive pulse Reversed

MT

(CPU bus)

IC2

®

Reversed

buscJI

IC3

@

Constant

H level

IC5

CD

Positive pulse (Turns H level

when

XXCOH

to

XXC7H are

transmitted

address bus.)

IC5

<V

Positive pulse

Reversed

RD

(CPU bus)

IC5

@

Positive pulse Reversed

10RQ

(CPU bus)

IC5

@

Positive pulse Reversed

MI.

(CPU bus)

IC5

@

Constant

L level

IC6

CD

Constant

H level

IC7

@

Constant

H level

IC7

@

Constant

H level

.

IC7

@

Constant

H level

IC7

CID

Constant

H level

IC7

@

Constant

H level

ICS

@

Negative pulse Same as

Mi

(CPU bus)

ICS

@

Negative pulse Same as lORQ (CPU bus)

Output

terminals

of

address decoding circuit

•

ICll

®

Develops negative pulse

when

I/O address

COH

to

C3H (192

to

195) are accessed.

IC9

@

Develops negative pulse

when

I/O address C4H (196)

is

read

out.

ICg

QV

Develops negative pulse when

data

are

written

on

to

I/O address C4H (1961.

ICg

Q)

Develops negative pulse

when

data

are

written

on

to

I/O address C5H (197).

.

~.

25

Page 26

Input

terminals

of

PlO

IC12

@

Same signal

as

A 1 (CPU bus)

,

®

Same signal as

AO

(CPU bus)

@

Same signal as

RC

(CPU bus)

••

@

Same signal as

IORa

(CPU bus)

@

Same signal

as

MI

(CPU bus)

@

Same signal as IEI (CPU bus'

@

Same signal as

BUSt/I

(CPU bus)

In

BASIC ready status

At

transmission

of

data

to

GP·IB

At

receiving

data

in

slave mode

IC13 @

Constant L

hivel

Outputs

positive pulse

of

Constant L level

about

5llsec.

,

IC13

<I}

Constant

H level

Constant

H level

Outputs

negative pulse

of

about

500llSec .

.

,

26

Page 27

•

2

3

4

5

7

8

A

B

c

o E F G

H

MZ-8BI04

PWB AND CIRCUI

DIAGRAM

Notes: The printed wiring board and circuit diagram are subject to change

without

prior notice .

• Printed Wiring Board

•

. .'

•

27

•

Perspective

View

D Paru·flned 'ace

D Opposne Side

,

•

Page 28

Page 29

Protected

Seat

(SSAKH0043PAZZ)

PWB

Sleeve

(SPAKS002SPAZZ)

:~,~

.,.,'

'(;''<i1-~'::;~'~'~'~

j':~".e.:

~.::~

.•

>.:.:";~,'~;"

,:':.~~,,~

,

....

_.

.,',

' -

~---

Packing

Case

(SPAKC01S5PAZZ) for MZ-SBI03

(SPAKC01S7PAZZ)

for MZ-SBI04

30

Instruction Manual

(TiNSE0036PAZZ)

English

for MZ-SBI03

(TiNSE0037PAZZ)

English

for MZ·SBI04

'----

Seal

x 2

(TSELF0001PAZZ)

Page 30

REPLACEMENT PARTS LIST

,:,,','

" ,i:;;'HOW;;:rO,"ORD,ER:

R~,LACE~ENT:.~AFtT~~;:~;t:~~i:';~~'

.;

..

(

:T~

have

you~

~rd8r,fllled

promptly end

corr~ly:.~J88S1t.furnlsr

tIl8

f()lI~i~.19tor.if1f9nt

'

...

'~

.'.

,,1'

MOOE~

NAMe·~·· , ,~"

'2

·FiEF

NO'

.,,~

1',

)(,£,.1

'.

"

.

\.,'

. , ',.

".

r.·

',; ''''.

"t.

.',

• ."

"'."t..

i

1

.,

~.

'.

,;

•

~.'

l-\

..

:;.

tJ:

~~',.J\

.:-

~*-( ~ '.,.,.~

...

~'t.'

~"

~:;

,;:t.~

"'

't',

~;;:

~

..

':~';

'~',.

l,.',

!.3~,P~R!{Nq·

..

t~'.,,:(·

....

~:7::~,fo";(J>.~.,}?,e~.~p,r'~~\\··

~'I

/;1S~~f,"'.:¥

NOTES;

Be

sure

to

use

regular parts

for

securing the safety and reliability

of

the

set.

Be

sure

to

replace

these

parts

with

specified

ones

for

maintaining the safety and performance

of

the

set.

MODEL

MZ·8BI03

REF.

PART

NO. DESCRIPTION

CODE

REF.

PART

NO.

DESCRIPTION

CODE

NO.

NO.

INTEGRATED CIRCUITS

C3

}

VCTYPU1BD104Z'

O.lMFD.

12V. Ceramic

C16

AB

ICl

AH·iX0297PAZZ

MCl4411

BA

C4

IC2

}

AH·iX0305PAZZ

SN75189AN

AM

I

IC8

C7

VCKZPR1HB221K

220PFD. 5OV. Ceramic

AA

IC3

}

AH·iX0190PAZZ SN74LS266N

AF

C22

IC4

(

(

IC5 AMPTHOOO2PAZZ Hybrid IC

BU

C24

IC6/'

AH·iX0085PAZZ SN75188N

AM

C8

VCEAAUOJW107Y

l00MFD.

6.3V. 'Alumlnum AB

IC7

C9

r

IC9 AH·iX0152PAZZ TL497CN

AU

Cll

IC13 DUNTK0064PAZZ

12Nl0Kl

BF

C12

VCKZPA1HF103?

O.OlMFD.

5OV.

Ceramic

AA

C14

TRANSISTORS

AND

DIODE

C18

C20

Ql

}

VS2SA49&O/.1 2SA49&O

AF

Cl0

VCSACU 1 AE336K

33MFD.

10V. Tantalum

AD

Q2

C13

)

01

VHD1S1586//1A

lS1586

AB

C15

VCEAAU

1 CW336Y

33MFD. 16V.

Aluminum

AB

(

C19

RESISTORS

C21

C17

VCCSPR1H6151J

150PFD.

5OV.

Ceramic

AA

Al

VAC·MT2EG 106K 10M ohm. 1/4W

AA

A2

}

VAD·SC2EF102J

lK

ohm. 1/4W

AA

MISCELLANEOUS

A14

R3

}

VAD·SC2EF103J 10K ohm. 1/4W

AA

L1

RCi

LF7863VAZZ

Coil CH04

AG

R15

L2

}

RCi

LF7862VAZZ

Coli CH03

AG

A4

VRD·SC2EF272J 2.7K ohm. 1/4W

AA

L4

R5

VRD·SC2EF472J 4.7K ohm. 1/4W

AA

L3

RCiLF7864VAZZ

Coll8S651

AK

R6

}

VRD·SC2EF101J 100 ohm. 1/4W

AA

X'TAL

RCRSAOO17PAZZ

Crystal

1.8432MHz

AP

(

Rl0

SWl

QSW·DOOO4PAZZ

Dip

Switch (6 contacts) AR

R7

VAD·RU2EE222J 2.2K ohm. 1/4W

AA

SW2

}

QSW-DOOO6PAZZ

Dip

Switch (10 contacts) AR

RSr

VRD-RU2EE561J

560 ohm. 1/4W

AA

SW3

R9

VAD-RU2EE273J 27K ohm. 1/4W

AA

J-l

QPLGZ0103PAZZ

4-Pin Plug

AD

Rl1

VRD·SC2EF221 J 220 ohm. 1/4W

AA

J.2

}

QPLGZ0102PAZZ 3-Pin Plug

AC

A12

VAD-SC2EF561 J

560 ohm. 1/4W

AA

J.3

R13

VAN·RT2HCl

ROF

1 ohlfl. 1/2W

AB

QJUM-0004PAZZ

Jumper

(for

J·l.

J.2. J-3)

AF

R16

VRD·SC2EF

l04J

lOOK

ohm. 1/4W

AA

CNl

}

QPLGZ0104PAZZ g.Pin Terminal

AY

RAl

RMPTC10l9PAZZ

Resistor A.rray 3.3K ohm x 6

AC

CN2

LANG

K0296PAZZ

Fixing Metal

(for

two

9-Pin AF

CAPACITORS

terminal)

QSOCZ0010PAZZ

24-Pin IC Socket

AF

Cl

}

VCTYPU1BD104Z

O.lMFD. 12V. Ceramic

AB

TiNSEOO36PAZZ

Instruction Manual (English)

BP

C2

.

..

(

31

Page 31

/-

MODEL

MZ~8BI04

PARTS

LIST

MODEL MZ·8BI04

QEF.

PART

NO.

DESCRIPTION

CODE

REF.

PART

NO.

DESCRIPTION

CODE

,-

NO.

NO.

INTEGRATED CIRCUITS

R7

VR D-..

S<;2E; F l23J

l2K

ohm, 1/4W

AA

R8 V,RD-SC2EF822J

S.2K ohm,

1/4W

AA

ICl

RH-iXOO78PAZZ

SN74LS32N

AF

R9

}

VR.o-SC2E F 1 03J

10K

ohm, 1/4W

AA

IC2

RH-iX0276PAZZ

SN74LS191N

AL

Rl0

IC3

RH-iX0149PAZZ

SN74LS27N

AF

IC4

}

RH·iX0102PAZZ

SN74LS14N

AM

CAPACITORS

ICS

IC5

}

RH-iXOO70PAZZ

SN74LSOON

AE

Cl

}

VC

KYPU2HB 1 02K

l,OOOPFD,500V, Ceramic AA

ICll

C2

IC6

RH-iX0124PAZZ

SN74LS245N

AR

C3

VCQYKU1HM683K

. O.068MFD,

SOV,

Film

AB

IC7

RH·iX0200PAZZ

SN7407N

AG

C4 VCQSMU1HM102J

l,OOOPFD,

50V,

Film

AC

IC9

RH-IX0303PAZZ

SN74LS138N

AG

C5

VCEAAU1AW107M

l00MFD,

10V,

Aluminum

AB

IC10

RH-iXOO75PAZZ

SN74LS08N

AE

C6

}

IC12

RH-iX0229PAZZ

LH0081A

Z-80APIO

BD

I

VCSACU 1 AE 106M

10MFD,

10V, Tantalum

AD

r--

IC13

R H-i X0227PAZZ

SN74LS221N

AN

Cll

IC14

RMPTHOOOl PAZZ

Hybrid

IC

BY

C12

}

VCTYPU1BD104Z

ORESISTORS

I

b.1MFD,

l2V,

Ceramic

'AB

C24

Rl

}

MISCELLANEOUS

VRD-SC2EF332J

3.3K

ohm.

1/4W

AA

R6

R2

}

QPLGZ0105PAZZ

25-Pin Terminal

BC

VRD-SC2EF221J

220

ohm,

1/4W

AA

LANG

K0297PAZZ

Fixing

Metal

of

25-Pin Terminal

AG

R4

R3

VRD·SC2EF153J

l5K

ohm,

1/4W

AA

TiNSEOO37PAZZ

Instruction

Manual (English)

BR

R5

VRD-SC2EF33l J

330

ohm,

1/4W

AA

0

o

32

Loading...

Loading...