Page 1

-

MZ-5600A

3. BASIC OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

4.

DRIVE INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

5.

ENCODER/DECODER,

DATA

SEPARATOR

............................

~

......

10

6.

MAINTENANCE

.........................................................

12

7.

EXPLANATION OF

LSI

...................................................

15

9.

PARTS GUIDE AND LIST

Page 2

..._..,

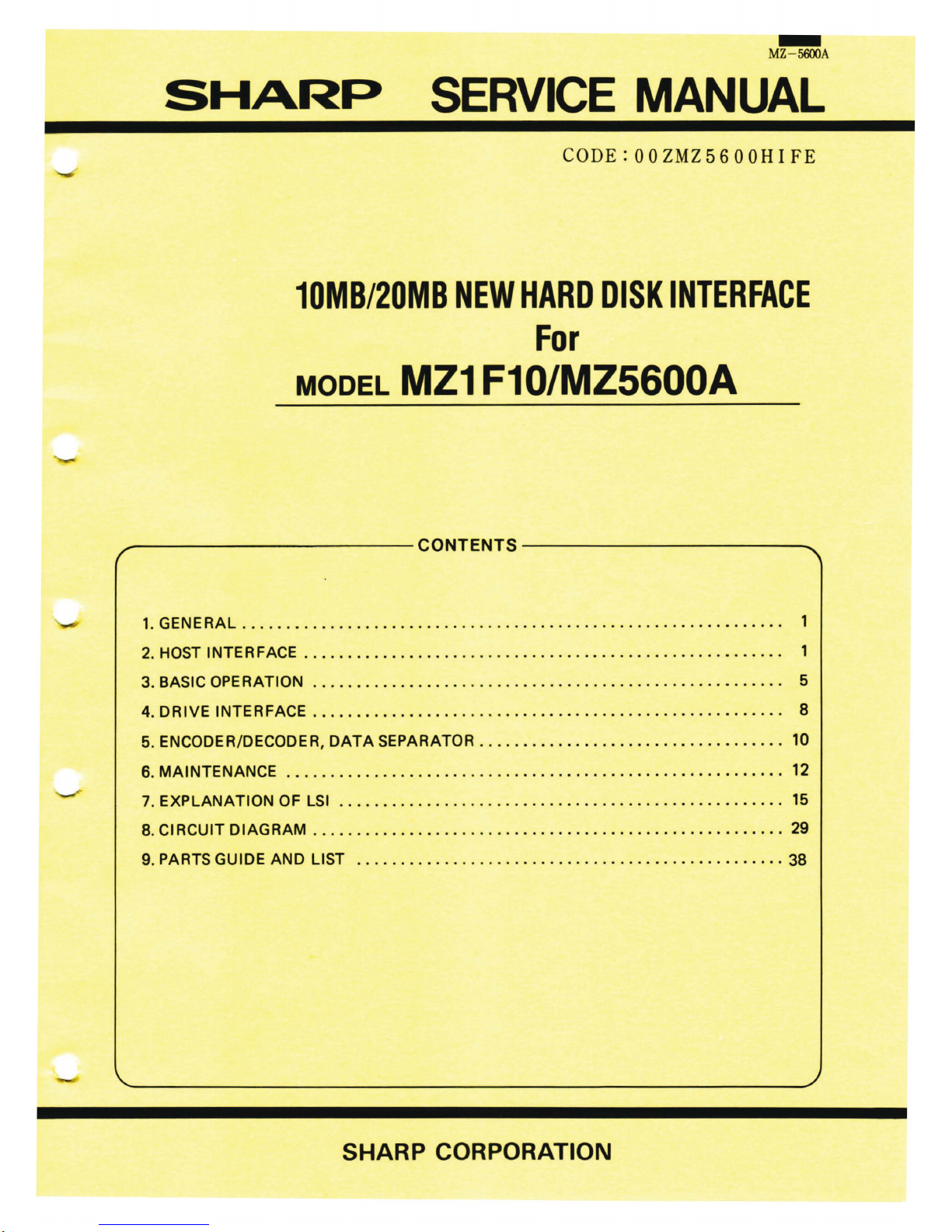

1.

GENERAL

DUNTK

1517

ACZZ

is

constructed

with

four

exclusive

LSis,

CPU

Z-80

and

others.

The description here

is

mainly

on

the LSis.

2.

HOST

INTERFACE

NDC-848

is

an

LSI

device

for

the

NCL

host interface.

NDC-848

can

be

easily conncted

with

the host

and

can

construct a disk

controller

with

NDC-840 (HOC)

and

others.

Commands

and

Data Write from the host

are

set in the

internal register

of N DC

-848

and

are

transferred

to

RAM

by

DMA

of

NDC-840.

Status

and

Data

Read

are

set

by

DMA

in the register

of

N DC848

and

are

read

by the host.

2-1. Main Operation Time Chart

(1)

COMMAND

SET

1/

0pon 11---

-,

,------

\

,------)}--

-"", ,

r-

---

(0383JH I.

\...

___

_J

~----'

~-----

IOWC

DATA

CS

ADI\0

ADRI

DRQ

H

IJoVR

UOO-UU7

---

--\

....

'.:'

.....~,------

-,\...

'~

.J~------n

-----\~

~

.Jr-

---

--

----

--c~------

--c=)------1)------c=

..

J---

----

note:

-----

host signals

-----internal

signals

- 1 -

-

MZ-5600A

(2) STATUS

READ

1/0

port

H-

----

-,

I----

---

-

--

[0380)

HL

\......

_____

...J

DATA

H

L

H

DDO~

DD7

-------,

,-------------

\_

__

_)

------

--z.-J-----

--------

25 ns

-I-~

0.31/J-:-

-1--

25 ns

[ oin ) [

1

"

[ o

in

)

0.

111

5 .... -

0

[ o

in)

[ o

in

)

r

note:

---

--

host signals

-----

internal signals

(3) RESULT READ

110

pon

ll

- - - - - - - - - -

~,

,,...

- - - -

-1~

- - -

-.

,

[0382

] H L

\.

............ /

\....

............

J

'-

.......

... J

\

...

Jr

............ - - -

....

""'\

....

...J,,...

- - - - -

-{J-

- -

.........

,L

.J,- - - - -

DATA

-----()----

-----{)--

- - - -

-H----

-{}-

-

----

(4)

DATA

READ

(DMA)

~

....

....

,\....

___

,.~

---

---""'

............

...J • .--

...........

-

--,'---

..J

r-

-----t--

"' . .._

___

F--

.............

----

'uc

Jto

......................... \ _____

/,_.

........ ---·\

...............

_, • .------,\... .............

_,

r--

Jt-

--

-------.~---

_, . .--

............

....

rnl'i:.'

------

--.\..._

..Jr------

--,'-- J

,,..------

---\

......

Jr-

-

-~-

-

-----.\...

...

J

',.....

... -----

•AT•

----

---

-c

:::>-----

-----c:::>------

----c:::>---+-------c)------

nnl

-----

------

----

-------

---------------n--

-------

-"'....

___

_

Page 3

-

MZ-5600A

(5) DATA WRITE (DMA)

OI

UlQO --...

\ ........

_,'

..... -----...,

,....

- - -

.... --.\

__

...

_/,..

- - - -1f- --.,'-

...

...

Jr

- - - - - ......

"'i5ACi"a ----

...

...,\_---

. ./,...-

...... -'"'',

....

- - - J:

---

--

~

\

... ---

j

.....

-

~f-

-

--

'"""

·~

-·-

...

Jr -... ---

"--

....1

.....

----

- - ....... \.... .... J

......

- -

---

- .... \

...

-

J,

....

-

-jf--

- -

-

~

..........

_/.----

- -

...

DATA

-------CJ--------CJ----

-

---c:J---jf-------c:)------

~

----

---

- - -

---

--------

------ - !r---

- - -

---

;_ -

~

~

~~

~-

--.

~

~

~~--~

}~~

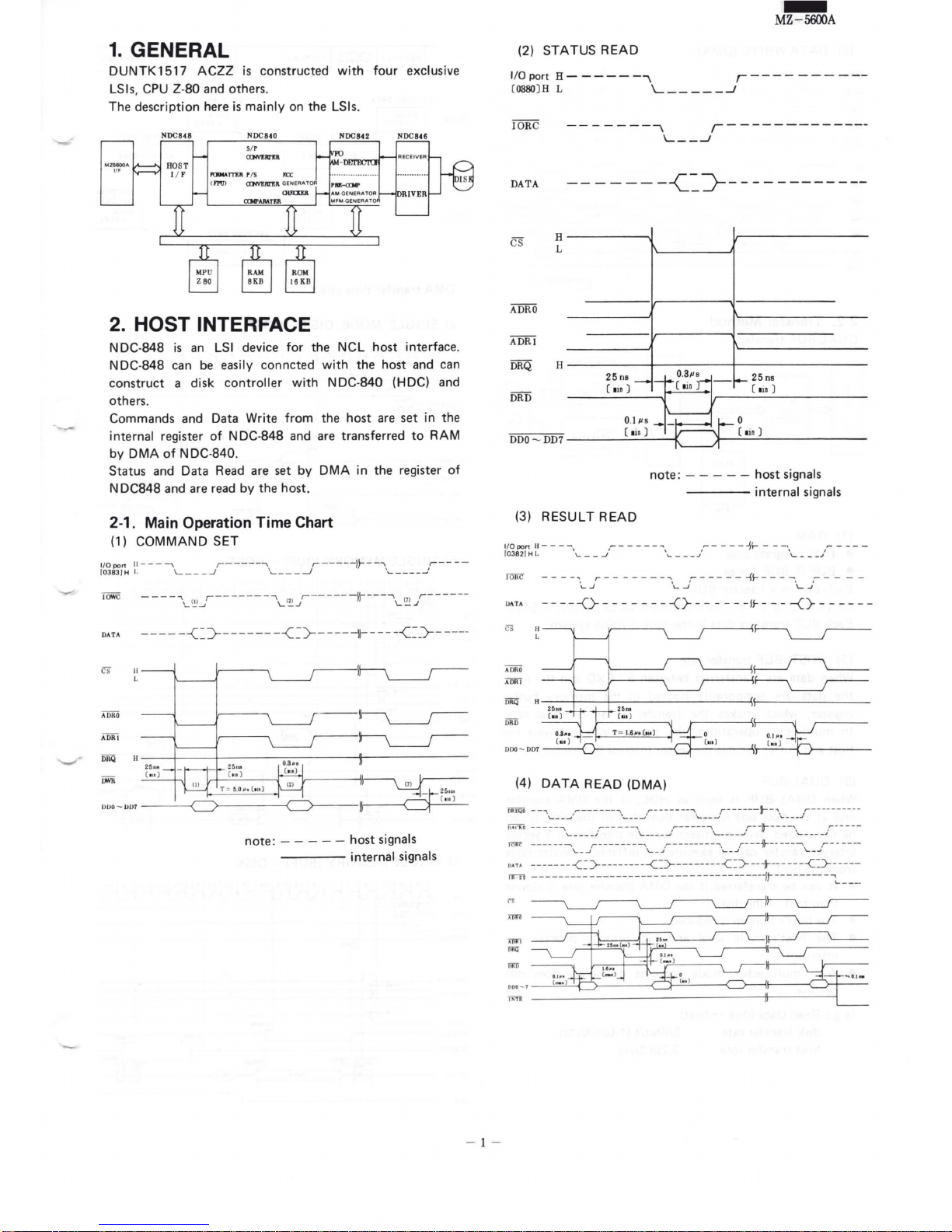

2-2. Transfer Method

DUAL-BUF

transfer

B

liF

I

( R All)

(1) RAM

• HDC

program

area

• BUF 0, BUF 1 area

Eac~

BUF

is

a 1

sector

BUF.

--L

wr

ite execution

-!--J.

-

ti

me

At

2KB/Chip

RAM,

the

maximum

sector

length =

5128

.

Each BUF

transfers

data

in

the

time

division

system.

(2) HOST, BUF

transfer

rate

When

data

are

transferred

between

5"

F XD

and

the

host

,

the

data

are

temporarily

housed

in

the

memory

buffer

register,

which

makes

the

transfer

at

an

optional

rate.

In

multisector

operations,

the

transfer

rate

between

the

host

and

buffer

decides

the

sector

interval (interleave).

(3) DUAL-BUF

When

DUAL

-BUF

is

used

as

HDC, if

the

DMA

transfer

rate

at

the

host

side

is

slower

than

that

of

the

disk,

it

can

be

transferred.

With

multisector

mode

transfers,

a 1

sector

interval -

transfer

can

be

executed

at

different

transfer

rates

from

the

host.

•

lt

can

be

transferred

if

the

DMA

transfer

rate

is

slower

than

that

of

the

disk .

•

The

host's

burden

is

reduced.

•

The

host's

cycle

steal

and

high-priority process

can

interrupt.

• With

multisector

mode,

process dificiency does

not

decline.

(e

.g.) Read Data

(disk~

host)

disk

transfer

rate

5Mbit/s

(1.6Ms/byte)

host

transfer

rate

3.2Ms/byte

SECTOR!

DATA

BUF 0

I

DI

SK

- au

ro

BUF I

S ECTO

R!

DATA

BUFO

~HOS

T

J

S ECTOR2 DATA

DISK

_,. BUrt

DMA

transfer

time

chart

SECTORS

DATA

I D I S K

~

BUFO

S ECTOR2

DATA

BUF I - HOS T

a)

SINGLE

MODE, DISK -

HOST

b)

SINGLE

MEMORY (BUF) -· HOST

C

L<

H

RQ

HLDA

P

W..

S£0

SEC

TOR 4

S ECTO

RB

OAT A

BUFO

-~>HOS

T

S ECTO

R4

D

ATA

DI

SK

- BUFI

ADR

-

STI=~~~~

ADI\0-1

ADA£

IlEA()

WR

ITE

ii="ifilj

c)

SINGLE

MEMORY

(BUF)-

DISK

C

LK

HRQ

HLOA

~m'-------~-+~~--------+---------~--------~

-----

Al>ft-S

TB=====~st======t=

==>

~~~====

t===

TCAR

ADRO

-1

- 2 -

Page 4

·-

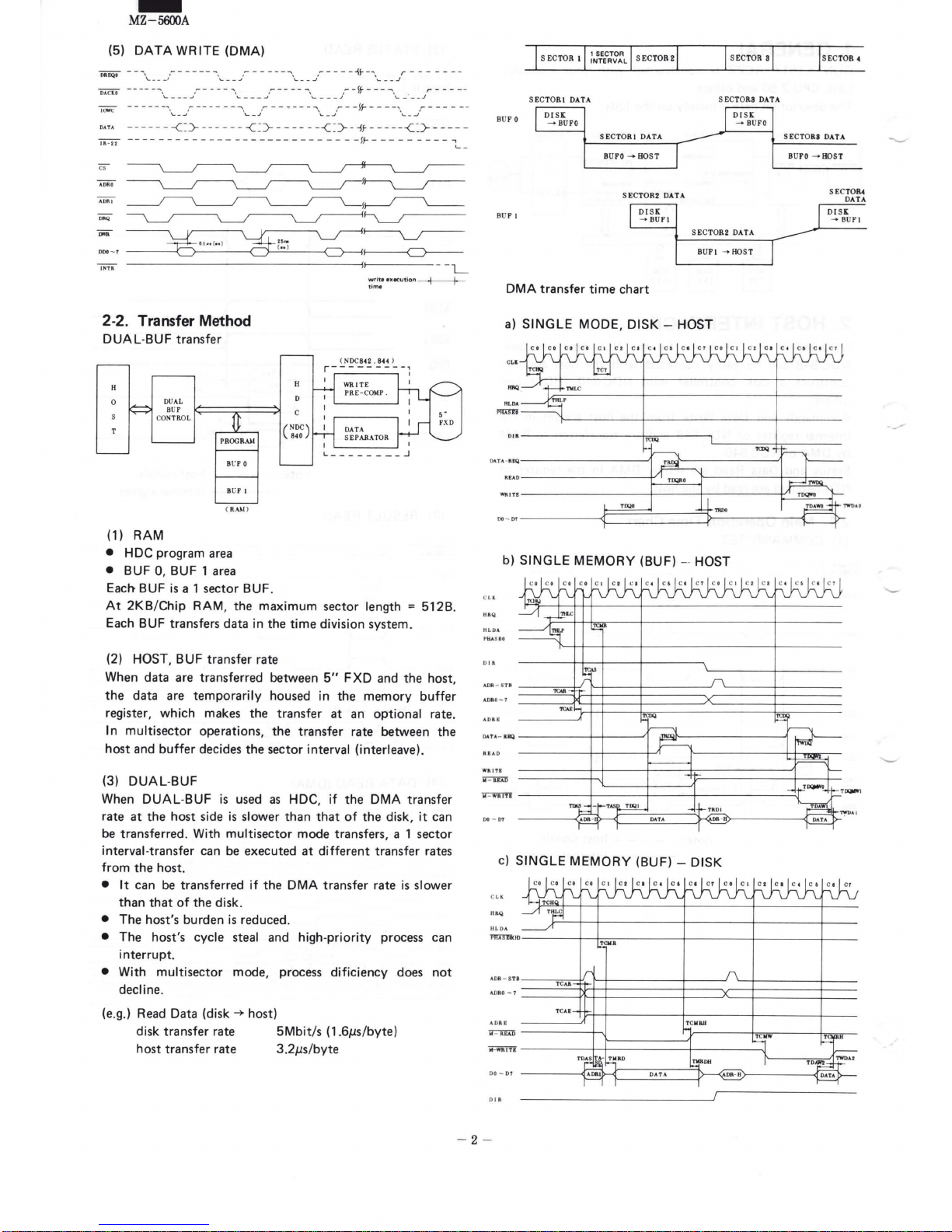

2-3. Basic Operations General Flow Chart

No

Power~n

or

reset

Command

control

program

format

,

read, write, seek,

etc

.

2-3-1.

Timing

(1) Command Transfer

NDC848-

17

CS

NDC848 - 18

DRD

NDC848 -

19

JJWR

NDC

848-

16

HADR1

NDC84

8-

15

HADRO

___

__

(hardware,

memory,

etc.}

2000

(2)

Magnification

of

the

A Part

-

MZ-5600A

.____

_

______.nL...__

_ ___,/L_

I I I I I I I I I

(3) Data

Read

NDC848 -

17

CS

NDC

848-

18

DRD

NDC848 - 19

DWI\

NDC848- 16

HADR1

I I I I

I I I I

1000

2000

I•

'''I

rl:l·· , ,

,,I,,

I'

•I

,,

''I'

I

''

I •

I'

I I I I ••

••••

'

I'

••

' I

NDC848 - 15

HADRO

DRQ

NDC848 - 14

INTR

(4)

Magnification

of

the B Part

0

--

-+--____J

3

0246

I 0271

0296

I•

I I I

,,

I I

[TI,

I I I I ' I I I I I I

••

I I I I I I I I I I I I I I I I I I I I I I I ' I I I I I I I I I I I I I I

5

6

------+-----------------------

----------------------

7

__

_,

____________

_______

___

- 3 -

Page 5

-

MZ-5600A

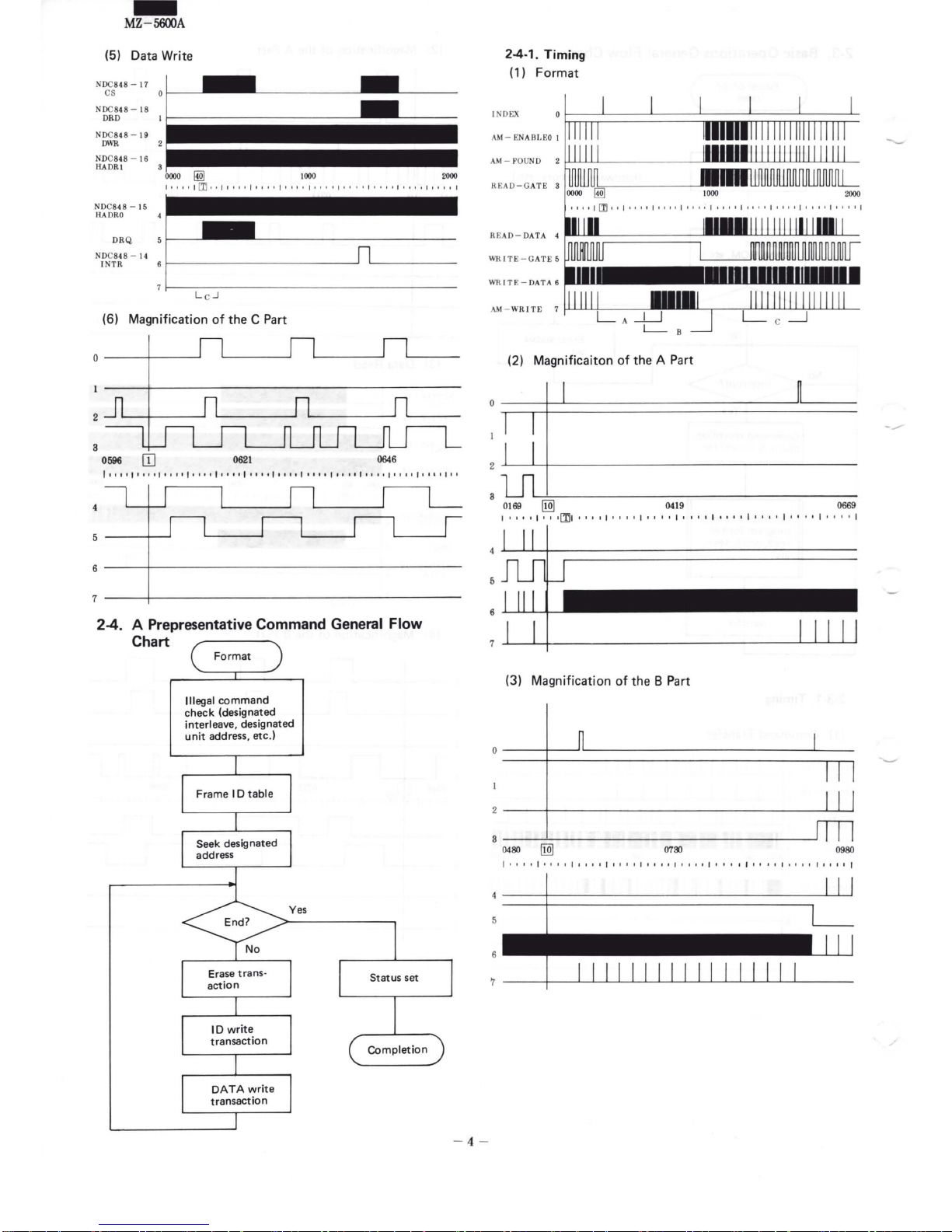

(5) Data Write

NDC848-17

CS

NDC848-18

DRD

NDC848 -

19

OWR

NDC848 -

16

HADRI

NDC848 -

15

HADRO

DRQ

NDC848 -

14

INTR

(6) Magnification

of

the C Part

2-4. A Prepresentative Command General Flow

Chart

Illegal

command

check

(desi

gnated

interleave, designated

unit address,

etc

.)

- 4 -

2-4-1. Timing

(1) Format

INDEX

AM-

ENABLEO I

AM

- FOUND

READ-G

ATE

3

READ-

DATA

4

WRITE-G

ATES

WRITE-D

ATA

6

(2) Magnificaiton

of

the A Part

2

a

0169

[!Q]

04

19 0669

I I I I I I I I

•[T}

I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I I

5

6

7

(3) Magnification

of

the 8 Part

o---+~nL_

__

__________

____

,L_

_

Ill

2

--+-

--------------~

"

~

3--

~--------

----

----------nll

0480

[!Q]

0700

0980

I'

I I I I ' I I I I I I I I

I•

I I I I I I I I I I I I I I I I I I J I I I I

I'

I'

I I I I

11

I

Page 6

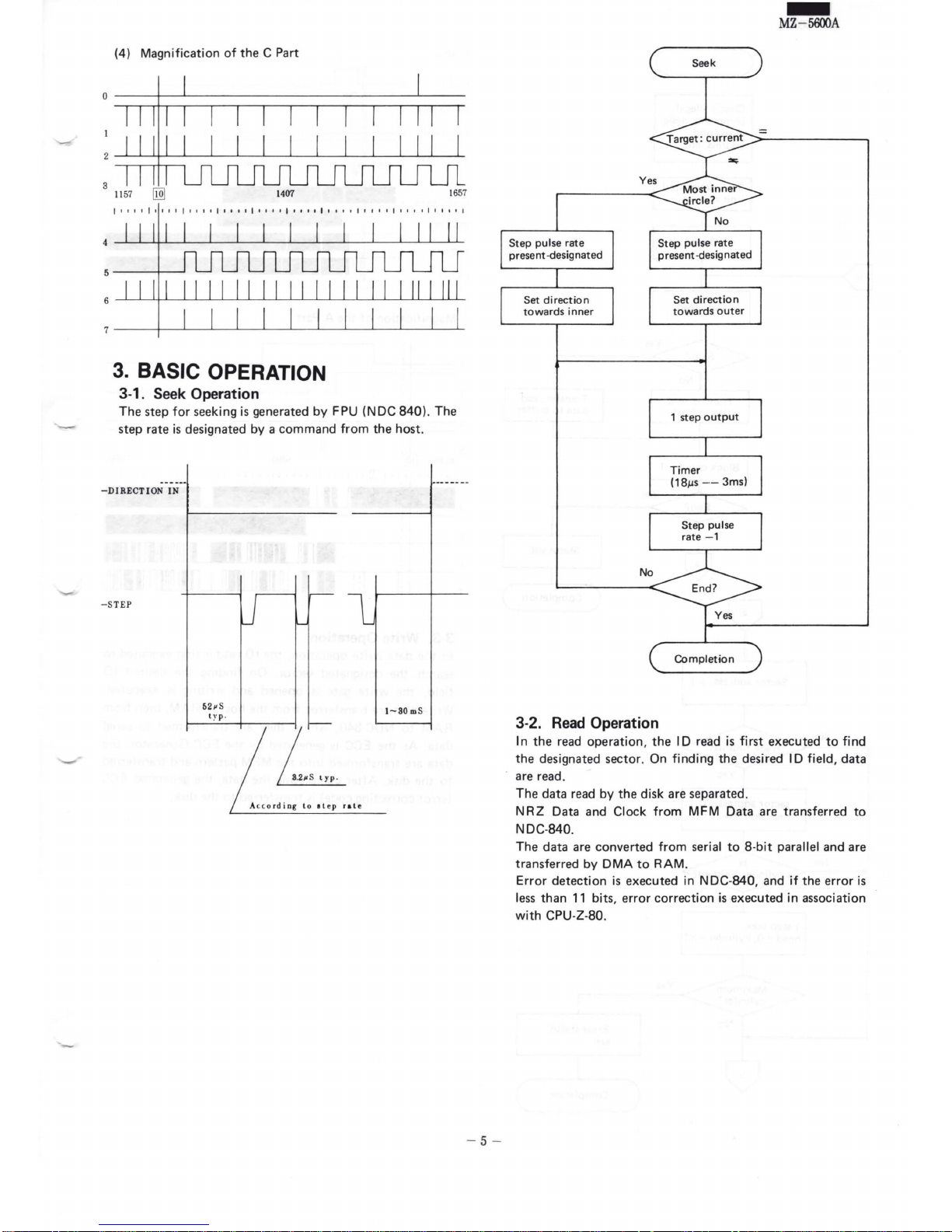

(4) Magnification

of

the

C Part

1

157

!.@]

1407

1

657

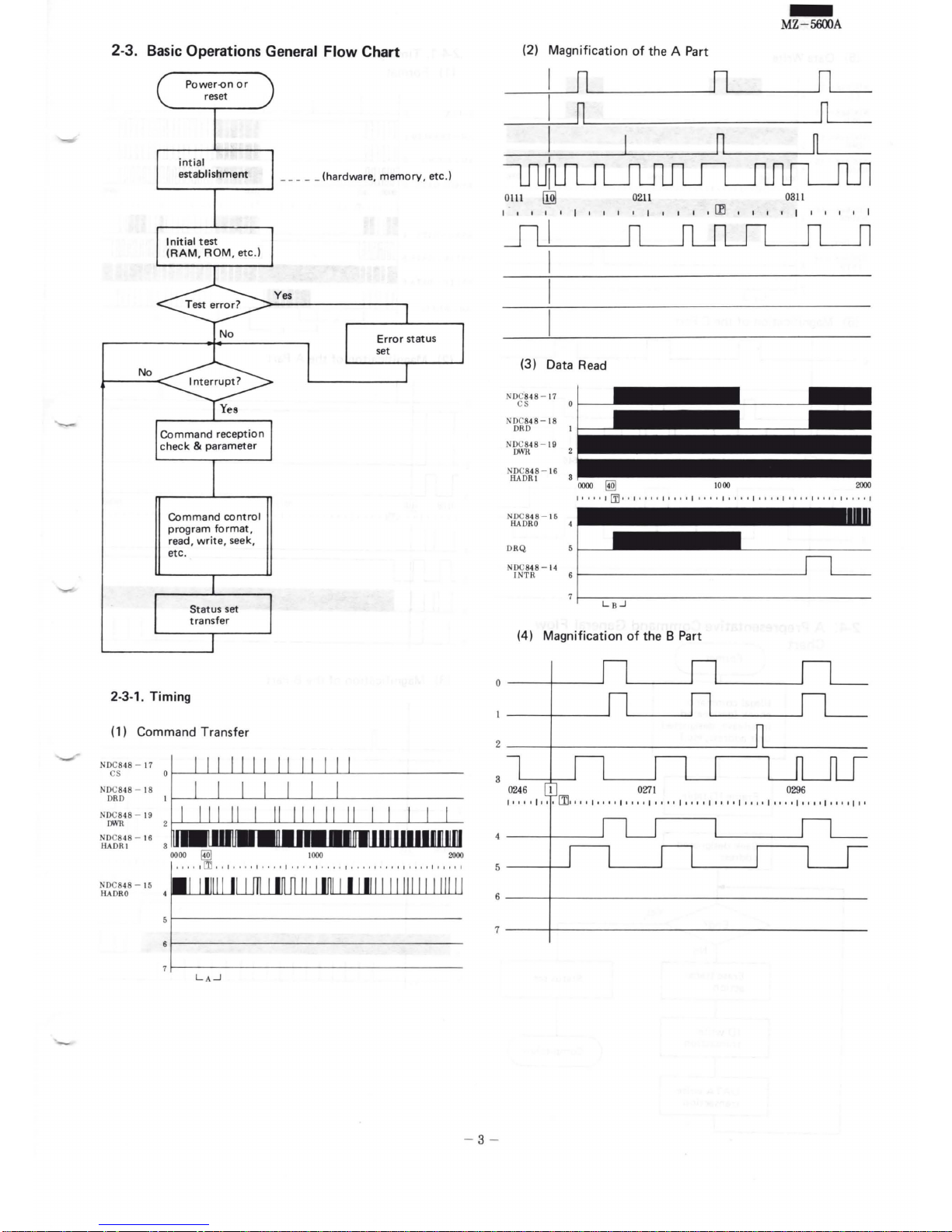

3.

BASIC OPERATION

3-1.

Seek

Operation

The

step

for

seeking

is

generated by FPU (NDC

840).

The

step

rate is designated by a

command

from

the

host.

- DIRECTION I N

-STEP

1-80

mS

L

A

ccordi ng l o llep

rat

e

- 5 -

Seek

1

step

output

3-2.

Read

Operation

-

MZ-5600A

In

the

read

operation, the

ID read

is

first

executed

to

find

the

designated

sector

. On finding

the

desired

ID

field,

data

are read.

The

data

read by

the

disk are

separated.

NRZ

Data

and

Clock

from

MFM Data

are

transferred

to

NDC-840.

The

data

are

converted

from serial

to 8-bit

parallel

and

are

transferred

by DMA

to

RAM.

Error

detection

is

executed

in NDC-

840

, and if

the

error

is

less

than

11

bits,

error

correction

is

executed

in association

with

CPU-Z-80.

Page 7

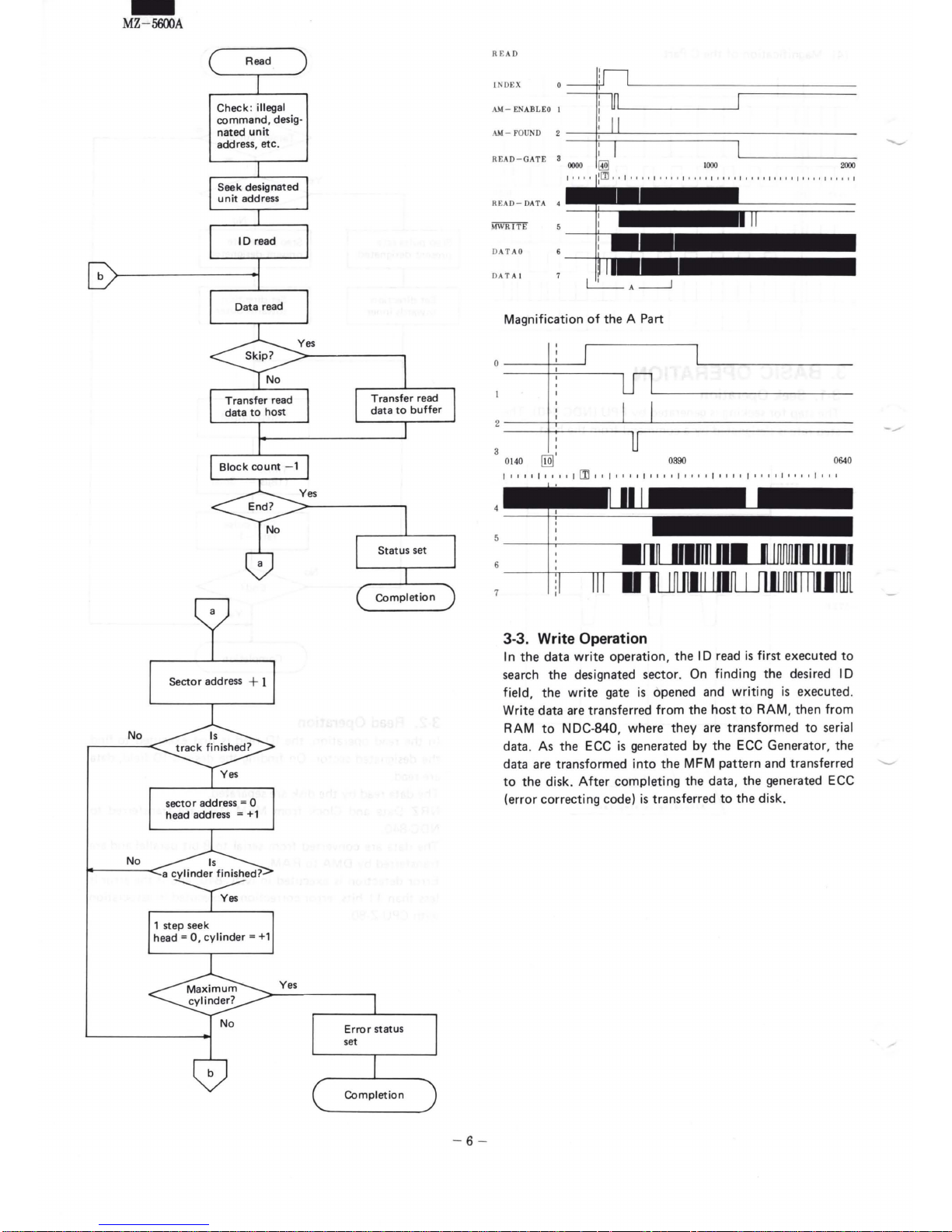

b

-

MZ-5600A

Check

: illegal

command

, desig-

nated

unit

address, etc.

Sector

address + 1

No

No

1

step

seek

head =

0,

cylinder =

+1

Yes

- 6 -

READ

INDEX

AM-

ENABLEO I

AM-

FOlJND

READ-GA

TE 3

~

I

~

~

0000

:

rn

.. I··,. , .... , ... ,,

,,,,,,,

,,,,,,.,

..

,.,,,,,,

D

ATAO

DATA

l

L__A

___j

3

Magnification

of

the

A Part

I

I

I I

0

140

[Q]

'

0390

0640

, , . , . , ... , , m , , , , . , , , , , , , , , , , . , , , , , ,

..

, , , , , .. , , , ,

3-3. Write Operation

In

the

data

write

operation,

the

ID

read

is

first

executed

to

search

the

designated

sector

. On finding

the

desired

ID

field,

the

write

gate is

opened

and

writing

is

executed

.

Write

data

are

transferred

from

the

host

to

RAM,

then

from

RAM

to

NDC-840,

where

they

are

transformed

to

serial

data

. As

the

ECC

is

generated

by

the

ECC

Generator,

the

data

are

transformed

into

the

MFM

pattern

and

transferred

.._.,

to

the

disk.

After

completing

the

data, the

generated

ECC

(error

correcting

code)

is

transferred

to

the

disk.

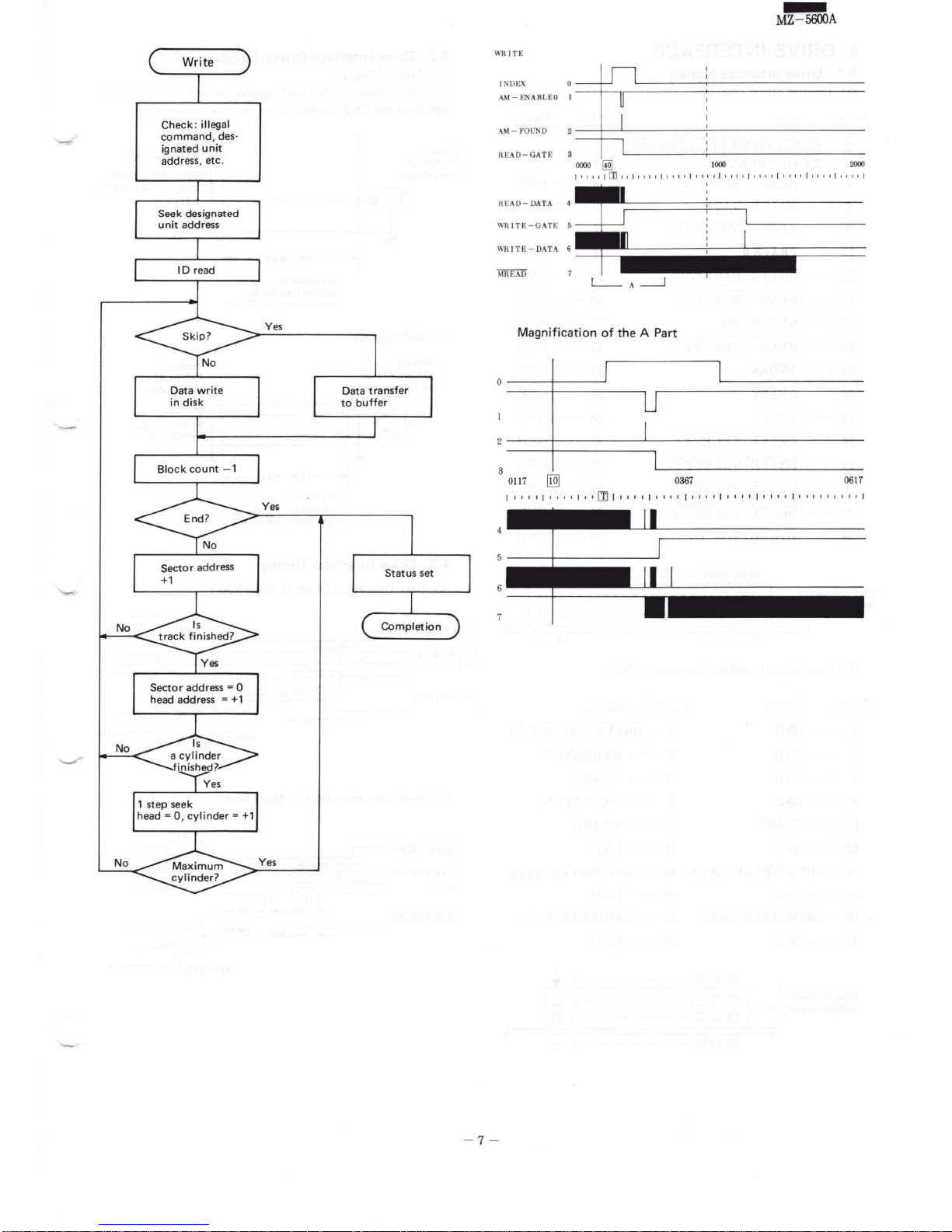

Page 8

No

No

No

-

Check : illegal

command,

designated unit

address, etc.

WR

IT E

I N

DEX

AM

- ENABLEO

AM

- FOUND

RE

AD-GATE

RE

AD-

DATA

WRITE-DATA

6

-

MZ-5600A

0000

~

I

000

2000

,,,

, , r

LrJ

,,,,,,,

r,, ,,,,,,,,,

' '

,,,,,,,,

'''

I•

•' ,,,, ,,,

'

l__

A

__j

Magnification

of

the A Part

0

--t----''

I

2

--~---~'----------

3

I

0117

0367

0617

, . , .. , , , , , , . , m, , . , , , .... , . , , . ,

..

, , , . ,

..

, .. , . , ,

..

, ,

- 7 -

Page 9

-

MZ-5600A

4.

DRIVE INTERFACE

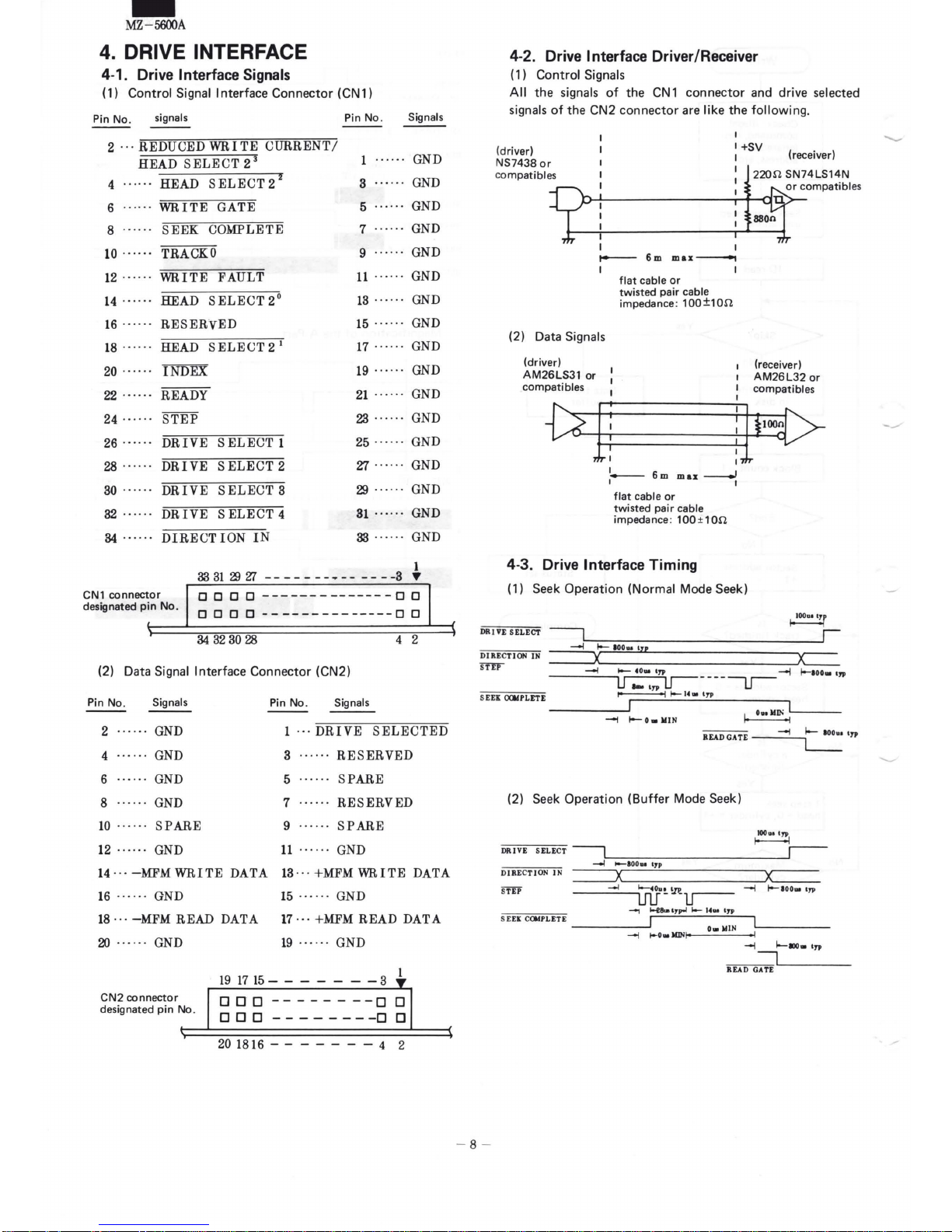

4-1. Drive Interface Signals

(1) Control Signal Interface Connector (CN1)

Pin

No.

signals Pin

No.

Signals

2 · · ·

REDUCED

WRITE

CURRENT

I

HEAD

SELECT

2

3

1

GND

GND

GND

GND

4

HEAD

SELECT2

2

3

6

8

10 ....

..

12 ...

.. .

14 .

.....

16 ......

18 ....

. .

20 ....

. .

22

....

..

24 ..... .

26

····

··

28

... ...

30 . . .

...

32 . .....

84

...

...

WRITE

GATE

SEEK

COMPLETE

TRACKO

WRITE

FAULT

HEAD

SELECT

2°

RESERVED

HEAD

SELECT

2

1

INDEX

READY

STEP

DRIVE

SELECT

1

DRIVE

SELECT

2

DRIVE

SELECT

3

DRIVE

SELECT

4

DIRECT

ION

IN

5

7

9 GND

11 ···

···

GND

13 ······ GND

15

·····

· GND

17 ·····

· GND

19

·····

· GND

21 ····· · GND

23 ·····

· GND

25

··

·· ··

GND

?:l ···

···

GND

29

···

···

GND

81 ······ GND

33

····· · GND

1

33

31

2}

'Zl

- - - - - - - • - - - - - -8

~

CN1

connector

designated

pin

No.

o o o o

--------------0

o I

0 0 0

0--------------0

0.

84

32

30

28

4 2

(2) Data Signal Interface Connector (CN2)

Pin No.

Signals

Pin No .

Signals

2 GND

1 .

..

DRIVE

SELECTED

4

GND 3

RESERVED

6 GND

5

SPARE

8 GND 7

RESERVED

10

......

SPARE

9

SPARE

12 ......

GND

11

......

GND

14

...

-MFM

WRITE

DATA

13 ... +MFM

WRITE

DATA

16

..

..

..

GND

15

.. · ..

· GND

18 ...

-MFM

READ DATA

17 ...

+MFM

READ

DATA

20 ....

..

GND

CN2 connector

designated

pin

No .

t

19

......

GND

19

17

15

- - - - - - - 3

ODD

--------o

ODD

--------0

20 1816 - - - - - - - 4 2

4-2. Drive Interface Driver/Receiver

( 1) Control Signals

All

the signals

of

the

CN1

connector and drive selected

signals

of

the CN2 connector

are

like the

following

.

I

(driver)

NS7438

or

compatibles

I +SV

I

(receiver)

I

t---

6m

max--,

I I

(2) Data Signals

(driver)

AM26LS31

or

:

compatibles

I

flat

cable

or

twisted pair cable

impedance:

100±10.n

-

I

6m

max---'

I

flat

cable

or

twisted pair cable

impedance: 100±10.n

4-3. Drive Interface Timing

(1) Seek Operation (Normal Mode Seek)

(receiver)

AM26L32

or

compatibles

DRIVE

SELECT

DIRE

CTION IN

S'fEP

~

I--

IOOu trp

--~X

~

--1

-

eo

..

'"

--1

1-aoo.

,,

~----~

:-;S E""

EJ[

;;;-

OCAI=P=-:L-=:ET=E

~

IC,. 1n>

--i

-O•JoiiN

--:REA_D_G-AT-E

~In>

(2)

Seek

Operation

(Buffer

Mode Seek)

DRIVE SELECT

--l

1--IOOu

trp

DIRECTION IN

=:J~;----------,-'X'----

_

--~;.;__

......

Ouo

!n.

-l

~

lOO•

In>

UlJ-

~

.....,

~--ta-t,.poo~

t--

14u.

'"

S

EU

C<»>PLETE

____

....J

-~·~·~Joi~IN~~L------

-l

t-O•MINI--

-1

l-IDO•

In>

I

READ

GATE.__

___

_

- 8 -

-

----

Page 10

-

MZ-5600A

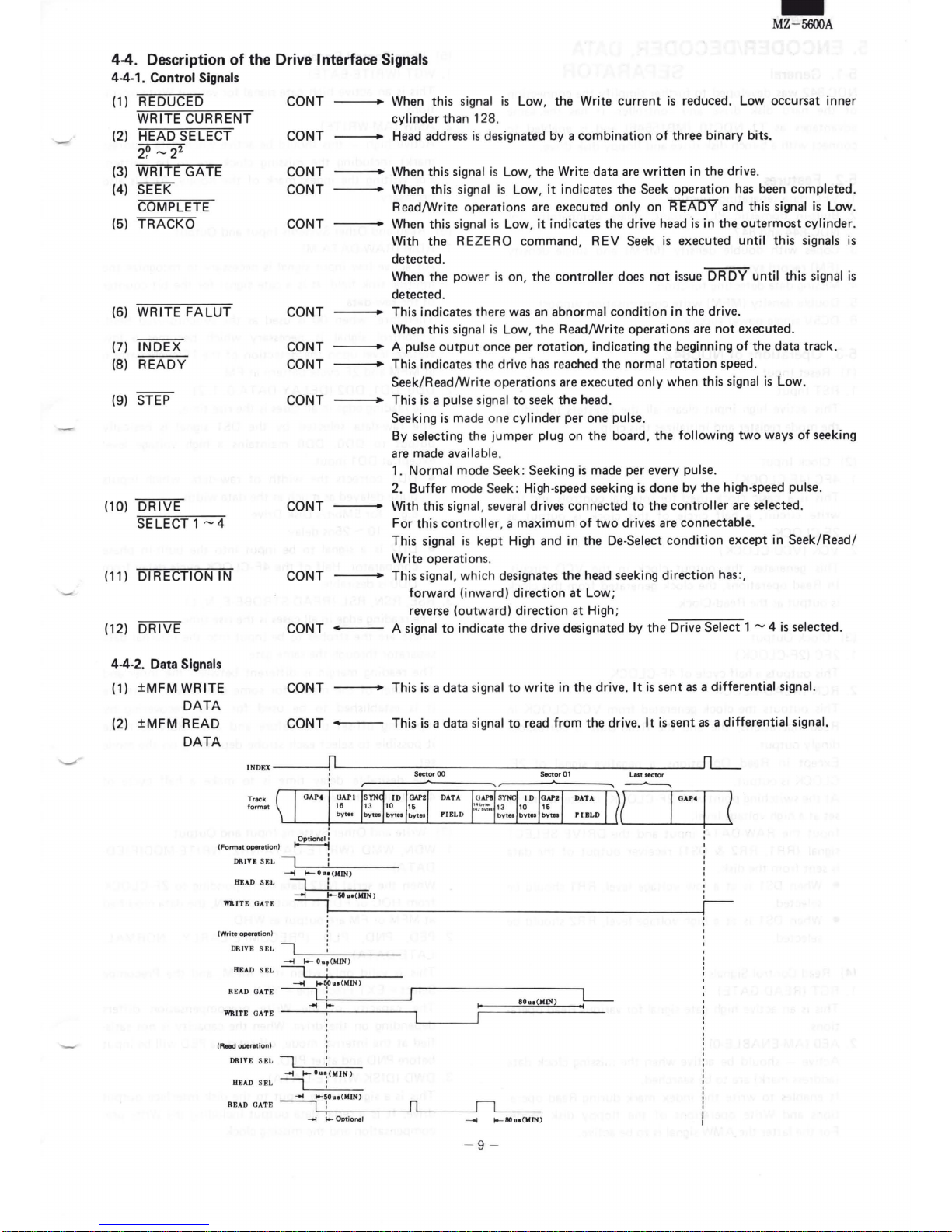

4-4. Description

of

the Drive Interface

Signals

4-4-1. Control Signals

( 1)

REDUCED

WRITE

CURRENT

(2)

HEAD

SELECT

2?-

2

2

(3)

WRITE GATE

(4)

SEEK

COMPLETE

(5)

TRACKO

(6)

WRITE

FALUT

(7)

INDEX

(8)

READY

(9)

STEP

(10) DRIVE

SELECT1

- 4

(11)

DIRECTIONIN

(12) DRIVE

4-4-2. Data Signals

(1)

±MFMWRITE

DATA

(2)

±MFM

READ

DATA

CONT

CONT

CONT

CONT

CONT

CONT

CONT

CONT

CONT

CONT

CONT

CONT

CONT

CONT

When

this

signal is Low,

the

Write

current

is

reduced.

Low

occursat

inner

cylinder

than 128

.

Head address

is

designated

by a combination

of

three

binary

bits.

When

this

signal

is

Low,

the

Write

data

are

written

in

the

drive.

When

this sign

al

is Low ,

it

indicates

the

Seek

operation

has

been

completed

.

Read/Write

ope

rati

ons

are

executed

only

on

READY

and

this signal

is

Low.

When this sign

al

is

Low, it indicates

the

drive head

is

in

the

outermost

cylinder.

With

the

REZERO

command, REV

Seek

is

executed

until

this

signals

is

detected

.

When

the

power is on,

the

controller

does

not

issue

DRDY

until

this

signal

is

detected.

This

indicate

s there was an

abnormal

condition

in

the

drive.

When

this

signal

is

Low,

the

Read/Write

operations

are

not

executed.

A pulse

output once

per

rotation,

indicating

the

beginning

of

the

data

track.

This

indicates the

drive has reached

the

normal

rotation

speed.

Seek/Read/Write

operations

are

executed

only

when

this

signal

is

Low.

This

is

a pulse signal

to

seek

the

head.

Seeking

is

made

one

cylinder

per

one

pulse.

By

selecting the j

umper

plug on

the

board, the

following

two

ways

of

seeking

are

made

available .

1. Normal

mode

Seek

: Seeking

is

made

per

every pulse.

2. Buffer

mode

Seek: High -

speed

seeking

is

done

by

the

high-speed pulse.

With

this

signa

l,

several drives

connected

to

the

controller

are

selected

.

For

this

controller, a

maximum

of

two

drives are

connectable

.

This signal

is kep

t High

and

in

the De-

Select

condition

except

in

Seek/Read/

Write

operat

ions.

---

This signal, which designates

the

head seeking

direction

has:,

forward

(inward)

direction

at

Low;

reverse

(outward)

direction

at

High;

A signal

to

indicat e

the

drive

designated

by

the

Drive

Select

1 - 4

is

selected

.

This

is a data

signal

to

write

in

the

drive.

lt

is

sent

as a differential signal.

This

is a data

signal

to

read

from

the

drive.

lt

is

sent

as a differential

signal.

IN

DEX

----!

'-------....,.,...-

---

----,----------.1

Sector

00

Sector

01

l

•t

aector

,-,-~--~=;~==~==~~~~~;===~~----'~~~

~~

___l____..l._~

__L____._l__l(

I Gm I (

Track

format

{Fo

i1'N

t operet ion)

1

0ptione

l~

:

DR

IT E S E L

HEAD

SEL

WR

ITE OA

TE

{W

rite

o~tion

)

DRIVE

SEL

BEAD

SEL

'

'

'

--f

.._O

.. (lUN

)

!i

--t

1-&0u•(lO

N)

--t

t-50u•OHN)

READ GA

TE

~~+

:

____

__J

WRITE OATE

__

-4-'--Tt---

----,

I

Reed

operation)

DRIVE S

EL

---,

:

-t

t-

Oua,(MJN)

IIEADSEL

~

-+1

,._50u•(W:IN

)

8

0-..

(MIN)

READ GATE

~

L..;..:

____

__.JnL. ___

..JnL

_ _ _

-t

;..._

Optional

---t

1-

80

Ul

(

)f]N

)

- 9 -

Page 11

-

MZ-5600A

5. ENCODER/DECODER,

DATA

5-1.

General

SEPARATOR

NDC-842 was

developed

to

further

simplify

the

connection

of

the

hard

disk drive

and

controller. it

has

the

same

advantages as

T1

NDC10

(MB15546)

and

is

enabled

to

connect

with

a 5 -inch disk drive

and

floppy

disk drive.

5-2.

Features

1.

VFO

data

separating

function.

2. Built-in

domestic

PLL

circuit,

phase

comparator

for

N DC-844

and

84

7.

3.

Copes wi

th

double

density

(MFM)

and

single

density

(FM)

record

system.

4. Missing

data

detecting

function

.

5.

Double

density

(MFM)

write

compensation

support

.

6.

DC5V single

power

supply.

5-3. Operations

of

NDC842

(1) Reset

Input

1.

RST

Input

This active high

input

clears

all

the

registers including

the

mode

register and initializes

this

chip.

(2)

Clock

Input

1.

4FC

(4F-CLOCK)

This

is

a basic

clock

used

for

internal

controls

and

the

write

circuit; a half

circle

of

this

clock

is

output

as

2F-CLOCK .

2. VCK (VCO-CLOCK)

This

generates

the

output

clock

in

the

VCO

circuit

.

In Read

operations,

the

clock

generated

from

this

clock

is

output

as

the

Read-Clock.

(3) Clock

Output

1.

2FC

(2F-CLOCK)

This

outputs

a half

cycle

of

4F-CLOCK.

2. RCK (READ-CLOCK)

This

outputs

the

clock

generated

from

VCO-CLOCK in

Read

operations,

the

and

the

Read-Data

is

correspon

-

dingly

output

.

Except

in Read

Operations,

a negative signal

of

2F-

CLOCK

is

output.

At

the

switching

point

with 2F-CLOCK, it

is

temporarily

set

at

a high voltage level.

Input

the

RAW-DATA

input

and

the

DRIVE

SELECT

signal

(RR1,

RR2

& DS1) receiver

output

of

the

data

is

sent

from

the

disk.

• When

DS1

is

at

a low voltage level , R R 1

should

be

selected.

•

When

DS 1 is

at

a high voltage level, R R2

should

be

selected.

(4) Read

Control

Signals

1.

RGT

(READ-GATE)

This

is

an active high gate signal

for

various Read

opera-

tions

.

2. AEO (AM-ENABLE-D)

Active -

should

be active

when

the

missing

clock

data

(address

mark)

are

to

be

searched

.

it

enables

to

write

the

index

mark

during

Read

opera

-

tions

and

Write

operations

of

the

floppy

disk

mode.

For

the

latter

the

AMW signal

is

to

be active.

-10-

(5) Write

Control

Signals

1. WGT (WRITE -BATE)

This

is

an active high gate signal

for

various Write opera-

tions

.

2. AMW

(AM-WRITE)

Active high - this

should

be active

when

data

(address

mark)

including

the

missing

clock

are

to

be

written

.

For

writing

the

index

mark

of

the

floppy,

AE1

is

also

necessary.

(6) Read

and

Other

Systems

Input

and

Output

1. RDM (RAW-DATA-M)

An

active low

input

signal

is

necessary

to

recognize

the

internal sink field.

it

is

a gate signal

for

the

bit

counter

of

the

raw-

data

.

Therefore,

when

00

is

used

as

the

synchronized

field,

a

control

signal

is

necessary

which

becomes

a low

voltage level

upon

the

detection

of

the

1 F

cycle

pattern

at M FM

and

2 F cycle

pattern

at

FM.

2. DDO, DD1,

DD2

(DELAY-DATA-0, 1, 2)

The

reading edge in all cases

is

the

rise

time.

The

raw-data

selected

by

the

DS1

signal

is

basically

output

to

DDO. DDO

maintains

a high voltage level

except

at

DD1

input

.

• DD1

corrects

the

width

of

raw-data,

which

inputs

pulse

delayed

as

much

as

the

data width.

e.g.:

for

5Mbit/s

Disk Drive

10-

25ns

delay

•

DD2

is

a signal

to

be

input

into

the

built

-in phase

comparator.

Half

of

the 4F-CLOCK

cycle

delay

from

DDO

is

desirable.

3.

RSE, RSN , RSL (READ-STROBE-E,

N,

L)

The

reading edge in all cases

is

the

rise

time

.

These

are

the

strobes

to

be

input

into

the

internal

data

separator

through

the

same

gate.

The

reading margin

is

different

between

the

inner

and

the

outer

of

the

media

for

some

disk drives,

therefore

it

is

established

to

be used

for

error

recovering

by

inputting

off-set

data

before

and

after

RSN

to

make

it possible

to

select

each

strobe

depending

on

the

mode

set.

The

desirable delay

time

is

to

make a half

cycle

of

4F-CLOCK

the

center.

(7) Write and

Other

Systems

Input

and

Output

1. WDN, WMD (WRITE-DATA-NRZ, WRITE-

MODIFIED

DATA)

When

the

serial N R2

data

corresponding

to

ZF-CLOCK

from

HOC

or

FDC

is

input

into

WDN ,

the

data

modified

at

MFM

or

FM are

output

as WHD.

2.

PED, PND, PLD

(PRECOMPE-EARLY

, NORMAL,

LATE-DATA)

This

is

valid

only

when

it

is

MFM,

and

the

Precompe

Select=

EXT

Precompe

= YEX.

The

capacity

of

the

Write

precompensation

differs

depending

on

the

drive. When

the

capacity

is

not

satis-

fied

at

the

internal

mode,

off-set

data

PED will be

input

before

PND

and

after

PLD .

3.

DWD (DISK-WRITE-DATA)

This

is

a signal

to

b~

input

to

the

disk

interface

output

drive.

it

is

a serial

data

output

including

the

Write

pre

compensation

and

the

missing

clock

.

Page 12

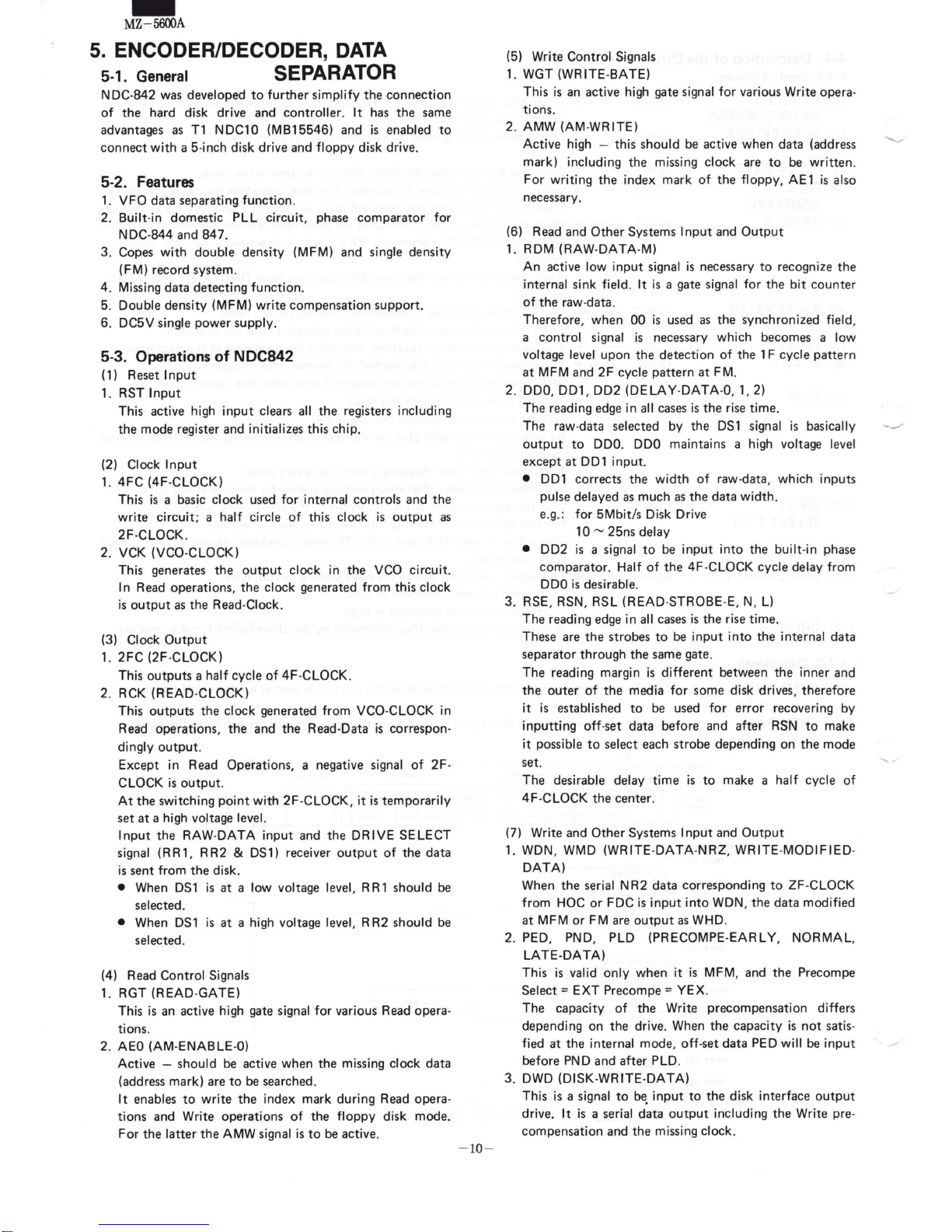

(8) Write Precompensation Detecting Pattern

The precompensation

bit

pattern

is

shown below.

(2) 4F-Ciock

Input

and 2F Clock

Output

-

MZ-5600A

The pattern shows the 3rd

bit

timing,

monitored by the

4-

bit

shift

register.

bit

pattern

0 0

1

0

2

0

3

0

4 0

5

0

6

0

7

0

8

1

9

1

A

1

B

1

c 1

D

1

E 1

F

1

*Th

e data are

effective

at

MFM

.

0 0 0

0 0

1

0

1 0

0

1

1

1

0 0

1 0 1

1 1

0

1 1

1

0 0 0

0

0 1

0 1 0

0

1

1

1

0

0

1

0

1

1

1

0

1 1 1

precompensation

NORMAL

CLOCK

EARLY

CLOCK

NORMAL

DATA

LATE

DATA

-----

-------

EARLY

DATA

NORMAL

DATA

LATE

CLOCK

NORMAL

CLOCK

NORMAL

DATA

LATE

DATA

----

-----

EARLY

DATA

NORMAL

DATA

When

the

precompensation select is

internal,

precompensation

is

added.

5-4. Timing

(

1)

Mode Set

Input

oil 9.8

no

I

AI,

AO

I

CS

'----JI(HOLD)

·

·-8

Dl

oil 6.8

Dl

(3)

Read

Input/Output

1)

Read

Clock and N RZ

Output

Data

•

b

ORCR

~

I

v---

BIT

SEL

lo-b

I<&DO

logic

1

0

I

-

ORDT

yp-

~

lyp-

1--

8DO

8.101

OAMF

7P

lyp

&.&no

11.6no

2)

Read

Clock (in

Read

operation/Non-

Read

operation)

02

FC

~

~

r

\'----------.1/

~

ORCK

r---~

(in

Non

-Read

--+1

\.._

__

.-~/

\'----'

operation)

lyp

lyp

6.8

DO

1.2no

3)

I V

CK

c

')

-

f:

.7.

I-

o - 7 ( I R

SE

, I R S

N,

I R S L )

IVCK

--J

Data Separate

Window

(interna

l)

r_

\

lyp 10.7

Dl

window

I

RSE,

IRSN.

IRSL

--

- - lyp

12.6

DO

window

.I

\.

----if-+--

lyp 8.8 DO

-11-

Data Separate

---l..IJ

Clock

(internal)

\

I

Page 13

-

MZ-5600A

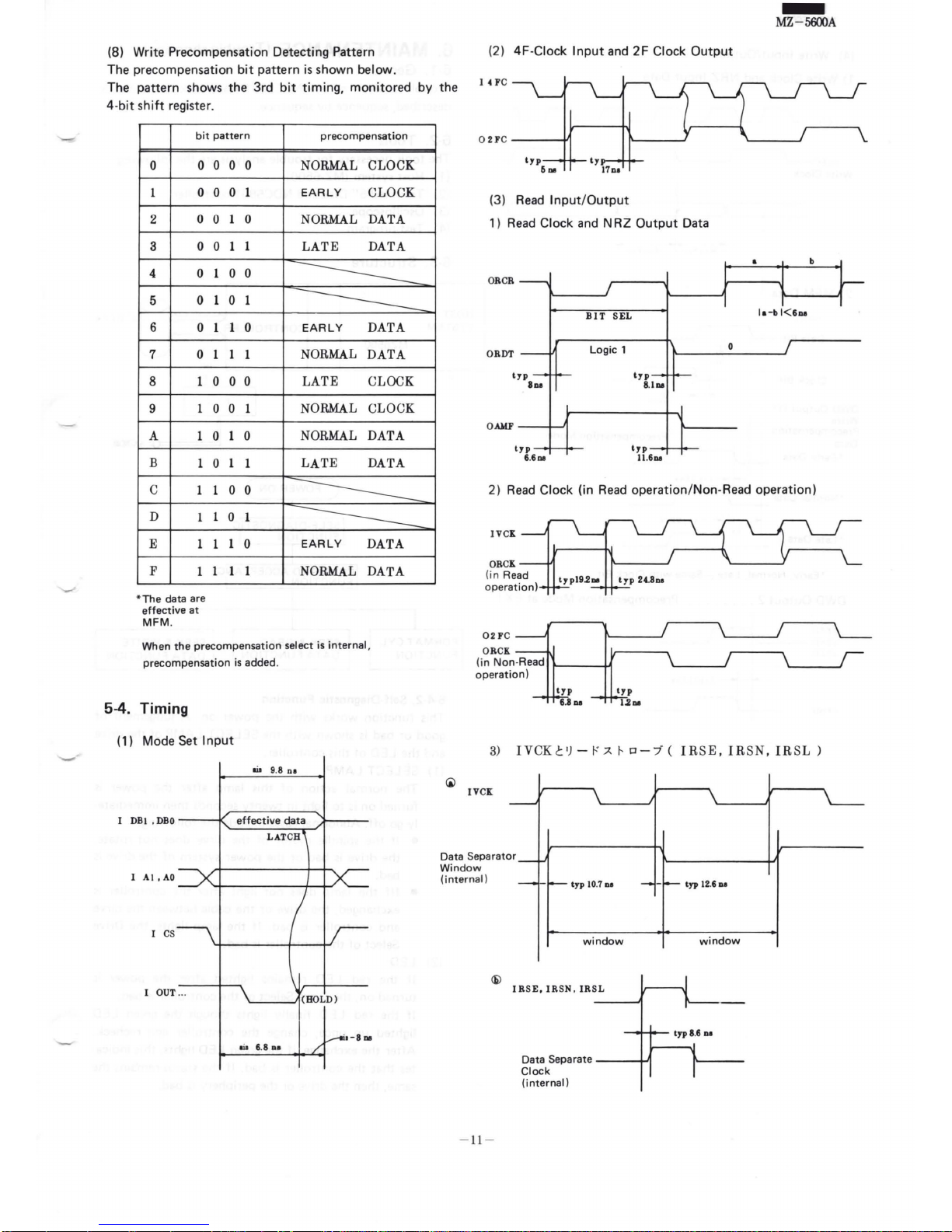

(4) Write

Input/Output

1)

Write Clock

and N RZ

Input

Data

14

FC

0

2F

C

Write Clock

2) MFM Data

OWMD

Data

Bit

Clock

Bit

DWD

Output

(1)

Write

M

in8n

::s

M

in

4 n s

Precompensation

Data

··

..................

........

..... Precompensation Mode

*Early

Data

*Normal

Data

*Late

Data

* Early,

Normal,

Late-

Same

with

Clock

Bit

DWD

Output

2 . . . . . . . . Precompensation Mode at

EXT

IPED

IPND

---..J

I

!PLO

ODWD

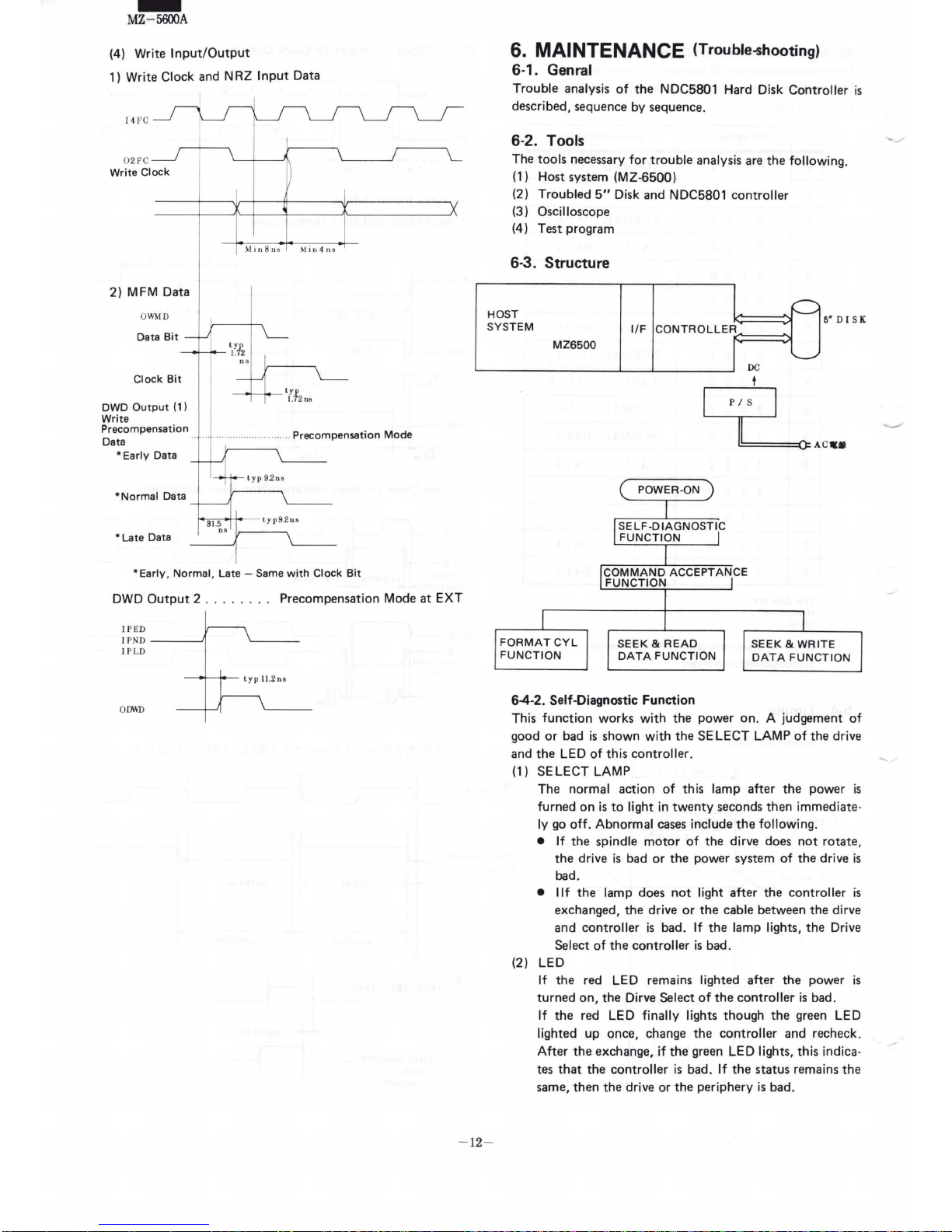

6.

MAINTENANCE (Trouble-ihooting)

6-1. Genral

Trouble analysis

of

the NDC5801 Hard Disk Controller

is

described, sequence by sequence.

6-2. Tools

The tools necessary

for

trouble analysis

are

the

following

.

(1) Host system (MZ-6500)

(2) Troubled

5"

Disk and NDC5801 controller

(3) Oscilloscope

(4) Test program

6-3. Structure

I

r---

HOST

r------

SYSTEM

1/F

CONTROLLER

6"

D l S K

MZ6500

I

DC

6-4-2. Self-Diagnostic Function

This

function

works

with

the power on. A judgement

of

good

or

bad

is

shown

with

the SELECT LAMP

of

the drive

and the LED

of

this controller.

(1) SELECT LAMP

The

normal action

of

this lamp after the power

is

turned on

is

to

light in

twenty

seconds

then immediate·

ly

go

off.

Abnormal

cases

include the following.

•

If

the spindle

motor

of

the dirve

does

not

rotate,

the drive

is

bad

or

the power system

of

the drive

is

bad.

•

llf

the lamp

does

not

light after the controller

is

exchanged, the drive

or

the cable between the dirve

and

controller

is

bad.

If

the lamp lights, the Drive

Select

of

the controller

is

bad.

(2) LED

If

the red LED remains lighted after the power

is

turned on, the Dirve Select

of

the controller

is

bad.

If

the red LED

finally

lights though the

green

LED

lighted up once, change the controller and recheck.

After

the exchange,

if

the

green

LED lights, this indica-

tes

that

the controller

is

bad.

If

the status remains the

same,

then the drive or the periphery

is

bad

.

-12-

Page 14

._

6-4-3.

Basic

Operations

of

the Controller

To check

if

the self-diagnosis

is

executing normally after

the

controller

is

turned on

or

reset:

( 1)

If

the red LED remains lighted after the power

is

on or

reset.

CD

Confirm

if

the MPU Z-80 39PIN

READ

signal

is

output

after

eset

.

(ID

MPU Z-80 39PIN

CLK

is

normal

or

2.5MHz.

• 26LS31 (5F)

is

bad.

• 74LS74 (5C)

is

bad

.

• NDC842 (7G)

is

bad

.

•

OSC

(6G)

is

bad. 10MHz

@

Is

the RESET signal at High?

•

TL7700

(&B) and the peripheral

circuit

are

bad

.

• RESET

from

the host and the

circuit

are

bad.

• NDC848

is

bad.

(2)

If

the red LED remains lighted after the

green

LED

lights

with

the power on

or

reset,

CD

Change

the controller and reconfirm.

•

If

the green LED lights after the change, this indicates

that

the controller

is

bad

.

•

If

the status remains the

same,

then the drive

or

the

periphery

is

bad.

6-4-4. Operation Check

with

the Self-Diagnostic Switch

(1)

Read

Test

•

RD

(SW3) switch

is

ON.

• ST (SW1)

switch

is

ON.

CD

If

the NG lamp doe

:;

not

light

unitl

15 minutes after the

switch

is

on,

•

lt

can

be

judged

that

the

Read

system

is

normal.

6-4-5. Impossibility

of

Command Acceptance

(1) Host Interface Circuits

RC

SET

Ill

.Aa

AJ

~~

'~

ts-'1!

I

;}.,

_s,lSIU_f

6\110-

~'!

11.

y

8

•

~

~J1

~

-

® The

NG

lamp lights:

-

MZ-5600A

a)

Confirm NDC847 (8G) Pin 2,

13-5V.

•

TL497

(88)

is

bad.

• Peripheral

circuit

of

TL497

is

bad.

b) Confirm NDC847 (8G) Pin

8t{).5V±2.0V

• NDC847

is

bad.

c) Confirm the REad data from the disk.

• NDC842 (7G)

is

bad.

• NDC840 (4E)

is

bad.

• NDC846 (4G)

is

bad.

•

74LS123(8H)isbad.

• 26LS32 (5E)

is

bad.

• N DC84 7 (8G)

is

bad.

d)

74LS123 (8H) Pin 12:

• Confirm Low level at 260ns+30ns.

(2) Write Test

•

RW

(SW4) switch

is

ON.

• ST (SW1)

switch

is

ON.

CD

If

the NG lamp

does

not

light

until

15 minutes after the

switch

is

on,

•

lt

can

be judged

that

both the

Read

and Write

sys-

tems

are

normal.

® The

NG

lamp lights:

a)

If

the

Read

system

is

normal,

it

can

be

judged

that

the Write system

is

abnormal.

•

NDC842 (7G)

is

bad.

• NDC840 (4E)

is

bad.

• NDC846 (4G)

is

bad.

• 74LS38 (6C)

is

bad.

• 26LS31 (5F)

is

bad.

~-

se

"''

~~

AI

Y~

wn·,

I I

~

•. , oft

w

;.~

,~~

~·

l.bo:"'

~

-:-::

~

~

lA

r11

11

VT:JJ

68

-

-

t;:JC.:rc

/1.6

AS

M

~

~

~

X1ll'Jr

~

~A

I

.1

,,_,

l:tSGf

r---

~

..,

I

...WXJIL,

·a·

7£1

18..r

CS

~

r

91.&

~rr=~

•

::zax:

~-:::

A y

F.f

~

~

I

::

~

9

..

~

All@

._.,

~

'-

.-d.K./

811

..

!If

tell!!ll

81

~

_l

~o

8

~

6A

=~

I·

/:<re~

~

817

5B

()RQ

lt

L1!l

11.1:1

INr.

88

lYNSe

~

CJ,llf.F

M

014

OIJ

()I;>

011

01.

fl

01

06

os

C><J

DJ

02

01

{)N

:m

·u

-m

A e

HD1

A'.:

:!

JA

'!:!:

~

HOJ

IPl

._HO;>

1\2

~

;;

-

~--~

c

.13

l:s'm

~Jt,

~

11

8

;;;

fll

8~

Al3

~

DtR

r:

ts;;;s

-13-

Page 15

-

MZ-5600A

(2) H t I terface LSis

os

n

r~

~5

~-

HOJ

Hr).;>

<D~

~

(~

llf]R

~

~~HA~}

(

DR.b

~

~R

...I,JD

~-

,.:K"_n

""""''""'

RMI

1~

j~.;>Kn•l

rxr

"I

r5re

r

~Ls

l

-a!:::

_8.

·~·

:RJ

[IC

~

~"-~

~

_,..,.,~<D®

..11.

NOC848

'~11

.naru

~

18

........

""A\

-

_(J;

'':!:.

?Nti~

:Bz1t>

.IJ.

31_

JJ

'•IOSII"fi'O

~

_LC

_15

NC

JtJ

NC

lM:

_/8

M:

ADI!O

~

~~

...Jii

::

..1

...,j,.,

~~

)1

~!...,

,,iiJii"l

)(i

~l

..L

~

.uf:..

p!)

lS&_

IS/

L.Y. • .,

·-;&:Q

.

.n

..-j~.:;

_TlliL

r-~~~

r-

~~

COW'MD

-~

!Si

'""'

___

;:,;;(!5

r-,...,

01"1

--

"

~~

~~~

lf""'Y"

L!.

_.2.3

~;:i

~I!

rl

~

T'

l !

~~'!

..21

~~

i

--.1

aK.-slNlr

..21

L:

..

:--.~

--

-·

~lr

IKA

fllr1

~~

UN"

~~

(3) Status 0

Read

D7

DO

l

STATUS

J

Ll

N

SELF-OIAGNOSIS

: 1

DISK

DRIVES

0:

~10MB,

1:

>10MB

DIR

INPUT

: 0 ,

OUTPUT

: 1

'----I

DRQE

: 1

DRO

: 1

ERROR

: 1

I

NTR

: 1

BUSY : 1

Q)

Status 0

is

abnormal though MPL Z-80 and the internal

circuits (NDC840- etc.)

are

operating

and

the self -

diagnosis

are

normally completed.

• NDC848 (4B)

is

bad.

• The host interface circuiti

are

bad.

®

One

byte

of

command

is

sent

but

the

next

DRO

does

not

rise.

a)

If

NDC840 (4E) Pin 1

is

High,

• NDC848

(4B)

is

bad.

b)

If

NDC840 (4B) Pin 1

is

Low,

• NDC840

(4E)

is

bad.

• The

IC

peripheral

of

MPU Z-80

is

bad.

® A command

was

transferred

but

it

does

not

start operating.

a)

If

NDC840 (4E) Pin 1 stays High,

•

N DC840

is

bad

.

• NDC848 (4B)

is

bad

.

• The host interface

circuitry

is

bad.

6-4-6.

Read

Mode

CD

The compelte

IRQ

does

not

rise

.

• The host interface NDC848 (4B)

is

bad.

-14-

129

lllmr

lJI

lfl1fnt

149

~-G>{j)

151

141

:~:

lsJ.

151

rg:

~

~

~~.-m

.~,

Q)

?~

pV.;>()

mmrQ>

• NDC840 (4E)

is

bad

(DMA).

®

lt

started operating

but

it

always

gets

an

Error.

Reconfirm ltesm:

a)

Recoefirm NDC847 (8G) Pin 2,

13-5V.

•

TL497

(8B)

is

bad

.

• The peripheral circuits

of

TL497

are

bad

.

b) Reconfirm

NDC847 (5G) Pin 8

+5V

±2.0V.

• EDC847

(8G)

is

bad.

c)

Confirm

Read

Data

from

the disk.

• NDC847 (7G)

is

bad.

• NDC840 (4E)

is

bad.

• NDC846 (4GT

is

bad.

• 74LS123 (8H)

is

bad.

@

lt

started operating

but

it

sometimes

gets

an

Error.

a)

Confirm NDC847 (8G) Pin 8 +5V ± 2.0V.

b) 74LS123 (8H) Pin 12:

• Confirm Low level at 260ns±30ns.

6-4-7. Write Mode

CD

The complete I RO does

not

rise, though the command

is

transferred.

• cd.

6-4-6CD

®

lt

always

gets

an

Error, though

it

started operating.

a)

In the

case

of

an

ID Error, refer

to

6-4-6(2)

b) Data Write Error:

• NDC842 (7G)

is

bad.

• NDC840 (4E)

is

bad.

• NDC846 (4G)

is

bad.

• 26LS31 (5F)

is

bad.

®

lt

sometimes

gets

an

Error, though

it

started operating.

a)

In the

case

of

an

ID Error, refer

to

6-4-6®

b) Data Write Error:

• cf.

6-4-7~

Page 16

7.

EXPLANATION OF LSI

7-1.

NDC840

1)GENERAL

NDC840

is

a highly integrated one-chip Hard Disk Control-

ler (HOC).

This high-speed controller

uses

a dual buffer.

A

DMA

controller

is

built

in HOC.

FEATURES

• Transfer Rate between HOC and a Hard Disk Drive

(HOD)

20

Mbits/s

• Buffer

•

DMA

Dual buffer

ava

ilable

DMA

controller in HOC

•

Transfer Rate between Host

and

HOC

DMA

dual=

2.3MB/s (max)

• Data check, Correction

CRC

or

ECC

(11

bit

burst correct ion)

• Drive

1/F

SMD

1/F

or Floppy

1/F

• Data

Bus

• Dynamic Memory

• Power Supply

8-bit timign signal bidirection

Refresh

timing

signal bidirection

+5VDC

2)

APPLICATIONS

2)-1. Main Memory Direct Transfer

H

O

MAIN~=~

~

MEMORY

Main Memory

When

a Main-Memory cycle time

can

follow

up a disk

transfer rate, data

can

be

transferred

directly

into

the

Main Memory.

(1) Main-Memory

cycle time (Byte Transfer)

10

6

0

. k T f R (b.

I )x 8 Memory Cycle Time

(J.LS)

ts

rans

er

ate

tt s

2)-2. Single-Buffer Transfer

H

0

s

T

PROGRAM

EJ

RAM

(1) RAM

HOC PROGRAM

area

*BUF =BUFFER

BUF: 1 SECTOR

or 1 TRACK

BUF

(2)

HOST, BUF Transfer Rate

-

MZ-5600A

When

data

are

transferred between the 5"

FXD

and host,

data

shall

be

accomdated temporarily in a

buffer

register.

Transfers

can

be

executed at any transfer rate.

(3) BUF

area

A

buffer

area

can

be

allocated

as

one

area

of

Main Memory ,

2)-3.

DUAL-BU

F Transfer

(1) RAM

P~M

6

(RAM)

HOC PROGRAM

area

BUF 0, BUF 1

area

Either BUF

is

a 1 SECTOR BUF.

2KB/CHIP

RAM - maximum SECTOR

length=

512 Bytes

A

buffer

transfers data in time-sharing.

(2)

HOST, BUF Transfer Rate

When

data

are

transferred between the 5" F

XD

and

host,

data

shall be accomodated temporarily in a

buffer

register.

Transfers

can

be

executed at any transfer rate.

In multisectors, transfer rates

of

the host

and

buffer

deter-

mine sector interleaves.

3)

TRANSFER

MODES

3)-1. Single Buffer

DMA

shall

be

transferred regardless

of

the disk transfer

rate.

The hardware

of

the host shall become

Japanese.

Host cycle-steal

and

prior

interruption.

In a

multi

-sector mode, process efficiency

decreases

.

(e.g

.)

READ

DATA

(DISK~

HOST)

~~!

~,\T

I

SECTOR

1 I n SECTOR interleave I

SECTOR

21

D

ATA

-15-

l:iECTOil I

DATA

S E

<.:

TOU

2 DATA

lDil:iK-BUJ-

'

l:iECTOH I

DATA

BUF-HO

S T

Sector interleaves

need

ti

me

for

buffer

- host

transfer .

l!ll:iK-BUJ-

'

SEC

TOR

2

DATA

BUJ-'

-HOl:iT

Page 17

-

MZ-5600A

3)-2. Dual Buffer

DMA shall be

transferred

regardless

of

the

disk

transfer

rate.

The

hardware

of

the

host

shall

become

Japanese

.

Host

cycle-steal and prior

interruption.

In a multi-sector

mode,

process efficiency decreases.

(e.g.) READ DATA

(DISK~

HOST)

DISK

transfer

rate 5 Mbit/s

(1.6us/Byte)

HOST

transfer

rate 3,2

J.Ls/Byte

UUF

0

tiEUTOR

IllATA

IUISK

- H

UFO

SECTO

R I DATA

BUFU - UOti'l'

tiECTO

H 2

UATA

DISK

- H

UF

I

I

tiEC1'0H4

tiE

C'I'OR3 DATA

I

UltiK

- H

UFO

SECTO

R3

DATA

SEU'

I'OR2 UATA

DUF 1- IIOS T

DUFO

-UOST

SECTO

R 4

DATA

DISK

- B

UF

I

4)

INTER

FACE

SINGNALS

D0-7

A0-2

A3-15

READ/

WRIT

E/

CS/

D

IR

DRQ/

M-READ/

M-wRITE

/

HRQ

HLDA

ADR-E

DM.EM

PHASED/

TIME-{)UT

ATN

CH

OEX

C/

CLKO

CLK I

RE

ST

/

VDD

~

E

L_

NDC

840

RD

DDO

WO

I

RC

DD7

AM.EO

AOO

AMEI

I

A02

I

DXP

A03

R

DY

I

l'LT

A 15

SK

C

RED

TRKO

WRT

SELD

CS

DIR

DD

IR

STEP

ORQ

MSTP

MR

ED

RW

C

MWR

T

HDSI

HRQ

HD

S2

HLDA

HDS3

AD

RE

HDS4

DRSI

DMEM

DRS2

DRS3

PHAS

DRS4

T I

MO

AMWT

ATN

AMFD

RO

C

HO

E

WO

SE

CR

WPRT

TAOI

TA02

C

LKO

TA03

CLKI

TA04

R

EST

svc

VDD

vss

VDD

VSS

~

READ-DATA(READ-0)

WRI

TE-DATA(WRfTE-0

)

READ-

CLK(READ

- C )

~~-ENADLEO(B-STBO

)

AM-ENA8LE1(8-STDI

)

IN

DEX( INDEX )

READY(READY )

WRITE

FAULT(FAULT)

SEEK

COMPLETE(tiEEK-END

)

TRACK

00

(ON- CLY)

DRIVE

SELECTED(

SELECTED

)

DIRECTION

/ ECC

WRITE

STEP

( SEEK

ER

J

MICRO-STEP( 89)

REDUC

E-WC

(D8

)

HEAD

SEL

2'

(DO)

HEADSEL

2' (DJ

)

HEAD SEL 2' (

82)

H

EADSEL

2'

(D3)

DRIVESEL

I (D4)

DRIVESEL2 (85

)

D

RIV

ESEL3 (D6

)

DRIVE SEL 4 (D7)

AM

WRIT

E

AM

FOUND

(AM

FOUND )

RE

AD

OATE

WRIT

E OATE

SE

CTOR

WRIT

E PROTECT

TAO

I

(

TAO

I )

TAO

2

(TAO

2)

TAO

3

(TAO

3 )

TAO

4

(TAO 4 )

( SERVO )

VSS

* Signals in parentheses are used for SMD 1/F.

-16-

4)

-1. Floppy Interface

NDC840

AM-ENABLED

AM-FOUND

NRZ-READ - DATA

READ-

GATE

READ-CLK

NRZ -WRITE - DATA

w~g~-

AM-WRITE

WRITE-GATE

HO

C

READY

WRITE-FAULT

S

EEK-COMPLETE

TRACKO

D

RIVE-

SELECTED

I NDEX

DIRECTION

STEP

REDUCE

-W-

CURRENT

HEAD-SEL

2°

H

EAD-SE

L 2

1

HEAD-

SEL

2

2

DRIVE-SEL

l

DRIVE-SEL2

DRIVE -SEL8

D

RIV

E -SEL4

4)-2.

SMD

Interface

NRZ-READ-DATA

R

EAD

- C

LK

S

ERVO

- C

LK

I

I

NDEX

I

NDC842

AM-DETECT

DATA

-

SEPARATOR

(

UFO

)

--

------

WRITE

-PRE

COMP

MFM-GEN

..----

R

E

c

E

I

V

E

R

~

r---

D

R

I

V

E

R

'--

r---

D

R

I

V

E

R

~

r-

r---

r--

f---

MFM

-READ-DATA

MFM-W

RIT

E- DATA

WRITE-GATE

WRI

TE-FAULT

SEEK-CCI\IPLETE

TRAC

KO

DR

IV

E-SELECTED

I NDEX

DIRECTION-I

STEP

REDUCE-W-CURRENT

HEAD-

SEL2o

HEAD-SEL2

1

HEAD-SEL22

DRIVE-SELl

DRIVE-SEL2

DRIVE-SEL3

OR

JVE-

SEL4

R

E

1---

R

EAD

- D

ATA

LK

C

LK

c

1---

HEAD-

C

E

1---

SERVO-

I

V

1---

I

NDEX

E

R

SECTOR

~~

I---

S EC

TOR

f---

WRIT

E -

C

LK

DATA

NRZ-WRI TE-DATA

TAG

I

TAG

2

TAG

3

UN I

'!'-SELECT-

TAG

BUS-STBO

BO

)

89

BUS-STB

J

READY

FAULT

SEEKER

WPRT

SELEC

TED

ONC

YL

AM

FOUND

HO

C

D

f---

WRITE-

R

I

f---

TAG

I

V

f---

TAG2

E

f---

TAG3

R

r--

UN

IT-

S

'--

r-

-

L

t--

D

-

A

t-

R

-

I

-

T

V

-

c

E

-R

H

f--

f--

~

~

f-f--

A

R V

f--

T

E

c

IR

.....!!._

~

,.---

D

f--

R

'--

I

f--

'--

V

f--

E

'---

R

f--

..__

r--

R

E

c

E

I

V

E

R

~

ELECT-TAG

BITO

" I

,, 2

,, 3

,, 4

,,

5

,,

6

,, 1

,,

8

,,

9

UNIT-SEL-2

0

2'

22

//

28

UN IT-R EADY

FAULT

SEEK-ERROR

WRITE-PROTE

CT

UN

IT-SELECTED

ON-CYLINDER

AM-FOUND

SPARE

Page 18

5) DESCRIPTION OF SIGNALS

5)-1. Host

1/F

Signals

(1)

DATA-BUS(DO-D7)

8-

bit

bidirectional data

bus

is

in a tristate.

Data

are

transferred between

CPU

and

the host.

(2)

READ

This active low signal

is

used

to

take parameters

such

as

data, status,

DMA

address, BYTE counter

and

mode

from

HDC.

(3) WRITE

This active low signal

is

used

to

load parameters

such

as

data,

DMA

address, BYTE counter anti mode.

(4)

CS

(CHIP SELECT)

This

is

low

signal which

makes

READ/WRITE

of

HDC

parameters

and

STATUS READ effective

and

directs

ADRO-

ADR2

from

CPU

to

HDC.

(5) DIR

(DIRECTION)

lt

indicates data-bus directions.

"H"

: HDC (DISK

or

BUF)

""*

HOST

" L" : HDC (DISK

or

BUF) +-HOST

When

DMA

channel 0

is

in execution, this signals

is

output

by the

READ/WRITE

modes

as

follows:

READ mode : H

DC

""*

HOST

WRITE

mode : HDC +-HOST

When

DMA

is

not

being executed the direction

is

HDC +-HOST.

(6)

DATA-REO

When

DMA

channel 0

is

excuted, this

output

signal

requests the host

for

data. By this signal, the host

activates

1/0 mode

and

the

DMA

controller

of

CPU

.

When

DMA

signal 0

is

designated

to

the 1/0 mode,

this

signal

makes

a handshake

with

the

Read

and

Write signals.

(7)

ADRO-

ADR2

ADRO -

ADR2

are

bidirectional. Unless

DMA

is

executed, these bits

address

internal registers. In

DMA

execution, these three bits

are

tristate signals

whi

ch

output

three lower bits

of

the 16-bits memory

address

.

(8)

ADR3-ADR15

This signal outputs 13 bits from the 2nd

to

the 7th

bit

of

Memory Address generated

by

HDC in

DMA

execution.

(9) M-

READ

(MEMORY

-READ)

This active low tristate

output

is

used

to

read

data

from

an

addressed

memory in the

DMA

read-cycle.

When a DMA

channel

is

designated the

to

the 1/0

mode, this signal

is

output

handshaking

with

READ

or

WRITE. This signal

is

also

used

as

a program load

timing in

format

programming.

(10)

M-WRITE (MEMORY-WRITE)

This active

low

tristate

output

is

used

to

write

data

into

an

addressed

memory in the

DMA

write

cycle.

When a DMA

channel

is

designated

to

ttie 1/0 mode,

this signal

is

output

by handshaking

with

READ

or

WRITE.

(11)

ADRE

This indicates

that

HDC

is

executing

DMA

and

reading

commands and

that

the

addresses

from HDC

are

effective.

-17-

-

MZ-5600A

(12) HRO

This

is

an

output

signal which requests a control over

a system bus.

(13)

HLDA

This signal answers

to

HRO and indicates

that

HDC

has

a control over a system

bus.

(14) PHASE 0

This indicates a

DMA

transfer mode.

AD

RE

= H PHASE 0 = L

HOST~

DISK

HOST -

MEMORY

(BUF)

AD

RE

= H PHASE 0 = L

t

DMA

MODE R

EG.

MEMORY

(BUF)

-DISK:

DMA

MODE

REG

.

(15) DMEM

This

signal turns "H''

with a DMA

channel termination

and

turns

"L"

by a INTER

reset

command.

(16)

CLK 0, 1 (CLOCK 0, 1)

This

is

a clock

input

signal

to

make

an

internal timing

in

HDC.

CLK 0

=

DMA

CONTROLLER

CLOCK

CLK 1 =DISK

CONTROLLER

CLOCK

(17) RESET

This

is

a synchronized

input

used

to clear

an

internal

register and

control line.

(18)

ATN

This stops

READ/WRITE.

READ/WRITE

operations

continue

until a write

gate turns

off

.

5)-2. SMD Interface

5)-2-1. Unidirectional Signals

(1)

NRZ

-READ-

DATA

This signal

is

the data

of

N RZ.

(2) READ-CLK

Synchronized

with

Read-Data, this signal

is

output

from

a disk drive when reading.

(3)

SE

RVO-CLK

This signal

is

phase

-locked

to

the data recorded on a

servo-track,

and

is

always the

output

from

a disk drive.

(4)

INDEX

A pulse generated once in a revolution which indicates

the start

of

a track.

(5)

SECTOR

This

is

a signal

used

to

get a sector

timing

when reading

data.

(6)

NRZ-WRITE-DATA

Synchronized

with

Write Clock , these

NRZ

data

are

output

to

a disk drive.

(7)

TAG 1 (CYLINDER

SELECT)

This is a strobe signal

to

select a cylinder

address

on

bus

bit

0 - 9. A disk drive

seeks

for

a cylinder

address

on a

bus

strobed

by

TAG

1.

(8)

TAG 2 (HEAD

SELECT)

This signal selects a

head

by designating

bus

bit 0-2.

(9)

TAG

3 (CONTROL SELECT)

When this signal is gated, the

following

operations

are

enabled.

a)

WRITE

GATE

(BIT

0)

This signal enables a Write operation.

b) READ

GATE

(BIT

1)

This signal enables a

Read

operation.

Page 19

-

MZ-5600A

c)

SERVO OFFSET PLUS (BIT

2)

When this signal

is

active,

it

makes an inner offset

of head from a normal on-track position.

d) SERVO OFFSET

MINUS

(BIT

3)

When this signal

is

active, it makes an outer offset

of

head from a normal on-track position.

e)

FAULT CLEAR (BIT

4)

This clears a fault status of a selected drive.

f)

AM

ENABLE (BIT

5)

• Write

When

this signal

is

active

in

an active Write

Gate, a

DC

erase area

is

written by synchroniz-

ing

with this signal.

•

Read

When this

signal

is

active

in

an active

Read

Gate,

an

Address

Mark

Found signal

is

output

after

an

Address

Mark

has

been detected.

g)

RTZ

(BIT 6)

This signal moves a head

to

Cylinder

"0",

Head

"0".

h)

DATA STROBE EARLY (BIT 7)

When this signal

is

active, data of the

PLO

Data

Separator

in

a disk drive are strobed earlier.

i) DATA STROBE

LATE

(BIT

8)

When this signal

is

active, data of the

PLO

Data

Separator

in

a disk drive are the strobed late.

(10) UNIT-SELECT-TAG

This

is

a drive-select gate signal and samples Unit-Sel

20-23.

5)-2-2. Bidirectional Signals

5)

-2-2-

1.

Output Signals

BO -B9

are latched

in

an outer latch area and

used

as

bus bit 0-9 or Unit-Sel 2° - 2

3

)

(1)

UNIT-

SEL2°

-23 (UNIT-SELECT2°

-2

3

)

This

is

a signal used

to

select a drive unit and sampled

by Unit-Select-

Tag.

(2)

BU5-BIT

0-9

This signal

has

different meanings depending on the

selection

of

TAG

1 - 3.

TAG1

TAG2 TAG3

BUS

(CYLINDER (HEAD (CONTROL

SELECT) SELECT) SELECT)

BITO

1

1

WRITE GATE

1 2 2

READ

GATE

2

4

4

SERVO

OFFSET PLUS

3

8 8

SERVO

OFFSET

MINUS

4 16

8

FAULT CLEAR

5 32

AM

ENABLE

6

64

RTZ

7 128

DATA STROBE

EARLY

8

256

DATA

STROBE

LATE

9

512

- 18-

5)

-2-2-2. Input Signals

(1)

UNIT-READY

This indicates that disks reach a rated revolution and

heads are on a recording zone. When a drive

is

in

fault, this signal shall be inhibited.

(2)

FAULT

This indicates

that

a selected drive

is

in

fault.

(3)

SEEK-ERROR

This indicates that a seek error

is

found.

(4)

WRITE-PROTECT

This indicates

that

a write-circuit of a disk drive

is

in

a status of Write Protect.

(5)

UNIT-SELECTED

This indicates that a drive designated by Unit-Select

2° - 23 and Unit-Select-Tag

is

selected.

(6)

ON-CYLINDER

This indicates

that

the heads are positioned on the

tracks.

(7)

AM-FOUND (ADDRESS

MARK

FOUND)

AM

FOUND

is

output when Read Gate and

AM

Enable are active, and a disk drive detects Address

Mark.

6) HDS STATUS

AND

REGISTER

HOC

Statsu and Register are shown below:

c

ADR

READ

WRITE

2 1

0

1

0 0 0

INTR

STATUS

RW/SEEK START

1 0 0

1

READ/WRITE

INTR

RESET

ERROR STATUS

1 0 1 0

DISK

STATUS

DMA

START

1 0

1 1

REGISTER SELECT

1 1 0 0

REGISTER

READ

REGISTER

WRITE

1 1 0 1

PC

-H

PC

-H

1

1 1 1

FPU

RESET

0

X

X X

DMA

TRANSFER

DMA

TRANSFER

The Read/Write Status and Register shall not be executed

during an

HOC

operation. However Read

is

enabled

in

a

Zero Search Command execution. To Read/Write, each

register shall be executed

by

designating a register at

Resigter

Select.

Page 20

-

D7

DO

REGISTER

SELECT

I 0 I 1/0,110,1/0,1/0,1/0,1/0,1/0 I

j. j. j. j. j. + +

0 0 0 1 0 0 0 :

UNIT

0

0 0

1 0 0 1 :

CYL-H

0

0 0

1 0 1 0 :

CYL

-L

0 0 0 0 1

1 :

HEAD

0 0 0

1

0 0

: SECTOR

0 0 0 1 1 0 1 :

MULTI

0

0 0

1 1 1 0 :

FLAG

0 0 0

1 1

1 1 :

MODE

0

0

1 0

0 0 0

'

ECCSRO~

0 0 0 0 0 1

:

ECC

SR1 READ

ONLY

0 0 0 0 0 :

ECC

SR2

0 0 1

0 0 1 :

ECC

SR3

0

1

0 0 0 0 0 :

CHO

ADR

-H

0 1 0 0 0 0 1 :

CHO

ADR

-L

0 1 0 0 0 1

0

:

CHO

BYTE-H

0

1 0

0 0

1 1

:

CHO

BYTE-L

0 1 0 0 1 0 0 :

CH1

ADR-H

0 1 0 0

0

1 :

CH1

ADR

-L

0 1 0 0 1 0 :

CH1

BYTE-H

0 1 0 0 1 1 1 :

CH1

BYTE

-L

(1) INTR STATUS

This indicates the result at the completion

of

Seek

and

Read/Write operations.

BIT

NO.

STATUS

Description

07

READY

HOC

is

ready.

06

COMMAND

INTR

INTR

0 signal.

Interruption

generated by

the

HOC command.

05

END INTR

INTR signal

to

indicate a

completion .

04

SEEK END

This indicates

an

interruption

by a

seek

completion.

03

READ/WRITE

This indicates

an

interruption

END

of

the Read/Write comple-

tion .

02