Page 1

MZ-3500

SERVICE MANUAL

CODE:

OOZMZ

3500SM/E

r C

PERSONAL COMPUTER

MODEL

MZ-350C

CONTENTS

1.

Specifications

1

2.

Software (Memory)

Configuration

7

3. CPU and

memory

12

4. CRT

display

25

5. MFD

Interface

52

6.

R232C Interface

72

7.

Printer Interface

7g

8.

Other Interface

81

9.

Power

Circuit

discription

37

10.

Keyboard Controller Circuit

discription

QQ

11.

Seif

check functions

94

12. IPL

flow

chart

103

13.

Circuit

diagram & P.W.B

Parts

list & Guide

SHARP

CORPORATION

Page 2

M Z 3500

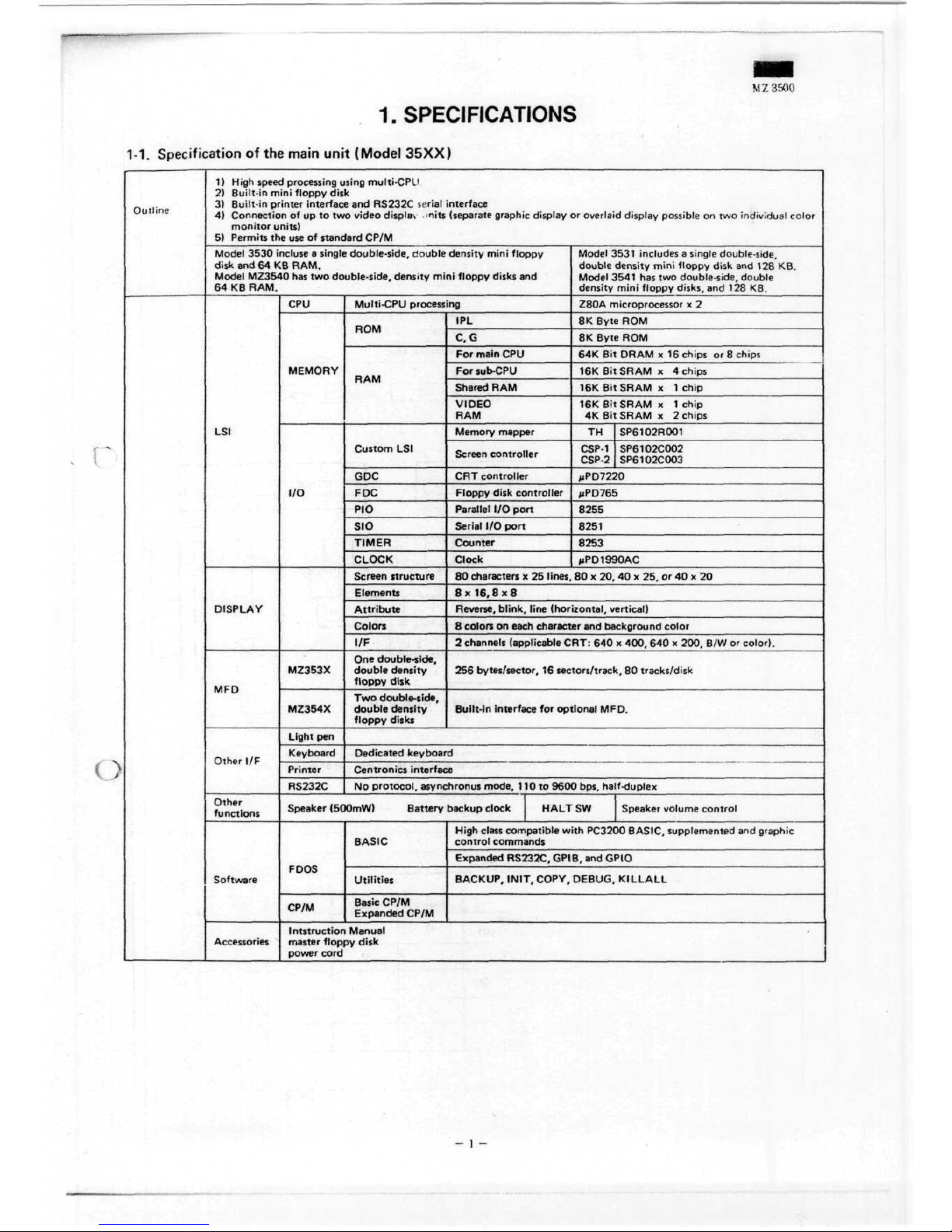

1.SPECIFICATIONS

1-1.

Specification

of the

main

unit

(Model 35XX)

Outline

1)

High

speed

processing

using multi-CPU

2)

Built-in

mini

floppy

disk

3)

Built-in

printer

interface

and

RS232C serial interface

4)

Connection

of up to two

Video displav

>nits

(separate

graphic display

or

overlaid

display

possible

on two

individual color

monitor

units)

5)

Permits

the use of

Standard CP/M

Model 3530

incluse a single double-side, double density

mini

floppy

disk

and 64 KB

RAM.

Model

MZ3540

has two

double-side, density

mini

floppy

disks

and

64 KB

RAM.

LSI

DISPLAY

MFD

Other

I/F

Other

functions

Software

Accessories

CPU

MEMORY

I/O

MZ353X

MZ354X

Light

pen

Keyboard

Printer

RS232C

Multi-CPU processing

ROM

RAM

Custom

LSI

GDC

FDC

RIO

SIO

TIMER

CLOCK

Screen

structure

Elements

Attribute

Colors

I/F

One

double-side.

double

density

floppy

disk

Two

double-side,

double

density

floppy

disks

IPL

C, G

For

main

CPU

For

sub-CPU

Shared

RAM

VIDEO

RAM

Memory mapper

Screen

Controller

CRT

Controller

Floppy

disk Controller

Parallel

I/O

port

Serial

I/O

port

Counter

Clock

Model 3531 includes a single

double-side,

double density

mini

floppy

disk

and 128 KB.

Model 3541

has two

double-side, double

density

mini

floppy

disks,

and 128 KB.

Z80A microprocessor

x 2

8K

Byte

ROM

8K

Byte

ROM

64K Bit

DRAM

x 16

Chips

or 8

Chips

16K Bit

SRAM

x 4

Chips

16K Bit

SRAM

x 1

Chip

16K Bit

SRAM

x 1

chip

4K Bit

SRAM

x 2

Chips

TH

SP6102R001

CSP-1

SP6102C002

CSP-2

SP6102C003

MPD7220

pPD765

8255

8251

8253

/JPD1990AC

80

characters

x 25

lines.

80 x 20, 40 x 25. or 40 x 20

8 x

16,8x8

Reverse,

blink,

line

(horizontal,

Vertical)

8

colors

on

each Character

and

background color

2

channels (applicable CRT:

640 x

400,

640 x

200,

B/W or

color).

256

bytes/sector,

16

sectors/track,

80

tracks/disk

Built-in

interface

for

optional

MFD.

Oedicated keyboard

Centronics interface

No

protocol.

asynchronus

mode,

110 to

9600

bps, half-duplex

Speaker

(500mW) Battery

backup

Clock

HALT

SW

Speaker

volume control

FDOS

CP/M

BASIC

Utilities

Basic

CP/M

Expanded CP/M

High

class

compatible

with

PC3200 BASIC, supplemented

and

graphic

control

commands

Expanded

RS232C,

GPIB,

and

GPIO

BACKUP,

INIT,

COPY, DEBUG.

KILLALL

Intstruction

Manual

master

floppy

disk

power

cord

O

Page 3

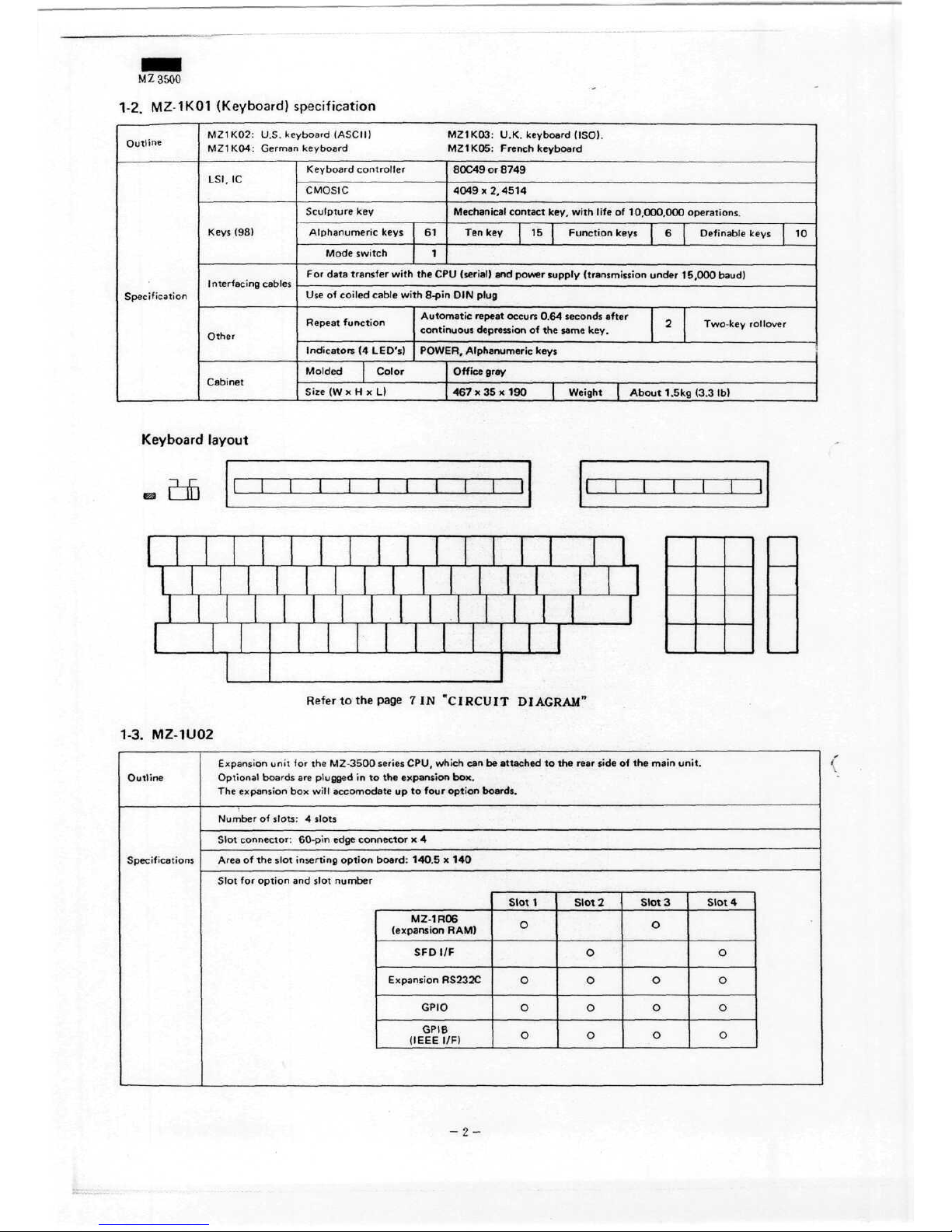

M Z 3500

1-2.

MZ-1K01

(Keyboard)

specification

Outline

Specification

MZ1K02: U.S. keyboard (ASCII)

MZ1K03:

U.K. keyboard (ISO).

MZ1K04: Germankeyboard

MZ1K05:

French keyboard

LSI,

IC

Keys

(98)

Interfacing

cables

Other

Cabinet

Keyboard Controller

CMOSIC

Sculpture

key

Alphanumeric

keys

Mode switch

61

1

80C49

or

8749

4049x2,4514

Mechanical contact key,

with

life

of

10,000,000

operations.

Ten key

15

Function

keys

6

Definable keys

10

For

data transfer

with

the CPU

(serial)

and

power

supply

(transmission

under

15,000

baud)

Use

of

coiled

cable

with

8-pin

DIN

plug

Repeat

function

Indicators

(4

LED's)

Molded

Size

(W x H

Automatic

repeat

occurs

0.64 seconds after

....

, 2

Two-key rollover

contmuous depression

of the

same

key.

POWER,

Alphanumeric

keys

Color

xL)

Office

gray

467 x 35 x 190

Weight | About 1 .5kg

(3.3

Ib)

Keyboard

layout

Refer

to the

page

7 IN

"CIRCUIT

DIAGRAM"

1-3.

MZ-1U02

Outline

Specifications

Expansion

unit

for the

MZ-3500

series

CPU,

which

can be

attached

to the

rear side

of the

main

unit.

Optional

boards

are

plugged

in to the

expansion

box.

The

expansion

box

will

accomodate

up to

four

Option

boards.

Number

of

slots: 4 slots

Slot

connector:

60-pin

edge

connector

x 4

Area

of the

slot inserting

option

board:

140.5

x 140

Slot

for

Option

and

slot

number

MZ-1R06

(expansion RAM)

SFDI/F

Expansion RS232C

GPIO

GPIB

(IEEE

I/F)

Slot

1

O

O

o

o

Slot2

o

o

o

0

Slot

3

O

O

o

o

Slot

4

O

0

o

0

-2-

Page 4

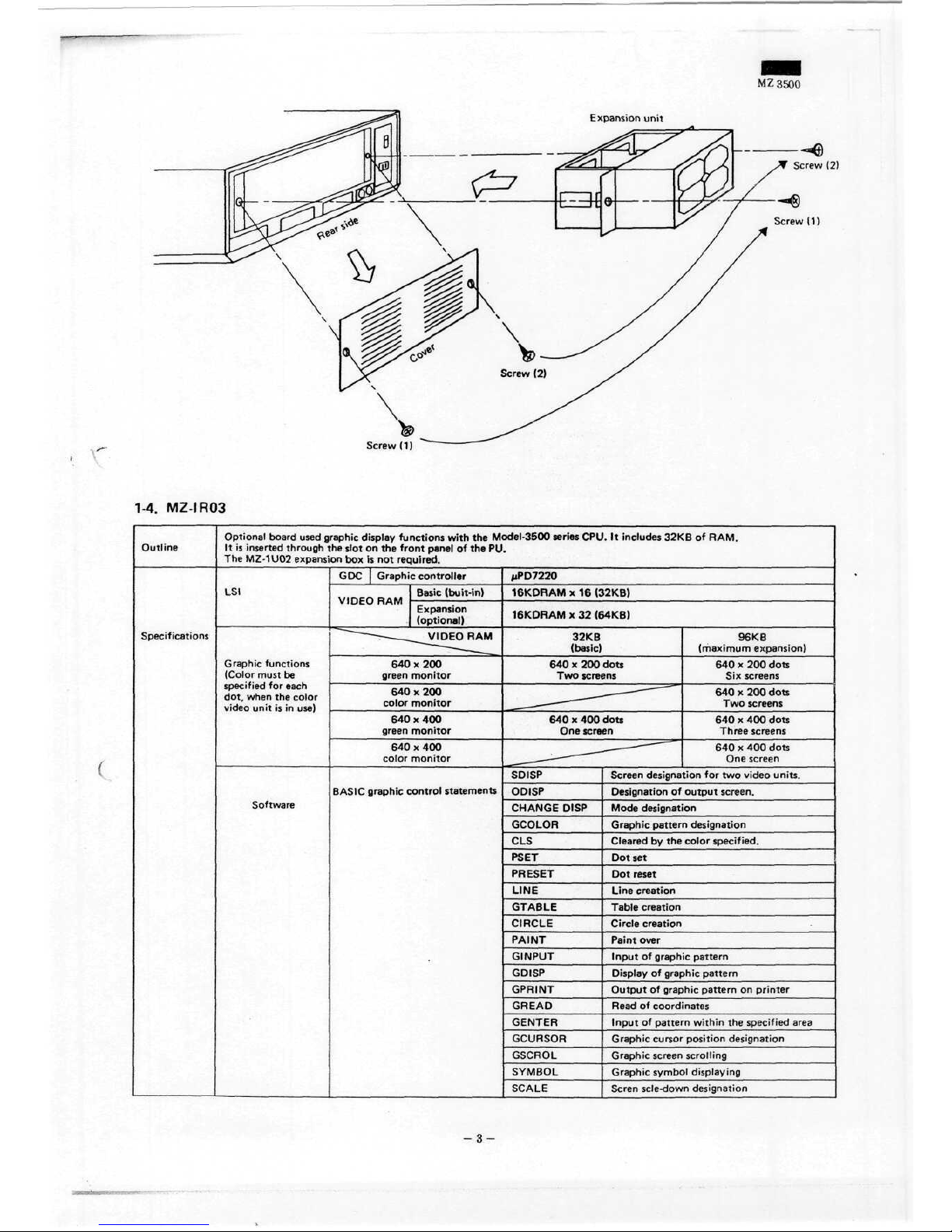

MZ3500

Expansion

unit

Screw

(2)

Screw

(1)

1-4. MZ-IR03

Outline

Specifications

Optional board

used

graphic display

functions

with

the

Model-3500

series

CPU.

It

includes 32KB

of

RAM.

It is

inserted

through

the

slot

on the

front

panel

of the PU.

The

MZ-1U02 expansion

box is not

required.

LSI

Graphic

functions

(Color

must

be

specified

for

each

dot. when

the

color

video

unit

is in

use)

Software

GDC

Graphic

Controller

Basic

(buit-in)

vinrn

RAM

-

Expansion

(optional)

-~-___WDEO

RAM

640 x 200

green

monitor

640 x 200

color

monitor

640

x 400

green

monitor

640 x 400

color

monitor

BASIC

graphic

control

Statements

MPD7220

16KDRAM

x 16

(32KB)

16KDRAM

x 32

(64KB)

32KB

(basic)

640 x 200

dots

Two

screens

______

—

- ~

640 x 400

dots

One

screen

___—

SDISP

ODISP

CHANCE DISP

GCOLOR

CLS

PSET

PRESET

LINE

GTABLE

CIRCLE

PAINT

GINPUT

GDISP

GPRINT

GREAD

GENTER

GCURSOR

GSCROL

SYMBOL

SCALE

96KB

(maximum expansion)

640 x 200

dots

Six

screens

640 x 200

dots

Two

screens

640 x 400

dots

Three

screens

640 x 400

dots

One

screen

Screen

designation

for two

video units.

Oesignation

of

Output

screen.

Mode designation

Graphic

pattern

designation

Cleared

by the

color specified.

Dot set

Oot

reset

Line

creation

Table creation

Circle creation

Paint over

Input

of

graphic pattern

Display

of

graphic pattern

Output

of

graphic pattern

on

printer

Read

of

coordinates

Input

of

pattern

within

the

specified

area

Graphic

Cursor

Position designation

Graphic

screen

scrolling

Graphic

symbol displaying

Seren

scle-down

designation

(

-3-

Page 5

M Z 3500

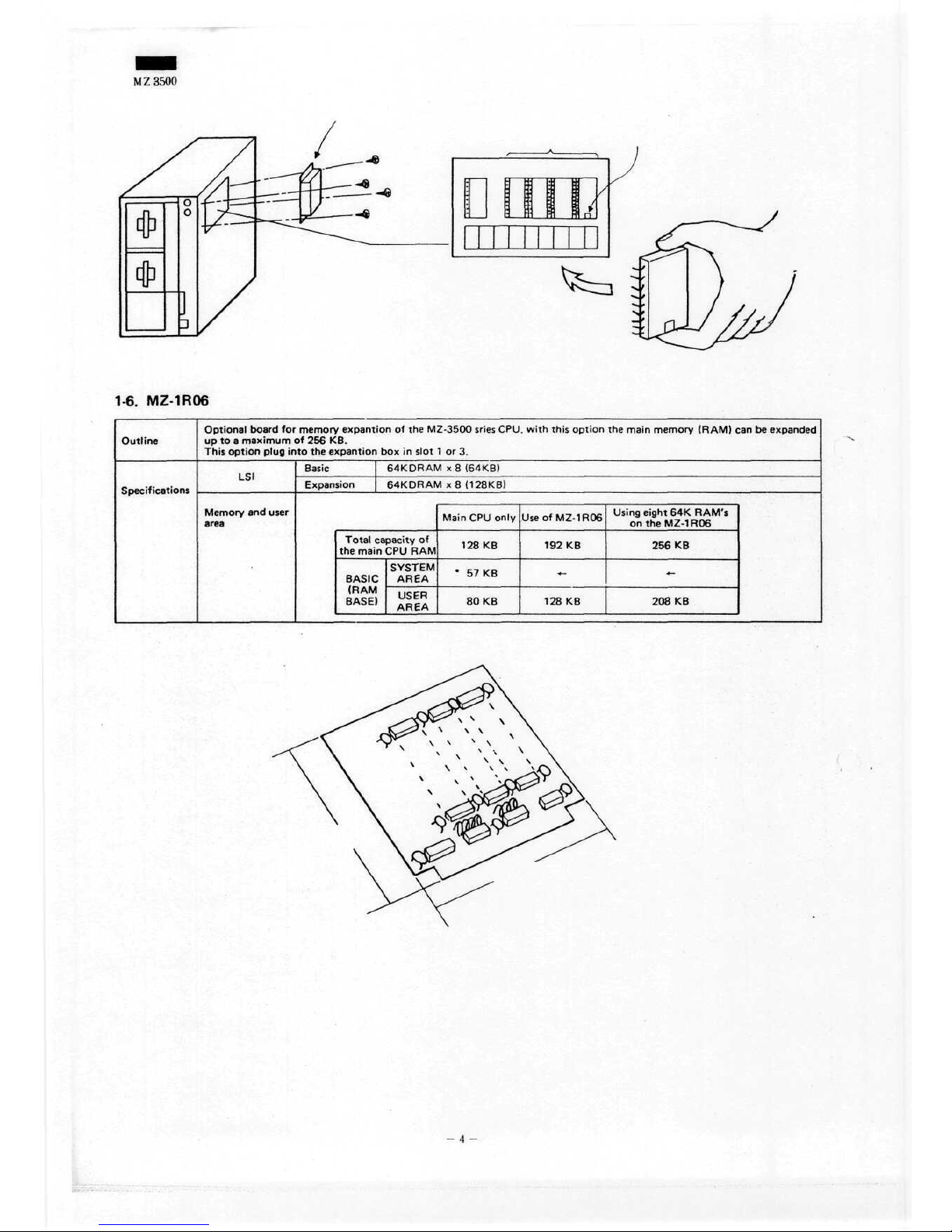

1-6.

MZ-1R06

Outline

Specifications

Optional board

for

memory expantion

of the

MZ-3500

sries

CPU. with this

Option

the

main memory (RAM)

can be

expanded

up to a

maximum

of 256 KB.

This

Option plug

into

the

expantion

box in

slot

1 or 3.

LSI

Memory

and

user

area

Basic

Expansion

64KDRAM

x 8

(64KB)

64KDRAM

x8

(128KB)

Total

capacity

of

the

main

CPU RAM

BASIC

(RAM

BASE)

SYSTEM

AREA

USER

AREA

Main

CPU

only

128 KB

• 57 KB

80 KB

Useof

MZ-1R06

192KB

-

128 KB

Using

eight

64K

RAM's

on

theMZ-1R06

256KB

-

208 KB

- 4 -

Page 6

MZ3500

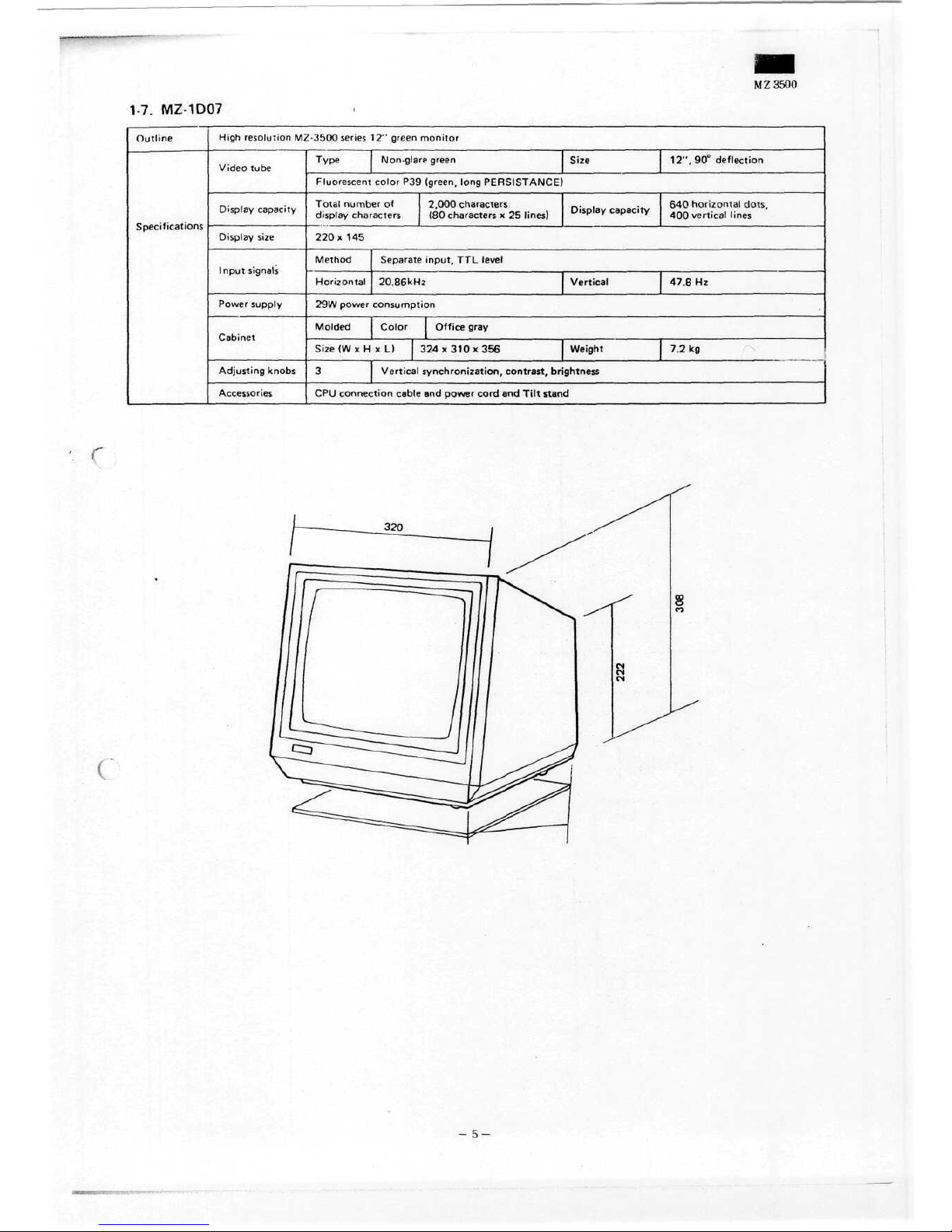

1-7.

MZ-1D07

Outline

Specifications

High

resolution

MZ-3500

series

12"

green

monitor

Video tube

Display capacity

Display

size

Input

Signals

Power supply

Cabinet

Adjusting

knobs

Accessories

Type

Non-glare green

Size

12".

90°

deflection

Fluorescent

color

P39

(green,

long

PERSISTANCE)

Total

number

of

display characters

2,000

characters

(80

characters

x 25

lines)

Display

capacity

640

horizontal

dots,

400

Vertical lines

220 x 145

Method

Horizontal

Separate

input,

TTL

level

20.86kHz

Vertical

47.8

Hz

29W

power

consumption

Molded

Color

Size

(W x H x L)

3

Office gray

324x310x356

Weight

7.2kg

Vertical

synchronization,

contrast,

brightness

CPU

connection

cable

and

power

cord

and Tut

stand

c

Page 7

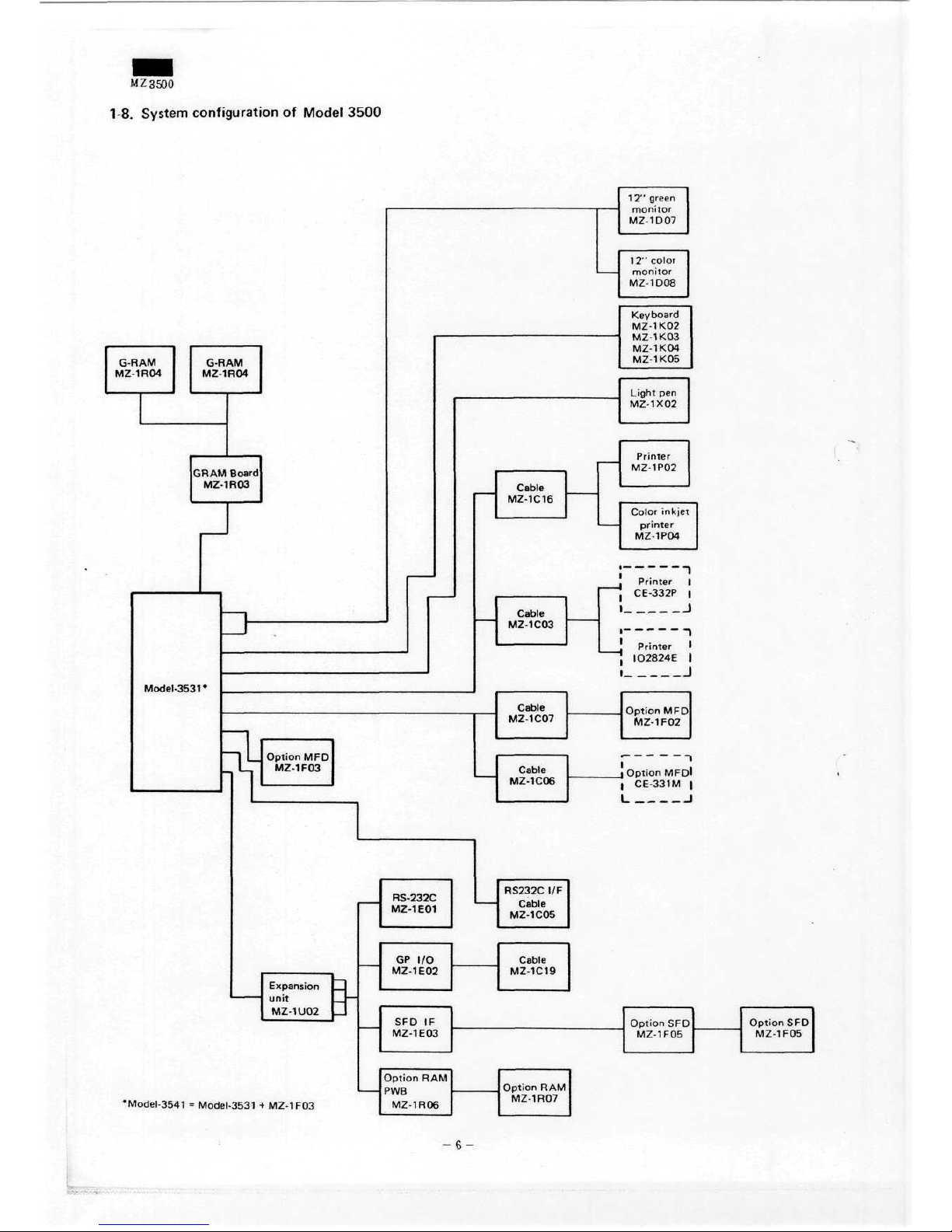

MZ3500

1-8.

System

configuration

of

Model 3500

Keyboard

M2-1K02

MZ-1K03

MZ-1K04

MZ-1K05

1

1

Printer

'

I02824E

l

|

l

Option MFDl

l

CE-331M

|

l l

*Model-3541 = Model-3531 + MZ-1F03

-6-

Page 8

M Z 3500

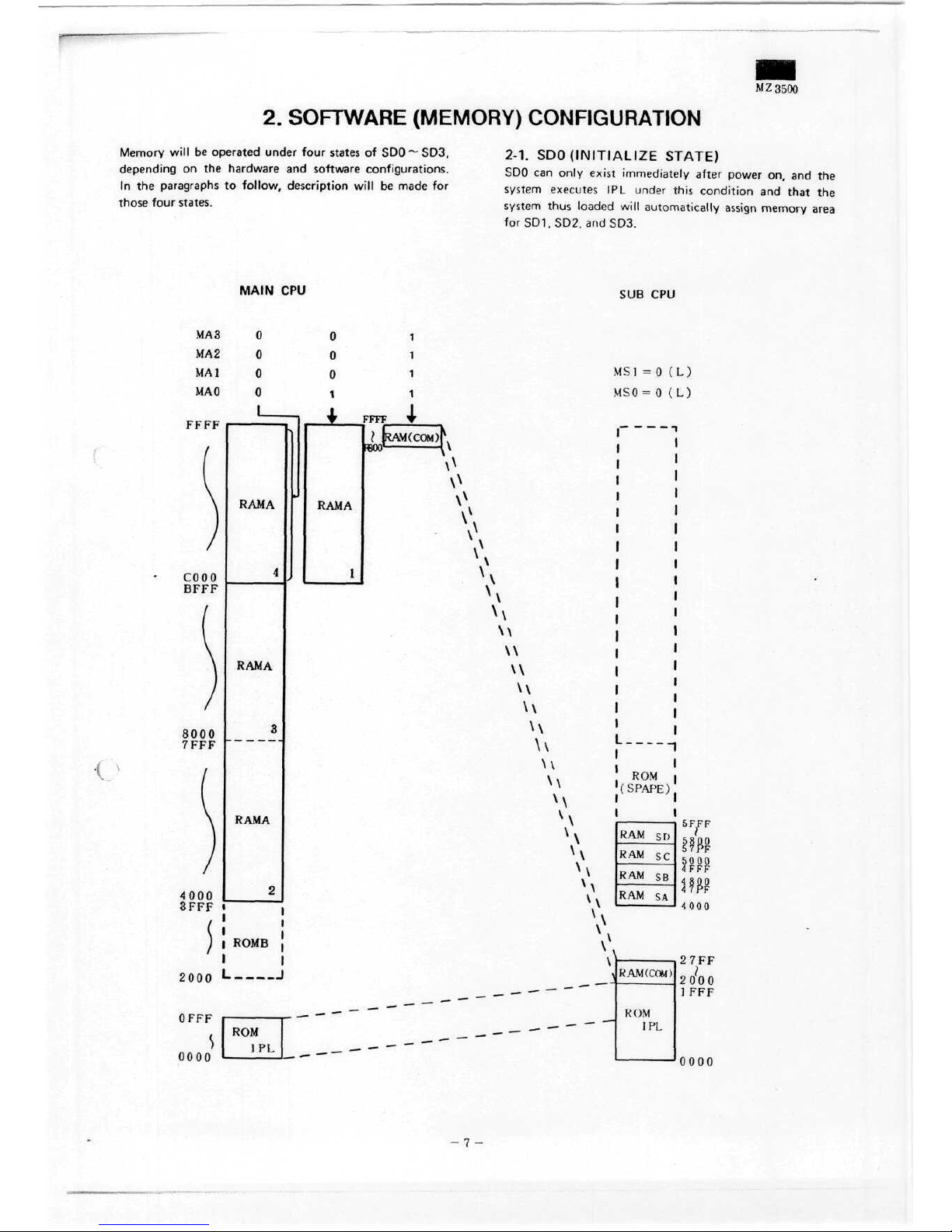

2.

SOFTWARE (MEMORY) CONFIGURATION

Memory

will

be

operated under

four

states

of

SDO ~ SD3,

depending

on the

hardware

and

Software

configurations.

In the

paragraphs

to

follow,

description

will

be

made

for

those

four

states.

2-1.

SDOUNITIALIZE STATE)

SDO

can

only

exist

immediately after power

on, and the

System

executes

IPL

under this

condition

and

that

the

system

thus loaded

will

automatically

assign

memory

area

for

SD1,

SD2,

and

SD3.

MAIN

CPU

SUB

CPU

MAS

MA2

MAI

MAO

17

p

171?

r

r r r

{

,

/

cooo

BFFF

]

/

8000

7

FFF

J

/

4000

3FFF

1

0

0

0

0

1

RAMA

4

RAMA

3

RAMA

2

1

1

ROMB

]

1

0

1

0 1

0 1

1 1

— 1 T

FFFF

T

] l

|RAM(COM)f

:nAn

1 i

tiOO

^\

\

RAMA

J 1

MSI

=0 (L)

MSO

= 0 (L)

2000

OFFF

0000

l

J

v

A

\\

\\

\\

U

\\

\\

\\

\\

\\

\\

ROM

(SPÄHE)

ROM

IPL

ROM

IPL

4000

2 7 FF

l

FFF

0000

Page 9

M Z 3500

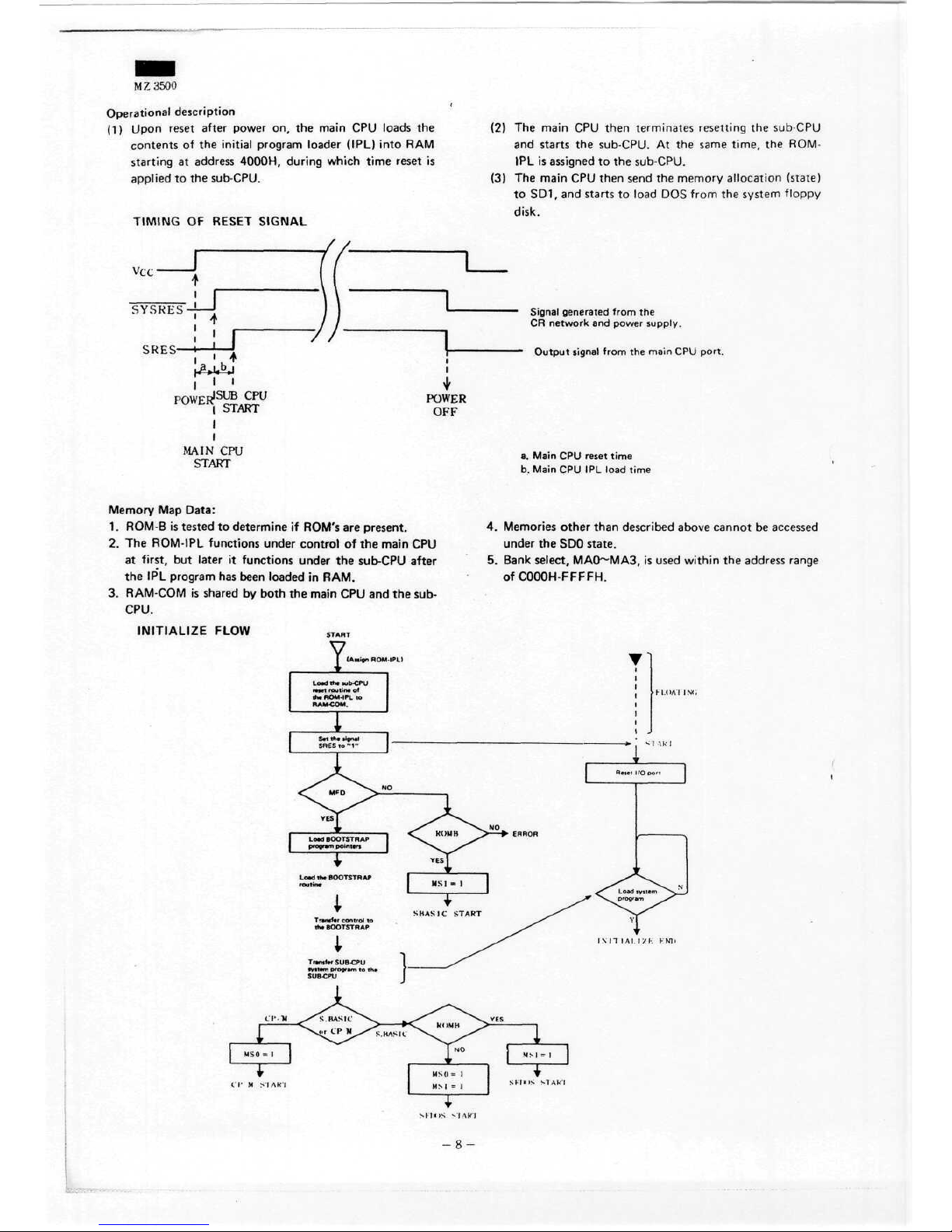

Operational

description

(1)

Upon

reset

after

power

on, the

main

CPU

loads

the

contents

of the

initial

program loader (IPL)

into

RAM

starting

at

address

4000H,

during

which

time

reset

is

applied

to the

sub-CPU.

TIMING

OF

RESET

SIGNAL

Vcc-

SYSRES-

SRES-

•*

I

l

pnwFR

ISUB

CPU

P°*E

*<

START

l

l

POWER

OFF

(2) The

main

CPU

then

terminates

resetting

the

sub-CPU

and

Starts

the

sub-CPU.

At the

same

time,

the

ROM-

IPL is

assigned

to the

sub-CPU.

(3) The

main

CPU

then send

the

memory allocation

(state)

to

SD1.

and

Starts

to

load

DOS

from

the

System

floppy

disk.

Signal

generated

from

the

CR

network

and

power

supply.

Output

Signal

from

the

main

CPU

port.

MAIN

CPU

START

a.

Main

CPU

reset

time

b.

Main

CPU IPL

load

time

Memory

Map

Data:

1.

ROM-B

is

tested

to

determine

if

ROM's

are

present.

2. The

ROM-IPL

functions

under

control

of the

main

CPU

at

first,

but

later

it

functions

under

the

sub-CPU

after

the IPL

program

has

been

loaded

in

RAM.

3.

RAM-COM

is

shared

by

both

the

main

CPU and the

sub-

CPU.

INITIALIZE

FLOW

4.

Memories

other

than

described above

cannot

be

accessed

under

the SDO

state.

5.

Bank select,

MAO~MA3,

is

used

within

the

address

ränge

ofCOOOH-FFFFH.

-

Page 10

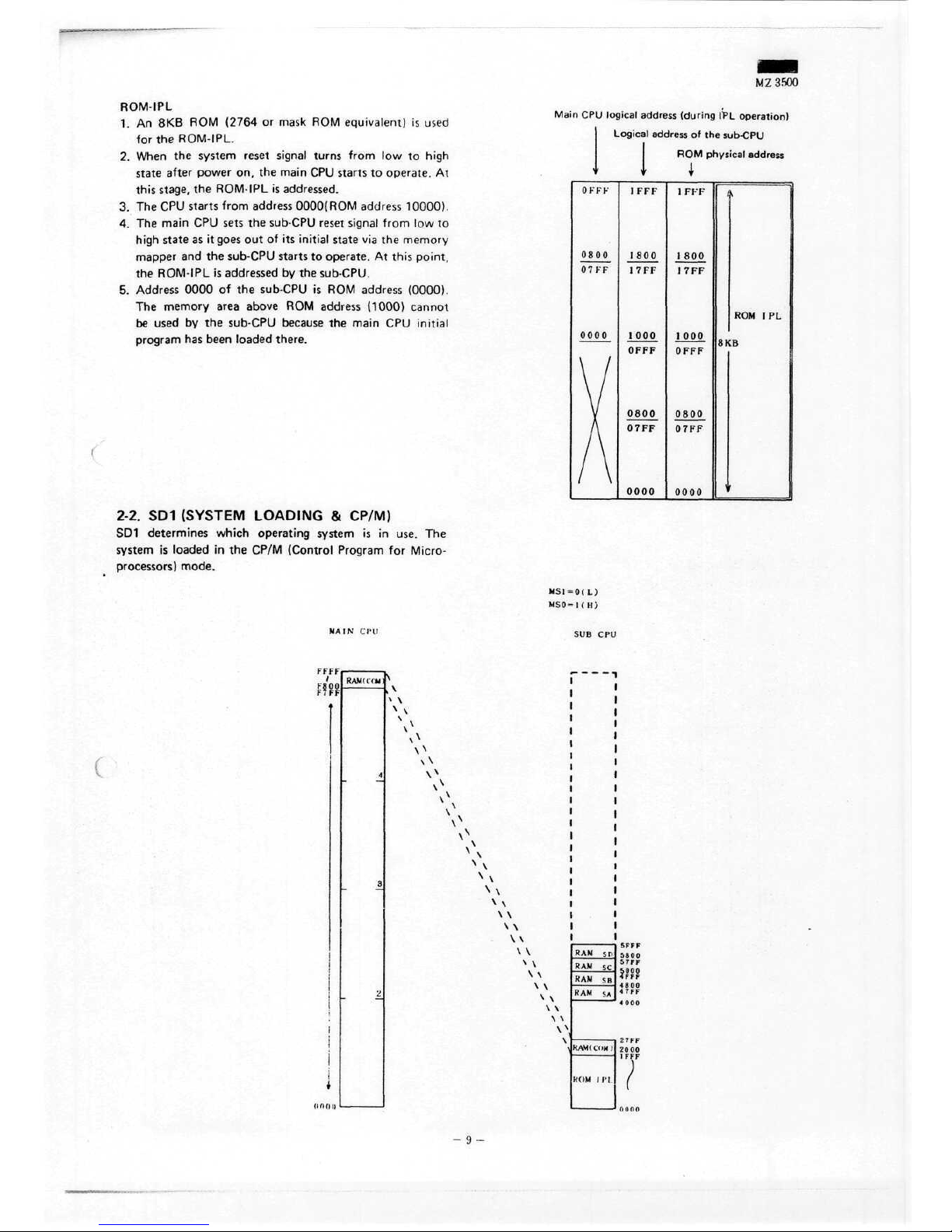

ROM IPL

1. An 8KB ROM

(2764

or

mask

ROM

equivalent)

is

used

for the

ROM-IPL.

2.

When

the

system

reset

signal turns

from

Iow to

high

state

after

power

on, the

main

CPU

Starts

to

operate.

At

this stage,

the

ROM-IPL

is

addressed.

3. The CPU

Starts

from

address

0000(ROM

address

10000).

4. The

main

CPU

sets

the

sub-CPU

reset

signal

from

Iow to

high

state

äs

itgoes

out of its

initial

state

via the

memory

mapper

and the

sub-CPU

Starts

to

operate.

At

this

point,

the

ROM-IPL

is

addressed

by the

sub-CPU.

5.

Address

0000

of the

sub-CPU

is ROM

address

(0000).

The

memory

area above

ROM

address

(1000)

cannot

be

used

by the

sub-CPU because

the

main

CPU

initial

program

has

been loaded

there.

'

2-2.

SD1

(SYSTEM

LOADING & CP/M)

SD1

determines

which

operating

system

is in

use.

The

system

is

loaded

in the

CP/M

(Control

Program

for

Micro-

processors)

mode.

MZ3500

Main

CPU

logical

address

(during

IPL

Operation)

Logical

address

of the

sub-CPU

I

ROM

physical

address

i

OFFF

0800

07

FF

0000

X

V

1

FFF

1

800

17

FF

1

000

OFFF

0800

07FF

0000

1

FFF

1

800

17FF

1

000

OFFF

0800

07FF

0000

8F

\

'

ROM IPL

.B

MS1=0(L)

WSO=1(H)

SUB

CPU

r r r r

/

F7

(

FF

; 'i f i ( i

RAM

(KM

4

3

k

\

»

\

x

\

V

- 9 -

Page 11

M Z

3500

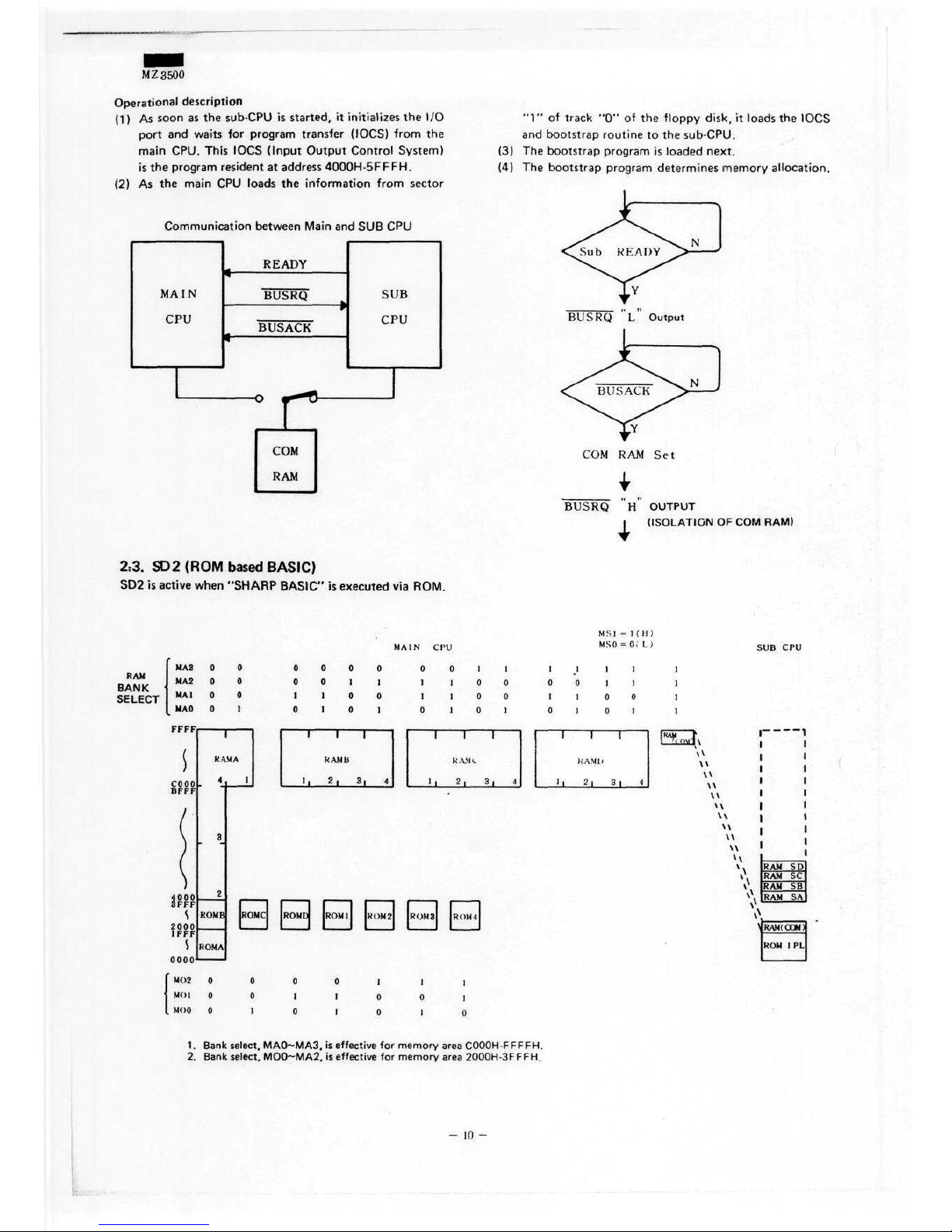

Operational

description

(1)

As

soon

äs the

sub-CPU

is

started,

it

initializes

the I/O

port

and

waits

for

program transfer (IOCS)

from

the

main

CPU.

This

IOCS

(Input

Output

Control

System)

is

the

program resident

at

address

4000H-5FFFH.

(2)

As the

main

CPU

loads

the

Information

from

sector

Communication between Main

and SU B CPU

"1" of

track

"0" of the

floppy

disk,

it

loads

the

IOCS

and

bootstrap routine

to the

sub-CPU.

(3) The

bootstrap program

is

loaded next.

(4)

The

bootstrap program determines memory allocation.

BUSRQ H OUTPUT

l

(ISOLATION

OF COM

RAM)

2.3.

SD 2

(ROM

based

BASIC)

SD2

is

active

when

"SHARP

BASIC"

is

executed

via

ROM.

MAIN

CI'U

MS]

= l (H)

MSO

= 0; L;

SUB CPU

MA3

RAM

BANK

MAI

SELECT

MAI

MAO

FFFF

cooo

4000

im

0000

{MO2

00

0000

00

0011

00

1100

01

0101

1

III

RAMA

RAMB

4

3

2

ROM

B

ROMA

0

1

1,2,3,4

ROMC ROMU

ROM]

ROM2

000]

MO]

00110

MOO

01010

0

1

I

0

1

'l

0 1 1

I

0 0

I

0 0

1

0 1

1 1

HAM<_

2, 3, 4

1111

0 0 1 1

1100

0101

1 1 1

KAMI.

l| 2, S| 4

]

1

1

1

püS >

LZLrnm

v V

\\

\\

\\

U

u

\\

u

\\

u

H

1»

»\

v\

°v

RAM

SD

RAM

SC

RAM

SB

RAM

SA

1.

Bank

select.

MAO~MA3.

is

effective

for

memory

area

COOOH-FFFFH.

2.

Bank

select.

MOO~MA2,

is

effective

for

memory

area

2000H-3FFFH.

Page 12

M.Z

3500

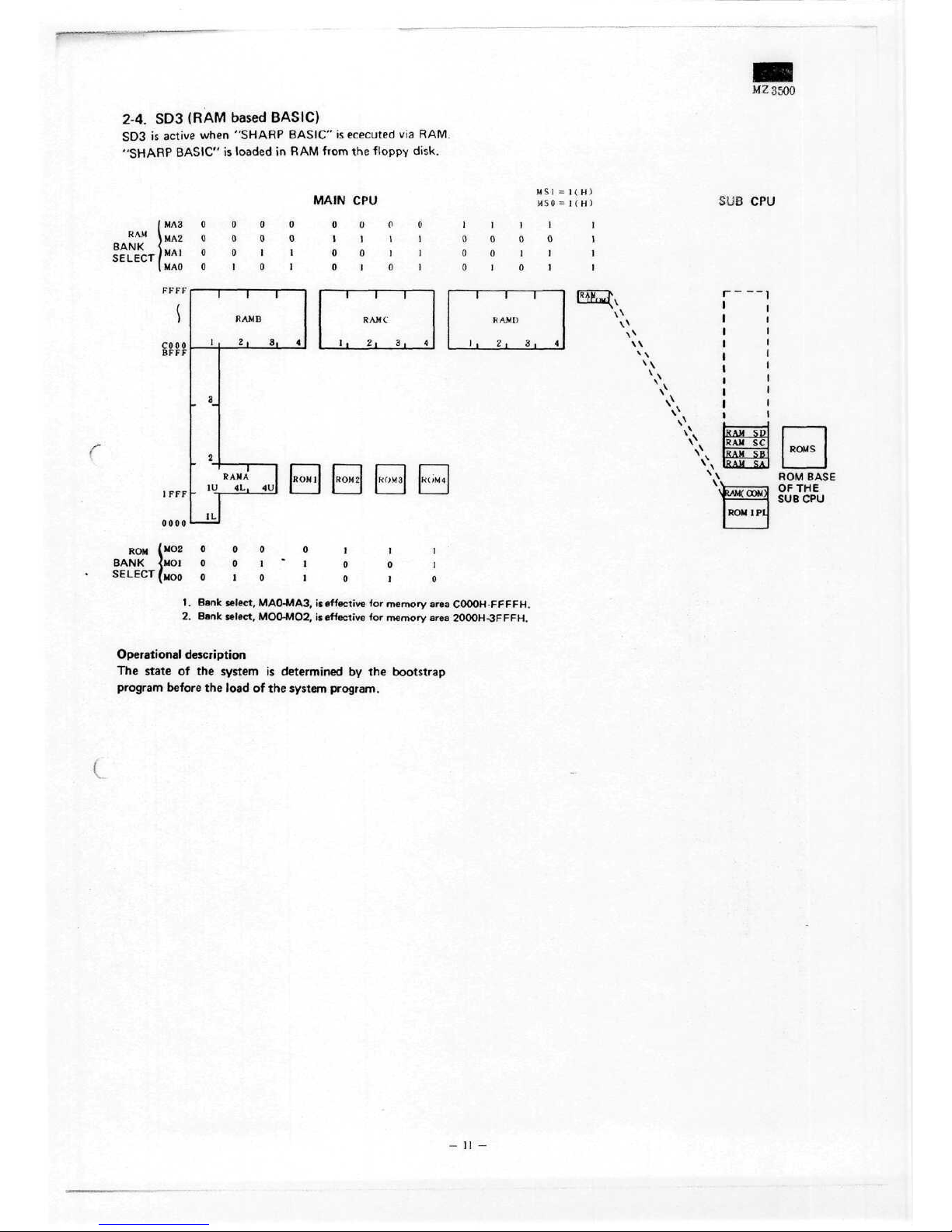

2-4.

SD3

(RAM based BASIC)

SD3 is

active

when

"SHARP BASIC"

is

ececuted

via

RAM.

"SHARP BASIC"

is

loaded

in RAM

from

the

floppy disk.

MAIN

CPU

MSI

=

1<H)

SUB CPU

RAM

BANK

SELECT

MA3

0000 0000

1111

1

MA

10011

0011 0011

1

MAO

0101 0101 0101

1

(

)

SFF?

1FFF

0000

III III III

lüftaJx

" '

RAMB

RAMC

RAM»

x

\

\^

1

2,3,4

1,2,3,4

1,2,3,4

\\

3_

L

2

^\

^\

V

*

0

\\

RAJt|

SP

\\

RAM

SC

V, RAM SB

KOMo

RAMA

ROMl

ROM2 KOW3 ROM4

\\ ROM BAS

1L

"-•

"u S'WfOOM)

Ut

" '"

C

ROM

1 Pl

ROM

(«02

0 0 0 0 l 1 1

BANK <M01

0 0 1 " 1 0 0 1

SELECT (

MOO

010 10 I 0

1.

Bank select, MAO-MA3,

is

effective

for

memory

area COOOH-FFFFH.

2.

Bank select. MOO-MO2,

is

effective

for

memory

area

2000H-3FFFH.

Operational description

The

state

of the

System

is

determined

by the

bootstrap

program

before

the

load

of the

System

program.

Page 13

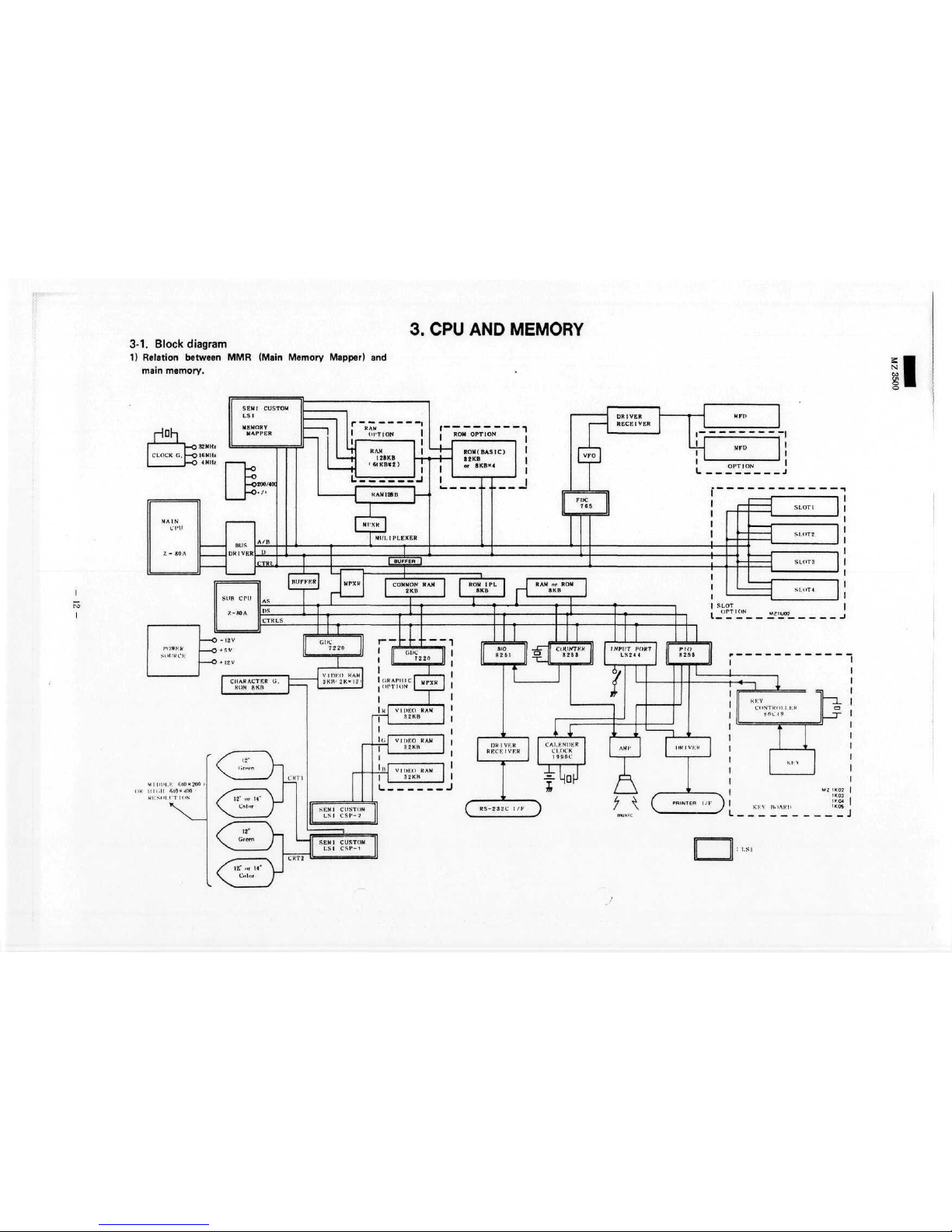

3-1. Block

diagram

1)

Relation between

MMR

(Main Memory Mapper)

and

main memory.

3. CPU AND

MEMORY

Höh

PH

CLOCK

('..

—O 32 MI!

—O

ISMHi

—O

4Mll>

MAIN

CI'U

7.

- 80 A

SEMI

CUSTOM

LSI

MEMORY

MAPPER

-0

-o

-O

200/4«

-O./.

=

Sl

BUS

DK1VKR

=====

B CPU

/-80A

A/B

U

CTRL]

||AS

m

P^—

—

l

1

,

r-„-

r

FKER

II 1 1

T"

RAM |

<64KB»2)

'

1

1

1

MI'XH

MDL

IPLEXER

pou

OPTION

U_ m

MPXK

COMMON

RAM

2KB

1

!•

ROM ( BAS

I C ) 1

S2KB

1

or

«KBX4

1

L

i

V

F

=

K

76

=

ROM

IPL 1 RAM or ROM

8KB

[~~|

8KB

1 - 1

r—

RECEIVER

L LL

MFD

i

-o

1 ' 1

.

OPTION

'

f

P

. II

SLOT1

SI.OTZ

SLOT3

SLOT

4

n

^T 1 ON

MZIUO?

yinni.i:

OK

H n.n

V V T

PRINTER

l/K J

l

Page 14

M Z 3500

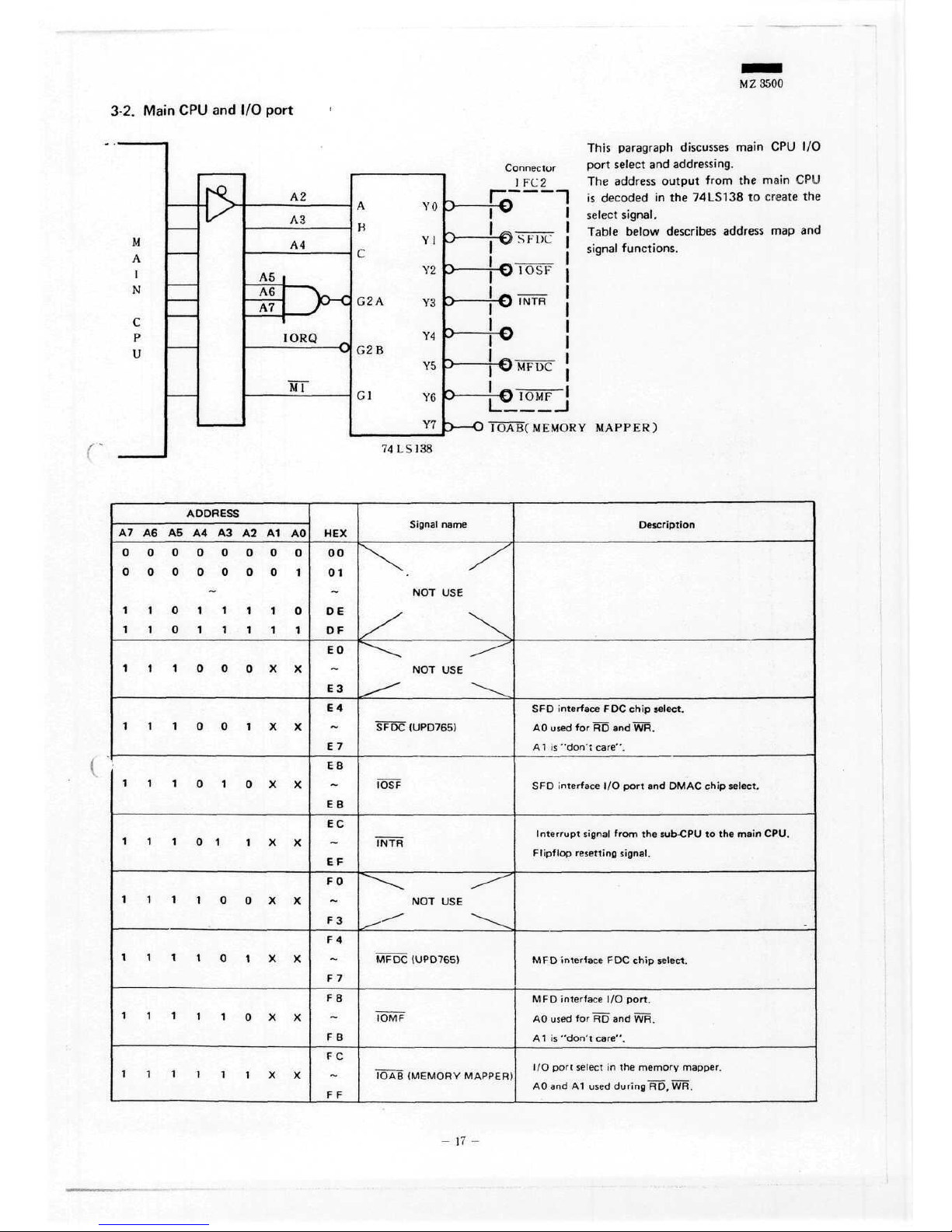

3-2.

Main

CPU and I/O

port

M

A

I

N

C

P

U

[NO

Ix

A2

A3

A4

A5

i

A6

"A

V\

r

A7

P

C

IORQ

MT

A YO

Y 1

Oi A Y3

Y4

G2

B

Y5

Gl Y6

74LS138

This

paragra

Connector

Port

select

an

1

FC2 The

address

_

\~f\

~~\ is

decoded

it

v

select

signal.

T f^i

-,-,.,-

Table

below

^ v#

."> r L)C

signal

functic

J

V

J

0

MFÜC

0 T"O

IOMF

L

|

3

U

IOABCMEMORY

MAPPER)

ADDRESS

A7

A6 A5 A4 A3 A2 A1 AO

00000000

00000001

11011110

11011111

1 1 1 0 0 0 X X

t'\-\OQ1XX

^t'\OtOXX

11101

1 X X

1111QOXX

1 1 1 1 0 1 X X

1 1 1 1 1 0 X X

1 1 1 1 1 1 X X

HEX

00

01

DE

DF

EO

E3

E4

E

7

E8

EB

EC

EF

FO

F3

F4

F7

F8

F

B

FC

F F

NOT USE

NOT USE

SFDC

(UPD765)

IOSF

INTR

NOT USE

MFDC

(UPD765)

IOMF

IOAB

(MEMORY

MAPPER)

SPD

interface

FDC

chip

select.

AO

used

for RD and WR.

A1 is

"don' t care".

SPD

interface

I/O

port

and

DMAC chip select.

!

Interrupt

signal

from

the

sub-CPU

to the

main

CPU.

i

Flipflop

resetting

signal.

MFD

interface

FDC

chip

select.

MFD

interface

I/O

port.

AO

used

for RD and WR.

AI is

"don't

care".

I/O

port

select

in the

memory

mapper

AOand

A1

used

during

RD, WR.

Page 15

MZ3500

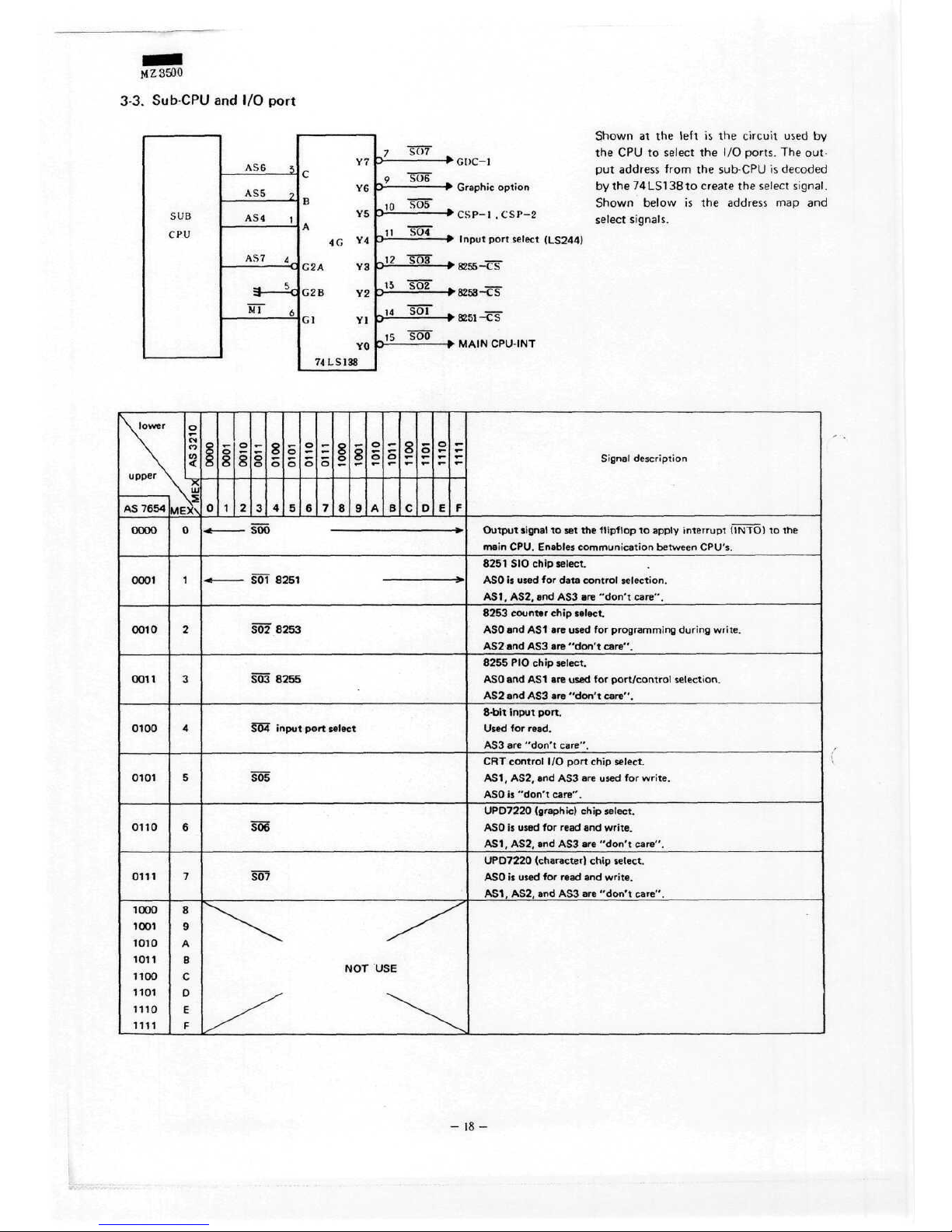

3-3.

Sub CPU and I/O

port

SUB

CPU

AS6 5

ASS

2

AS4

i

AS7

4^

5

*Ü~

6

Y6

4G

Y4

Gl

Yl

YO

74LS138

„7

S07

t

Ä

9 506

^IQ

SO5 ^

J ^

CSP

1 ,

CSP

2

^11 SO4 -

-12

SÖ3" ^ -JTTT

D15 SÖ2"

HEC3

"C"-

14

SÖT —

D

"H^

MAIN

CPU-INT

Shown

at the

left

is the

Circuit

used

by

the CPU to

Select

the I/O

ports.

The

out-

put

address

from

the sub CPU is

decoded

by the

74LS138to

create

the

Select

signal.

Shown

below

is the

address

map and

select

Signals.

AS

7654 MEX\

8

8

1

23456789A8CDEF

8

8

Signal

description

0000

SOO

Output

signal

to set the

flipflop

to

apply

Interrupt (INTO)

to the

main CPU.

Enable:

communication

between CPU's.

0001

S01

8251

8251

SIO

Chip Select.

ASO

is

used

for

data

control

selection.

AS1,

AS2,

and ASS are

"don't care".

0010

S02

8253

8253 counter

chip

Select.

ASO

and AS1 are

used

for

Programming

during write.

AS2

and ASS are

"don't

care".

0011

S03

8255

8255

PIO

Chip

select.

ASO

and AS1 are

used

for

port/control

selection.

AS2

and ASS are

"don't

care".

0100

S04

input

port

Select

8-bit

input

port.

Used

for

read.

AS3

are

"don't

care".

0101

CRT

control

I/O

port

chip select.

AS1, AS2,

and ASS are

used

for

write.

ASO

is

"don't

care".

0110

S06

UPD7220

(graphic)

chip

select.

ASO

is

used

for

read

and

write.

AS1, AS2,

and ASS are

"don't

care"

0111

SÜ7

UPD7220

(Character)

chip

select.

ASO

is

used

for

read

and

write.

AS1, AS2,

and AS3 are

"don't

care"

1000

1001

1010

1011

1100

1101

1110

1111

NOT USE

-

18-

Page 16

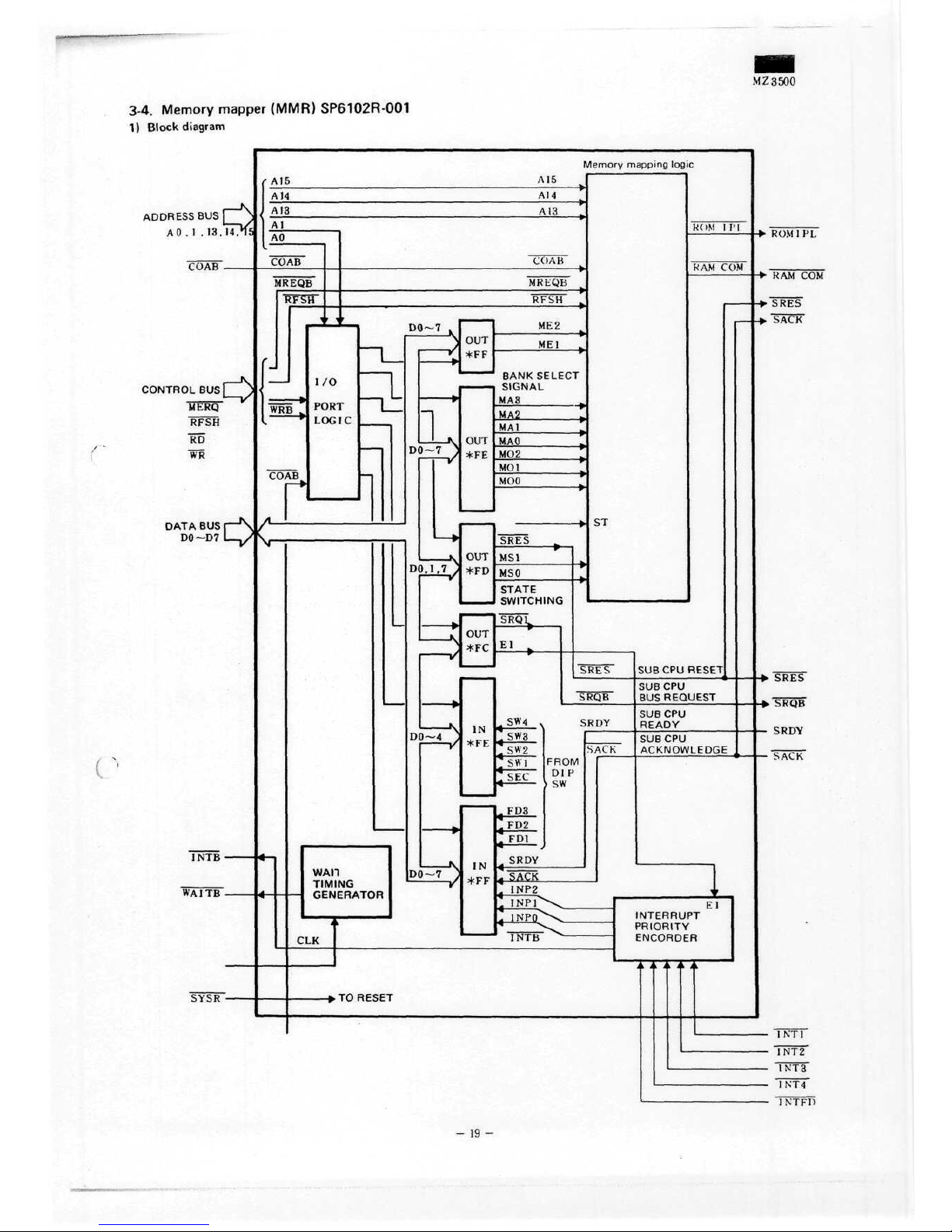

MZ3500

3-4. Memory mapper (MMR) SP6102R-001

1)

Block

diagram

ADDRESS

BUS[

J)

AO

. l

.13.14?1S

CÜAB

CONTROL

BUS

MERQ

RFSH

RD

DATA

BUS

DO-D7

oc

INTB

WAITB

SYSR

A15

A14

AI3

AI

AO

COAB

MREQB

RFSH

Memory

A 15

AI4

RB

GAB

1/0

PORT

LOGIC

~L

""L

1

-

WAIT

TIMING

GENERATOR

CLK

TORESET

INTERRUPT

PRIORITY

ENCORDER

I

NTFI)

19

-

Page 17

M Z 3500

2)

Memory

mapper

(MMR)

SP6102R-001

signal

description

1

2

9

10

12

13

14

15

16

18

19

20

21

22

23

26

27

~

30

31

Polarity

Signal

Name

ST

DO

D7

A15

A13

A1

SRES

SRQ

AR13

AR15

R32

IOAB

SRDY

ROPB

ROAB

RODB

RSAB

~

RSDB

SACK

IN

IN/OUT

IN

IN

OUT

OUT

OUT

OUT

IN

IN

OUT

OUT

OUT

IN

Main

CPU

DRAM Output buffer

(LS244)

switching

strap.

Bidirectional main

CPU

data bus.

(Data

bus 0 ~ 7)

Main

CPU

address

bus.

Used

in the

memory mapping logic

of the MMR for

address

Output

for the

DRAM, ROM,

and

shared

RAM. (Address

bus 13 ~ 15)

Main

CPU

address

bus.

Used

in the I/O

port

Select

logic

of the MMR to

assign

device

number.

Sub-CPU

bus

request

signal.

•

After

power

on:

Halts

the

sub-CPU.

•

After

write

command

(LDA-80H: OUT#FD)

by the

main CPU:

Starts

the

sub-CPU.

This signal

is

issued after transfer

of the

main

CPU

program contained

in the

ROM-IPL.

(Sub

CPU

Reset)

Sub-CPU

bus

request

signal.

•

After power

on:

Resets

bus

request

to

sub-CPU.

•

After write command

(LDA-02H:

OUT#FC)

by the

main CPU:

Place

bus

request

to the

sub-CPU.

This

signal

is

issued

to bus of the

sub-CPU, after

the

main

CPU

writes

to the

shared

RAM a

command

Parameter

to the

sub-CPU

or

reads

the

message

Status

from

the

sub-CPU.

(Sub

CPU

Request)

Address

signal

to the

main

CPU

dynamic RAM.

The

main

CPU

address signals,A13-A

15,

merged

in the

memory mapping logic

Circuit

to

produce

AR13-AR15.

This

is

means

by

which

the 4

basic

and

CP/M memory

maps

are

made.

along

with

MS1

and

MSO.

BASIC

interpreter

32KB mask

ROM

chip

Select

signal.

Valid

when

SD2 is

active (Sharp

ROM

based BASIC). Command (LDA

02H OUT

3FD)

(ROM

32K

Select)

Internal

MMR I/O

port

select

logic

Signal.

Goes

Iow by the

command

IN/OUT

#FC-#FF.

(Input/Output

Address)

Input

of

ready

signal

from

the

sub-CPU.

(Sub

CPU

Ready)

Chip select signal issued

from

the

main

CPU to the 8KB

mask

ROM.

Valid

with

SDO

active

(initialize

state).

(ROM

ipl)

Chip

select signal

for

four

chip

BASIC interpreter

8KB

EPROM

(A. B. C, D).

Valid

with

SD2

active (Sharp

ROM

based

BASIC).

*R32B (alternate choice

with

the

32KB

mask

ROM

chip

select signal).

(ROM

A~D

Buffer)

Row

address

Select

Signal

for the

main

CPU

dynamic

RAM

(block A-block

D).

RAS

(ROW ADDRESS SELECT; LINE

ADDRESS

SELECT)

SIGNAL.

(Row

address

Select)

Input

of bus

acknowledge

signal

from

the

sub-CPU.

command

is

Written

in the

shared

RAM

after

acknowledgement from

the

sub-CPU.

l

At the end of the

command

cycle

bus

request

is

released

and the sub CPU

executes

the

command.

/

-

20-

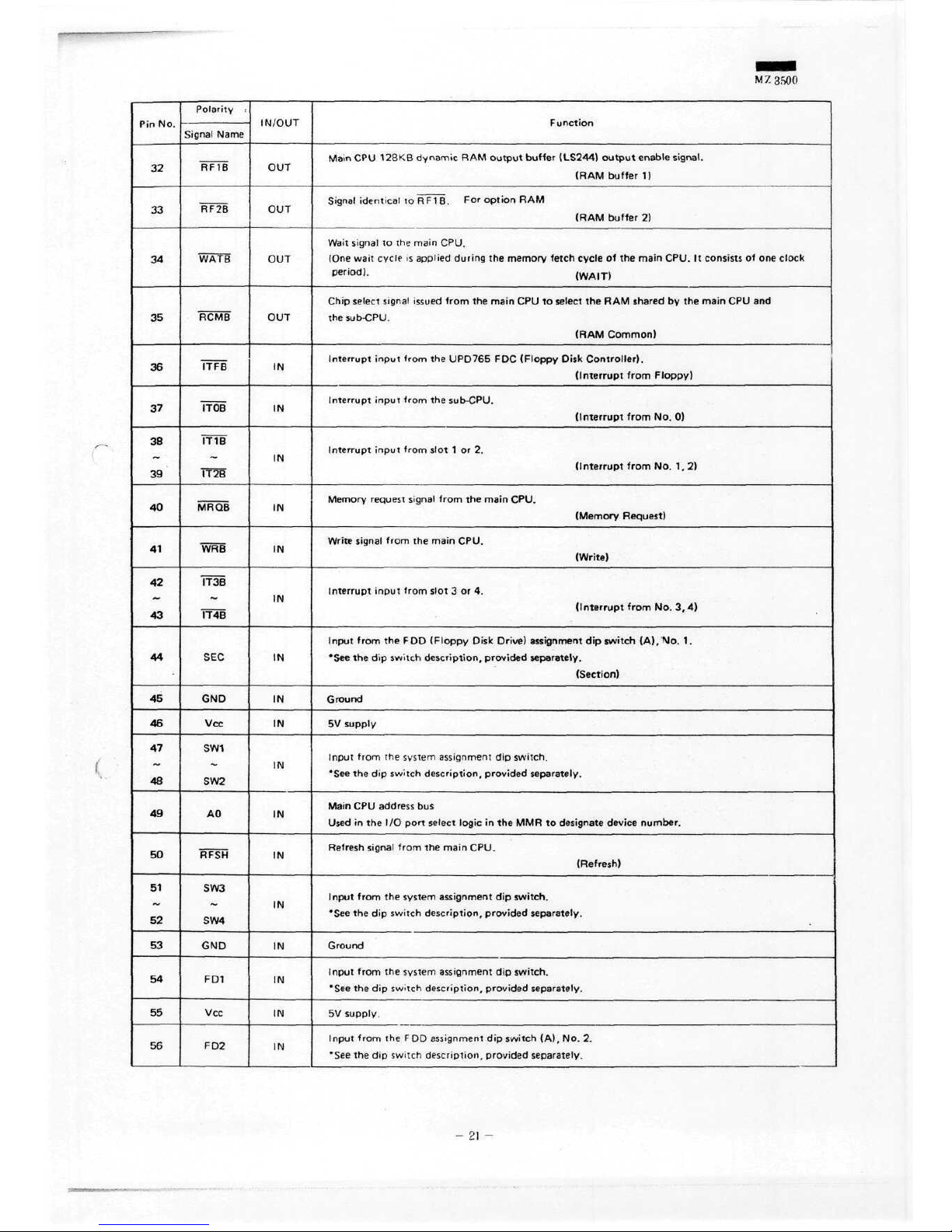

Page 18

M 7,

3500

Pin

No.

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

SO

51

52

53

54

55

56

Polarity

:

Signal

Name

RF1B

RF2B

WATB

RCMB

ITFB

ITOB

IT1B

IT2B

MRQB

WRB

IT3B

TT4B

SEC

GND

Vcc

SW1

SW2

AO

RFSH

SW3

SW4

GND

FD1

Vcc

FD2

IN/OUT

OUT

OUT

OUT

OUT

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

Function

Main

CPU

128KB

dynamic

RAM

Output

buffer

(LS244)

Output

enable

signal.

(RAM

buffer

1)

Signal

identical

to R F 1 B. For

Option

RAM

(RAM buffer

2)

Wait

signal

to the

main CPU.

(One

wait

cycle

is

applied during

the

memory

fetch cycle

of the

main

CPU.

It

consists

of one

clock

period). (WAIT)

Chip

Select

signal

issued

from

the

main

CPU to

Select

the RAM

shared

by the

main

CPU and

the

sub-CPU.

(RAM

Common)

Interrupt

input

from

the

UPD765

FDC

(Floppy

Disk

Controller).

(Interrupt

from

Floppy)

Interrupt

input

from

the

sub-CPU.

(Interrupt

from

No. 0)

Interrupt

input

from slot

1 or 2.

(Interrupt

from

No. 1, 2)

Memory

reguest

signal

from

the

main CPU.

(Memory Request)

Write

signal

from

the

main CPU.

(Write)

Interrupt

input

from slot

3 or 4.

(Interrupt

from

No. 3, 4)

Input

from

the FDD

(Floppy

Disk Drive) assignment

dip

switch

(A).

No. 1.

'See

the dip

switch

description,

provided

separately.

(Section)

Ground

5V

supply

Input

from

the

System

assignment

dip

switch.

•See

the dip

switch description.

provided

separately.

Main

CPU

address

bus

Used

in the I/O

port

Select

logic

in the MMR to

designate device

number.

Refresh

signal

from

the

main CPU.

(Refresh)

Input

from

the

system

assignment

dip

switch.

'See

the dip

switch

description,

provided

separately.

Ground

Input

from

the

System

assignment

dip

switch.

'See

the dip

swuch description,

provided

separately.

5V

supply.

Input

from

the F DO

assignment

dip

switch (A),

N o. 2.

*See

the dip

switch

description, provided

separately.

-

2l

-

-

.-..,,,..,

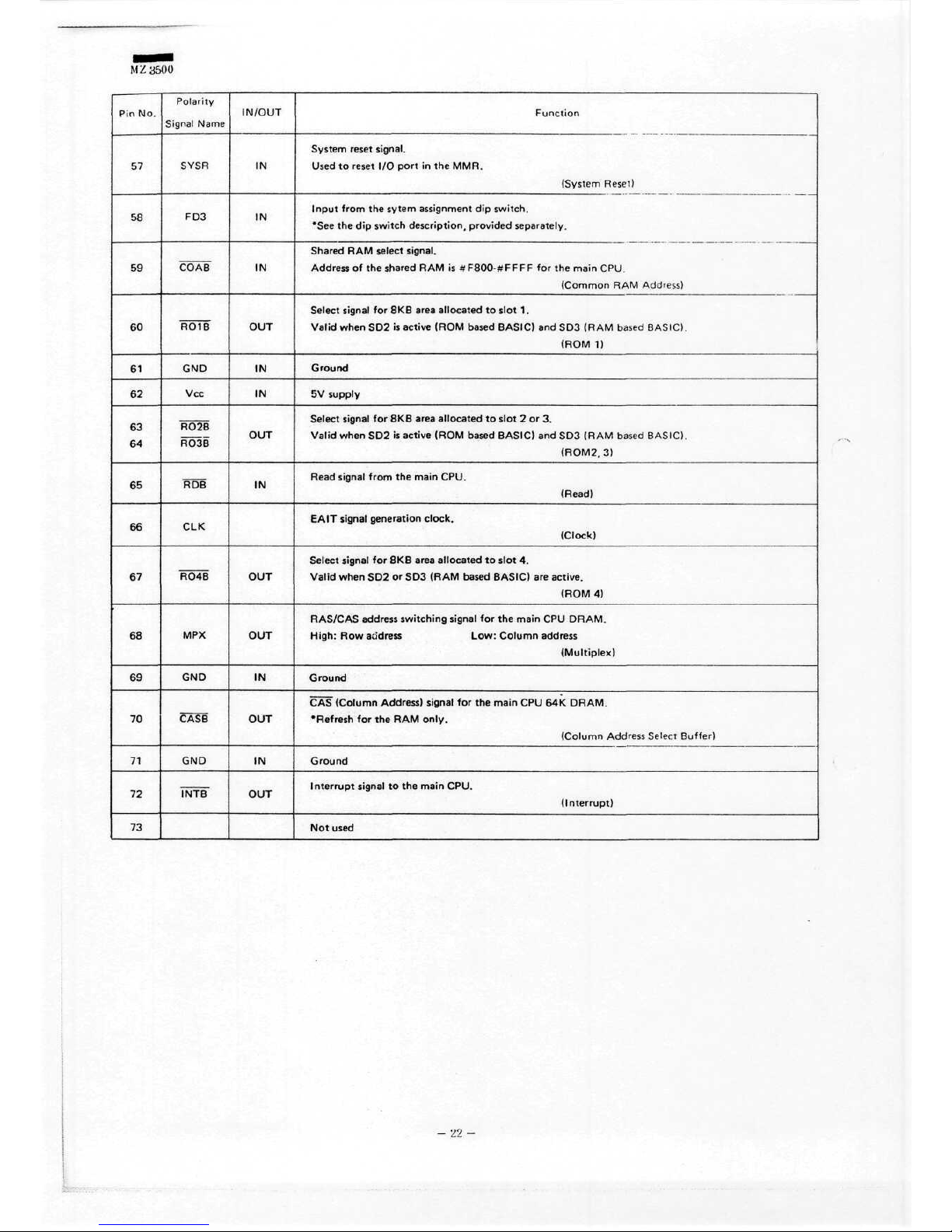

Page 19

M

7,3500

Pin

No.

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

Polarity

Signal

Name

SYSR

FD3

COAB

RO1B

GND

Vcc

RO2B

RÖ3B

'ROB

CLK

RO4B

MPX

GND

CASB

GND

INTB

IN/OUT

IN

IN

IN

OUT

IN

IN

OUT

IN

OUT

OUT

IN

OUT

IN

OUT

Function

System

reset

Signal.

Used

to

reset

I/O

port

in the

MMR.

(System

Reset)

Input

from

the

sytem

assignment

dip

switch.

'See

the dip

switch description, provided

separately.

Shared

RAM

Select

Signal.

Address

of the

shared

RAM is

*F800-#FFFF

for the

main

CPU

(Common

RAM

Address)

Select

Signal

for 8KB

area

allocated

to

slot

1.

Valid

when

SD2 is

active (ROM

based

BASIC)

and SD3

(RAM

based

BASIC).

(ROM

1)

Ground

5V

supply

Select

signal

for 8KB

area

allocated

to

slot

2 or 3

Valid

when

SD2 is

active (ROM

based

BASIC)

and SD3

(RAM

based

BASIC).

(ROM2.

3)

Read

signal from

the

main CPU.

(Read)

EAIT signal generation

Clock.

(Clock)

Select

signal

for 8KB

area

allocated

to

slot

4.

Valid

when

SD2 or SD3

(RAM

based BASIC)

are

active.

(ROM

4)

RAS/CAS

address

switching signal

for the

main

CPU

DRAM.

High:

Row

address

Low:

Column

address

(Multiplex)

Ground

CAS

(Column

Address) signal

for the

main

CPU 64K

DRAM.

•Refresh

for the RAM

only.

(Column

Address

Select

Buffer)

Ground

' l h •

(Interrupt)

Not

used

-22-

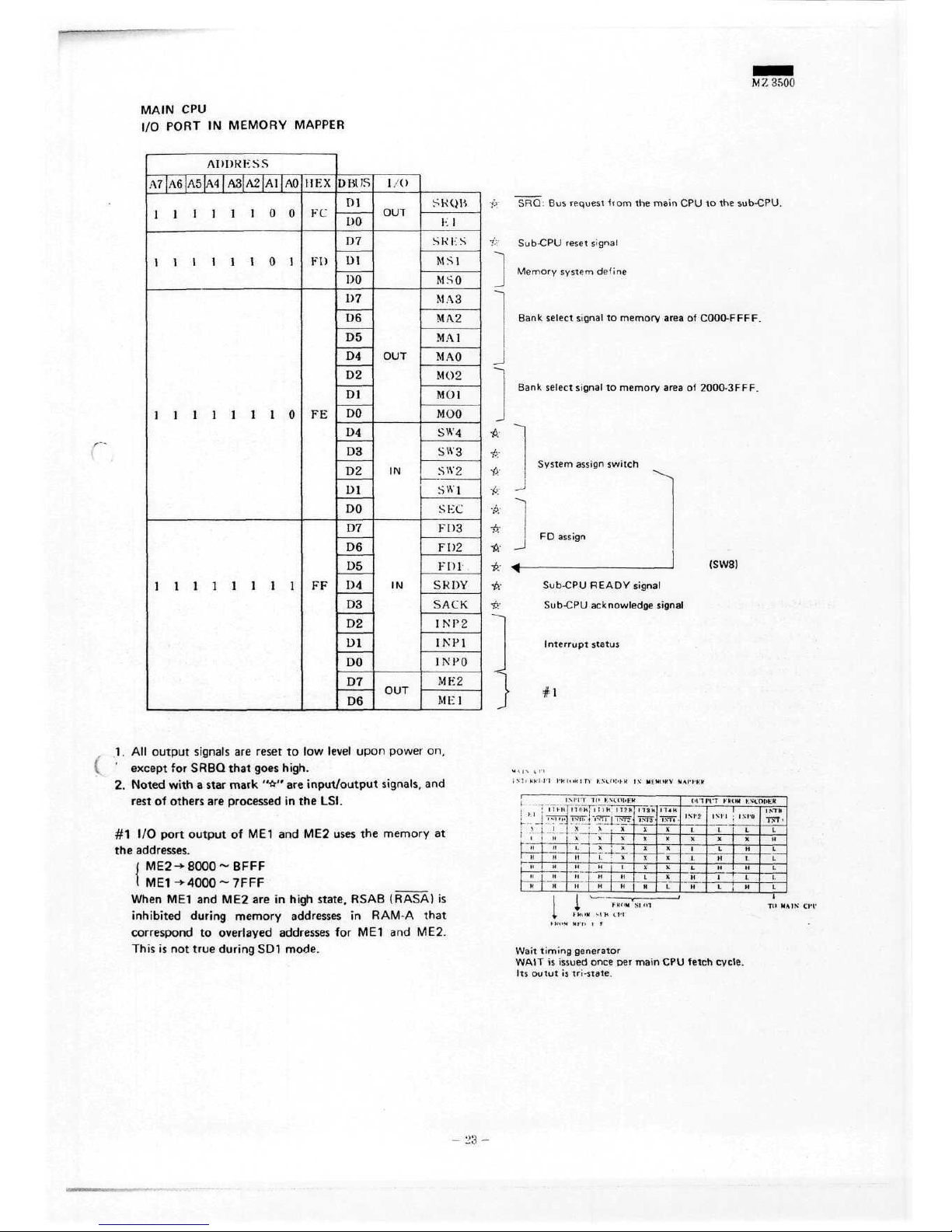

Page 20

M Z 3500

MAIN

CPU

I/O

PORT

IN

MEMORY

MAPPER

ADDRESS

A7|A6|A5|A4|A3|A2|Al|AO

11111101

11111110

11111111

II

EX

U f~

KI)

FE

FF

UHUS

Dl

00

D7

ül

DO

1)7

D6

D5

D4

D2

Dl

DO

D4

D3

D2

Dl

DO

D7

D6

D5

1)4

D3

D2

Dl

DO

D7

D6

I/O

OUT

IN

IN

SKQH

i-;

i

S K K S

MSI

MSO

M

A3

MA2

MAI

MAO

MO2

MOI

MÜO

S\\'4

swg

SW2

swi

SHC

FD

3

FD2

FD1

SKDY

SACK

INP2

INT1

INFO

ME2

M

El

-•->

SRQ:

Bus

request

Irom

the

main

CPU to the

sub-CPU.

7-V

Sub-CPU

reset

signal

Memory

System

define

Bank select signal

to

memory

area

of

COOO-FFFF.

,J

•A

Bank

select

Signal

to

memory

area

of

2000-3FFF.

System

assign

switch

FD

assign

(SW8)

•fr

Sub-CPU READY signal

•fr

Sub-CPU acknowledge

signal

Interrupt

Status

.1.

All

Output

Signals

are

reset

to Iow

level

upon

power

on,

l

except

for

SRBQ

that

goes

high.

2.

Noted

with a star

mark

"6" are

Input/Output

Signals,

and

rest

of

others

are

processed

in the

LSI.

#1 I/O

port

Output

of ME1 and ME2

uses

the

memory

at

the

addresses.

ME2->8000~BFFF

ME1->-4000~7FFF

When

ME1 and ME2 are in

high

state,

RSAB (RASA)

is

inhibited

during

memory

addresses

in

RAM-A

that

correspond

to

overlayed addresses

for ME1 and

ME2.

This

is not

true

during

SD1

mode.

; 1 1 )• ii

.il'lLI

-iq-r-j

H 1 H

II 1 H

H j H

i

MTT Td f.

r

i n

H"T"i

1 1 h

Tvr7T.J

'i'vfr

"l4-

M [ 1.

H J H

" i "

H

t»

i "-

i-

ki

IM

M>

i

«U

»Ft.

1

72h

ITSL

K

X

'

H

"

Y

fHOH

i

r'

1

13h

•Jvn

X

X

X

X

L

H

si

m

inh

/

on

IM'2

1

X

1.

L

H

H

Cl'T

K K

-T"

X

L

K

H

.

L

»M

t-M

IM'O

L

X

H

I

H

L

H

11

IKK

IM h

Tvf>

L

II

L

L

L

l

L

1

TO Vf

Wait

timing

generator

WAIT

is

issued once

per

main

CPU

fetch

cycle.

Its

outut

is

tri-state.

-

L>3

-

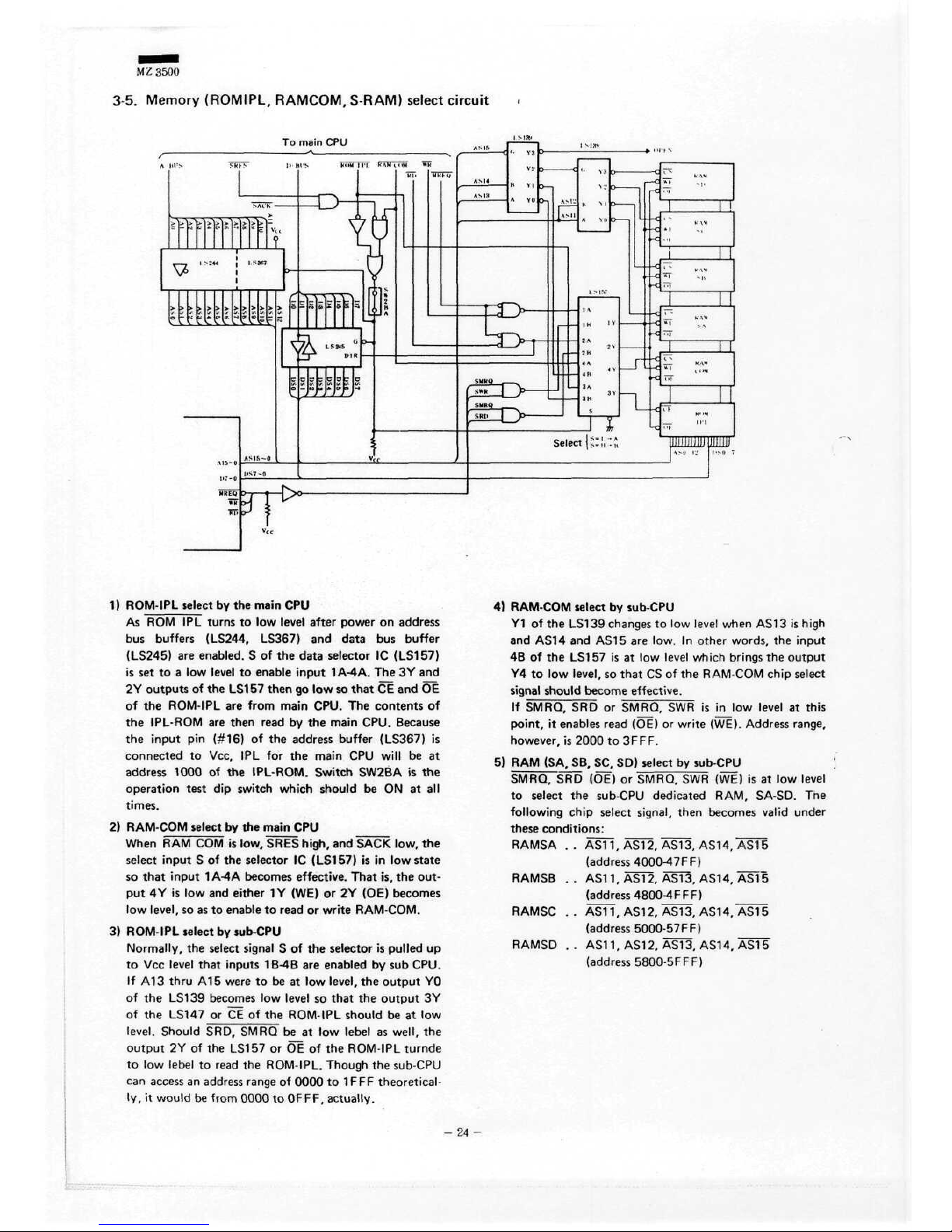

Page 21

MZ3500

3-5.

Memory

(ROMIPL,

RAMCOM,

S-RAM) Select

Circuit

To

main

CPU

1)

ROM-IPL

Select

by the

main

CPU

As

ROM IPL

turns

to Iow

level after power

on

address

bus

buffers (LS244, LS367)

and

data

bus

buffer

(LS245)

are

enabled.

S of the

data selector

IC

(LS157)

is

set to a Iow

level

to

enable

input

1A-4A.

The 3Y and

2Y

Outputs

of the

LS157

then

go Iow so

that

CE and ÖE

of the

ROM-IPL

are

from

main

CPU.

The

Contents

of

the

IPL-ROM

are

then

read

by the

main

CPU. Because

the

input

pin

(#16)

of the

address

buffer

(LS367)

is

connected

to

Vcc,

IPL for the

main

CPU

will

be at

address 1000

of the

IPL-ROM.

Switch

SW2BA

is the

Operation test

dip

switch

which

should

be ON at all

times.

2)

RAM-COM

Select

by the

main

CPU

When

RAM COM is

Iow, SRES

high,

and

SACK Iow,

the

Select

input

S of the

selector

IC

(LSI

57) is in

Iowstate

so

that

input

1A-4A becomes

effective.

That

is, the

out-

put 4Y is Iow and

either

1Y

(WE)

or 2Y

(OE) becomes

Iow

level,

so äs to

enable

to

read

or

write

RAM-COM.

3)

ROM-IPL

Select

by

sub-CPU

Normally,

the

Select

signal

S of the

selector

is

pulled

up

to Vcc

level

that

inputs

1B-4B

are

enabled

by sub

CPU.

If A13

thru

A15

were

to be at Iow

level,

the

Output

YO

of the

LS139 becomes

Iow

level

so

that

the

Output

3Y

of the

LS147

or CE of the

ROM-IPL

should

be at Iow

level.

Should SRD, SMRQ

be at Iow

lebel

äs

well,

the

Output

2Y of the

LS157

or 51 of the

ROM-IPL

turnde

to Iow

lebel

to

read

the

ROM-IPL.

Though

the

sub-CPU

can

access

an

address

ränge

of

0000

to

1FFF theoretical-

ly, it

would

be

from

0000

to

OFFF,

actually.

4)

RAM-COM

Select

by

sub-CPU

Y1 of the

LS139

changes

to Iow

level

when AS13

is

high

and

AS14

and

AS15

are

Iow.

In

other words,

the

input

4B of the

LS157

is at Iow

level

which

brings

the

Output

Y4 to Iow

level,

so

that

CS of the

RAM-COM

chip

select

signal

should

become

effective.

If

SMRQ,

SRD or

SMRQ,

SWR is in Iow

level

at

this

point,

it

enables read (OE)

or

write (WE). Address ränge,

however,

is

2000

to

3FFF.

5) RAM

(SA,

SB. SC, SD)

Select

by

sub-CPU

SMRQ,

SRD

(ÖT)

or

SMRQ,

SWR

(WE)

is at Iow

level

to

select

the

sub-CPU dedicated RAM, SA-SD.

The

following

chip

select

signal, then becomes valid under

these

conditions:

RAMSA

..

AS11, ÄS12, AS13, AS14, AS15

(address

4000-47FF)

RAMSB

..

AS11.ÄST2,

ÄS~T3,

AS14, ÄS15

(address

4800-4FFF)

RAMSC

..

AS11, AS12, AS13, ASM. AS15

(address

5000-57FF)

RAMSD

..

AS11, AS12,

ÄSl3,

AS14,

(address

5800-5FFF)

-

24

-

Page 22

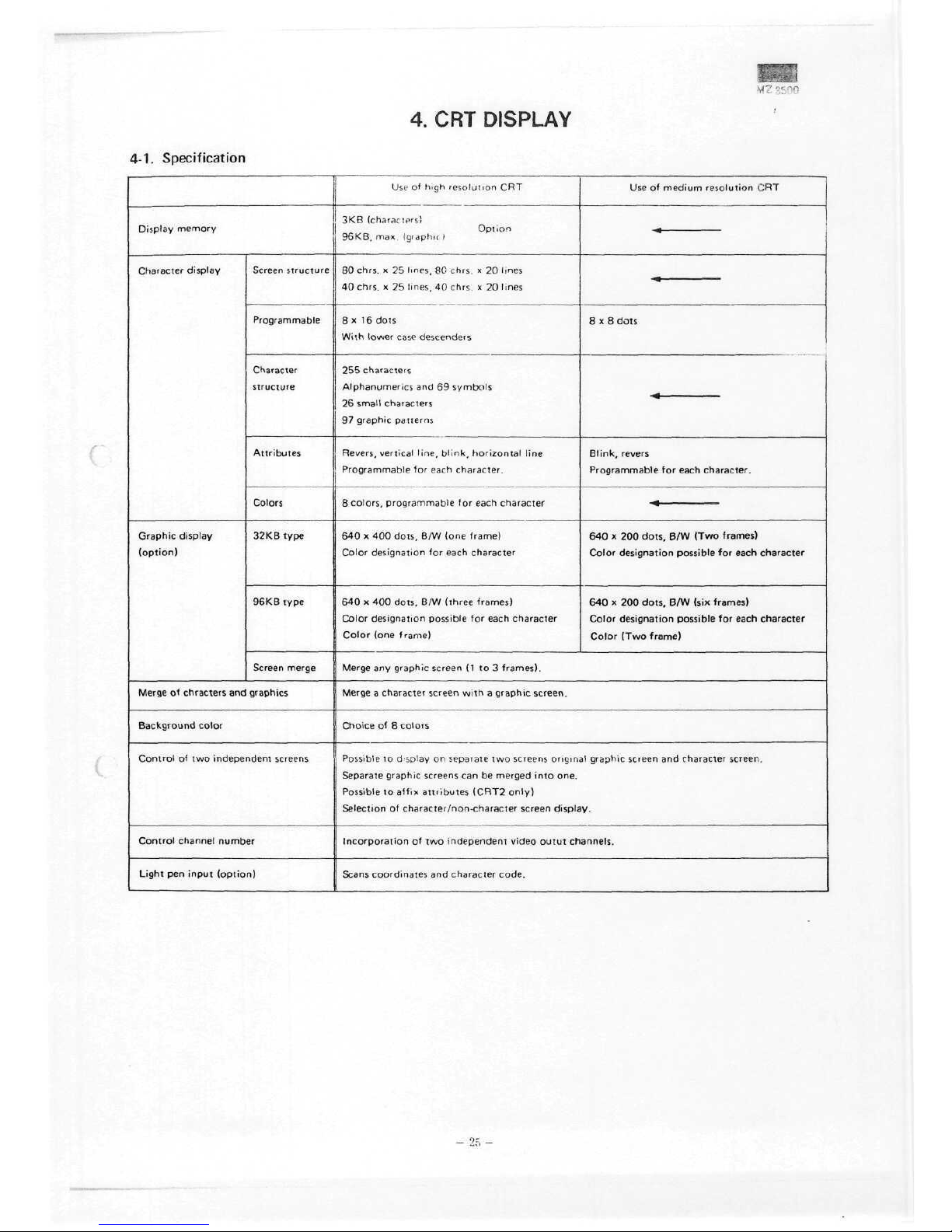

4. CRT

DISPLAY

V 3i 30

4-1.

Specification

Use

of

high resolution

CRT

Display

mernory

Character display

Graphic

display

(option)

Screen

structure

Programmable

Character

structure

Attributes

Colors

32KB

type

96KB

type

Screen

merge

Merge

of

chracters

and

graphics

Background

Color

Control

of two

independent

screens

Control

channel

number

Light

pen

input

(option)

3KB

(Character;)

Option

96KB.

max.

(graphic

l

80

chrs.

x 25

Imes,

80

chrs.

x 20

lines

40

chrs.

x 25

Imes.

40

chrs.

x 20

Imes

8x16 dots

With

Iower

case

descenders

255

characters

Alphanumerics

and 69

Symbols

26

small

characters

97

graphic

patterns

Revers,

Vertical

line.

blink,

horizontal

line

Programmable

for

each Character.

8

colors,

Programmable

for

each Character

640 x 400

dots.

B/W

(one frame)

Color

designation

for

each

Character

640 x 400

dots.

B/W

(three frames)

Color

designation possible

for

each Character

Color

(one frame)

Use

of

medium

resolution

CRT

8x8

dots

Blink,

revers

Programmable

for

each Character.

640 x 200

dots,

B/W

(Two

frames)

Color

designation

possible

for

each Character

640 x 200

dots.

B/W

(six frames)

Color

designation

possible

for

each Character

Color

(Two

frame)

Merge

any

graphic screen

(1 to 3

frames).

Merge a Character screen

with a graphic

screen.

Choice

of 8

colors

Possible

to

d'bplay

on

separate

two

screens

original

graphic

scieen

and

Character screen.

Separate

graphjc

screens

can be

merged

into

one.

Possible

to

affix

attributes

(CRT2

only)

Selection

of

Character

/non-character screen

display.

Incorporation

of two

independent Video

outut

channels.

Scans

coordinates

and

Character

code.

Page 23

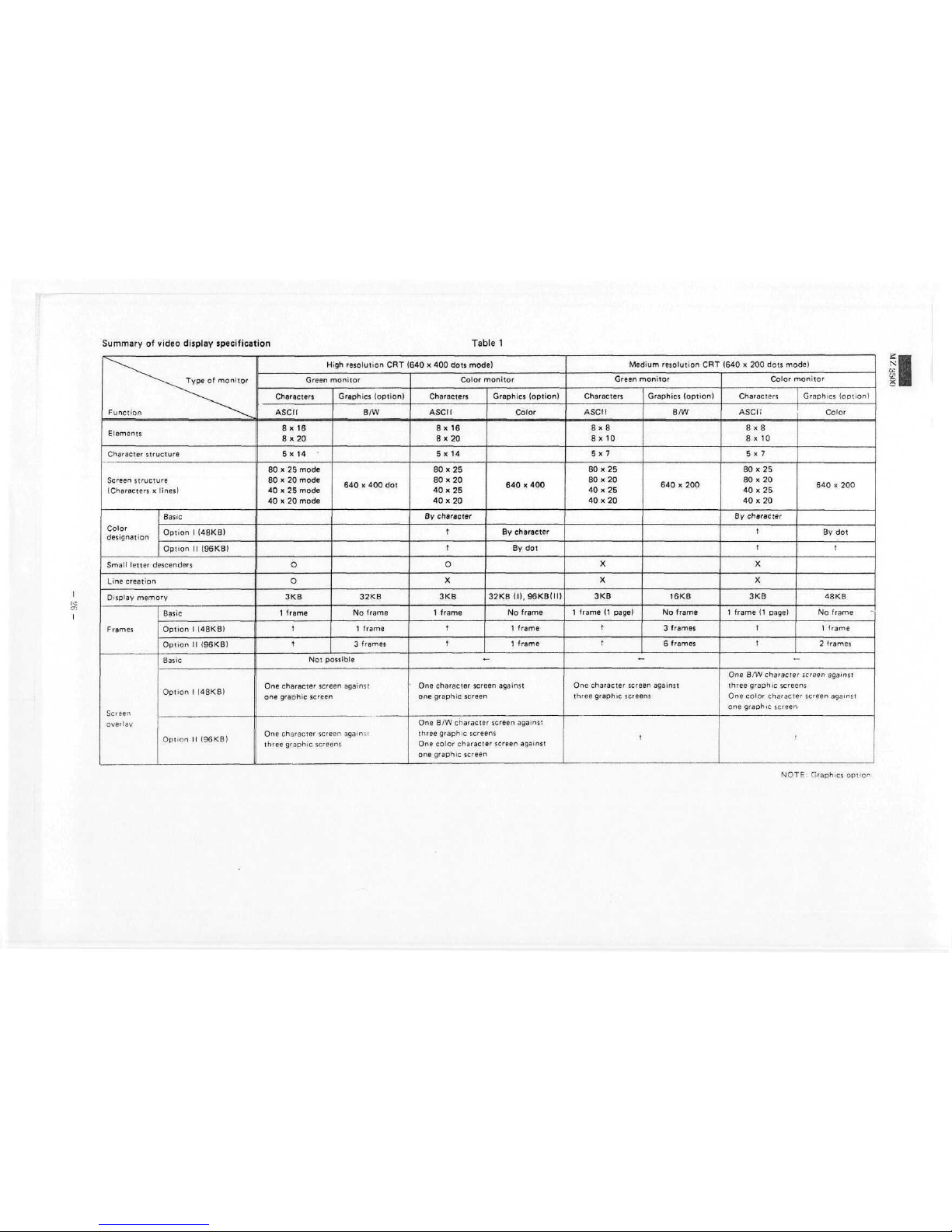

Summary

of

video

display specification

Table

1

^^^^^

Type

of

monitor

Function

^^^^

Elements

Character structure

Screen

structure

(Characters x ines)

Color

designation

Basic

Option 1 (48KB)

Option

II

(96KBI

Small letter descenders

Line

creation

Display

memory

Frames

Screen

overlay

Basic

Option 1 (48KB)

Option

II

(96KB)

Basic

Option 1 (48KB)

Option

II

196KB)

High

resolution

CRT

(640

x 400

dots

mode)

Green

monitor

Characters

ASCII

8x 16

8x20

5x 14

80 x 25

mode

80 x 20

mode

40 x 25

mode

40 x 20

mode

O

O

3KB

1

frame

t

t

Graphics

(option)

B

/W

640 x 400 dot

32KB

No

frame

1

frame

3

frames

Not

possible

One

Character

screen

against

one

graDhic

screen

One

Character

screen

ngamsi

three

graphic

screens

Color

monitor

Characters

ASCII

8x 16

8x 20

5x 14

80 x 25

80 x 20

40 x 25

40 x 20

By

Character

t

t

O

X

3KB

1

frame

t

t

Graphics

(option)

Color

640 x 400

By

Character

By

dot

32KB

(I),96KB(II)

No

frame

1

frame

1

frame

«-

One

Character

screen against

one

graphic screen

One B/W

Character

screen

against

three graphic

screens

One

color

Character

screen

against

one

graphic screen

Medium

resolution

CRT

(640

x 200

dots

mode)

Green

monitor

Characters

ASCII

8x8

8x10

5x7

80 x 25

80 x 20

40 x 25

40

x20

X

X

3KB

1

frame

(1

page)

t

t

Graphics

(option)

B /W

640 x 200

16KB

No

frame

3

frames

6

frames

*-

One

Character

screen

against

three graphic screens

Color

monitor

Characters

ASCI:

8x8

8x10

5x7

80 x 25

80 x 20

40 x 25

40 x 20

By

Character

t

1

X

X

3KB

1

frame

(1

page)

t

t

Graphics

(option)

Color

640 x 200

By

dot

t

48KB

No

frame

1

frame

2

frames

-

One B/W

Character screen agamst

three graphic

screens

One

Color

Character

screen

agamst

one

graphic

screer,

!

I

l

IC

er.

NOTE:

Graphics

option

Page 24

M Z 3500

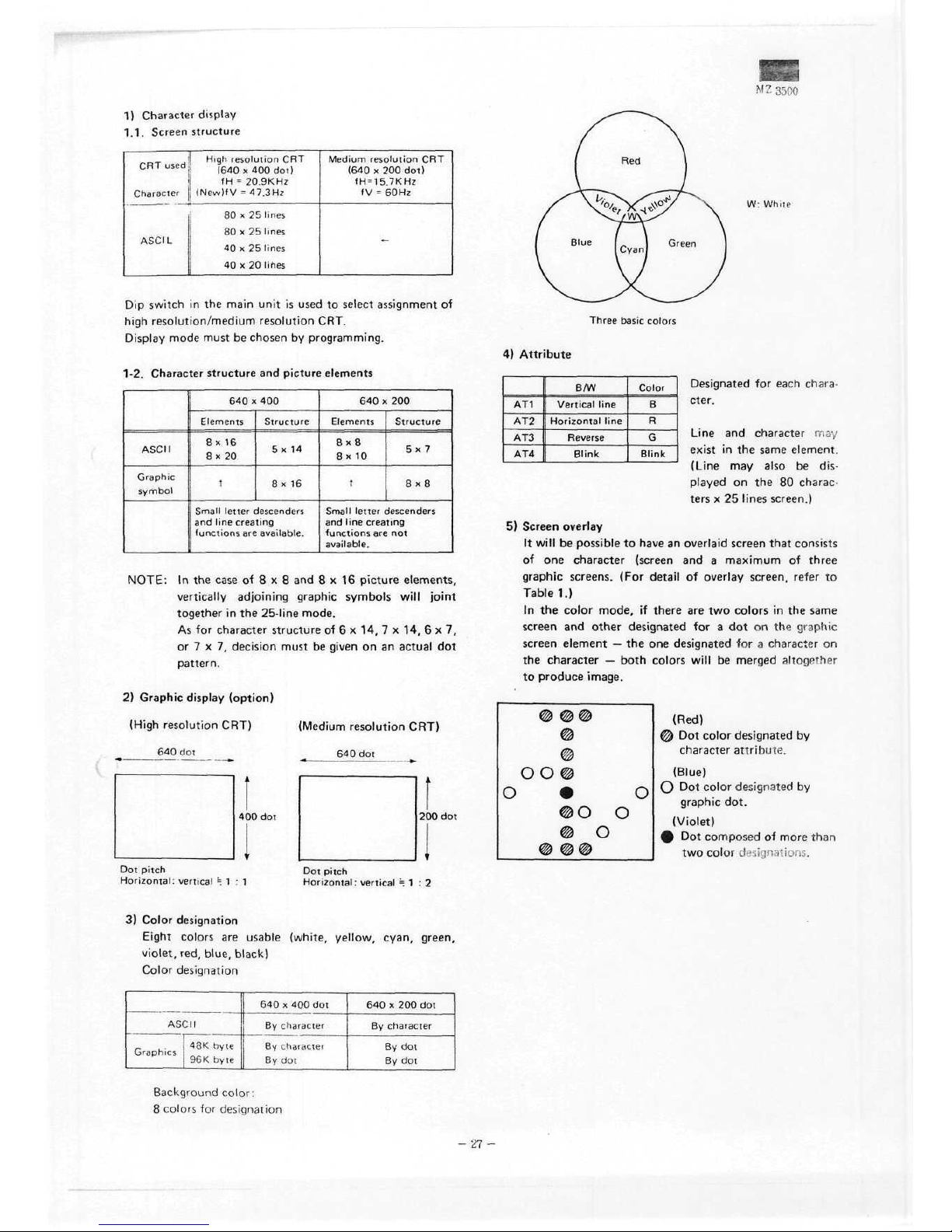

1}

Character display

1.1.

Screen

structure

CRT

used

Character

ASCII

High

resolution

CRT

(640

x 400

dot)

fH • 20.9KHz

(New)fV = 47.3

Hz

80 x 25

lines

80 x 25

lines

40 x 25

lines

40 x 20

lines

Medium

resolution

CRT

(640

x 200

dol)

fH =

15.7KHz

fV =

60Hz

-

Dip

switch

in the

main

unit

is

used

to

Select

assignment

of

high resolution/medium resolution CRT.

Display

mode must

be

chosen

by

Programming.

1-2.

Character

structure

and

picture elements

ASCII

Graphic

Symbol

640 x 400

Elements

8x 16

8x 20

1

Structure

5 x 14

8x 16

Small

letter

descenders

and

line

creating

functions

are

avaitable.

640 x 200

Elements

8x8

8 x 10

t

Structure

5x7

8x8

Small

letter

descenders

and

line

creating

functions

are not

available.

NOTE:

In the

case

of 8 x 8 and

8x16

picture

elements,

vertically

adjoining graphic Symbols

will

joint

together

in the

25-line

mode.

As

for

Character

structure

of 6 x 14, 7 x 14,

6x7,

or

7 x 7,

decision must

be

given

on an

actual

dot

pattern.

2)

Graphic

display

(option)

(High

resolution

CRT)

640 dot

(Medium

resolution

CRT)

640 dot

400 dot

200

dot

Dot

pitch

Horizontal:

Vertical

= 1:1

Dot

pitch

Horizontal:

Vertical

= 1:2

W:

White

Three

basic

colors

4)

Attribute

AT1

AT2

ATS

AT4

B/W

Vertical

line

Horizontal

line

Reverse

Blink

Color

B

R

G

Blink

Designated

for

each

Chara-

cter.

Line

and

Character

rr.üy

exist

in the

same

element.

(Line

may

also

be

dis-

played

on the 80

charac-

ters

x 25

lines

screen.)

5)

Screen overlay

It

will

be

possible

to

have

an

overlaid

screen

that

consists

of one

Character (screen

and a

maximum

of

three

graphic

screens.

(For

detail

of

overlay screen,

refer

to

Table

1.)

In the

color

mode,

if

there

are two

colors

in the

same

screen

and

other

designated

for a dot on the

graphic

screen

element

— the one

designated

for a

Character

on

the

Character — both

colors

will

be

merged

altogpTher

to

produce

Image.

00

o

o

>o

o

»

o

(Red)

© Dot

color

designated

by

Character

attribute.

(Blue)

O Dot

color

designated

by

graphic dot.

(Violet)

£ Dot

composed

of

more than

two

color

designntions.

3)

Color

designation

Eight

colors

are

usable

(white,

yellow,

cyan, green,

violet,

red,

blue,

black)

Color

designation

ASCII

_

48K

hyte

Graphics

| 96 K

byte

640 x 400 dot

By

Character

By

Character

By

dot

640 x 200 dot

By

Character

By

dot

By

dot

Background

color:

8

colors

for

designation

Page 25

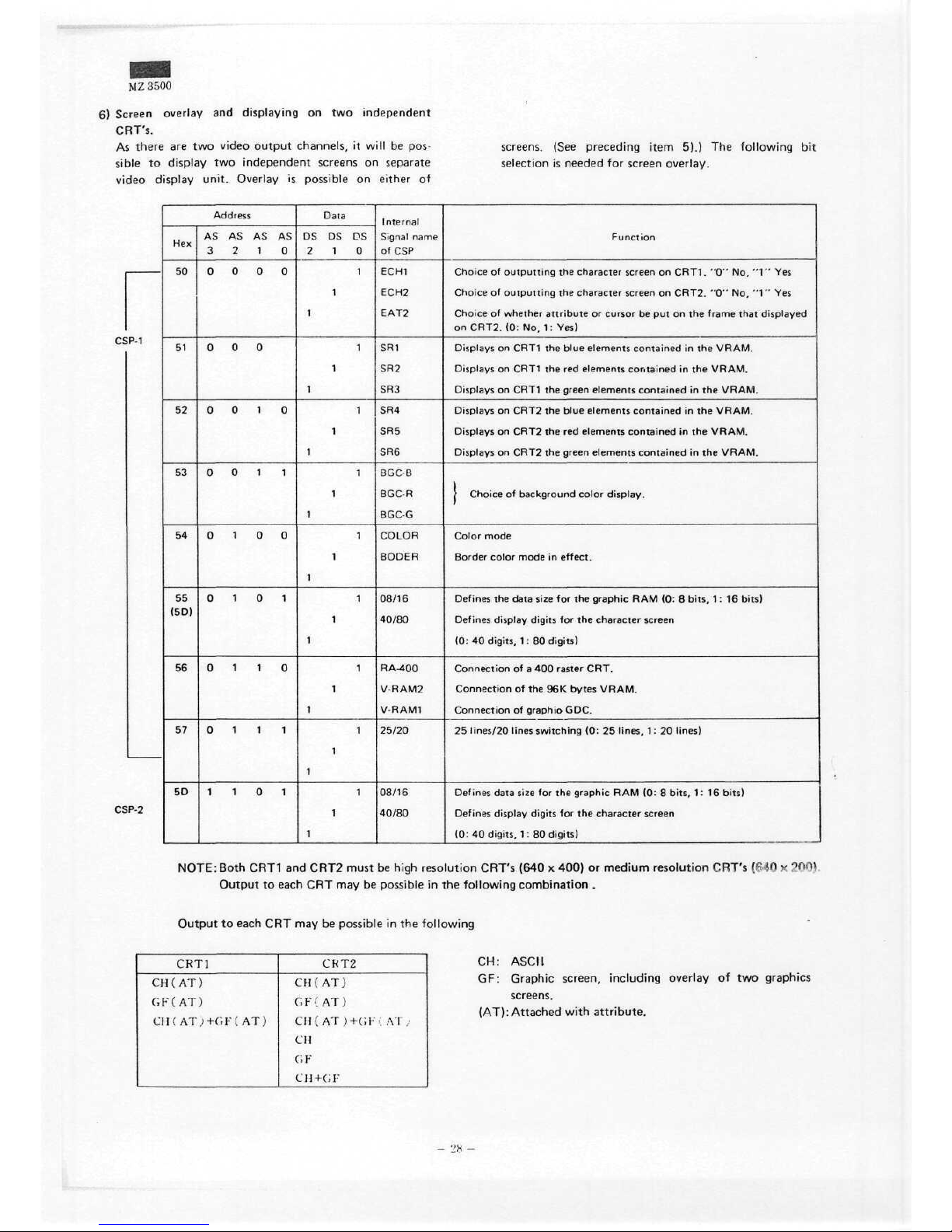

M Z 3500

6)

Screen

overlay

and

displaying

on two

independent

CRT's.

As

there

are two

video

Output

channels,

it

will

be

pos-

sible

to

display

two

independent

screens

on

separate

video

display

unit.

Overlay

is

possible

on

either

of

screens.

(See

preceding

item

5).)

The

following

bit

selection

is

needed

for

screen

overlay.

;p-i

;p-2

Address

Hex

50

51

52

53

54

55

(50)

56

57

5D

AS AS AS AS

3210

0000

000

0010

0011

0100

0101

0110

0111

1101

Data

DS

DS DS

2 1 0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Internal

Signal

name

of CSP

ECH1

ECH2

EAT2

SR1

SR2

SR3

SR4

SR5

SR6

BGC-B

BGC-R

BGC-G

COLOR

BODER

08/16

40/80

RA-400

V-RAM2

V-RAM1

25/20

08/16

40/80

Function

Choice

of

outputting

the

Character

screen

on

CRT1.

"0" No, "1" Yes

Choice

of

outputting

the

Character

screen

on

CRT2.

"0" No, "1 " Yes

Choice

of

whether

attribute

or

Cursor

be put on the

frame that displayed

on

CRT2.

(0: No, 1:

Yes)

Displays

on

CRT1

the

blue elements contained

in the

VRAM.

Displays

on

CRT1

the red

elements contained

in the

VRAM.

Displays

on

CRT1

the

green elements contained

in the

VRAM.

Displays

on

CRT2

the

blue elements contained

in the

VRAM.

Displays

on

CRT2

the red

elements

contained

in the

VRAM.

Displays

on

CRT2

the

green elements contained

in the

VRAM.

/

Choice

of

background

Color

display.

Color mode

Border color mode

in

effect.

Defines

the

data

size

for the

graphic

RAM (0: 8

bits,

1:16 bits)

Defines

display digits

for the

Character screen

(0:

40

digits,

1 : 80

digits)

Connection

of a 400

raster CRT.

Connection

of the 96K

bytes

VRAM.

Connection

of

graphio GDC.

25

lines/20 lines switching

(0: 25

lines,

1 : 20

lines)

Defines

data

size

for the

graphic

RAM (0: 8

bits,

1: 16

bits)

Defines

display digits

for the

Character

screen

(0:

40

digits,

1 : 80

digits)

NOTE:Both

CRT1

and

CRT2

must

be

high

resolution

CRT's

(640 x 400)

or

medium

resolution

CRT's

(640 x 200>

Output

to

each

CRT may be

possible

in the

following

combination

.

Output

to

each

CRT may be

possible

in the

following

CRT1

CH

( AT )

GF(AT)

CH ( AT

.)+r,F(

AT)

CKT2

CH(AT)

GF(

AT)

cn( AT

)-K;F>,

AT .

CH

GF

CH+GF

CH:

ASCII

GF:

Graphic

screen,

including

overlay

of two

graphics

screens.

(AT):Attached

with

attribute.

Page 26

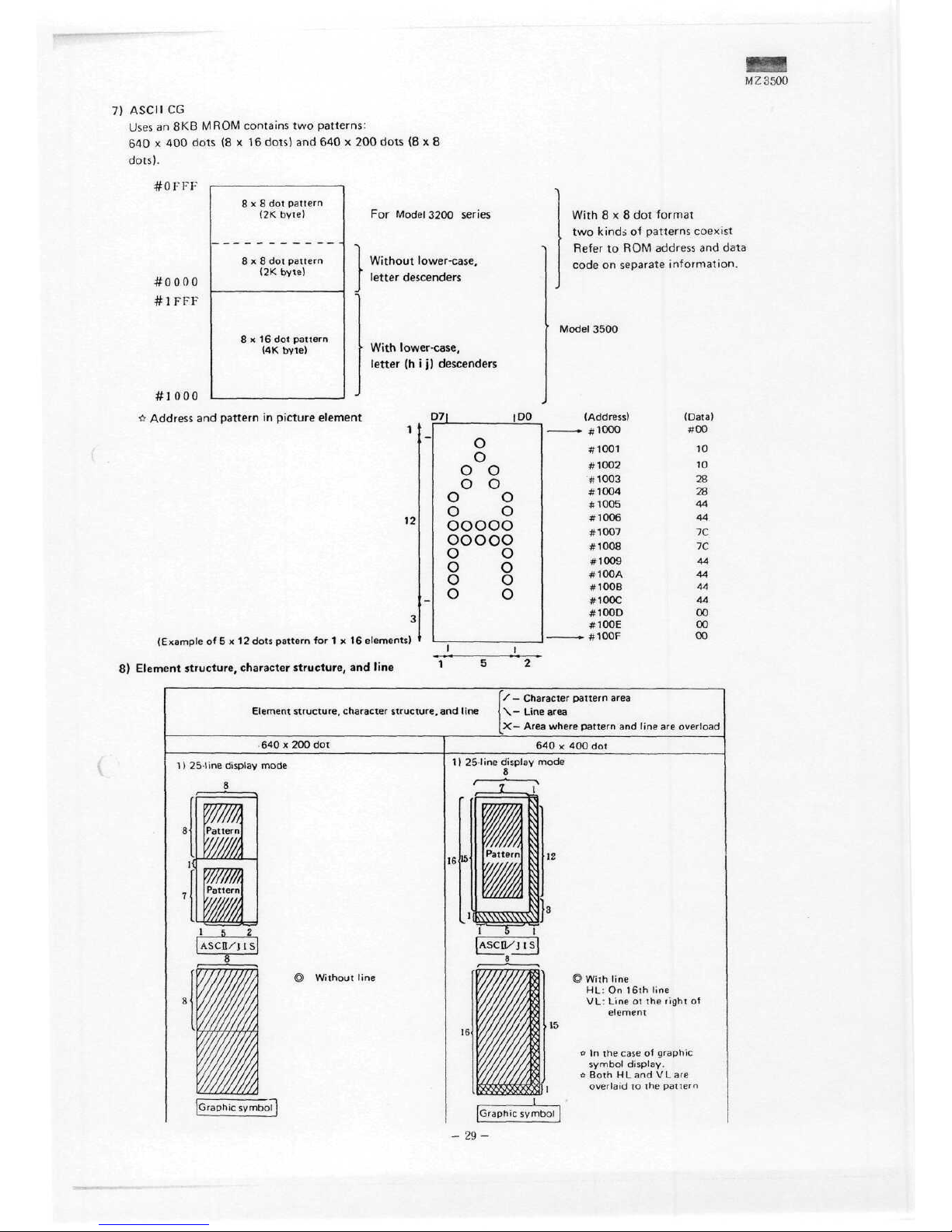

7)

ASCII

CG

Uses

an 8KB M ROM

contains

two

patterns:

640 x 400

dots

(8x16

dots)

and 640 x 200

dots

(8x8

dots).

M Z 3500

-H-

u r r r

#0000

#1FFF

#1 onn

8x8 dot

pattern

(2K

byte)

8x8 dot

pattern

(2K

byte)

8x16

dot

pattern

(4 K byte)

For

Model

3200

series

With

8x8 dot

formal

two

kindi

of

patterns

coexist

~\

Without

Iower-case,

letter

descenders

>

With

Iower-case,

letter

(h i j)

descenders

Address

and

pattern

in

picture

element

D7| |DO

1

12

/F*amnlp

nf fi x 12

dots

nattern

for

1x16 elements)

_

O

o

o

o

o

o

^*s ^-S

o o

o

o

ooooo

ooooo

o o

0

0

o o

o o

Refer

to ROM

address

and

data

code

on

separate

Information.

Model

3500

(Address)

(Data)

.

#1000

#00

#1001

10

#1002

10

#1003

28

#1004

28

#1005

44

#1006

44

#1007

7C

#1008

7C

#1009

44

#100A

44

#100B

44

#100C

44

#100D

00

#100E

00

~

#100F

00

8)

Element

structure,

Character

structure,

and

line

Element

structure,

Character

structure,

and

line

/—

Character

pattern

area

\—

Line area

X—

Area where pattern

and

line

are

overload

640x200

dot

1)

25-line

display

mode

fil

Iflf:

Pattern

'A

Pattern

l 5 2

IASCD/JIS]

Without

line

[(^raphic

symbolj

640 x 400 dot

1)

25-line

display

mode

8

16

12

Ascn/jis

©With

line

HL: On

16th line

VL:

Line

ot the

right

of

element

o In the

case

of

graphic

Symbol

display.

e

Both

HL and VL are

overlaid

to the

pattern

l

Graphic

symbol

i

-

29-

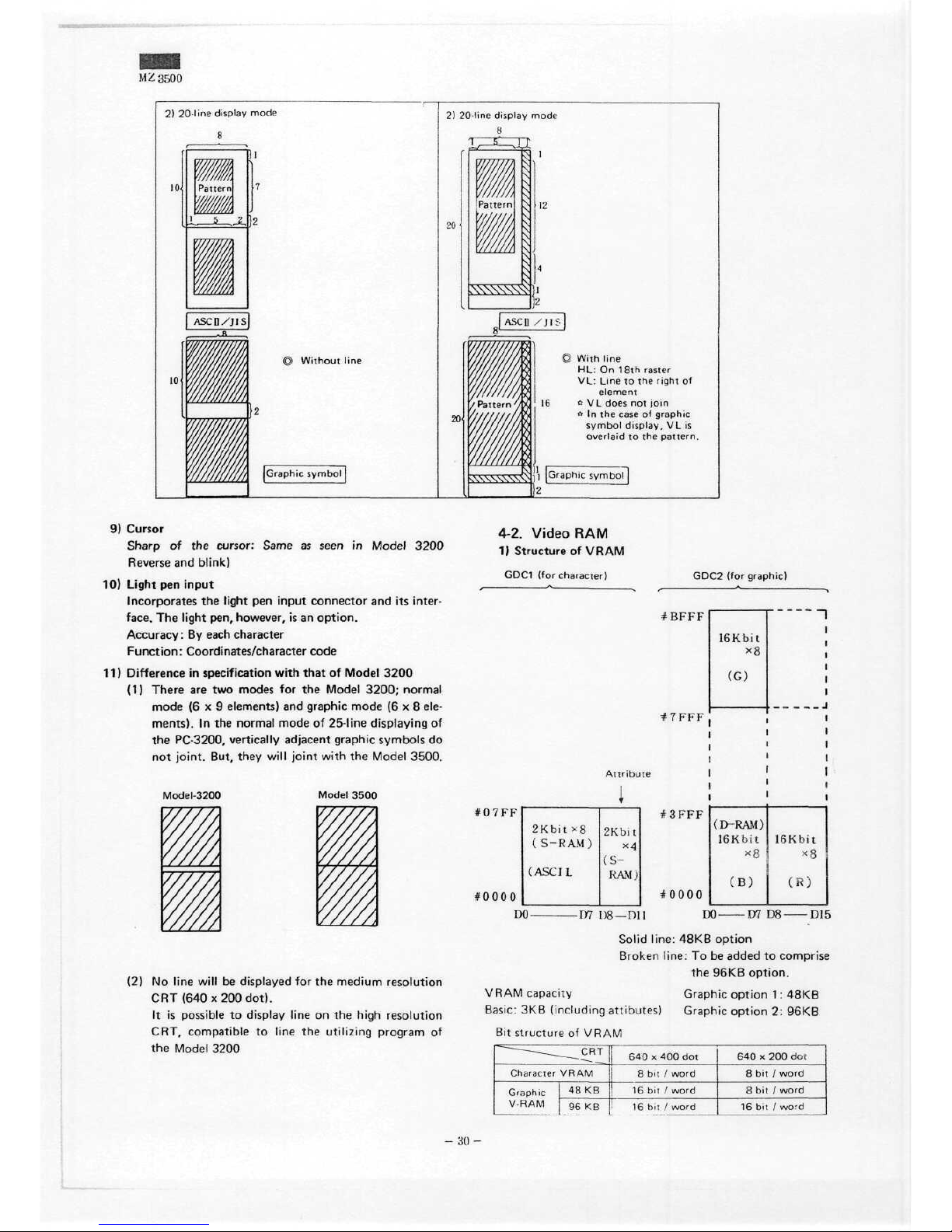

Page 27

M ^ 3500

2)

20-line display

mode

10

Without

line

Graphic

Symbol

2)

20-line display

mode

8

20«

20

XXSNNX^-ll

With

line

HL: On

18th

raster

VL:

Line

to the

right

of

element

c

V L

does

not

join

0 In the

case

of

graphic

Symbol

display,

VL is

overlaid

to the

pattern.

Graphic Symbol

|

9)

Cursor

Sharp

of the

Cursor: Same

äs

seen

in

Model

3200

Reverse

and

blink)

10)

Light

pen

input

Incorporates

the

light

pen

input

connector

and its

inter-

face.

The

light

pen, however,

is an

Option.

Accuracy:

By

each

Character

Function:

Coordinates/character code

11)

Difference

in

specification

with

that

of

Model

3200

(1)

There

are two

modes

for the

Model

3200;

normal

mode (6x9 elements)

and

graphic mode (6x8 ele-

ments).

In the

normal mode

of

25-line displaying

of

the

PC-3200, vertically adjacent graphic symbols

do

not

joint.

But, they

will

joint

with

the

Model 3500.

Model-3200

Model

3500

(2)

No

line

will

be

displayed

for the

medium resolution

CRT

(640

x 200

dot).

It is

possible

to

display line

on the

high resolution

CRT,

compatible

to

line

the

utilizing program

of

the

Model 3200

4-2.

Video

RAM

1)

Structure

of

VRAM

GDC1 (for Character)

GDC2

(for graphic)

#BFFF

*7FFF

16Kbit

(G)

Attribute

#07FF

#0000

2Kbit

*8

(

S -R

AM)

(ASCI

L

2Kbit

x4

(S-

RAM)

#3FFF

#0000

(D-RAM)

16Kbit

xS

(B)

16Kbit

x8

(R)

DO-

-D7

D8—DU

DO-

-D7

D8-

-D15

Solid

line:

48KB

Option

Broken

line:

To be

added

to

comprise

the

96KB

Option.

VRAM

capacity

Graphic

Option

1:

48KB

Basic:

3KB

(including

attibutes)

Graphic

Option

2:

96KB

Bit

Structure

of

VRAM

— — £^J

640x400

dot

Character

VRAM

Graphic l 48KB

V-RAM

j

96 KB

j

8 bit /

word

16

bit /

word

16 b<t /

word

640

x 200 de i

8

bit /

word

8 bit /

word

16

bit /

word

-

30-

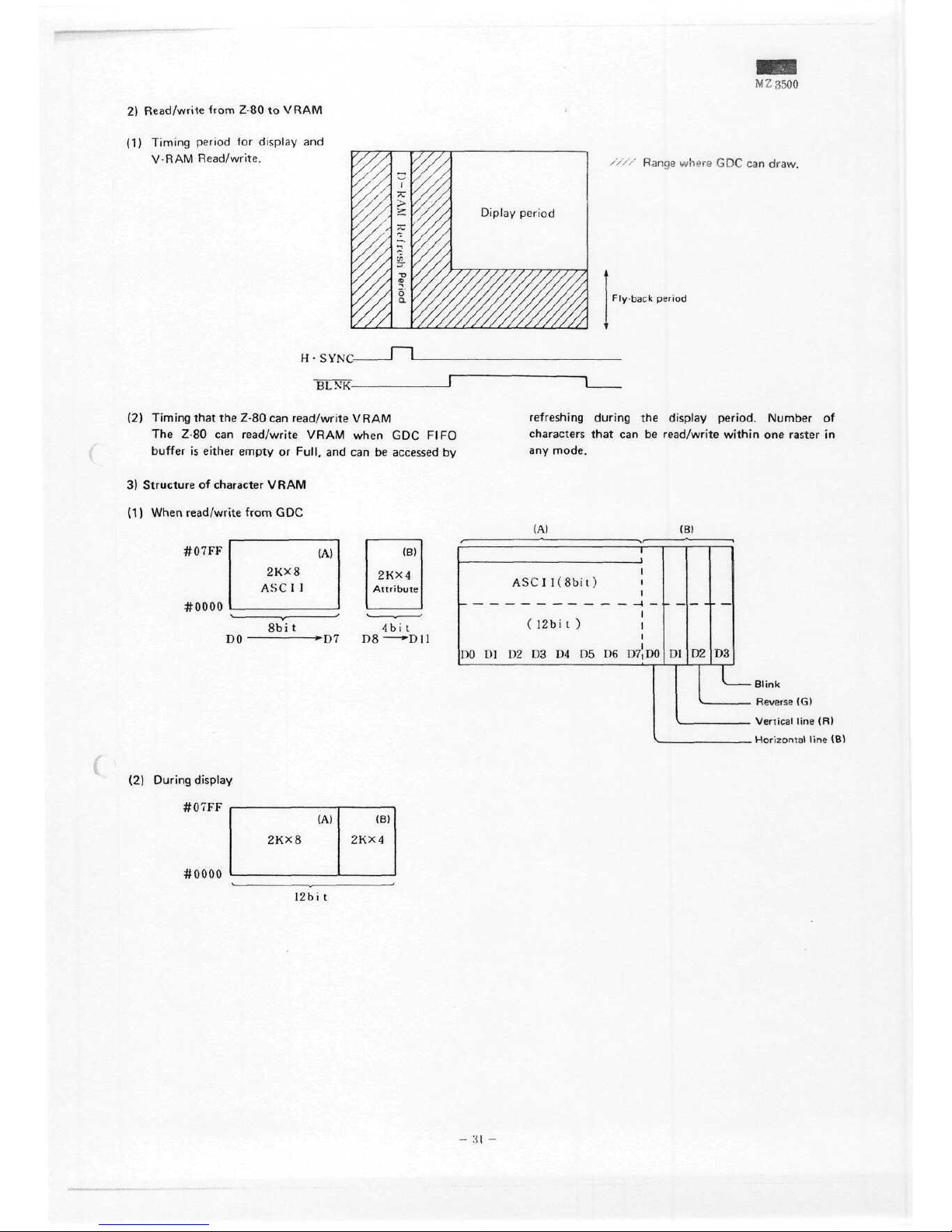

Page 28

M Z 3500

2)

Read/write from 2-80

to

VRAM

(1)

Timing

period

for

display

and

V-RAM

Read/write.

Diplay

period

////

Range

whers

GDC can

draw.

Fly-back

period

H •

SYNC-

BLNK-

(2)

Timing

that

the

Z-80

can

read/write VRAM

The

Z-80

can

read/write VRAM when

GDC

FIFO

buffer

is

either empty

or

Füll,

and can be

accessed

by

3)

Structure

of

Character

VRAM

(1)

When read/write

from

GDC

#07

FF

#0000

refreshing

during

the

display

period.

Number

of

characters

that

can be

read/write

within

one

raster

in

any

mode.

(A)

(B)

(A)

2KX8

ASCI

I

8bi t

30 * D i

(B)

2KX4

Attribute

4bi

t

)ö * U

l

1

ASClKSbit)

i

i

_ — — — __ — —

__i-

l

(12bit)

i

DO

Dl D2 D3 D4 D5 D6

D7|D

0

D

1D2

D3

L

Blink

Vertical

line

(R)

Horizontal

line

(B)

(2)

During

display

#07FF

#0000

(A)

2KX8

(B)

2KX4

,

12bi

t

Page 29

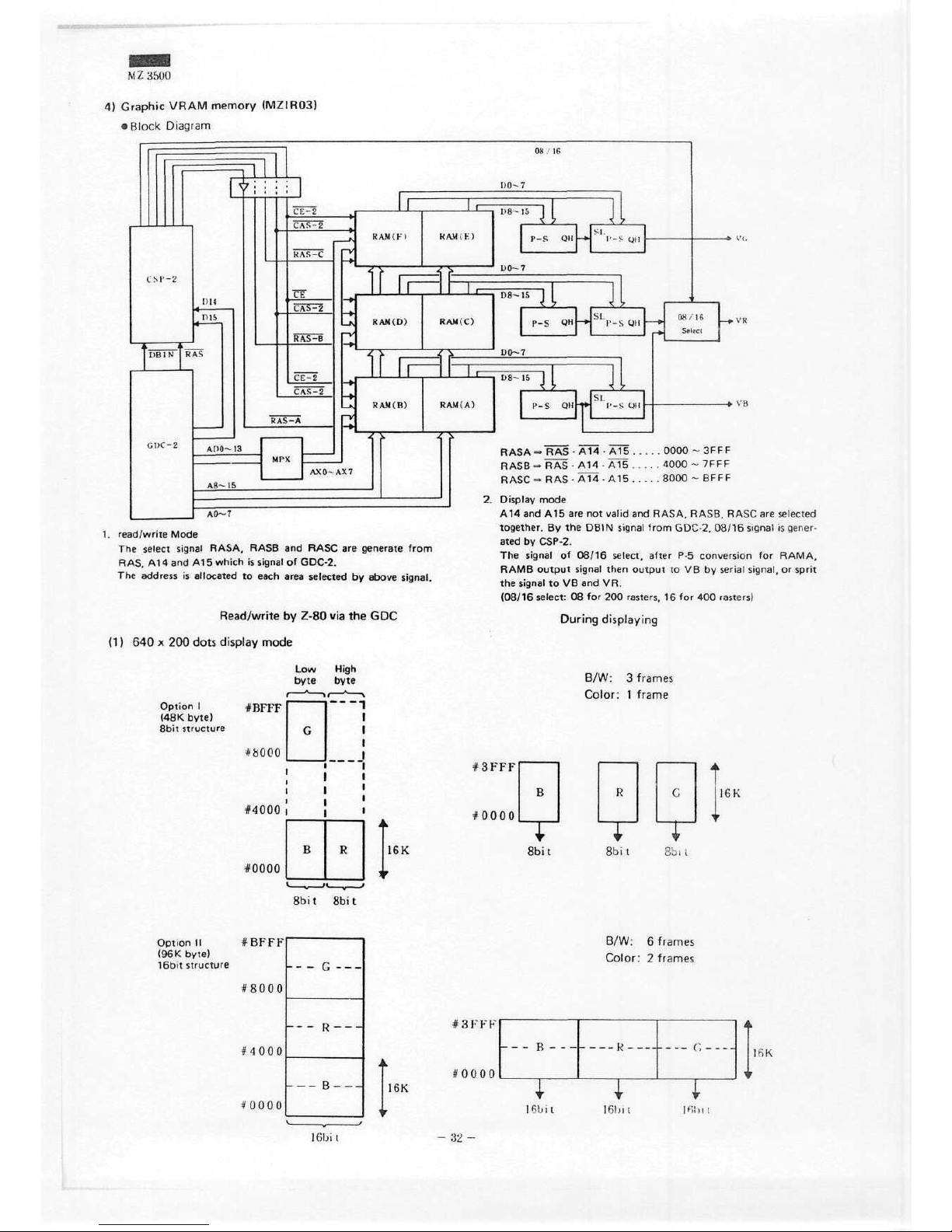

M 2 3500

4)

Graphic

VRAM

memory

(MZIR03)

•

Block

Diagram

t+r-

1

CSP-8

D14

CAS-2

RAM'.FI

RAMCK)

M

1

1 Ir—

RAM(D)

RAW(C)

1 1

|

RAM(B)

RAM(A)

i

n

P-S QH

T

\[

SL

I'-S

A8-15

AO—7

1.

read/write Mode

The

select

signal

RASA, RASB

and

RASC

are

generate

from

RAS,

A14 and A1 5

which

is

signal

of

GDC-2.

The

address

is

allocated

to

each

area

selected

by

above

signal.

Read/write

by

Z-80

via the GDC

(1)

640 x 200

dots

display

mode

Option l #BFFF

(48K

byte)

8bit

structure

#8000

#4000

#0000

Low

byte

G

B

High

byte

-

__

i

R

i

16K

RASA

= RAS • A14 • A15 . .

RASB=

RAS • A14 • A15 .

RASC

=• RAS • A14 • A15 . .

.

. .

0000 ~ 3FFF

.

. .

4000

~ 7 F F F

. . 8000 ~ BFFF

2.

Display mode

A14 and A15 are not

valid

and

RASA, RASB. RASC

are

selected

together.

By the

DBIN

signal

from

GDC-2. 08/16 signal

is

gener-

ated

by

CSP-2.

The

signal

of

08/16

Select,

after

P-5

conversion

for

RAMA,

R

AM B

Output signal then Output

to V B by

Serial

signal,

or

sprit

the

signal

to VB and VR.

(08/16

Select:

08 for 200

rasters.

16 for 400

rasters)

During

displaying

B/W: 3 frames

Color: 1 frame

#3KFF

#0000

8bit

16 K

it

8bii

8bit

8bit

Option

ll

#BKFK

(96K byte)

16bit structure

#8000

#4000

*0000

G

16K

#3FFF

#0000

B/W: 6 frames

Color: 2 frames

i

16bit

16bit

]fiK

16bil

Page 30

M Z 3500

(2)

640 x 400

dots display

mode

Option

1

(48Kbyte)

#4000

16

bits structure

# o u-

i.-p

#0000

f

BKFF

Option

H

(96K byte)

16

bits

structure

#8000

#4000

#0000

5)

Synchronize signal

timing

(1)

For 640 x 200

dots display

r

|

fH = 15.87kHz

l t\i - cn

u-»

1

Video

t

i

16bit

G

R

B

V

t

16bit

node

B/W: 1 frame

Color: 1 frame

Color

can be

A

#3FFF

'k

designated

tor

each

Character.

I6K

Video

!6K

,,

#0000

X

i

16b.t

B/W: 3 frames

Color: 1 frame

#8FFF

"

B R G 16K

iL

#0000

,r

16K

4 l i-

,r 16bit

16bit 16bit

.X

e

s

\

T ' X : Y ^ 1 : 2

Dot

Clock

(ÖD)

2XCCLK

Horizontal display

time

HFP

HS

HBP

Vertical

display

time

VFP

VS

VBP

GDC-1

(SOdigits)

Character

display

(40

digits)

<16MHz)

(

8MHz>

(4MHz)

<2MHz>

40/js

7/as

6>JS

10n«

1

2.6ms

1.2ms

1 ms

1.8ms

GDC-2

8

bits

16MHz

4MHz

-

-(14 Chr.)

(12

Chr.)

(tREFO.Sms)

»-

(20

Chr.)

-

*•

•-

«-

graphic)

16

bits

16MHz

2MHz

-

10>JS

5jus

(tREF=1.6msl

8^s

-

l

-

Total

rasters:

261

rasters

Display

raster:

200

rasters

—i —-

'—n

-

^Lt""

1

VSYNC

Jl

-

33-

Page 31

(2) 640 x. 400

bits display mode

fH =

20.92

kHz

fV =

47.3

Hz

4-4

: Y -.

l : l

Doi

Clock

(ÖD)

2XCCLK

Horizontal display

time

HFP

HS

H BP

Vertical display

time

VFP

VP

VBP

GDC-1