Sharp LH540203U-50, LH540203U-25, LH540203U-20, LH540203U-15, LH540203K-50 Datasheet

...

LH540203

CMOS 2048 × 9 Asynchron ous FIFO

FEATURES

•• Fast Acces s Times : 15/20/ 25/ 35/50 ns

•• Fast- Fall-Through Time Ar chitect ure Based on

CMOS Dual-Port SRAM Tec hnology

•• Input Port and Output Port Have Entirely

Indepen dent Timing

•• Expandable in Width and Depth

•• Full, Half-Full, and Empty Status Flags

•• Data Retransmission Capability

•• TTL-Compa tible I/O

•• Pin and Functionally Comp atible with Sharp LH5498

and with Am/IDT/ MS7203

•• Control Signals Assertive- LO W for Noise Immunit y

•• Packages:

28-Pin, 300-mil PDIP

28-Pin, 300-mil SOJ *

32-Pin PLCC

FUNCTIONAL DESCRIP TIO N

The LH540203 is a FIFO (First-In, First-Out) memory

device, based on fully-static CMOS dual-po rt SRAM technology, capable of storing up to 2048 nine-bit words. It

foll ows the industry-standard architecture and package

pinouts for nine-bit asynchronous FIFOs. Each nine-bit

LH540203 wor d m ay consist of a st andard eight -b it by te ,

toget her with a parity bit or a block-marking/ fram ing bit.

The input and output ports operate entirely independent ly of each other , unless the LH540203 becomes

either tota lly full or else totally empty. Data flow at a port

is initiated by asserting either of two asynchronous, assertive- LOW con trol input s: Wr ite (W) for data ent r y at t he

input por t, or Read ( R) for data retrieval at the output port .

Full, Half-Full, and Empty status flags monitor the

extent to which the interna l memory has been filled. The

system may make use of these status outputs to avoid

the risk of data loss, which otherwise might occur either

by attempt ing to write addition al words into an already-f ull

LH540203, or by att empting to r ead additional words from

an already-empty LH540203. When an LH540203 is

operating in a depth-cas caded configuration, the Half-Full

Flag is not available.

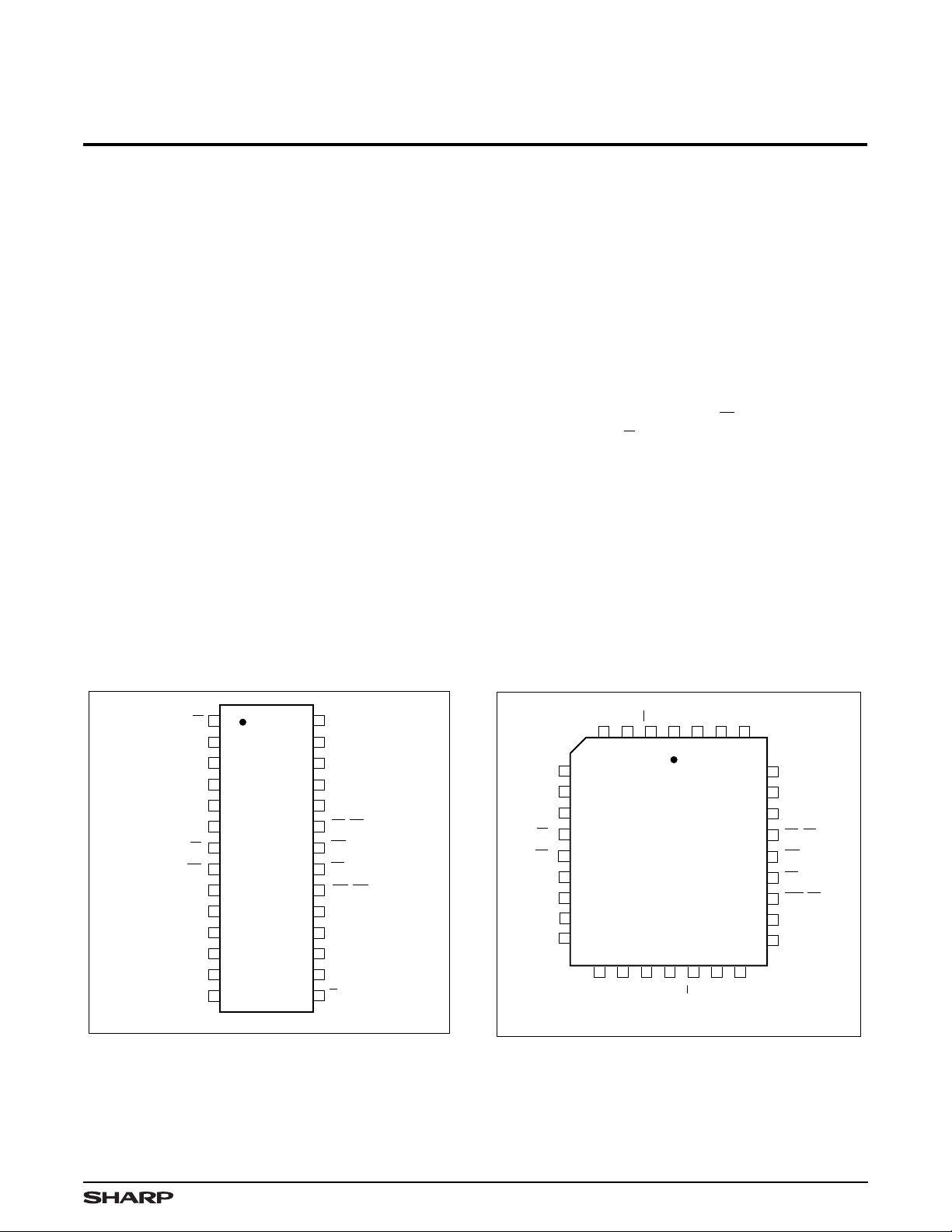

PIN CONNECTIONS

28-PIN PDIP

28-PIN SOJ

*

W

1

2

D

8

D

3

3

D

4

2

D

5

1

D

6

0

XI

7

8

FF

9

Q

0

Q

10

1

11

Q

2

Q

12

3

Q

13

8

V

14

SS

28

27

26

25

24

23

22

21

20

19

18

17

16

15

Figure 1. Pin Connections fo r PDIP and

SOJ * Packages

V

CC

D

4

D

5

D

6

D

7

FL/RT

RS

EF

XO/HF

Q

7

Q

6

Q

5

Q

4

R

TOP VIEW

540203-2D

32-PIN PLCC TOP VIEW

D

2

D

1

D

0

XI

FF

Q

0

Q

1

Q

2

NOTE: * = No external electrical connections are allowed.

10

11

12NC

13

D3D

4

3

5

6

7

8

9

14

15

3

8

Q

Q

*

8

W

NC

2

1

16

17

SS

V

NC*

18

32

4

CC

V

R

19

31

5

D

D

30

D

29

6

D

28

7

27

NC

26

FL/RT

25

RS

24

EF

23

XO/HF

22

Q

7

21

Q

20

4

Q

Q

6

5

540203-3D

Figure 2. Pi n Connecti ons for PLCC Package

* This is a final data sheet; except that all references to the SOJ package have Advance Information status .

1

LH540203 CMOS 2048 × 9 Asynchronous FIFO

FUN CTIONAL DESCRIPTION (con t’d)

Data w ords are read out from the LH540203’s output

port in precisely the same order that the y were writt en in

at its input port; that is, according to a First-In, First Out

(FIFO) queue discipline. Since the addressing sequence

for a FIFO device’s memory is internally predefined, no

external a ddressing inform ation is required for the operation of the LH540203 device.

Drop-in-replacement compatibility is maintained with

both larger sizes and smaller sizes of industry-standard

nine-bit asynchronous FIFOs. The only change is in the

number of internally-stored data words implied by the

states of the Full Flag and the Half-Full Flag.

The Retran smit (RT) cont r ol s ignal c auses the int ern a l

FIFO- memo ry- ar ray re ad- addr ess po in ter t o be set back

to zero, to point to the LH540203’s f irs t physical mem ory

location, without affecting the internal FIF O-memoryarray write -ad dress pointer. Thus, the Retransmit cont rol

signal provides a mechanism whereby a block of data,

delimited by the zero physical address and the current

write-a ddr ess- po int er value, may be read out

an arbit rary number of times. The o nly rest riction s are t hat

neither the read-address pointer nor the write-address

pointer ma y ‘wrap ar ound’ during t his entire pro cess, i.e.,

advance past physical location zero after traversing the

entire memory. The retransmit facility is not available

when an LH540203 is operating in a depth-expanded

configuration.

repea tedly

The Reset (RS) control signal returns the LH540203

to an initial state, empty and ready to be filled. An

LH5 40203 sho uld be reset dur ing every syst em p ower- up

sequence. A reset operation causes the internal FIFOmem or y-arr ay writ e-a ddr ess p ointe r , as we ll as the rea daddress pointer, to be set back to zero, to point to the

LH540203 ’s first physical mem ory locat ion. Any info rmation which previously had been stored within the

LH5 40203 is not recoverable af ter a reset operat ion.

A cascading (depth-expansion) scheme may be implemented by using the Expansion In (XI) input signal and

the Expansion Out (XO/HF) output signal. This allows a

deeper ‘effective FIFO’ to be implemented by using two

or more LH540203 devices, without incurring additional

laten cy (‘fallthro ugh’ or ‘bubblethrough’) d elays, and without the necessity of storing and r et rieving any given dat a

word more tha n once. In this casc aded oper at ing mode ,

one LH540203 device must be designated as the ‘firstload’ or ‘master’ device, by grounding its First-Load

(FL/RT) control input; the remaining LH540203 devices

are designated as ‘slaves,’ by tying their FL/RT inputs

HIGH. Because of the need to share control signals on

pins, the Half- Full Flag and the retransm ission ca pability

are not available for either ‘master’ or ‘slave’ LH540203

devices operating in cascaded mode.

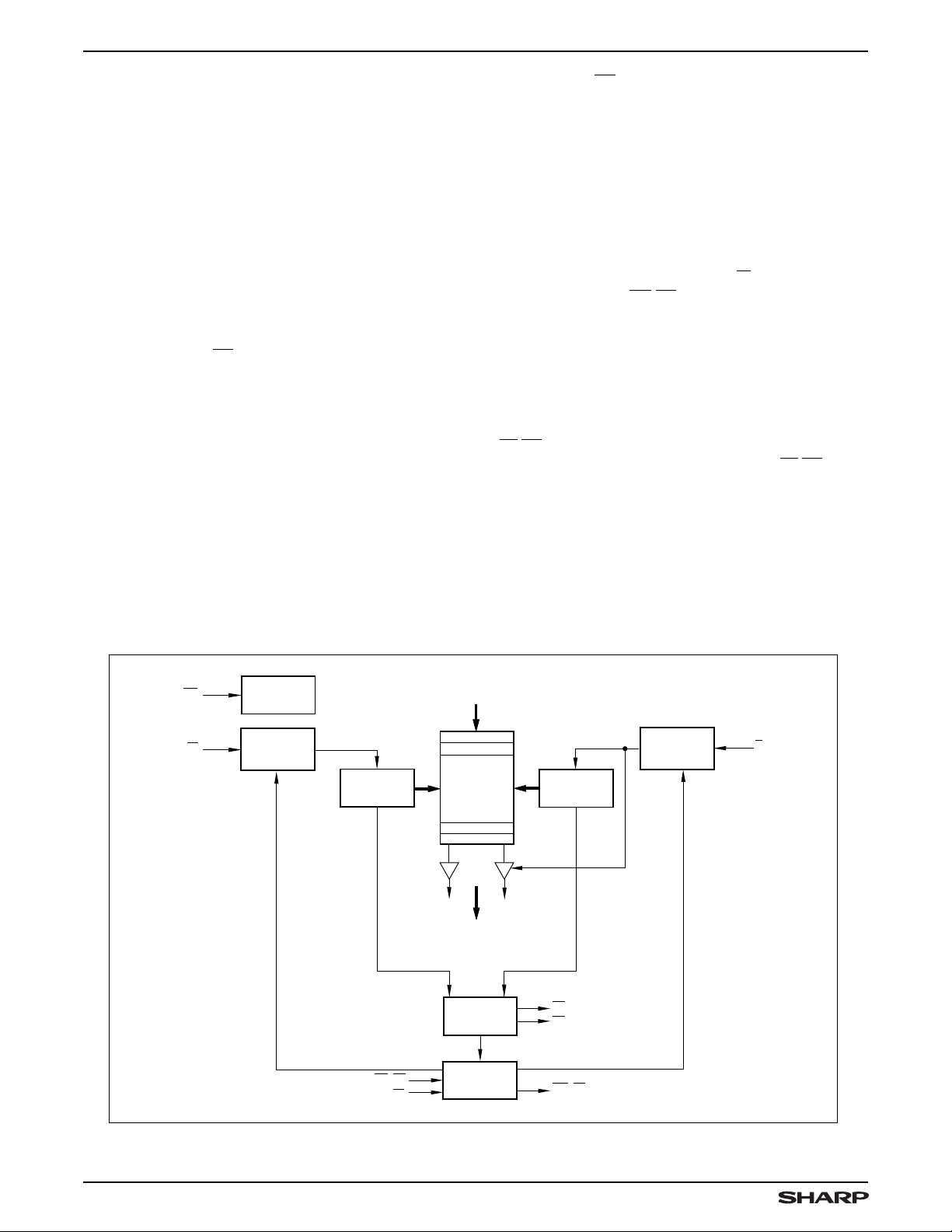

RS

RESET

LOGIC

W

INPUT

PORT

CONTROL

WRITE

POINTER

DATA INPUTS

- D

D

0

8

DUAL-PORT

RAM

ARRAY

2048 x 9

READ

POINTER

OUTPUT

PORT

CONTROL

R

. . .

DATA OUTPUTS

- Q

Q

0

8

EF

FF

XO/HF

540203-1

FL/RT

XI

FLAG

LOGIC

EXPANSION

LOGIC

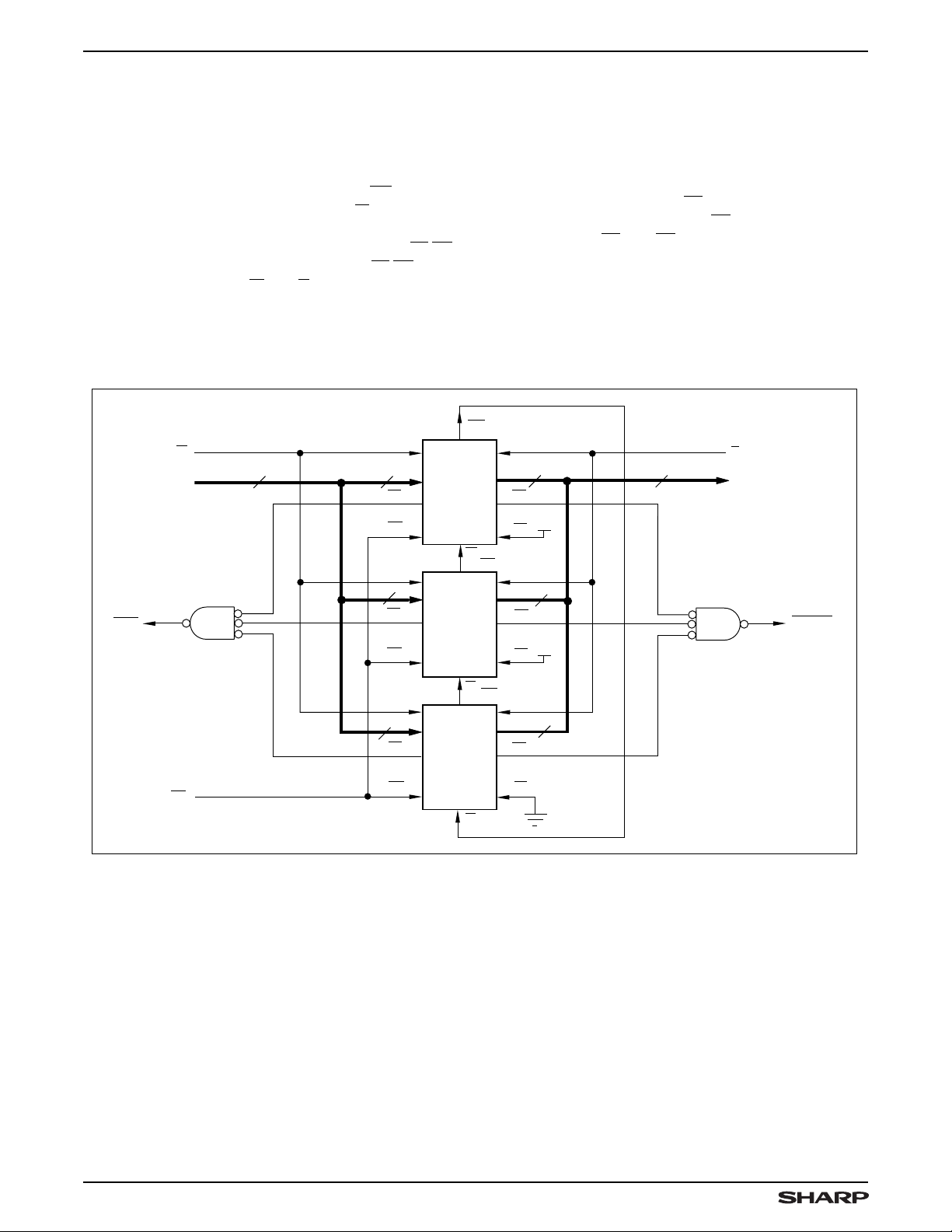

Figure 3. LH540203 Bloc k Diagram

2

CMOS 2048 × 9 Asynchronous FIFO LH540203

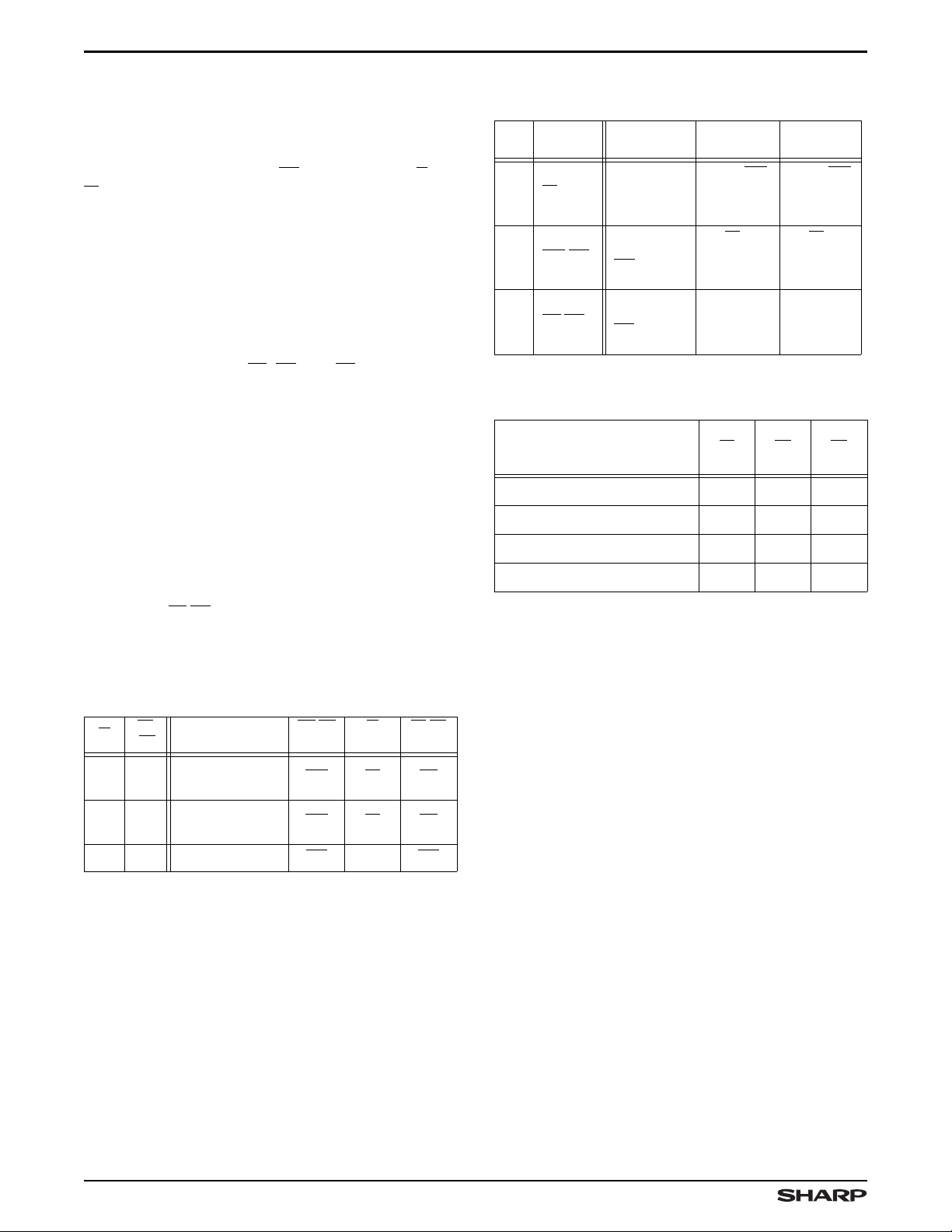

PIN DESCRIPTIONS

I

O/Z

I

I

O

O

1

Input Data Bus

Output Data Bus

Write Request

Read Request

Empty Flag

Full Flag

DESCRIPTION

PIN PIN TYPE

D0 – D

8

Q0 – Q

8

W

R

EF

FF

NOTE:

1. I = Input, O = Output, Z = High-Impedance, V = Power Voltage Level

PIN PIN TYPE

XO/HF

XI

FL/RT

RS

V

CC

V

SS

1

O

I

I

I

V

V

Expansion Out/Half-Full Flag

Expansion In

First Load/Retransmit

Reset

Positive Power Supply

Ground

DESCRIPTION

OPERATIONAL DESCRIPT ION

Reset

The LH540 203 is r eset whenever the Reset input (RS)

is taken LO W. A reset operat ion initializes bot h the readaddress pointer and the write- add res s point er to point to

location zero, the first physical memory location. During

a reset operation, the state of the XI and FL/RT inputs

determines whethe r the device is in standalone mode or

in depth- cascaded mode. (See Tables 1 and 2.) The reset

operation forces the Empty Flag EF to be asserted

(EF = LOW ), and t he Half-Full Flag HF and the Full Flag

FF to be de assert ed (HF = FF = HIGH); the Data Out pins

(D0 – D8) are for ced int o a hig h-im peda nce stat e.

A reset oper at ion is required when ever the LH540 203

first is powered up. The Read (R) and Write (W) inputs

may be in any state when the re set oper atio n is initiated;

but they must be HIGH, before the reset operation is

terminated by a rising edge of RS, by a time t

Read) or t

(for Write) respectively. (See Figure 10.)

WRSS

Write

A write cycle is initiated by a falling edge of the Write

(W) contr ol input . Data setup tim es and hold times must

be observed for the data inputs (D0 – D8). Write operations may occur independently of any ongoing read operation s. However , a write operat ion is possible only if the

FIFO is not full, (i. e., if the Ful l Flag FF is HIGH).

At the fa lling e dge of W for the first write o peration after

the memory is half filled, the Half-Full Flag is asserted

(HF = LOW). It remains asserted until the difference

between the write pointer and the read pointer indicates

that the data words remaining in the LH540203 are filling

the FIFO memory to less than or equal to one-half of its

total capacity. The Half-Full Flag is deasserted

(HF = HIGH) by the appropriate rising edge of R. (See

Table 3.)

The Full F lag is as serted (FF = LOW) at the falling edge

of W for the write operation which fills the last available

location in the FIFO memory array. FF = LOW inhibits

further write oper ations until FF is cleared by a va lid r ead

RRSS

(for

operation. The Full Flag is deasser ted (FF = HIGH) after

the next rising edge of R releases anot he r mem ory lo cation. (See Table 3.)

Read

A read cycle is initiated by a falling edge of the Read

(R) control input. Read data becomes valid at the data

output s (Q0 – Q8) after a time tA from the falling e dge of

R. After R goes HIGH, the data outputs return to a

high-impedance stat e. Read oper ations m ay occur in dependently of any ongoing write operations. However, a

read operation is possible only i f the FIFO is not empty

(i.e., if the Empty Flag EF is HIGH).

The LH5402 03 ’s internal read-address and wri t eadd ress point er s oper ate in suc h a way that con secut ive

read operations always access data words in the same

order that they wer e written . The Empty Flag is asse rted

(EF = LOW) after that falling edge of R which accesses

the last available data word in the FIFO memory. EF is

deasserted (EF = HIGH) after the next rising edge of W

loads another valid data wor d. (See Table 3.)

Data Flow-Through

Read-data flow- throu gh mode occurs when the Read

(R) cont rol inpu t is brought LOW while the FIFO is empty ,

and is held LOW in antic ipation of a write cycle. At the end

of the next write cycle, the Empty F lag EF momentarily is

deasserted, and the data word just written becomes

available at the data outputs (Q0 – Q8) after a maximum time of t

+ tA. Additional write operations may occur

WEF

while the R input remains LOW; but only data from the

first write operation flows through to the data outputs.

Additional data words, if any, may be accessed only by

toggling R.

Write-data flow-through mode occurs when the Write

(W) input is brought LOW while t he FIFO is full, and is

held LOW in anticipation of a read cycle. At the end of the

read cycle, the Full Flag momentarily is deasserted, but

then immediately is reasserted in response to W being

held LOW. A data word is written into the FIFO on the

rising edge of W, which may occur no sooner than

t

RFF

+ t

after the read oper ation.

WPW

3

LH540203 CMOS 2048 × 9 Asynchronous FIFO

OPERATIONAL DESCRIPTI ON (cont’ d)

Retransmit

The FIFO can be made to reread previously-read data

by means of the Retransmit function. A retransmit operation is initiated by pulsing the

W must be deasserted (HIGH) for the duration of the

retransmit pulse. The FIFO’s internal read-address

pointer is reset to point to location zero, the first physical

memory location, while the internal write-address

pointer remains unchanged.

After a retransmit operation, those data words in the

region in between the read-address pointer and the

write-address pointer may be reaccessed by subsequent

read operations. A retransmit operation may affect the

state of the status flags

the relocation of the read-address pointer. There is no

restriction on the number of times that a block of data

within an LH540203 may be read out, by repeating the

retransmit operation and the subsequent read operations.

The maximum length of a data block which may be

retransmitted is 2048 words. Note that if the write-address

pointer ever ‘wraps around’ (i.e., passes location zero

more than once) during a sequence of retransmit operations, some data words will be lost.

RT input LOW. Both R and

FF, HF, and EF, depending on

Table 2. Expansion-Pin Usage Acco rding t o

Grouping Mode

I/O PIN

XI Grounded

I

STANDALONE

CASCADED

MASTER

From

(n-1st

CASCADED

XO

FIFO)

XI

XO/HF

O

FL/RT

I

Becomes

HF

Becomes

RT

To

(n+1st

FIFO)

Grounded

(Logic

LOW)

Table 3. Status Flags

NUMBER OF UNREAD DATA

WORDS PRESENT WITHIN

2048 × 9 FIFO

FF HF EF

0HHL

1 to 1024 H H H

1025 to 2047 H L H

SLAVE

From XO

(n-1st

FIFO)

To XI

(n+1st

FIFO)

Logic

HIGH

The Retransmit function is not available when the

LH540203 is operating in depth-cascaded mode,

because the

FL/RT control pin must be used for first-load

selection rather than for retransmission control.

Table 1. Grouping-Mode Determinatio n

During a Reset Operation

FL/

XI

RT

1

H

H

NOTES:

1. A re set operation forces XO HIGH for the n

2. The terms ‘master’ and ‘slave’ refer to opera tion in depth-cas-

3. H = HIGH; L = LOW; X = Don’t Care.

H

1

L

L

X

XI HIGH for the (n+1)st FIFO.

caded grouping mode.

MODE

Cascaded

2

Slave

Cascaded

Master

2

Standalone

XO/HF

USAGEXIUSAGE

XO XI FL

XO XI FL

HF (none) RT

th

FIFO, thus forcing

FL/RT

USAGE

2048 L L H

4

CMOS 2048 × 9 Asynchronous FIFO LH540203

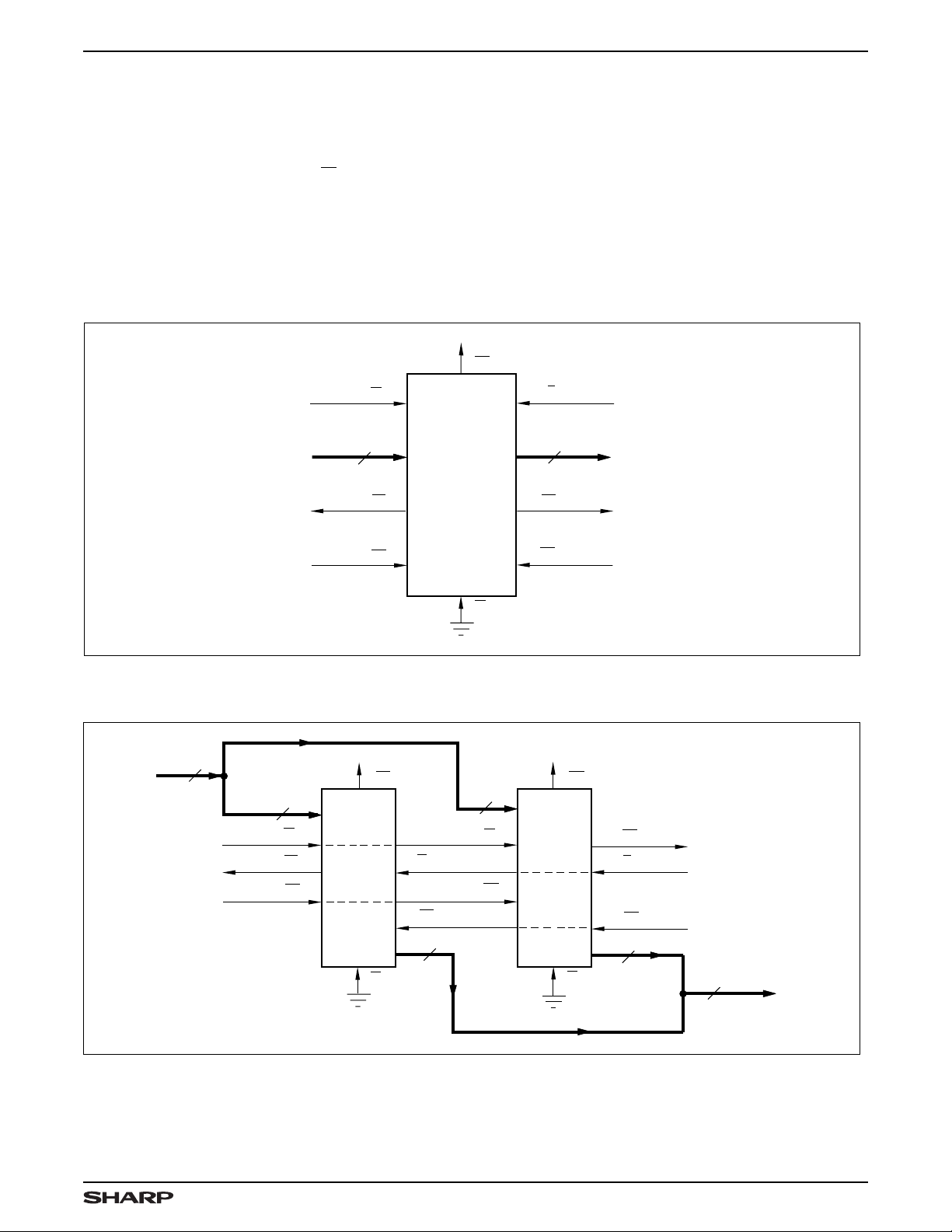

OPER ATIONAL MO DES

Standalo n e Configuration

When depth cascading is not required for a given

application, the LH540203 is placed in st anda lone mode

by tying the Expansion In input (XI) to gro und. This

input is interna lly samp led during a reset operatio n. (See

Table 1.)

WRITE

DATA IN

- D

D

0

FULL FLAG

8

W

9

LH540203

FF

Width Expansion

Word -width expansion is imp lemented by placing multiple LH540203 devices in parallel. Each LH540203

should be configured for standalone mode. In this arrangem ent, the behavior of the status flags is ident ical for

all devices; so, in principle, a representative value for

each of these flags could be der ived from any one device .

In practice, it is be tter to derive ‘composite’ flag values

using external logic, since there may be minor speed

variat ions between differe nt actua l devices. (See Figures

4, 5, an d 6 .)

HF

R

9

EF

READ

DATA OUT

Q

- Q

0

8

EMPTY FLAG

DATA IN

D

- D

0

17

18

WRITE

FULL FLAG

RESET

RESET

9

W

FF

RS

RS

XI

RT

Figur e 4. Standalone FI FO (2048 × 9)

HF

9

W

R

LH540203

RS

RT

9

XI

HF

LH540203

XI

RETRANSMIT

EF

R

RT

9

EMPTY FLAG

READ

RETRANSMIT

18

540203-17

DATA OUT

Q

- Q

0

17

Figure 5. FIFO Word-Width Expansion ( 2048 × 18)

540203-18

5

LH540203 CMOS 2048 × 9 Asynchronous FIFO

OPER ATIONAL MO DES (cont’d )

Depth Cascading

Depth cascading is implemented by configuring the

required nu mber of LH540203s in dept h-casca ded mode.

In this arrangem ent, the FIFOs are c onnected in a circular

fashion, with the Expansion Out output (XO) of each

device tied to the Expansion In input (XI) of the next

device. One FIFO in the c ascad e must be designat ed as

the ‘f irst - load’ device, by t ying its First Load input ( FL/RT)

to ground. Al l ot her devices m ust have th eir FL/R T inpu ts

tied HIGH. In this mode, W and R signals are share d by

all devices, while logic within each LH540203 controls the

steering of data. Only one LH540203 is enabled during

any given write cycle; thus, the common Data In inputs of

W

DATA IN

D

- D

0

9

8

9

FF

RS

LH540203

all devices are tied together. Likewise, only one

LH540203 is enabled during any given read cycle; thus,

the common Da ta Out outputs of all devices are wireORed toget her.

In depth-cascaded mode, external logic should be

used t o gene rate a composite F u ll Flag and a compos ite

Empty Flag, by ANDing the FF ou tputs of all LH540203

devices together and ANDing the EF outputs of all devices

together. Since FF and EF are assertive-LOW sign als ,

this ‘ANDing’ actually is implemented using an a sser tive-HIGH physical OR gate. The Half-Full Flag and the

Retr ansm it funct ion are not available in depth- casc aded

mode.

XO

R

9

EF

Vcc

FL

XI

XO

9

DATA OUT

Q

- Q

0

8

FULL

RS

9

FF

LH540203

RS

XI

XO

9

FF

LH540203

RS

XI

EF

FL

EF

FL

9

Vcc

9

Figur e 6. FIFO Depth Cascadi ng (6144 × 9)

EMPTY

540203-19

6

Loading...

Loading...