LH5324C00

CMOS 24M (1.5M × 16) MROM

FEATURES

•• 1,572 ,864 × 16 bit org ani zation

•• Access time: 120 ns (MAX.)

•• Supply curre nt:

– Operating: 80 mA (MAX.)

– Standby: 100 µA (MAX.)

•• TTL compatible I/O

•• Three-state output

•• Single +5 V Power supply

•• Stati c ope ration

•• When the address input at both A

19

an d

A

20

is high level, outputs become high

impedan ce irresp ective o f

CE or OE.

•• Package:

42-pin, 600-mil DIP

•• Others:

– Non programmab le

– Not de sign ed o r rate d as rad iatio n

ha rden ed

– CMOS process (P ty pe sil icon

substrate)

DESCRIPTION

The LH5324C00 is a 24M-bit mask-programmable

ROM organized as 1,572,864 × 16 bits. It is fabricated

usi ng sili con-gate CMOS process technology.

PIN CONNECTIONS

5324C00-1

TOP VIEW

2

3

4

5

8

9

A

2

A

5

39

38

37

36

35

34

31

28

A

7

A

6

6

7A

3

A

4

33

32

A

10

A

11

A

13

A

15

GND

D

14

10

11

12

41

40 A

9

A

1

13 30 D

15

29 D

7

OE

A

0

CE

A

12

42-PIN DIP

14

15

16

17

18

19

20

21

25

22

27

26

24

23

D

13

D

5

D

12

D

4

D

2

D

10

D

9

GND

D

8

D

1

D

0

D

3

D

11

V

CC

A

8

A

14

A

16

D

6

421

A

17

A

18

A

19

A

20

Figure 1. Pin Connecti ons

1

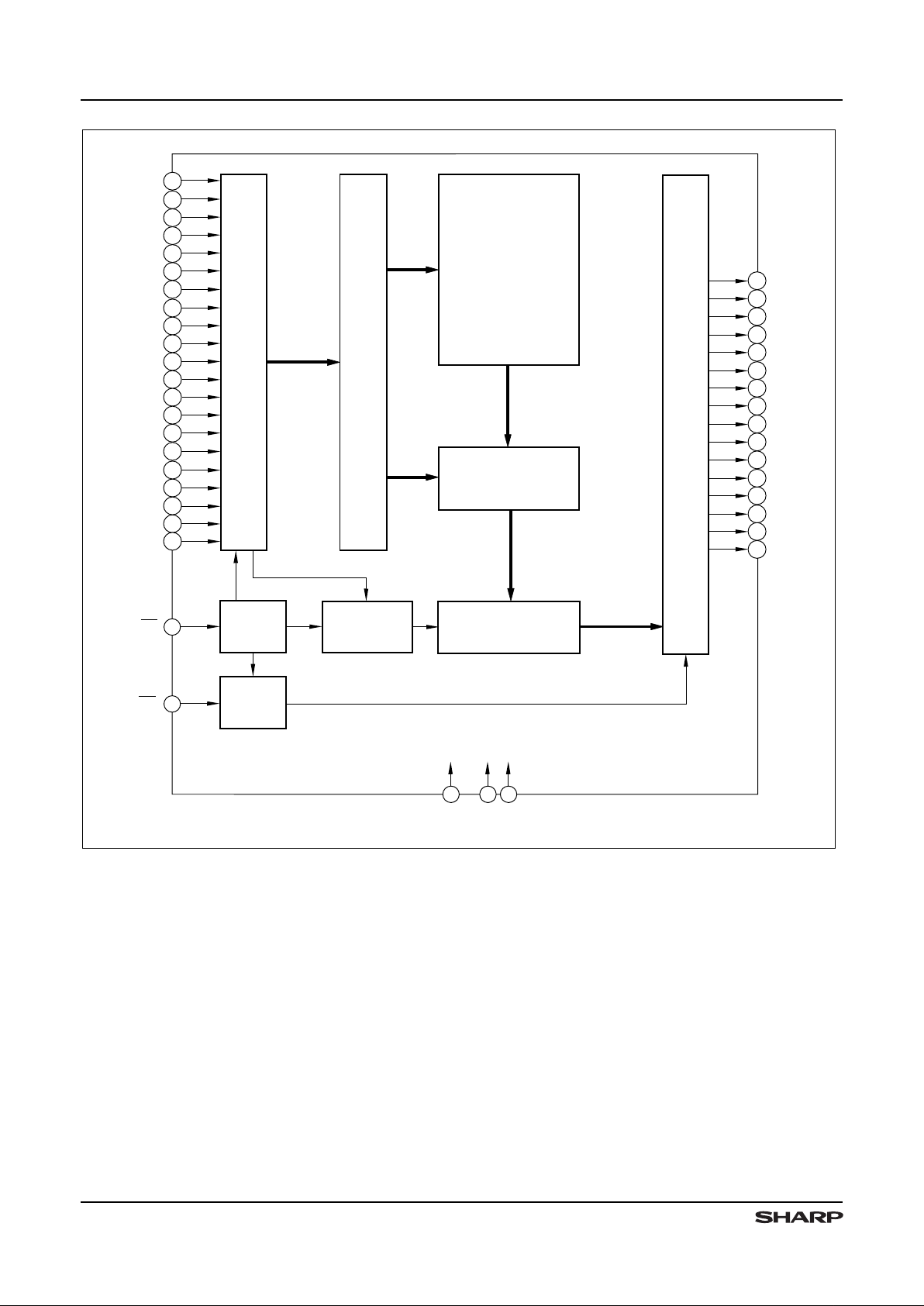

5324C00-2

A

3

A

2

A

1

A

12

A

11

A

10

A

9

A

8

A

7

A

6

V

CC

A

4

MEMORY

MATRIX

(1,572,864 x 16)

SENSE AMPLIFIER

GND

A

5

A

13

ADDRESS BUFFER

A

0

ADDRESS DECODER

COLUMN SELECTOR

CE

BUFFER

A

14

A

15

TIMING

GENERATOR

A

16

DATA SELECTOR/OUTPUT BUFFER

OE

BUFFER

OE

CE

A

17

A

19

A

18

A

20

37

38

39

40

4

7

8

9

3

6

41

5

36

10

35

34

33

2

42

1

32

11

13

22

31

12

D

3

D

2

D

1

D

7

D

6

D

4

D

5

D

0

25

18

16

14

20

29

23

27

D

11

D

10

D

9

D

15

D

14

D

12

D

13

D

8

26

19

17

15

21

30

24

28

Figure 2. LH5324C00 Block Diagram

PIN DESCRIPTION

SIGNA L PIN NAME

A0 - A

20

Addr ess in put

D

0

- D

15

Data ou tput

CE Chip en abl e in pu t

SIGNAL PIN NAME

OE Outpu t e nab le i np ut

V

CC

Power su ppl y ( +5 V)

GND Groun d

LH5324C 00 CMOS 2 4M (1 .5M x 16) MROM

2

Loading...

Loading...