Sharp LH532100BU, LH532100BT, LH532100BSR, LH532100BN, LH532100BD Datasheet

...

LH532100B

CMOS 2M (256K × 8) MROM

FEATURES

•• 262,144 words × 8 bi t organ izatio n

•• Access time: 150 ns (MAX.)

•• Low-pow er consumptio n:

Operating : 27 5 mW (MAX.)

Standb y: 550 µW (MAX.)

•• Static operation

•• Mask-programmable OE /

OE a nd

OE

1

/OE1/DC

•• TTL compatible I/O

•• Three-state outputs

•• Singl e +5 V p owe r su ppl y

•• Packa ges:

32-pi n , 600 -mil DIP

32-pi n , 525 -mil S OP

32-pi n , 450 -mil Q FJ (PLC C)

32-pi n , 8 × 20 mm

2

TSOP (Type I)

32-pin, 400-mil TSOP (Type II)

•• JEDEC stan dard EPROM pinout (DIP)

DESCRIPTION

The LH532100B is a 2M-bit mask-programmable

ROM organized as 262,144 × 8 bits. It is fabricated

using si licon-gate CMOS process technology.

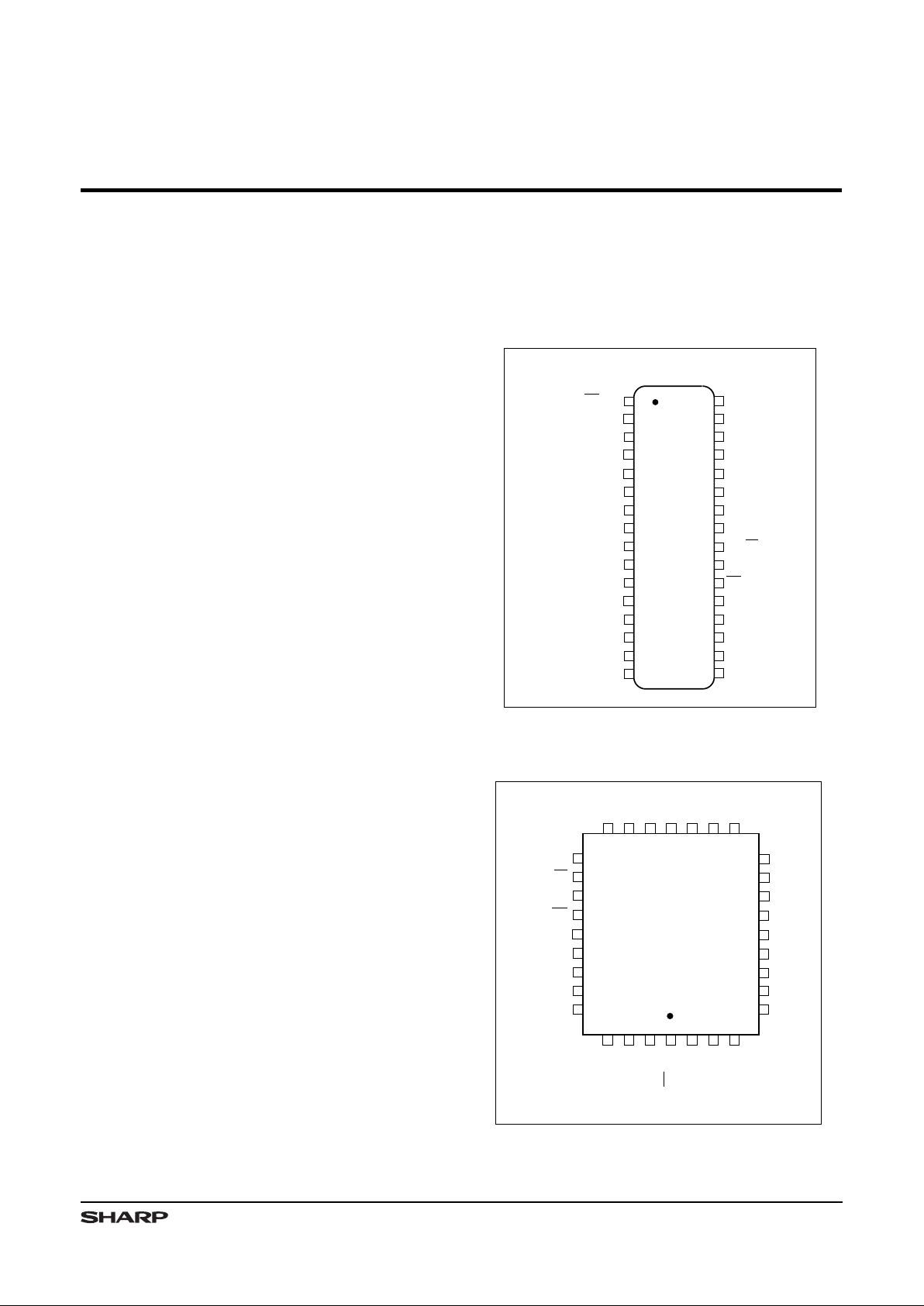

PIN CONNECTIONS

532100B-1

TOP VIEW

1

2

3

4

5

6

9

10

A

2

A

5

V

CC

28

27

26

25

24

23

20

17

A

7

A

6

7

8

A

3

A

4

22

21

A

15

A

12

GND

A

13

A

8

A

11

A

10

CE

D

7

D

6

D

3

11

12

13

32

31

30

29

A

14

A

1

14

15

16

19

D

5

18

D

4

D

1

D

2

A

0

D

0

A

9

A

16

OE/OE

32-PIN DIP

32-PIN SOP

OE1/OE1/DC

DC

A

17

Figure 1. Pin Connections for DIP and

SOP Packages

21

22

23

24

25

26

27

D

7

CE

A

10

A

9

A

8

13

12

11

10

9

8

D

0

A

0

A

1

A

2

A

5

5

30 31 32 4321

28

29

A

13

A

14

6

A

7

7

DC

17181920 16 15 14

D6D5D4D3GND

D2D

1

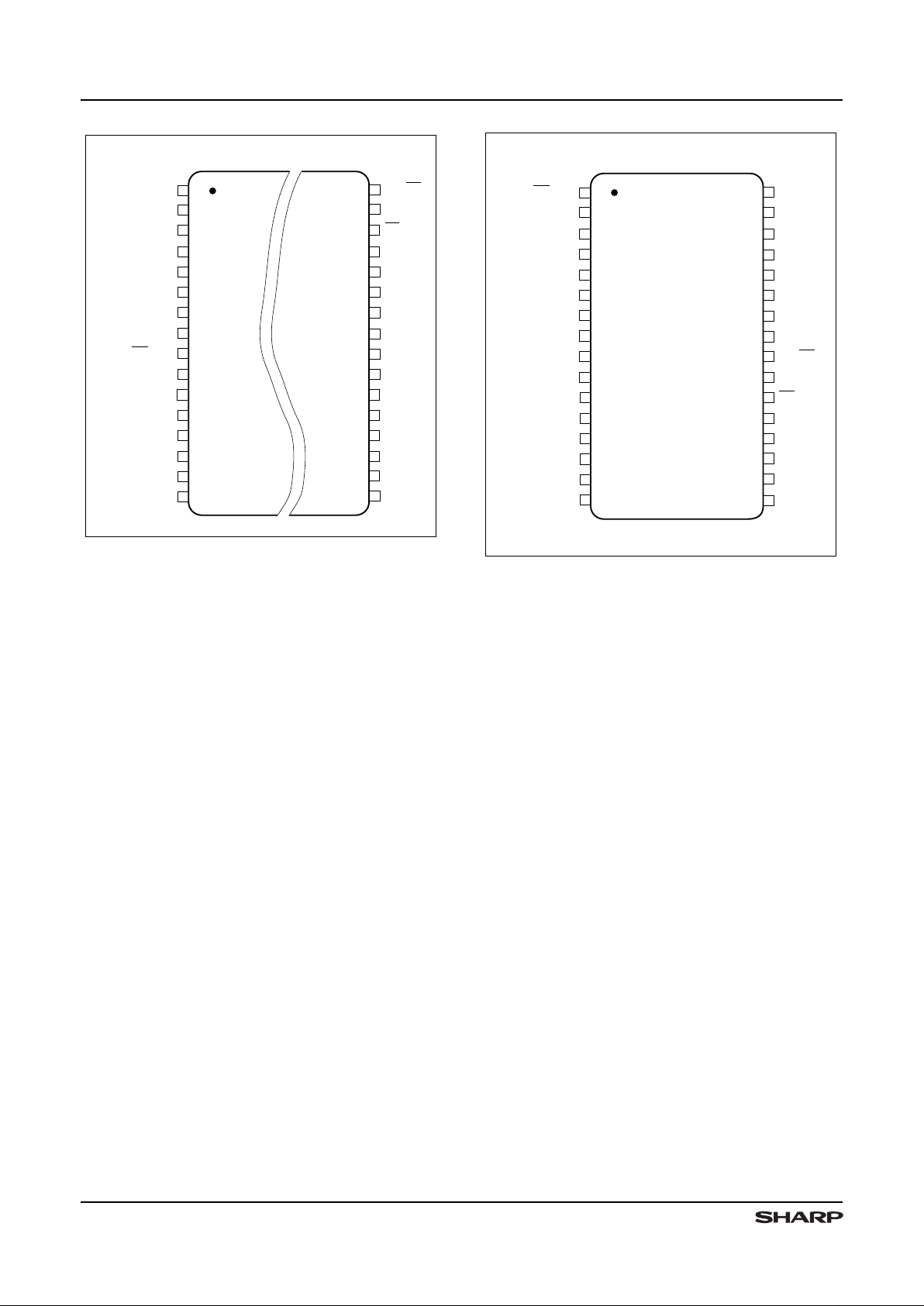

32-PIN QFJ TOP VIEW

532100B-7

OE/OE

A

11

A

3

V

CC

OE

1

/OE

1

/DC

A

16A15A12

A

17

A

4

A

6

Figure 2. P in Connections QFJ

(PLCC) Package

1

532100B-2

TOP VIEW

2

3

4

5

8

9

V

CC

A

14

29

28

27

26

25

24

21

18

A

8

A

13

6

7

23

22

D

7

A

2

10

11

12

31

30

A

16

13

20

19

OE

1

/OE1/DC

32-PIN TSOP (Type I)

14

15

16

17

A

3

32

1

A

9

A

10

D

6

D

4

D

3

GND

D

2

D

5

D

0

A

0

A

1

A

11

A

15

A

12

A

7

A

6

A

5

A

17

DC

OE/OE

CE

A

4

D

1

Figure 3. Pin Connect ions for TSOP

(Type I) P ackage

1

2

3

4

7

8

A

7

30

29

28

27

26

25

22

19

A

15

A

12

5

6

A

6

24

23

A

16

DC

A

14

A

8

A

10

CE

D

5

9

10

11

32

31

12

21

D

7

20

D

6

A

0

D

0

A

2

A

1

A

13

13

14

A

9

532100B-3

TOP VIEW32-PIN TSOP (Type II)

NOTE: Reverse bend available on request.

D

1

D215

16

GND

17

D

3

18

D

4

OE/OE

A

11

OE1/OE1/DC

A

5

A

4

A

3

A

17

V

CC

Figure 4. Pin Connections for TSOP

(Type II) Packages

LH532100B CMOS 2M MROM

2

NOTE:

1. Active levels of OE/OE and OE1/OE1/DC are mask-program mable.

Select ing DC a llows the outputs to be act ive f or both high and low levels applied to this pin.

It is recommended to apply either a HIGH or a LOW to t he DC pin.

TRUTH TABLE

CE OE/OE OE1/OE

1

MODE D0 – D

7

SUPPLY CURRENT

H X X Non selected High-Z Standby (ISB)

L L/H X Non selected High-Z Operating (I

CC

)

L X L/H Non selected High-Z Operating (I

CC

)

L H/L H/L Selected D

OUT

Operating (ICC)

NOTE:

X = H or L

532100B-4

A

3

A

2

A

1

A

12

A

11

A

10

A

9

A

8

32

4

25

23

26

6

9

10

11

A

7

A

6

V

CC

A

4

18 19 2013 21

D

0

MEMORY

MATRIX

(262,144 x 8)

SENSE AMPLIFIER

OUTPUT BUFFER

16

5

GND D

1D2D3D4D5D6D7

1714 15

8

27

A

5

7

A

13

28

ADDRESS BUFFER

CE/CE

A

0

12

ADDRESS DECODER

COLUMN SELECTOR

CE

BUFFER

OE

BUFFER

A

14

29

A

15

3

22

TIMING

GENERATOR

A

16

2

OE1/OE1/DC

A

17

30

24

OE/OE

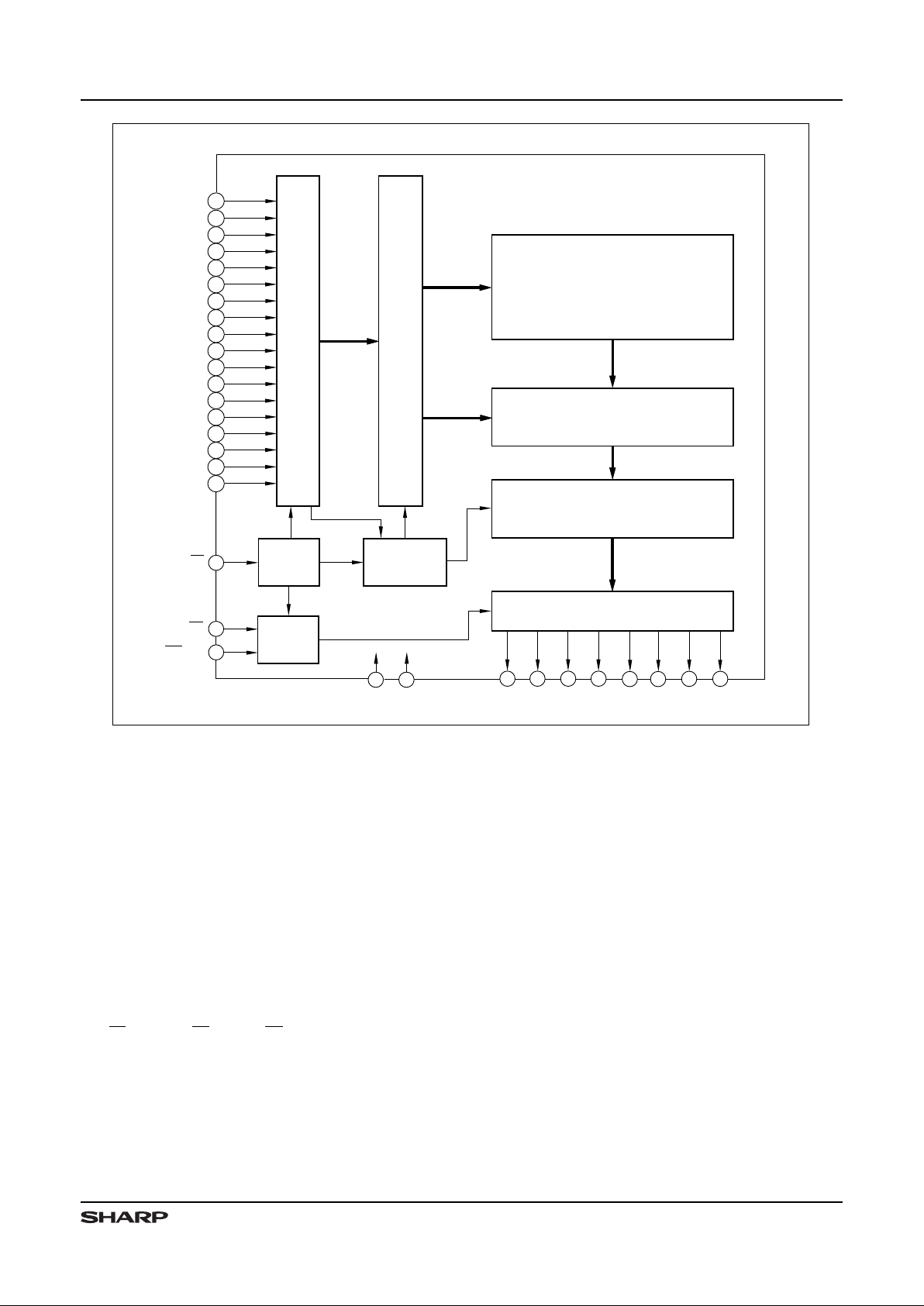

NOTE: Pin numbers apply to the 32-pin DIP, SOP, QFJ, or TSOP (Type II).

1

Figure 5. LH532100B Block Diagram

PIN DESCRIPTI ON

SIGNAL PIN NAME NOTE

A0 – A

17

Addr ess in put

D

0

– D

7

Data ou tput

CE Chip En abl e i npu t

OE/

OE Outp ut E nab le inp ut 1

SIGNAL PIN NAME NOTE

OE1/OE1/DC

Outpu t E nab le inp ut/

Don’t Ca re c on nec tio n

1

V

CC

Power su ppl y ( +5 V)

GND Groun d

CMOS 2M MROM LH532100B

3

Loading...

Loading...