Sharp LH532000BT, LH532000BD Datasheet

LH532000B

FEATURES

•• 262,144 words × 8 bi t organ izatio n

(Byte mode)

131,072 w ords × 16 bit orga niza tio n

(Word mode)

••

BYTE input pin selects bit configu ration

•• Access times: 120/150 ns (MAX.)

•• Low-pow er consumptio n:

Operating : 27 5 mW (MAX.)

Standb y: 550 µW (MAX.)

•• Programmabl e OE /

OE and OE1/OE1/DC

•• Static operation

•• TTL compatible I/O

•• Three-state outputs

•• Singl e +5 V p owe r su ppl y

•• Packa ges:

40-pi n , 600 -mil DIP

40-pi n , 525 -mil S OP

48-pi n , 1 2 × 18 mm

2

TSOP (Type I)

••×16 word-wide pinout

DESCRIPTION

The LH532000B is a 2M-bit mask-programmable

ROM with two programmable memory organizations,

byte and word m odes. It is fabricated using silicon-gate

CMOS process technology.

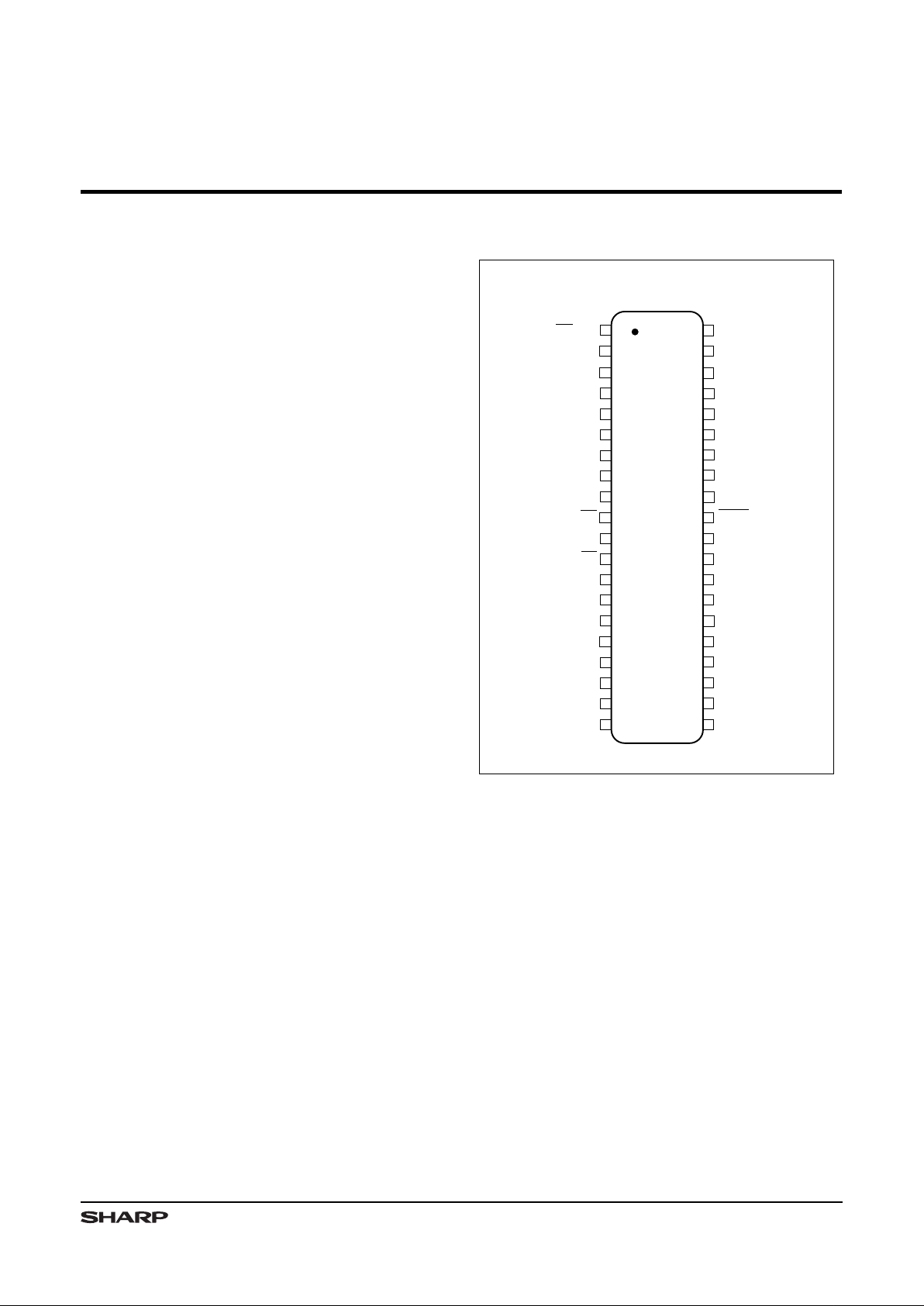

PIN CONNECTIONS

CMOS 2M (256K × 8/1 28K × 16) MROM

532000B-1

TOP VIEW

1

2

3

4

7

8

A

2

A

5

48

37

36

35

34

33

30

27

A

7

A

6

5

6

A

3

A

4

32

31

OE

1

/OE1/DC

A

10

A

11

A

13

A

15

BYTE

GND

D

14

9

10

11

40

39

A

9

A

1

12

29

D15/A

-1

(LSB)

28

D

7

OE/OE

A

0

CE

A

12

40-PIN DIP

40-PIN SOP

13

14

15

16

17

18

19

20

24

21

26

25

23

22

D

13

D

5

D

12

D

4

D

2

D

10

D

9

GND

D

8

D

1

D

0

D

3

D

11

V

CC

A

8

A

14

A

16

D

6

Figure 1. Pin Connections for DIP and

SOP Packages

1

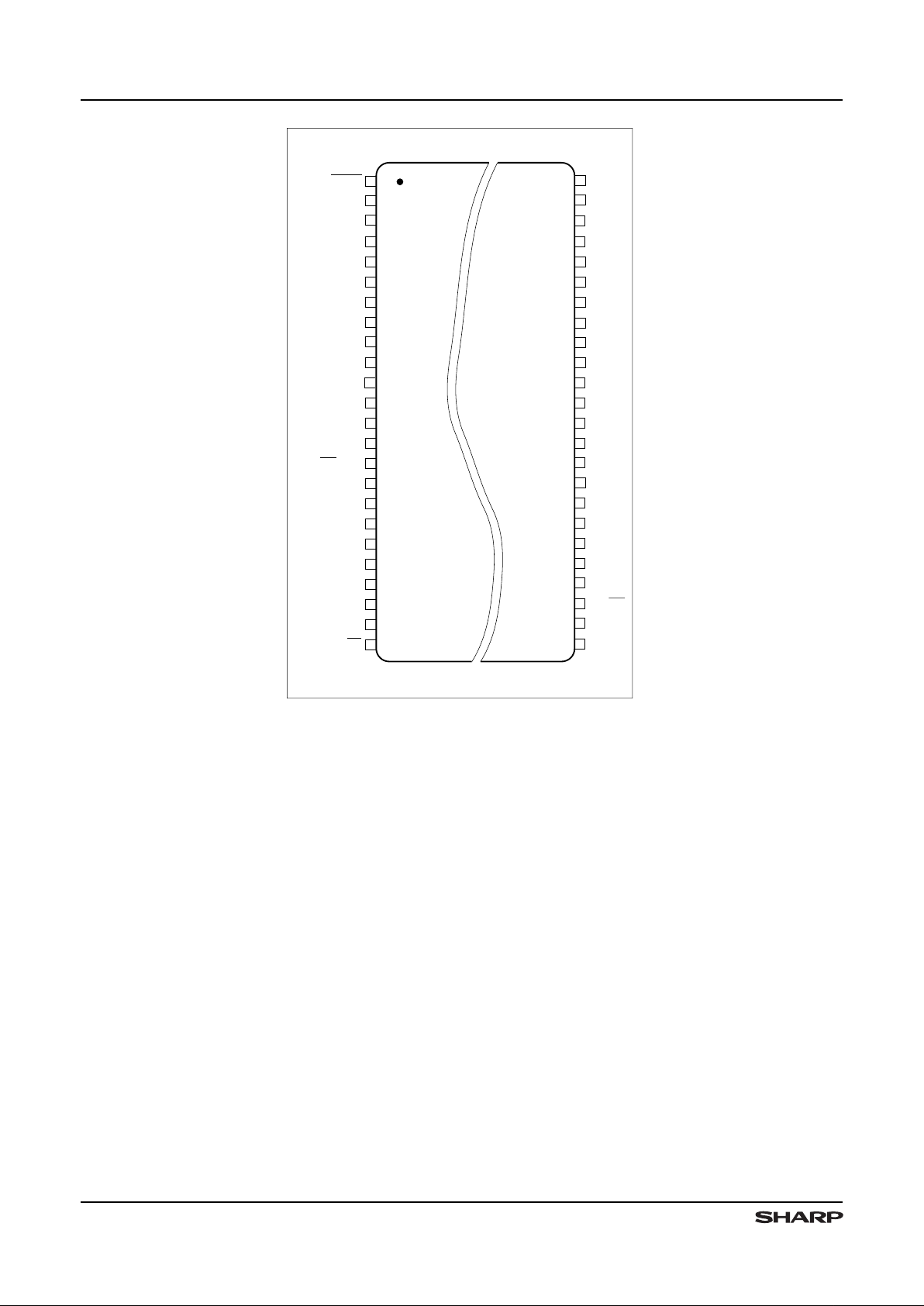

532000B-5

TOP VIEW

2

3

4

5

8

9

A

10

A

13

45

44

43

42

41

40

37

34

A

15

A

14

6

7

A

11

A

12

39

38

D

7

D

3

10

11

12

47

46

D

15/A-1

A

9

13

36

35

A

8

48-PIN TSOP (Type I)

14

15

16

17

18

19

20

21

31

28

33

32

30

29

D

2

D

9

D

1

D

8

OE/OE

D

10

GND

48

1

A

16

BYTE

22

27

D

0

GND

23

26

V

CC

24

25

GND

A

7

A

6

A

5

A

4

A

3

A

2

A

1

A

0

CE

GND

D

14

D

13

D

5

D

12

D

4

D

6

V

CC

GND

D

11

GND

NC

NC

NC

OE

1

/OE1/DC

NOTE: Reverse bend available on request.

Figure 2. Pin Connections for TSOP Package

LH532000B CMOS 2M MROM

2

NOTES:

1. D15/A–1 pin becomes LSB address input (A–1) when the bit configuration is set in byte mode,

and data output (D15) when in word mode. BYTE input pin se lects bit configur at ion.

2. The active levels of OE/

OE and OE1/OE1/DC are mask-program mable.

Select ing DC a llows the outputs to be act ive f or both high and low levels applied to this pin.

It is recommended to apply either a HIGH or a LOW to t he DC pin.

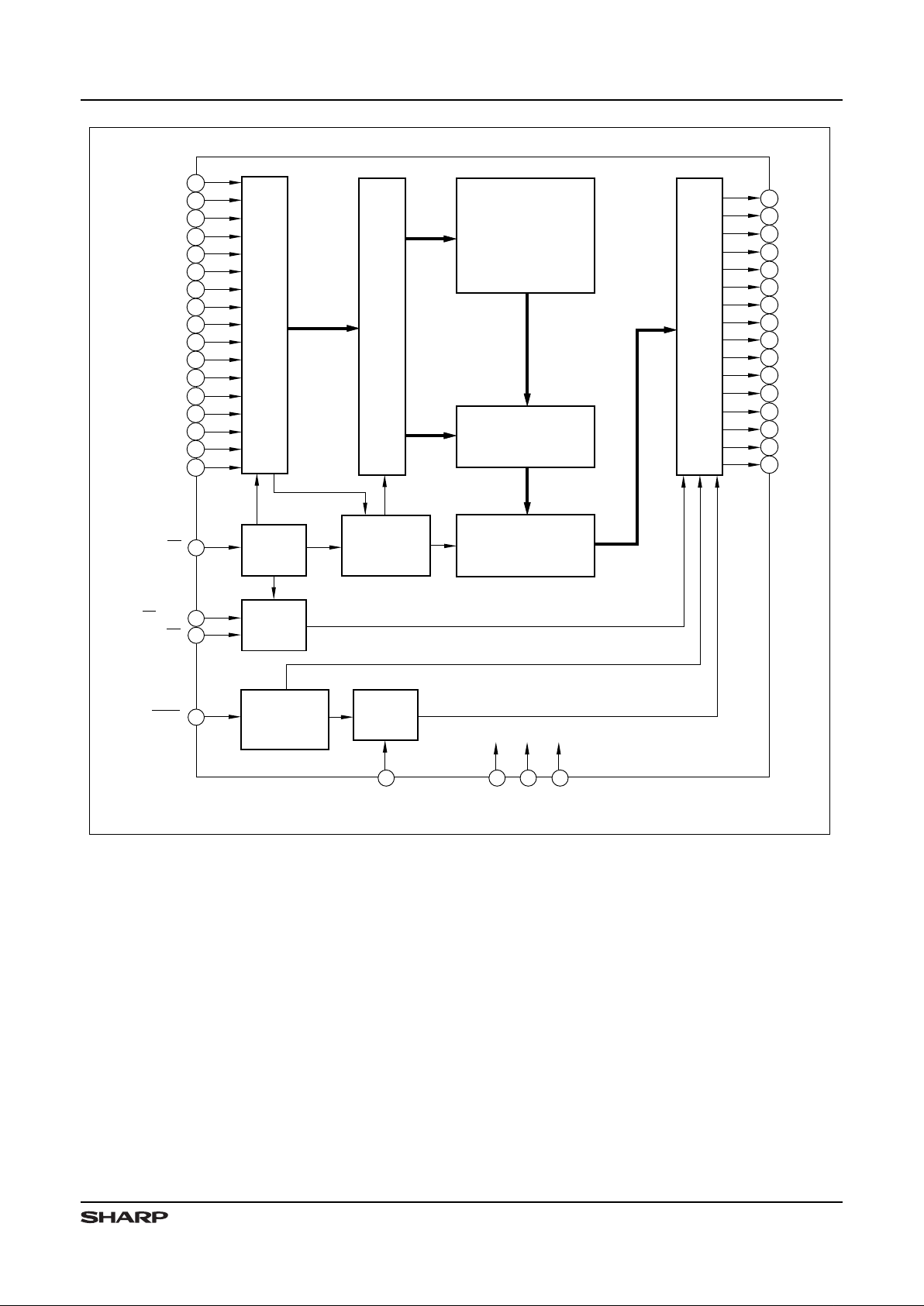

532000B-2

A

3

A

2

A

1

A

12

A

11

A

10

A

9

A

8

29

A

7

A

6

V

CC

A

4

MEMORY

MATRIX

(262,144 x 8)

(131,072 x 16)

SENSE AMPLIFIER

GND

A

5

A

13

ADDRESS BUFFER

A

0

ADDRESS DECODER

COLUMN SELECTOR

CE

BUFFER

A

14

A

15

TIMING

GENERATOR

A

16

NOTE: Pin numbers apply to the 40-pin DIP or SOP.

A

-1

D

3

D

2

D

1

D

12

D

11

D

10

D

9

D

8

D

7

D

6

D

4

D

5

D

13

D

0

D

14

D

15

DATA SELECTOR/OUTPUT BUFFER

21 11

30

OE

BUFFER

ADDRESS

BUFFER

BYTE/WORD

SWITCHOVER

CIRCUIT

31

OE1/OE1/DC

OE/OE

CE

BYTE

10

12

1

3

6

7

8

5

4

9

36

37

38

39

2

40

35

34

33

32

20

18

16

14

24

17

15

13

26

19

28

22

23

25

27

29

Figure 3. LH532000B Block Diagram

PIN DESCRIPTION

SIGNA L PIN N AME NOT E

A

–1

Addre ss input (BY TE mode) 1

A

0

– A

16

Addre ss inp ut

D

0

– D

15

Data out put 1

CE Chip ena ble in put

OE/

OE Outpu t e nab le inp ut 2

SIGNAL PIN NAME NO TE

OE1/OE1/DC

Outpu t en abl e i npu t o r

Don’t ca re

2

BYTE Byte/ wor d mo de swi tch

V

CC

Power su ppl y (+ 5 V)

GND Ground

CMOS 2M MROM LH532000B

3

Loading...

Loading...