SGS Thomson Microelectronics ST72T752J6B1, ST72E752J6D1, ST72752J6, ST72752J5, ST72752J4 Datasheet

...

R

ST72752

8-BIT MCU FOR MONITORS WITH UP T O 32K ROM, 1K RAM, ADC,

2

TIMER, SYNC, PWM/BRM, DDC/DMA & I

■

User ROM/OTP/EPROM: up to 32 Kbytes

■

Data RAM: up to 1 Kbytes (256 bytes stack)

■

8 MHz Maximum Internal Clock Frequency in

fast mode, 4 MHz in normal mode

■

Run, Wait and Halt CPU modes

■

Sync Processor for Mode Recognition, power

management and composite video blanking,

clamping and free-running frequency

generation.

– Corrector mode

– Analyzer mode

■

Fast I2C Multi Master Interface

■

DDC Bus Interface fully compliant with DDC1,

2B, 2B+, 2AB, 2Bi standards

■

23 I/O lines

– 1 high current I/O (10 mA)

– Up to 5 high voltage outputs (9V)

■

16-bit timer with 2 in put captures an d 2 output

compare functions (with 1 output pin)

■

8-bit Analog to Digital Converter with 4

channels on port B

■

8 10-bit PWM/BRM Digital to Analog outputs

■

One 12-bit PWM/BRM Digital to Analog output

■

Master Reset and Power on/off reset1

■

Programmable Watchdog for system reliability

■

42-pin Shrink Dual In line Plastic package

■

Fully static operation

■

0 to + 70 oC Operating Temperature Range

■

4.0V to 5.5V supply operating range

■

24 MHz Quartz Oscillator

■

63 basic instructions/17 main address modes

■

8x8 unsigned multiply instruction

■

True bit manipulation

■

Versatile Development Tools (DOS and

Windows) including assembler, linker, Ccompiler, archiver, source level debugger,

programmer, and hardware emulator

BRIEF DATA

PSDIP42

See Ordering Information at the end of the Document

Device Summary

Features ST72752J6 ST72752J5 ST72752J4

ROM

(bytes)

RAM

(bytes)

ADC 4 channels

Timer 1

2

I

C Bus one multimaster

DDC/DMA yes

Sync yes

PWM 9

I/O 23

EPROM

Device

OTP

Device

32K 24K 16K

1K 768 512

ST72E752J6D1

ST72T752J6B1

C

Note 1

: Power On/Off reset not implemented in

this revision.

April 1998 1/3

This is preliminary information on a new product in development or undergoing evaluation. Details are subject to change without noti ce.

1

ST72752

1 GENERAL DESCRIPTION

1.1 INTRODUCTION

The ST72752 is a HCMOS microcontroller unit

(MCU) from the ST7 family with dedicated peripherals for Monitor applications.

It is based around an indu stry standard 8-bi t core

and offers an enhanced i nstruction set. The processor runs with an external clock at 24 MHz with

a 5V supply. Due to the fully static de sign of this

device, operation down to DC is possible. Under

software control the ST72752 can be placed in

WAIT or HALT mode thus reducing power consumption. The enhanced instruction set and addressing modes afford real programming potential.

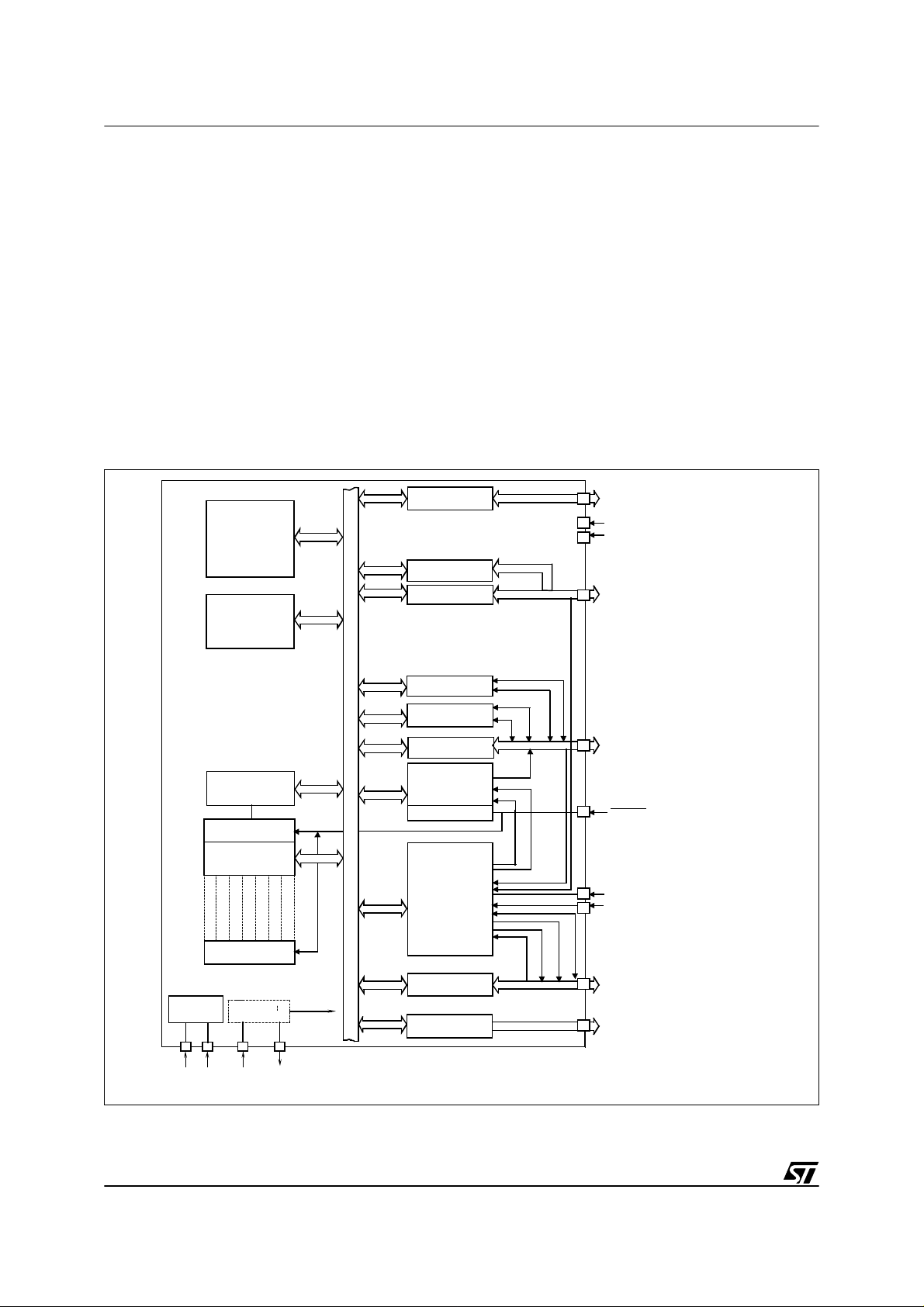

Figure 1. .ST72752 Block Diagram

PORT A

1K Bytes

A

Y

X

C

C

INTERNAL

CLOCK

PORT B

S

E

S

U

B

A

T

A

D

/

S

S

E

R

D

D

A

PORT C

PORT C

TIMER

WATCHDOG

SYNC

PROCES SOR

PORT D

PWM/BRM

Up to

CONTROL

8-BIT CORE

POWER ON/OFF

POWER

SUPPLY

32K Bytes

ROM/

EPROM/OTP

Up to

RAM

DDC DMA

ALU

L

H

C

C

P

P

P

S

OSC /3 or 6

In addition to standard 8-bit data management the

ST7 features true bit manipulation, 8x8 unsigned

multiplication and indirect addressing modes.

The device includes an on-chip oscillator, CPU,

Sync Processor for video timing & Vfbac k analysis, up to 32K ROM, up to 1K RAM, I/O, a timer

with 2 input captures and 2 o utput compares , a 4channel Analog to Digital Converter, DDC/DMA,

2

C multi Master, Watchdog Reset, and one 12-bit

I

and eight 10-bit PWM/BRM outputs for analog DC

control of external functions.

PA1(HV)

PA3..6(HV)

PA7/BLANKOUT

V

DDA

V

SSA

ADC

I²C

DDC

AIN 0..2, AIN7

SCLD

SDAD

OCMP

C

N

C

Y

N

S

Y

C

/

S

V

H

I

C

N

Y

S

C

PB7/AIN7

PB1..2/ AI N1 ..2

PB0

/

VFBACK/AIN0

VFBACK

I

I

A

L

D

S

O

O

C

C

N

N

Y

Y

S

S

V

H

PC6 (HC)

C

S

PC5/SDAI

PC4/SCLI

PC3/SDAD

PC2/RX/SCLD

PC0/OCMP/HFBACK

RESET

K

C

A

B

F

H

VSYNCI

HSYNCI

T

U

PD6/CLAMPOUT

O

PD5/ITA

P

M

PD4/ITB

A

L

PD3/ITC

C

PD2/VSYNCO

PD1/HSYNCO

PD0/CSYNCI

DA0

DA1,DA8

2/3

V

V

DD

SS

OSCOUTOSCIN

VR01735R

Loading...

Loading...