SGS Thomson Microelectronics M29F010B70K1, M29F010B45N1, M29F010B45K1, M29F010B, M29F010B70P1 Datasheet

...

1/20

PRELIMINARY DATA

July 1999

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

M29F010B

1 Mbit (128Kb x8, Uniform Block) Single Supply Flash Memory

■ SINGLE 5V±10% SUPPLY VOLTAGE for

PROGRAM, ERASE and READ OPERATIONS

■ ACCESS TIME: 45ns

■ PROGRAMMING TIME

–8µs per Byte typical

■ 8 UNIFORM 16Kbytes MEMORYBLOCKS

■ PROGRAM/ERASE CONTROLLER

– Embedded Byte Program algorithm

– Embedded Multi-Block/Chip Erase algorithm

– Status Register Polling and Toggle Bits

■ ERASE SUSPEND and RESUME MODES

– Read and Program another Block during

Erase Suspend

■ UNLOCKBYPASS PROGRAM COMMAND

– Faster Production/Batch Programming

■ LOW POWER CONSUMPTION

– Standby andAutomatic Standby

■ 100,000 PROGRAM/ERASE CYCLESper

BLOCK

■ 20 YEARS DATA RETENTION

– Defectivity below 1 ppm/year

■ ELECTRONIC SIGNATURE

– Manufacturer Code: 20h

– Device Code: 20h

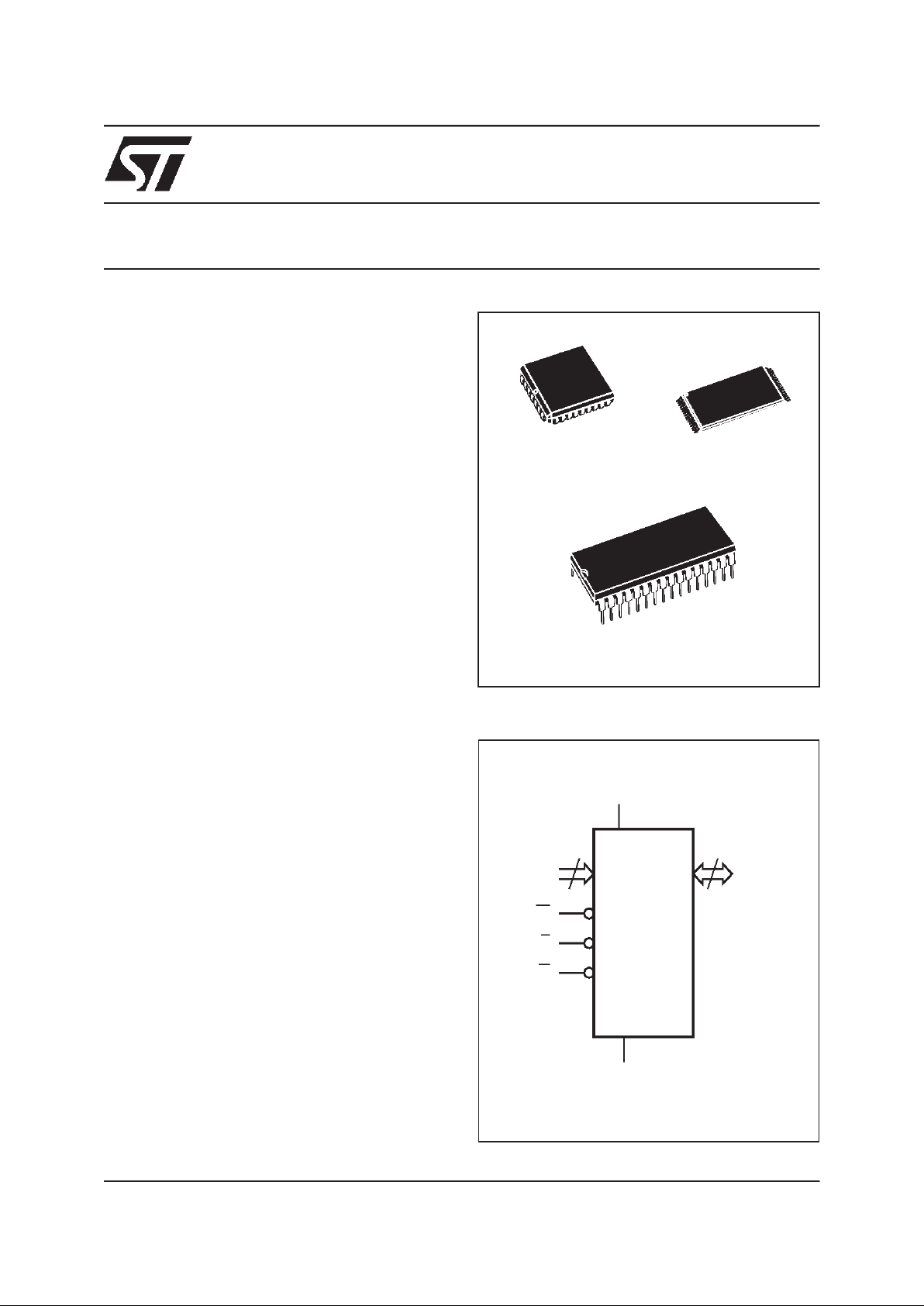

32

1

TSOP32 (N)

8 x 20mm

PLCC32 (K)

PDIP32 (P)

Figure 1. Logic Diagram

AI02735

17

A0-A16

W

DQ0-DQ7

V

CC

M29F010B

E

V

SS

8

G

M29F010B

2/20

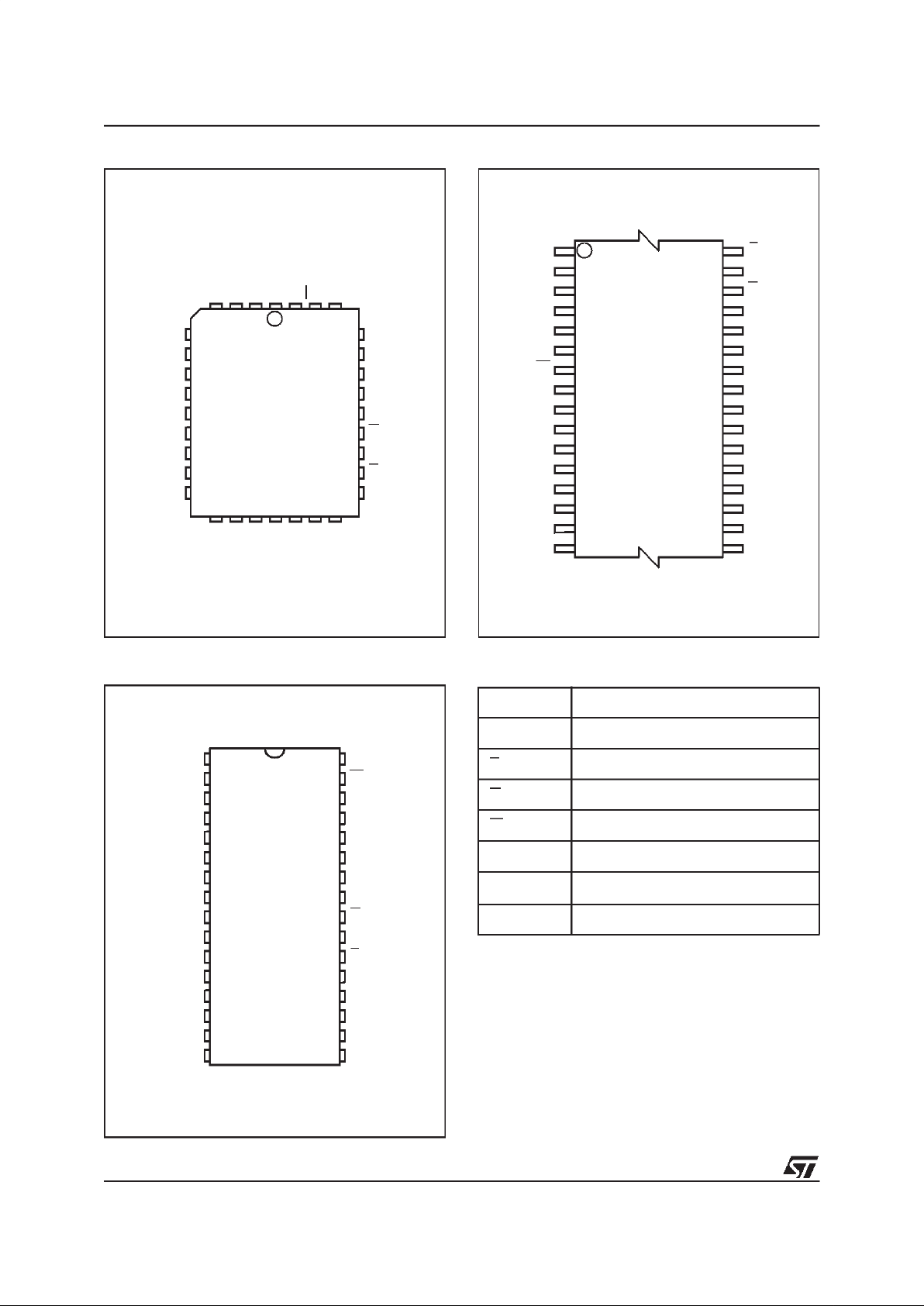

Figure 2A. PLCC Connections

AI02737

NC

A13

A10

DQ5

17

A1

A0

DQ0

DQ1

DQ2

DQ3

DQ4

A7

A4

A3

A2

A6

A5

9

W

A8

1

A16

A9

DQ7

A12

A14

32

NC

V

CC

M29F010B

A15

A11

DQ6

G

E

25

V

SS

Figure 2B. TSOP Connections

A1

A0

DQ0

A7

A4 A3

A2

A6

A5

A13

A10

A8

A9

DQ7

A14

A11 G

E

DQ5

DQ1

DQ2

DQ3

DQ4

DQ6

NC

W

A16

A12

NC

V

CC

A15

AI02738

M29F010B

8

1

9

16 17

24

25

32

V

SS

Figure 2C. PDIP Connections

A1

A0

DQ0

A7

A4

A3

A2

A6

A5

A13

A10

A8

A9

DQ7

A14

A11

G

E

DQ5DQ1

DQ2

DQ3V

SS

DQ4

DQ6

NC

WA16

A12

NC V

CC

A15

AI02736

M29F010B

8

1

2

3

4

5

6

7

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

Table 1. Signal Names

A0-A16 Address Inputs

DQ0-DQ7 Data Inputs/Outputs

E Chip Enable

G Output Enable

W Write Enable

V

CC

Supply Voltage

V

SS

Ground

NC Not Connected Internally

SUMMARY DESCRIPTION

The M29F010B is a 1Mbit (128Kb x8) non-volatile

memory that can be read, erased and reprogrammed. Theseoperations canbe performedusing a single 5V supply. On power-up the memory

defaults to its Read mode where it can be read in

the same way as a ROM or EPROM.

The memory is divided into blocks that can be

erased independently so it is possible to preserve

3/20

M29F010B

valid data while old data is erased. Eachblock can

be protected independently to prevent accidental

Program or Erase commands from modifying the

memory. Program and Erase commands are written to the Command Interface of the memory. An

on-chip Program/Erase Controller simplifies the

process ofprogramming orerasing the memory by

taking care of all of the special operations that are

required to update the memory contents. The end

of a program or erase operation can be detected

and any error conditions identified. The command

set required to control the memory is consistent

with JEDEC standards.

Chip Enable, OutputEnable andWrite Enable signals control the bus operation of the memory.

They allow simple connection to most microprocessors, often without additional logic.

The memory is offered in PLCC32, TSOP32 (8 x

20mm) and PDIP32 packages. Access times of

45ns, 70ns, 90ns and 120ns are available. The

memory is supplied with all the bits erased (set to

’1’).

SIGNAL DESCRIPTIONS

See Figure 1, Logic Diagram, and Table 1, Signal

Names, for a brief overview of thesignals connected to this device.

Address Inputs (A0-A16). The Address Inputs

select the cells in the memory array to access during Bus Read operations. During BusWrite operations they control the commands sent to the

Command Interface of the internal state machine.

Data Inputs/Outputs (DQ0-DQ7). The Data Inputs/Outputs output thedata storedat the selected

address during a Bus Readoperation. During Bus

Write operations they represent the commands

sentto theCommand Interface ofthe internal state

machine.

Chip Enable (E). The Chip Enable, E, activates

the memory, allowing BusRead and Bus Write operations to be performed. When Chip Enable is

High, VIH, all other pins are ignored.

Output Enable (G). The Output Enable, G, controls the Bus Read operation of the memory.

Write Enable (W). The WriteEnable, W, controls

the Bus Write operation of the memory’s Command Interface.

VCCSupply Voltage. The VCCSupply Voltage

supplies the power for all operations (Read, Program, Erase etc.).

The Command Interface is disabledwhen the V

CC

Supply Voltage is less than the Lockout Voltage,

V

LKO

. Thisprevents Bus Write operationsfrom accidentally damaging the data during power up,

power down and power surges. If the Program/

Erase Controller is programming orerasing during

this time thenthe operation aborts and the memory contents being altered will be invalid.

A 0.1µF capacitor should be connected between

the VCCSupply Voltage pin and the VSSGround

pin to decouplethe current surges from the power

supply. The PCB track widthsmust be sufficient to

carry the currents required during program and

erase operations, I

CC4

.

Vss Ground. The VSSGround is the reference

for all voltage measurements.

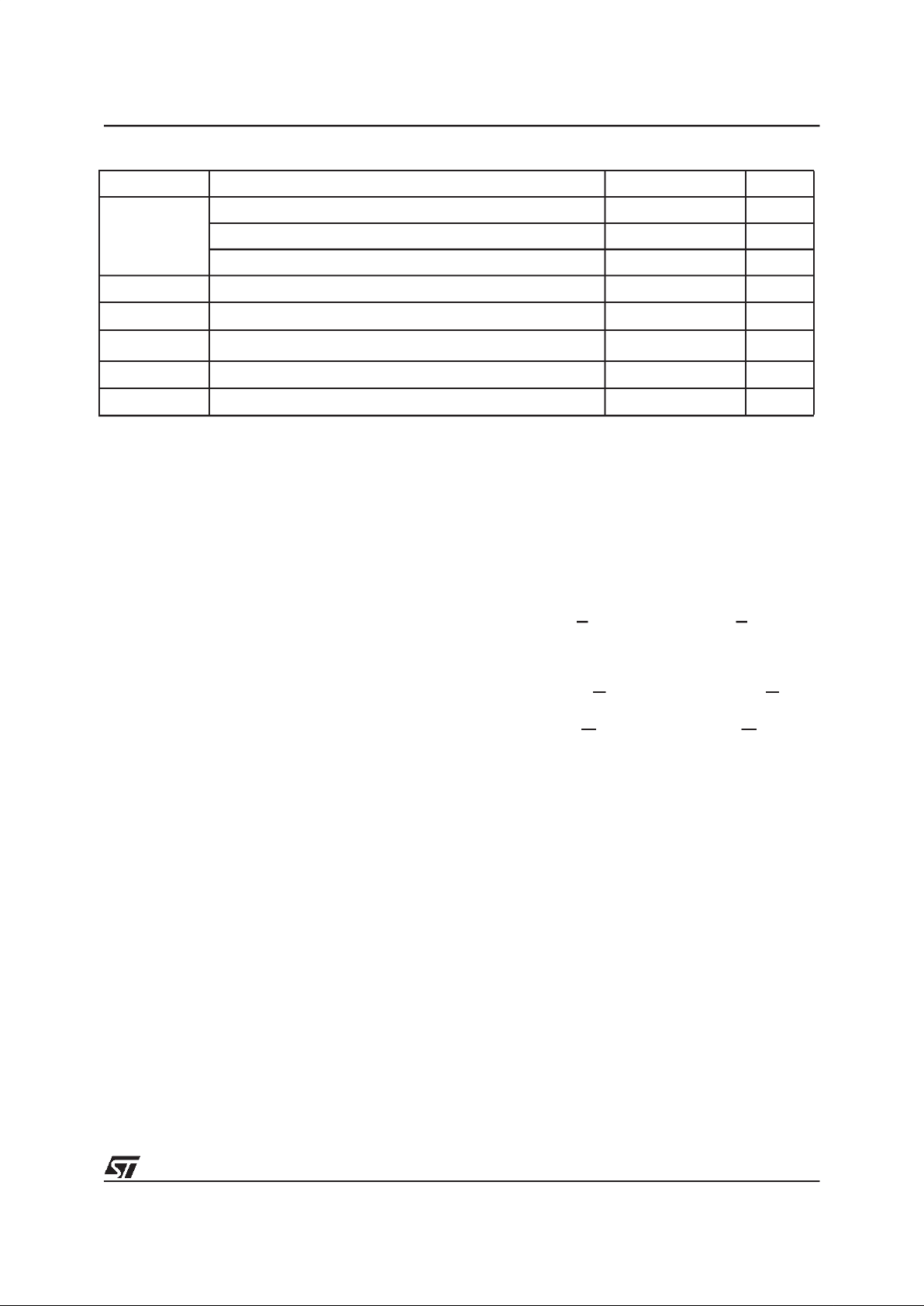

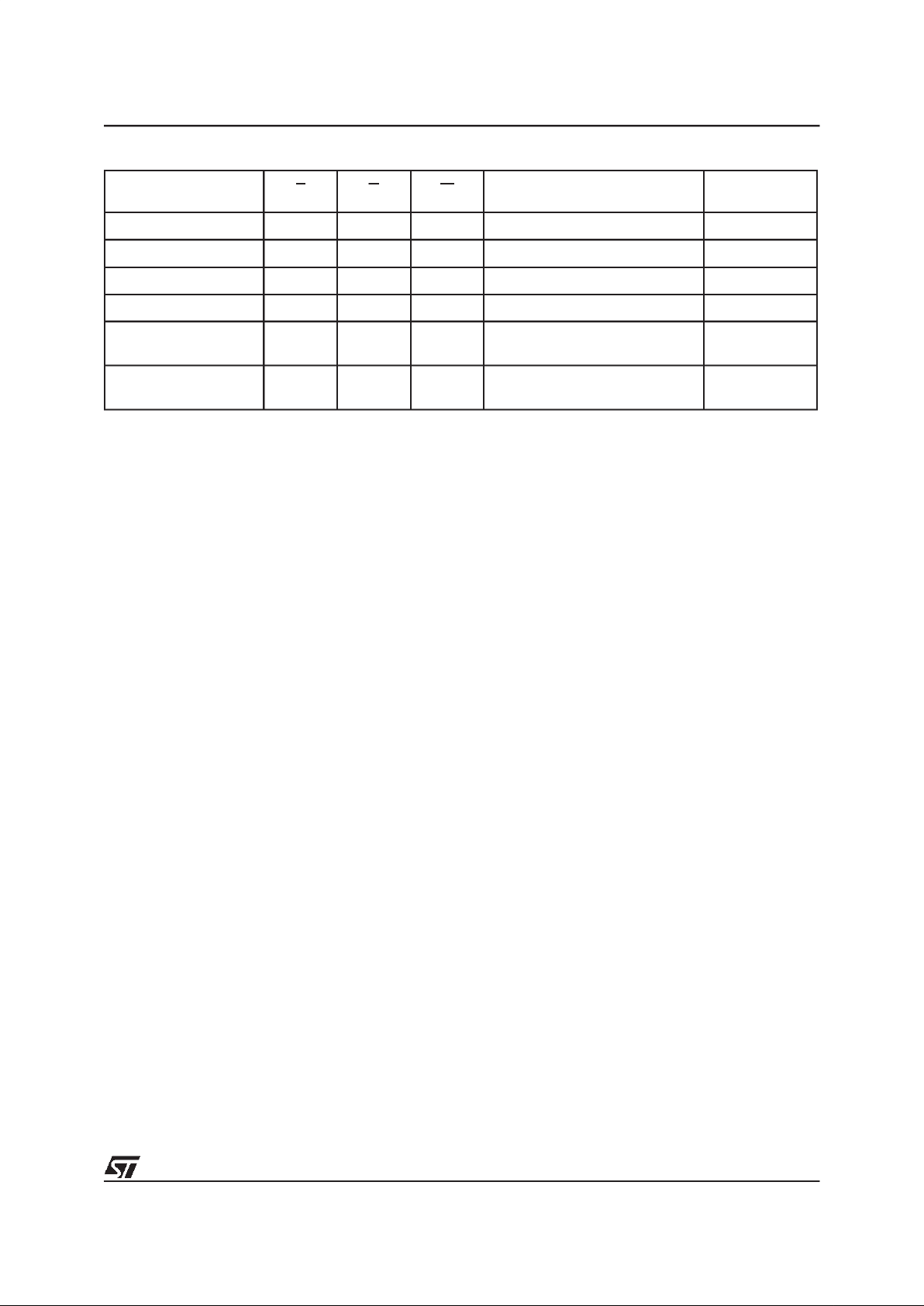

Table 2. Absolute Maximum Ratings

(1)

Note: 1. Except for the rating ”Operating Temperature Range”, stresses above those listed in the Table ”Absolute Maximum Ratings” may

cause permanent damage to the device. These are stress ratings only and operation of the device atthese or any other conditions

above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions forextended periods may affect device reliability. Refer also tothe STMicroelectronics SURE Program and other relevantquality documents.

2. Minimum Voltage may undershoot to –2V during transition and for less than 20ns during transitions.

Symbol Parameter Value Unit

T

A

Ambient Operating Temperature (Temperature Range Option 1) 0 to 70 °C

Ambient Operating Temperature (Temperature Range Option 6) –40 to 85 °C

Ambient Operating Temperature (Temperature Range Option 3) –40 to 125 °C

T

BIAS

Temperature Under Bias –50 to 125 °C

T

STG

Storage Temperature –65 to 150 °C

V

IO

(2)

Input or Output Voltage –0.6 to 6 V

V

CC

Supply Voltage –0.6 to 6 V

V

ID

Identification Voltage –0.6 to 13.5 V

M29F010B

4/20

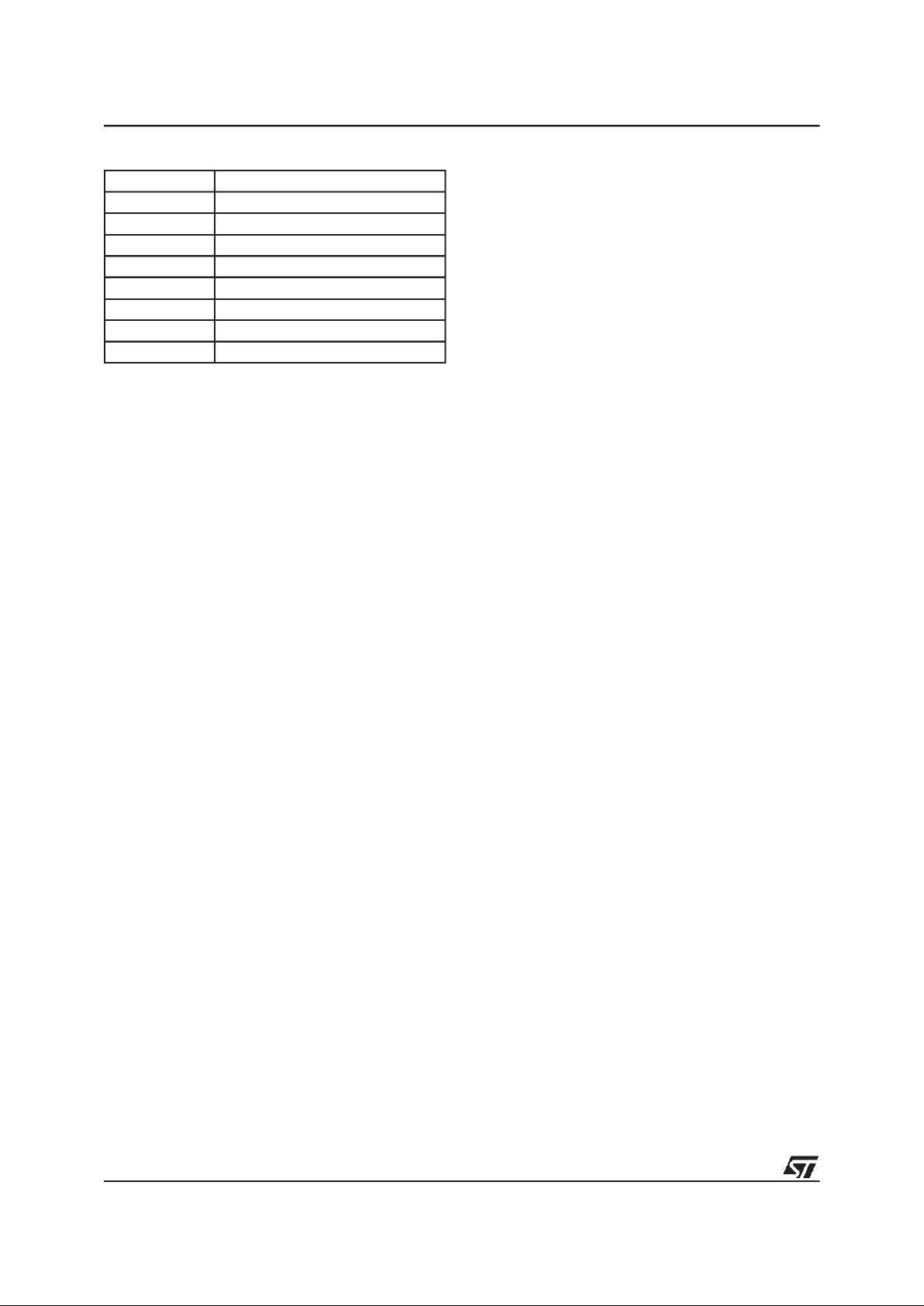

Table 3. Block Addresses

Size (Kbytes) Address Range

16 1C000h-1FFFFh

16 18000h-1BFFFh

16 14000h-17FFFh

16 10000h-13FFFh

16 0C000h-0FFFFh

16 08000h-0BFFFh

16 04000h-07FFFh

16 00000h-03FFFh

BUS OPERATIONS

There are five standardbusoperations that control

the device. These are Bus Read, Bus Write, Output Disable, Standby and Automatic Standby. See

Table 4, Bus Operations, for asummary. Typically

glitches of less than 5ns on Chip Enable or Write

Enable are ignored by the memory and do not affect bus operations.

Bus Read. Bus Read operations read from the

memory cells, or specific registers in the Command Interface. A valid Bus Read operation involves setting the desiredaddress on the Address

Inputs, applying a Low signal, VIL, to Chip Enable

and Output Enable and keeping Write Enable

High, VIH. The Data Inputs/Outputs will output the

value, see Figure 7, Read Mode AC Waveforms,

and Table 11, Read AC Characteristics, for details

of when the output becomes valid.

Bus Write. Bus Write operations write to the

Command Interface. A valid Bus Write operation

begins by setting the desired address on the Address Inputs. The Address Inputs are latched by

the Command Interface onthe falling edgeof Chip

Enable or Write Enable, whichever occurs last.

The Data Inputs/Outputs are latched by the Command Interface on the rising edge of Chip Enable

or Write Enable,whichever occursfirst.OutputEnable must remain High, VIH, during the whole Bus

Write operation. See Figures 8 and 9, Write AC

Waveforms, and Tables 12 and 13, Write AC

Characteristics, for details of the timing requirements.

Output Disable. The Data Inputs/Outputs are in

the high impedance state when Output Enable is

High, VIH.

Standby. When Chip Enable is High, VIH, the

Data Inputs/Outputs pins are placed in the highimpedance state and the Supply Current is reduced to the Standby level.

When Chip Enable is at VIHthe Supply Current is

reduced to the TTL Standby Supply Current I

CC2

.

To furtherreduce theSupply Current tothe CMOS

Standby Supply Current, I

CC3

, Chip Enable should

be held within VCC± 0.2V. For Standby current

levels see Table 10, DC Characteristics.

During program or erase operations the memory

will continue to use the Program/Erase Supply

Current, I

CC4

, for Program orErase operationsun-

til the operation completes.

5/20

M29F010B

Table 4. Bus Operations

Note: X = VILor VIH.

Operation E G W Address Inputs

Data

Inputs/Outpu ts

Bus Read

V

IL

V

IL

V

IH

Cell Address Data Output

Bus Write

V

IL

V

IH

V

IL

Command Address Data Input

Output Disable X

V

IH

V

IH

XHi-Z

Standby

V

IH

XXX Hi-Z

Read Manufacturer

Code

V

IL

V

IL

V

IH

A0 = VIL,A1=VIL,A9=VID,

Others V

IL

or V

IH

20h

Read Device Code V

IL

V

IL

V

IH

A0 = VIH,A1=VIL,A9=VID,

Others V

IL

or V

IH

20h

AutomaticStandby. IfCMOS levels (VCC± 0.2V)

are usedto drive thebus and the busis inactivefor

150ns or more the memory enters Automatic

Standby where the internal Supply Current is reduced tothe CMOS Standby Supply Current,I

CC3

.

The Data Inputs/Outputs will still output data if a

Bus Read operation is in progress.

Special Bus Operations

Additional bus operations can be performed to

read the Electronic Signature and also to apply

and remove Block Protection. These bus operations are intended for use by programming equipment and are not usually used in applications.

They require VIDto be applied to some pins.

Electronic Signature. The memory has two

codes, the manufacturer code and the device

code, that can be read to identify the memory.

These codes can be read by applying the signals

listed in Table 4, Bus Operations.

Block Protection and Blocks Unprotection. Each

block can be separately protected against accidental Program orErase. Protected blocks can be

unprotected to allow data to be changed. Block

Protection and Blocks Unprotection operations

must only be performed on programming equipment. For further information refer to Application

Note AN1122, Applying Protection and Unprotection to M29 Series Flash.

M29F010B

6/20

COMMAND INTERFACE

All Bus Write operations to the memory are interpreted by the Command Interface. Commands

consist of one or more sequential Bus Write operations. Failure to observe a valid sequence of Bus

Write operations will result in the memory returning to Read mode. The long command sequences

are imposed to maximize data security.

The commands are summarized in Table 5, Commands. Refer to Table 5 in conjunction with the

text descriptions below.

Read/Reset Command. The Read/Reset command returns the memory toits Read modewhere

it behaves like a ROM or EPROM. It also resets

the errors in the Status Register. Either one or

three Bus Write operations can be used to issue

the Read/Reset command.

If the Read/Reset command is issued during a

Block Eraseoperation or followinga Programming

or Erase error then the memory will takeupto 10µs

to abort. During the abort period no valid data can

be read from the memory. Issuing a Read/Reset

command during a Block Erase operation will

leave invalid data in the memory.

Auto Select Command. The Auto Select command is used to read the Manufacturer Code, the

Device Code and the Block Protection Status.

Three consecutive Bus Write operations are required to issue the Auto Select command. Once

the Auto Select command is issued the memory

remains in Auto Select mode until another command is issued.

From the Auto Select mode the Manufacturer

Code can be read using a Bus Read operation

with A0 = VILand A1 = VIL. The otheraddress bits

may be set to either VILor VIH. The Manufacturer

Code for STMicroelectronics is 20h.

The Device Code can be read using a Bus Read

operation with A0 = VIHand A1 = VIL. The other

address bits may be set to either VILor VIH.The

Device Code for the M29F010B is 20h.

The Block Protection Status of each block can be

read using a Bus Read operation with A0 = VIL,

A1 = VIH, and A14-A16 specifying the address of

the block. The otheraddress bits maybe set to either VILorVIH. If the addressed block is protected

then 01his output on the Data Inputs/Outputs,otherwise 00h is output.

Program Command. The Program command

can be used to program a value to one address in

the memory array at a time. The command requires fourBus Write operations, the final writeoperation latchesthe address and data inthe internal

state machine and starts the Program/Erase Controller.

If the address falls in a protected block then the

Program command is ignored, the data remains

unchanged. The Status Registeris never read and

no error condition is given.

During the program operation the memory will ignore all commands. It is not possible to issue any

command to abortor pause the operation. Typical

program timesare givenin Table 6. Bus Read operations during the program operation will output

the Status Register on the Data Inputs/Outputs.

See the section on the Status Register for more

details.

After the program operation has completed the

memory will return to the Read mode, unless an

error has occurred. When an error occurs the

memory will continue to output the Status Register. A Read/Reset command must beissued to reset the error condition and return to Read mode.

Note thatthe Program command cannotchange a

bit set at ’0’ backto ’1’ and attempting to do so will

cause anerror. One of the Erase Commands must

be used to set all thebits in a blockor in the whole

memory from ’0’ to ’1’.

Unlock Bypass Command. The Unlock Bypass

command is used in conjunction with the Unlock

Bypass Programcommand to program the memory. When the access time to the device is long (as

with some EPROM programmers) considerable

time saving can be made by using these commands. Three Bus Write operations are required

to issue the Unlock Bypass command.

Once the Unlock Bypass command has been issued the memory will only accept the Unlock Bypass Program command and the Unlock Bypass

Reset command. Thememory can be readas if in

Read mode.

Unlock Bypass Program Command. The Un-

lock Bypass Program command can be used to

program one address in memory at a time. The

command requires two Bus Write operations, the

final write operation latches the address and data

in the internal state machine and starts the Program/Erase Controller.

The Program operation using the Unlock Bypass

Program command behaves identically tothe Program operation using the Program command. A

protected block cannot be programmed; the operation cannotbe aborted and theStatus Register is

read. Errors must be reset using the Read/Reset

command, which leaves the device in Unlock Bypass Mode. See the Program command for details

on the behavior.

Loading...

Loading...