1/18October 2000

HARDWARE FEATURES

S/T ISDN Interf a c e

■ SUPPORTS OSI LEVEL 1 IN CONFOR-

MANCE WITH UIT-T I.430 FOR BASIC

ACCESS AT S AND T INTERFACES (ETSI

300012/ANSI T1.605)

■ LINE INTERFACE TRANSFORMER DIRECT

DRIVE

■

FULL-DUPLEX TRANSMISSION AT 192KBps

ON SEPARATE TRANSMIT AND RECEIVE

TWISTED PAIRS US ING ALTERNATE M ARK

INVER SIO N (AMI) LINE CO DING

■ 2 B CHANNELS AT 64KBps EACH PLUS 1 D

CHANNEL AT 16KBps

■ ALL I.430 WIRING CONFIGURATIONS

SUPPORTED INCLUDING PASSIVE BUS

FOR TE’S DISTRIBUTED POINT TO POINT

AND POINT TO MULTIPOINT

■ MULTIFRAME SUPPO R T

■ ANALOG PART: INCLUDED WITH

ADAPTIVE DETECTION THRESHOLD AND

EQUALIZER

USB Interface

■ USB 1.0 SPECIFICATION FULL COMPLI-

ANCE, 1.1 SPECIFICATION COMPATIBILITY (1.1 POWER MANAGEMENT COMPLIANCE), 12 MBps FUL L SPEED

■ ON-CHIP USB TRANSCEIVER WITH

DIGITAL PLL

■ 6 ISOCHRONOUS ENDPOINTS FOR B1,

B2, D CHANNELS DATA.INTERRUPT

ENDPOINT FOR I430

■ ISDN PROTOCOL AND DATA.CONTROL

ENDPOINT FOR USB STANDARD PLUS

VENDOR SPECIFIC REQUEST

■ COMMUNICATION DEVICE CLASS AND

VENDOR REQUESTS

■ BUS OR SELF POWERED APPLICATION

(PIN PROGRAMMABLE)

■

ONNOW POWER MANAGEM ENT (D0 ,D2,D3)

SUSPEND MODE COMPLIANCE

■

PIN PROGRAMMABLE HIGH/LOW POWER

USB DEVICE REGISTRATION, WAKE-UP

CAPABILITY, USB DEVICE IDENTIFICATION

GENERAL

– USB hot plug and play interface.

– Control access and interrupt handling provided

through the USB interface.

– All FIFOS and FIFOS management needed in-

cluded for USB/ISDN data processing.

– Internal PLL to ge nerate the USB 48 MHz clock

from a 15.36MHz crystal.

– Internal regulator for 3.3V generation from USB

bus 5V.

– 48 pin TQFP package.

– 0.35 m icron HC MO S 6 process.

DESCRIPTION

ST5481 combines ISDN li nk access and an USB

interface to allow a very simple USB/ISDN

modem design with all ISDN prot ocols and up per

applications processed into the HOST PC.

TQFP48

ORDERING NUMBER:

ST5481 TQF7

ST5481

PRODUCT PREVIEW

L.O.U.I.S - LOW COST USB ISDN SOLUTION

This is advance information on a new product now in development or undergoing evaluation. Details are subject to change without notic e.

ST5481

2/18

1 - GENERAL PURPOSE

The ST5481 is a single chip ISDN -BRI with USB

Interface low cost controller. The purpose is a low

cost ISDN modem for applications like INTERNET

ACCES and FAX capabilities when the PC is ON

(full operating mode). The bonus is to offer an

easy and lowcost access to INTERNET at a rate

of 128kbits/sec. EASY access due to plug and

play features via USB bus and lowcost due to host

processing concept and remote powering via USB

bus features.

2 - MAIN FUNCTIONS

The device controls the S0 ISDN basic rate

access (ITU normalization I430) and manages the

B1, B2, D channels through the USB bus. B1, B2,

D channels data flow is regulated through FIFO

memories of respectively 32, 32, 16 bytes in each

direction. On D, B1, B2 channels, all upper

protocols than basic HDLC framing protocol

are host processed from upper-datalink protocol

(I440 normalization), network protocol up to

applications drivers. Link Activation, deactivation

protocols (I430) is managed by the device. But the

full handling of the command and indicate

primitives is done by the host processor

accessing to dedicated registers. Call setup

signalling frames through D channel are managed

by the host processor.

Internal regulators can be enabled to feed the

device (and external devices) via the GNDBUS,

VBUS USB powering lines. They convert the USB

5 volts to 3.3 volts.

The device respects the USB release 1.0 power

management recomm endat ions. When e ntered in

suspend mode on USB side the device drop into a

low power mode. An internal oscillator and a P LL

provide from an external 15.36MHz crystal a

48MHz clock for USB data rate recovering and

15.36MHz clock for S interface.

The device offers one operating mode called

CLOSED mode plus several test modes. In

CLOSED MODE the device presents the USB

interface, the S interface and 8 GPIO pins.

3 - PIN-OUT

Figure 1 : Pin-out Synoptic

1098765432112 11

48

47

46

45

44

43

42

41

40

39

38

37

27 28 29 30 31 32 33 34 35 3625 26

13

14

15

16

17

18

19

20

21

22

23

24

MODE3

MODE2

MODE1

MOD0

RPSM

GNDA

VREGA

VBUS

VREGD1

GNDBUS

DP

DM

DR_TEST5

FS_TEST4

CLK_TEST3

ID3_TEST2

ID2_TEST1

ID1_TEST14

ID0_TEST15

NRESET

VREGD2

GNDD2

CFG0/TEST0

GPIO7

GPIO6

GPIO5

GPIO4

GNDD1

GPIO3

GPIO2

GPIO1

GPIO0

XTALIN

XTALOUT

FLTPLL

LIP

LIN

IREF

LON

LOP

TEST13

TEST12

NCS_TEST11

SDI_TEST10

CFG1_TEST9

SDO_TEST8

SCK_TEST7

ST5481

DX_TEST6

ST5481

3/18

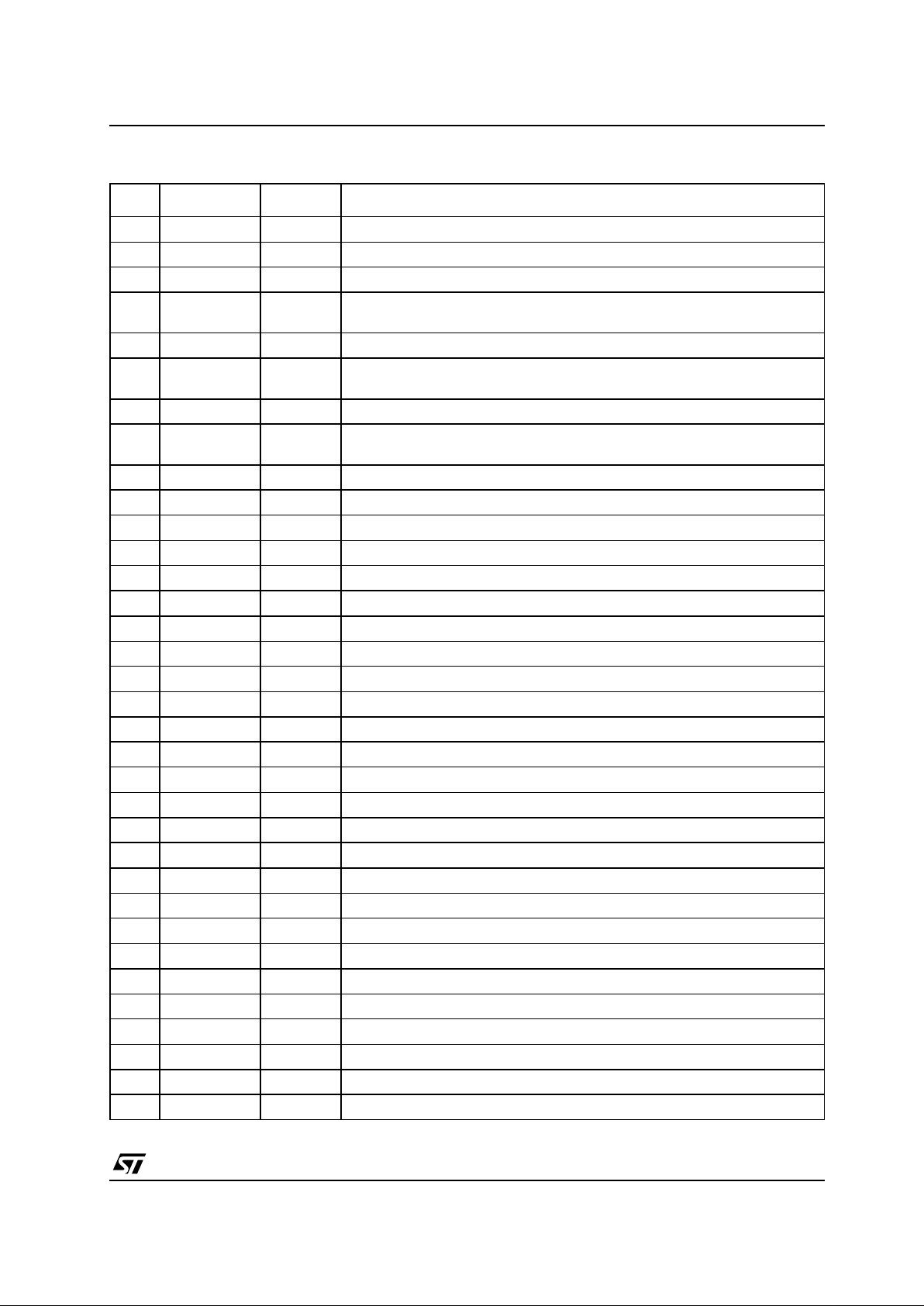

3.1 - Pin List

Pin Name Type Function

1 DM I/O Negative USB differential data line

2 DP I/O Positive USB differential data line

3 GNDBUS I USB remote ground

4 VREGD1 I/O Digital input/ output regulated supply, is an input when RPSM is tied to a logic

zero value

5 VBUS I USB remote positive supply 5 volts.

6 VREGA I/O 3.3V input/ output analog regulated supply, is an input when RPSM is tied to a

logic zero value

7 GNDA I Analog groun d

8 RPSM I REMOTE POWER SUPPLY MODE: when tied to a logic zero value the device

is self powered

9 MODE0 I Static configuration pin. Used for working modes and test modes programming

10 MODE1 I Static configuration pin. Used for working modes and test modes programming

11 MODE2 I Static configuration pin. Used for working modes and test modes programming

12 MODE3 I Static configuration pin. Used for working modes and test modes programming

13 LIP In analog Receive AMI signal differential positive inputs from the S line

14 LIN In analog Receive AMI signal differential negative input from the S line

15 IREF In analog External current reference (connected to an external resistor)

16 LON Out analog Transmit AMI signal differential negative output to the S line

17 LOP Out analog Transmit AMI signal differential positive output to the S line

18 TEST13 Out analog Analog test pin: AOPTEST1

19 TEST12 Out analog Analog test pin: AOPTEST2

20 TEST11 I/O Test pin

21 TEST10 I/O Test pin

22 TEST9 I/O Test pin

23 TEST8 I/O Test pin

24 TEST7 I/O Test pin

25 TEST6 I/O Test pin

26 TEST5 I/O Test pin

27 TEST4 I/O Test pin

28 TEST3 I/O Test pin

29 ID3_TEST2 I/O Either ID product bit 2 for USB descriptor either test pin

30 ID2_TEST1 I/O Either ID product bit 3 for USB descriptor either test pin

31 ID1_TEST14 I Either ID product bit 1 for USB descriptor either test pin

32 ID0_TEST15 I Either ID product bit 0 for USB descriptor either test pin

33 NRESET I Initialisation input pin, zero active.

34 VREGD2 I Digital input supply, must be connected to VREGD1

ST5481

4/18

3.2 - PLL

An internal oscillator provides a 15.36MHz clock for S interface from an external 15.36MHz crystal. From

this clock, the analog block PLL provides a 48MHz clock for USB data rate recovering.

35 GNDD2 I Digital ground

36 CFG0_TEST0 I/O CFG0 input for configuration when closed or open mode else test9

37 FLTPLL In analog Used to adjust the internal PLL filter

38 XTALOUT O Tied to 15.36MHz external crystal

39 XTALIN I Tied to 15.36MHz external crystal

40 GPIO0 I/O General purpose input-output pin 2mA

41 GPIO1 I/O General purpose input-output pin 2mA

42 GPIO2 I/O General purpose input-output pin 2mA

43 GPIO3 I/O General purpose input-output pin 2mA

44 GNDD1 I Digital ground

45 GPIO4 I/O General purpose input-output pin 4mA

46 GPIO5 I/O General purpose input-output pin 4mA

47 GPIO6 I/O General purpose input-output pin 4mA

48 GPIO7 I/O General purpose input-output pin 4mA

Pin Name Type Function

ST5481

5/18

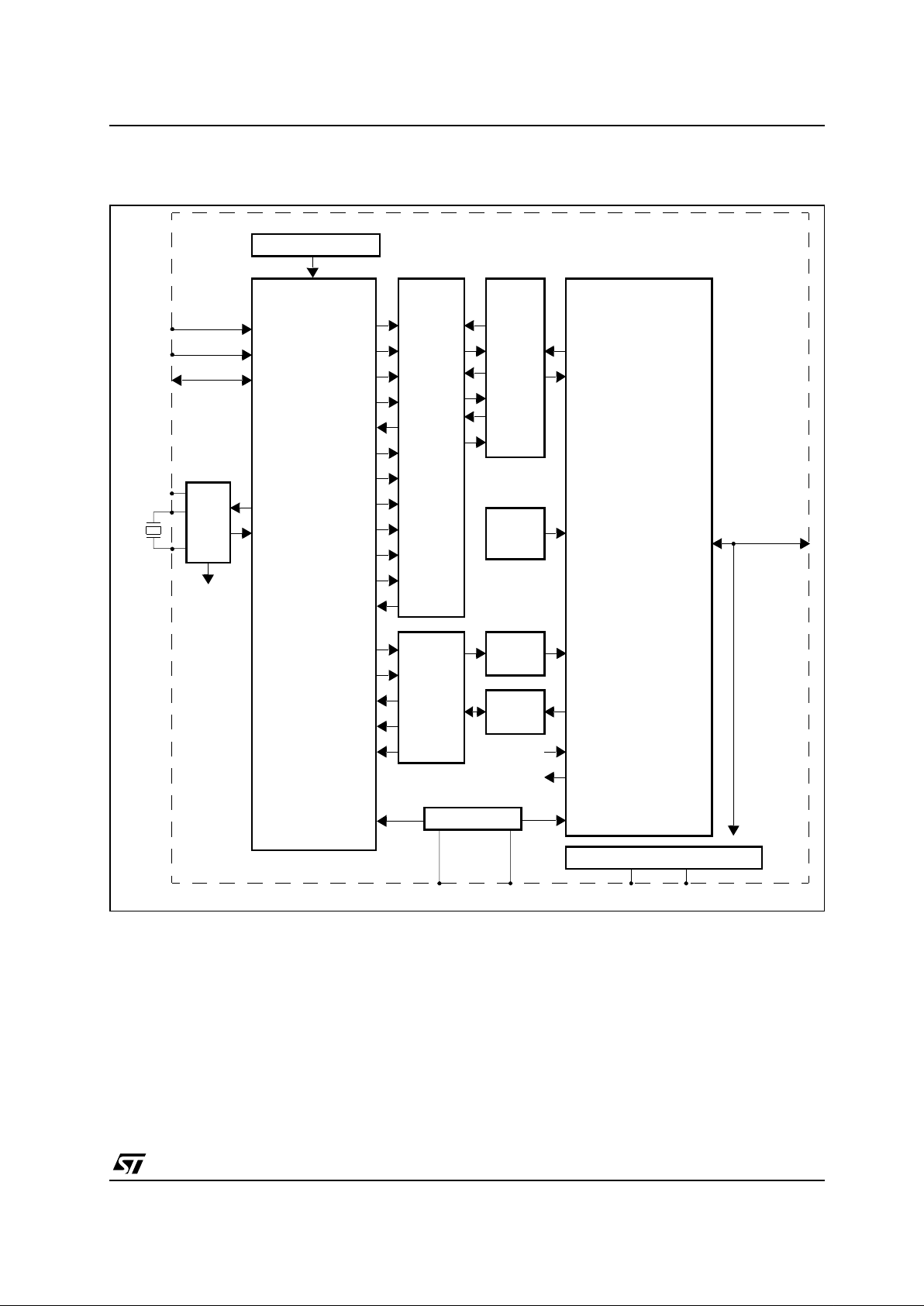

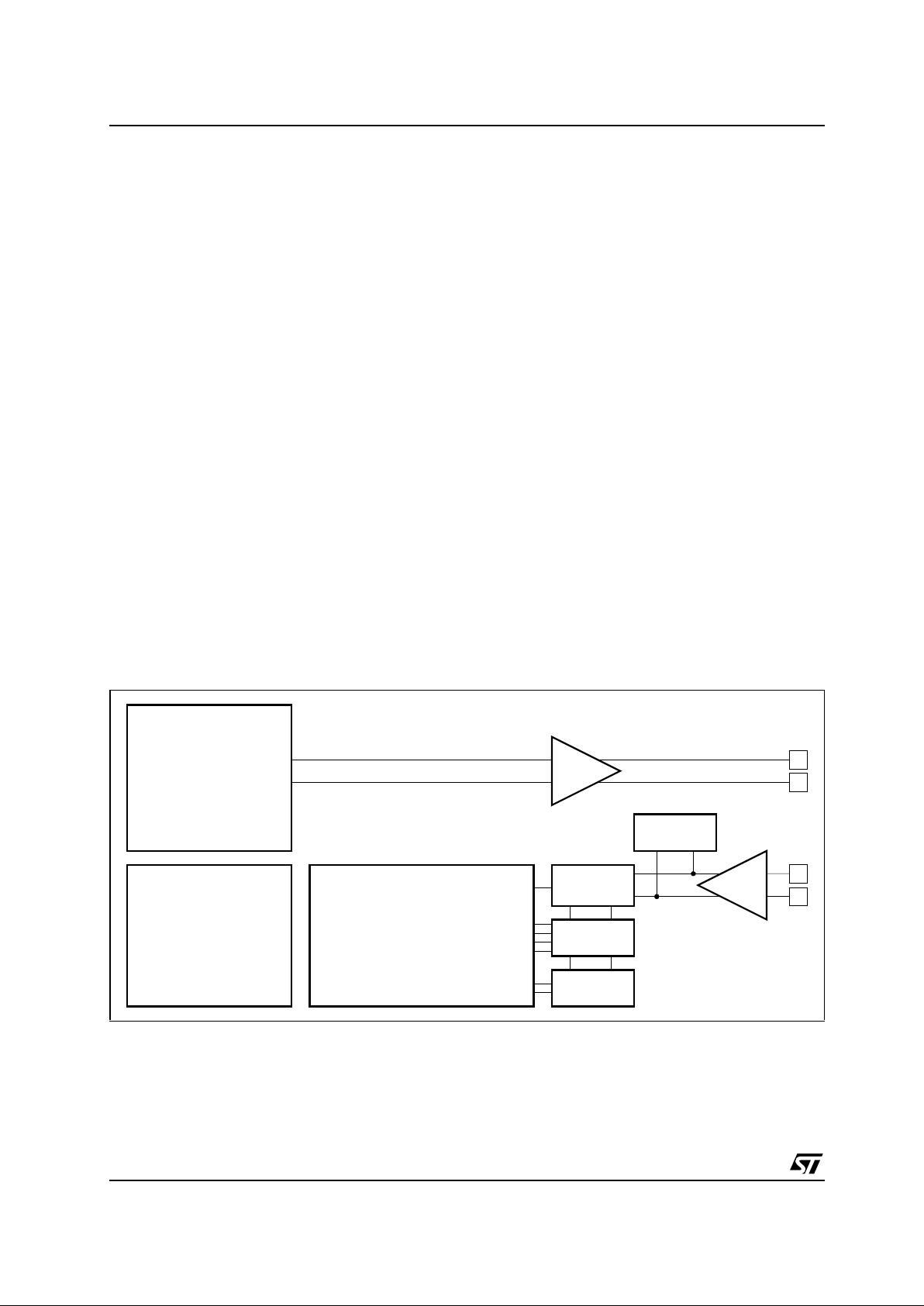

4 - SYNOPTIC

Figure 2 : Global Synoptic

I430

MACROCELL

MCLK

STOP_OSC

S0 interface

TXCK_O

IREF

VREF

NRESET

NINT

DEN

DREQ

NLSD

SDO

SDI

SCK

NCS

RXCK_O

TXFS_O

RXFS_O

TXDATA

RXDATA

B1_W

B2_W

D_W

TEST

VREF-GEN

CHANNEL

B1, B2, D

FIFOS

for

ROM

Descriptor

ACCESS

and

controller

Endpoint 1

Microwire

interface

controller

Endpoint 0

TEST interface

CK48

USB

MACROCELL

USB Driver

CK12

CONTROL_DATA_IN( 7-0)

CONTROL_DATA_O UT( 7-0)

TEST2-0

USB Bus

4

Power manag em ent and R EGU LATORS

8 power pinsRPSM

MODE(3-0)Test pins

15.36MHz

FLTPLL

PLL

15.36

48MHz

4

S0

CK48

isochonous

endpoints

256 bytes

FRAMING

ST5481

6/18

5 - ISDN ACCESS

The device is directly connected to the ISDN line

at S0 interface point.

4 pins are dedicated to this access:

LIP, LIN: receive AMI differential signals inputs

connected to the appropriate transformer LOP,

LON: transmit AMI differential signals outputs

connected to the appropriate transformer.

The S interface access sub-function is clockfeeded by a 15.36MHz clock signal from the

on-chip oscillator.

I431 recommendation protocols are fully implemented.

The activation / deactivation command management is done by the device.

5.1 - ISDN S Interface Synoptic

See Figure 3.

6 - USB ACCESS

The device is directly connected to the USB bus.

4 pins are dedicated to this access:

DP, DM for data exchange. VBUS, GNDBUS as

power lines.

The data transfer rate is 12 MBits. The clock is

extracted from the differential lines DP, DM by a

digital PLL from a 48MHz internal clock. This

48MHz clock is created from the 15.36MHz clock.

The USB protocol is fully implemented following

the 1.0 USB specification.

6.1 - USB Normalization

This specification refers to USB normalization

documents:

– Universal Serial Bus Specification revision 1.0

– Universal Serial Bus Common Class S pecifica-

tion revision 1.0

– ST5481 belongs to the VENDOR SPECIFIC

DEVICE CLASS and to a vendor specific

subclass defined as ISDN MODEM DEVICE

SUBCLASS.

It presents ONE INTERFACE belonging to the

VENDOR SPECIFIC INTERFACE CLASS and a

vendor specific interface subclass defined as

ISDN SOFT MODEM INTERFACE SUBCLASS.

It satisfies to a vendor specific control protocol

called ISDN SOFT MODEM PROTOCOL.

Figure 3 : S-Interface Block Diagram

Line Signal

Rx

Slicers

RXNUMCONTROL

TXNUM

- Tx multiframe control

- D channel monitoring

- Loopbacks

- Frame construction

- AMI code generation

Detector

- C/I control

- Activation state machine

- Master clocks generation

- D & E channel processing

- Auto threshold controller

- Auto equalizer controller

- Digital PLL, line synchronization

- AMI decoder

- Frame synchronization & polarity check

- Signal ID

- Multiframe control.

Pre Filter &

equalizer

2x6 bits DA Cs

Line

Driver

Loading...

Loading...