SANYO LC78626E Datasheet

Overview

The LC78626E is a monolithic compact disk player signal

processing and servo control CMOS IC equipped with an

internal anti-shock control function. Designed for total

functionality including support for EFM-PLL, and one-bit

D/A converter, and containing analog low-pass filter, the

LC78626E provides optimal cost-performance for low-end

CD players that provide anti-shock systems. The basic

functions provided by this IC include modulation of the

EFM signal from the optical pick-up, deinterleaving,

detection and correction of signal errors, prevention of a

maximum of approximately 10 seconds of skipping, signal

processing such as digital filtering (which is useful in

reducing the cost of the player), and processing of a

variety of servo-related commands from the

microprocessor.

Functions

• When an HF signal is input, it is sliced to precise levels

and converted to an EFM signal. The phase is compared

with the internal VCO and a PLL clock is reproduced at

an average frequency of 4.3218 MHz.

• Precise timing for a variety of required internal timing

needs (including the generation of the reference clock) is

produced by the attachment of an external 16.9344 MHz

crystal oscillator.

• The speed of revolution of the disk motor is controlled

by the frame phase difference signal generated by the

playback clock and the reference clock.

• The frame synchronizing signal is detected, stored, and

interpolated to insure stable data read back.

• The EFM signal is demodulated and converted to 8-bit

symbolic data.

• The demodulated EFM signal is divided into subcodes

and output to the external microprocessor. (Three

general I/O ports are shared [exclusively] for this

purpose.)

• After the subcode Q signal passes the CRC check, it is

output to the microprocessor through a serial

transmission (LSB first).

• The demodulated EFM signal is buffered in the internal

RAM, which is able to absorb ± 4 frame's worth of jitter

resulting from variations in the disk rotation speed.

• The demodulated EFM signal is unscrambled to a

specific sequence, and deinterleaving is performed.

• Error detection and correction is performed, as is a flag

process. (C1: two error/C2: two error correction

method.)

• The C2 flag is set after referencing the C1 flag and the

results of the C2 check, where the signal from the C2

flag is interpolated or held at its previous level. The

interpolation circuit uses double interpolation. When

there are two or more C2 flags in a row, the previous

value is held.

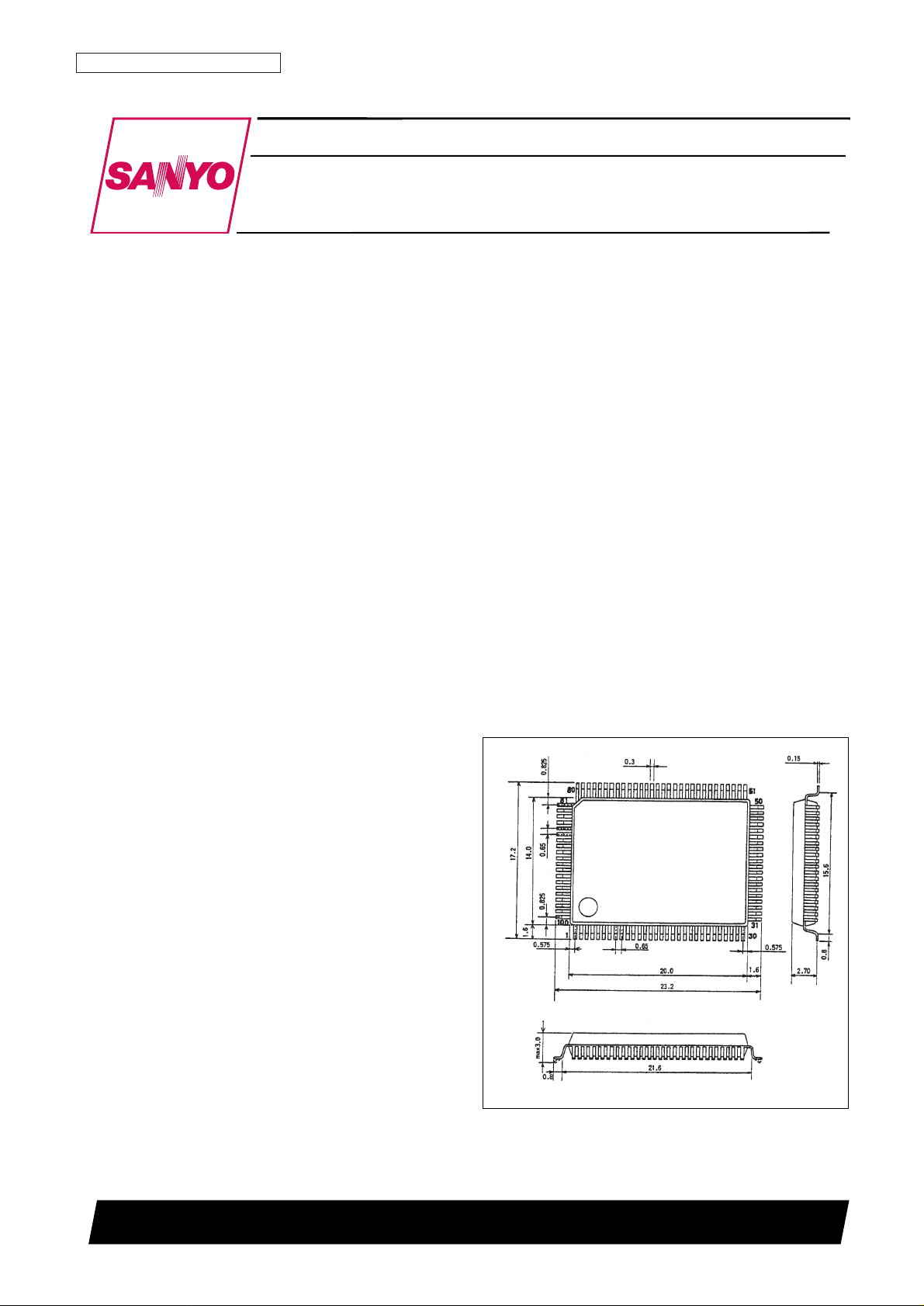

Package Dimensions

unit: mm

3151-QFP100E (FLP100)

CMOS LSI

13098HA(OT) No. 5692-1/32

SANYO: QIP100E (FLP100)

[LC78626E]

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-0005 JAPAN

DSP for Compact Disk Players

LC78626E

Ordering number : EN5692

Continued on next page.

No. 5692-2/32

LC78626E

Continued from preceding page.

• Command (such as track jump, start focus, disk motor

start/stop, muting on/off, track count, etc.) is are

executed after they are entered from the microprocessor.

(An 8-bit serial input is used.)

• The digital output is equipped internally.

• High speed access is supported through discretionary

track counting.

• Using the 4× oversampling digital filter, D/A converter

signals with improved continuity of output data are

produced.

• A ∆∑-type D/A converter using a 3-order noise shaper is

equipped internally. (An analog low-pass filter is

equipped internally.)

• Internal digital attenuator (8-bit-[ALPHA]; 239 steps.)

• Internal digital deemphasis.

• Uses 0 cross mute.

• Bilingual compatibility.

• General I/O ports: 4. (Three of these are shared,

exclusively, with the subcode output function.)

• Up to ten seconds of skip prevention (when using 4M of

DRAM) through ADPCM compression/decompression

processing. 1M/4M bit DRAM can be selected.

• Memory overflow detection output.

• Free memory output.

Features

• 100-pin QFP

• A single 3.2 V/5 V power supply

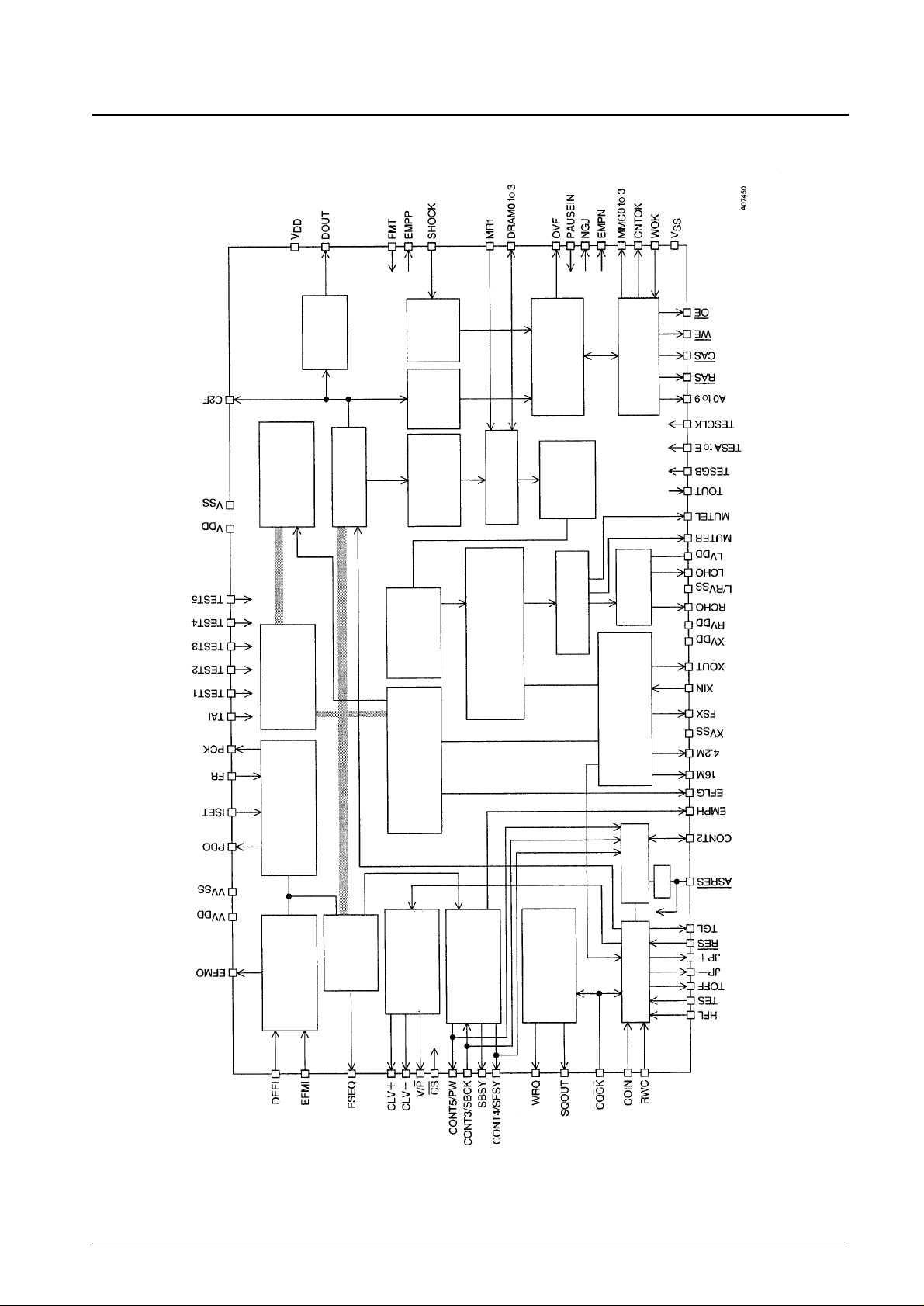

Equivalent Circuit Block Diagram

No. 5692-3/32

LC78626E

Digital out

RAM address

generator

Interpolation mute

Shock

detector

Contact

detector

ADPCM

encoder

Data width

changer

2K × 8-bit RAM

Digital

attenuator

4 × oversampling digital filter

C1, C2 error detection and

correction flag process

VCO clock production

clock control

Slice level control

Sync detect

EFM

demodulation

CLV digital servo

Subcode partition

QCRC

Microprocessor

interface

Servo commands

General ports

Disable

Crystal oscillator-system

timing generator

One-bit DAC

Low-pass

filter

ADPCM

decoder

DRAM control

Overflow process

initiation control

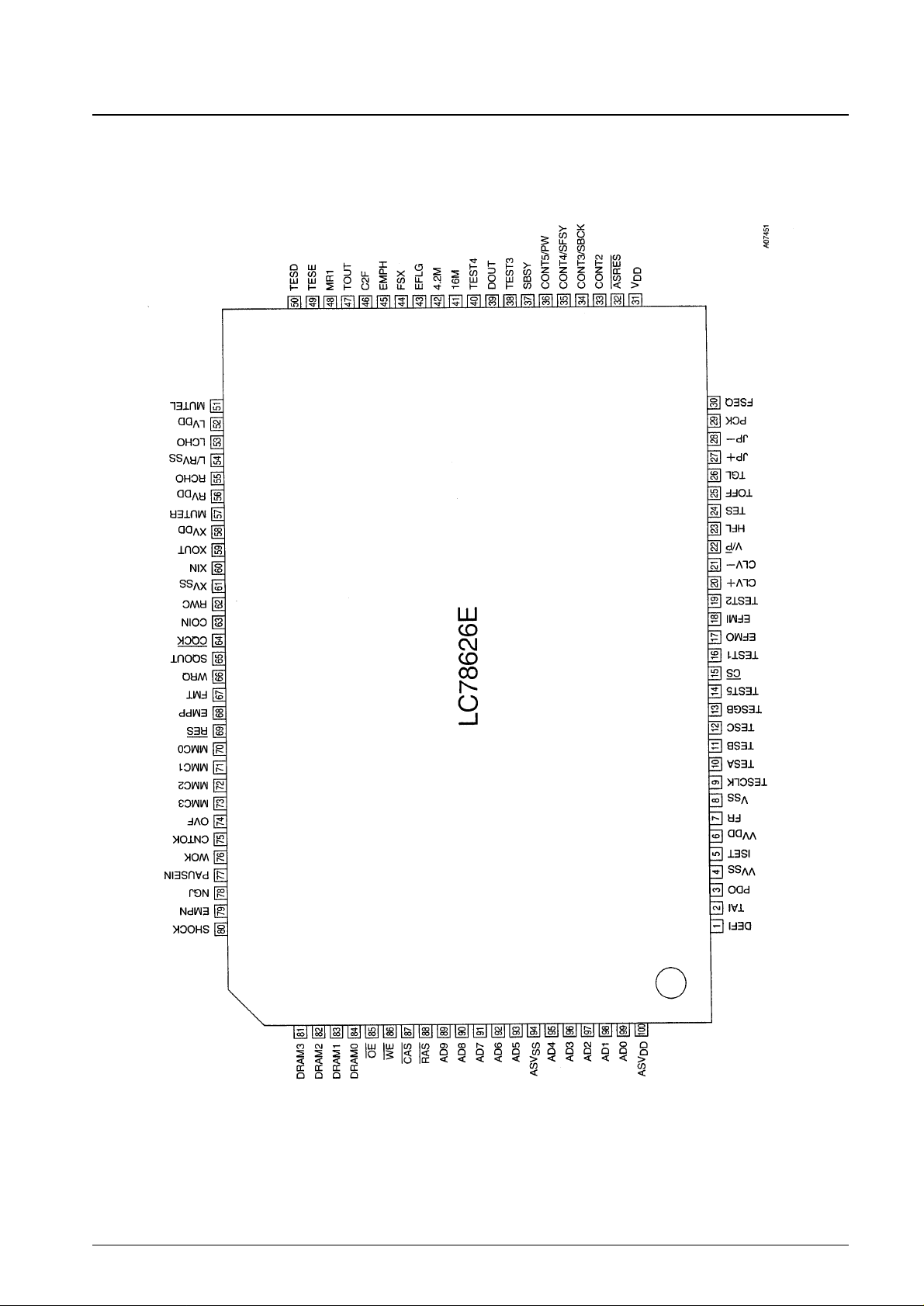

Pin Assignment

No. 5692-4/32

LC78626E

Top view

No. 5692-5/32

LC78626E

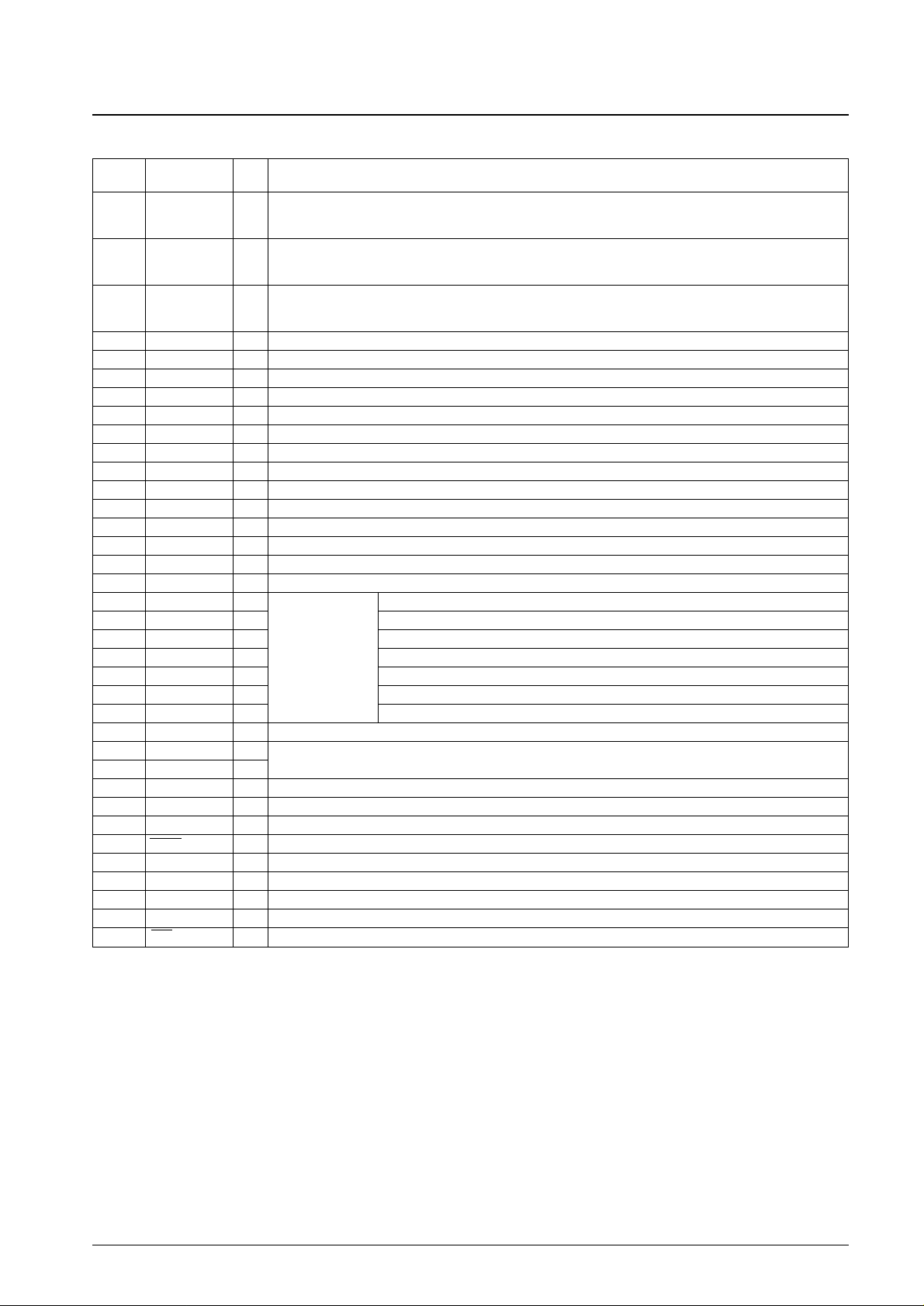

Parameter Symbol Conditions Ratings Unit

Maximum power supply voltage V

DD

max VSS–0.3 to VSS+7.0 V

Input voltage V

IN

VSS–0.3 to VDD+0.3 V

Output voltage V

OUT

VSS–0.3 to VDD+0.3 V

Allowable power dissipation Pd max 400 mW

Operating temperature range Topr –20 to +75 °C

Storage temperature range Tstg –40 to +125 °C

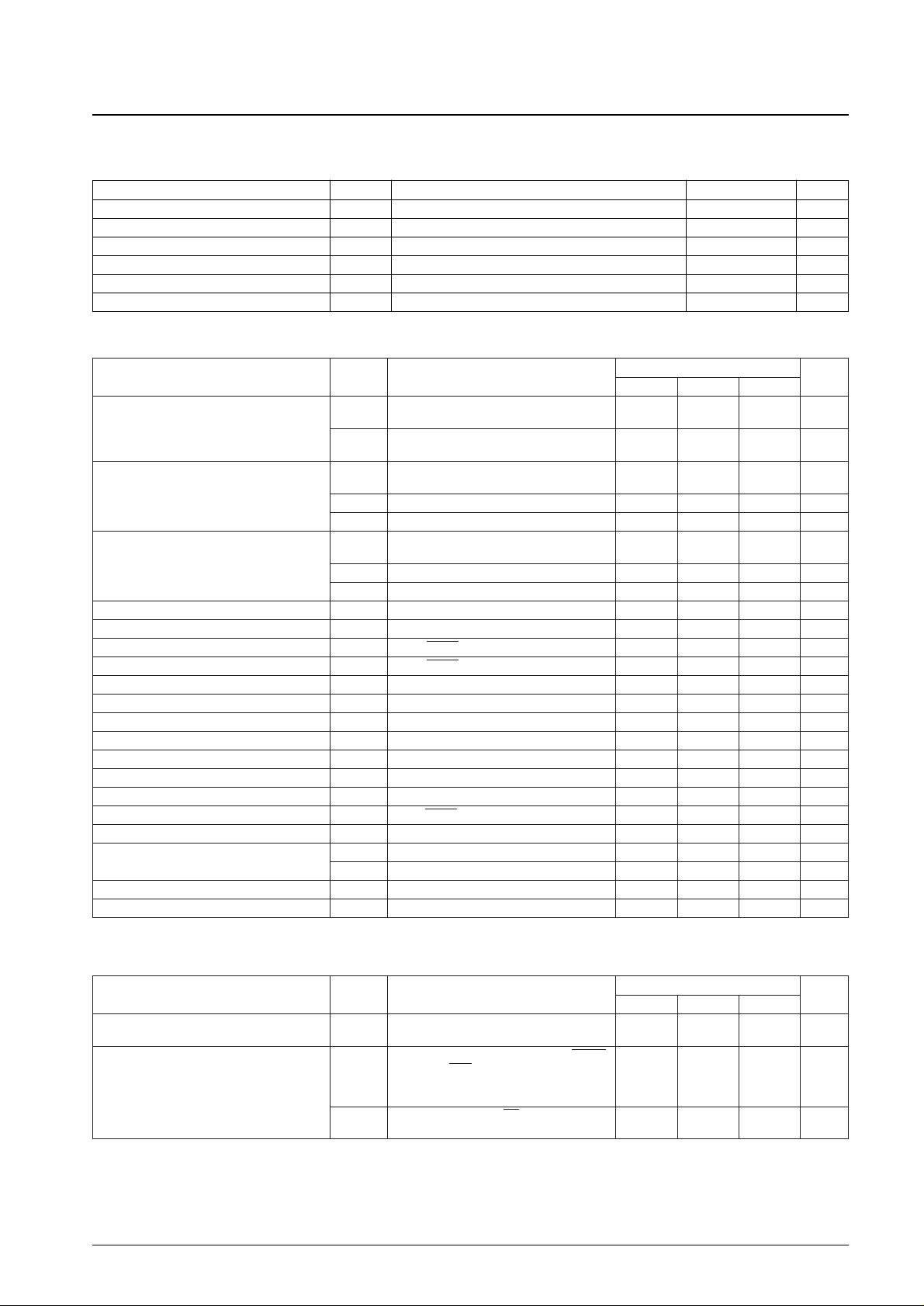

Specifications

Absolute Maximum Ratings at Ta = 25°C, VSS= 0V

Parameter Symbol Conditions

Ratings

Unit

min typ max

V

DD

1

V

DD

, XVDD, LVDD, RVDD, VVDD:

3.0 5.5 V

Power supply voltage

ATT/DF/DAC to the normal speed

V

DD

2

V

DD

, XVDD, LVDD, RVDD, VVDD:

3.6 5.5 V

All functions guaranteed to 2× speed

V

IH

1

I/O and input pins with the exception of

0.7V

DD

V

DD

V

Input high level voltage

EFMI and DRAM0 to DRAM3

V

IH

2 EFMI 0.6V

DD

V

DD

V

V

IH

3 DRAM0 to DRAM3 0.45V

DD

V

DD

V

V

IL

1

I/O and input pins with the exception of

0 0.3V

DD

V

Input low level voltage

EFMI and DRAM0 to DRAM3

V

IL

2 EFMI 0 0.4V

DD

V

V

IL

2 DRAM0 to DRAM3 0 0.2V

DD

V

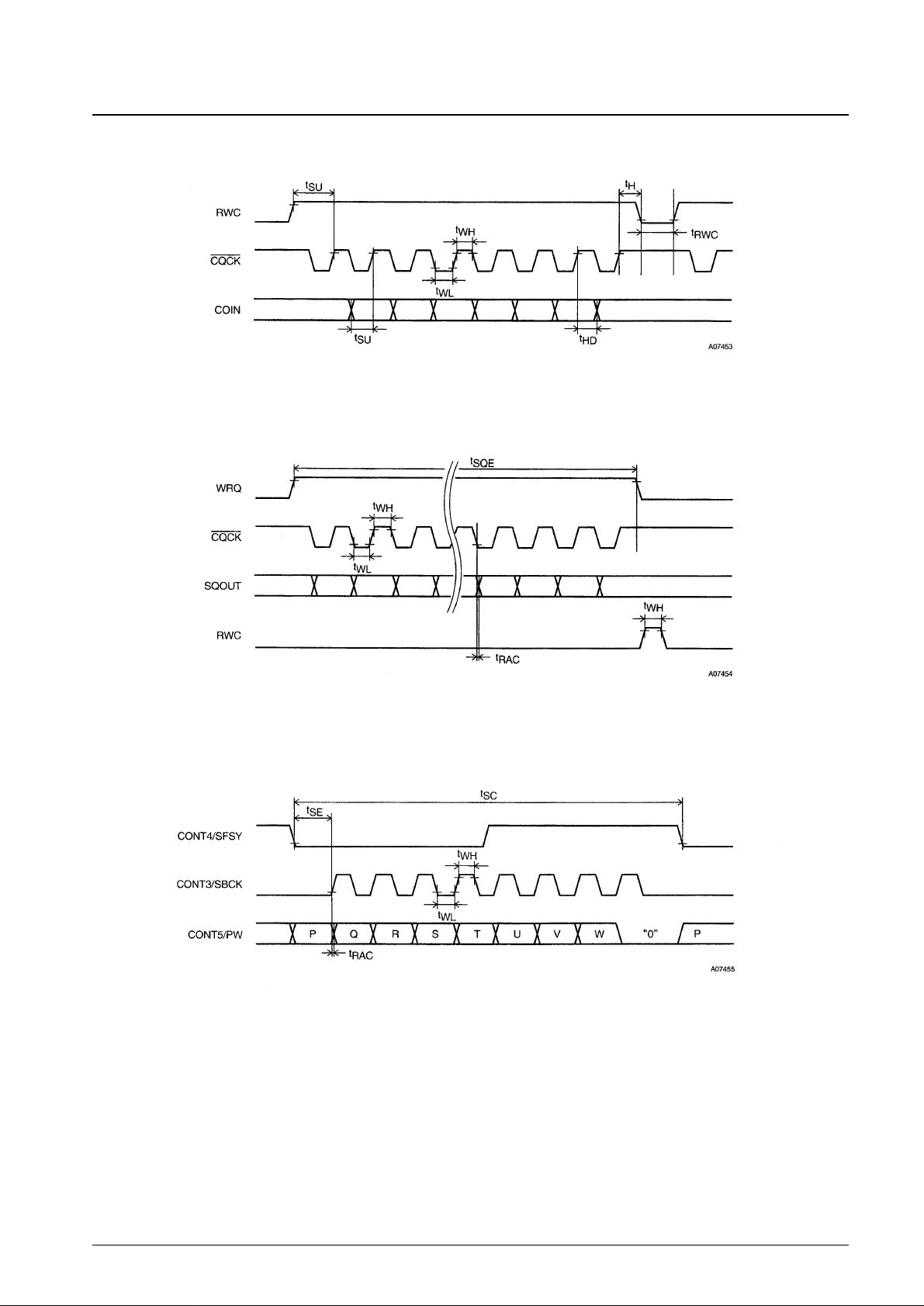

Data setup time t

SU

COIN, RWC: Figure 1 400 ns

Data hold time t

HD

COIN, RWC: Figure 1 400 ns

High level clock pulse width t

WH

SBCK, CQCK: Figures 1 to 3 400 ns

Low level clock pulse width t

WL

SBCK, CQCK: Figures 1 to 3 400 ns

Data read access time t

RAC

SQOUT, PW: Figures 2 and 3 0 400 ns

Command transfer time t

RWC

RWC: Figure 1 1000 ns

Subcode Q read enable time t

SQE

WRQ: Figure 2, no RWC signal 11.2 ms

Subcode ready cycle time t

SC

SFSY: Figure 3 136 µs

Subcode read enable time t

SE

SFSY: Figure 3 400 µs

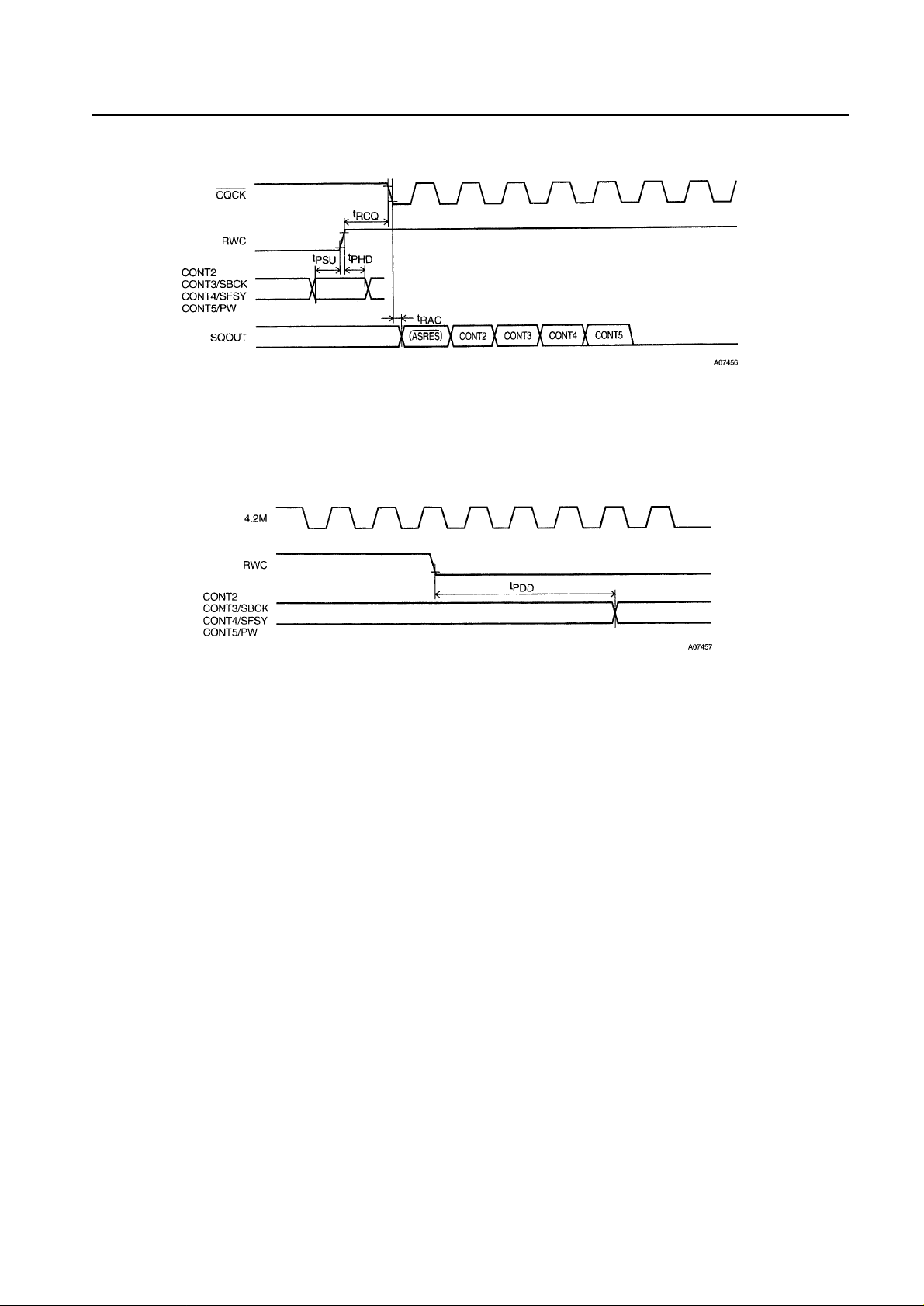

Port input data setup time t

CSU

CONT2 to CONT5, RWC: Figure 4 400 ns

Port input data hold time t

CHD

CONT2 to CONT5, RWC: Figure 4 400 ns

Port input clock setup time t

RCQ

RWC, CQCK: Figure 4 100 ns

Port output data delay time t

CDD

CONT2 TO CONT5, RWC: Figure 5 1200 ns

Input level

V

IN

1 EFMI: slice level control, VDD= 3.0 V 0.8 Vp-p

V

IN

2 XIN: C coupling input 1.0 Vp-p

Range of operating frequencies f

OP

EFMI 10 MHz

Crystal oscillator frequency f

X

XIN, XOUT 16.9344 MHz

Allowable Operating Range at Ta = 25°C, VSS= 0V

Parameter Symbol Conditions

Ratings

Unit

min typ max

Consumption current I

DD

VDD, XVDD, LVDD, RVDD, VVDD:

14 20 mA

V

DD

= 3.0 to 3.4 V with normal playback

DEFI, EFMI, HFL, TES, RWC, COIN, CQCK,

I

IH

1

FMT, MR1, RES, TESD, WOK, PAUSE IN,

5 µA

SHOCK, TESCLK, TESA, TESB, TESC,

Input high level current.

TESGB, TEST1: V

IN

= V

DD

IIH2

TAI, TEST2 to TEST5, CS, TESE:

15 55 µA

V

IN

= VDD= 3.4 V

Electrical Characteristics at Ta = 25°C, VDD= 3.2 V VSS= 0V

Continued on next page.

No. 5692-6/32

LC78626E

Continued from preceding page.

Parameter Symbol Conditions

Ratings

Unit

min typ max

DEFI, EFMI, HFL, TES, RWC, COIN, CQCK,

FMT, MR1, RES, TESE, TESD, WOK,

Input low level current I

IL

PAUSE IN, SHOCK, TESCLK, TESA, TESB, –5 µA

TESC, TESGB, TAI, TEST1 to TEST5, CS :

V

IN

= 0 V

EFMO, CLV

+

, CLV–, V/P, TOFF, TGL, JP+,

V

OH

1 JP–, PCK, FSEQ, EFLG, FSX, EMPH : 2.56 V

I

OH

= –1 mA

CONT2 to CONT5, SBSY, MUTEL, MUTER,

Output high level current

VOH2 C2F, WRQ, SQOUT, 16M, 4.2M, EMPP, 2.56 V

OVF, CNTOK, NGJ : I

OH

= –0.5 mA

V

OH

3 DOUT : IOH= –12 mA 2.72 V

V

OH

4

OE, WE, CAS, RAS, AD9 to AD0, 256 V

DRAM3 to DRAM0 : I

OH

= –0.5 mA

V

OH

5 MMC0 to MMC3 : IOH= –2 mA 2.24 V

V

OL

1

EFMO, CLV

+

, CLV–, V/P, TOFF, JP+, JP–,

0.64 V

PCK, FSEQ, EFLG, FSX, EMPH : I

OL

= 1 mA

CONT2 to CONT5, SBSY, MUTEL, MUTER,

V

OL

2 C2F, WRQ, SQOUT, 16M, 4.2M, EMPP, 0.32 V

Output low level current

OVF, CNTOK, NGJ : I

OL

= 2 mA

V

OL

3 DOUT : IOL= 12 mA 0.48 V

V

OL

4

OE, WE, CAS, RAS, AD9 to AD0,

0.44 V

DRAM3 to DRAM0 : I

OL

= 0.5 mA

V

OL

5 MMC0 to MMC3 : IOL= 2 mA 0.96 V

PDO, CLV

+

, CLV–, JP+, JP–,

I

OFF

1 CONT2 to CONT5, DRAM0 to DRAM3, 5 µA

Output off leakage current

ASRES : V

OUT

= V

DD

PDO, CLV+, CLV–, JP+, JP–,

I

OFF

2 CONT2 to CONT5, DRAM0 to DRAM3, –5 µA

ASRES : V

OUT

= 0 V

Charge pump output current

I

PDOH

PDO : RISET = 68 kΩ 30 42 54 µA

I

PDOL

PDO : RISET = 68 kΩ –54 –42 –30 µA

Parameter Symbol Conditions

Ratings

Unit

min typ max

Total harmonic distortion rate TRD+N

LCHO, RCHO; 1 kHz: Uses the 0 dB data

0.015 0.018 %

input and the 20 kHz-LPF (in the AD725D).

LCHO, RCHO; 1 kHz: Uses the -60 dB data

Dynamic range DR input, the 20 kHz-LPF (in the AD725D), and 85 90 dB

the A filter.

LCHO, RCHO; 1 kHz: Uses the –0 dB data

Signal to noise ratio S/N input, the 20 kHz-LPF (in the AD725D), and 87 92 dB

the A filter.

Cross talk CT

LCHO, RCHO; 1 kHz: Uses the 0 dB data

79 82 dB

input and the 20 kHz-LPF (in the AD725D).

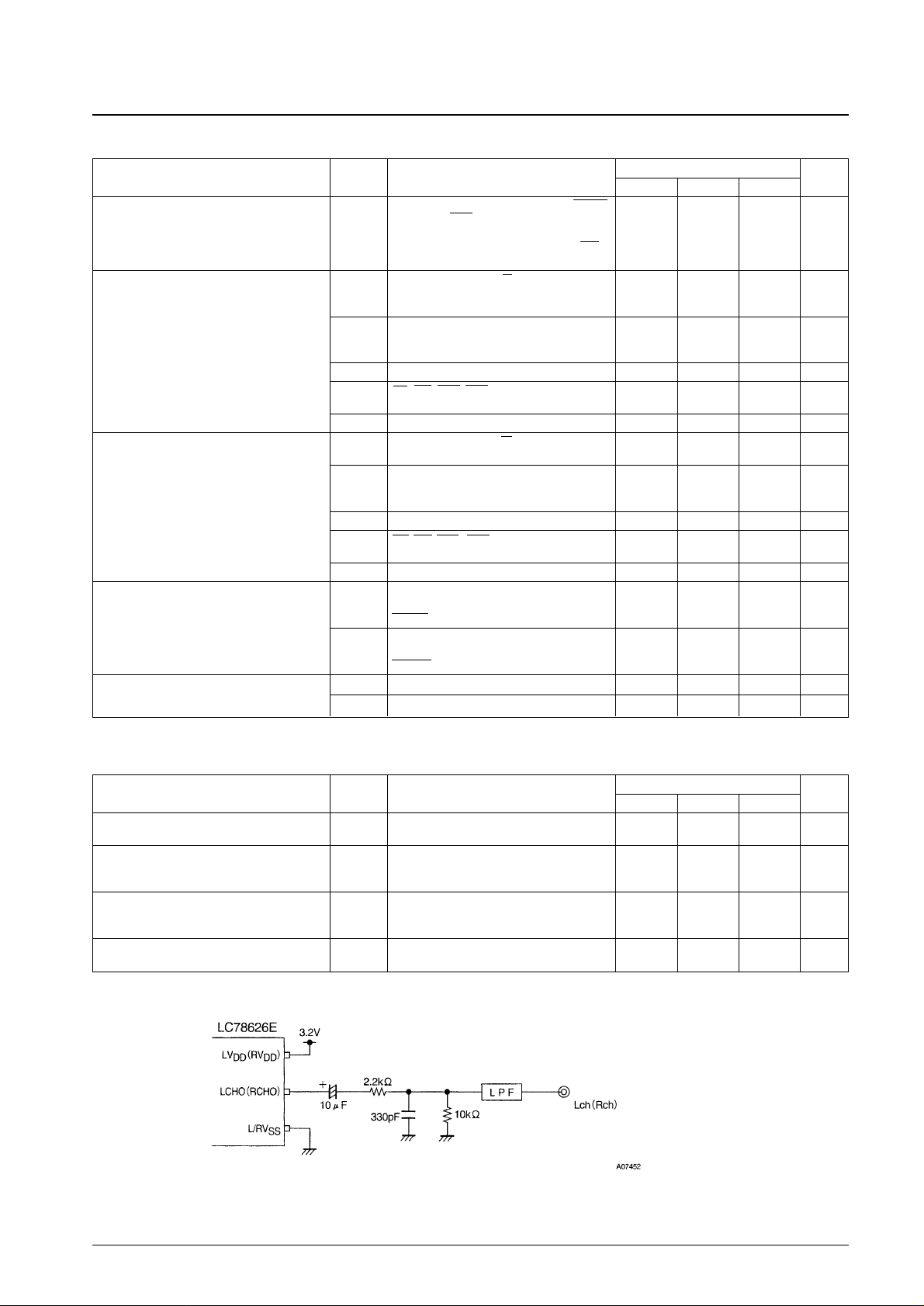

One-bit D/A Converter Analog Characteristics at

Ta = 25°C, VDD= LVDD= RVDD= 3.2 V, VSS= L/RVSS= 0 V

Analog output

Note: Measured with the normal-speed playback mode in the Sanyo one-bit D/A converter block reference digital attenuator circuit.

Figure 1 Command Input

Figure 2 Subcode Q Output

Figure 3 Subcode Output

No. 5692-7/32

LC78626E

No. 5692-8/32

LC78626E

Figure 4 General Port Input Timing

Figure 5 General Port Output Timing

No. 5692-9/32

LC78626E

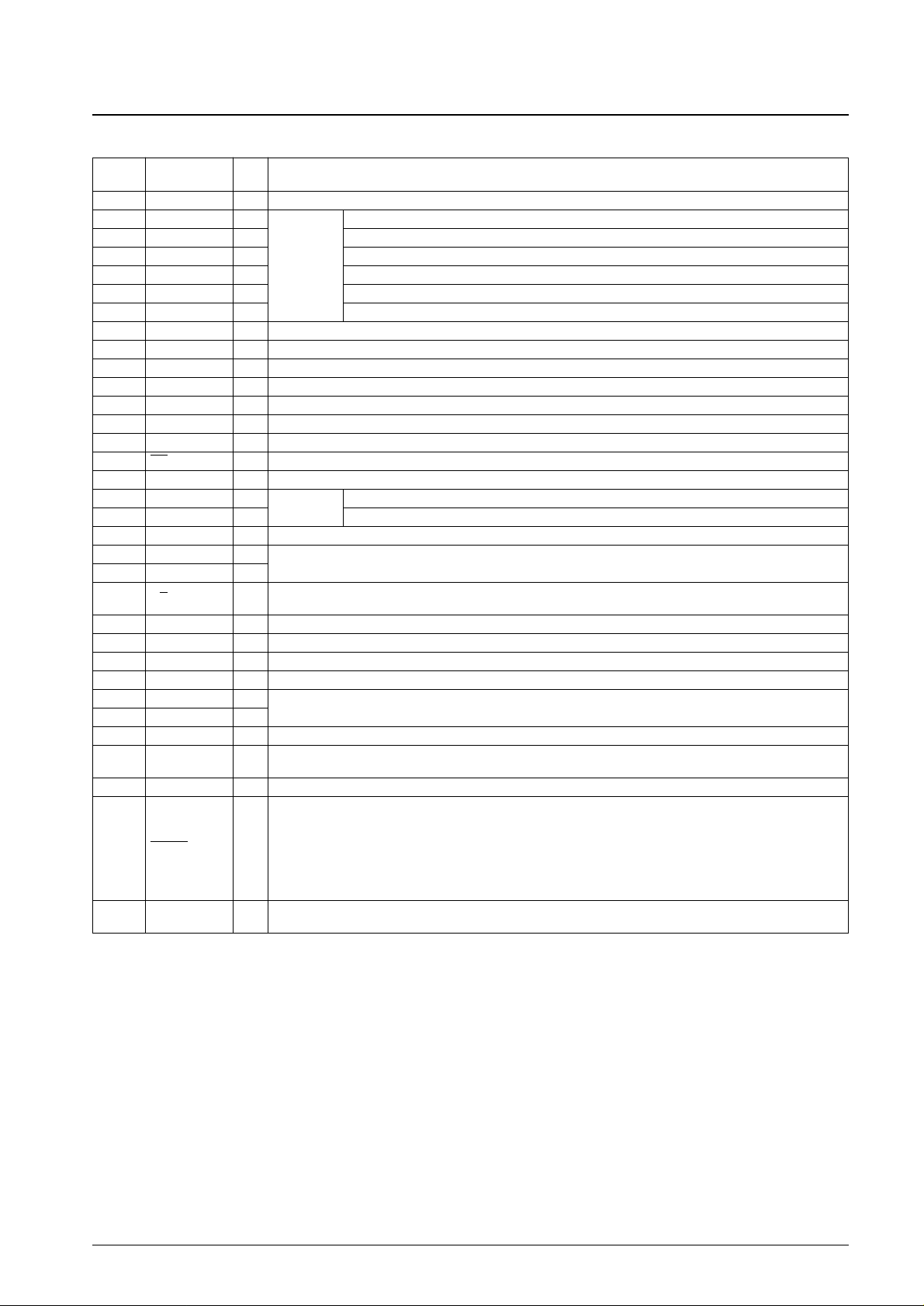

Description of Pins

Pin Pin

I/O Function

No. Name

1 DEFI I Defect detection signal (DEF) input. When not used, must be connected to 0 V.

2 TAI I Test input. Equipped with internal pull-down resistor. Must be connected to 0V.

3 PDO O External VCO control phase comparator output.

4 VV

SS

P

For the PLL

Internal VCO ground. Must be connected to 0 V.

5 ISET AI PDO output current adjustment resistor connection.

6 VV

DD

P Internal VCO power supply.

7 FR AI VCO frequency range adjustment

8 V

SS

P Digital system ground. Must be connected to 0 V.

9 TESCLK I Test clock input. Must be connected to VDD.

10 TESA I Test operation mode control input. Must be connected to VDD.

11 TESB I Test operation mode control input. Must be connected to VDD.

12 TESC I Test operation mode control input. Must be connected to VDD.

13 TESGB I Test operation mode control input. Must be connected to VDD.

14 TEST5 I Test input. Equipped with internal pull-down resistor. Must be connected to 0 V.

15 CS I Chip select input. Equipped with internal pull-down resistor. When not controlled, must be connected to 0 V.

16 TEST1 I Test input. Must be connected to 0 V.

17 EFMO O For slice EFM signal output.

18 EFMI I level control. EFM signal input.

19 TEST2 I Test input. Equipped with internal pull-down resistor. Must be connected to 0 V.

20 CLV

+

O

Disk motor control output. Can have a 3-state output depending on the command.

21 CLV

–

O

22 V/P O

Rough servo/phase control automatic switching monitor output. If a high level then rough servo mode. If a low level then

phase control mode.

23 HFL I Track detect signal input. Schmidt input.

24 TES I Tracking error signal input. Schmidt input.

25 TOFF O Tracking off output.

26 TGL O Tracking gain switch output. Gain is increased with low level.

27 JP

+

O

Track jump control output. Can be 3-state output depending on the command.

28 JP

–

O

29 PCK O EFM data playback clock monitor. 4.3218 MHz during phase lock.

30 FSEQ O

Sync signal detect output. A high level when the sync signal detected from the EFM signal matches the internally

generated sync signal.

31 V

DD

P Digital system power supply.

Reset signal input for initializing only the anti-shock control part (i.e. excluding the DSP part). Resets when this

pin is low level, and release the reset when this pin is high level. Tie this pin to the low level (i.e., connected to 0 V) if

when using software control on the anti-shock part alone through the anti-shock part only reset disable/release

32 ASRES I(I/O) command ($F4) or the anti-shock only reset enable/inrush command ($F5).

Note: This pin is assigned as the least significant bit of the general I/O port however, use as a general I/O

pin is disabled. When the port I/O set command ($DB) is executed, the least significant bit is always “0,” and the

output driver is not turned ON.

33 CONT2 I/O

General I/O pin 2. This controls the commands from the microcontroller. When not used, either set this as an input

port and connect to 0 V, or set this as an output port and leave it open.

Continued on next page.

No. 5692-10/32

LC78626E

Continued from preceding page.

Pin Pin

I/O Description

No. Name

General I/O pin 3. This controls the commands from the microcontroller. This pin is shared exclusively with

34 CONT3/SBCK I/O the subcode read clock input (SBCK). When not used, either set this as an input port and connect to 0 V, or set

this as an output port and leave it open.

General I/O pin 4. This controls the commands from the microcontroller. This pin is shared exclusively with

35 CONT4/SFSY I/O the subcode frame sync signal output (SFSY). When not used, either set this as an input port and connect to 0

V, or set this as an output port and leave it open.

General I/O pin 5. This controls the commands from the microcontroller. This pin is shared, exclusively, with

36 CONT5/PW I/O the subcode P, Q, R, S, T, U, V, W output (PW). When not used, either set this as an input port and connect to

0 V, or set this as an output port and leave it open.

37 SBSY O Subcode block sync signal output.

38 TEST3 I Test input. Equipped with an internal pull-down resistor. Must be connected to 0 V.

39 DOUT O Digital output. EIAJ format.

40 TEST4 I Test input. Equipped with an internal pull-down resistor. Must be connected to 0 V.

41 16M O 16.9344 MHz output.

42 4.2M O 4.2336 MHz output.

43 EFLG O C1, C2, one error, two error error correction monitor output

44 FSX O 7.35 kHz sync signal output (frequency divided from the crystal oscillator).

45 EMPH O Deemphasis monitor output. When high level, a deemphasis disk is being played back.

46 C2F O C2 flag output.

47 TOUT O Test output. Under normal operation, this should be left open.

48 MR1 I DRAM switch: high : 1M, low : 4M

49 TESE I Test input. Must be connected to 0V.

50 TESD I Test input. Must be connected to 0V.

51 MUTESL O L channel mute output.

52 LV

DD

P L channel power supply.

53 LCHO AO L channel output.

54 L/RV

SS

P

For the one-bit D/A

L/R channel ground. Must be connected to 0 V.

55 RCHO AO

converter

R channel output.

56 RV

DD

P R channel power supply.

57 MUTER O R channel mute output.

58 XVDD P Crystal oscillator power supply.

59 XOUT O

16.9344 MHz crystal oscillator connection.

60 XIN I

61 XVSS P Crystal oscillator ground. Must be connected to 0 V.

62 RWC I Read/write control input. Schmidt input.

63 COIN I Microcontroller command input.

64 CQCK I Input pin for the command input latch clock and the subcode readout clock. Schmitt input.

65 SQOUT O Subcode Q output.

66 WRQ O Subcode Q output standby output.

67 FMT I Operating mode switch: high: shock proof, low: through.

68 EMPP O DRAM empty (an RZP pulse is output when the DRAM is empty).

69 RES I External reset input: low reset (all internal blocks are reinitialized).

Continued on next page.

Loading...

Loading...