Overview

The LC75864E and LC75864W are 1/4 duty LCD display

drivers that can directly drive up to 96 segments and can

control up to four general-purpose output ports. These

products also incorporate a key scan circuit that accepts

input from up to 30 keys to reduce printed circuit board

wiring.

Features

• Key input function for up to 30 keys (A key scan is

performed only when a key is pressed.)

• 1/4 duty - 1/2 bias and 1/4 duty - 1/3 bias drive schemes

can be controlled from serial data (up to 96 segments).

• Sleep mode and all segments off functions that are

controlled from serial data

• Segment output port/general-purpose output port

function switching that is controlled from serial data

• Serial data I/O supports CCB format communication

with the system controller.

• Direct display of display data without the use of a

decoder provides high generality.

• Independent V

LCD

for the LCD driver block

(V

LCD

can be set to in the range VDD- 0.5 to 6.0 volts.)

• Provision of an on-chip voltage-detection type reset

circuit prevents incorrect displays.

• RC oscillator circuit

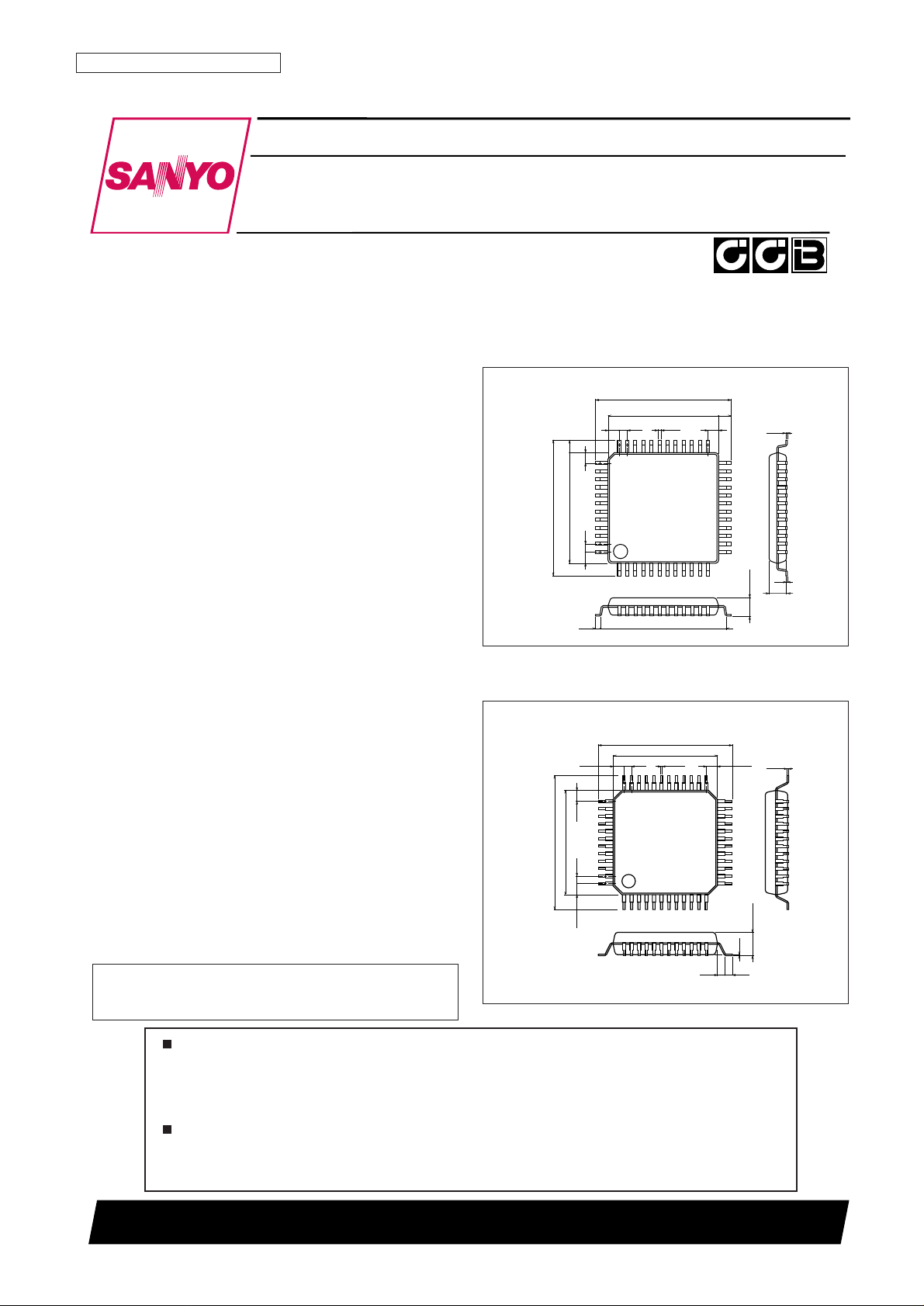

Package Dimensions

unit: mm

3156-QIP48E

Ordering number : ENN6860

D2501TN (OT) No. 6860-1/26

LC75864E, 75864W

SANYO Electric Co.,Ltd. Semiconductor Company

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

1/4 Duty LCD Display Drivers with Key Input Function

CMOS IC

Any and all SANYO products described or contained herein do not have specifications that can handle

applications that require extremely high levels of reliability, such as life-support systems, aircraft’s

control systems, or other applications whose failure can be reasonably expected to result in serious

physical and/or material damage. Consult with your SANYO representative nearest you before using

any SANYO products described or contained herein in such applications.

SANYO assumes no responsibility for equipment failures that result from using products at values that

exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other

parameters) listed in products specifications of any and all SANYO products described or contained

herein.

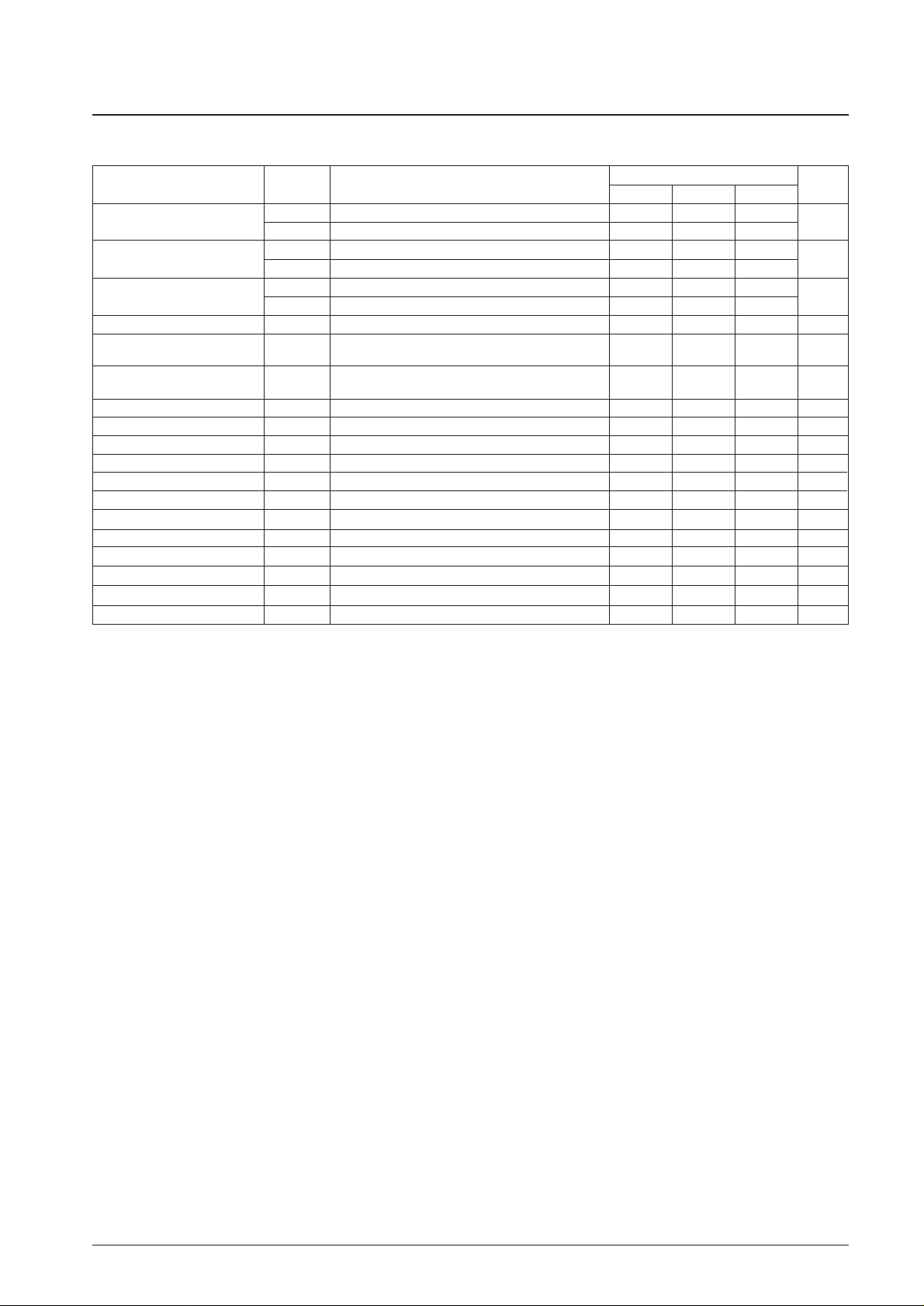

unit: mm

3163A-SQFP48

0.5

7.0

9.0

0.15

0.180.75 0.5

0.75

0.75

0.5

0.75

0.5

0.1

112

13

24

25

36

37

48

7.0

9.0

1.7max

SANYO: SQFP48

[LC75864W]

• CCB is a trademark of SANYO ELECTRIC CO., LTD.

• CCB is SANYO’s original bus format and all the bus

addresses are controlled by SANYO.

[LC75864E]

SANYO: QIP48E

17.2

14.0

0.35

1.0

1.5

36

1.6

37

1.5

14.0

17.2

1.0

48

1.5

1

0.8

15.6

1.6

1.5

25

24

13

12

3.0max

0.15

0.1

2.7

No. 6860-2/26

LC75864E, 75864W

LC75864E

(QIP48E)

LC75864W

(SQFP48)

KI5

KI4

KI3

KI2

KI1

KS6

KS5

KS4

KS3

KS2/S24

KS1/S23

COM4

COM3

P1/S1

P2/S2

P3/S3

P4/S4

S5S6S7S8S9

S10

S11

S12

V

DD

V

LCD

V

LCD

1

V

LCD

2

V

SS

TEST

OSC

DO

CE

CL

DI

COM2

36

37 24

48 13

25

1 12

COM1

S22

S21

S20

S19

S18

S17

S16

S15

S14

S13

Pin Assignment

Specifications

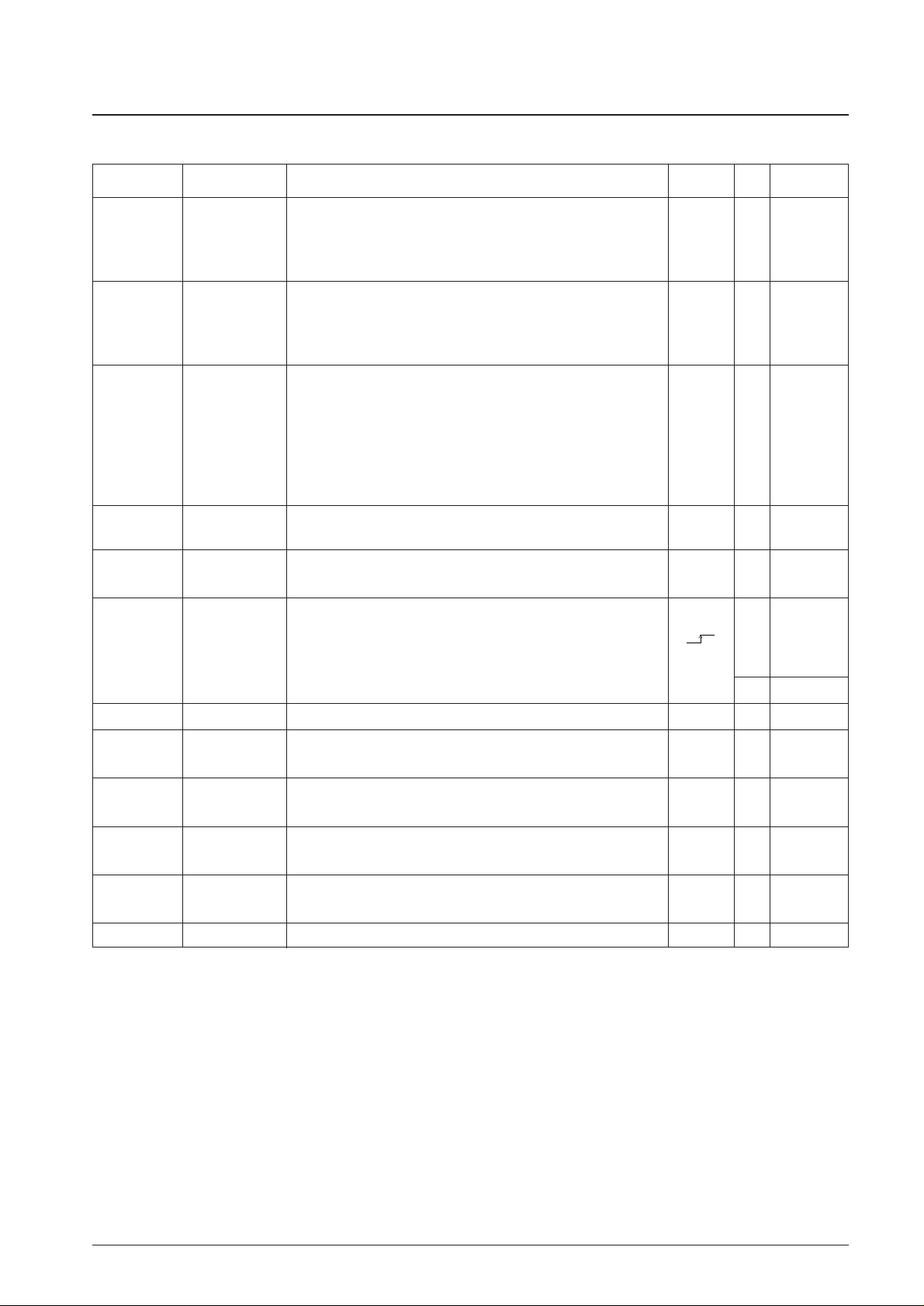

Absolute Maximum Ratings at Ta = 25°C, VSS= 0 V

Parameter Symbol Conditions Ratings Unit

Maximum supply voltage

V

DD

max V

DD

–0.3 to +7.0

V

V

LCD

max V

LCD

–0.3 to +7.0

V

IN

1 CE, CL, DI –0.3 to +7.0

Input voltage V

IN

2 OSC, TEST –0.3 to VDD+ 0.3 V

V

IN

3 V

LCD

1, V

LCD

2, KI1 to KI5 –0.3 to V

LCD

+ 0.3

V

OUT

1 DO –0.3 to +7.0

Output voltage V

OUT

2 OSC –0.3 to VDD+ 0.3 V

V

OUT

3 S1 to S24, COM1 to COM4, KS1 to KS6, P1 to P4 –0.3 to V

LCD

+ 0.3

I

OUT

1 S1 to S24 300 µA

Output current

I

OUT

2 COM1 to COM4 3

I

OUT

3 KS1 to KS6 1 mA

I

OUT

4 P1 to P4 5

Allowable power dissipation Pd max Ta = 85°C 150 mW

Operating temperature Topr –40 to +85 °C

Storage temperature Tstg –55 to +125 °C

Top view

Allowable Operating Ranges at Ta = –40 to +85°C, VSS= 0 V

No. 6860-3/26

LC75864E, 75864W

Parameter Symbol Conditions

Ratings

Unit

min typ max

Supply voltage

V

DD

V

DD

4.5 6.0

V

V

LCDVLCD

VDD– 0.5

6.0

Input voltage

V

LCD

1 V

LCD

1 2/3 V

LCD

V

LCD

V

V

LCD

2 V

LCD

2 1/3 V

LCD

V

LCD

Input high level voltage

V

IH

1 CE, CL, DI 0.8 V

DD

6.0

V

V

IH

2 KI1 to KI5 0.6 V

DD

V

LCD

Input low level voltage V

IL

CE, CL, DI, KI1 to KI5 0 0.2 V

DD

V

Recommended external

R

OSC

OSC 43 kΩ

resistance

Recommended external

C

OSC

OSC 680 pF

capacitance

Guaranteed oscillation range f

OSC

OSC 25 50 100 kHz

Data setup time t

ds

CL, DI: Figure 2 160 ns

Data hold time t

dh

CL, DI: Figure 2 160 ns

CE wait time t

cp

CE, CL: Figure 2 160 ns

CE setup time t

cs

CE, CL: Figure 2 160 ns

CE hold time t

ch

CE, CL: Figure 2 160 ns

High level clock pulse width t

øH

CL: Figure 2 160 ns

Low level clock pulse width t

øL

CL: Figure 2 160 ns

Rise time t

r

CE, CL, DI: Figure 2 160 ns

Fall time t

f

CE, CL, DI: Figure 2 160 ns

DO output delay time t

dc

DO, RPU= 4.7 kΩ, CL= 10 pF*1: Figure 2 1.5 µs

DO rise time t

dr

DO, RPU= 4.7 kΩ, CL= 10 pF*1: Figure 2 1.5 µs

Note: *1. Since DO is an open-drain output, these times depend on the values of the pull-up resistor RPUand the load capacitance CL.

Electrical Characteristics for the Allowable Operating Ranges

No. 6860-4/26

LC75864E, 75864W

Parameter Symbol Conditions

Ratings

Unit

min typ max

Hysteresis V

H

CE, CL, DI, KI1 to KI5 0.1 V

DD

V

Power-down detection voltage V

DET

2.5 3.0 3.5 V

Input high level current I

IH

CE, CL, DI: VI= 6.0 V 5.0 µA

Input low level current I

IL

CE, CL, DI: VI= 0 V –5.0 µA

Input floating voltage V

IF

KI1 to KI5 0.05 V

DD

V

Pull-down resistance R

PD

KI1 to KI5: VDD= 5.0 V 50 100 250 kΩ

Output off leakage current I

OFFH

DO: VO= 6.0 V 6.0 µA

V

OH

1 KS1 to KS6: IO= –500 µA

V

LCD

– 1.0 V

LCD

– 0.5 V

LCD

– 0.2

Output high level voltage

V

OH

2 P1 to P4: IO= –1 mA

V

LCD

– 1.0

V

V

OH

3 S1 to S24: IO= –20 µA

V

LCD

– 1.0

VOH4 COM1 to COM4: IO= –100 µA

V

LCD

– 1.0

VOL1 KS1 to KS6: IO= 25 µA 0.2 0.5 1.5

V

OL

2 P1 to P4: IO= 1 mA 1.0

Output low level voltage V

OL

3 S1 to S24: IO= 20 µA 1.0 V

V

OL

4 COM1 to COM4: IO= 100 µA 1.0

V

OL

5 DO: IO= 1 mA 0.1 0.5

V

MID

1 COM1 to COM4: 1/2 bias, IO= ±100 µA

1/2 V

LCD

– 1/2 V

LCD

+

1.0 1.0

V

MID

2 S1 to S24: 1/3 bias, IO= ±20 µA

2/3 V

LCD

– 2/3 V

LCD

+

1.0 1.0

Output middle level voltage

*2

V

MID

3 S1 to S24: 1/3 bias, IO= ±20 µA

1/3 V

LCD

– 1/3 V

LCD

+

V

1.0 1.0

V

MID

4 COM1 to COM4: 1/3 bias, IO= ±100 µA

2/3 V

LCD

– 2/3 V

LCD

+

1.0 1.0

V

MID

5 COM1 to COM4: 1/3 bias, IO= ±100 µA

1/3 V

LCD

– 1/3 V

LCD

+

1.0 1.0

Oscillator frequency f

OSC

OSC: R

OSC

= 43 kΩ, C

OSC

= 680 pF 40 50 60 kHz

I

DD

1 VDD: Sleep mode 100

I

DD

2 VDD: VDD= 6.0 V, output open, f

OSC

= 50 kHz 270 540

Current drain I

LCD

1 V

LCD

: Sleep mode 5 µA

I

LCD

2

V

LCD

: V

LCD

= 6.0 V, output open, 1/2 bias, f

OSC

= 50 kHz

100 200

I

LCD

3

V

LCD

: V

LCD

= 6.0 V, output open, 1/3 bias, f

OSC

= 50 kHz

60 120

Note: *2. Excluding the bias voltage generation divider resistor built into V

LCD

1 and V

LCD

2. (See Figure 1.)

To the common segment driver

Excluding these resistors.

V

LCD

1

V

LCD

V

LCD

2

Figure 1

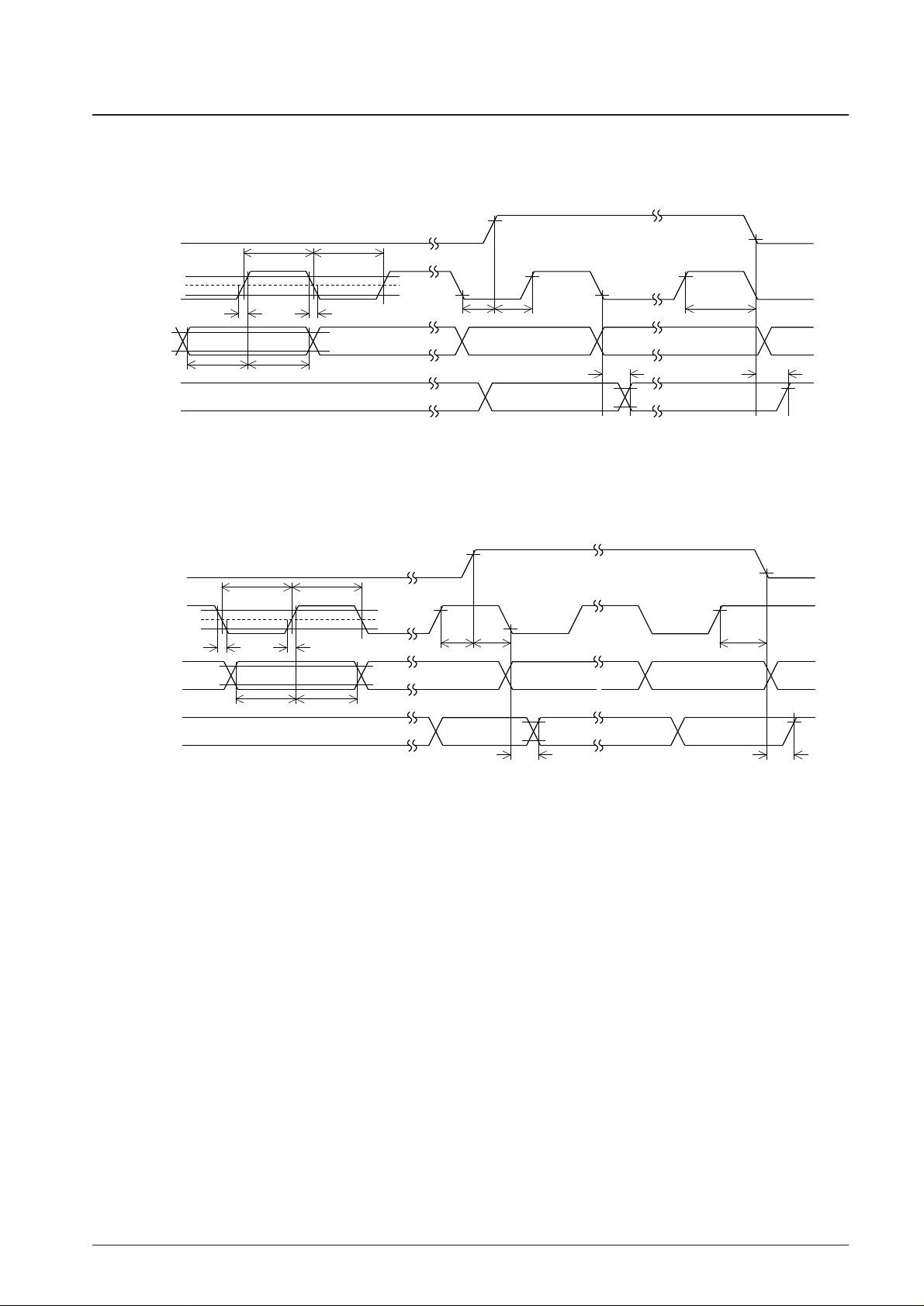

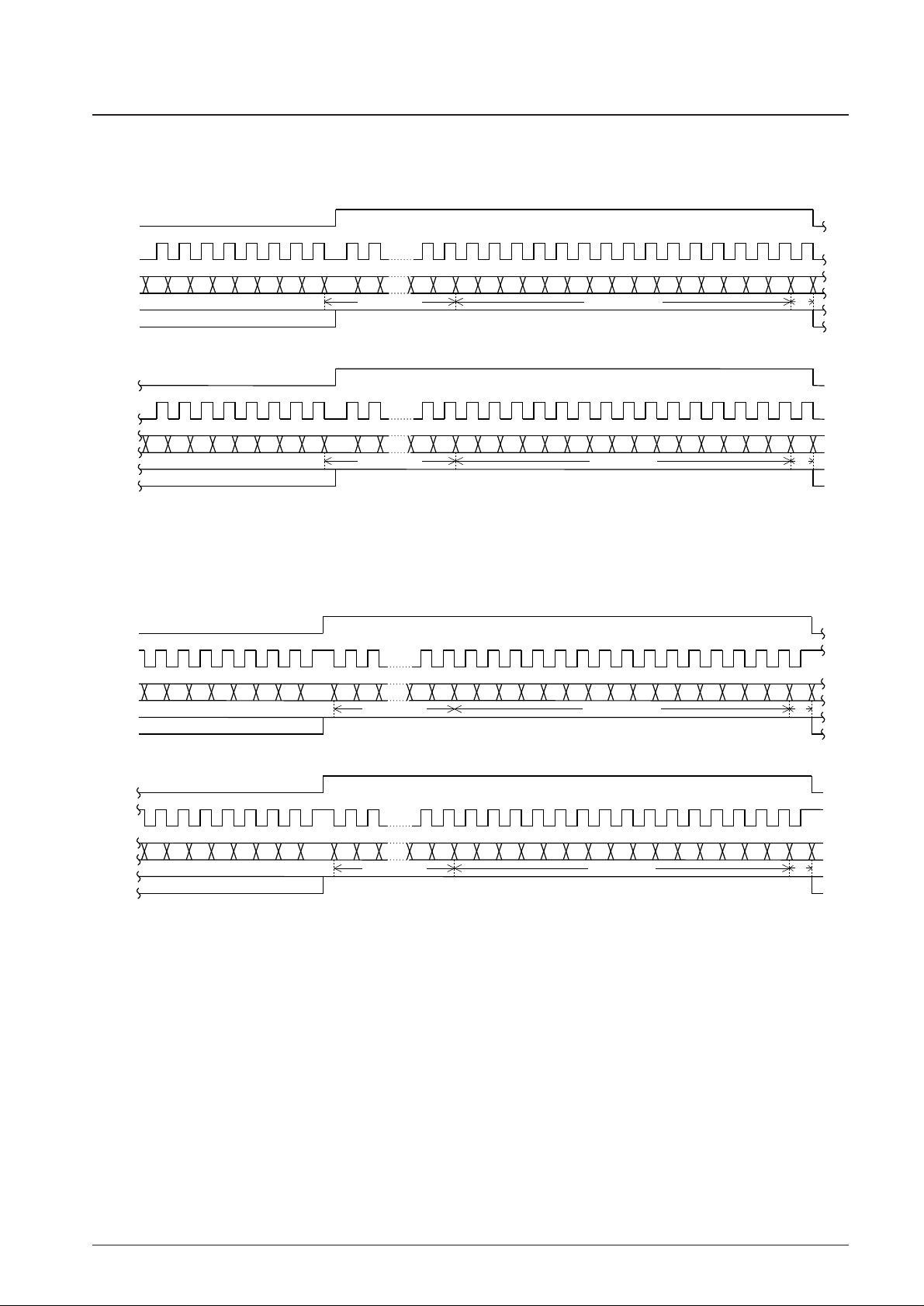

1. When CL is stopped at the low level

No. 6860-5/26

LC75864E, 75864W

2. When CL is stopped at the high level

Figure 2

CE

tøH

tr

tds tdh

tf

tøL

tcp tcs

tch

tdr

tdc

D1D0

VIH1

VIH1

VIH1

50%

VIL

VIL

VIL

CL

DI

DO

CE

tøL

tf

tds tdh

tr

tøH

tcp tcs

tch

tdr

tdc

D1D0

VIH1

VIH1

VIH1

50%

VIL

VIL

VIL

CL

DI

DO

No. 6860-6/26

LC75864E, 75864W

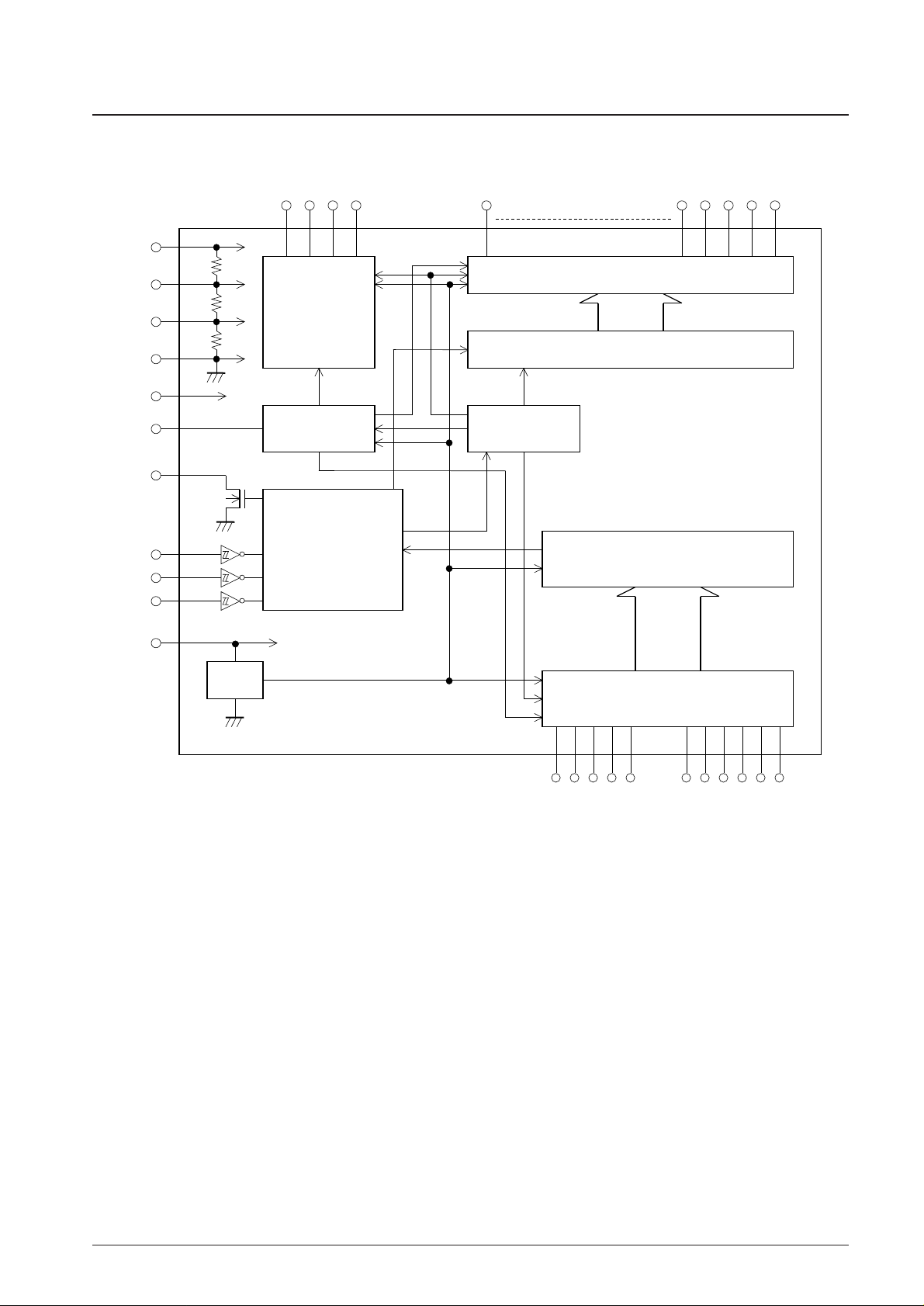

V

LCD

COM4

COM3

COM2

COM1

S22

S5

S4/P4

S3/P3

S2/P2

S1/P1

KI5

KI4

KI3

KI2

KI1

KS6

KS5

KS4

KS3

S24/KS2

S23/KS1

V

LCD

1

V

LCD

2

V

SS

TEST

OSC

DO

DI

CL

CE

V

DD

VDET

CCB

INTERFACE

CLOCK

GENERATOR

COMMON

DRIVER

CONTROL

REGISTER

SHIFT REGISTER

SEGMENT DRIVER & LATCH

KEY SCAN

KEY BUFFER

Block Diagram

Pin Functions

No. 6860-7/26

LC75864E, 75864W

Pin Pin No. Function Active I/O

Handling

when unused

S1/P1 to S4/P4

S5 to S22

COM1

COM2

COM3

COM4

KS1/S23

KS2/S24

KS3 to KS6

KI1 to KI5

OSC

CE

CL

DI

DO

TEST

V

LCD

1

V

LCD

2

V

DD

V

LCD

1 to 4

5 to 22

23

24

25

26

27

28

29 to 32

33 to 37

44

46

47

48

45

43

40

41

38

39

Segment outputs for displaying the display data transferred by serial data

input.

The S1/P1 to S4/P4 pins can be used as general-purpose output ports

under serial data control.

Common driver outputs

The frame frequency f

O

is given by: fO= (f

OSC

/512) Hz.

Key scan outputs

Although normal key scan timing lines require diodes to be inserted in the

timing lines to prevent shorts, since these outputs are unbalanced CMOS

transistor outputs, these outputs will not be damaged by shorting when

these outputs are used to form a key matrix. The KS1/S23 and KS2/S24

pins can be used as segment outputs when so specified by the control data.

Key scan inputs

These pins have built-in pull-down resistors.

Oscillator connection

An oscillator circuit is formed by connecting an external resistor and

capacitor at this pin.

Serial data interface connections to the controller. Note that DO, being an

open-drain output, requires a pull-up resistor.

CE: Chip enable

CL: Synchronization clock

DI: Transfer data

DO: Output data

This pin must be connected to ground.

Used for applying the LCD drive 2/3 bias voltage externally. Must be

connected to V

LCD

2 when a 1/2 bias drive scheme is used.

Used for applying the LCD drive 1/3 bias voltage externally. Must be

connected to V

LCD

1 when a 1/2 bias drive scheme is used.

Logic block power supply connection. Provide a voltage of between 4.5 and

6.0 V.

LCD driver block power supply connection. Provide a voltage of between

V

DD

– 0.5 and 6.0 V.

—

—

—

H

—

H

—

—

—

—

—

—

—

O

O

O

I

I/O

I

I

I

O

I

I

I

—

—

Open

Open

Open

GND

V

DD

GND

Open

—

Open

Open

—

—

V

SS

42

Power supply connection. Connect to ground. —

— —

Serial Data Input

1. When CL is stopped at the low level

No. 6860-8/26

LC75864E, 75864W

Note: B0 to B3, A0 to A3 ... CCB address

DD ... Direction data

CE

0 1 0 0 0 0 1 0 0 0 0 0 0 0 S0 S1 K0 K1 P0 P1 P2 SC DR 0

B0 B1 B2 B3 A0 A1 A2 A3

Display data Control data

DD

D1 D2

D47 D48

0 1 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1

B0 B1 B2 B3 A0 A1 A2 A3

Display data Fixed data

DD

D49

D50 D95 D96

CL

DI

DO

Note: B0 to B3, A0 to A3 ... CCB address

DD ... Direction data

• CCB address......42H

• D1 to D96..........Display data

• S0, S1................Sleep control data

• K0, K1...............Key scan output/segment output selection data

• P0 to P2.............Segment output port/general-purpose output port selection data

• SC......................Segment on/off control data

• DR.....................1/2 bias or 1/3 bias drive selection data

2. When CL is stopped at the high level

CE

0 1 0 0 0 0 1 0 0 0 0 0 0 0 S0 S1 K0 K1 P0 P1 P2 SC DR 0

B0 B1 B2 B3 A0 A1 A2 A3

Display data Control data

DD

D1 D2

D47 D48

0 1 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1

B0 B1 B2 B3 A0 A1 A2 A3

Display data Fixed data

DD

D49 D50 D95 D96

CL

DI

DO

Loading...

Loading...