SANYO LC573202A Datasheet

Ordering number : ENN*6726

CMOS IC

LC573202A

4-Bit Microcontroller

with 2K-Byte ROM, 64

Preliminary

Overview

The LC573202A is a CMOS 4-bit microcontroller that operates on low voltage and very low power consumption. It also

contai ns 2K-byte ROM, 64 × 4 bits RAM, LCD drivers and melody function.

Features

(1) Read-Only Memory (ROM)

- 2048 × 8 bits

(2) Random Access Memory (RAM)

- 64 × 4 bits

(3) Cycle Time

Cycle time Oscillation source Oscillation Frequency Power supply voltage Power source

122µs

122µs

122µs

(4) Input/Output ports

- Input ports : 6 ports (S-port : 4 terminals, M-port : 2 terminals)

- Output ports : 1 port (Buzzer output/General output port : mask option changeover)

- LCD segment output ports : 25 terminals

(Possible to use output port (SEG13 to SEG25) : by mask option)

- LCD common output ports : 4 terminals

Crystal oscillation

RC oscillation

Crystal oscillation 32.768kHz 2.60 - 3.60V Li Battery

Crystal oscillation

RC oscillation

32.768kHz 1.30 - 1.65V Ag Battery

32.768kHz 2.00 - 6.00V External voltage

××××

4Bits RAM and LCD Driver

supply

Ver.1.02

22698

91400 RM (IM) HO No.6726-1/18

LC573202A

(5) LCD driver

Drivable LCD panel Number of drivable LCD segment output

1/2bias 1/4duty 100 segments

1/2bias 1/3duty 75 segments

1/2bias 1/2duty 50 segments

STATIC 25 segments

(Possible to use output port by mask option.)

- Built-in Step-up/Step-down circuit

(6) Melody/Buzzer (When buzzer output is selected on output port by mask option.)

- Melody function Octave : 3 octaves

Time of musical note : specified by program

- Buzzer output

- Possible to use genera l output by mask op tion.

(7) Base timer

- 15-bit base timer for timekeeping

(8) HALT release

- Five vec t ors

1. 15-bit base timer (500ms overflow output)

2. 15-bit base timer (output every 32ms)

3. S-port

4. M-port

5. 1/10 second pulse

(9) Stand-by mode

- HALT mode

The program operation will be stopped in this mode. This mode is released by system reset and 5 vectors for HALT

release above-mentioned.

(10) System reset

- RES terminal

- Reset by setting S1 to S4 terminals to “H” level simultaneously.

(11) Oscillation

- 32.768kHz crystal oscillation/External RC oscillation (mask option)

(Selectable built-in or external capacitor for crystal oscillation by mask option.)

(12) Power supply

- Ag-battery : VDD1-VSS=1.30V to 1.65V, Step-up voltage (VDD2-VSS=2.4V to 3.3V)

- Li-battery : VDD2-VSS=2.60V to 3.60V, Step-down voltage (VDD1-VSS=1.3V to 1.8V)

- External voltage supply : VDD2-VSS=2.00V to 6.00V, Step-down voltage (VDD1-VSS=1.3V to 3.00V)

(LCD displa y voltage : VDD2-VSS≥2.60V)

(13) Shipping form

- Bare chip, QIP48E

(14) The development tool

- Evaluation chip : LC5797

- Emulator : EVA520 + TB5734 + DCB-1A

No.6726-2/18

LC573202A

K

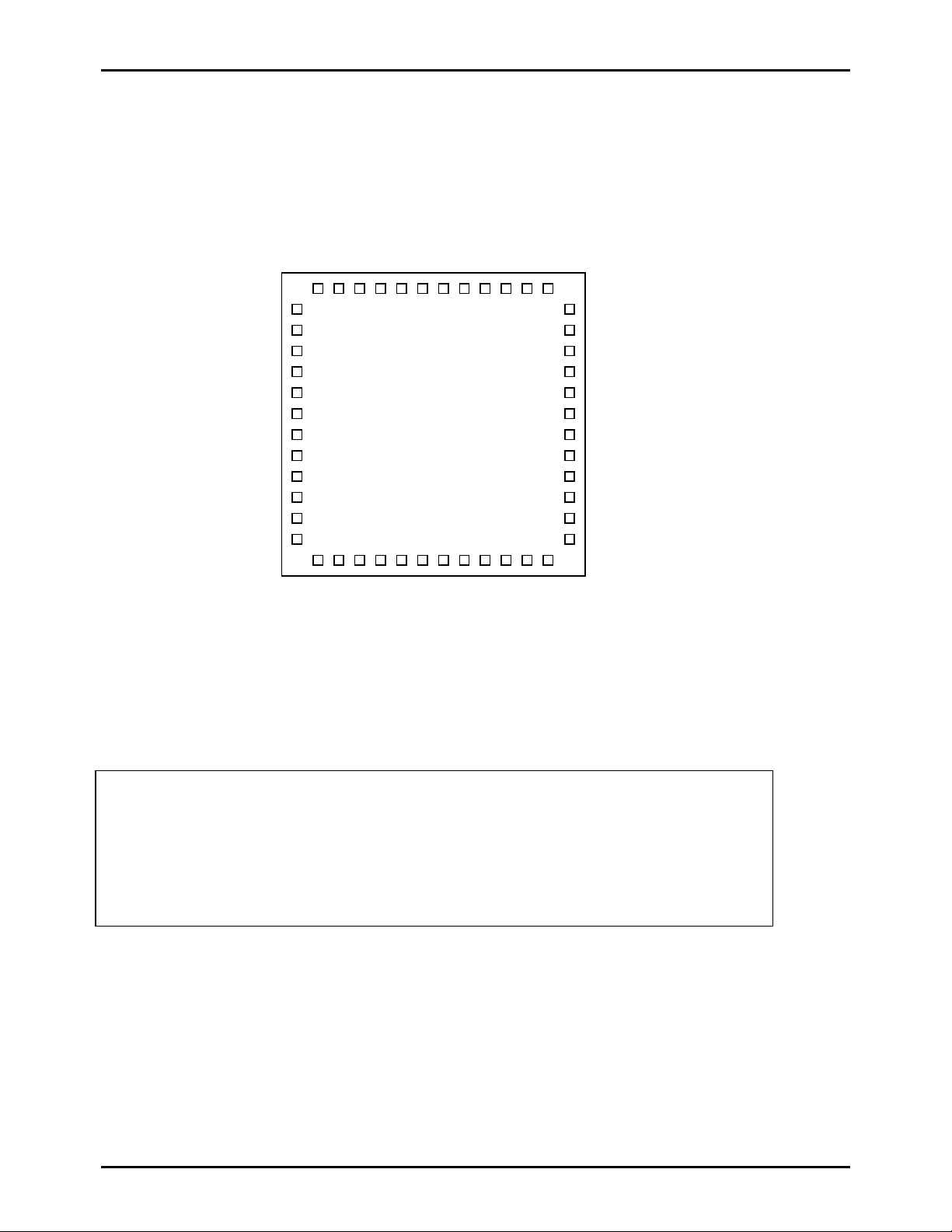

Pad assignment

Chip thickness : 480µm

Chip size (X × Y) : 2. 54mm × 2.27mm

Pad size : 120µm × 120µm

Pad pitch : 140µm minimum

SEG1

SEG2

SEG3

SEG4

SEG5

SEG6

SEG7

SEG8

SEG9

SEG10

SEG11

SEG12

Note:

When a Lithium battery has been selected as the power supply, please note the following points.

There are two modes of use for the lithium battery: Backup mode and Normal mode (backup flag off). In backup

mode, the battery potential is applied directly to the oscillation circuit, whereas in Normal mode only half the

battery potential is applied.

Because of the different voltage applied to the oscillation circuit in each mode, there may be a difference in the

generate d o scil lat io n fre quen cy. W hen en ter ing b ac kup mod e a c or re spo ndin g er ro r will a ris e. I f timing acc ura cy

is required (for clocks, etc), please bear in mind the above in the program design.

COM2

TEST

OSCOUT

OSCIN

RES

S1

S2

32Hz

T3

36 35 34 33 32 31 30 29 28 27 26 25

37

38

39

40

41

42

43

44

45

46

47

48

1 2 3 4 5 6 7 8 9 10 11 12

S4

S3

M1

COM3

VSS

OUT

BA

VDD2

VDD1

CUP2

M2

CUP1

COM4

COM1

SEG25

24

SEG24

23

SEG23

22

SEG22

21

SEG21

20

SEG20

19

SEG19

18

SEG18

17

SEG17

16

SEG16

15

SEG15

14

SEG14

13

SEG13

No.6726-3/18

LC573202A

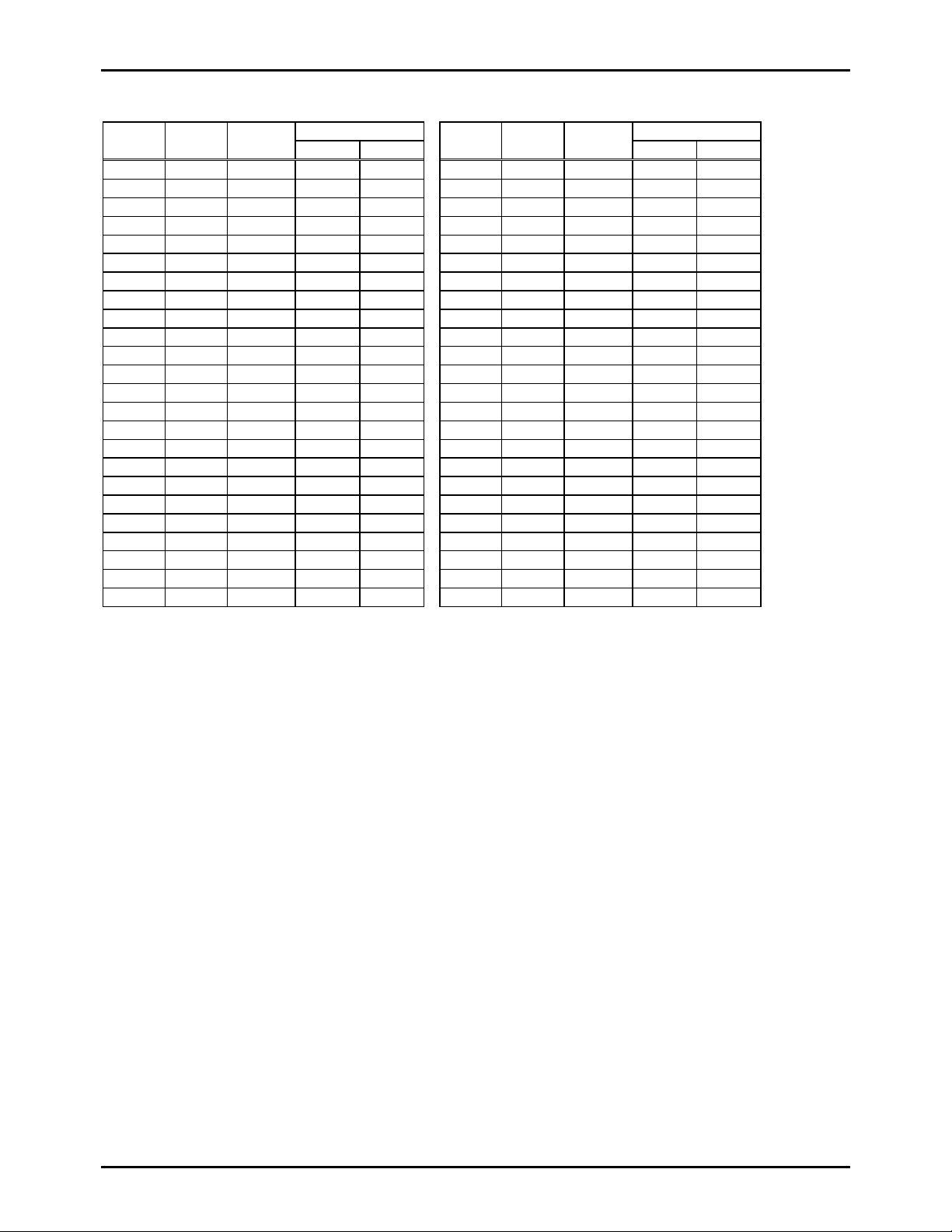

Pad name and coordinates

Pad

PIN No.

1 1 COM3 -700 -1030 25 25 COM1 840 1030

2 2 OUT -560 -1030 26 26 CUP1 700 1030

3 3 VDD2 -420 -1030 27 27 CUP2 560 1030

4 4 VDD1 -275 -1030 28 28 T3 420 1030

5 5 BAK -135 -1030 29 29 32HZ 280 1030

6 6 VSS 5 -1030 30 30 S2 140 1030

7 7 S4 145 -1030 31 31 S1 0 1030

8 8 S3 285 -1030 32 32 RES -140 1030

9 9 M1 425 -1030 33 33 OSCIN -280 1030

10 10 M2 565 -1030 34 34 OSCOUT -420 1030

11 11 COM4 705 -1030 35 35 TEST -560 1030

12 12 SEG13 845 -1030 36 36 COM2 -700 1030

13 13 SEG14 895 -775 37 37 SEG1 -895 765

14 14 SEG15 895 -635 38 38 SEG2 -895 625

15 15 SEG16 895 -495 39 39 SEG3 -895 485

16 16 SEG17 895 -355 40 40 SEG4 -895 345

17 17 SEG18 895 -215 41 41 SEG5 -895 205

18 18 SEG19 895 -75 42 42 SEG6 -895 65

19 19 SEG20 895 65 43 43 SEG7 -895 -75

20 20 SEG21 895 205 44 44 SEG8 -895 -215

21 21 SEG22 895 345 45 45 SEG9 -895 -355

22 22 SEG23 895 485 46 46 SEG10 -895 -495

23 23 SEG24 895 625 47 47 SEG11 -895 -635

24 24 SEG25 895 765 48 48 SEG12 -895 -775

No.

Pad

Name

Coordinates Coordinates QFP64

Xµm Yµm

QFP64

PIN No.

Pad

No.

Pad

Name

Xµm Yµm

• The pad coordinates are such that the chip center is taken as the origin and the va lues for (X, Y) represent the coordinates of

the center point of each pad.

• Substrate must be connected to VSS or left open.

No.6726-4/18

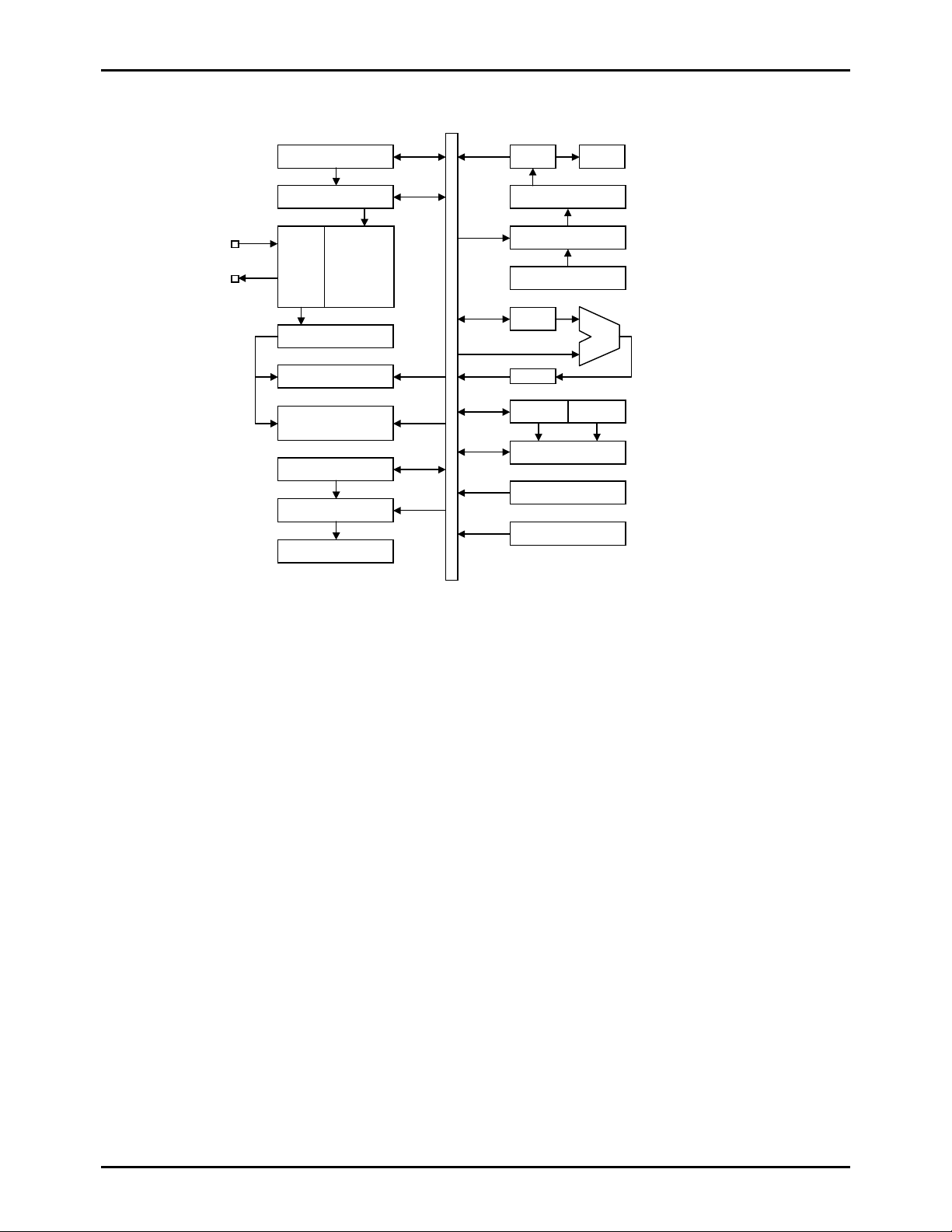

System Bl ock Diagram

HALT mode control

Stand-by control

X’tal

or

RC

Chronograph counter

Melody/buzzer

SEGMENT PLA

Clock

generator

Base timer

circuit

Strove pointer

LCD driver

LC573202A

IR PLA

ROM

PC

Stack

AC

ALU

TMP

DPL DPH

RAM

S port

M port

No.6726-5/18

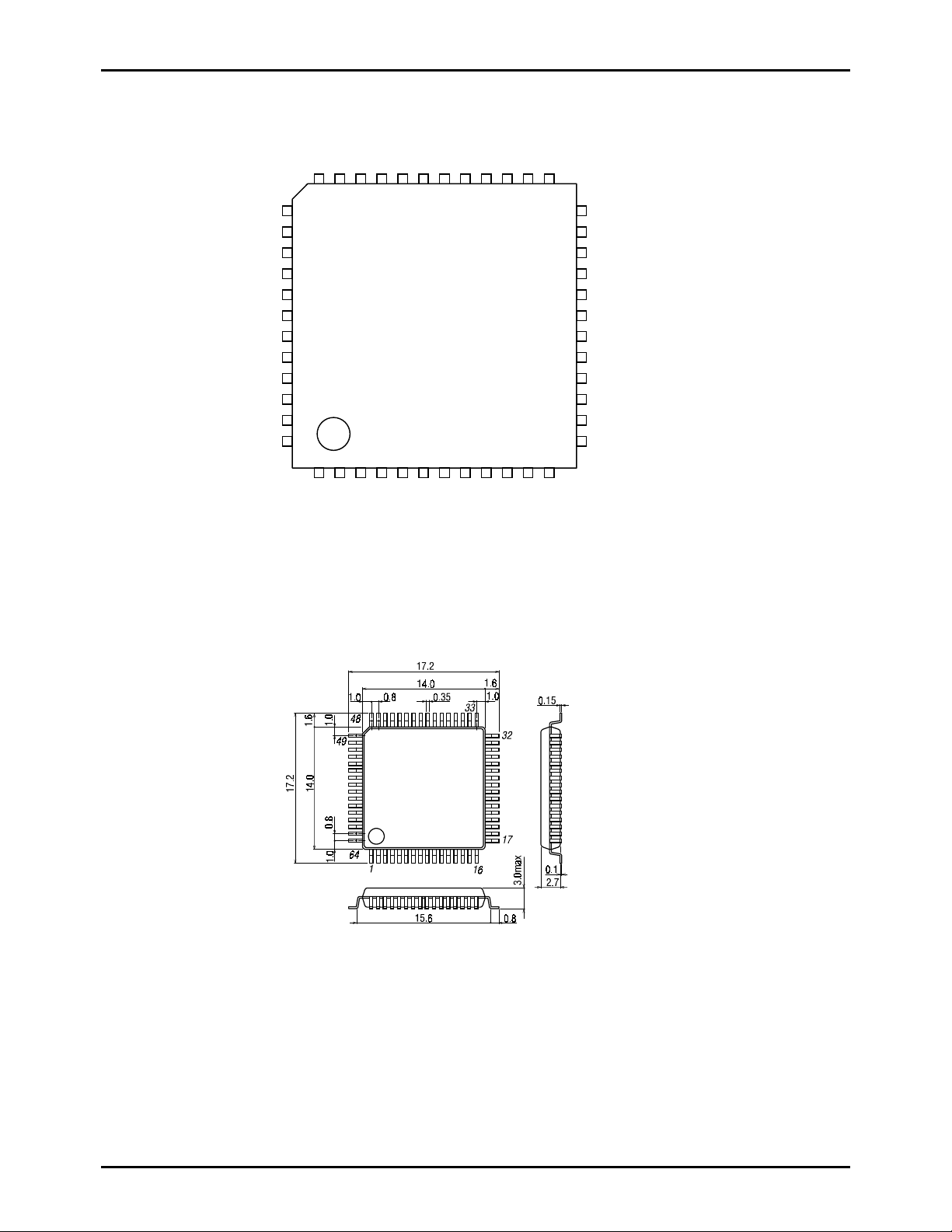

Pin Assignment

T

K

SEG1

SEG2

SEG3

SEG4

SEG5

SEG6

SEG7

SEG8

SEG9

SEG10

SEG11

SEG12

Package Dimension

(unit : mm)

3159

LC573202A

COM2

TEST

OSCOUT

OSCIN

RES

S1

S2

32Hz

T3

CUP2

36 35 34 33 32 31 30 29 28 27 26 25

37

38

39

40

41

42

43

44

45

46

47

48

1 2 3 4 5 6 7 8 9 10 11 12

S4

S3

M1

M2

COM3

OU

VSS

BA

VDD2

VDD1

CUP1

COM4

COM1

SEG25

24

SEG24

23

SEG23

22

SEG22

21

SEG21

20

SEG20

19

SEG19

18

SEG18

17

SEG17

16

SEG16

15

SEG15

14

SEG14

13

SEG13

SANYO : QIP-64E

No.6726-6/18

Loading...

Loading...