Page 1

TOKYO OFFICE

Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

Telephone: 81-(0)3-3837-6339, 6340, 6342, Facsimile: 81-(0)3-3837-6377

•

SANYO Electric Co.,Ltd. Semiconductor Company Homepage

URL; http://www.semic.sanyo.co.jp/index_e.htm

This catalog provides information as of February, 2004. Specifications and information herein are subject to change without notice.

Printed in Japan / February 2004 2k PC Plan

Ordering number : EP58B

Digital TV, Analog TV,

Flat Panel Display, and VCR ICs

'04-2

Page 2

TV IC Lineup that Has Earned the

Top Market Share

CONTENTS

Digital TV Decoder System Chipset

Digital TV TS + Audio + Video Decoder IC with Built-in OSD Function

Digital TV 32-Bit RISC Microcontroller

Flat Panel Display Video Signal-Processing ICs

Scan Converter IC for Flat Panel Displays

Video Signal Processor

8-Bit Flash Microcontroll

2

Color TV I

Built-in CTV Microcontroller Signal-Processing System ICs

SUSOCTMLA76930 Series

Signal-Processing IC with Integrated Microcontroller

2

I

C Bus Control Lineup LA76810 Series

Vertical Output IC

LC863 Series

TV Control Microcontrollers (LC863 Series)

VHS Format VCR System Chip Set

Tuner IC

VIF/SIF Signal-Processing Circuit

PAL Hi-Fi Audio Signal Record and Playback Processing

Hi-Fi Signal Processing HiFi Processing with Built-in Audio Multiplex

Decoder for US Market Products

Hi-Fi Signal Processing HiFi Processing with Built-in Audio Multiplex

Decoder for Japanese Market Products

Video and Audio Signal-Processing IC

VCR SECAM Chrominance Signal-Processing IC

On-Screen Display Controller IC

VPS/PDC Slicer IC

VHF Band RF Module

PWM Capstan + Sensorless Drum + Loading Motor Drivers

Package Dimensions

: SUSOC

✽

These flash memory products are manufactured and sold by SANYO Electric Co., Ltd.

under license from Silicon Storage Technologies, Inc. (SST).

C Bus System Chip Set

.......................................................................................................................41.42

TM

is a trademark of SANYO Electric Co., Ltd.

.......................................................................................................10

er

..............................................................................................11.12

...................................................................................................24 to 34

s

.....................................................................................................35 to 36

.............................................................................................................60

.. ....................................................................................................61.62

............................................................................................64 to 66

....................................................................................6

....................................................................................15.16

.......................................................................19 to 23

...............................................................................43 to 49

..........................................................................................51

................................................................................52

........................................................................53 to 55

.................................................................................57 to 59

..................................................................3.4

........................................5

............................................7.8

...............................................................................9

.................................................................13.14

.........................................................17.18

.................................................................37 to 38

.................................................................39.40

.......................................................50

..................................................................56

....................................................63

New proposals from SANYO, the industry leader in

New proposals from SANYO, the industry leader in

TV IC sales worldwide.

TV IC sales worldwide.

SANYO has now developed the SUSOC(TM) series of

SANYO has now developed the SUSOC(TM) series of

on-chip microcontroller TV signal-processing ICs

on-chip microcontroller TV signal-processing ICs

that support all TV signal standards worldwide.

that support all TV signal standards worldwide.

SANYO was also one of the first companies to

SANYO was also one of the first companies to

respond to digital TV system needs with devices

respond to digital TV system needs with devices

based on SANYO's industry-leading bipolar technology.

based on SANYO's industry-leading bipolar technology.

SANYO provides powerful support as the curtain rises

SANYO provides powerful support as the curtain rises

on full-scale adoption of digital TV.

on full-scale adoption of digital TV.

For worldwide TV, for next generation TV,

For worldwide TV, for next generation TV,

SANYO ICs can help you open new markets worldwide.

SANYO ICs can help you open new markets worldwide.

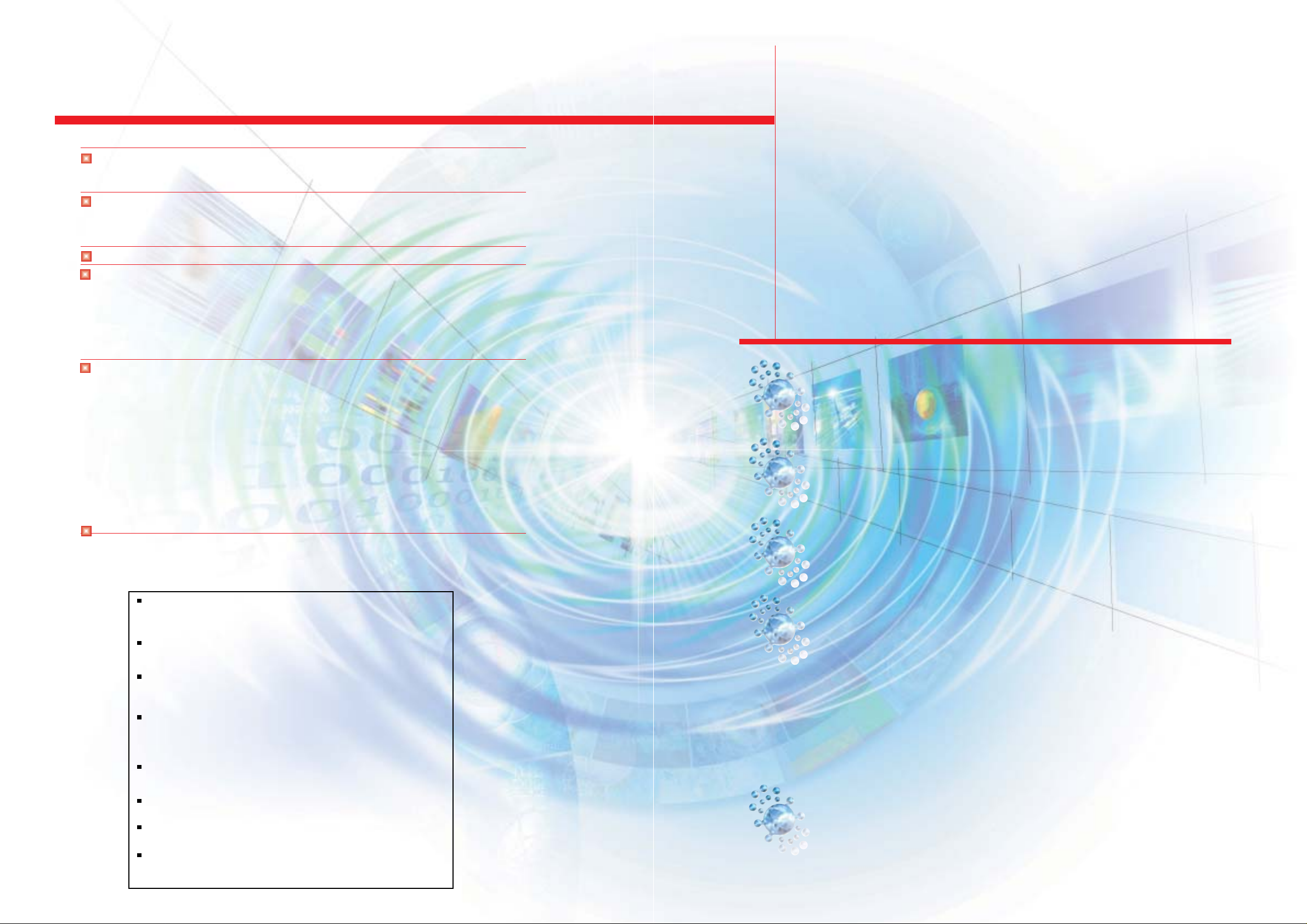

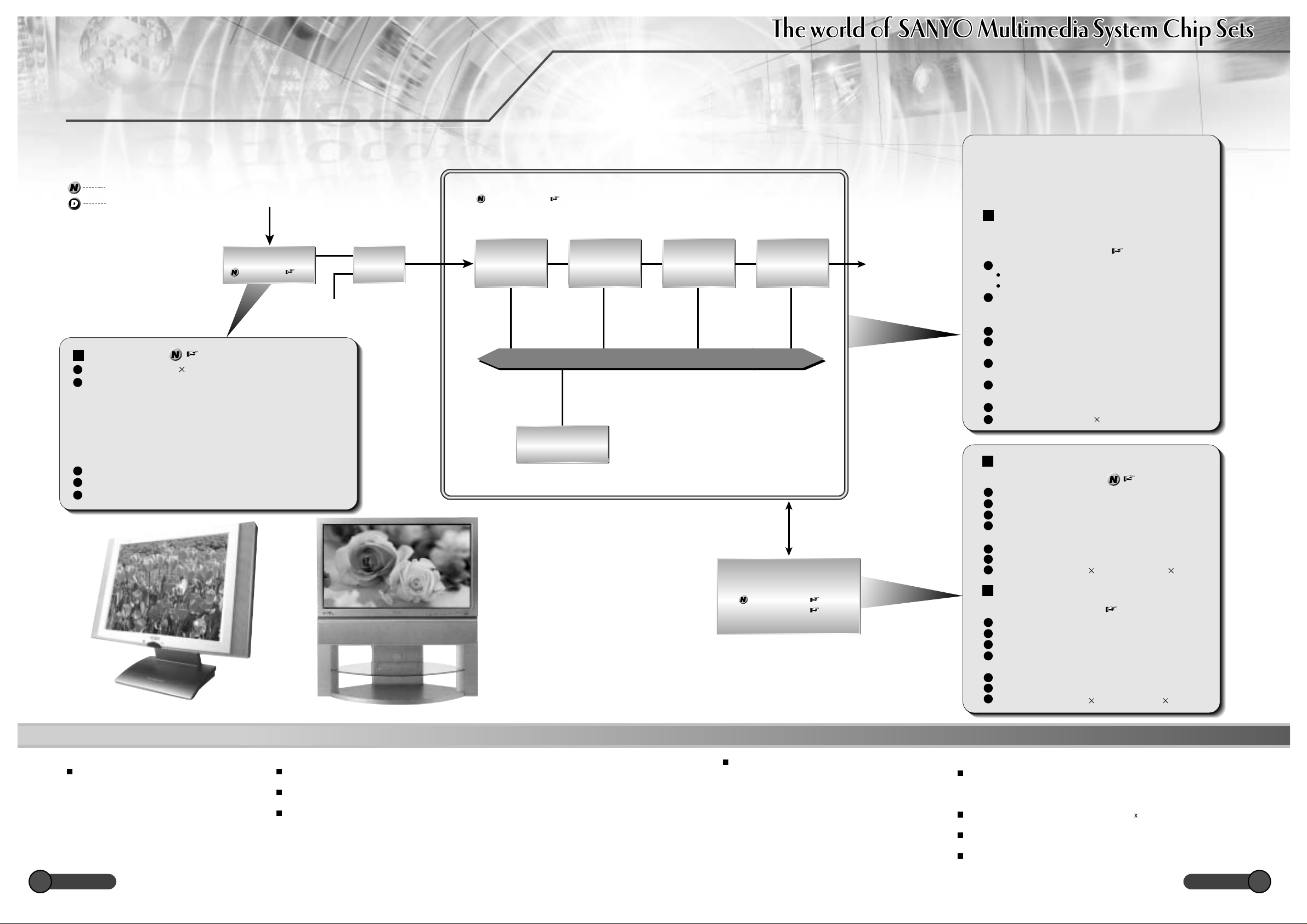

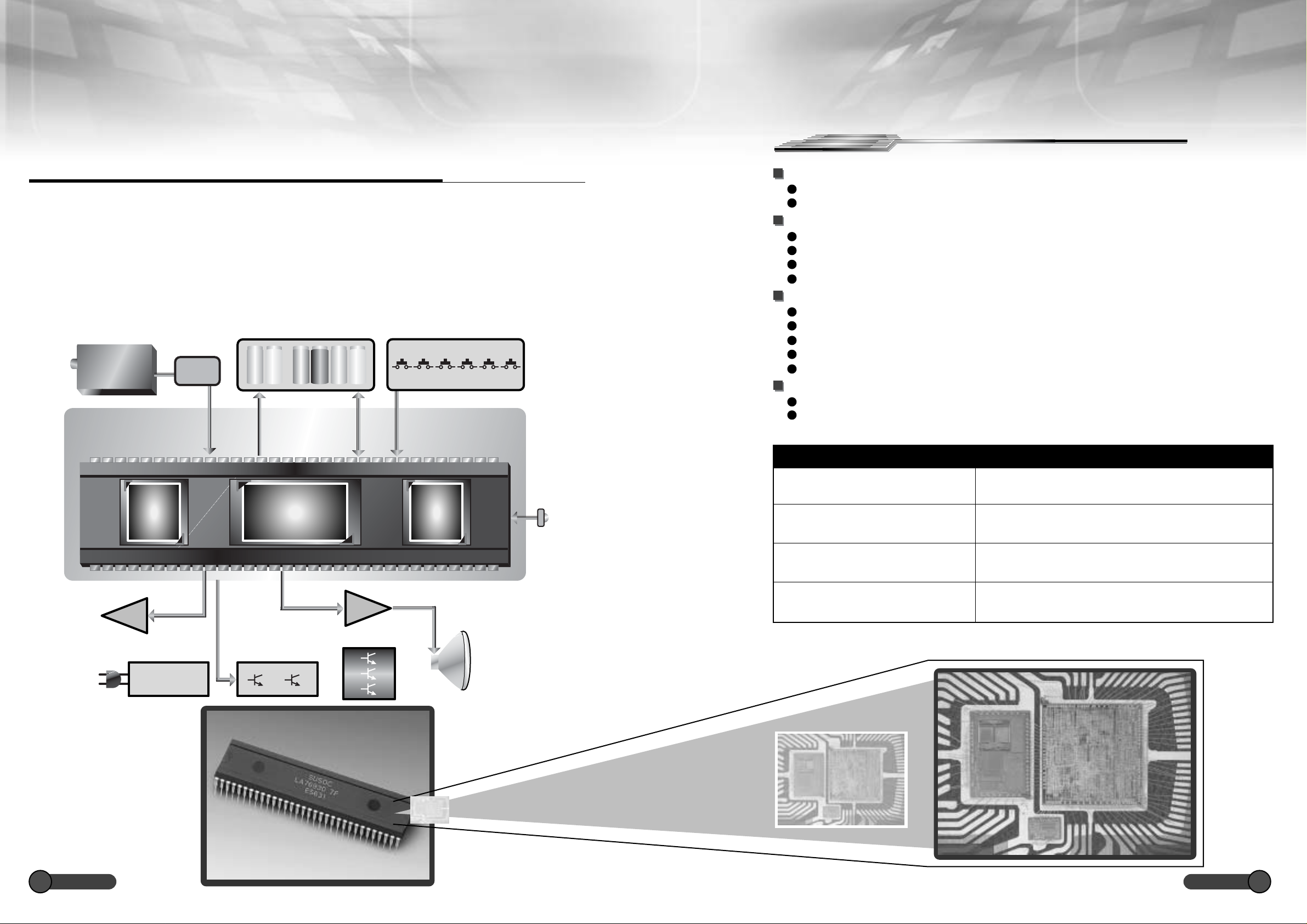

Digital TV Decoder System Chip Set

SANYO 480i / 480p down decoder chipsets support both digital

satellite broadcast and digital terrestrial broadcast reception,

and are optimal for compact and popularly-priced TV sets.

Color TV I

SANYO's extensive lineup of color TV I

2

C Bus System Chip Set

2

C bus control system ICs

support design and manufacture of products appropriate for any

and all markets.

TM

SUSOC

Built-in CTV microcontroller TV signal-processing system ICs

Full lineup that covers all worldwide markets

Global pin-compatible series (Multiformat, PAL/NTSC, NTSC)

Any and all SANYO products described or contained herein do not have specifications that can handle

applications that require extremely high levels of reliability, such as life-support systems, aircraft's

control systems, or other applications whose failure can be reasonably expected to result in serious

physical and/or material damage. Consult with your SANYO representative nearest you before using

any SANYO products described or contained herein in such applications.

SANYO assumes no responsibility for equipment failures that result from using products at values that

exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other

parameters) listed in products specifications of any and all SANYO products described or contained

herein.

Specifications of any and all SANYO products described or contained herein stipulate the performance,

characteristics, and functions of the described products in the independent state, and are not guarantees

of the performance, characteristics, and functions of the described products as mounted in the customer's

products or equipment. To verify symptoms and states that cannot be evaluated in an independent device,

the customer should always evaluate and test devices mounted in the customer's products or equipment.

SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all

semiconductor products fail with some probability. It is possible that these probabilistic failures could

give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire,

or that could cause damage to other property. When designing equipment, adopt safety measures so

that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective

circuits and error prevention circuits for safe design, redundant design, and structural design.

In the event that any or all SANYO products(including technical data,services) described or

contained herein are controlled under any of applicable local export control laws and regulations,

such products must not be exported without obtaining the export license from the authorities

concerned in accordance with the above law.

No part of this publication may be reproduced or transmitted in any form or by any means, electronic or

mechanical, including photocopying and recording, or any information storage or retrieval system,

or otherwise, without the prior written permission of SANYO Electric Co. , Ltd.

Any and all information described or contained herein are subject to change without notice due to

product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification"

for the SANYO product that you intend to use.

Information (including circuit diagrams and circuit parameters) herein is for example only ; it is not

guaranteed for volume production. SANYO believes information herein is accurate and reliable, but

no guarantees are made or implied regarding its use or any infringements of intellectual property rights

or other rights of third parties.

LC863 Series

The LC863 Series devices are multifunction high-speed 8-bit

CMOS system microcontrollers that include OSD functionality.

This series provides simple and easy support for frequent

specification changes during production ramp up and

specification changes by target application by providing flash

ROM versions instead of the earlier erasable EPROM and

one-time programmable PROM versions.

In addition to the well-received large-capacity display RAM, the

LC864 Series provides a high-performance OSD function that

features increased CGROM capacity and provides a simple

graphics function.

VHS Format VCR System Chip Set

These products support high quality and high reliability in end

products by adopting adjustment-free technologies and

furthermore integrate even more peripheral components on the

same chip. This increased integration density promotes even

further reductions in the required circuit board mounting area.

Page 3

Digital TV Decoder

Digital TV Decoder

SANYO 480i / 480p down decoder chipsets support both digital satellite

SANYO 480i / 480p down decoder chipsets support both digital satellite

broadcast and digital terrestrial broadcast reception and

broadcast and digital terrestrial broadcast reception and

System Chip Set

System Chip Set

New product

Development

are optimal for compact and popularly-priced TV sets.

are optimal for compact and popularly-priced TV sets.

Satellite broadcast

antenna

BS

Terrestrial broadcast

antenna

Terrestrial

broadcast

signals

System-on-chip A/V decoder

LC74152B

MP@HL stream support (down decoding)

480i/480p video output

MPEG2 AAC/BC audio support

Built-in OSD function

NTSC encoder

Uses two external 64 Mbit SDRAMs

Supply voltage: 1.8 V/3.3 V

Package: PGBA352

P 5

Tuner

Tuner

Single-chip AV decoder

LC74152B

TS demultiplex

Descrambler

Microcontroller for digital TV

LC74186E

Peripheral

P 5

P 6

MPEG2

video decoder

OSD

controller

IBM PowerPC

Host bus

R

Audio decoder

Video scaler

D/AEncoder

D/A

Video

output

Audio

output

Digital TV microcontroller

LC74186E

IBM PowerPC

Includes UART, I

and PIO interfaces

Supply voltage: 3.3 V

Package: PQFP208

R

2

C, Smart Card, SIO,

P 6

: The following are trademarks of International Business Machines Corporation in the

✽

Unaited States,or other countries,or both. IBM,PowerPC

R

Extensive Lineup Provides Full System Support

RF amplifier transistors

Ultrahigh frequency transistors

2SC4869, 2SC5225, 2SC5501,

2SC5503, SBFP420M

TV tuner and VCR transistors

PicoGET Series

15GN01M, 55GN01M

SANYO TV . VCR SANYO TV . VCR

3 4

Power supply system peripheral transistors

High breakdown voltage MOSFET series

Ultralow on-resistance MOSFET series

Ultraminiature lightweight PicoMOSTM series

Ultralow saturation voltage MBIT-II transistor series

Low VF Schottky barrier diode series

PicoTR series

Muting circuit block

Muting transistor series

Page 4

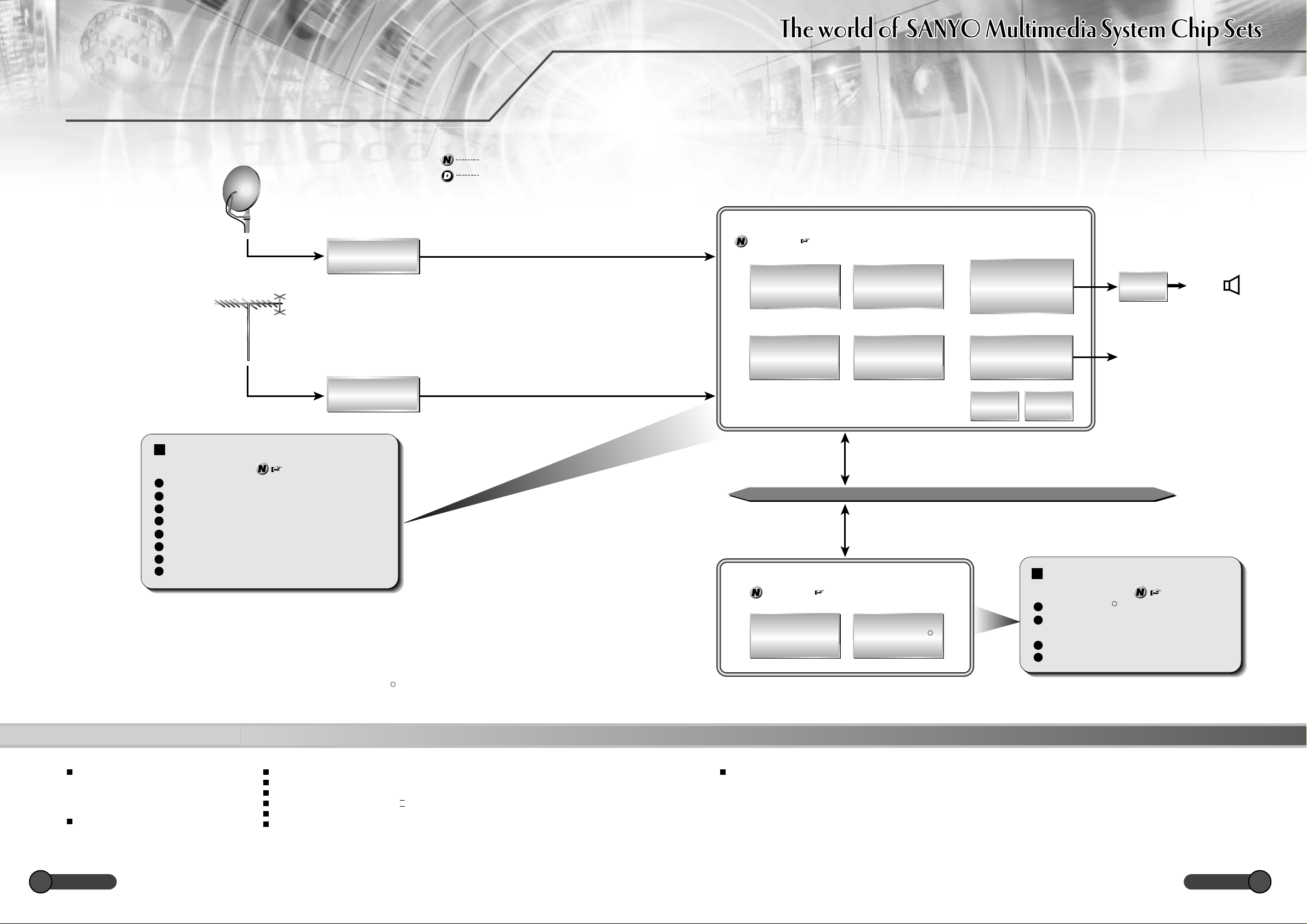

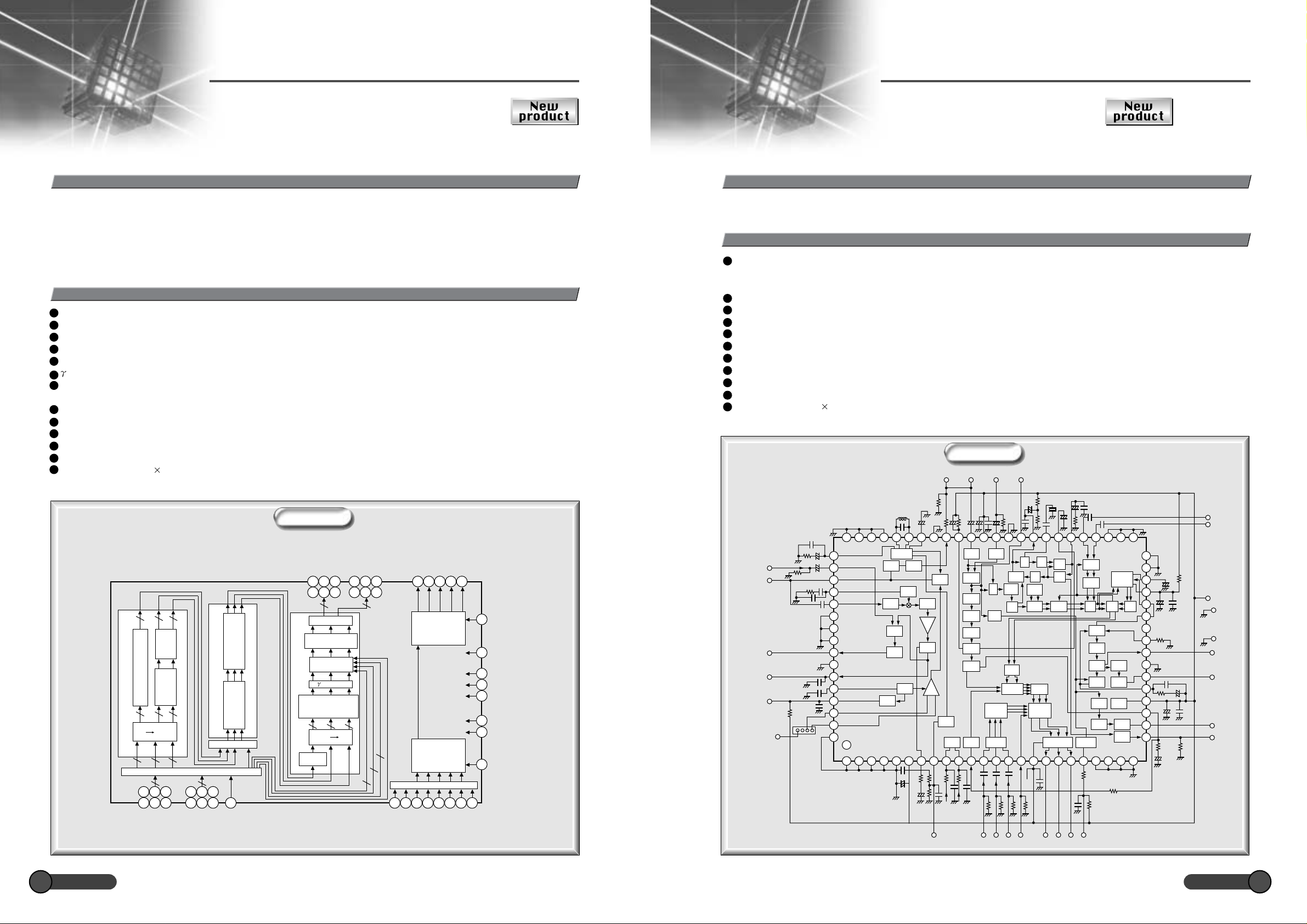

Digital TV TS + Audio + Video Decoder IC

with Built-in OSD Function

LC74152B

Overview

The LC74152B is a digital TV decoder IC that integrates MPEG2 video decoder, AAC audio decoder, transport stream decoder, data

broadcast OSD, video scaler, and NTSC encoder functions on the same chip.

The video decoder down decodes the HDTV stream to 480i/480p. The digital TV backend block can be implemented by combining

this IC with a system controller (CPU).

Functions

[TS Decoder Block]

Supports two TS channel inputs

8-bit parallel TS inputs

Either internal or external synchronization can be selected

Supports up to 55 indexes. The PID and channel number can

be set for each index.

[Video Decoder Block]

Down decodes the HD stream to 480i/480p

Supports two-channel HD down decoded playback,

two-channel HD down decoded plus 480p normal playback,

and three-channel 480p normal playback

[Audio Decoder Block]

MPEG AAC 5.1 channel decoding (with the output mixed

down to two channels)

MPEG BC decoding

[OSD Block]

Supports both 480i and 480p display

Supports both the 16 bits per pixel YUV 422 format and the

8 bits per pixel CLUT8 format

[Scaler Block]

Two scalers are provided, supporting two-screen structures or

video recording output

Supports satellite broadcast multi-view 3-screen display

[Encoder Block]

NTSC interlaced encoding

Can generate two video output systems

Supply voltage: 1.8 V (internal), 3.3 V (I/O)

Package: PBGA352 (35 35)

Digital TV 32-Bit RISC Microcontroller

LC74186E

Overview

The LC74186E is 32-bit microcontroller for digital TV that uses the IBM PowerPC as its CPU core and integrates on a single chip a

wide range of peripheral functions, including UART, I

2

C bus control, timer, synchronous serial port, parallel port, external SDRAM

control, and external bus control functions.

: The following are trademarks of International Business Machines Corporation in the

✽

Unaited States,or other countries,or both. IBM,PowerPC

R

Functions

[IBM PowerPC (PPC405D4)]

Operation at clock frequencies up to 216 MHz

16 KB instruction cache

16 KB data cache

[External SDRAM Control]

32-bit data bus

Support for two logical banks (two chip select signals)

Support for 4 MB to 256 MB per logical port

[External Bus Control]

Up to 8 ROM, EPROM, SRAM, flash, and slave peripheral

I/O banks (8 CS signals)

Support for both burst and non-burst transfer devices

26-bit address bus, 16-bit data bus

R

SCP (synchronous serial port): 1 channel

UART: 3 channels

2

I

C bus controller: 1 channel (I2C)

Smart Card interface: 1 channel

General-purpose timer (GPT)

General-purpose parallel port (GPIO)

Interrupt controller (UIC)

DMA controller (DMAC)

System clock generator PLL circuit

Supply voltage: 3.3 V

Package: PQFP208 (0.5 mm lead pitch, 28 mm square)

R

27MHz

Host CPU

TSIN1

TSIN2

TSOUT

(32bit 2M)

CPUIF

TS

VIDEO

AUDIO

(Main output: video recording output)

DAC I/F

Block Diagram Block Diagram

SDRAM

DIT(PCM&encoded stream)

SDRAM

(32bit 2M)

Arbiter

SCALER

OSD with

ISDB support

NTSC encoder

VDAC

VDAC

16-bit digital video interface

(SD input, main output)

8-bit digital video interface

(Recording output)

Three analog video channels

(Main outputs: Y.Pb.Pr/Y.C)

Three analog video channels

(Subsidiary output

: Y/C composite video)

Debugging

interface

ROM/SRAM control SDRAM control

ROM/SRAM

external

bus controller

Arbiter

Instruction

cache

JTAG

port

PPC405core

Memory management unit

Execution unit

Time

SDRAM

controller

Data

cache

16KB16KB

PLB

DMA control

DMA

controller

PLB/OPB

bridge

Interrupt

controller

OPB

Clock generator

PLL

Parallel port Parallel port

General-purpose timer

Smart Card interface

Asynchronous serial port Asynchronous serial port

Synchronous serial port

2

C bus controller I2C bus control

I

Timer I/O

Smart Card control

Synchronous 3-wire

serial port

Interrupt input

Clock inpu

SANYO TV . VCR SANYO TV . VCR

5 6

Page 5

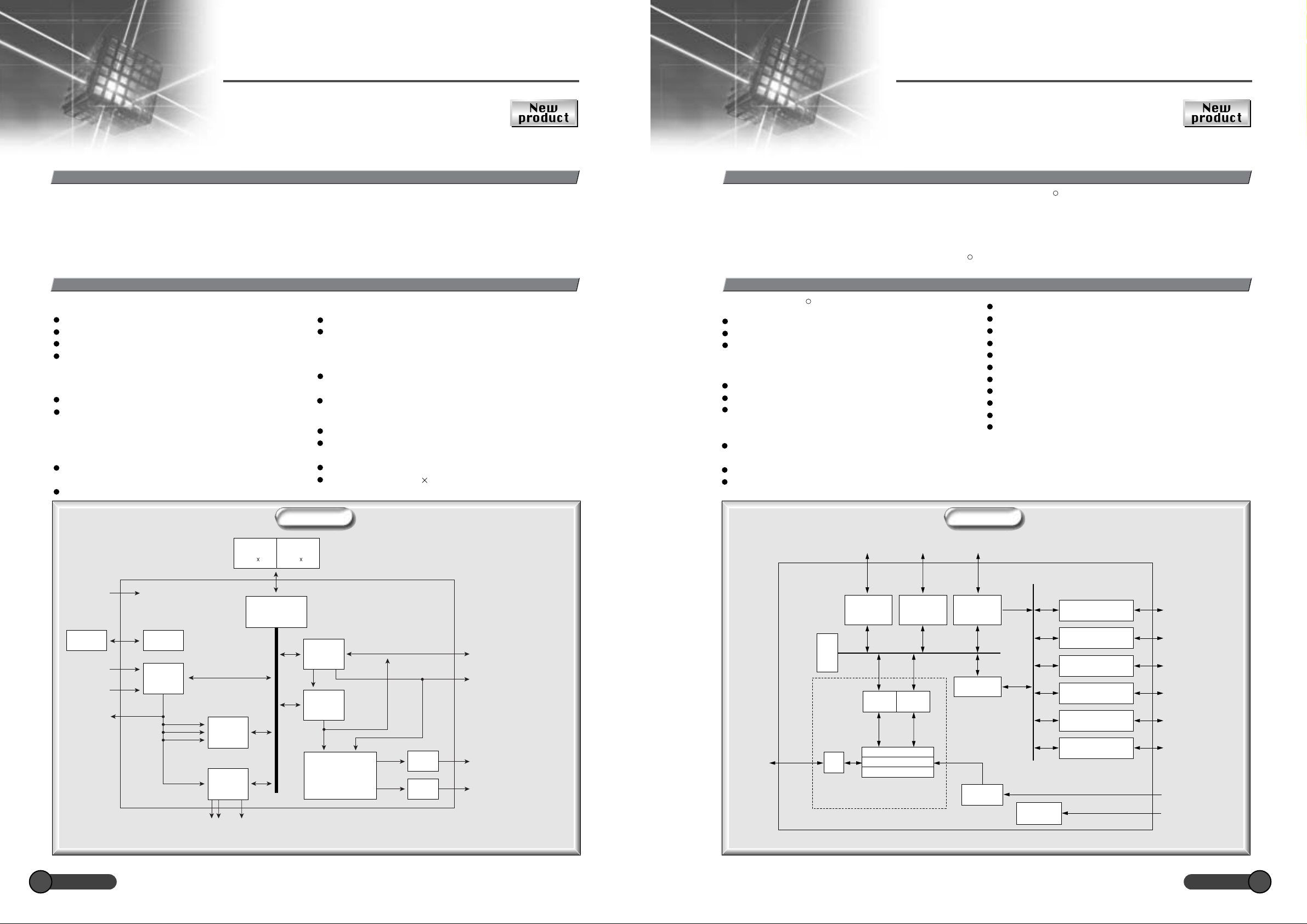

Flat Panel Display Video

Flat Panel Display Video

Home AV Equipment Related DevicesHome AV Equipment Related Devices

Signal-Processing ICs

Signal-Processing ICs

Flat Panel Display System Chipsets

Optimal for Flat Panel Displays

New product

Development

LA7605M

Package: QIP80E (14 20) plastic package (flat package)

Functions: I

audio bandpass filter and trap, Y, C, and deflection

signal processing, CbCr internal (for DVD),

dynamic contrast support, one crystal oscillator

system (with built-in DDS circuit), external OSD

input, HS, VS, and BGP outputs, RGB analog

output

Applications: PAL/NTSC color TV

Supply voltage: 5 V single-voltage power supply

Power consumption: About 1 W

2

C bus controller, adjustment-free VIF/SIF,

P 10

LCD TV PDP TV

TV signal

(NTSC or PAL)

Decoder

LA7605M

Personal computer

(up to XGA resolution)

P 10

video signal

ADC

RGB

FPD video signal-processing IC

LC74986NWF

Input

processing

Timing control

P 9

Data bus

Scaling IP

Resolution

conversion

Picture quality

adjustments

These flash memory products are manufactured and

sold by SANYO Electric Co., Ltd. under license from

Silicon Storage Technologies, Inc. (SST).

SANYO has created video signal processing ICs that adopt high image quality scan

SANYO has created video signal processing ICs that adopt high image quality scan

converter technology and are optimal for flat panel displays.

converter technology and are optimal for flat panel displays.

Conversion of TV signals and

PC video signals to WXGA

resolution using resolution

conversion technology.

Video signal processing IC for

flat panel displays

Output

processing

LCD panel

(up to WXGA

resolution)

LC74986NWF

Support for multiple signal sources

NTSC/PAL and DTV (480i/480p) inputs

Up to XGA progressive scan input

Independent enlargement in the horizontal and

vertical directions. Reduction in the horizontal

direction is also provided.

Interlaced to progressive scan conversion

Built-in OSD function (On-chip 510-character,

8-color, font RAM 8 characters)

2

I

C bus interface (The OSD function can also be

controlled from a 3-wire bus)

Supply voltage: Dual-voltage supply - I/O: 3.3 V,

core: 2.5 V

Maximum operating frequency: 85 MHz

Package: SQFP144

(20 20)

P 9

8-bit flash microcontroller

P 11

P 12

Microcontroller

LC87F57C8A

LC87F5564A

P 11

P 12

LC87F57C8A

Flash ROM: 128 KB

RAM: 3,072 bytes

Minimum bus cycle time: 100 ns (10 MHz)

UART and synchronous serial port

( bus compatible)

12-channel 8-bit A/D converter

PWM: Two variable period 12-bit PWM circuits

Package: QIP64E

(14 14), SQFP64 (10 10)

8-bit flash microcontroller

LC87F5564A

Flash ROM: 64 KB

RAM: 1,024 bytes

Minimum bus cycle time: 100 ns (10 MHz)

UART and synchronous serial port

( bus compatible)

12-channel 8-bit A/D converter

PWM: Two variable period 12-bit PWM circuits

Package: QIP48E

(14 14), SQFP48 (7 7)

Extensive Lineup Provides Full System Support

AC/DC Converter Transistors

High breakdown voltage MOSFET series

2SK2624LS, 2SK2625LS, 2SK2628LS

SANYO TV . VCR SANYO TV . VCR

7 8

DC/DC Converter Transistors

Low saturation voltage transistors

CPH3115, CPH3109

Ultralow on-resistance MOSFETs

FSS140, FS132, FS134, CPH3314, CPH3414

Ultraminiature light weight PicoMOSTM series

2.5V drive: VDSS=30V system, N-channel and P-channel devices

2.5V drive: VDSS=50V system, N-channel and P-channel devices

4.0V drive: VDSS=50V system, N-channel and P-channel devices

Diodes

SBS004, SBS005, SBS006, SBE001, SBE002

Backlight Inverter Transistors

Low saturation voltage transistors

2SC5566, 2SC5706, 2SC5707,

CPH3216, CPH3205, CPH3212, CPH3223,

CPH3115, CPH3109, CPH3116, 2SA2039

Dual device single package products (PNP 2)

CPH5503, CPH5504 ,CPH5506, CPH5508

Dual device single package products (PNP + NPN)

CPH5506

MOSFETs

FW332, FW351, FW238, FW256

Page 6

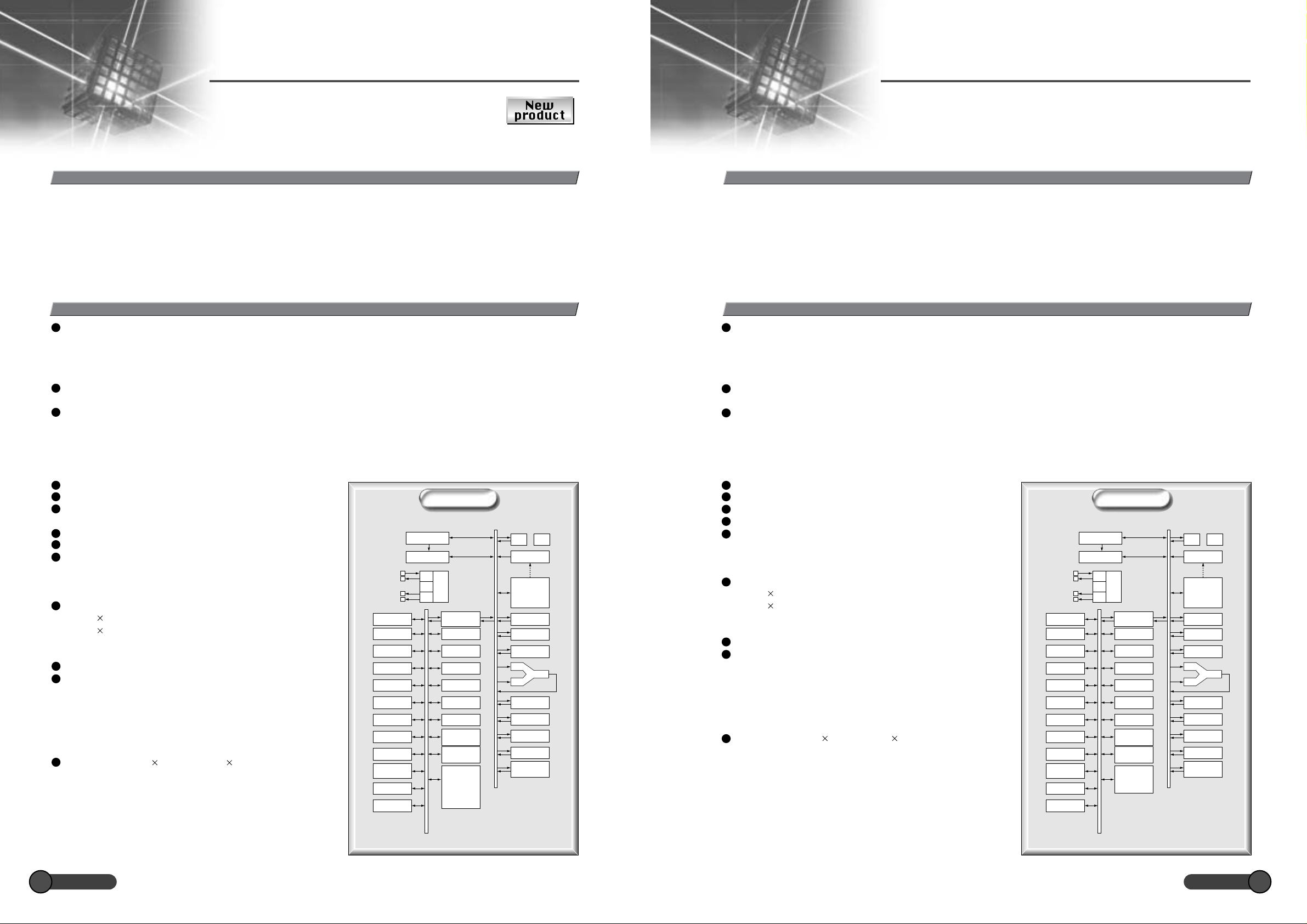

Scan Converter IC for Flat Panel Displays

LC74986NWF

Overview Overview

The LC75986NWF is a video signal processing IC that performs resolution conversion, IP conversion, and image quality corrections

without requiring external memory. It can convert and display a wide variety of video signal formats for display on a flat panel

display. In particular, its image quality correction function adjusts the image quality to be optimal for display on a flat panel.

Its OSD function can display characters with a size optimal for the panel used. A video signal processing system for flat panel

displays can be implemented easily by combining this IC with video converter, A/D converter, and microcontroller ICs and an

LCD panel.

Functions

NTSC/PAL and DTV (480i/480p) inputs: YCbCr digital 8-bit signal inputs

Up to WXGA progressive scan input: RGB digital 8-bit signal input

Independent enlargement in the horizontal and vertical directions. Reduction in the horizontal direction is also provided.

Interlaced to progressive scan conversion

Image quality adjustment function (sharpness, color, tint, black stretch, brightness, contrast, white balance, black balance)

correction circuit (Look-up table system. Common characteristics for each 8-bit RGB color can be programmed.)

Single RGB 24-bit or 18-bit signal output or dual RGB 48-bit or 36-bit signal output (with built-in bit depth simulation and

conversion functions)

No external frame memory required (Input and output have the same frame period)

Built-in OSD function (On-chip 510-character 8-color, font RAM 8 characters)

2

I

C bus interface (The OSD function can also be controlled from a 3-wire bus)

Supply voltage: Dual-voltage supply - I/O: 3.3 V, core: 2.5 V

Maximum operating frequency: 85 MHz

Package: SQFP144 (20 20)

The LA7605M is a flat panel display color TV signal-processing I2C bus controller IC that supports all the broadcast standards used

worldwide.

Functions and Features

VIF/SIF bloc

· Adjustment-free VCO, 4-mode audio trap/audio bandpass filter, buzz canceller

· RF AGC/video level

Single crystal color system: PAL and NTSC

Black stretch, sharpness control with coring on/off control, built-in variable Y system filters (Y-DL and chrominance trap)

Chrominance bandpass filter, demodulation ratio/angle control, support for CbCr input

VS, HS, and BGP outputs, C-sync output, FSC output

Dynamic contrast control

VIF, SIF, video, and sync separator circuits with superlative weak field and nonstandard signal characteristics

Adjustment-free VIF/SIF, audio trap, and audio bandpass filters

Horizontal resonator-less adjustment-free system

Supply voltage: VCC: 5 V

Package: QIP80E (14 20)

Video Signal Processor

LA7605M

Block Diagram

INT-V IN

(S-C:IN)

EXT-V

SVO

IN

VIDEO

OUT

Y

SHARPNESS

Input Processing

Y

RGB Y Cb Cr

88

Data

24 24

VPA1[7:0]

Cb

COLOR TINT

Cb

8

135125117

128118110

VPA3[7:0]

VPA2[7:0]

Cr

Cr

Select

107

9989

100

9282

1

1

VPB2[7:0]*

VPB1[7:0]*

Horizontal and vertical

direction enlargement

Scaling Processing

Horizontal direction

reduction

Select

81

1

VPBEN

VPB3[7:0]*

Block Diagram

External

voltage

signals

BOUT[7:0]

GOUT[7:0]

ROUT[7:0]

716151

645444

OSD

Bit depth conversion

processing

MIX

correction

White balance

Output Processing

Contrast, Black balance

Brightness

RGB

Y Cb Cr RGB

Black

stretch

1

1

1

BOUT_2[7:0]*

GOUT_2[7:0]*

ROUT_2[7:0]*

107

9989

100

9282

2424

B

8

G

8

R

8

VSI

VS0

Output Timing

Input Timing

142 143141140

HSI

DEVI

HS0

Select

DEHI

DEV0

CLKI

DEH0

3438394041

2

VPBH

DCLK0

3117355

VPBCK

VPBV*

DCLKI

26

XTAL

25

AIC

19

AIDA

18

2

17

AICS*

SCL

14

SDA

13

CLKIEN

4

*1, *2: Register selectable

EXT AUDIO INT

S CARRIER OUT

AUDIO OUTPUT

PM OUT

RF AGC

IF IN

Ω

1k

F

µ

VCO

F

µ

TRAP

BPF

0.47

A2C

PLL

VIDEO

AMP

SPLL

SW

64

1000P

330

Ω

+

0.47µF

+

10

µ

F

600

Ω

µ

0.01

1k

Ω

1000P

10P

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41

65

66

67

F

68

69

70

71

72

RF

AGC

VOL

CD

IF

AGC

73

74

(M)

75

µ

F

0.01

76

0.022µF

77

µ

F

0.01

30k

Ω

1

78

79

80

2.2

+

Ω

1k

+

VIDEO

DIT

BPF

LIM

AMP

FM

DET

VIF

AFT

BUS DCS CL AMP IRIVE/OUT-OFF C_SYNC

F

µ

Ω

1

680k

+

VIDEO

SW

TRAP

DELAY

LINE

PEAKING

CORING

BLACK

STRETCH

DC

REST

F

µ

100

+

F

µ

0.01

+

CLMPCLMP

SW

SYNC

SEP

OSD

FIX GAIN

ERIGHT

Ω

V/C

F

75

µ

1

GND

BPF

(ON/OFF)

AOC

COLOR

CLAMP

CONTRAST

ERIGHT

123456789101112131415161718192021222324

F(M)

0.01µF

100

Ω

Ω

100k

27k

Ω

+

µ

F

+

100k

F

µ

1

Ω

Ω

100

100

F

µ

0.1

100P

100P

AFT R IN

µ

0.01

G IN

F(M)

µ

0.01

Ω

Ω

75

75

B IN

Ω

µ

F

0.47

24k

+

VXD

APC1

F(M)

µ

0.01

Ω

75

FB IN R OUT G OUT B OUT

P(M)

µ

0.047

TINT

PAL

SW

DEMO

MATRIX

F

µ

10

Ω

10k

RGB

OSD

SW

DOD

+

Ω

24k

16P

APC2

VCO

CLAMP

+

F

µ

0.47

F

µ

1

1000P

Ω

0.1µF

1k

0.1µF

CLAMP

DC ADS

SW

HOR

VCO

1/256

HOR

C/D

AFC1

VER

SEP

VER

C/D

Ω

1k

Ω

30k

C_SYNC OUT

DELAY

+

PHASE

SHIFTER

HOR

OUT

HOR

VCC

VER

OUT

PSC

1k

Ω

CR_IN

CB_IN

40

39

IH

38

37

LPF

36

ALC

35

34

(METUL FILM)

33

32

Ω

F

100

+

µ

10

VCC 5V

F

+

F

µ

µ

10

REF

4.7k

Ω

0.01

GND

GND

BGP

31

F

µ

0.01

Ω

10k

HS

VS

FSC OUT

30

(M)

15000P

29

1µF

3.3k

Ω

28

+

F

µ

27

10

26

25

Ω

1k

+

F

µ

1

SANYO TV . VCR SANYO TV . VCR

9 10

Page 7

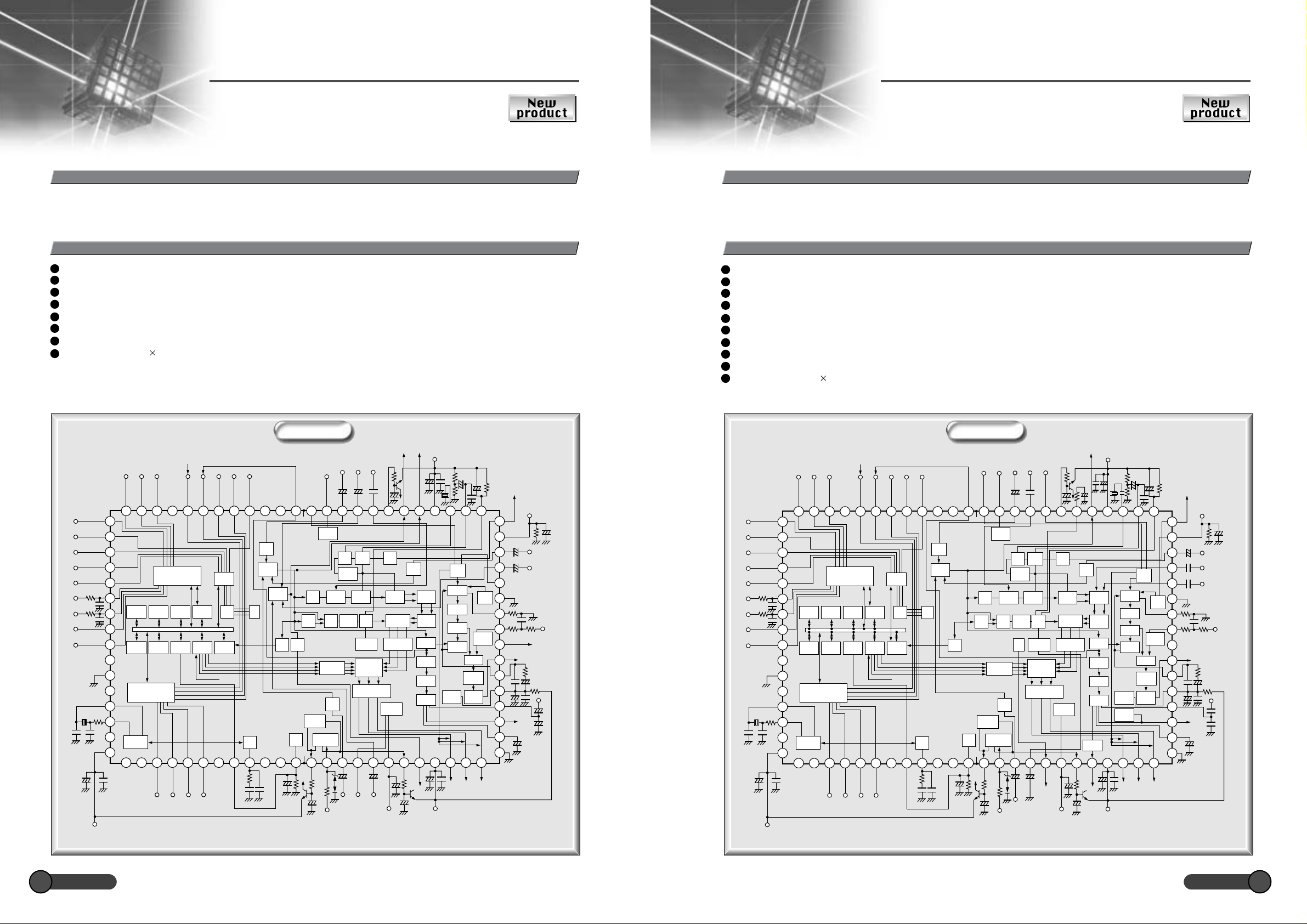

8-Bit Flash Microcontroller 8-Bit Flash Microcontroller

LC87F57C8A

Overview

The LC87F57C8A is an 8-bit microcontroller built around a CPU block that operates with a minimum bus cycle time of 100 ns and

that integrates 128 KB of flash ROM (that supports onboard programming), 4 KB of RAM, and an extensive set of peripheral

functions on a single chip. The peripheral functions include two multifunction 16-bit timer/counters (that can be used as separate

8-bit counters), four 8-bit timers with prescalers, a clock time base timer, two synchronous SIO channels that provide an automatic

transfer function, one asynchronous/synchronous SIO channel, two 12-bit PWM circuits, a 12-channel 8-bit A/D converter, a highspeed 8-bit parallel interface, a high-speed clock counter, a system clock divider function, and an interrupt function that supports 20

interrupts and 10 vector locations.

Functions

Timers

· One 16-bit timer/counter with capture register (can also be used as two 8-bit timers)

· One 16-bit timer/counter with PWM/toggle output function (can also be used as two 8-bit timers)

· Four 8-bit timers with 6-bit prescaler function

· Clock time base timer

High-speed clock counter

(Can count a clock signal up to 20 MHz when a 10 MHz main clock frequency is used.)

SIO

· Two 8-bit SIO channels with automatic transfer function

- Two 8-bit baud rate generators included

- Maximum clock: 4/3 tCYC

· One 8-bit asynchronous/synchronous SIO channel

- Asynchronous: 8 to 2048 tCYC, Synchronous: 2 to 512 tCYC

A/D converter: 12-channel 8-bit converter

PWM: two variable-period 12-bit PWM circuits

Parallel interface (switchable polarity, can perform read and write

operations in 1·tCYC)

Remote control receiver

(using the P73/INT3/T0IN shared function pin)

Watchdog timer (Uses an external RC circuit)

Interrupts

· 20 interrupt sources with 10 vector locations (Multiple interrupts

supported using three interrupt levels: low level (L), high level (H),

and maximum level (X))

High-speed multiply and divide instructions

· 16 bits 8 bits (Execution time: 5 tCYC)

· 24 bits 16 bits (Execution time: 12 tCYC)

· 16 bits ÷ 8 bits (Execution time: 8 tCYC)

· 24 bits ÷ 16 bits (Execution time: 12 tCYC)

System clock divider function

Standby functions

· Halt mode: instruction execution stopped, peripheral circuit

operation continues

· Hold mode: instruction execution stopped, peripheral circuit

operation stopped

· Crystal hold mode: instruction execution stopped, peripheral

circuit operation stopped except for the clock time base timer

Package: QIP64E (14 14), SQFP64 (10 10)

SIO 0

SIO 1

SIO 2

Timer 0

Timer 1

Timer 4

Timer 5

PWM0

PWM1

Clock time base

timer

Timer 6

Timer 7

Block Diagram

Interrupt control

Standby control

CF

RC

Clock

X'tal

INT0 to INT3

noise rejection

generator

Bus

interface

Port 0

Port 1

Port 3

Port 7

Port 8

ADC

Port 2

INT4,5

Parallel

interface

Port A

Port B

Port C

IR

PLA

Flash ROM

PC

ACC

Register B

Register C

ALU

PSW

RAR

RAM

Stack pointer

Watchdog

timer

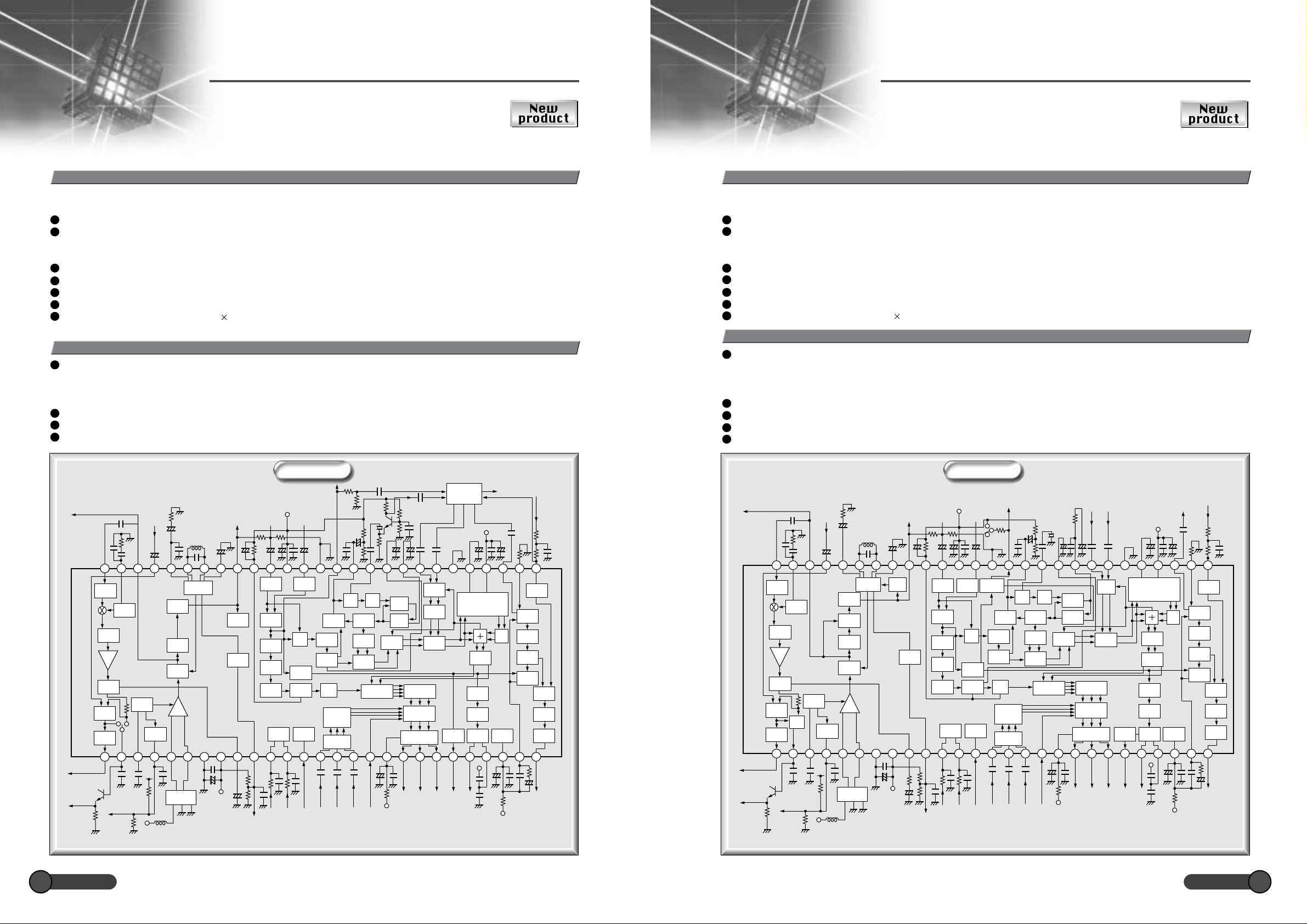

LC87F5564A

Overview

The LC87F5564A is an 8-bit microcontroller built around a CPU block that operates with a minimum bus cycle time of 100 ns and

that integrates 64 KB of flash ROM (that supports onboard programming), 1 KB of RAM, and an extensive set of peripheral functions

on a single chip. multifunction 16-bit timer/counters (that can be used as separate 8-bit counters), four 8-bit timers with prescalers, a

clock time base timer, two synchronous SIO channels that provide an automatic transfer function, one asynchronous/synchronous SIO

channel, two 12-bit PWM circuits, a 12-channel 8-bit A/D converter, a high-speed 8-bit parallel interface, a high-speed clock counter,

a system clock divider function, and an interrupt function that supports 20 interrupts and 10 vector locations.

Functions

Timers

· One 16-bit timer/counter with capture register (can also be used as two 8-bit timers)

· One 16-bit timer/counter with PWM/toggle output function (can also be used as two 8-bit timers)

· Four 8-bit timers with 6-bit prescaler function

· Clock time base timer

High-speed clock counter

(Can count a clock signal up to 20 MHz when a 10 MHz main clock frequency is used.)

SIO

· Two 8-bit SIO channels with automatic transfer function

- Two 8-bit baud rate generators included

- Maximum clock: 4/3 tCYC

· One 8-bit asynchronous/synchronous SIO channel

- Asynchronous: 8 to 2048 tCYC, Synchronous: 2 to 512 tCYC

A/D converter: 12-channel 8-bit converter

PWM: two variable-period 12-bit PWM circuits

Remote control receiver (using the P73/INT3/T0IN shared function pin)

Watchdog timer (Uses an external RC circuit)

Interrupts

· 20 interrupt sources with 10 vector locations (Multiple interrupts

supported using three interrupt levels: low level (L), high level (H),

and maximum level (X))

High-speed multiply and divide instructions

· 16 bits 8 bits (Execution time: 5 tCYC)

· 24 bits 16 bits (Execution time: 12 tCYC)

· 16 bits ÷ 8 bits (Execution time: 8 tCYC)

· 24 bits ÷ 16 bits (Execution time: 12 tCYC)

System clock divider function

Standby functions

· Halt mode: instruction execution stopped, peripheral circuit operation

continues

· Hold mode: instruction execution stopped, peripheral circuit operation

stopped

· Crystal hold mode: instruction execution stopped, peripheral circuit

operation stopped except for the clock time base timer

Package: QIP48E (14 14), SQFP48 (7 7)

SIO 0

SIO 1

SIO 2

Timer 0

Timer 1

Timer 4

Timer 5

PWM0

PWM1

Clock time base

timer

Timer 6

Timer 7

Block Diagram

Interrupt control

Standby control

CF

RC

Clock

X'tal

noise rejection

generator

Bus

interface

Port 0

Port 1

Port 3

Port 7

Port 8

ADC

INT0 to INT3

Port 2

INT4,5

Port A

Port B

Port C

IR

PLA

Flash ROM

PC

ACC

Register B

Register C

ALU

PSW

RAR

RAM

Stack pointer

Watchdog

timer

This flash memory product is manufactured and sold by SANYO Electric Co., Ltd.

under license from Silicon Storage Technologies, Inc. (SST).

SANYO TV . VCR SANYO TV . VCR

11 12

This flash memory product is manufactured and sold by SANYO Electric Co., Ltd.

under license from Silicon Storage Technologies, Inc. (SST).

Page 8

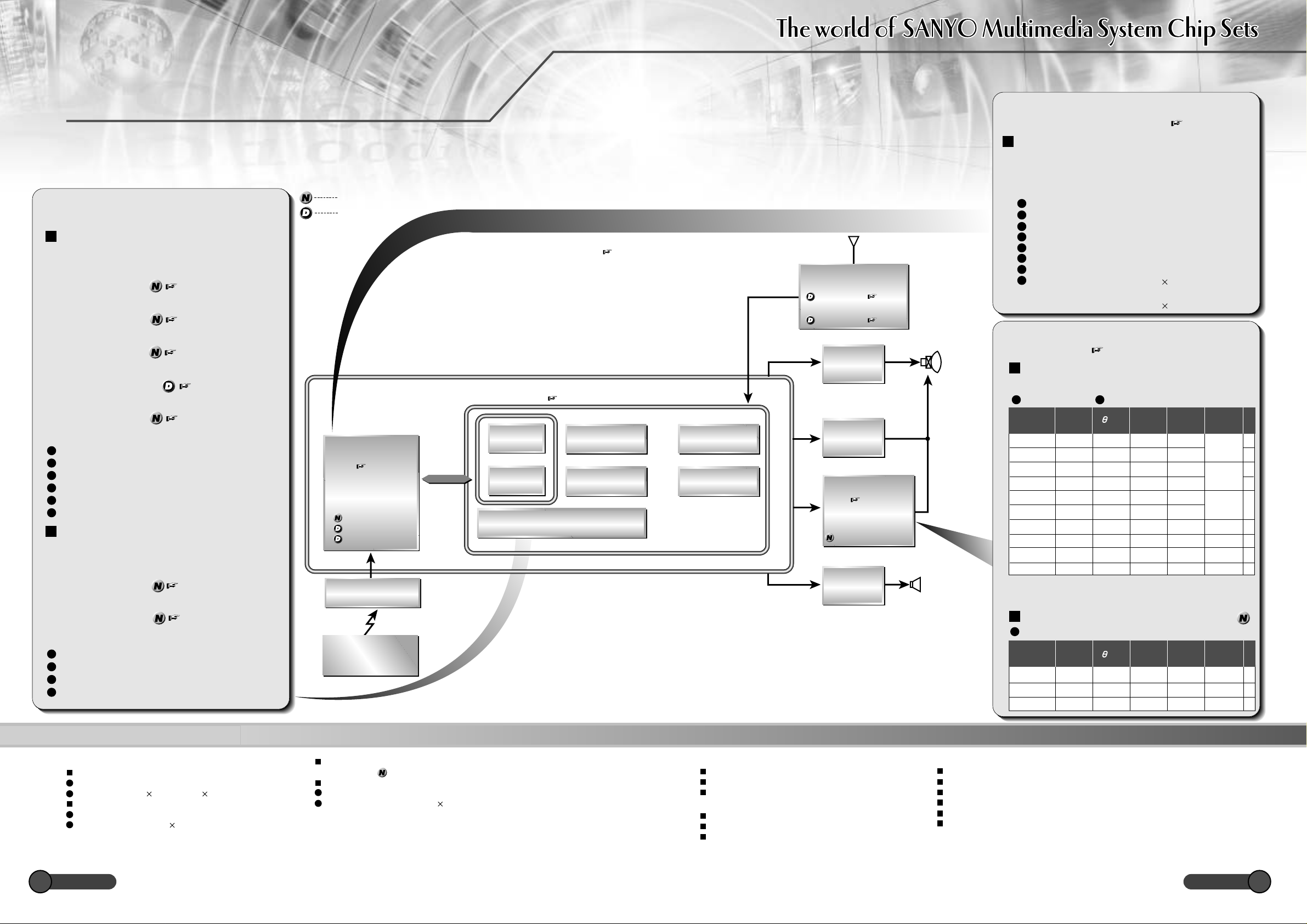

Color TV Bus

Color TV Bus

System Chip Set

System Chip Set

Full lineup of system ICs that feature I2C

bus control

SANYO supports end product design and manufacture appropriate for all markets

SANYO supports end product design and manufacture appropriate for all markets

with a full product line of color TV I2C bus control system ICs.

with a full product line of color TV I2C bus control system ICs.

2

C Bus Control for TV

I

Signal-Processing ICs

P 35~38

TV Control Microcontrollers

LC8632 Series, LC8633 Series

LC8634 Series, LC8635 Series

LC838 Series

ROM: 12 to 64 KB

RAM: 512 to 640 bytes

Caption data slicer (LC8632/LC8634 Series)

Simple graphics function OSD

Multi-master I

ROM correction function

On-chip flash memory microcontrollers for evaluation

Packages:

Full Lineup of I

Output ICs

2

C bus system

DIP42S (600mil), QIP48E (14 14) (LC8632/33 Series)

DIP36S (400mil), MFP36SDJ (375mil) (LC8634/35 Series)

DIP42S (600mil), QIP48E (14 14) (LC838 Series)

2

C Bus Vertical

P 29~

LA7840/41/45N/46N/75/76

78040N/040/041/045

High reliability Low power consumption

Type

No.

LA7840

LA7841

LA7845N

LA7846N

LA7875N

LA7876N

LA78040N

LA78040

LA78041

LA78045

Package

SIP7H

SIP7H

SIP7H

SIP10H

SIP10HD

SIP10H

T0220-7H

T0220-7H

T0220-7H

T0220-7H

4.0°C/W

4.0°C/W

4.0°C/W

3.0°C/W

4.0°C/W

3.0°C/W

3.0°C/W 70V 1.8APP

3.0°C/W 70V 1.8APP

3.0°C/W 70V 2.2APP

3.0°C/W 92V 2.2APP

j-C

Output

voltage

(max)

70V

70V

85V

85V

110V

110V

Output

current

1.8APP

2.2APP

2.2APP

3.0APP

2.2APP

3.0APP

16 to 33V

16 to 38V

16 to 33V

16 to 33V

16 to 33V

16 to 33V

16 to 43V

On-Chip I2C Bus and E/W

Driver Circuits

LA7847, LA7848, LA7849

For large-screen and flat-screen CRT TVs

Type

No.

LA7847

LA7848

LA7849

Package

SIP10HD

SIP10HD

SIP10H

4.0°C/W 72V 2.2APP

4.0°C/W 92V 2.2APP

3.0°C/W 92V 2.2APP

j-C

Output

voltage

(max)

Output

current

V

CC

V

CC

16 to 34V

16 to 43V

16 to 43V

P

24

25

26

27

32

29

28

30

31

P

33

33

34

Full lineup that responds to

market needs

PAL multiformat I2C bus

control system ICs

LA76810 Series

LA76818A

(PAL/NTSC,YCbCr)

LA76828N

(PAL/NTSC,E/W,YCbCr)

LA76835A

(NTSC,E/W support)

LA76835NM

(NTSC,E/W,YCbCr)

LA76843N

(NTSC)

Adjustment-free VIF/SIF

Built-in trap and bandpass filter

Single crystal chrominance system

Built-in horizontal period (1H) delay line

Supply voltage: VCC = 5 V/9 V

Package: DIP54S

(600mil)

P 19

P 20

P 21

P 22

P 23

Signal-processing ICs with

built-in microcontroller

(CPU + VCD)

LA76919M

(NTSC)

LA76922M

(NTSC E/W YCbCr)

Built-in microcontroller TV signal-processing ICs

VCC = 5 V or 9 V

TV signal-processing functions

TV system control microcontroller

P 17

P 18

New product

Development

TV control

microcontrollers

P 35~38

LC8632 Series

LC8633 Series

LC8634 Series

LC8635 Series

LC8638 Series

LC863A Series

LC863B Series

Remote control

receiver block

Remote control

transmitter

microcontroller

LC587XXX Series

SUSOCTM ICs

(LA76930 Series)

P 15

(SANYO Ultimate Super One Chip LSI)

LA76930 (IF+VCD+CPU)

with YcbCr

LA76932 (IF+VCD+CPU)

with YcbCr & E/W

LA76936 (IF+VCD+Micon)

with YcbCr SECAM

LA76938 (IF+VCD+Micon)

with YcbCr & E/W

I2C bus control super single-chip system ICs

LA76810 Series

VIF

I2C bus

SIF

LA76950 (IF+VCD+Micon)

with YcbCr

LA76952 (IF+VCD+Micon)

with YcbCr & E/W

LA7695X (IF+VCD+Micon+3line Comb)

with YcbCr & E/W

P 19~

Video /Chroma

Hori. /Ver.

2

C Bus interface

I

RGB drive

RGB input

✽

These flash memory products are manufactured and

sold by SANYO Electric Co., Ltd. under license from

Silicon Storage Technologies, Inc. (SST).

: SUSOC

Tuner

U/V mixer/OSC.

LA79106V

U/V mixer/OSC.+PLL

LV4512V

Video

output

Horizontal

output

Vertical output

LA7840 Series

LA78040 Series

LA7847/48 Series

LA7849 Series

Audio

output

TM

is a trademark of SANYO Electric Co., Ltd.

P 41

P 42

P 24~34

CRT

Speaker

Extensive Lineup Provides Full System Support

Remote control transmitter microcontrollers

4-bit system-on-chip microcontrollers: LC587XXX series

Built-in LCD display circuit: 92 to 140 segments

ROM capacity: 2K 16 bits to 8K 16 bits

4-bit system-on-chip microcontrollers: LC573400 series

Built-in LCD display circuit: Up to 120 segments

ROM capacity: 4K or 6K 8 bits

SANYO TV . VCR SANYO TV . VCR

13 14

Flash microcontrollers

LC58F7416A lineup

4-bit system-on-chip microcontrollers: LC573100 series

Optimal for low-end remote controls that do not require LCD display

ROM capacity: 1K, 2K, or 4K 8 bits

VHF/UHF Tuner Transistors

High-frequency MOSFET series

High-frequency transistor series (fT=1 to 6 GHz)

PicoGET series

Video Transistors

Horizontal deflection output transistor series

Video output transistor series

Ultralow on-resistance MOSFETs

Power Supply System Transistors

High breakdown voltage MOSFET series

Ultralow on-resistance MOSFET series

Ultraminiature light weight PicoMOSTM series

Ultralow saturation voltage MBIT-II transistor series

Low VF Schottky barrier diode series

PicoTR series

Page 9

Built-in CTV Microcontroller

Built-in CTV Microcontroller

Signal-Processing System ICs

Signal-Processing System ICs

SUSOC

TM

TM

LA76930 SeriesSUSOC

LA76930 Series

FeaturesFeatures

Support for Worldwide Markets with All-in-One ICs

A newly-developed signal-processing IC, a microcontroller, and even a CCD.

There is no one other than SANYO who has included so much functionality in a single package.

Additionally, series deployment with pin-to-pin compatibility* means that users can handle TV

signal standards in different markets around the world by changing only certain specific

components.

These ICs, which SANYO has named SUSOC

powerful support for design and manufacturing for all markets.

: This allows different models to be used with essentially no changes to the pin layout.

✽

AV input

SAW filter

TUNER

TMTM

TM

(SANYO Ultimate Super One Chip), provide

Switch

SUSOCSUSOC

1 chip

1 chip

CCDCCD

++

(IF/V/C/D)

(IF/V/C/D)

CPUCPU

Remocon

RX

General features

Complete lineup that covers all markets worldwide

Global pin-to-pin series (multiformat, PAL/NTSC, NTSC)

VIF/SIF

Adjustment-free VIF/SIF

No VCO coil required

Built-in audio bandpass filter, four-system audio trap

Digital AFT system

V/C/D (Video/Chrominance/Deflection)

Blue stretching technology that creates high-quality images

DDS technology single crystal VCO system

DVD component signal inputs (YCbCr)

Built-in SECAM demodulator (LA76936, LA76938)

Special architecture and algorithms that create high-quality images

CPU

Up to 15 colors can be selected

Four colors per character

SUSOC ICs (LA76930Series)

LA76930 (IF+VCD+CPU)

with YcbCr

LA76932 (IF+VCD+CPU)

with YcbCr & E/W

LA76936 (IF+VCD+Micon)

with YcbCr SECAM

LA76950 (IF+VCD+Micon)

with YcbCr

LA76952 (IF+VCD+Micon)

with YcbCr & E/W

LA7695X (IF+VCD+Micon+3line Comb)

with YcbCr & E/W

Audio power

RGB drive

AC

Power

supply

SANYO TV . VCR SANYO TV . VCR

15 16

Pre drive

H out

V-out

CRT

LA76938 (IF+VCD+Micon)

with YcbCr & E/W

TM

: SUSOC

✽

is a trademark of SANYO Electric Co., Ltd.

CPUCPU

CCD

CCD

1 chip

1 chip

1 chip

1 chip

(IF/V/C/D)

(IF/V/C/D)

(IF/V/C/D)

(IF/V/C/D)

CCD

CCD

Page 10

Signal-Processing IC with Integrated

Microcontroller

LA76919M

Overview Overview

The LA76919M and LA76922M series are I

TV set design, improved manufacturability, and lower total costs.

Functions and Features

Black stretch, sharpness control with coring on/off control, built-in variable Y system filters (Y-DL and chrominance trap)

Chrominance bandpass filter, demodulation angle control

Audio and video switching: three systems

Built-in microcontroller video, chrominance, and deflection signal processing

Adjustment- free horizontal resonator system

Simplified SG

Supply voltage: VCC = 11 V (built-in reference voltage for 5.7 V and 8.5 V regulators)

Package: QIP80E (14 20)

2

C bus controller ICs that support the NTSC format and aim for rationalization of color

The LA76919M and LA76922M series are I

TV set design, improved manufacturability, and lower total costs.

Functions and Features

Black stretch, sharpness control with coring on/off control, built-in variable Y system filters (Y-DL and chrominance trap)

Chrominance bandpass filter, demodulation angle control, CbCr input

E/W support

VM output

Audio and video switching: three systems

Built-in microcontroller video, chrominance, and deflection signal processing

Adjustment- free horizontal resonator system

Simplified SG

Supply voltage: VCC = 11 V (built-in reference voltage for 5.7 V and 8.5 V regulators)

Package: QIP80E (14 20)

Signal-Processing IC with Integrated

Microcontroller

LA76922M

2

C bus controller ICs that support the NTSC format and aim for rationalization of color

P17

P34

P35

P36

P37

P10/SDA0

P11/SCK0

P12/SDA1

P13/SCK1

+

Block Diagram Block Diagram

SAO

SVO

IR-IN

P03/INT3

P15/PWM2

P16/PWM3

P14/PWM1

P02/INT2

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41

65

66

67

68

69

I/O

PORT 1

70

ADC

71

ROM RAM

I IC-BUS BUS BUS

72

BASE

73

TIMER

0

TIMER

CPU

CORE

OSD

74

75

76

I/O

PORT 0

77

78

79

CLOCK

CONTROL

80

23456789101112 13 14 15 16 17 18 19 20 21 22 23 24

1

P04/AN4

P05/AN5

P06/AN6

KEY-IN AFT

V

DD

P07/AN7

P01/INT1

I/O

PORT 3

DATA

SLICER

HS/VS

CSYNC

P00/INT0

PLL

P33

CLMP

VIDEO

SW

AUDIO

SW

LPF ATT

C INEXT-A

EXT-V

P-SW

+

+

+

REG

SW

VXO

APC 1 FSC

TINT

EPF

TRAP

CONTROL

REG-SW

5V/8V-REG

RST

+

11V

+

YC SW

V/Y

SW

OSD

CLMP

11V

ACC DEMO

DL

SHARP

DC REST

DRIVE/OUT-OFF

+

INT-V

SG

BS

OSD

SW

+

ABLREF

11V

RGB

MATRIX

CONTRAST

ERIGHT

ABL-ACL

INT-A

ABL

CLMP

+

+

AF

SW

COLOR

CLAMP

SYNC

SEP

VER

SEP

VER

C/D

VER

RAMP

ATT

OUT

VCC:5V

VCD

+

+

RGB

7.8V

+

+

X-RAY

HOR

VCO

X-RAY

1/256

HOR

C/D

FEP

AFC1

AFC2

PHASE

SHIFTER

HOR

HOR

VOC

OUT

R

OUTGOUTBOUT

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

FSC

+

+

HOR

GND

+

VER

OUT

VRAMP

+

X-RAY

V3

A3

H OUT

F

µ

8.47

+

+

FEP

KILLER OUT

HOR V

CC

+

+

P17

P34

P35

P36

P37

P10/SDA0

P11/SCK0

P12/SDA1

P13/SCK1

+

V

SVO

P15/PWM2

P16/PWM3

P14/PWM1

IR-IN

P03/INT3

P02/INT2

P00/INT0

P01/INT1

CSYNC

P33

X-RAY

IN

P-SW

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41

EXT V

X-RAY

C IN

REF

+

+

+

11V

65

REG

RST

TRAP

REG-SW

11V

EPF

CONTROL

5V/8V-REG

+

SW

OSD

CLMP

11V

YC SW

V/Y

SW

+++

VXO

APC 1 FSC

TINT

ACC DEMO

DL

BS

SHARP

SG

DC RESTVM

OSD

SW

DRIVE/OUT-OFF

INT-V

YNR FIL

VM

OUT

RGB

MATRIX

CONTRAST

ERIGHT

ABL-ACL

+

ABL

CLMP

COLOR

CLAMP

E/W

AMP

E/W

OUT

66

67

68

69

I/O

PORT 1

I/O

PORT 3

CLMP

VIDEO

SW

70

ADC

71

ROM RAM

I IC-BUS BUS BUS

72

73

TIMER

0

BASE

TIMER

CPU

CORE

OSD

DATA

SLICER

LPF

74

75

76

I/O

PORT 0

HS/VS

77

78

79

CLOCK

CONTROL

80

DD

23456789101112 13 14 15 16 17 18 19 20 21 22 23 24

1

P04/AN4

P05/AN5

P06/AN6

KEY-IN AFT

P07/AN7

PLL

+

VCC:5V

+

AF/D1

SW

SYNC

SEP

VER

SEP

VER

C/D

VER

RAMP

+

VCD

HOR

VOC

VER

D/A

R

OUTGOUTBOUT

RGB

7.8V

HOR

VCO

1/256

HOR

C/D

AFC1

+

+

X-RAY

X-RAY

FEP

AFC2

PHASE

SHIFTER

HOR

OUT

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

FSC

+

HOR

GND

(METUL FILM)

H OUT

+

VER

OUT

VRAMP

+

X-RAY

V3

CR

CB

F

µ

8.47

+

FEP

+

HOR V

CC

SANYO TV . VCR SANYO TV . VCR

17 18

Page 11

I2 C Bus Control Lineup

LA76810 Series

LA76818A

Overview

The LA76810 series are I2C bus controller ICs that support the different TV broadcast formats used worldwide and aim for

rationalization of color TV set design, improved manufacturability, and lower total costs

Single crystal multiformat system that supports the different TV broadcast formats used worldwide

ICs optimal for each individual broadcast standard deployed as a pin-to-pin compatible lineup

· Multiformat system: LA76818A (YCbCr support), LA76828N (YCbCr and E/W support)

· NTSC system: LA76843N/LA76835A (YCbCr and E/W support), LA76835NM (YCbCr and E/W support)

Adjustment-free VIF/SIF, audio trap/audio bandpass filters

Adjustment- free horizontal resonator system

Simplified SG

Supply voltage: VCC = 5 V/9 V

Package: DIP54S (600mil), QIP80E (14 20) (LA76835NM only)

Functions and Features

VIF/SIF

· Adjustment-free VCO, 4-mode audio trap/audio bandpass filter, buzz canceller

· RF AGC/video level

· SIF system automatic discrimination (The LA7973 is used as the automatic discrimination IC.)

Single crystal color system: PAL, NTSC, SECAM (The LA7642N is used as the SECAM decoder.)

Black stretch, sharpness control with coring on/off control, built-in variable Y system filters (Y-DL and chrominance trap)

Chrominance bandpass filter, demodulation ratio and angle control

I2 C Bus Control Lineup

LA76810 Series

LA76828N

Overview

The LA76810 series are I

rationalization of color TV set design, improved manufacturability, and lower total costs

Single crystal multiformat system that supports the different TV broadcast formats used worldwide

ICs optimal for each individual broadcast standard deployed as a pin-to-pin compatible lineup

· Multiformat system: LA76818A (YCbCr support), LA76828N (YCbCr and E/W support)

· NTSC system: LA76843N/LA76835A (YCbCr and E/W support), LA76835NM (YCbCr and E/W support)

Adjustment-free VIF/SIF, audio trap/audio bandpass filters

Adjustment- free horizontal resonator system

Simplified SG

Supply voltage: VCC = 5 V/9 V

Package: DIP54S (600mil), QIP80E (14 20) (LA76835NM only)

Functions and Features

VIF/SIF

· Adjustment-free VCO, 4-mode audio trap/audio bandpass filter, buzz canceller

· RF AGC/video level

· SIF system automatic discrimination (The LA7973 is used as the automatic discrimination IC.)

Single crystal color system: PAL, NTSC, SECAM (The LA7642N is used as the SECAM decoder.)

Black stretch, sharpness control with coring on/off control, built-in variable Y system filters (Y-DL and chrominance trap)

Chrominance bandpass filter, demodulation ratio and angle control

E/W support

2

C bus controller ICs that support the different TV broadcast formats used worldwide and aim for

S CARRIER OUT

AUDIO OUTPUT

SAO

Block Diagram Block Diagram

SVO

V/C

EXT

AUDIO

IN

+

VCO

IF AGC

IF IN

RF AGC

V

CC

+

A2C

PLL

VIDEO

AMP

TRAP

VIDEO

DET

VIF

SAW

FILTER

54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28

BPF

SPLL

BPF

LIM

AMP

FM

DET

SW

DC

VOL

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27

RF AGC

+

IF

VCC5V

+

VIDEO

OUT

IF

IDENT

IFT

+

+

VCC 5V

I IN-V IN

[S-C IN]

EXT-V IN

[Y-IN]

+

++

SW

LINE

BUS ABL

CLMP

SW

SYNC

SEP

BLACK

STRETOHDCREST

ABL

AFT

CLMP

VIDEO

TRAP

DELAY

PEAKING

CORING

V/C

GND

APC1 TINT

EPF

(ON/OFF)

ACC

OSD

CONTRAST

CLAMP

GINB

R

IN

+

VXO DDS

PAL

SW

DEMO

CONTRAST

ERIGHT

FB

IN

IN

CLAMP

+

RGB

VCC 9V

+

+

APC2

VCO

MATRIX

DRIVE/OUT-OFF

R

OUT

RGB

OSD

SW

G

OUTBOUT

ON

CLAMP

DC ADS.

SW

SECAM

DECODER

CCD/

HOR

GND

SYNC

SYNC

OUT

1H DELAY

COLOR

CLAMP

VER

SEP

VER

C/D

VER

RAMP

VER

OUT

SEOAM-KIL

SCP

CCD

VCC5V

REF

+

+

HOR

VCO

LPF

1/256

ALC

HOR

C/D

AFC1

HOR

VCC

+

HOR

VCC 9V

FBP

IN

FBP

AFC2

PHASE

SHIFTER

HOR

OUT

HOR

OUT

S CARRIER OUT

AUDIO OUTPUT

SAO

EXT-V IN

[Y-IN]

SW

SYNC

SEP

BLACK

ABL

FSC/SYNC

V/C

GND

FSC/

SYNC SW

BPF

(ON/OFF)

ACC

CONTRAST

R

IN

OUT

+

VXO DDS

APC1 TINT

PAL

SW

DEMO

OSD

BRIGHT

CLAMP

GINB

IN

CLAMP

CONTRAST

ERIGHT

+

FB

RGB

IN

VCC 9V

+

APC2

VCO

DRIVE/OUT-OFF

R

OUT

+

MATRIX

RGB

OSD

CB

CR

IN

IN

CLAMP

SW

SW

G

OUTBOUT

EW

E/W

OUT

CCD/

HOR

GND

1H DELAY

DC ADS.

COLOR

CLAMP

VER

SEP

VER

C/D

VER

RAMP

VER

OUT

VCC5V

+

CCD

+

LPF

ALC

HOR

VCC

+

HOR

VCC 9V

4M

OUT

REF

1/256

AFC1

HOR

VCO

HOR

C/D

+

V/C

EXT

AUDIO

IN

+

VCO

IF AGC

V

IF IN

+

RF AGC

CC

VIDEO

AMP

S.TRAP

SW

TRAP

VIDEO

DET

VIF

SAW

FILTER

A2C

PLL

54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28

BPF

SPLL

BPF

LIM

AMP

FM

DET

SW

SW

DC

VOL

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27

RF AGC

OVER

MOD.

+

IF

VCC5V

+

VIDEO

OUT

AFT

+

+

VCC 5V

I IN-V IN

[S-C IN]

+

++

CLMP

CLMP

VIDEO

SW

TRAP

DELAY

LINE

PEAKING

STRETOHDCREST

CORING

BUS ABL

AFT

FBP

IN

FBP

AFC2

PHASE

SHIFTER

HOR

OUT

HOR

OUT

SANYO TV . VCR SANYO TV . VCR

19 20

Page 12

I2 C Bus Control Lineup

LA76810 Series

LA76835A

Overview

The LA76810 series are I2C bus controller ICs that support the different TV broadcast formats used worldwide and aim for

rationalization of color TV set design, improved manufacturability, and lower total costs.

Single crystal multiformat system that supports the different TV broadcast formats used worldwide.

ICs optimal for each individual broadcast standard deployed as a pin-to-pin compatible lineup.

· Multiformat system: LA76818A (YCbCr support), LA76828N (YCbCr and E/W support)

· NTSC system: LA76843N/LA76835A (YCbCr and E/W support), LA76835NM (YCbCr and E/W support)

Adjustment-free VIF/SIF, audio trap/audio bandpass filters

Adjustment-free horizontal resonator system

Simplified SG

Supply voltage: VCC = 5 V/9 V

Package: DIP54S (600mil), QIP80E (14 20) (LA76835NM only)

Functions and Features

VIF/SIF

· Adjustment-free VCO, buzz canceller

· RF AGC/video level/FM level control

Black stretch, sharpness control with coring on/off control, built-in variable Y system filters (Y-DL and chrominance trap)

Chrominance bandpass filter, demodulation angle control

E/W support

I2 C Bus Control Lineup

LA76810 Series

LA76835NM

Overview

The LA76810 series are I

rationalization of color TV set design, improved manufacturability, and lower total costs.

Single crystal multiformat system that supports the different TV broadcast formats used worldwide.

ICs optimal for each individual broadcast standard deployed as a pin-to-pin compatible lineup.

· Multiformat system: LA76918A (YCbCr support), LA76828N (YCbCr and E/W support)

· NTSC system: LA76843N/LA76835A (YCbCr and E/W support), LA76835NM (YCbCr and E/W support)

Adjustment-free VIF/SIF, audio trap/audio bandpass filters

Adjustment-free horizontal resonator system

Simplified SG

Supply voltage: VCC = 5 V/9 V

Package: DIP54S (600mil), QIP80E (14 20) (LA76835NM only)

Functions and Features

VIF/SIF

· Adjustment-free VCO, buzz canceller

· RF AGC/video level/FM level control

Black stretch, sharpness control with coring on/off control, built-in variable Y system filters (Y-DL and chrominance trap)

Chrominance bandpass filter, demodulation ratio and angle control, blue stretch

E/W support

2

C bus controller ICs that support the different TV broadcast formats used worldwide and aim for

AUDIO OUTPUT

FM OUT

RF AGC

IF IN

Block Diagram Block Diagram

F

µ

1

+

680K

CLMP

VIDEO

SW

TRAP

DELAY

LINE

PEAKING

CORING

BUS ABL

100

F

µ

0.1

EXT-V

IN

Y-IN

F

µ

F

µ

47

0.01

F

µ

1

+

+

CLMP

BPF

C SW

(BYPASS)

SYNC

SEP

BLACK

STRETOH

FIX GAIN

ERIGHT

F

IN

100P

µ

0.01

F

µ

0.01

100

100P

DC

REST

OSD

CLAMP

(M)

75

APC1

F

µ

0.01

(M)

+

ACC

F

µ

0.0

75

BINGINRINIB

16P

F

µ

1

VXO

KIL

CONTRAST

BRIGHT

F

µ

10

(M)

75

IN

V

CC

+

10k

X-RAYCWOUTSVO

1

µ

F

+

24K

0.47µF

F

+

µ

(M)

0.047

CW

DEMO CLAMP

COLOR TINT

DRIVE/OUT-OFF

F

µ

0.01

R

OUT

24K

H-OUT

CONTROL

RGB

MATRIX

OSD

SW

G

OUT

X-RAY

AUTO

FLESH

B

OUT

10k

1H-DL/

HOR

GND

E / W

OUT

EW

OUT

VER

OUT

VER

SEP

VER

C/D

VER

RAMP

(M)

CRC_ IN

F

µ

0.01

CLMP

CB.CR

SW

(M)

CB

F

F

µ

µ

REF

1

1

++

HOR

VCO

1/256

HOR

C/D

AFC1

HOR

VCC

H

V

CC

F

F

+

µ

µ

10

0.01

(M)

F

F

µ

µ

0.33

0.015

F

µ

0.33

+

EXT

S

AUDIO

OARRIER

IN

OUT

IF AGC

+

RF AGC

F

µ

(M)

0.022

F

µ

10

600

VIDEO

VIDEO

F

µ

0.01

1

+

AMP

TRAP

SW

SND

TRAP

DET

VIF

SAW

FILTER

VCO

330

F

µ

0.47

1000P

3K

F

µ

10P

0.01

54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28

BPF

SPLL

BPF

LIM

AMP

FM

DET

SW

DC

VOL

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27

F

µ

0.01

30K

A2C

PLL

0.01µF

100µF

VIDEO

OUT

510

510

+

F

µ

F

µ

0.47

+

2.2

AFT

+

12K

+

µ

F

1

100K 100K

AFT FB

FBP IN

(METUL FILM )

4.7K

FBP

H OUT

AFC2

PHASE

SHIFTER

HOR

OUT

150

Ω

3.0K

F

µ

1

VCC 5V

GND

VCC 9V

GND

EXT AUDIO INT

S OARRIER OUT

AUDIO OUTPUT

FM OUT

RF AGC

IF IN

10P

30k

1

330

660

1000P

100

µ

0.022µF(M)

SVO

EXT-V IN

INT-V IN

DET

µ

H

15

F

µ

2.2

680k

510

AFT

100

100

100P

100P

[S-C : IN]

F

F

µ

µ

F

µ

0.01

0.01

+

1

DC

OSD

FIX GAIN

ERIGHT

F(M)

µ

0.01

757575

G IN

75

NC

CLMPCLMP

SW

IST AMP

BPF

2ND AMP

BPF

DEMO

COLOR

CLAMP

CONTRAST

BRIGHT

F(M)

F(M)

µ

µ

0.01

0.01

B IN FB IN

F

++

µ

1

VIDEO

SW

TRAP

DELAY

LINE

PEAKING

CORING

BLACK

STRETOH

REST

ACC

KILLER

CLMP

DELAY

CB.CR

SW

COLOR

HS/VS

10k

V/C/D

GND

MATRIX

20kHS20k

VS

RGB

OSD

SW

+

VIDEO OUT

510

39

+

V

CC

F

µ

0.47

EPF

SW

DC

VOL

A2C

PLL

VIDEO

AMP

SPLL

IF AGC

+

DET

EPF

LIM

ANP

FM

NC

VIDEO

VIF

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43

GND

65

+

0.47µF

66

+

µ

F

10

67

µ

F

0.01

3k

68

69

70

NC

71

+

µ

F

10

72

NC

73

F

+

74

µ

F

0.01

75

0.01µF(M)

76

77

RF AGC

78

79

IF GND

80

GND GND

1

2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24

0.01µF

+

µ

F

100

BUS ABL OL AMP

100K

12K

F

+

µ

F

µ

0.1

1

100K

AFT ABL R IN

+

TINT

AUTO

FLESH

F

µ

10

VM IN

VCO

DRIVE/OUT-OFF

0.47

µ

16P

F

+

µ

F

µ

1

0.0471

CW

KIL

TINTAPC1

HOR

VCO

1/256

SYNC

HOR

SEP

C/D

AFC1

VER

SEP

VER

C/D

R OUT G OUT B OUT

F

FSC OUT

24k24k

FEP

AFC2

PHASE

SHIFTER

HOR

OUT

HOR

VCC

VER

RAMP

E/W

10k

42 41

GND

X-RAY

VM

AMP

CPU

RESET

RESET

VDD

40

+

µ

F

1

39

+

1µF

38

+

5.6k

37

36

HOR

GND

35

(METUL FILM)

REF

34

4.7k

33

10k

32

( )

31

(M)

330

15000P

30

3.3k 150

µ

F

1

29

F

+

µ

10

28

µ

0.47

27

26

25

CR

CB

X-RAY

µ

F

1

VM OUT

FEP IN

HOR OUT

µ

F

0.01

0.47µF

F

VER OUT

EW OUT

VSI ZE 0OMP

V

CC

GND

VCC 9V

GND

5V

SANYO TV . VCR SANYO TV . VCR

21 22

Page 13

I2 C Bus Control Lineup

LA76810 Series

LA76843N

Overview

The LA76810 series are I2C bus controller ICs that support the different TV broadcast formats used worldwide and aim for

rationalization of color TV set design, improved manufacturability, and lower total costs

Single crystal multiformat system that supports the different TV broadcast formats used worldwide

ICs optimal for each individual broadcast standard deployed as a pin-to-pin compatible lineup

· Multiformat system: LA76818A (YCbCr support), LA76828N (YCbCr and E/W support)

· NTSC system: LA76843N/LA76835A (YCbCr and E/W support), LA76835NM (YCbCr and E/W support)

Adjustment-free VIF/SIF, audio trap/audio bandpass filters

Adjustment-free horizontal resonator system

Simplified SG

Supply voltage: VCC = 5 V/9 V

Package: DIP54S (600mil), QIP80E (14 20) (LA76835NM only)

Functions and Features

VIF/SIF

· Adjustment-free VCO, buzz canceller

· RF AGC/video level/FM level control

Black stretch, sharpness control with coring on/off control, built-in variable Y system filters (Y-DL and chrominance trap)

Chrominance bandpass filter, demodulation angle control

Vertical Output IC

LA7840

Overview

The LA7840 is a vertical deflection output IC for high-definition TV and CRT displays in systems that use a bus control system

signal-processing IC. This IC can directly drive (including the DC component) the deflection yoke from the sawtooth wave output

from the bus control system signal-processing IC. The color TV vertical deflection system adjustment function can be controlled

from the bus system when this IC is used in conjunction with a SANYO LA768X or LA769XX series TV bus control system signalprocessing IC.

The LA7840 provides a maximum deflection current of 1.8 A p-p, and thus is optimal for small to medium diameter CRTs.

Functions

Low power operation achieved by using integrated charge pump circuit

Vertical output circuit

Thermal protection circuit

Excellent crossover characteristics

Supports DC coupling

Package: SIP7H

Block Diagram

V/C

S CARRIER OUT

54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28

BPF

BPF

LIM

AMP

FM

DET

SW

DC

VOL

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27

AUDIO OUTPUT

RF AGC

SPLL

IF AGC

V

IF IN

EXT

AUDIO

IN

+

RF AGC

CC

+

VIDEO

AMP

SND

TRAP

VIDEO

DET

VIF

SAW

FILTER

VCO

A2C

PLL

+

IF

VCC5V

+

VIDEO

OUT

AFT

+

+

VCC 5V

I IN-V IN

[S-C IN]

EXT-V IN

[Y-IN]

+

++

SW

LINE

BUS ABL

CLMP

SW

SYNC

SEP

BLACK

STRETOH

ABL

AFT

CLMP

VIDEO

TRAP

DELAY

PEAKING

CORING

SVO

V/C

GND

+

APC1 TINT

BPF

(BYPASS)

AOC

KIL

DC

REST

WPL

OSD

FIX GAIN

CLAMP

GINB

R

IN

VXO CW

DEMO

CONTRAST

BRIGHT

+

FB

IN

IN

+

RGB

VCC 9V

FSC

+

FILTER

ADJ

RGB

MATRIX

OSD

SW

DRIVE/OUT-OFF

G

R

OUTBOUT

OUT

X-RAY

X-RAY

RESET

CCD/

HOR

GND

C_SYNC

OUT

SYNC

OUT

VER

OUT

COLOR

CLAMP

VER

SEP

VER

C/D

VER

RAMP

HS VS

+

HOR

VCC 9V

HOR

VCC

REF

HOR

VCO

1/256

HOR

C/D

AFC1

FBP

IN

FBP

AFC2

PHASE

SHIFTER

HOR

OUT

HOR

OUT

Block Diagram

Thermal

Protection

-

AMP

+

1234567

GND

CC

Ver.OUTPUT

NON INV.INPUT

OUTPUT STAGE V

Pump UP

CC

V

INVERTING INPUT

PUMP UP OUT

SANYO TV . VCR SANYO TV . VCR

23 24

Page 14

Vertical Output IC Vertical Output IC

LA7841

Overview

The LA7841 is a vertical deflection output IC for high-definition TV and CRT displays in systems that use a bus control system

signal-processing IC. This IC can directly drive (including the DC component) the deflection yoke from the sawtooth wave output

from the bus control system signal-processing IC. The color TV vertical deflection system adjustment function can be controlled

from the bus system when this IC is used in conjunction with a SANYO LA768X or LA769XX series TV bus control system

signal-processing IC.

The LA7841 provides a maximum deflection current of 2.2 A p-p, and thus is optimal for large diameter CRTs.

Functions

Low power operation achieved by using integrated charge pump circuit

Vertical output circuit

Thermal protection circuit

Excellent crossover characteristics

Supports DC coupling

Package: SIP7H

LA7845N

Overview

The LA7845N is a vertical deflection output IC for high-definition TV and CRT displays in systems that use a bus control system

signal-processing IC. This IC can directly drive (including the DC component) the deflection yoke from the sawtooth wave output

from the bus control system signal-processing IC. The color TV vertical deflection system adjustment function can be controlled

from the bus system when this IC is used in conjunction with a SANYO LA768X or LA769XX series TV bus control system

signal-processing IC.

The LA7845N provides a maximum deflection current of 2.2 A p-p, and thus is optimal for large diameter CRTs, and can drive the

CRTs used in TV sets in the 33 to 37 inch range.

Functions

Low power operation achieved by using integrated charge pump circuit

Vertical output circuit

Thermal protection circuit

Excellent crossover characteristics

Supports DC coupling

Package: SIP7H

Block Diagram Block Diagram

Thermal

Protection

-

AMP

+

1234567

GND

CC

Ver.OUTPUT

NON INV.INPUT

OUTPUT STAGE V

Pump UP

CC

V

INVERTING INPUT

PUMP UP OUT

Thermal

Protection

-

AMP

+

1234567

GND

CC

Ver.OUTPUT

NON INV.INPUT

OUTPUT STAGE V

Pump UP

CC

V

INVERTING INPUT

PUMP UP OUT

SANYO TV . VCR SANYO TV . VCR

25 26

Page 15

Vertical Output IC Vertical Output IC

LA7846N

Overview

The LA7846N is a vertical deflection output IC for high-definition TV and CRT displays in systems that use a bus control system

signal-processing IC. This IC can directly drive (including the DC component) the deflection yoke from the sawtooth wave output

from the bus control system signal-processing IC. The color TV vertical deflection system adjustment function can be controlled