Samsung SGH-V200 Circuit Descriptions

2. SG H-V200 Circuit Description

1. SGH-V200RF Circuit Description

1) RX PART

1. ASM(U1005)→Switching Tx, Rx path for GSM900, DCS1800 and PCS1900 by logic controlling.

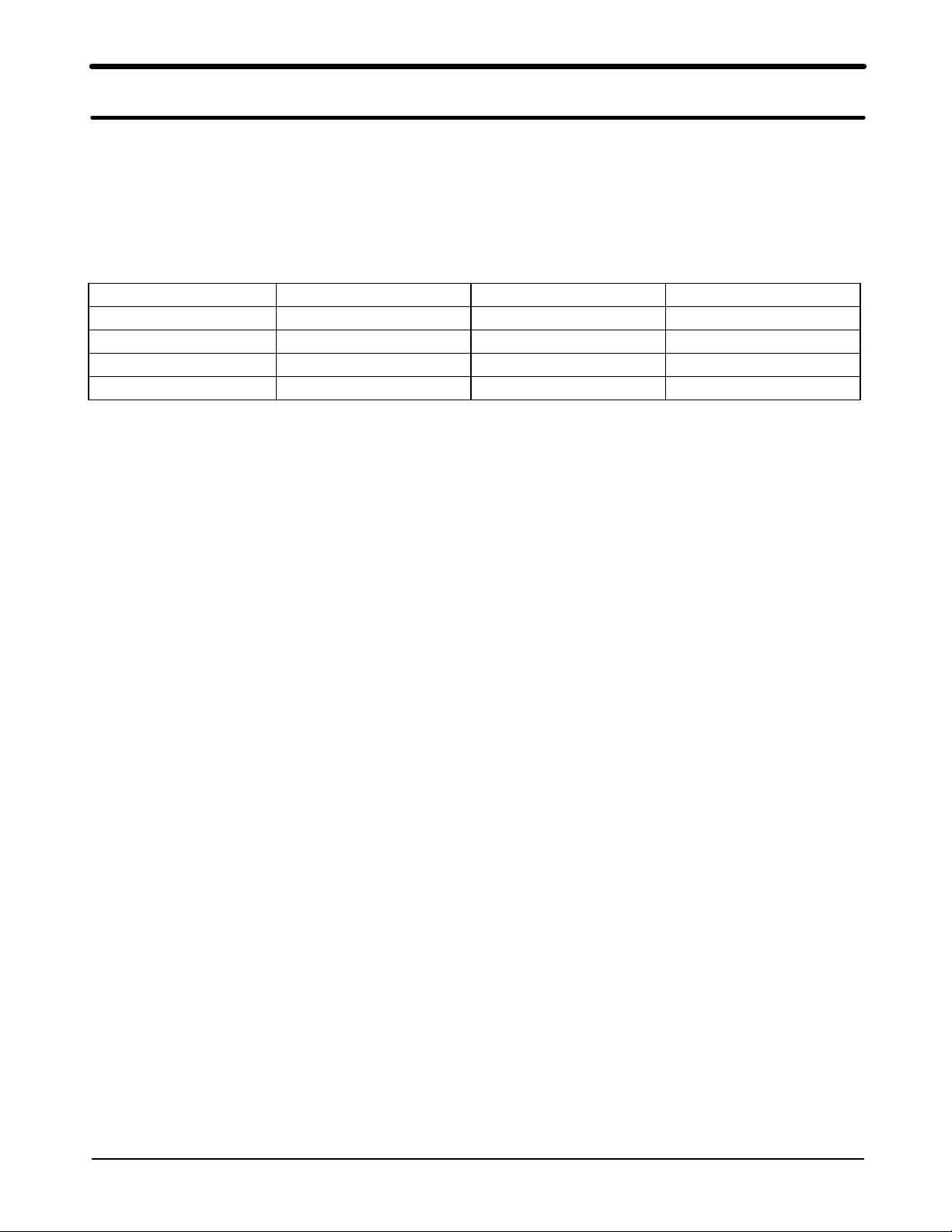

2. ASM Control Logic (U701, U702, U703)→Truth Table

VC1 VC2 VC3

GSM Tx Mode H L L

DCS / PCS Tx Mode L H L

PCS Rx Mode L L H

GSM / DCS Rx Mode L L L

3. FILTER

To convert Electromagnetic Field Wave to Acoustic Wave and then pass the specific frequency band.

- GSM FILTER (C1003,C1004,L1001)→For filtering the frequency band between 925 ~ 960 MHz

- DCS FILTER (C1005,C1006,L1002)→For filtering the frequency band 1805 and 1880 MHz.

- PCS SAW FILTER (F1003)→For filtering the frequency band between 1930 and 1990 MHz

4. TC-VCXO (OSC801)

To generate the 13MHz reference clock to drive the logic and RF.

After additional process, the reference clock applies to the U900 Rx IQ demodulator and Tx IQ modulator.

The oscillator for RX IQ demodulator and Tx modulator are controlled by serial data to select channel and use fast lock

mode for GPRS high class operation.

5. Si 4200 (U901)

This chip integrates three differential-input LNAs.

The GSM input supports the E-GSM, DCS input supports the DCS1800, PCS input supports the PCS1900. The LNA

inputs are matched to the 200 ohm differential output SAW filters through eternal LC matching network.

Image-reject mixer downconverts the RF signal to a 100 KHz intermediate frequency(IF) with the RFLO from SI4133T

frequency synthesizer. The RFLO frequency is between 1737.8 ~ 1989.9 MHz.

The Mixer output is amplified with an analog programmable gain amplifier(PGA), which is controlled by AGAIN.

The quadrature IF signal is digitized with high resolution A/D converts (ADC).

6. Si 4201 (U900)

The SI4201 down-converts the ADC output to baseband with a digital 100 KHz quadrature LO signal. Digital decimation

and IIR filters perform channel selection to remove blocking and reference interface signals.

After channel selection, the digital output is scaled with a digital PGA, which is controlled with the DGAIN. DACs drive

a differential analog signal onto the RXIP, RXIN, RXQP, RXQN pins to interface to standard analog-input baseband IC.

SAMSUNG Proprietary-Contents may change without notice

2-1

SGH-V200 Circuit Description

2) TX PART

Baseband IQ signal fed into offset PLL, this function is included inside of U902 chip.

SI4200 chip generates modulator signal which power level is about 1.5dBm and fed into Power Amplifier(U1008).

The PA output power and power ramping are well controlled by Auto

Power Control circuit. We use offset PLL below

GSM -35dBc

DCS -35dBc

PCS -35dBc

GSM -66dBc

DCS -65dBc

PCS -66dBc

GSM -75dBc

DCS -68dBc

PCS -75dBc

Modulation Spectrum

200kHz offset

30 kHz bandwidth

400kHz offset

30 kHz bandwidth

600kHz ~ 1.8MHz offset

30 kHz bandwidth

2. Baseband Circuit description of SGH-V200

1. PSC2006

1.1. Power Management

Seven low-dropout regulators designed specifically for GSM applications power the terminal and help ensure optimal

system performance and long battery life. A programmable boost converter provides support for 1.8V, 3.0V, and 5.0V

SIMs, while a self-resetting, electronically fused switch supplies power to external accessories. Ancillary support functions,

such as an LED driver and two call-alert drivers, aid in reducing both board area and system complexity.

A three-wire serial interface unit(SIU) provides access to control and configuration registers. This interface gives a

microprocessor full control of the PSC2006 and enables system designers to maximize both standby and talk times.

Supervisory functions. including a reset generator, an input voltage monitor, and a thermal monitor, support reliable system

design. These functions work together to ensure proper system behavior during start-up or in the event of a fault

condition(low microprocessor voltage, insufficient battery energy, or excessive die temperature).

1.2. Battery Charge Management

A battery charge management block provides fast, efficient charging of a single-cell Li-ion battery. Used in conjunction

with a current-limited voltage source and an external PMOS pass transistor, this block safely conditions near-dead cells

and provides the option of having fast-charge and top-off controlled internally or by the system's microprocessor.

1.3. Backlight LED Driver

The backlight LED driver is a low-side, programmable current source designed to control the brightness of the keyboard

and LCD illumination. The driver is enabled by EN_LED, and its current setting is determined by LED[0:2]. Provided

EN_LED is‘1’, the driver can be programmed to sink from 12.5mA to 100mA in 12.5mA steps. LED_DRV is

capable of sinking 100mA at a worst-case maximum output voltage of 0.6V. For efficient use, the LEDs is connected

between the battery and the LED_DRV output.

SAMSUNG Proprietary-Contents may change without notice

2-2

Loading...

Loading...