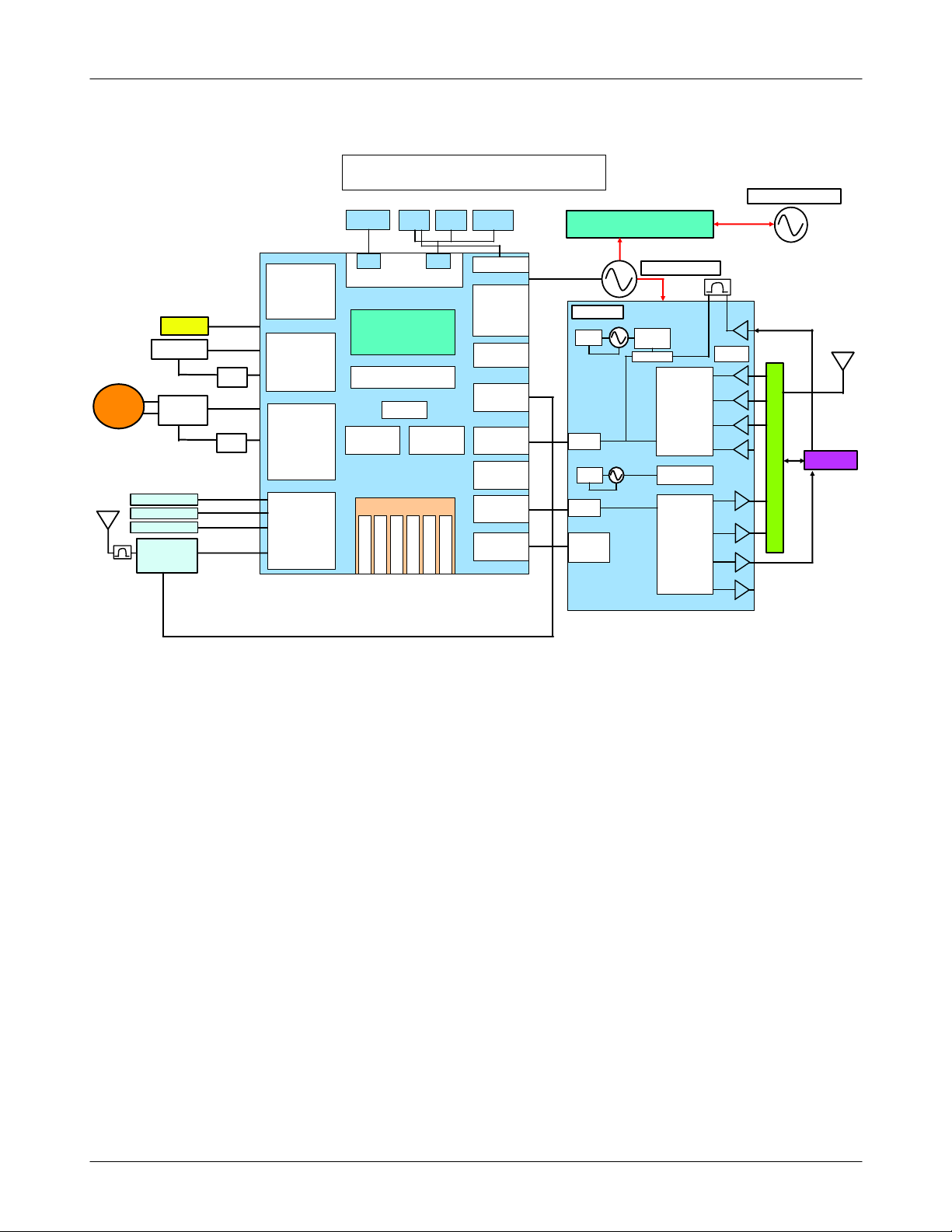

Samsung SGH-U900 Block Diagram

Block Diagrams

8.

HB_RF_OUT2

HB_RF_OUT3

HB_RF_OUT1

LB_RF_OUT1

LB_RF_OUT2

RF_ON

DAC_IRE

SBDT

TX_BIA

GCELL_IN

GCELL_IN

EGSM_INP

EGSM_INN

DCS_INP

DCS_INN

PCS_INP

PCS_INN

WPRXHBP

WPRXHBN

WPRXLBP

WPRXLBN

WPRXSE2_IN

WPRXSE1_IN

BPF

BPF

BPF

BPF

I

B

S

S

T

U

O

_

1

E

S

X

R

P

W

Gain Ctl &

Bias

Circuits

Downconverter

T

U

O

_

2

E

S

X

R

P

W

Quadrature

Upconverter

LO Generation &

Quadrature

Downconverter

Quadrature

LO GEN

N

P

N

N

I

I

_

_

X

X

M

M

_

_

B

B

W

W

Quadrature

Upconverter

Distribution

Quadrature

Downconverter

Quadrature

Downconverter

Quadrature

Downconverter

& Dist

s

A

D

D

V

LPF

PLL 2

2

E

N

U

T

V

LPF & DO

Correction

LPF & DO

Correction

To SSBI

TCXO

TX_IP

LPF

TX_IN

TX_QP

LPF

TX_QN

TCX

PLL 1

TCX

VTUNE

LPF

PRX_IP

PRX_IN

PRX_QP

PRX_QN

Power

Detector

ground

slug

PWD_DET_IN

D

N

G

8-1

SAMSUNG Proprietary-Contents may change without notice

This Document can not be used without Samsung's authorization

Block Diagrams

SGH-U900 Block Diagram

SDRAM

LCD NAND OTHER

RTC : 32.768MHz

PM6658

MOT

FLASH

Touch_Key

MOTOR

DRIVE IC

Handset speaker

Stereo headset

Microphone

Bluetooth IC

(BCM2048)

LDO

LDO

CAMERA

PROCESSING

MDDI Client

GRAPHICS

OpenGL ES

3D,2D

VIDEO

MPEG-4

H.263,H.264,

WM,Real

AUDIO

MP3,AAC,

EVRC,QCELP,

AMR,AMR-WB/+,

CMX,MIDI

EBI 1 EBI 1

DUAL MEMORY BUSES

MSM6280

Modem QDSP4000

PLL Inside

QDSP4000

ARM 926ejs

with Jazelle

CONNECTIVITY

F

/

I

G

O

T

I

d

a

p

y

e

K

1

O

D

T

S

/

B

R

S

A

D

S

U

U

2

T

R

A

U

M

I

S

U

/

3

T

R

A

U

MDDI Host

UMTS,HSDPA

GSM,GPRS,

EGPRS

Processor

gpsOne

processor

BT

processor

Rx ADCs (2)

Equalizer

Tx DAC

SSBI Control

RTR6280

PLL

LPF

PLL

LPF

SSBI

Control

TCXO: 19.2MHz

LO

Generato

Rx Demod

Rx

modulator

LO

Generator

Tx

modulator

HDET

S

W

I

T

C

H

P

Duplexer

L

E

X

E

R

8-2

SAMSUNG Proprietary-Contents may change without notice

This Document can not be used without Samsung's authorization

Loading...

Loading...