Page 1

Repair Manual

1. Block Diagram

2. Connection Diagram

3. Circuit Description

4. Schematic Diagrams

SAMSUNG FACSIMILE

SF-330/331P/335T

C•O•N•T•E•N•T•S

Page 2

- This Service Manual is a property of Sam sung Electronics Co.,Lt d.

Any unautho rized use of Ma nual can be punis hed under app licable

International and/or dome stic law. -

Page 3

Samsung Electronics Digital Printing

CS Group

Copyright (c) 2002. 07

This manual is made and

described centering around

circuit diagram

and circuit description needed

in the repair center

in the form of appendix.

Page 4

1

1-1

Samsung Electronics

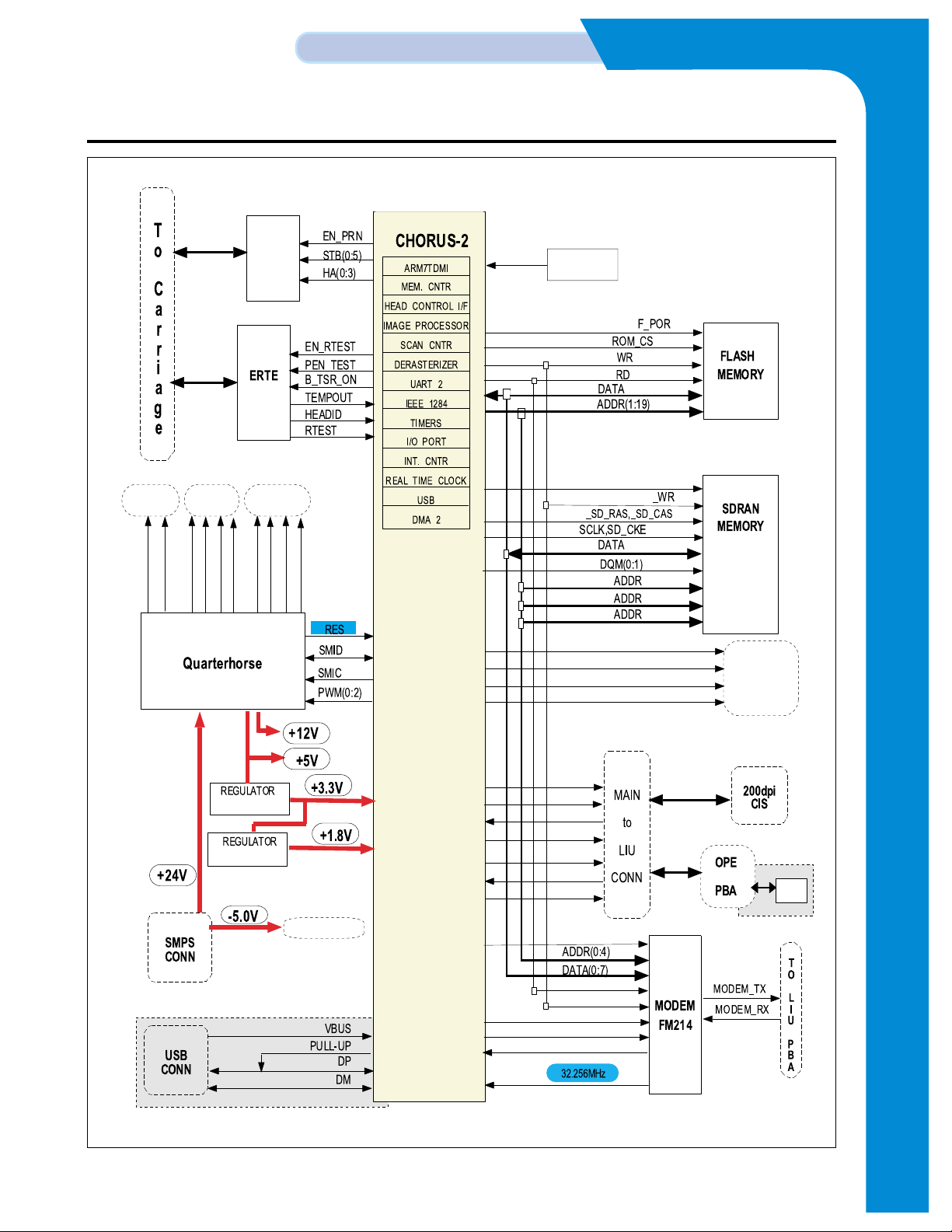

BLOCK DIAGRAM

Repair Manual

1. Block diagram

2Pin

5pin

4pin

7pin

7pin

5pin

SCAN MOTOR

(STEP)

5pin

2pin

CR

MOTOR

(DC)

LF

MOTOR

(STEP)

60 pin

30Pin

2pin

SS

MOTOR

(STEP)

CIS (200dpi)

LCD (16*1)

MICOM

DDET DSCA N

SMPS

(+24V,-5V)

SIXSHOOT

OR

DI SCRETE

TRANS

600:600

RELAY

CHORUS2

(Including IP)

MODEM

FM214 : SF-330/331P

FM214-VS : SF-335T

(14.4k)

FLASH

MEMOR Y

(8Mbit)

ERTE

SDRAM

16Mbit : SF-330/331P

64Mbit : SF-335T

QUARTER-

HO RSE

(C

DC-DC CONVERT

R/LF/SS

MOTOR DRV.)

Scec on

SPEECH

MAIN

OPE

LIU

SPEAKER

Encorder

Sensor

CR

HOOK S/W

(Ph oto

(SF-330/331P ONLY)˚

Interr upt or )

EXT LINE

TEL LINE

HANDSET

AFE

Mic

(SF-335T ONLY)

USB

SF-331P ONLY

SCAN

MOTOR DRV.

TRANS

600:600

MAIN P CB : 2 75 x 67 .5 m m

OPE PCB: 247 x 95.5mm

LIU PCB: 100 x 98.5mm

STUBBY

INK

INK-M40

INK-C

(SF-331P ONLY)

40

(3Pin Connector)

(8Pin Connector)

(6Pin Connector)

- This Document can not be used without Samsung's authorization -

Page 5

2

2-1

Samsung Electronics

CONNECTION DIAGRAM

Repair Manual

2. Connection Diagram

R37

R11

C1 COU

R13

R9

R39

R14

R40

ID2

R38

R48

R12

CIS

(200 DPI)

23456781

2341

A

B

C

D

E

ED DATE 01 2002.07.12

SIGN

D

W

G

E

N

G

C

H

K

A

P

P

REF NO SEC

1/1

RHINE(SF-330/331P/335T)

CONNECTION DIAGRAM

F

E

A

B

C

D

S

a

m

s

u

n

g

E

l

e

c

t

r

o

n

i

c

s

C

o

L

t

d

A

l

l

R

i

g

h

t

s

r

e

s

e

r

v

e

d

¡£¡¢

¡£

TX MOTOR

1

PICK_UP

SENSOR

CR

8

ENCODER

SENSOR

CN

2

MAIN

USB

11

1

2

3

4

5

1

2

3

4

5

6

LF MOTOR

LF _A

LF_nA

LF_nB

LF _B

1

2

3

4

5

1

2

3

4

5

+19.2V

CR MOTOR

6

CR_MOT_P

CR_MOT_M

1

2

1

2

3

SS MOTOR

SMPS

3

1

2

3

4

-5V

DGND

+24V

1

2

3

4

1

2

3

4

5

SS_A

+19.2V

SS_nA

SS_nB

SS_B

1

2

3

4

5

R1

R7

R3

R5

R15

R21

R17

R19

R23

R25

R27

R31

R33

R29

R35

R41

R43

R45

R47

TSR1

+19.2V (R49)

C3 COL

C4 CEL

ID1 (R50)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

9

LIU

HANDSET

1

2

3

4

1

2

3

4

MICRCV2

RCV1

MIC+

M

J

3

1

0

1

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

CIS_SI

DGND

OPE_R XD

nOPE_RST

+24V

OPE_TXD

+5V

nHOOK_DET1

CIS_LED

CIS_CLK

+5V

nDP

MJ1 MJ2

OPE

LCD

(16X1)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

DGND

+5V

VD

LCD_RW

LCD_CS

D0

D1

D2

D3

D4

D5

D6

D7

LCD_RS

D_DET

D_SCAN

OPE_TXD

nOPE_RST

OPE_RXD

+5V

1

2

3

4

5

6

7

3

2

DGND

1

2

3

4

5

6

7

AGND

MIC_IN

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

HS_VOL_CTL

AGC

HS_TX_CTL

AGND

MODEM_RX

AGND

MODEM _TX

DGND

-5V

MIC_IN

CIS_SIG

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

R46

R44

R42

R36

R32

R30

R34

R28

R26

R24

R20

R16

R18

R22

R6

R4

R8

R2

R10

C2 CE U

DGND

CH_X

+5V

CH_Y

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

CIS_SIG

DGND

+5V

CIS_SI

CIS_CLK

CIS_LED

+24V(VLED)

1

2

3

4

5

6

7

8

3

1

2

3

4

5

6

7

VBUS

USB_DM

USB_DP

DGND

1

2

3

4

TX_A

nTX_A

nTX_B

TX_B

+24V

N.C

N.C

5

DGND

nCML2

HS_RX_CTL

nCML1

+3.3V

REMOTE

nRING_DET

nHOOK_DET2

1

2

MIC_SIG

AGND

2

Only SF-335T

N.C

HOOK

DET

SPEAKER

1

2

1

2

SPK_ O UT

DGND

7

TEL LINE EXT LINE

FPC PIN NAME

SS SWITCH

1

3

2

1

2

nSS_SW

DGND

4

N.C

(42)(44)(4 6)(T2) (C4)(C3) ( T1)(45)(4 3)(41)

(40)(38)(3 6) (50)(49) (3 5)(37)(39)

(30)(32)(3 4) (I D2)(ID1 ) (33)(3 1)(29)

(28)(26)(2 4) (48)(47) (2 3)(25)(27)

(18)(20)(2 2) (21)(19)(1 7)

(16)(14)(1 2) (11)(13)(1 5)

(4)(6) (5)(3)

(2)(8) (7)(1)

(C2)(10) (9)(C1)

CN

CN

CN

CN

CN

CN

CN

CN

CN

CN

CN

CN

CN

CN

CN

CN

- This Document can not be used without Samsung's authorization -

Page 6

3

CIRCUIT DESCRIPTION

3.1 Main B’D

3.1.1 GENERAL DESCRIPTION

Main circuit consists of mainly consists of CPU and the controller part with various types of built-in I/O device driver(built-in RISC

Processor Core : ARM7TDMI), system memory part, Image control part (CHORUS-2) controlling input of image received from

media and conversion. The following nomenclatures by section is the same as those listed in the circuit diagram.

3.1.2 MEMORY MAP

The entire Addressing area provided by MAIN CONTROLLER(S3C46Q0X) is 256MBytes from 0x00000000 to 0x10000000,

and the Max. Address Range for each External Chip Select is 32M Byte or Half word from 0x000000 to 0x01FFFFFF and

embodied with Big-Endian Bus interface. MEMORYarea is divided into EXTERNAL ROM and RAM areas(See (Figure 1)), and

the areas actually used are 2M/8M BYTES SDRAM and 1M BYTES ROM(FLASH MEMORY). In case of SDRAM0, it uses

0x0000000h ~ 0x01BFFFFFFh area.

3. Circuit Description

<Figure 1. S3C46Q0X MEMORY MAP>

- This Document can not be u sed without Samsung's authorization -

Page 7

CIRCUIT DESCRIPTION

<1> General description

MAIN CONTROLLER(S3C46Q0X,U12) consists of this

system consists of CPU(ARM7TDMI RISC PROCESSOR), 8K BYTES CACHE, DATA and ADDRESS BUS,

PLL deriding input frequency and CLOCK CONTROLpart,

SERIAL COMMUNICATION part supporting UART, PRINT

HEAD control part, PARALLEL PORT INTERFACE part,

USB INTERFACE part, Internal Image Processor Part,

External DMA part MEMORY and EXTERNAL BANK control part, SYNCHRONOUS SERIAL INTERFACE control

part for interfacing Quarter_Horse, and TX Motor drive control and general purpose I/O control parts.(See Figure 2 )

3.1.3.2 S3C46Q0X FUNCTION DESCRIPTION

<1> SYSTEM CLOCK

There are two ways of Clock input method. One is the

method to make Master Clock(MCLK) at the internal PLL

by connecting X-tal and Capacitor to the outside, and

another method is to use MCLK(When inputting 40MHz)

directly, which supplies maximum 40MHz Clock to the

EXTCLK terminal(PIN65). The range of frequency being

input in case of using X-tal is limited to 4MHz~10MHz.

For making the MCLK, the Clock is supplied to the

EXTCLK Terminal of the ASIC by sending output power

(32.256MHz) of the MODEM (FM214 or FM214-VS, U16)

XCLK via the RC Filter. The inner side of the ASIC takes

the Clock, and it goes to the MPLL circuit to create a basic

operating frequency (66MHz MCLK signal). Also the Clock

goes to the UPLL circuit to make the operating frequency

of the USB Controller (48MHz).

<2> DATA and ADDRESS BUS CONTROL

1. _RD & _WR

_RD & _WR SIGNAL are synchronized with the inside

MCLK(66MHZ) and becomes active to Low.

These signal are Strobe Signal used to Read or Write

data when each Chip Select becomes active connected

to SDRAM, ROM(Flash), _WR PIN, _RD of Modem.

2. CHIP SELECT

(_ROMCS, _IP_CS,_MED_CS,_SCS0,_SCS1)

• _ROMCS : FLASH MEMORY(U7) CHIPSELECT

(LOW ACTIVE)

• _MODEM_CS : MODEM(U16) CHIP SELECT

(LOW ACTIVE)

• _SCSO : SDRAM (BASIC 16MBIT(U9), TAD 64MBIT(U8),

CHIP SELECT (LOW ACTIVE)

In case each Chip Select is low, it may Read or Write data.

3. D0 ~ D15

• 16BIT DATA BUS

4. A0 ~ A24

• ADDRESS BUS (A23 ~ A24 RESERVED)

3.1.3.1 BLOCK DIAGRAM and MAIN CONTROLLER description

- This Document can not be u sed without Samsun g's authorization -

Page 8

CIRCUIT DESCRIPTION

<Figure 2. Main Part Interface Signals>

_SS_SW

CR

MOTOR

(U5)

(U4)

(U7)

(SF-330 : U9)

(SF-331P : U9)

(SF-335T : U8)

(0:15)

(0:15)

(0:11)SF-330 :

SF331P:

SF-335T :

(0:11)

(0:12)

TX_A

CIS_LED

CIS_CLK

CIS_CIG

CIS_SI

_RD

_WR

-MODEM_RST

-MODEM_MCS

-MODEM_MIRQ

OPE_TXD

OPE_RXD

OPE_RST

TX_nA

TX_B

TX_nB

(U2)

(U12)

(U16)

3.3V

(U10)

(SF-331P ONLY)

1.8V

(U13 )

-

_scs0

-

-

-

-

-

-

-

LF

MOTORSSMOTOR

TX

MOTOR

SIX

SHOOTER

CR_MOT_P

CR_MOT_M

SS A

SS nA

SS B

SS nB

LF_B

LF_nB

LF_A

LF_nA

MIC

(SF-335T ONLY)

To Analog Part

- This Document ca n no t be used w it hout Samsung's authorization -

Page 9

CIRCUIT DESCRIPTION

<Figure 3. Flash Memory Read Timing>

<Figure 4. Flash Memory Write Timing>

EXTCLK

nGCSx

nGCSx

ADDR

tRWD

tRAD

Tacs

tRCD

nWE

DATA

nBEx

Tacc

Toch

Tcah

Tocs

tRCD

tRWD

tRDD

tRAD

tRDH

’1’

- This Docume nt can not be used without Samsung's authorization -

EXTCLK

ADDR

nGCSx

nWE

nGCSx

nBEx

DATA

tRAD

tRCD

Tacs

tRWD

Tocs

tRWBED

Tcos

tRDD

Tacc

tRWD

Toch

tRWBED

Toch

tRAD

tRCD

Tcah

tRDD

Page 10

CIRCUIT DESCRIPTION

<Figure 5. SDRAM Read Timing>

SCLK

SCKE

ADDR/BA

AP/A10

nGCSx

nSRAS

nSCAS

nBEx

nWE

DATA

’1’

tSAD

tSAD

tSCSD

tSRD

Trp Trcd

tSCD

tSBED

Tcl

tSWD

tSDS

tSDH

- This Docume nt can not be used without Samsung's authorization -

Page 11

CIRCUIT DESCRIPTION

<Figure 6. SDRAM Write Timing>

SCLK

’1’

SCKE

ADDR/BA

AP/A10

nGCSx

nSRAS

nSCAS

nBEx

nWE

DATA

tSAD

tSAD

tSCSD

tSRD

Trp

Trcd

tSWD

tSDD

tSDD

tSBED

tSCD

- This Docume nt can not be used without Samsung's authorization -

Page 12

CIRCUIT DESCRIPTION

<Figure 7. SDRAM Write Timing>

SCLK

SCKE

ADDR/BA

AP/A10

nGCSx

nSRAS

nSCAS

nBEx

nWE

DATA

tSAD

’1’

’1’

’HZ’

tSAD

tSCSD

tSRD tSRD

tSCD

tSWD

tSCSD

tSAD

Trp Trc

- This Docume nt can not be used without Samsung's authorization -

Page 13

CIRCUIT DESCRIPTION

<Figure 8. SDRAM auto Refresh Timing>

SCLK

SCKE

ADDR/BA

AP/A10

nGCSx

nSRAS

nSCAS

nBEx

nWE

DATA

tSAD

’1’

’1’

’HZ’

tSAD

tSCSD

tSRD tSRD

tSCD

tSWD

tSCSD

tSAD

Trp Trc

- This Document ca n no t be used w it hout Samsung's authorization -

Page 14

CIRCUIT DESCRIPTION

<Figure 9. SDRAM Self Refresh Timing>

SCLK

SCKE

ADDR/BA

AP/A10

nGCSx

nSRAS

nSCAS

nBEx

nWE

DATA

’HZ’

tSWD

’HZ’

’1’

’1’

’1’

’1’

’1’

’1’

’1’

tCKED

tSAD

tSAD

tSCSD

tSRD tSRD

tSCD

tSCSD

tSAD

tCKED

Trc

Trp

- This Document can not be u sed without Samsung's authorization -

Page 15

CIRCUIT DESCRIPTION

<3> EXTERNAL DMA part

This system does not use External DMA part.

<4> DRAM control part

Since S3C46Q0X has the DRAM CONTROLLER build-in,

it may be used by connecting DRAM with external memory. The Control mode of DRAM CONTROLLER provided

by S3C46Q0X is available for EARLY WRITE, NORMAL

READ, P AGE MODE, and BYTE_HALF WORD ACCESS,

and is supported even by EDO DRAM,and SDRAM as well

as, Fast page DRAM. This system uses SDRAM, and the

signal used for READ_WRITE uses _RD,_WR signal used

for SYSTEM BUS CONTROL. It is supported with auto

REFRESH and also by the Self-refresh mode for DRAM

BACK UP. It consists of 2 Banks connected to common

_SCSO, _SCAS, _SRAS, _SCLK, _SCKE, _DQM[1:0],

each of them may use up to 2M ~ 32M HALF WORD.

In this system, Basic 2MB (T AD 8MB) is applied as system

memory. The area of DRAM is specified in the DRAM

MEMORY MAP of Fig. 1, while the related TIMING DIAGRAM in Fig. 5, 6, 7, 8, 9.

<5> RTC (REAL TIME CLOCK) part

S3C46Q0X real time clock (RTC) operates by the super

capacitor although the system power turns off. In case of

the Basic, the backup is operated with the primary battery

(CR2032), and in case of the TAD, the backup is operated

with the secondary battery (Super-cap). The RTC has the

time data that is stored as the 8 bit BCD (binary coded decimal) format. The data include second, minute, hour, date,

day , month, and year. The RTC unit works with an external

32.768 kHz crystal and also can perform the alarm function

and round reset function.

<6> PARALLEL PORT INTERFACE division

This system does not use Parallel Port Interface Division.

<7> USB INTERFACE PART

1. USB function description

As the mode of implementing low cost express PC

Interface, USB was applied. At USB, PC plays the role of

route hub simultaneously by existing in the highest level as

the host. That is, the device supporting each USB is connected centering on PC.

The device is available for Interface for the maximum of

127. USB cable is composed of total of a set of twisted pair

and 2 power lines. The part for implementing USB function

is included in S3C46Q0X.

For Interface of USB, pull-up of 15KΩ is interfaced to the

data line of high level instruments, and, among data lines

of lower level instruments, pull-up resistance of 1.5KΩ is

interfaced to any one.

At this time, DP line is pulled up for Full Speed device, and,

for Low Speed device, DMline is pulled up. For upper level

instruments(Host, HUB) speed of device is classified interfaced to low level by detecting any one among DP and DM.

If both lines are in the level of GND at the same time,

device is judged that low device is not interfaced. In the

transmission mode of USB, there are (1) Control transmission, (2) Interrupt transmission, (3) Bulk transmission,

isochronous transmission. Control transmission is for Host

to find out configuration information from USB device. This

is conducted when device is interfaced. Interrupt transmission is used when small quantity of data is sent periodically. Interval value may be known from device in the case of

initial setting. Bulk transmission is valid in case of trying to

transmit data in large quantities or in case of transmitting

them accurately.

Isochronous transmission should be assured of bandwidth,

and is used when transmitting large quantities of information. Data in voice is used where delay is not allowed but

small error is allowed. At USB coding mode and bit supping

are being conducted. First, in case original data is 1, bit

shall not change, and only when original data is 001, it shall

be inverted. Only while data is 1, 1 and 0 shall be repeated. Also, in case 1, original data, is continued in 6 bit, 0

shall be inserted, Also, in the 1st phase of packet, data in

the synchronized pattern shall be sent. About more

detailed information regarding USB,

see http//:www.usb.org.

- This Document ca n no t be used w it hout Samsung's authorization -

Page 16

CIRCUIT DESCRIPTION

2. operation description

This system, when Host and USB cables are connected, and when +5V is detected in power detector inside chip and Vbus,

3.3V comes out through Pull-uP terminal. This is also connected to DPin pattern of hardware and supports Full-speed. Utilizing

Configuration Endpoint, EPO, in USB controller, Plug & Play function is operated. Exchange of information between PCs is

accomplished through DP and DM erminals. This terminal decides transmission speed depending on connection of regulator

output in USB controller, and decides size of signal following USB and SPFC. Signal of general DPand DM terminals are same

as Figure 10-3.

<8> HEAD Control Part

1. General Information

It drives the Inkjet Head, and it controls the HA[3:0] and _STB[5:0], which control the Six-Shooter. The Six-shooter creates the

signal to drive 48 Nozzle of the HEAD. The Stubby Head in the system is the Bubble type head, and has 48 nozzle for the

Mono and Color(Printer only). 48 Nozzle Head of the mono and color head receives the data by 6 bytes per1 slice. The data

from the HDMAgoes to the CDE (Consecutive Dot Eliminator), DITH, and Data Out Block, and the data and address, controlled

by the Fire signal and the Fire Window Time of the CRCON_CRFIRE Block, are outputted to the head Driver (Six-Shooter).

The head consists of the 4 firing groups. Each group has 12~14 nozzles, and only one nozzle is firing per a Fire in each group.

It means that one Fire can make 4 nozzles firing.

< Figure 10-3. USB Signal Line DIAGRAM >

< Figure 12. Print48(HP) Firing Timing >

- This Document can not be u sed without Samsung's authorization -

Page 17

CIRCUIT DESCRIPTION

2. HEAD DATA OUTPUT FORMAT

The 1 slice data [47:0] from the HDMA is outputted with the PHADR in order as below.

<9> SYNCHRONOUS SERIAL INTERFACE PART

It interfaces with Quarter-horse ASIC and consists of SMIC, SMID, PWM, and _RST. The Quarter-horse is the

Motor Driver IC. The Quarter-horse interface Logic makes the data as a serial for transmitting the data to the

Quarter-horse, and transmits the serial to the Quarter-horse IC by controlling it with the arranged Protocol. The

Quarter-horse uses two signals, SMIC (clock) and SMID (data) to transmit the data. It transmits 3 bytes at once,

and the 3 bytes mean the Device Address, Data 1, and Data 2. It is transmitted from MSB to LSB. The Quarterhorse sends the ACK signal at the end of the each byte to confirm the transmitted data. In case of no receiving

ACK signal, the Quarter-horse_interface Logic sends the 3 bytes again. Depending on the level of the SMIC and

SMID signals, the different messages are shown.

If it is high (SMIC) and high (SMID), it means the IDLE condition which means no data is received, if it is high

(SMIC) and high-to-low-transition (SMID), it means the data transfer is started, and if it is high (SMIC) and low-tohigh-transition (SMID), it means the last data transfer.

- This Document ca n no t be used w it hout Samsung's authorization -

Page 18

CIRCUIT DESCRIPTION

While transferring the motor phase, if there is NAK, the data transfer is automatically stopped and being in the

IDLE condition. In the case, The S/W makes new value to transfer the data, or if the NAK Enable of the Control

Register is set, automatically the same value is transferred for data transfer after for a while.Quarter-horse controls two Stepper motors (Line Feeder and Service Station) and one DC Motor (Carriage Motor).

<10> MOTOR Control Part

S3C46Q0X supports two Step Motors and one DC Motor, but only TX Scan Motor is used in the system. The Quarter-horse

supports LF, SS, and CR MOTOR.

<11> S3C46QOX General Purpose I/O Port.

1. 1 Chorus-2 Assigned GCS Ports for RHINE

- This Document ca n no t be used w it hout Samsung's authorization -

Page 19

CIRCUIT DESCRIPTION

2. Chorus-2 Assigned GPO Ports for RHINE

- This Document ca n no t be used w it hout Samsung's authorization -

Page 20

CIRCUIT DESCRIPTION

3. Chorus-2 Assigned GPI Ports for RHINE

4. Chorus-2 Assigned GPIO Ports for RHINE

- This Docume nt can not be used without Samsung's authorization -

Page 21

CIRCUIT DESCRIPTION

5. HP IMPORTANT ASIC Ports for RHINE

- This Document can not be u sed without Samsung's authorization -

Page 22

CIRCUIT DESCRIPTION

3.1.3.3 RESET circuit

This system is configured with PRIMARY RESET(_RST) of Power Reset, Reset by WATCH DOG TIMER, external PRIMARY

RESET , and SECOND RESET(__F_POR) which was done AND. PRIMARYRESET SYSTEM is used for resetting MAIN CONTROLLER(U12) when System Power is authorized, and SECOND RESET resets FLASH MEMORY(U7). Figure below is

BLOCK DIAGRAM related to the reset of entire system.

When +5V reaches +4.75V so that system may operate, POWER MONITOR(U2) moves to High(+5V) after maintaining

low(OV) in the degree of 50mS-200mS output while monitoring it. This Reset signal is input into MFP

CONTROLLER(S3C46Q0X, U12) right away, and MFPCONTROLLER becomes awake. And it releases _F_POR after MCLK

1 clock. The Quarter-horse needs +24V to be operated, but +5.0V is supplied by the Buck Regulator circuit. If +5.0V is incompletely supplied such as +4.75V, it is checked as the Power Failure. The _RST output becomes low (0V), and the S3C46Q0X

(U12) confirms it to make it RESET (LOW ACTIVE). When the S3C46Q0X is released from RESET, the _F_POR of the

S3C46Q0X and FLASH MEMORY are reset.

<1> WATCH DOG OUTPUT (_F_POR)

Since WA TCH DOG TIMER, which is Programmable Counter in (S3C46Q0X, U12) is set as disable for INITIALSTATE, it shall

be set as Disable so that it won’t operate, and after it is initialized for operation, it shall be reused by setting it Enable. When

Watch Dog Reset occurs, it is about 10mS depending on the value set at the initial stage. And Counter value of Watch Dog

Timer is changed by the program. Reset signal (_F_POR,U12-94) shall be generated, and entire system shall be Reset and

initialized.

_RST

< Figure 13. POWER RESET BLOCK DIAGRAM >

- This Document can not be u sed without Samsung's authorization -

Page 23

CIRCUIT DESCRIPTION

3.1.5.1 General description

The image processor, built-in to Chorus-2 is consisted of

Scanner Interface, Motor control, Shading Acquisition _

Shading Correction, Gamma Correction, Vertical

Decimation, Horizontal Enlargement/Decimation and

Binarization. (See Figure 16)

3.1.5.2 Features & Functions

• 0.18µm CMOS process, 208-pin QFP, std 130 library

• Frequency : 66MHz(15ns)

• Image Sensor I/F : 200/300/600dpi CIS or CCD

• Scanning Function

-

Color Gray Image : each 8 bits / RGB

- Mono Gray Image : 8 bits / pixel

• Maximum processing Width

-

A4, 600 dpi

- 5KB Effective pixel

• Ideal MSLT (Minimum Scan Line Time)

-

Grey mode(Color) : 3(RGB) X 5KB X 15nsec X 16clock =3.69 msec

- Grey mode(mono) : 1 X 5KB X 15nsec X 16clock =1.23 msec

- Grey mode(Color) : 1 X 5KB X 15nsec X 16clock =1.23 msec

• A/D conversion depth : 10 bits

3.1.4.1 General description

MEMORYapplied in this system are FLASH MEMORY(U7)

of 1Mbyte, SDRAM (SF-330/331P:U9 ; 2Mbyte ,/ SF-335T

: U8 ; 8Mbyte)

3.1.4.2 MEMORY configuration

By each CHIP SELECT ( ROM_CS, _SCS0, _SD_RAS

,_SD_CAS ), FLASH MEMORY and SDRAM are selected,

and DATA is accessed by HALF WORD unit.

3.1.4 MEMORY

3.1.5 Image Processing Part

- This Document ca n no t be used w it hout Samsung's authorization -

Page 24

CIRCUIT DESCRIPTION

3.1.5.3 Block Diagram

<Figure 16. Block Diagram of IP_TOP>

- This Docume nt can not be used without Samsung's authorization -

Page 25

CIRCUIT DESCRIPTION

3.1.6 QUARTERHORSE ASIC

3.1.6.1 General Information

The Quarter-horse ASIC consists of the Serial Interface port which interfaces with the main controller, Linear Pre-regulator

Circuit, Power On Reset Generation Circuit, and Motor Drive part.

<1> SERIAL INTERFACE

It interfaces with the Main Controller (S3C46Q0X), and consists of SMIC, SMID, PWM, and _RST. Please, refer to the picture

17 for the timing.

< Figure 17. SERIAL INTERFACE INPUT timing diagram>

- This Docume nt can not be used without Samsung's authorization -

Page 26

CIRCUIT DESCRIPTION

<2> SERIAL INTERFACE

PIN NAME DESCRIPTION DIRECTION / TYPE

preg Pre-regulator control analog/output

Vin DC motor driver and 5V regulator input supply voltage power/input

DCMA DC motor drive half bridge A power/bidirectional

DCMB DC motor drive half bridge B power/bidirectional

DCPWM PWM input signal CMOS/input

nPA Paper motor phase Adrive power/open drain

nPnA Paper motor phase nA drive power/open-drain

nPB Paper motor phase B drive power/open drain

nPnB Paper motor phase nB drive power/open drain

+12V +12V EEPROM programming voltage output

nSA Service station motor phase Adrive power/open drain

nSnA Service station motor phase nA drive power/open drain

nSB Service station motor phase B drive power/open drain

nSnB Service station motor phase nB drive power/open drain

DATA Serial Data Input (and ACK output) CMOS/input

SCLK Serial Clock Input CMOS/input

GATE1 V1 gate drive power/output

SOURCE1 V1 source voltage return analog/input

Vfb V1 return to close loop analog/input

COMP1 V1 compensation pin analog

SWITCH +5V switching output power/output

COMP5 +5V compensation pin analog

+5V +5V input for logic and to close loop analog/input

Vdd Input Voltage power/input

CP1 Bootstrap capacitor pin 1 analog

CP2 Bootstrap capacitor pin 2 analog

Ground Ground analog

nRESET Active low totem pole reset output CMOS/output

Enable Chip Enable CMOS/input

CT Reset timing delay capacitor analog

SPWMA Stepper motor pwm phase A/nA CMOS/input

SPWMB Stepper motor pwm phase B/nB CMOS/input

Vp Boost voltage output for high side FETs power/output

GND (11) Used both as ground and as heatsinking analog

- This Document ca n no t be used w it hout Samsung's authorization -

Page 27

CIRCUIT DESCRIPTION

3.1.6.2 QUARTERHORSE FUNCTION

<1> PEN / MOTOR SUPPLY VOLTAGE REGULATOR

It receives the inputted power of +24V, and the power flows to the buck type regulator, which consists of the external N-channel FET and SCHOTTKY diode, to make +19.2V . The power uses as the main power of the ink head, CR, and LF, SS MOTOR.

<2> +5V REGULATOR

The +24V (inputted power) is supplied, and it becomes +5V of the logic power by using the internal switching FET Buck type

regulator. It becomes +3.3V to support the main power of the CPU by using external +3.3V Regulator , and the +3.3V becomes

+1.8V to support the internal power of the CPU by using +1.8 Regulator.

<3> RESET CIRCUIT

The Reset of the Quarter-horse starts to work when the +5V is going down under +4.75V. It has the 1.5~5 usec of Sensitivity

Timing Margin for preventing the minute shakiness of the power by ESD. Also, the Time Delay of the Reset can be controlled

from 1ms to 1s by the Capacitor when power on.

<4> MOTOR DRIVERS

The Quarter-horse drives one DC Motor and two stepping motors. The DC Motor drives +19.2V as the FULL H-BRIDGE, and

the direction information goes to the CPU via the Serial Interface port. Also, it is inputted the PWM Modulator from CPU. The

Stepping Motor is driven by the UNIPOLAR, and the phase information is transmitted to the CPU via the Serial Interface port.

1. DC MOTOR

TRUTH TABLE

DCA DCB PWM A high side A low side B high side B low side

00X offonoff on

010 onoffon off

0 1 1 off on on off

100 onoffon off

101 onoffoff on

11X onoffon off

- This Document ca n no t be used w it hout Samsung's authorization -

Page 28

CIRCUIT DESCRIPTION

2. STEPPER MOTOR TRUTH TABLES

<PAPER MOTOR>

<SERVICE STATION MOTOR>

Inputs Outputs

Whinny Register Bits Pin 38 (37) Pin 35(31) Pin 33(29)

PPWM pa pna SPWMA nPA nPnA

(pb) (pnb) (SPWMB) (nPB) (nPnB)

000 0offoff

000 1offoff

001 0offon

001 1offon

010 0onoff

010 1onoff

011 0offoff

011 1offoff

100 0offoff

100 1offoff

101 0onoff

101 1offon

110 0offon

110 1onoff

111 0offoff

111 1offoff

Inputs Outputs

Whinny Register Bits Pin 38 (37) Pin 36(32) Pin 34(30)

PPWM sa sna SPWMA nSA nSnA

(sb) (snb) (SPWMB) (nSB) (nSnB)

000 0offoff

000 1offoff

001 0onoff

001 1offon

010 0offon

010 1onoff

011 0offoff

011 1offoff

100 0offoff

100 1offoff

101 0offon

101 1offon

110 0onoff

110 1onoff

111 0offoff

111 1offoff

- This Document ca n no t be used w it hout Samsung's authorization -

Page 29

CIRCUIT DESCRIPTION

<5> Quarterhorse Block Diagram

<Figure 18. Quarterhorse Block Diagram showing typical external components>

- This Document ca n no t be used w it hout Samsung's authorization -

Page 30

CIRCUIT DESCRIPTION

3.1.6 SIXSHOOTOR ASIC

3.1.6.1 General Information

The Six-shooter ASIC exists for operating the Ballast Resistor and TIJ 2.0 Inkjet Head, and it has 4 head address HA [3-0],

input of the 6 strobe nSTB [5-0], and output of the 48 nozzle control.

3.1.6.2 OPERATE TIMING AND INTERNAL BLOCK DIAGRAM

<figure 19. SIXSHOOTER Power Driver Driver Diagram>

<figure 20. SIXSHOOTER inside Block diagram>

- This Document can not be u sed without Samsung's authorization -

Page 31

CIRCUIT DESCRIPTION

3.1.6.3 Decoder Logic Truth Table

nCS HA3 HA2 HA1 HA0 nSTRB5 nSTRB4 nSTRB3 nSTRB2 nSTRB1 nSTRB0 nRx

1 X X X X X X X X X X None

0 X X X X 1 1 1 1 1 1 None

0X000XXXXX0R26

0X001XXXXX 0R4

0X010XXXXX 0R6

0X011XXXXX 0R8

0X100XXXXX 0R10

0X101XXXXX 0R12

0X110XXXXX 0R14

0X111XXXXX 0R16

00X00XXXX0XR36

00X01XXXX0XR38

00X10XXXX0XR40

00X11XXXX0XR42

01X00XXXX0XR44

01X01XXXX0XR46

01X10XXXX0XR48

01X11XXXX0XR2

0 0 X 0 0 X X X 0 X X R24

0 0 X 0 1 X X X 0 X X R30

0 0 X 1 0 X X X 0 X X R32

0 0 X 1 1 X X X 0 X X R34

0 1 X 0 0 X X X 0 X X R18

0 1 X 0 1 X X X 0 X X R20

0 1 X 1 0 X X X 0 X X R22

0 1 X 1 1 X X X 0 X X R28

0 X 0 0 0 X X 0 X X X R25

0X0 01X X 0 X X XR3

0X0 10X X 0 X X XR5

0X0 11X X 0 X X XR7

0X1 00X X 0 X X XR9

0X1 01X X 0 X X XR11

0 X 1 1 0 X X 0 X X X R13

0 X 1 1 1 X X 0 X X X R15

0 0 X 0 0 X 0 X X X X R35

0 0 X 0 1 X 0 X X X X R37

0 0 X 1 0 X 0 X X X X R39

0 0 X 1 1 X 0 X X X X R41

0 1 X 0 0 X 0 X X X X R43

0 1 X 0 1 X 0 X X X X R45

0 1 X 1 0 X 0 X X X X R47

01X11X 0 X X X XR1

01X110XXXXXR27

00X110XXXXXR33

01X010XXXXXR19

00X010XXXXXR29

01X100XXXXXR21

00X100XXXXXR31

01X000XXXXXR17

00X000XXXXXR23

- This Document ca n no t be used w it hout Samsung's authorization -

Page 32

CIRCUIT DESCRIPTION

3.1.6.4 Power Driver Output Loading Schematic

<Figure 21. SIXSHOOTER Power Output Loading Schematic>

- This Document ca n no t be used w it hout Samsung's authorization -

Page 33

CIRCUIT DESCRIPTION

3.1.7 ERTE ASIC

3.1.7.1 General Information

The ERTE ASIC is driven by 19.2V, and consists of three functional blocks, such as the Head, the Pen ID which find out the

kind of head by checking temperature and resistance difference when firing, and the Resistor Test which checks the possibility of the head firing.

3.1.7.2 ERTE Block Diagram

<Figure 22. Block Diagram of ERTE>

- This Document ca n no t be used w it hout Samsung's authorization -

Page 34

CIRCUIT DESCRIPTION

3.1.8 FAX SENDING/RECEIVING PART

3.1.8.1 General Information

The circuit is for managing the transmitting signals of Modem and between the LIU part and Modem.

3.1.8.2 MODEM

There are two models, FM214 for the Basic model and FM 214-VS for the TAD model, which supports the Digital TAD and

Speaker Phone. The Main PCB is designed for joint use in the Rhine. The modem has the single chip fax modem function

and DTMF detection/DTMF signal generation function. The principal ports of the FM214 modem are as follows when using T AD

Model. The LineOut (PIN69) is a port of the sending output from the modem, and the LineIn (PIN60) is a receiving input port.

The Modem_RST (PIN115) is the signal from the CPU for initializing modem without system power off.D0~D7 are Data Bus,

and RS0~RS4 is the signal for internal Register Selection of modem to decide mode. _MCS (PIN 91) is a signal of the Modem

Chip, and _RD (PIN 92) and _WR (PIN 90) are control signals for a reading and writing. IRQ (PIN 108) is a signal for the Modem

Interrupt Output. The transmitting speed of the FM214 is Maximum 14.4k bps.

3.1.8.3 SENDING PART

The circuit manages the sending output, which is analog signal of the modem.The output signal by each mode comes out from

the modem lineout (PIN69), and it is sent out to PSTN telephone line via the Matching Transformer (600:600) of the LIU B'd.

3.1.8.4 RECEIVING PART

The analog signal from the Matching Transformer (600:600) of the LIU B'd is amplified at the LIU PBA, and the second amplification is at the main input part for inputting the signal in the LINEIN (PIN60) of receiving input part.

3.1.8.5 MIC INPUT PART (Not for the SF330 Basic Model)

SF335T Model has the Speaker Phone function and Tad function. For recording OGM and supporting a Speaker phone, MIC

is needed. The first amplified signal at the OPE goes to the main and makes the second amplification. After that, it is inputted

in the MIC (PIN61, 35) of modem.

- This Document ca n no t be used w it hout Samsung's authorization -

Page 35

CIRCUIT DESCRIPTION

3.1.8.6 FM214 MODEM BLOCK DIAGRAM

3.1.8.7 FM214-VS MODEM BLOCK DIAGRAM

- This Docume nt can not be used without Samsung's authorization -

Page 36

CIRCUIT DESCRIPTION

3.1.8.8 FM214 SERIES MODEM PIN DESCRIPTION

- This Document ca n no t be used w it hout Samsung's authorization -

Page 37

CIRCUIT DESCRIPTION

3.2 OPE

3.2.1 Basic Concept

3.2.2 UART Operation

3.2.1.1 Overview

OPE BOARD is separated from the Main Board functionally, and operates entire Micom(HT48C5A-000Z) in the

Board. OPE and Main exchange mutual information using

UART(universal asynchronous receiver/transmitter) channel. Also, Resetting of OPE is designed to control at the

Main. Micom in OPE performs key-scanning and LCD, LED

display control, and senses document detect, Scan position

and so on. When information is generated from OPE(key

touch, sensor level change, etc.), it sends specific code

coping with the situation to Main, and the Main operates

system by analyzing this code. If the Main tries to display

data on OPE, the Main sends data to OPE via UART line

on the basis of the format specified, and OPE displays it to

LCD.

In the case of the TAD Model, the MIC for the Speaker

Phone and OGM and the Pre-Amp part of the MIC have

built-in at OPE circuit.

3.2.1.2 UART

OPE and MAIN exchange information mutually by using

asynchronous communication mode(UART), and in full

duplex. Band rate is 9600bps, and uses 7.37MHz resonator

as oscillating element. It engages in communication with

8bit data without parity bit. UART line has two lines for Tx

and Rx, and the default level is in the 'high' state. For communication, the start bit(low level) is transmitted before 8bit

data. When the data transmission(8bit) is completed, the

high state is maintained as the stop bit(high level) is transmitted. Data is transmitted from LSB(DO), and MSB(D7) is

transmitted lastly.

3.2.2.1 UART Communication

<1> UART TX FORMAT

Codes for change of KEY, TOUCH, SENSOR LEVEL and

so on are transmitted in single code without PRE/POST

DATA, and OK or Error messages to check if communication is performed properly are also transmitted in single

code. Provided that, in case the Main requested a certain

value(LCD, other register) particularly, data requested is

transmitted followed by sending Post Data('EOH') first.

<2> UART RX FORMAT

Data being received will be arranged to be received according to the following specified format to know what data they

are.

DATA are received in the sequence of A,B,C, and D, and

the Check sum to check if the transmission is made properly will be found by doing XOR data from Ato C.

a) Type of data received

b) Number of data (N+1) received after.

----------

c) DATA(N)

----------

d) Check sum(1)

- This Document ca n no t be used w it hout Samsung's authorization -

D0 D1 D2 D3 D4 D5 D6 D7

start stopbit data 8bit (D0 ~ D7) bit

Page 38

CIRCUIT DESCRIPTION

3.2.2.2 UART communication DATA

<1> UART transmission DATA(received by the Main side)

<Note> 1. After this, keep waiting until there is response from the Main.

2. The case of longer time(longer than 10ms) elapsed longer than waiting time required for Interface

is regarded as fail.

3. After this code went out, then data requested it goes out.

Types STATUS USED PORT LEVEL REMARKS

key data ON PORT PC0~PORT PC7 L

OFF H

SCAN POSITION sensor ON PORT PB3 H MAGIC not applied

OFF L

DOC. detector sensor ON PORT PB-5 L MAGIC not applied

OFF H

For initial use of initial OPE After power on, generated only once

UART communication OK (Note 2)

ERR

LCD interface of OPE OK When failed in the interface once &

when succeeded first(Note 2)

ERR

Self initial generation of OPE LCD data keeps status quo

Send data requested by the Main Data types:LCD, other(Note 3)

- This Document ca n no t be used w it hout Samsung's authorization -

Page 39

CIRCUIT DESCRIPTION

<2> Received DATA(transmitted by MAIN)

1. DATA TYPE

2. NO. OF DATA

• In case DATA is N BYTE, N+1

3. DATA

In case DATATYPE is LCD DATA, it is configured with ASCII CODE to be displayed.

In case DATATYPE is LED DATA, it is 1 BYTE.

• LED DATA BITASSIGNMENT :

4. CHECK SUM

The value done XOR all of them from DATA TYPE to DATA.

DATA BIT BIT 0 BIT 1 BIT 2 BIT 3 BIT 4 BIT 5 BIT 6 BIT 7

LED NO. LED 0 LED 1 LED 2 LED 3 LED 4 LED 5 LED 6 LED 7

Answer LED Ink Save LED Silent Mode LED not used

DATA types Meaning Remarks

a1 H LCD DISPLAY DATA(FULL LINE)

a4 H LED DATA

- This Document ca n no t be used w it hout Samsung's authorization -

Page 40

CIRCUIT DESCRIPTION

3.2.3 I/O PORT configuration and use usage

It has 32 I/O Ports, and 24 Ports of them are arranged to decide I/O direction with Software Control, and the rest 8 Ports are

arranged to be used for Input or Output only. All of I/O Ports are classified into four Blocks according to the characteristics of

I/O Control, and each Block consists of 8 Ports.

<1> Assignment of Port PAX

• PA1 : ANSWER LED (RED)

• PA2 : INK_SAVE LED (GREEN)

• PA3 : NIGHT_MODE LED (GREEN)

• PA4 : RESERVED

• PA5 : SRESERVED

• PA6 : RESERVED

• PA7 : RESERVED

* HIGH --> LED OFF

LOW --> LED ON

<2> Assignment of port PBX

• PB0(Output) : LCD Enable

• PB1(Output) : LCD R/W

• PB2(Output) : LCD RS

• PB3(Input) : GND

• PB4(Input) : Unused (Pull-up)

• PB5(Input) : GND

• PB6(Output) : UART TXD in Main UART

• PB7(Input) : UARTRXD from Main UART

LCD ON/OFF

In case of VCC applied to LCD No. 3 PIN (BACKGROUND LEVEL), all the LCD screen will be erased. When the power is

applied, MICOM P A0~7 are Default High LEVEL, so LCD will be OFF. From Jupiter3, LCD will be ON simultaneously with OPE

reset.

Q1, Q2 have the function of simply doing On/off only.

When pressing the Power Key, actual power is not turned Off but 11.75V terminal of Thundervolt Off in the Main, while simply

the LCD DISPLAY should not appear in OPE. At this point, Micom should be operated normally to recognize the Key when

pressing the Power key again. [The same effect as Power save]

Type I/O Control I/O direction USE Remarks

PA X Byte Control I/O => Output LED Control

Used as LCD VCCCONTROL in MAGIC.

PB X Byte Control In : 4, Out : 4 UART, LCD, Sensor MAGIC SENSOR not applied.

PC X Byte Control I/O => Input Key Input

PD X Byte Control I/O => Output LCD Data, Key Scan

- This Document ca n no t be used w it hout Samsung's authorization -

Page 41

CIRCUIT DESCRIPTION

3.3 LIU B’d

3.3.1 GENERAL DESCRIPTION

LIU ( Line interface unit ) is consist of Tel-line interface part and FAX/Speech part.

<1> TEL LINE INTERFACE PART

• Surge and over voltage protection part

• Remote circuit

• Ring detector circuit

• Ext phone detector circuit

• DCR and Impedance matching circuit

1. Surge and over voltage protection circuit.

• ARR1 component is the protection of lightning surge. ( Spec : 400V ± 20% , 500A )

• VAR2 is a varistor that decrease over voltage noise. ( Spec : 82V , 1250A)

• Over 400V of high voltage is decreased by ARR1 and the rest voltage

• (low voltage : 400V under level) is decreased by VAR2.

2. Remote circuit

• C8, R13 use for DC coupling / On-hook impedance.

• Over voltage is depressed by ZD component

• DTMF Detector path for Local start ( SF-330/331P )

• Caller ID Signal path

TIP

RING

ARR1

Dode

VAR2

C8

Remote

Line

15nF, 250V

Trans

100-1016

R13

30k

ZD2

R6

30k

C4

1nF

- This Docume nt can not be used without Samsung's authorization -

Page 42

CIRCUIT DESCRIPTION

3. Ring detector circuit

• C9 use for DC coupling and Ring impedance ( Ring impedance spec : Min 4Kohm)

• R1 ( 1/ 1W )protect overvoltage into PC814.

• Ring signal transfer from 1st circuit to 2nd circuit through PC814

• R2/C1 translator to recognize for ring signal.

4. Ext hook detector circuit

• SF-330/331P model have Ext-phone jack to connect TAM or external phone.

• VAR1 protect overvoltage into PC814.

• R7 is marching component of Ext phone for detect another normal phone.

5. DCR / Current limit circuit / impedance

• DCR / Current limit circuit consist of R25, C13, Q2, Q3, R21, R23, R14.

• Current limit circuit apply only EU nation.( Q3, R21 )

• Impedance circuit consist of T2, C26, R43, R41, C35.

R7

R25

C13

Q3

R21

Q2

R23

R14

C26

AGND

R43

C15

R41

C35

C39

T2

100-1016

- This Document ca n no t be used w it hout Samsung's authorization -

Page 43

CIRCUIT DESCRIPTION

<2> Fax / Speech part

• Fax TX / RX circuit

• Speech part ( Handset MIC / RECEIVE )

1. FAX TX / RX circuit

• DTMF / OGM (335T) and Fax tone transmit from Modem tx part → impedance matching part (R43, C35, R4) →T1

trans → tel-line.

• Dial tone / ICM ( 335T ) and Fax tone transmit form tel-line → T1 trans → Modem rx part.

2. Speech part ( Handset MIC / Receive )

• Handset Receive

MODEM TX

MODEM RX

R41

C35

R43

C26

ZD3

AGND

T2

VDD

VDD

R27

C21

R24

AGND

Q5

C17

C10

Q2

BD2

RVC

R31

C23

C20

R16

C38

+

R26

Q4

R22

R28

VDD

VDD

VDD

BD1

C14

R20

C16

MIC

AGND

AGND

AGND

AGND

AGND

- This Document ca n no t be used w it hout Samsung's authorization -

Page 44

4

4-1

Samsung Electronics

SCHEMATIC DIAGRAMS

Repair Manual

Samsung Electronics

SCHEMATIC DIAGRAMS

Repair Manual

4. Schematic Diagrams

4-1 Main Circuit Diagram (1/4)

-> Bead 2012 type

SF-330/335T

-> 0ohm 2012 type

(BD5,BD8:600ohm, BD6,7:120ohm)

(*)

SF-331P

- T his Document can not be used without Samsung's authorization -

Page 45

4-2

SCHEMATIC DIAGRAMS

Samsung Electronics

Repair Manual

Main Circuit Diagram (2/4)

FOR SF-335T 64M

FOR SF-330 16M

- This Document can not be used without Samsung's authorization -

Page 46

4-3

Samsung Electronics

SCHEMATIC DIAGRAMS

Repair Manual

Main Circuit Diagram (3/4)

(DSP_D)

FM214 for SF-330/SF331P

(DSP_D)

(for SF-335T)

FOR SF-335T

(DSP_D)

(IA_D)

(IA_A)

(DSP_D)

(IA_D)

(DSP_A)

(DSP_D)

FOR SF-335T

FOR SF-330

(DSP_D)

(IA_A)

- This Document can not be used without Samsung's authorization -

Page 47

4-4

SCHEMATIC DIAGRAMS

Samsung Electronics

Repair Manual

Main Circuit Diagram (4/4)

(ONLY 331P)

(ONLY 331P)

(ONLY 331P)

(ONLY 331P)

ERTE

(ONLY 331P)

- This Document can not be used without Samsung's authorization -

Page 48

4-5

Samsung Electronics

SCHEMATIC DIAGRAMS

Repair Manual

4-2 LIU Circuit Diagram

2002.06.25

- This Document can not be used without Samsung's authorization -

Page 49

4-6

SCHEMATIC DIAGRAMS

Samsung Electronics

Repair Manual

4-3 OPE Circuit Diagram

2002.06.03

D2

D6

D4

D2

D0

D0

D6

D4

- This Document can not be used without Samsung's authorization -

Loading...

Loading...