Page 1

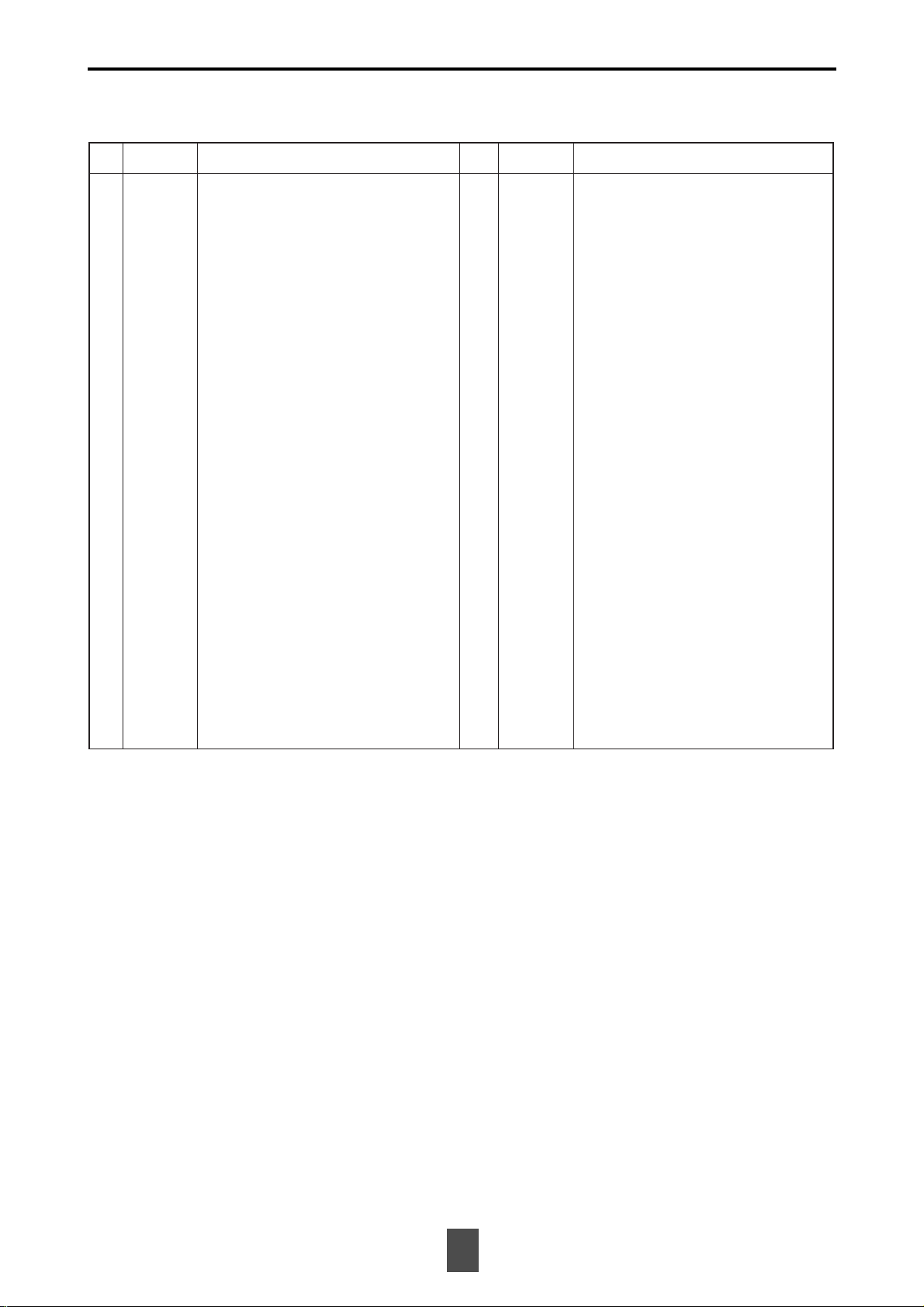

n CD-ROM Block diagram

SPINDLE CONTTROL

TRACKING CONTROL

FOUSING CONTROL

B.L SPINDLE MOTOR

BRUSH SLED MOTOR

OPTICAL PICKUP

DRIVING MECHANISM

SLED CONTROL

LASER CONTROL

RF SIGNAL

EJECT MECHANISM

COMPACT DISC

DISC TURN TABLE

CLAMPING PULLEY

DISC ACCESS INDICATOR

EJECT BUTTON

HEADPHONE OUTPUT

PLAY BUTTON

SLED SERVO ERROR

SPINDLE SERVO ERROR

TRACKING SERVO ERROR

FOCUSING SERVO ERROR

RF

SIGNAL

OSC

33.86MHz

CERAMIC OSC

25.4MHz

CERAMIC OSC

EFM DEMODULATOR

CIRC DECODER

TC9450F

RF AMP. & APC

TA2119FN

SPINDLE DRIVER

BA6849FP

ACTURATOR

DRIVER

SERVO SWITCHER

SUB CODE QCH

20MHz

CERAMIC

OSC

SPINDLE KICK/BRAKE

SLED DRIVER

LOAD/EJECT

DRIVER

KA3012D

CPU

KS88C4400

SUB CODE

DATA

DATA

CONTROL

CD-ROM DECODER

LAYERED ERROR

CORRECTION

SUB CODE DECODER

DATA CONTROL

TC9466FA

PROM

AT27C512R

CONTROLLER SECTION

MAIN PCB

DRIVE SECTION

AUDIO SECTION

DIGITAL

OUT

(OPTION)

AUDIO

OUTPUT

MASTER/

SLAVE

HOST

CONTROLLER

5/12V POWER

4PIN CNPIN CONNECTOR4PIN CN

HEADPHONE

AMPLIFIER

3414A

11 12

Page 2

1424

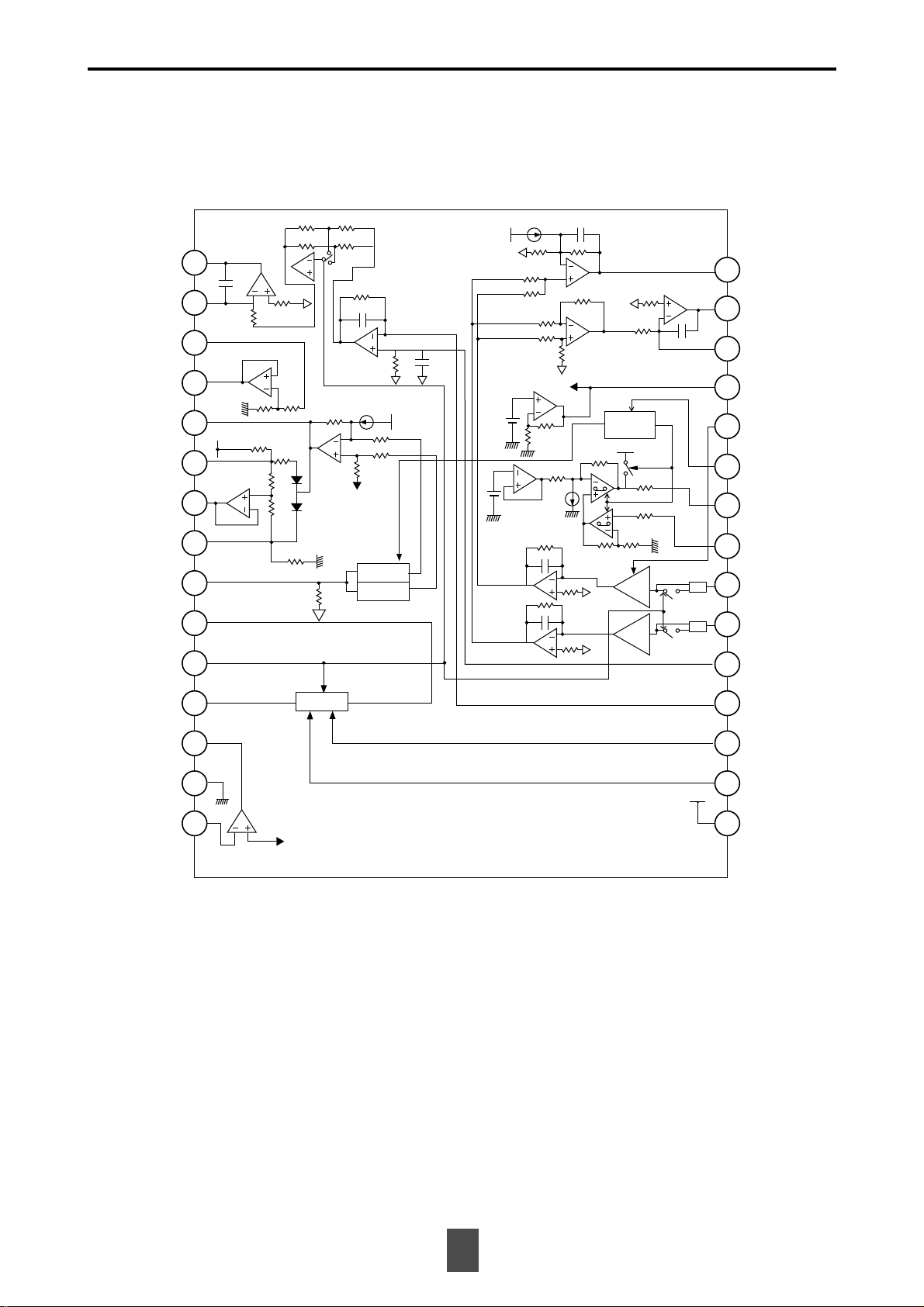

n Main Components Block Diagram and Pin Descriptions

• KS88C4400 MICROCONTROLLER

P0.2/A1080P0.3/A1179P0.4/A1278P0.5/A1377P0.6/A1476P0.7/A15

75

VDD1(int.)

74

P1.0/AD073P1.1/AD172P1.2/AD271P1.3/AD370P1.4/AD469P1.5/AD568P1.6/AD667P1.7/AD7

66EA65

1

P0.1/A9

2

P0.0/A8

3

P5.7

4

P5.6

5

P5.5

6

P5.4

7

P5.3

8

P5.2

9

P5.1

10

P5.0

11

V

DD2(ext.)

12

P2.7/TB

13

P2.6/TA

14

PM

15

DR

16

P2.3/DM

17

P2.2/DW

18

P2.1/DS

19

P2.0/AS

20

PxD

21

TxD

22

PWM1

23

PWM0

24

P3.0/TCCK/INT0

252627282930313233343536373839

40

P3.1/TDCK/INT1

P3.2/TCG/INT2

P3.3/TDG/INT3

P3.4

P3.5

P3.6/CAP

P3.7/WAIT

VSS2(ext.)

P4.0/INT4

P4.1/INT5

P4.2/INT6

P4.3/INT7

P4.4/INT8

P4.5/INT9

P4.6/INT10

P4.7/INT11

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

RESET

NC

NC

V

SS1(int.)

X

OUT

XIN

P6.0

P6.1

P6.2

P6.3

P6.4

P6.5

P6.6

P6.7

P7.7/ADC7

P7.6/ADC6

P7.5/ADC5

P7.4/ADC4

P7.3/ADC3

AV

SS

P7.2/ADC2

P7.1/ADC1

AV

REF

P7.0/ADC0

KS88C4400

80-QFP

(TOP VIEW)

EXTERNAL ADDRESS/DATA BUS

P0.0-P0.7

(A8-A15)

P1.0-P1.7

(AD0-AD7) P2.0-P2.7

PORT A PORT AD PORT C

(AS, DS, DW, DM, DR, PM)

SAM8 BUS

RESET

EA

P2.6

P2.7

X

IN

XOUT

PORT2

MAIN

OSC

TA

TB

TCCK

TDCK

TCG

TDG

TIMERS

A and B

TIMERS

C and D

SERIAL

PORT

RxD

TxD

AV

SS

AVREF

A/D

CONVERTER

ADC0/P7.0-

ADC7/P7.7

SAM8 BUS

V

DD1(INTERNAL)

VSS1(INTERNAL)

VDD2(EXTERNAL)

VSS2(EXTERNAL)

PWM/

CAPTURE

MODULE

PWM0 PWM1

CAPTURE

(P3.6)

P6.0-P6.7

1040-BYTE

REGISTER FILE

16-KB ROM

SAM8 CPU

PORT I/O & INTERRUPT

CONTROL

PORT 3

PORT 4

PORT 5

PORT 6

P5.4-P5.7

P5.0-P5.3

P4.0-P4.7

P3.0-P3.7

4 4 4 4

4

4

Page 3

25

MICOM PIN DESCRIPTIONS

PIN NAME FUNCTION PIN NAME FUNCTION

1 A9 ADDRESS LINE 41 TEST_P1 PRODUCTION TEST PIN 0

2 A8 ADDRESS LINE 42 AVref CVCC

3 /XCE MICOM INTERFACE CHIP ENABLE 43 TEST_P2 PRODUCTION TEST PIN 1

4 /XCM MICOM INTERFACE FIRST WORD ENABLE 44 TEST_P3 PRODUCTION TEST PIN2

5 /XRD MICOM INTERFACE READ SIGNAL 45 Avss GROUND

6 /XWR MICOM INTERFACE WRITE SIGNAL 46 NC NO CONNECTION

7 BUS3 MICOM INTERFACE DATA INPUT/OUTPUT SIGNAL 47 FVO NOT USE

8 BUS2 MICOM INTERFACE DATA INPUT/OUTPUT SIGNAL 48 UBL UNBALLACE DISC CHECK

9 BUS1 MICOM INTERFACE DATA INPUT/OUTPUT SIGNAL 49 /EJECT EJECT KEY INPUT

10 BUS0 MICOM INTERFACE DATA INPUT/OUTPUT SIGNAL 50 /PLAY PLAY KEY INPUT

11 VDD2 VCC 51 NC NO CONNECTION

12 NC NO CONNECTION 52 NC NO CONNECTION

13 NC NO CONNECTION CVCC 53 NC NO CONNECTION

14 /CE FLASH CHIP ENABLE 54 NC NO CONNECTION

15 /URO TC 9466 IC READ 55 XRST DSP RESET

16 /UCS TC 9466 IC CHIP SELECT 56 LED_BUSY BUSY LED

17 /UWR TC 9466 IC WRITE 57 EMPHA EMPHASIS CONTROL

18 NC NO CONNECTION 58 NC NO CONNECTION

19 CLK TC 9466 IC INTERRUPT 59 XIN RESONATOR CLOCK IN

20 NC NO CONNECTION 60 XOUT RESONATOR CLOCK OUT

21 NC NO CONNECTION 61 Vss1 GROUND

22 NC NO CONNECTION 62 NC NO CONNECTION

23 NC NO CONNECTION 63 NC NO CONNECTION

24 FLAGA TRACK ZERO CROSS CHECK 64 RESET MICOM RESET

25 FLAGC FOCUS OK CHECK 65 VCC VCC

26 GFS NOT USE 66 A7 ADDRESS LINE AND DATA PORT

27 SPM_DIR SPINDLE KICK/BRAKE 67 A6 ADDRESS LINE AND DATA PORT

28 NC NO CONNECTION 68 A5 ADDRESS LINE AND DATA PORT

29 DRV_MUTE KA3012 MUTE 69 A4 ADDRESS LINE AND DATA PORT

30 FG SPINDLE FG INPUT 70 A3 ADDRESS LINE AND DATA PORT

31 SPM_DIR SPM-DIR 71 A2 ADDRESS LINE AND DATA PORT

32 VSS GROUND 72 A1 ADDRESS LINE AND DATA PORT

33 NC NO CONNECTION 73 A0 ADDRESS LINE AND DATA PORT

34 D_INT ROM DECODER INTERRUPT 74 VDD VCC

35 CLOSE TRAY CLOSE SIGNAL 75 A15 ADDRESS LINE

36 OPEN TRAY OPEN SIGNAL 76 A14 ADDRESS LINE

37 NC NO CONNECTION 77 A13 ADDRESS LINE

38 MON SPINDLE MOTOR ON/OFF 78 A12 ADDRESS LINE

39 NC NO CONNECTION 79 A11 ADDRESS LINE

40 SCOR SUB CODE SYNC INTERRUPT 80 A10 ADDRESS LINE

Page 4

1626

• TC9466F QFP PIN DIAGRAM

TOP VIEW

SBSY

SFSY

SBDI

CLCK

SBOK

C2PI

LRCK

DAI

BCKI

VSS

XI

XO

VDD

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

VSS

MA0

MA1

MA2

ASCK

ADA

DASP

VSS

HCS3

HCS1

HA2

HA0

PDIAG

HA1

VSS

IOCS16

INTRQ

HDAK

CSEL

VSS

IORDY

HRD

HWR

HDRQ

VSS

HD15

HD0

HD14

HD1

ACK

ALRCK

VSS

VDD

TEST3

TEST2

TB14

TB13

TB12

TB11

TB10

TB9

VPB

TB8

TB7

TB6

TB5

TB4

TB3

TB2

TBST1

TBST0

VSS

VDD

VDD

MA3

MA4

MA5

MRD

MWR

MCE

MINT

CKSTP

RST

VDD

HD7

HD8

HD6

HD9

VSS

HD5

HD10

HD4

HD11

VSS

HD3

HD12

HD2

HD13

VSS

75 74 73 72 71 70 696867 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51

123 456789101112131415161718192021222324 25

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

4

4

32

16

8

16

16

16

8

16

32

8

8

8

6

3

8

13417

3

32

2

16

2

5

8

16 3 2 9

Buffer

DRAM 1Mbit

CD-Mecha

BCKI,LRCK

DAI,C2PI

SBDI,SBOK

SBSY,SFSY

CLCK

ACK

ABCK,ALRCK

ADA

Audio

ASYC

CD-IF

EDC

Da

C2P

HEDda

HSYC

BSYC

SUB-IF

SBDa

SBQDa

BD[15:0]

BWU,BWL

BOE

RAS,CAS

BA[8:0]

Buffer Address

ECC

M-FIFO

(8B)

H-FIFO

(32B)

DRIVER

H Interrupt

M Interrupt

(H-IF)

(M-IF)

Address

Clock

MICOM

CSEL

PDIAG,

DASP

IORDY

HDRQ

HDAK

IOCS16

HD[15:0]

HRD,HWR

HC33,HCS1

HA[2:0]

INTRQ

CKSTP

RST

GND

VDD

TEST[3:0]

TB[14:2]

MD[7:0]

MA[5:0]

MINT

MWR,MRD

MCE

DAC

XI XO

• TC9466F FUNCTIONAL BLOCK DIAGRAM

Page 5

27

NO SYMBOL DESCRIPTIONS NO SYMBOL DESCRIPTIONS

1 MA3 MICOM ADDRESS INPUT 51 VDD POWER SOURCE TERMINAL

2 MA4 MICOM ADDRESS INPUT 52 VDD POWER SOURCE TERMINAL

3 MA5 MICOM ADDRESS INPUT 53 VSS GROUND TERMINAL

4 MRD MICOM READ SIGNAL INPUT 54 TEST0 TEST TERMINAL

5 MWR MICOM WRITE SIGNAL INPUT 55 TEST1 TEST TERMINAL

6 MCE CHIP ENABLE SIGNAL INPUT 56 TB2 TEST TERMINAL

7 KINT INTERRUPT REQUEST OUTPUT 57 TB3 TEST TERMINAL

8 CKSTP CLOCK PARTIAL STOP INPUT 58 TB4 TEST TERMINAL

9 RST RESET TERMINAL 59 TB5 TEST TERMINAL

10 VDD POWER SOURCE TERMINAL 60 TB6 TEST TERMINAL

11 HD7 HOST DATA INPUT 61 TB7 TEST TERMINAL

12 HD8 HOST DATA INPUT 62 TB8 TEST TERMINAL

13 HD6 HOST DATA INPUT 63 VPB GROUND TERMINAL (DRAM AREA)

14 HD9 HOST DATA INPUT 64 TB9 TEST TERMINAL

15 VSS GROUND TERMINAL 65 TB10 TEST TERMINAL

16 HD5 HOST DATA INPUT 66 TB11 TEST TERMINAL

17 HD10 HOST DATA INPUT 67 TB12 TEST TERMINAL

18 HD4 HOST DATA INPUT 68 TB13 TEST TERMINAL

19 HD11 HOST DATA INPUT 69 TB14 TEST TERMINAL

20 VSS GROUND TERMINAL 70 TEST2 TEST TERMINAL

21 HD3 HOST DATA INPUT 71 TEST3 TEST TERMINAL

22 HD12 HOST DATA INPUT 72 VDD POWER SOURCE TERMINAL

23 HD2 HOST DATA INPUT 73 VSS GROUND TERMINAL

24 HD13 HOST DATA INPUT 74 ALRCK LRCK OUTPUT FOR DAC ON FAST PLAY

25 VSS GROUND TERMINAL 75 ACK BASE CLOCK INPUT ON FAST PLAY

26 HD1 HOST DATA INPUT 76 SBSY SUBCODE BLOCK SYNC OUTPUT

27 HD14 HOST DATA INPUT 77 SFSY SUBCODE DATA SYNC FRAME INPUT

28 HD0 HOST DATA INPUT 78 SBDI SUBCODE DATA INPUT

29 HD15 HOST DATA INPUT 79 CLCK SUBCODE DATA CLOCK OUTPUT

30 VSS GROUND TERMINAL 80 SBOK SUBCODE Q DATA FLAG INPUT

31 HDRQ DATA REQUEST TERMINAL 81 C2PI DATA CORRECTION FLAG INPUT

32 HWR HOST WRITE SIGNAL INPUT 82 LRCK CHANNEL CLOCK INPUT

33 HRD HOST READ SIGNAL INPUT 83 DAI DATA SIGNAL INPUT

34 IORDY IO TRANSFER READY OUTPUT 84 BCKI BIT CLOCK INPUT

35 VSS GROUND TERMINAL 85 VSS GROUND TERMINAL

36 CSEL CABLE SELECT INPUT 86 XI MASTER CLOCK I/O

37 HDAK DATA ACKNOWLEDGE INPUT 87 XO MASTER CLOCK I/O

38 INTRQ INTERRUPT SIGNAL OUTPUT 88 VDD POWER SOURCE TERMINAL

39 IOCS16 DATA BIT WIDE SELECT OUTPUT 89 MD0 MICOM DATA I/O

40 VSS GROUND TERMINAL 90 MD1 MICOM DATA I/O

41 HA1 HOST ADDRESS 1 INPUT 91 MD2 MICOM DATA I/O

42 PDIAG POST DIAGNOSTIC I/O 92 MD3 MICOM DATA I/O

43 HA0 HOST ADDRESS 0 INPUT 93 MD4 MICOM DATA I/O

44 HA2 HOST ADDRESS 2 INPUT 94 MD5 MICOM DATA I/O

45 HCS1 CHIP SELECT 1 INPUT 95 MD6 MICOM DATA I/O

46 HCS3 CHIP SELECT 3 INPUT 96 MD7 MICOM DATA I/O

47 VSS GROUND TERMINAL 97 VSS GROUND TERMINAL

48 DASP DRIVE ACTIVE OUTPUT 98 MA0 MICOM ADDRESS INPUT

49 ADA DATA OUTPUT FOR DAC ON FAST PLAY 99 MA1 MICOM ADDRESS INPUT

50 ABCK BCK OUTPUT FOR DAC ON FAST PLAY 100 MA2 MICOM ADDRESS INPUT

PIN DESCRIPTIONS

Page 6

18

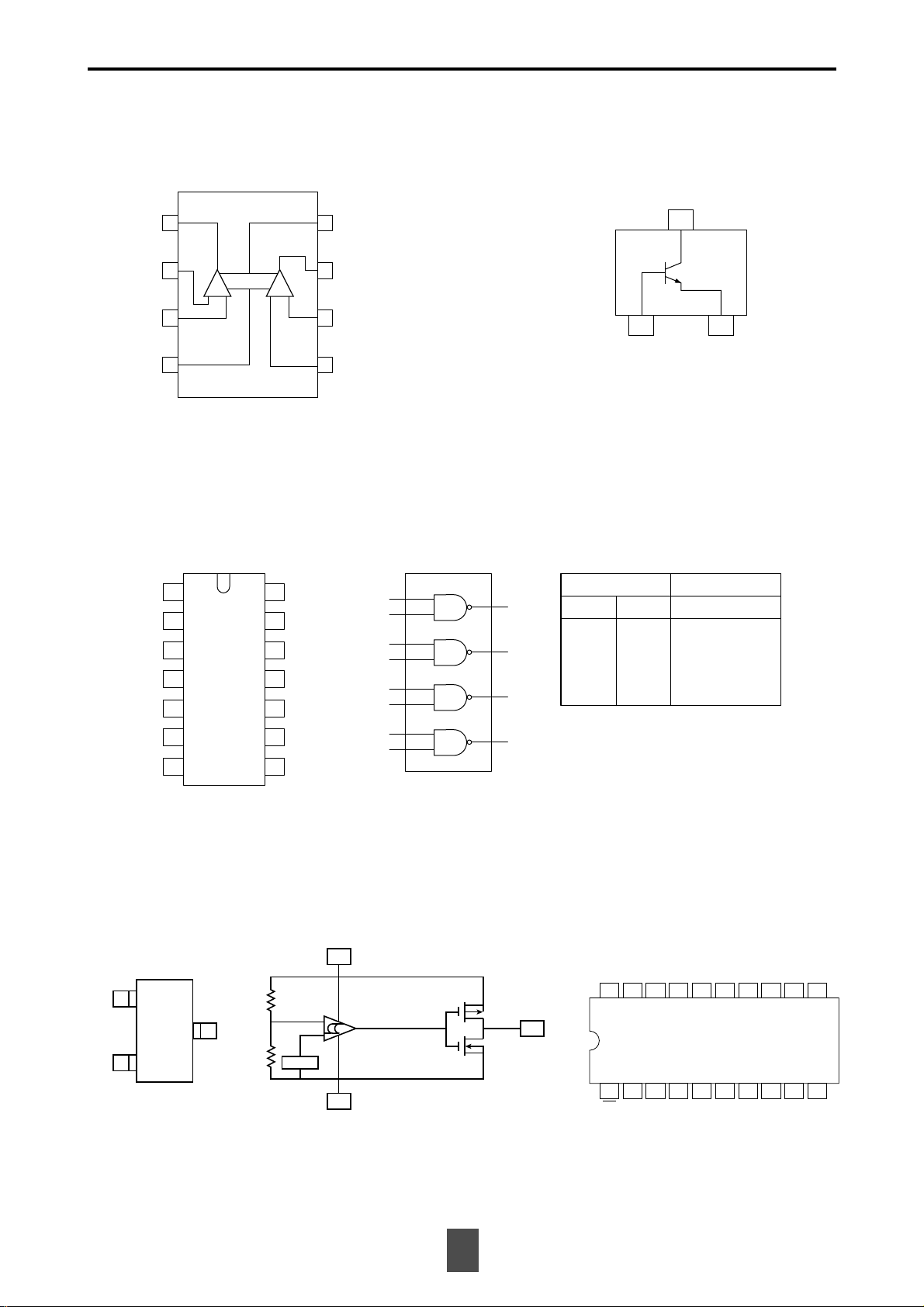

• TC9450F (DSP CHIP)

+

–

+

–

+

–

+

–

+

–

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

1

2

AUDIO

OUT

VSS3

BCK

AOUT

DOUT

MBOV

IPF

SBOK

CLOCK

VDD3

VSS5

DATA

SFSY

SBSY

SPCK

SPDA

COFS

MONIT

VDD5

TESTIO0

AWRC

PVDD3

PDOS

PDO

TMAX

TMAXS

XVDD3

XO

XI

XVSS3

TEST2

TEST1

TEST0

TESIN

TESTIO1

FGIN

DACT

CKSE

DMOUT

IO3

IO2

IO1

IO0

VSS3

VDD3

FLGD

FLGC

FLGB

FLGA

SEL

VDD3

DIGITAL

OUT

SUBCODE

OUT

16K RAM

ROM RAM

DIGITAL

EQUALIZER

SERVO

CONTROL

DECODER

ERROR

CORECTION

MICOM

INTERFACE

CLOCK

GENERATOR

CAV

ADRESS

STATUS

LPF

DA COUNTER

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

9998979695949392919089888786858483828180797877

76

100

30292827263132333435363738394041424344454647484950

+

–

DA PWMCONVERTOR

DATA

SLICER

CLV

ACTIVE

WIDERANGE

PLL

TMAX

VCO

DVSS3

RO

DVDD3

DVR

LO

DVSS3

TEST3

TEST4

BUS0

BUS1

BUS2

BUS3

VDD5

VSS5

XRD

XWR

XCM

XCE

TEST5

RST

HSO

UHSO

SHSO

EMPH

LRCK

VSS3

DMO

FVO

FMO

TEBC

RFGC

VREF

TRO

FOO

TEZI

TEI

SBAD

FEI

RFRP

RFZI

RFCT

AVDD3

RFI

SLCO

AVSS3

VCOF

VCOREF

PVREF

LPFO

LPFN

28

Page 7

29

PIN PIN DESCRIPTIONS PIN PIN DESCRIPTIONS

NO NAME NO NAME

1 VSS3 DIGITAL GND TERMINAL 51 VDD3 DIGITAL +3.3V POWER SOURCE TERMINAL

2 BCK BIT CLOCK OUTPUT TERMINAL (1.411MHz) 52 SEL AUTO POWER CONTROL ON/OFF SIGNAL OUTPUT TERMINAL

3 AOUT AUDIO DATA OUTPUT TERMINAL 53 FLGA INTERNAL SIGNAL CHECKING FLAG TERMINAL

4 DOUT DIGITAL DATA OUTPUT TERMINAL 54 FLGB INTERNAL SIGNAL CHECKING FLAG TERMINAL

5 MBOV BUFFER MEMORY OVER SIGNAL OUTPUT TERMINAL 55 FLGC INTERNAL SIGNAL CHECKING FLAG TERMINAL

6 IPF COMPLEMENTARY BLOCK OUTPUT TERMINAL 56 FLGD INTERNAL SIGNAL CHECKING FLAG TERMINAL

7 SBOK CRCC RESULT OUTPUT TERMINAL FOR SUBCODE Q DATA 57 VDD3 DIGITAL +3.3V POWER TERMINAL

8 CLCK SUBCODE P-W DATA READ CLOCK TERMINAL 58 VSS3 DIGITAL GND

9 VDD3 DIGITAL +3.3V POWER TERMINAL 59 I00 GENERAL I/O TERMINAL

10 VSS5 DIGITAL GND TERMINAL 60 I01 GENERAL I/O TERMINAL

11 DATA SUBCODE P-W OUTPUT TERMINAL 61 I02 GENERAL I/O TERMINAL

12 SFSY PLAY DEVICE FRAME SYNC SIGNAL OUTPUT TERMINAL 62 I03 GENERAL I/O TERMINAL

13 SBSY SUBCODE BLOCKING OUTPUT TERMINAL 63 /DMOUT 100~1 OUTPUT MODE SELECT TERMINAL

14 SPCK DSP INTERNAL STATUS CHECKING CLOCK TERMINAL 64 /CKSE OSCILLATING DEVICE SELECT TERMINAL

15 SPDA DSP STATUS OUTPUT TERMINAL 65 /DACT DIGITAL/ANALOG CONVERT TEST TERMINAL

16 COFS ERROR CORRECTION CLOCK (7.35 MHz)OUTPUT TERMINAL 66 FGIN DIGITAL/ANALOG CONVERT TEST TERMINAL

17 MONIT DSP INTERNAL STATUS OUTPUT TERMINAL 67 TESI01 TEST INPUT TERMINAL

18 VDD5 DIGITAL +5V TERMINAL 68 TESIN TEST INPUT TERMINAL

19 TESTOO TEST TERMINAL 69 TEST0 TEST TERMINAL

20 AWRC VCO OUTPUT TERMINAL FOR ACTIVE-WIDE RANGE PLL 70 TEST1 TEST TERMINAL

21 PVDD3 +3.3V POWER TERMINAL FOR PLL-EXCLUSIVELY 71 TEST2 TEST TERMINAL

22 PDOS POSITION GAP SIGNAL OUTPUT TERMINAL OF EFM & PLCK SIGNALS 72 XVSS3 MICOM CLOCK DRIVING CIRCUIT GND TERMINAL

23 PDO POSITION GAP SIGNAL OUTPUT TERMINAL OF EFM & PLCK SIGNALS 73 XI MICOM CLOCK DRIVING CIRCUIT INPUT TERMINAL

24 TMAXS TMAX DETECTION RESULT OUTPUT TERMINAL 74 XO MICOM CLOCK DRIVING CIRCUIT OUTPUT TERMINAL

25 TMAX TMAX DETECTION RESULT OUTPUT TERMINAL 75 XVDD3 MICOM CLOCK DRIVING CIRCUIT +3.3V POWER TERMINAL

26 LPFN AMP REVERSE INPUT TERMINAL FOR LOW-PASS FILTER 76 DVSS3 D/A CONVERT R CHANNEL ANALOG GND TERMINAL

27 LPFO AMP OUTPUT TERMINAL FOR LOW-PASS FILTER 77 RO R CHANNEL AUDIO OUTPUT TERMINAL

28 PVREF VREF(+1.65V) FOR PLL ONLY 78 DVDD3 DIGITAL/ANALOG CONVERT +3.3V POWER TERMINAL

29 VCOREF VCO CENTER FREQUENCY BASE LEVEL VOLTAGE TERMINAL 79 DVR DIGITAL/ANALOG CONVERT BASE VOLTAGE TERMINAL

30 VCOF VCO FILTER TERMINAL 80 LO L CHANNEL AUDIO OUTPUT TERMINAL

31 AVSS3 ANALOG GNDTERMINAL 81 DVSS3 D/A CONVERT L CHANNEL ANALOG GND TERMINAL

32 SLCO DATA SLICE GENERATING DIGITAL/ANALOG CONVERT OUTPUT TERMINAL 82 TEST3 TEST TERMINAL

33 RFI RF SIGNAL INPUT TERMINAL 83 TEST4 TEST TERMINAL

34 AVDD3 ANALOG +3.3V POWER TERMINAL 84 BUS0 DATA INPUT TERMINAL FOR MICOM INTERFACE

35 RFCT RERP SIGNAL INTERMEDIATE VOLAGE 85 BUS1 DATA INPUT TERMINAL FOR MICOM INTERFACE

36 RFZI INPUT TERMINAL FOR RERO ZERO CROSS 86 BUS2 DATA INPUT TERMINAL FOR MICOM INTERFACE

37 RFRP RF RIPPLE SIGNAL INPUT TERMINAL 87 BUS3 DATA INPUT TERMINAL FOR MICOM INTERFACE

38 FEI FOCUS ERRORSIGNAL INPUT TERMINAL 88 VDD5 DIGITAL 5V POWER SOURCE TERMINAL

39 SBAD SUBBEAM ADDITION SIGNAL INPUT 89 VSS5 DIGITAL GNDTERMINAL

40 TEI TRACKING ERROR SIGNAL INPUT 90 /XRD READ SIGNAL FOR MICOM INTERFACE

41 TEZI TRACKING ERROR ZERO CROSS INPUT 91 /XWR WRITE SIGNAL FOR MICOM INTERFACE

42 FDO FOCUS EQ. OUTPUT TERMINAL 92 /XCM FIRST WORD RECOGNIZE SIGNAL FOR MICOM INTERFACE

43 TRO TRACKING EQ. OUTPUT TERMINAL 93 /XCE MICOM INTERFACE CHIP ENABLE TERMINAL

44 VREF ANALOG-BASED POWER(+1.65V) 94 TEST5 TEST MODE SELECT TERMINAL

45 RFGC RF AMPLITUDE CONTROL SIGNAL OUTPUT TERMINAL 95 /RST RESET INPUT TERMINAL

46 TEBC TRACKING BALANCE CONTROL SIGNAL OUTPUT TERMINAL 96 /HSO PLAY SPEED MODE FLAG OUTPUT TERMINAL

47 FMO FEED EQ. OUTPUT TERMINAL 97 /UHSO PLAY SPEED MODE FLAG OUTPUT TERMINAL

48 FVO SPEED ERROR OR FEED EQ OUTPUT TERMINAL 98 /SHSO PLAY SPEED MODE FLAG OUTPUT TERMINAL

49 DMO DISK MOTOR EQ OUTPUT TERMINAL 99 EMPH EMPHASIS FLAG OUTPUT TERMINAL OF SUBCODE QDATA

50 VSS3 DIGITAL GND TERMINAL 100 LRCK CHANNEL CLOCK (44.1KHz) OUTPUT TERMINAL

PIN DESCRIPTIONS

Page 8

2030

FEO

16

FEN

17

VDDIN

18

VREF

19

RFRP

20

BTC

21

RFCT

22

PKC

23

RERPIN

24

RFGO

25

GVSW

26

AGCIN

27

RFO

28

GND

29

RFN2

30

SBAD

15

TEO

14

TEN

13

VRO

12

TEB

11

SEL

10

LDO

9

MDI

8

TNI

7

TPI

6

FPI

5

FNI

4

GMAD

3

RFGC

2

VCC

1

BOTTOM

PEAK

AGC-AMP

20k

11k

11k

100k

100k

100k

20k

20k

50µA

20k 20k

36k

150k

60k 60k

20k100k

150k

15k

10k

20µA 36p

50k

15k

10k

30k

16.7k

20k

48k

2.9k

83k

SW1

LDC

SW2

SW3

1k

1.4k

2.26k

I(1/4)

I(3/4)

I(3/4)

I(1/4)

10k

238k

238k

15k

15p

24k

3 STATE

DET

10p

30k

10k

10p

60k

40p

40p

12k

12k

I - I

I - I

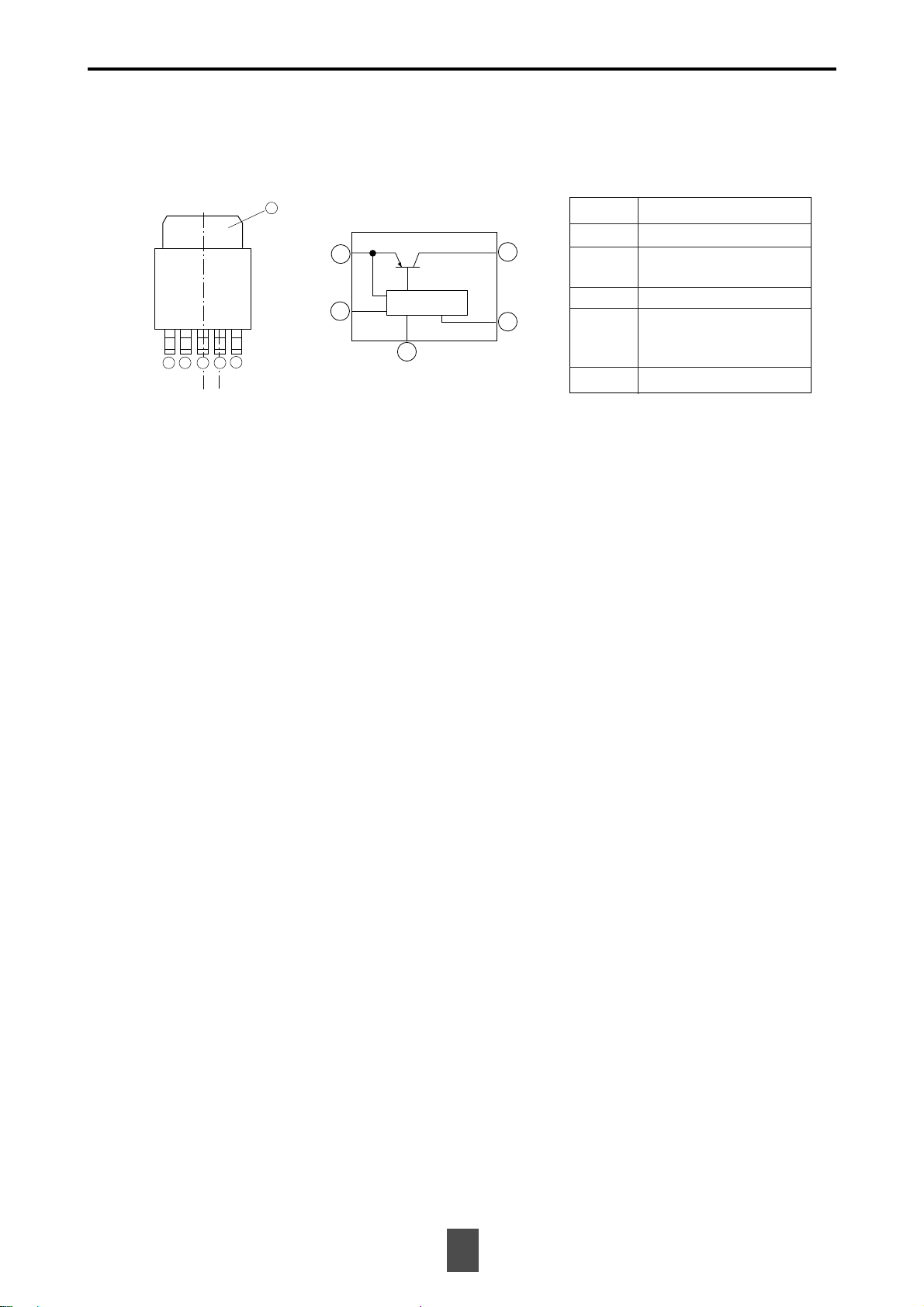

• TA2119FN

Page 9

31

PIN NO PIN NAME FUNCTION

1 VCC POWER SOURCE/VOLTAGE TERMINAL

2 RFGC RF FREQUENCY CONTROL SIGNAL INPUT TERMINAL

3 GMAD OPEN-LOOP GAIN CONTROL TERMINAL OF AGC AMP

4 FNI MAIN BEAM AMP INPUT TERMINAL

5 FPI MAIN BEAM AMP INPUT TERMINAL

6 TPI SUB BEAM AMP INPUT TERMINAL

7 TNI SUB BEAM AMP INPUT TERMINAL

8 MDI MONITOR PHOTO-DIODE AMP INPUT TERMINAL

9 LDO LASER DIODE AMP OUTPUT TERMINAL

10 SEL INTERNAL GAIN AND SIGNAL SWITCH TERMINAL

11 TEB TRACKING BALANCE CONTROL SIGNAL INPUT TERMINAL

12 VRO STANDARD VOLTAGE RATING TERMINAL(VRO,2.1V)

13 TEN TRACKING ERROR SIGNAL GENERATING AMP REVERSE INPUT TERMINAL

14 TEO TRACKING ERROR SIGNAL GENERATING AMP OUTPUT TERMINAL

15 SBAD SUB BEAM ADDITIONAL OUTPUT TERMINAL

16 FEO FOCUS ERROR SIGNAL GENERATING AMP OUTPUT TERMINAL

17 FEN FOCUS ERROR SIGNAL GENERATING AMP REVERSE INPUT TERMINAL

18 VDD 3.3V POWER SOURCE VOLTAGE TERMINAL

19 VREF VOLTAGE RATING (VREF,1.6V) OUTPUT TERMINAL

20 RFRP SIGNAL GENERATING AMP OUTPUT TERMINAL FOR TRACK COUNTER

21 BTC RECT SIGNAL GENERATING BOTTOM DETECTOR CONTROL TERMINAL

22 RFCT RFRP SIGNAL CENTER LEVEL OUTPUT TERMINAL

23 PKC RFCT SIGNAL GENERATING PEAK DETECTOR CONTROL TERMINAL

24 RFRPIN SIGNAL GENERATING AMP INPUT TERMINAL FOR TRACK COUNTER

25 RFGO RF SIGNAL AMPLITUDE ADJUSTING AMP INPUT TERMINAL

26 GVSW AGC,TE, FE AMP GAIN SWITCH TERMINAL

27 AGCIN RF SIGNAL AMPLITUDE ADJUSTING AMP INPUT TERMINAL

28 RFO RF SIGNAL GENERATING AMP OUTPUT TERMINAL

29 GND GND TERMINAL

30 RFN2 RF SIGNAL GENERATING AMP INPUT TERMINAL

PIN DESCRIPTIONS

Page 10

22

PIN DESCRIPTIONS

PIN DESCRIPTIONS

28 27 26 25 24 23 22 21 20 19 18 17 16

1 3 4 5 6 7 21 20 19 18 17 16 15

GND

LEVEL-SHIFT

LEVEL-SHIFT

10K

TSD

PV

CC1 PVCC2

PVCC1/2

PV

CC1/2

PV

CC1/2

PV

CC2/2 PVCC2/2

PV

CC2/2 PVCC2/2

SV

CC

GND

MUTE

PV

CC1/2

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

10

LEVEL-SHIFT

LEVEL-SHIFT

15

2

A3

A2

A1

GND

H1+

H1-

H2+

H2-

H3+

H3-

2

4

6

8

9

10

11

12

13

14

Hall 3

Hall 2

Hall 1

HALL AMP

+

+

+

+

+

FIN

Hall Bias

SHORT BRAKE

VH

CNF

SB

FR

ECR

EC

PS

FG

V

CC

VCC

VM2

VM1

V

M

RNF

RNF

28

27

26

25

24

23

22

21

20

18

17

15

V

CC

TORQUE

SENSE AMP

PS

V

CC

CURRENT

SENSE AMP

GAIN

CONTROL

TSD

DRIVER

TL

SERVO

SIGNAL

R

D

Q

Q

CK

+

+

PIN NO. PIN NAME

FUNCTION

1 N.C. N.C

2 A3 Output3 for motor

3 N.C. N.C

4 A2 Output3 for motor

5 N.C. N.C

6 N.C. N.C

7 A1 Output3 for motor

8 GND GND

9 H1+ Hall input Amp1.positive input

10 H1- Hall input Amp1.negative input

11 H2+ Hall input Amp2.positive input

12 H2- Hall input Amp2.negative input

13 H3+ Hall input Amp3.positive input

14 H3- Hall input Amp3.negative input

15 VH Hall Bias

16 N.C. N.C

17 CNF Capacitor connection pin for phase compensation

18 SB Short Brake terminal

19 N.C. N.C

20 FR Rotation detect terminal

21 ECR Torque control standsrd voltage input terminal

22 EC Torque control voltage input terminal

23 PS START/STOP switch

24 FG FG signal output terminal

25 VCC Power supply for signal division

26 VM2 Power supply2 for driver

27 VM1 Power supply1 for driver

28 RNF Power supply for driver division

FIN FIN GND

Pin No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

Symbol

CH1-O

CH1-O

AMP1-O

AMP1-I(-)

AMP1-I(+)

BIAS

SVCC

GND

MUTE

AMP2-1(+)

AMP2-1(-)

AMP2-O

CH2-O

CH2-O

GND

CH3-O

CH3-O

AMP3-O

AMP3-I(-)

AMP3-I(+)

PVCC2

PVCC1

AMP4-I(+)

AMP4-I(-)

AMP4-O

CH4-O

CH4-O

GND

I/O

O

O

O

I

I

I

-

I

I

I

O

O

O

O

O

O

I

I

-

-

I

I

O

O

O

-

Description

Drive CH1 Output(-)

Drive CH1 Output(+)

OP-AMP CH1 Output

OP-AMP CH1 Input(-)

OP-AMP CH1 Input(+)

Bias Input

Supply Voltage(Signal)

Ground

Mute

OP-AMP CH2 Input(+)

OP-AMP CH2 Input(-)

OP-AMP CH2 Output

Drive CH2 Output(+)

Drive CH2 Output(-)

Ground

Drive CH3 Output(-)

Drive CH3 Output(+)

OP-AMP CH3 Output

OP-AMP CH3 Input(-)

OP-AMP CH3 Input(+)

Supply Voltage(CH2&CH3)

Supply Voltage(CH1&CH4)

OP-AMP CH4 Input(+)

OP-AMP CH4 Input(-)

OP-AMP CH4 Output

Drive CH4 Output(+)

Drive CH4 Output(-)

Ground

• KA3012D

• BA6849FP

32

Page 11

2333

• DAP 202K

1 2

3

• 2SB 1132 (KTA 1664)

-TOP VIEW-

123

A12 NC A14

3 1 31

15 17 19

A7 A15 VCC A13

O2 NC O4

O1 GND O3 O5

4 2 32 30

14 16 18 20

5

6

7

8

9

10

11

12

13

29

A6

A5

A4

A3

A2

A1

A0

NC

O0

A8

A9

A11

NC

OE/VPP

A10

CE

O7

O6

28

27

26

25

24

23

22

21

PLCC Top View

Pin Name Function

A0-A15 Addresses

O0-O7 Outputs

CE Chip Enable

OE/Vpp Output Enable/Vpp

NC No Connect

• AT27PC512

• TC4S66F

OE, CE AND

PROGRAM LOGIC

OUTPUT

BUFFERS

DATA OUTPUTS

O0-O7

Y-GATING

CELL MATRIX

IDENTIFICATION

Y DECODER

X DECODER

A0-A15

ADDRESS

INPUTS

CE

OE/VPP

GND

Vcc

Mode/Pin CE OE/V

PP

Ai Outputs

Read V

IL

V

IL

Ai D

OUT

Output Disable V

IL

V

IH

X

(1)

High Z

Standby V

IH

X

(1)

X High Z

Pid Program

(2)

V

IL

V

PP

Ai D

IN

GM Inhibit V

IH

V

PP

X

(1)

High Z

Duct Identification

(4)

V

IL

V

IL

A9=V

H

(3)

IdentificationCode

A0=VIHor V

IL

A1-A15=V

IL

IN/OUT

1 5

4

OUT/IN

2

V

SS

V

CONT

DD

3

V

IN/OUT

DD

OUT/IN

V

CONTROL

SS

Page 12

2434

• GD74VHCT00

• XC61AC3502MR

• MC74LS374DW

20

Vcc19O

7

18

D

7

17

D

6

16

O

6

15

D

5

14

O

5

13

D

4

12

O

4

11

CP

1 2 3 4 5 6 7 8 9 10

OE O

0 D0 D1 O1 D2 O2 D3 O3 GND

1A1B1

2

1Y 3

2A2B4

5

2Y 5

3A3B9

10

3Y 8

4A4B12

13

4Y 11

11A

21B

31Y

42A

52B

62Y

7GND

14

13

12

11

10

9

8

Vcc

4B

4A

4Y

3B

3A

3Y

08

INPUTS OUTPUT

nA

L

L

H

H

nB

L

H

L

H

nY

H

H

H

L

H=HIGH voltage level

L=Low voltage level

VOUT

VIN

VSS

Vref

1

V

OUT

3

V

IN

2

V

SS

-TOP VIEW-

• KSC 1623 (2SC 2412K)

B E

C

• NJM3414M

A+INPUT 3

A OUTPUT 1

A-INPUT 2

4

6

8

7

5

B+INPUT

B OUTPUT

B-INPUT

GND

B B

V1(5V)

Page 13

25

35

• PQ20VZ51

20VZ51

1 2 334

5

1

2

3

4

5

Spesific IC

• Pin configuration

Pin No Pin Name

• DC input(VIN)

‚ ON/OFF control

terminal(VC)

ƒ DC output(VO)

„ Output voltage minute

adjustment

terminal(VADJ)

… GND

Loading...

Loading...