Samsung S6C0666 Datasheet

6 BIT 384 CHANNEL RSDS TFT–LCD SOURCE DRIVER PREMILINARY VER 1.0 S6C0666

S6C0666

6 BIT 384 CHANNEL RSDS TFT-LCD SOURCE DRIVER

August. 1999.

Prepared by: Akira Kang

akira211@samsung.co.kr

Ver. 0.0

1

S6C0666 PREMILINARY VER 1.0 6 BIT 384 CHANNEL RSDS TFT–LCD SOURCE DRIVER

S6C0666 Specification Revision History

Version Content Date

0.0 Original Aug.1999

2

6 BIT 384 CHANNEL RSDS TFT–LCD SOURCE DRIVER PREMILINARY VER 1.0 S6C0666

CONTENTS

INTRODUCTION .................................................................................................................................................4

FEATURES.........................................................................................................................................................4

BLOCK DIAGRAM..............................................................................................................................................5

PIN ASSINGMENTS............................................................................................................................................ 6

PIN DESCRIPTIONS...........................................................................................................................................7

OPERATION DESCRIPTION...............................................................................................................................8

RSDS RECEIVER AND DEMUX ......................................................................................................................8

RSDS DATA BUS INTERFACE CONTROL......................................................................................................8

DISPLAY DATA TRANSFER............................................................................................................................8

EXTENSION OF OUTPUT ...............................................................................................................................8

RELATIONSHIP BETWEEN INPUT DATA VALUE AND OUTPUT VOLTAGE..................................................8

ABSOLUTE MAXIMUM RATINGS ....................................................................................................................15

RECOMMENDED OPERATION CONDITIONS.................................................................................................. 15

DC CHARACTERISTICS ................................................................................................................................... 16

RSDS CHARACTERISTICS.............................................................................................................................. 17

AC CHARACTERISTICS ................................................................................................................................... 18

WAVEFORMS...................................................................................................................................................19

RSDS DATA TIMING DIAGRAM.......................................................................................................................20

3

S6C0666 PREMILINARY VER 1.0 6 BIT 384 CHANNEL RSDS TFT–LCD SOURCE DRIVER

INTRODUCTION

The S6C0666 is a Source Driver suitable for Reduced Swing Differential Signaling (RSDS) digital interface. It

converts 18-bit digital data into the analog voltage for 384 channels, charging each sub-pixel to the correct gray

level corresponding to the digital value.

The RSDS path to the panel timing controller contributes toward lowering radiated EMI, reducing system power

consumption and eliminates one of the two pixel busses used in typical XGA, SXGA TFT LCD panels. This single

9-bit differential bus conveys the 18-bit color data for XGA, SXGA panels.

FEATURES

• TFT active matrix LCD source driver LSI

• 64 G/S is possible through 10 (5 by 2) external power supply and D/A converter

• Both dot inversion display and N-line inversion display are possible

• Compatible with gamma-correction

• Logic supply voltage: 2.7 to 3.6 V

• LCD driver supply voltage: 7.0 to 10.5 V

• Output dynamic range: 6.8 to 10.3 Vp-p

• Maximum operating frequency: fmax = 65 MHz (internal data transmission rate at 2.7 V operation)

• Output: 384 outputs

• Reduced Swing Differential Signaling (RSDS) digital interface for low power consumption and low EMI.

• Minimum RSDS input swing level (CLKN, CLKP, DATAN, DATAP): 100mV

• Data bus interface control pin (DATPOL)

• TCP or COF available

4

6 BIT 384 CHANNEL RSDS TFT–LCD SOURCE DRIVER PREMILINARY VER 1.0 S6C0666

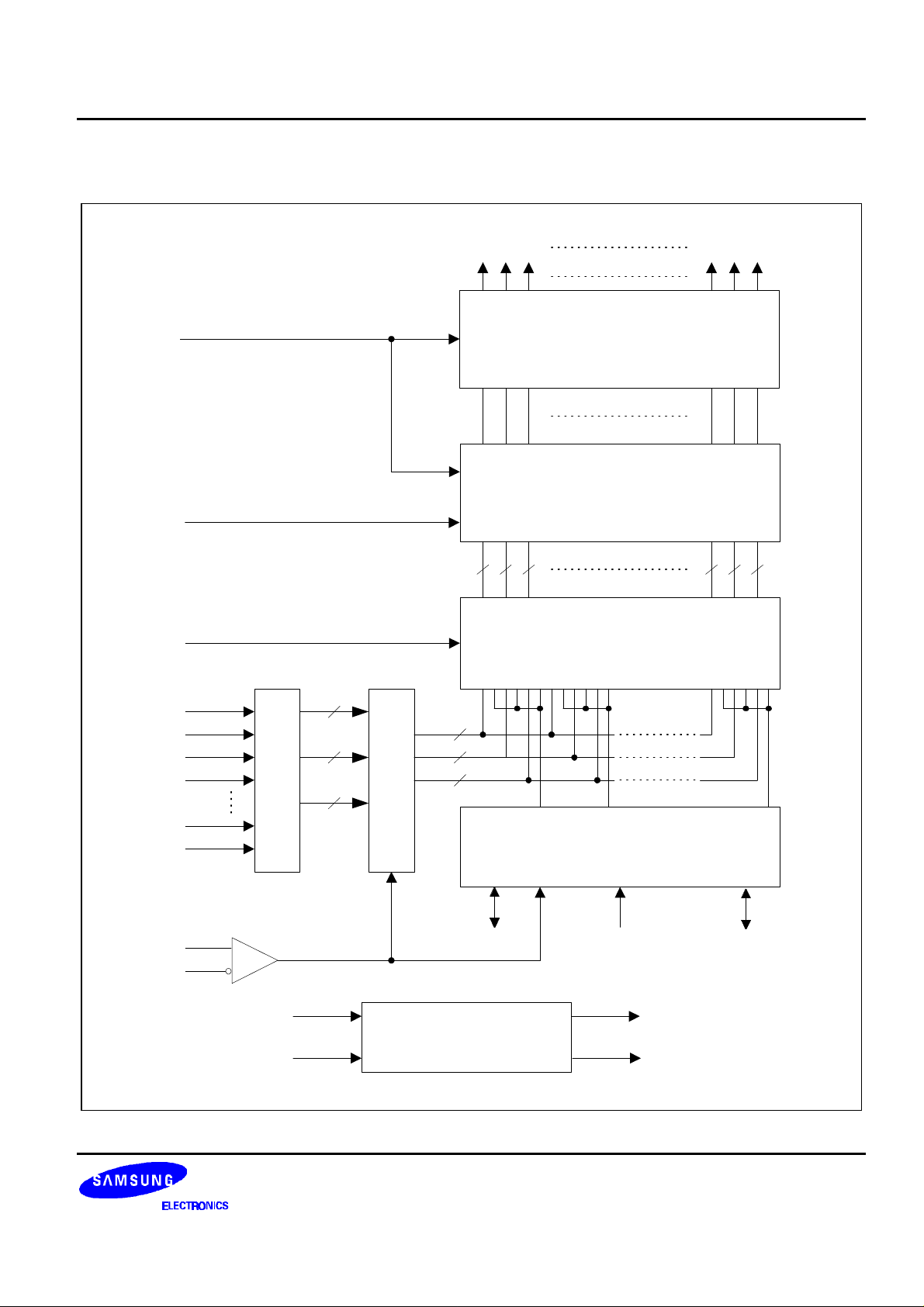

BLOCK DIAGRAM

POL

VGMA1 to VGMA10

CLK1

D00P

D00N

D01P

D01N

D22P

D22N

6

6

6

RSDS Receiver

Data Register

6

6

6

Y1Y2Y3

Output Buffer

R-DAC

Data Latches

128 bit Shift Register

6 6 66 66

Y382

Y383

Y384

CLKP

CLKN

RPI1

RPI2

DIO1

Line Repair AMP

Figure 1. S6C0666 Block Diagram

SHL

DIO2

RPO1

RPO2

5

S6C0666 PREMILINARY VER 1.0 6 BIT 384 CHANNEL RSDS TFT–LCD SOURCE DRIVER

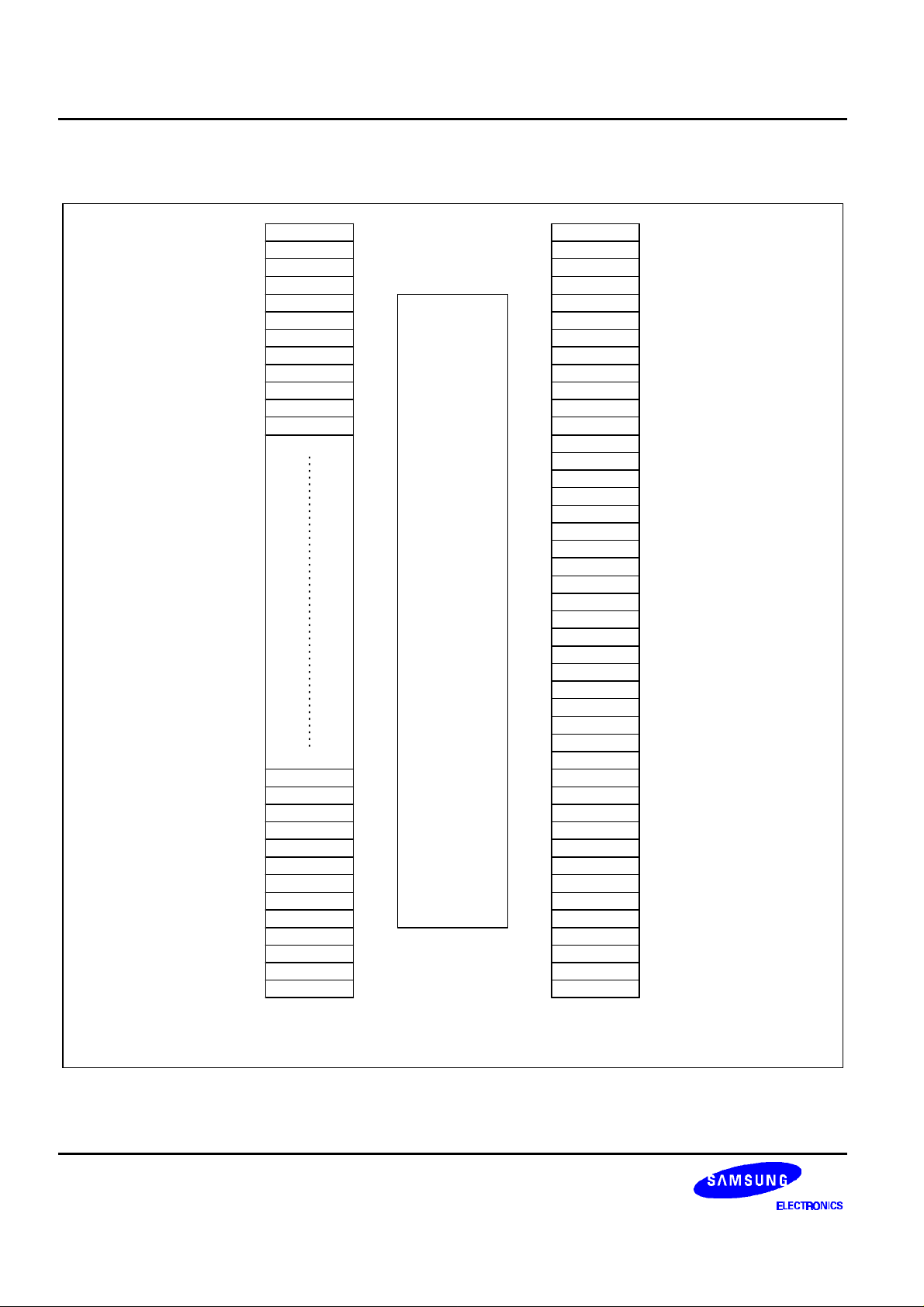

PIN ASSINGMENTS

Y1

Y2

Y3

Y4

Y5

Y6

Y7

Y8

Y9

Y10

Y11

Y12

Y372

Y373

Y374

Y375

Y376

Y377

Y378

Y379

Y380

Y381

Y382

Y383

Y384

S6C0666

RPI1

RPO1

DIO1

D00N

D00P

D01N

D01P

D02N

D02P

DATPOL

POL

CLK1

CLKN

CLKP

VSS1

VGMA1

VGMA2

VGMA3

VGMA4

VGMA5

VSS2

VDD2

VGMA6

VGMA7

VGMA8

VGMA9

VGMA10

SHL

VDD1

D10N

D10P

D11N

D11P

D12N

D12P

D20N

D20P

D21N

D21P

D22N

D22P

DIO2

RPO2

RPI2

Output 384 Input 44

Figure 2. S6C0666 Pin Assignments

6

Loading...

Loading...