Samsung S6B0794 Datasheet

`

written permission of LCD Driver IC Team.

S6B0794

160 SEG / COM DRIVER FOR STN LCD

Contents in this document are subject to change without notice. No part of this document may be reproduced

or transmitted in any form or by any means, electronic or mechanical, for any purpose, without the express

July, 2000

Ver. 3.0

Prepared by: Gyeong-Nam, Kim

kgn@samsung.co.kr

160 SEG / COM DRIVER FOR STN LCD SPEC. VER. 3.0 S6B0794

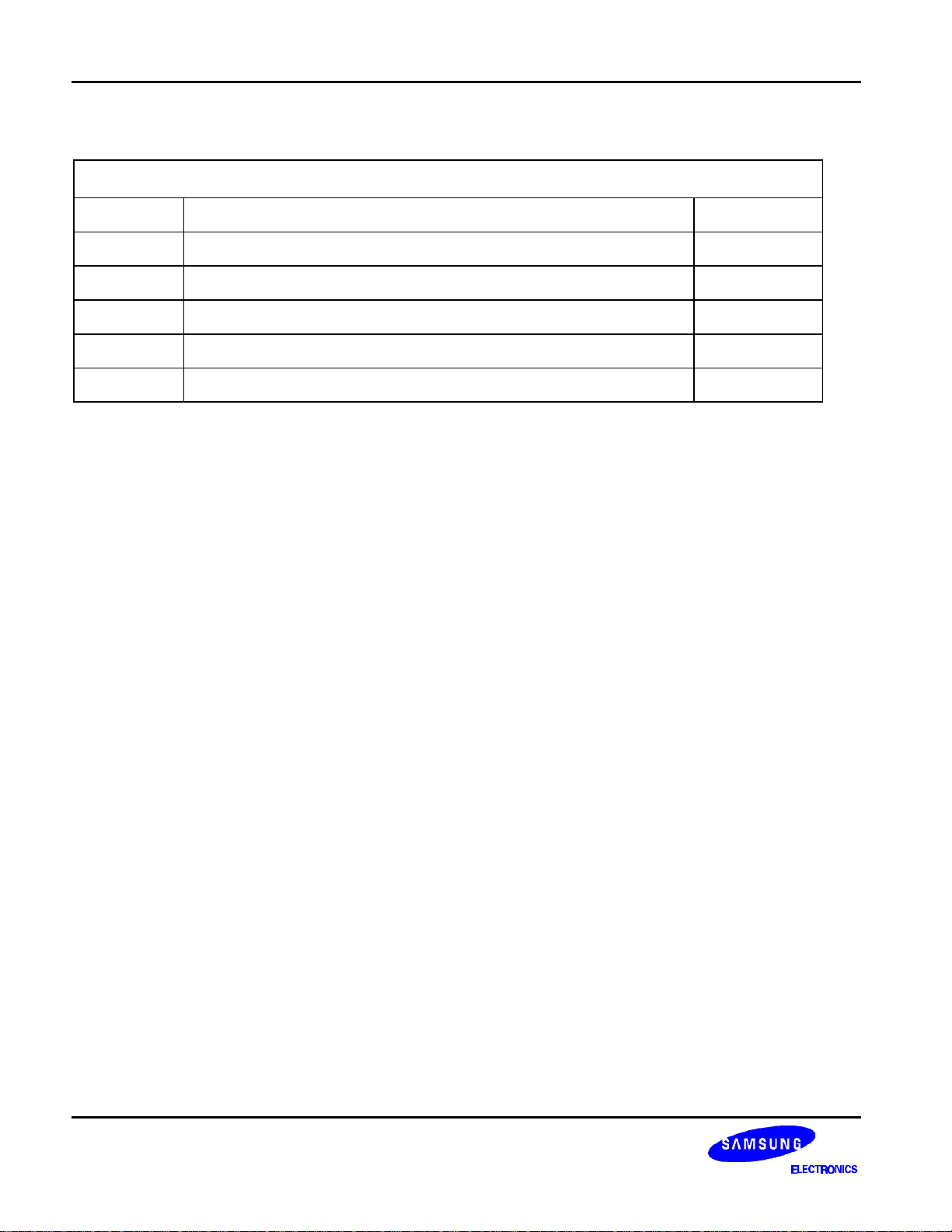

S6B0794 Specification Revision History

Version Content Date

0.0 l Original 1999. 4.15

1.0 l Including application note. 1999. 7.05

1.1 l p6, p16 revision. 1999. 8.17

2.0 l p4 Introduction revision. 2000.01.31

3.0 l p6,p8 dummy pad addition. 2000.07.21

2

S6B0794 SPEC. VER 3.0 160 SEG / COM DRIVER FOR STN LCD

CONTENTS

INTRODUCTION ..................................................................................................................................................4

FEATURES..........................................................................................................................................................4

BLOCK DIAGRAM...............................................................................................................................................5

PAD CONFIGURATION .......................................................................................................................................6

PAD CENTER COORDINATES ............................................................................................................................7

PIN DESCRIPTION ..............................................................................................................................................9

FUNCTIONAL DESCRIPTION............................................................................................................................ 10

BLOCK FUNCTION.....................................................................................................................................10

PIN FUNCTION...........................................................................................................................................11

FUNCTIONAL OPERATIONS......................................................................................................................15

SPECIFICATIONS..............................................................................................................................................18

ABSOLUTE MAXIMUM RATINGS...............................................................................................................18

RECOMMENDED OPERATING CONDITIONS ...........................................................................................18

DC CHARACTERISTICS.............................................................................................................................19

AC CHARACTERISTICS.............................................................................................................................21

PRECAUTION.................................................................................................................................................... 27

CONNECTION EXAMPLES OF PLURAL SEGMENT DRIVERS........................................................................28

TIMING CHART OF 4-DEVICE CASECADE CONNECTION OF SEGMENT DRIVERS......................................29

CONNECTION EXAMPLES OF PLURAL COMMON DRIVERS.........................................................................30

3

160 SEG / COM DRIVER FOR STN LCD SPEC. VER. 3.0 S6B0794

INTRODUCTION

The S6B0794 is a 160-outputs segment/common driver LSI for graphic dot-matrix liquid

crystal display systems. It is fabricated by low power CMOS high voltage process technology.

This device consists of 160-bits bi-directional shift register, 160-bits data latch and 160-bits

driver. In case of segment mode, the data input is selected 4bit parallel input mode and 8bit

parallel input mode by a mode (MD) pin. In case of common mode, data input/output pins are

bi-directional, four data shift directions are pin-selectable.

FEATURES

Both Segment Mode and Common Mode

- Supply voltage for LC driver: +15.0 to +32.0V

- Number of LC driver outputs: 160

- Low output impedance

- Low power consumption

- Supply voltage for the logic system: +2.4V to +5.5V

- CMOS silicon gate process (P-type Silicon Substrate)

- Package: 190-pin TCP (Tape Carrier Package) & Gold bumped chip

Segment Mode

- Shift clock frequency: 14MHz (Max) (Vdd=+5V±10%)

8MHz (Max) (Vdd=+2.4V to +4.5V)

- Adopts a data bus system

- 4-bit / 8-bit parallel input modes are selectable with a mode (MD) pin

- Automatic transfer function of an enable signal

- Automatic counting function which, in the chip select, causes the internal clock to be stopped

by automatically counting 160 of input data

- Line latch circuit reset function when DISPOFFB active

Common Mode

- Shift clock frequency: 4.0MHz (Max) (vdd=+2.4V to +5.5V)

- Built-in 160 bits bi-directional shift register (divisible into 80-bits ×2)

- Available in a single mode (160-bits shift register) or in a dual mode(80-bits shift register ×2)

- Shift register circuit reset function when DISPOFFB active

4

S6B0794 SPEC. VER 3.0 160 SEG / COM DRIVER FOR STN LCD

BLOCK DIAGRAM

FR

DISPOFFB

EIO1

EIO2

LP

XCK

L/R

MD

182

179

181

169

180

178

166

183

VOR V12R

190 189 188 164

V43R V5L

LEVEL

SHIFTER

ACTIVE

CONTROL

CONTROL

LOGIC

8

8BITS*2

DATA

LATCH

Y160Y159Y1 Y2

1 2 160159

160 BITS 4-LEVEL DRIVER

160

160 BITS LEVEL SHIFTER

160

160 BITS LINE LATCH/SHIFTER

REGISTER

16 16

16

16 16

16

16 16

16

DATA LATCH CONTROL

16

187

163

162

161

V5L

V43L

V12L

VOL

S/C

168

SP CONVERSION & DATA CONTROL

(4 to 8 or 8to 8)

170 171 172 173 174 175 176 177 165 186167

D I0 D I1 D

I

2 D I3 DI4 DI5 DI6 DI7

Figure 1. Block Diagram

VDD

VSS VSS

5

160 SEG / COM DRIVER FOR STN LCD SPEC. VER. 3.0 S6B0794

1

160

ð ð ð ð ð ð ð ð ð ð ð ð ð ð ð ð ð ð

ð

ð

ð

ð

ð

ð

ð

ð

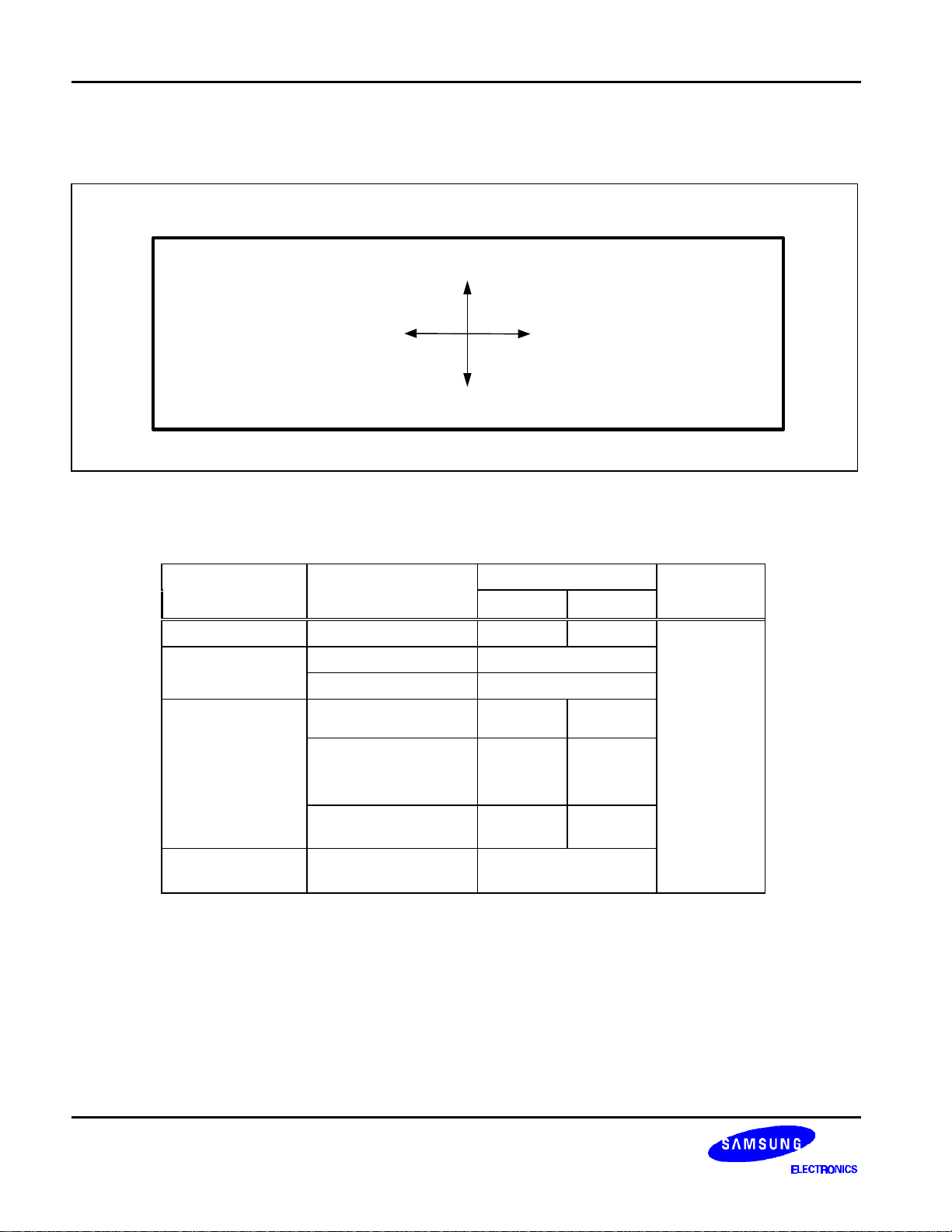

PAD CONFIGURATION

161

ррррррррррррррррррррр

- - - - - - - - - -

Y

рррррррррррррррррррр

S6B0794

(TOP VIEW, Pads Up)

(0,0)

X

ð ð ð ð ð ð ð ð ð ð ð ð ð ð

Figure 2. S6B0794 Chip Configuration

Table 1. S6B0794 Pad Dimensions

ITEM PAD NO.

CHIP SIZE - 11000 1100

1 to 160 65 (MIN)

PAD PITCH

161 to 190 260 (MIN)

1 to 160

SIZE

X Y

43 108

190

186 DummyDummy 165

187164

UNIT

161 to 164

BUMPED

PAD SIZE

BUMPED

PAD HEIGHT

6

187 to 190

165 to 186 58 76

1 to 190 14 (Typ)

76 58

µm

S6B0794 SPEC. VER 3.0 160 SEG / COM DRIVER FOR STN LCD

50

Y50

1982.5

395

100

Y100

-1267.5

395

150

Y150

-4517.5

395

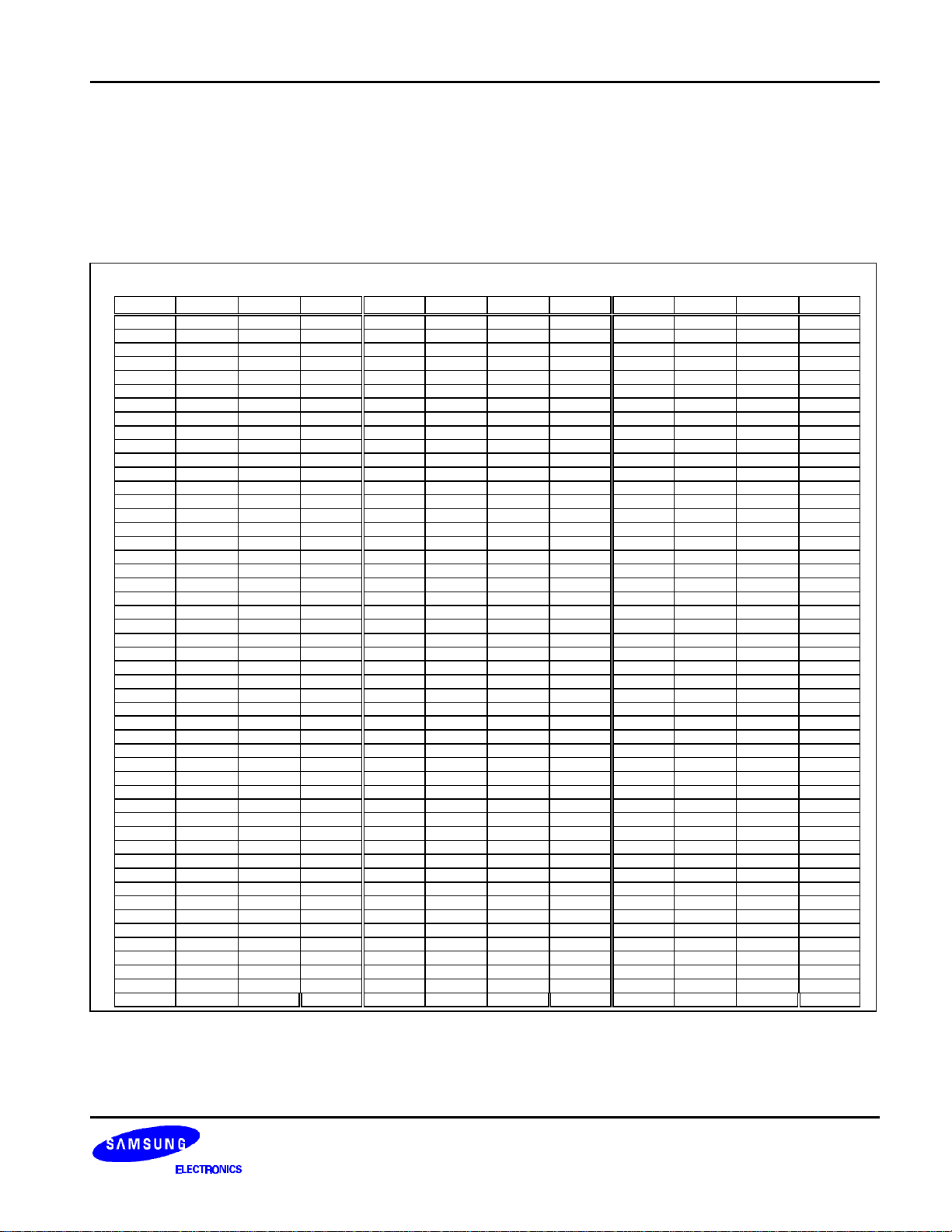

PAD CENTER COORDINATES

Table 2. Pad Location

[Unit: µm]

NO NAME X Y NO NAME X Y NO NAME X Y

1 Y1 5167.5 395 51 Y51 1917.5 395 101 Y101 -1332.5 395

2 Y2 5102.5 395 52 Y52 1852.5 395 102 Y102 -1397.5 395

3 Y3 5037.5 395 53 Y53 1787.5 395 103 Y103 -1462.5 395

4 Y4 4972.5 395 54 Y54 1722.5 395 104 Y104 -1527.5 395

5 Y5 4907.5 395 55 Y55 1657.5 395 105 Y105 -1592.5 395

6 Y6 4842.5 395 56 Y56 1592.5 395 106 Y106 -1657.5 395

7 Y7 4777.5 395 57 Y57 1527.5 395 107 Y107 -1722.5 395

8 Y8 4712.5 395 58 Y58 1462.5 395 108 Y108 -1787.5 395

9 Y9 4647.5 395 59 Y59 1397.5 395 109 Y109 -1852.5 395

10 Y10 4582.5 395 60 Y60 1332.5 395 110 Y110 -1917.5 395

11 Y11 4517.5 395 61 Y61 1267.5 395 111 Y111 -1982.5 395

12 Y12 4452.5 395 62 Y62 1202.5 395 112 Y112 -2047.5 395

13 Y13 4387.5 395 63 Y63 1137.5 395 113 Y113 -2112.5 395

14 Y14 4322.5 395 64 Y64 1072.5 395 114 Y114 -2177.5 395

15 Y15 4257.5 395 65 Y65 1007.5 395 115 Y115 -2242.5 395

16 Y16 4192.5 395 66 Y66 942.5 395 116 Y116 -2307.5 395

17 Y17 4127.5 395 67 Y67 877.5 395 117 Y117 -2372.5 395

18 Y18 4062.5 395 68 Y68 812.5 395 118 Y118 -2437.5 395

19 Y19 3997.5 395 69 Y69 747.5 395 119 Y119 -2502.5 395

20 Y20 3932.5 395 70 Y70 682.5 395 120 Y120 -2567.5 395

21 Y21 3867.5 395 71 Y71 617.5 395 121 Y121 -2632.5 395

22 Y22 3802.5 395 72 Y72 552.5 395 122 Y122 -2697.5 395

23 Y23 3737.5 395 73 Y73 487.5 395 123 Y123 -2762.5 395

24 Y24 3672.5 395 74 Y74 422.5 395 124 Y124 -2827.5 395

25 Y25 3607.5 395 75 Y75 357.5 395 125 Y125 -2892.5 395

26 Y26 3542.5 395 76 Y76 292.5 395 126 Y126 -2957.5 395

27 Y27 3477.5 395 77 Y77 227.5 395 127 Y127 -3022.5 395

28 Y28 3412.5 395 78 Y78 162.5 395 128 Y128 -3087.5 395

29 Y29 3347.5 395 79 Y79 97.5 395 129 Y129 -3152.5 395

30 Y30 3282.5 395 80 Y80 32.5 395 130 Y130 -3217.5 395

31 Y31 3217.5 395 81 Y81 -32.5 395 131 Y131 -3282.5 395

32 Y32 3152.5 395 82 Y82 -97.5 395 132 Y132 -3347.5 395

33 Y33 3087.5 395 83 Y83 -162.5 395 133 Y133 -3412.5 395

34 Y34 3022.5 395 84 Y84 -227.5 395 134 Y134 -3477.5 395

35 Y35 2957.5 395 85 Y85 -292.5 395 135 Y135 -3542.5 395

36 Y36 2892.5 395 86 Y86 -357.5 395 136 Y136 -3607.5 395

37 Y37 2827.5 395 87 Y87 -422.5 395 137 Y137 -3672.5 395

38 Y38 2762.5 395 88 Y88 -487.5 395 138 Y138 -3737.5 395

39 Y39 2697.5 395 89 Y89 -552.5 395 139 Y139 -3802.5 395

40 Y40 2632.5 395 90 Y90 -617.5 395 140 Y140 -3867.5 395

41 Y41 2567.5 395 91 Y91 -682.5 395 141 Y141 -3932.5 395

42 Y42 2502.5 395 92 Y92 -747.5 395 142 Y142 -3997.5 395

43 Y43 2437.5 395 93 Y93 -812.5 395 143 Y143 -4062.5 395

44 Y44 2372.5 395 94 Y94 -877.5 395 144 Y144 -4127.5 395

45 Y45 2307.5 395 95 Y95 -942.5 395 145 Y145 -4192.5 395

46 Y46 2242.5 395 96 Y96 -1007.5 395 146 Y146 -4257.5 395

47 Y47 2177.5 395 97 Y97 -1072.5 395 147 Y147 -4322.5 395

48 Y48 2112.5 395 98 Y98 -1137.5 395 148 Y148 -4387.5 395

49 Y49 2047.5 395 99 Y99 -1202.5 395 149 Y149 -4452.5 395

7

160 SEG / COM DRIVER FOR STN LCD SPEC. VER. 3.0 S6B0794

Table 3. Pad Location(Continued)

[Unit: µm]

NO NAME X Y

151 Y151 -4582.5 395

152 Y152 -4647.5 395

153 Y153 -4712.5 395

154 Y154 -4777.5 395

155 Y155 -4842.5 395

156 Y156 -4907.5 395

157 Y157 -4972.5 395

158 Y158 -5037.5 395

159 Y159 -5102.5 395

160 Y160 -5167.5 395

161 VOL -5369 330

162 V12L -5369 90

163 V43L -5369 -120

164 V5L -5369 -330

DUMMY1 -4860 -419

165 VSS -4600 -419

166 LR -4340 -419

167 VDD -4080 -419

168 SC -3820 -419

169 EIO2 -3560 -419

170 DI0 -3300 -419

171 DI1 -3040 -419

172 DI2 -2780 -419

173 DI3 -2520 -419

174 DI4 -2260 -419

175 DI5 -2000 -419

176 DI6 -1740 -419

177 DI7 -1480 -419

DUMMY -1380 -419

DUMMY -1280 -419

DUMMY -1180 -419

DUMMY -1080 -419

DUMMY 1990 -419

DUMMY 2090 -419

DUMMY 2190 -419

178 XCK 2290 -419

179 DISPOFFB 2550 -419

180 LP 2810 -419

181 EIO1 3070 -419

182 FR 3330 -419

183 MD 3590 -419

184 NC 3850 -419

185 NC 4110 -419

186 VSS 4370 -419

DUMMY2 4630 -419

DUMMY 5070 -419

187 V5R 5369 -330

188 V43R 5369 -120

189 V12R 5369 90

190 V0R 5369 330

8

S6B0794 SPEC. VER 3.0 160 SEG / COM DRIVER FOR STN LCD

PIN DESCRIPTION

Table 3. Pin Description

Pin No. Symbol I/O Description

1 to 160

161, 190

162, 189

163, 188

164, 187

166

167

168

169

170 to

176

177

178

179

180

181

182

Y1 – Y160 O LC driver output

V0L, V0R - Power supply for LC driver

V12L, V12R - Power supply for LC driver

V43L, V43R - Power supply for LC driver

V5L, V5R - Power supply for LC driver

L/R I Display data shift direction selection

VDD - Power supply for logic system(+2.4 to +5.5V)

S/C I Segment mode/common mode selection

EIO2 I/O Input/output for chip select or data of shift register

DI0 – DI6 I Display data input for segment mode

DI7 I Display data input for segment mode/Dual mode data input

XCK I Display data shift clock input for segment mode

DISPOFFB I Control input for deselect output level

LP I Latch pulse input/shift clock input for shift register

EIO1 I/O Input/output for chip select or data of shift register

FR I AC-converting signal input for LC driver waveform

183

165, 186

MD I Mode selection input

VSS - Ground(0V)

9

160 SEG / COM DRIVER FOR STN LCD SPEC. VER. 3.0 S6B0794

FUNCTIONAL DESCRIPTION

BLOCK FUNCTION

. Active Control

In case of segment mode, controls the selection or deselection of the chip. Following a LP

signal, and after the chip select signal is input, a select signal is generated internally until 160

bits of data have been read in. Once data input has been completed, a select signal for

cascade connection is output, and the chip is deselected. In case of common mode, controls

the input/output data of bidirectional pins.

. SP Conversion and Data Control

In case of segment mode, keep input data which are 2 clocks of XCK at 4-bit parallel mode into

latch circuit, or keep input data which are 1 clock of XCK at 8-bits parallel mode into latch

circuit, after that they are put on the internal data bus 8 bits at a time.

. Data Latch Control

In case of segment mode, selects the state of the data latch which reads in the data bus

signals. The shift direction is controlled by the control logic, for every 16 bits of data read in, the

selection signal shifts one bit based on the state of the control circuit.

. Data Latch

In case of segment mode, latches the data on the data bus. The latched state of each LC

driver output pin is controlled by the control logic and the data latch control, 160 bits of data are

read in 20 sets of 8 bits.

. Line Latch / Shift Register

In case of segment mode, all 160 bits which have been read into the data latch are

simultaneously latched on the falling edge of the LP signal, and output to the level shifter block.

In case of common mode, shifts data from the data input pin on the falling edge of the LP

signal.

. Level Shifter

The logic voltage signal is level-shifted to the LC driver voltage level, and output to the driver

block.

. 4-level Driver

Driver the LC driver output pins from the line latch/shift register data, selecting one of 4

levels(V0, V12, V43, V5) based on the S/C, FR and DISPOFFB signals.

. Control Logic

Controls the operation of each block. In case of segment mode, when a LP signal has been

input, all blocks are reset and the control logic waits for the selection signal output from the

active control block. Once the selection signal has been output, operation of the data latch and

data transmission are controlled, 160 bits of data are read in, and the chip is deselected. In

case of common mode, controls the direction of data shift.

10

Loading...

Loading...