Samsung S6B0108 Datasheet

64 CH SEGMENT DRIVER FOR DOT MATRIX LCD

S6B0108

written permission of LCD Driver IC Team.

June. 2000.

Ver. 0.0

Contents in this document are subject to change without notice. No part of this document may be reproduced

or transmitted in any form or by any means, electronic or mechanical, for any purpose, without the express

S6B0108 64CH SEGMENT DRIVER FOR DOT MATRIX LCD

INTRODUCTION

The S6B0108 is a LCD driver LSI with 64 channel output for dot matrix liquid crystal graphic display systems.

This device consists of the display RAM, 64 bit data latch, 64 bit drivers and decoder logic. It has the internal display RAM for storing the display data transferred from a 8 bit micro controller and generates the dot matrix Iiquid

crystal driving signals corresponding to stored data. The S6B0108 composed of the liquid crystal display system

in combination with the S6B0107 (64 channel common driver).

FEATURES

• Dot matrix LCD segment driver with 64 channel output

• Input and output signal

- Input: 8 bit parallel display data control signal from MPU divided bias voltage

(V0R, V0L, V2R, V2L, V3R, V3L, V5R, V5L)

- Output: 64 channel for LCD driving.

• Display data is stored in display data RAM from MPU.

• Interface RAM

- Capacity: 512 bytes (4096 bits)

- RAM bit data: RAM bit data = 1: On

RAM bit data = 0: Off

• Applicable LCD duty: 1/32-1/64

• LCD driving voltage: 8V-17V (VDD-VEE)

• Power supply voltage: + 5V ± 10%

• Interface

Drivers

Common Segment

S6B0107 Other S6B0108 MPU

• High voltage CMOS process.

• Bare chip available

Controller

2

64CH SEGMENT DRIVER FOR DOT MATRIX LCD S6B0108

S64

S63

S2

S1

BLOCK DIAGRAM

CL

Display

On/Off

Register

1

6

Input

DB<0:7>

8

Output

Register

Busy

Y-Counter

6

Y-Counter

64

8

6

Instruction

Decoder

3

X-Decoder

CLK1

8

CLK2

I/O Buffer

CS1B

CS2B

CS3

R/W

RS

E

RSTB

ADC

FRM

V0L

V2L

V3L

V5L

6

64

Z-Decoder

Display Data RAM

512 × 8 = 4096bits

8

Page Selector

Display Start Line Register

64

Data Latch

64

V0R

LCD Driver

M

V2R

V3R

V5R

3

S6B0108 64CH SEGMENT DRIVER FOR DOT MATRIX LCD

S43

S42

S41

S40

S39

S38

S37

S36

S35

S34

S33

S32

S31

S30

S29

S28

S27

S26

S25

S24

S23

S22

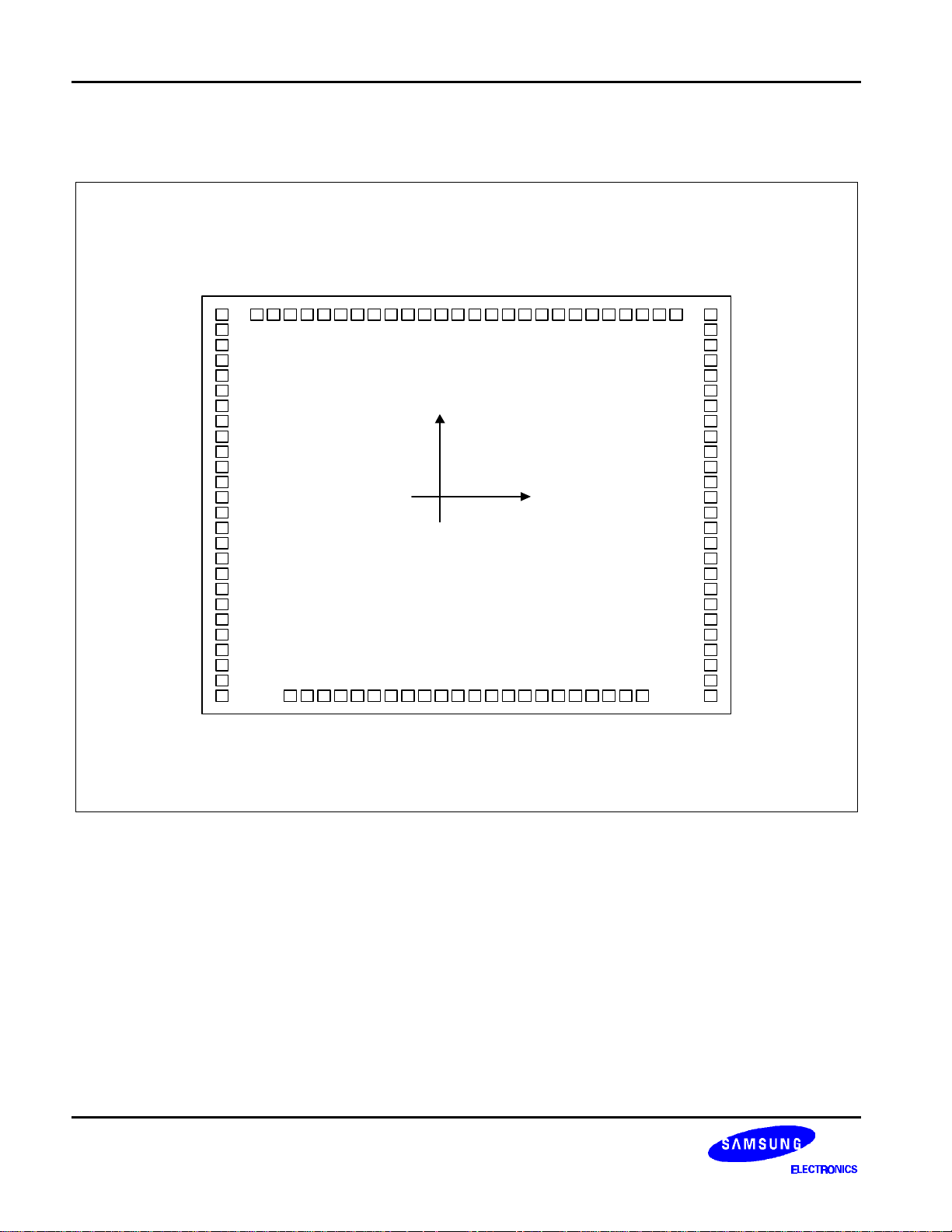

PAD DIAGRAM

V3R

V2R

V5R

V0R

V

S64

S63

S62

S61

S60

S59

S58

S57

S56

S55

S54

S53

S52

S51

S50

S49

S48

S47

S46

S45

S44

EE2

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

VDDMADC

321

4

5

6

7

8

9

FRMECLK1

10099989796959493929190898887868584838281807978

CLK2CLRS

Chip size: 4090

PAD size: 100

Unit : µm

R/W

Y

RSTB

CS1B

CS2B

CS3NCNCNCDB7

(0, 0) X

×

×

4020

100

DB6

DB5

DB4

DB3

DB2

DB1

DB0

VSS

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

V3L

V2L

V5L

V0L

V

EE1

S1

S2

S3

S4

S5

S6

S7

S8

S9

S10

S11

S12

S13

S14

S15

S16

S17

S18

S19

S20

S21

303132333435363738394041424344454647484950

There is mark of S6B0108 on the bottom left in the chip.

4

51

64CH SEGMENT DRIVER FOR DOT MATRIX LCD S6B0108

PAD CENTER COORDINATES

PAD

Number

1 ADC -1140 1845 35 S38 -687 -1845 69 S4 1882 791

2 M -1275 1845 36 S37 -562 -1845 70 S3 1882 916

3 VDD -1410 1845 37 S36 -437 -1845 71 S2 1882 1041

4 V3R -1882 1809 38 S35 -312 -1845 72 S1 1882 1166

5 V2R -1882 1684 39 S34 -187 -1845 73 VEE1 1882 1310

6 V5R -1882 1559 40 S33 -62 -1845 74 V0L 1882 1435

7 V0R -1882 1434 41 S32 62 -1845 75 V5L 1882 1559

8 VEE2 -1882 1309 42 S31 187 -1845 76 V2L 1882 1684

9 S64 -1882 1165 43 S30 312 -1845 77 V3L 1882 1809

10 S63 -1882 1040 44 S29 437 -1845 78 VSS 1412 1845

11 S62 -1882 915 45 S28 562 -1845 79 DB0 1277 1845

12 S61 -1882 790 46 S27 687 -1845 80 DB1 1142 1845

13 S60 -1882 665 47 S26 812 -1845 81 DB2 1007 1845

14 S59 -1882 540 48 S25 937 -1845 82 DB3 882 1845

15 S58 -1882 415 49 S24 1062 -1845 83 DB4 757 1845

16 S57 -1882 290 50 S23 1187 -1845 84 DB5 632 1845

17 S56 -1882 165 51 S22 1487 -1845 85 DB6 507 1845

18 S55 -1882 40 52 S21 1882 -1379 86 DB7 382 1845

19 S54 -1882 -84 53 S20 1882 -1239 87 NC

20 S53 -1882 -209 54 S19 1882 -1099 88 NC

21 S52 -1882 -334 55 S18 1882 -959 89 NC

22 S51 -1882 -459 56 S17 1882 -834 90 CS3 245 1845

23 S50 -1882 -584 57 S16 1882 -709 91 SC2B 120 1845

24 S49 -1882 -709 58 S15 1882 -584 92 SC1B -5 1845

25 S48 -1882 -834 59 S14 1882 -459 93 RSTB -130 1845

26 S47 -1882 -959 60 S13 1882 -334 94 R/W -255 1845

27 S46 -1882 -1099 61 S12 1882 -209 95 RS -380

28 S45 -1882 -1239 62 S11 1882 -84 96 CL -505 1845

29 S44 -1882 -1379 63 S10 1882 41 97 P2 -630 1845

30 S43 -1487 -1845 64 S9 1882 166 98 P1 -755 1845

31 S42 -1187 -1845 65 S8 1882 291 99 E -880 1845

32 S41 -1062 -1845 66 S7 1882 416 100 FRM -1005 1845

33 S40 -937 -1845 67 S6 1882 541

34 S39 -812 -1845 68 S5 1882 666

PAD

Name

Coordinate Coordinate Coordinate

X Y

Pad

Number

Pad

Name

X Y

Pad

Number

Pad

Name

X Y

1845

5

S6B0108 64CH SEGMENT DRIVER FOR DOT MATRIX LCD

PIN DESCRIPTION

Table 1. Pin Description

Pin Number

QFP(TQFP)

Symbol

Input /

Output

Description

For internal logic circuit (+5V ± 10%)

V

V

V

DD

SS

EE1.2

Power

GND (0V)

For LCD driver circuit

VSS = 0V, VDD = +5V ± 10%, VDD-VEE = 8V - 17V

3(1)

78(76)

73(71), 8(6)

VEE1 and VEE2 is connected by the same voltage.

Bias supply voltage terminals to drive the LCD.

74(72), 7(5)

76(74), 5(3)

77(75), 4(2)

75(73), 6(4)

V0L, V0R

V2L, V2R

V3L, V3R

V5L, V5R

Power

Select Level

V0L(R), V5L(R)

Non-Select Level

V2L(R), V3L(R)

V0L and V0R (V2L & V2R, V3L & V3R, V5L & V5R) should be

connected by the same voltage.

92(89)

91(87)

90(86)

CS1B

CS2B

CS3

Input

Chip selection

In order to interface data for input or output, the terminals

have to be CS1B = L, CS2B = L, and CS3 = H.

2(100) M Input Alternating signal input for LCD driving.

Address control signal to determine the relation between Y

address of display RAM and terminals from which the data is

1(99) ADC Input

output.

ADC = H → Y0: S1 - Y63: S64

ADC = L → Y0: S64 - Y63: S1

Synchronous control signal.

100(98) FRM Input

Presets the 6-bit Z counter and synchronizes the common

signal with the frame signal when the frame signal becomes

high.

Enable signal.

Write mode (R/W = L) → data of DB<0:7> is latched at the

99(97) E Input

falling edge of E.

Read mode (R/W = H) → DB<0:7> appears the reading data

while E is at high level.

98(96)

97(95)

CLK1

CLK2

Input

2 phase clock signal for internal operation.

Used to execute operations for input/output of display RAM

data and others.

Display synchronous signal.

96(94) CL Input

Display data is latched at rising time of the CL signal and

increments the Z-address counter at the CL falling time.

Data or Instruction.

95(93) RS Input

RS = H → DB<0:7>: Display RAM data

RS = L → DB<0:7>: Instruction data

6

64CH SEGMENT DRIVER FOR DOT MATRIX LCD S6B0108

Table 1. Pin Description (Continued)

Pin Number

QFP(TQFP)

Symbol

Input /

Output

94(92) R/W Input

79-86

(77-84)

72-9

(70-7)

DB0-DB7 Input/Output

S1-S64 Output

93(91) RSTB Input

Description

Read or Write.

R/W = H → Data appears at DB<0:7> and can be read by the

CPU while E = H, CS1B = L, CS2B = L and

CS3 = H .

R/W = L → Display data DB<0:7> can be written at falling of E

when CS1B = L, CS2B = L and CS3 = H.

Data bus.

Three state I/O common terminal.

LCD segment driver output.

Display RAM data 1: On

Display RAM data 0: Off (relation of display RAM data & M)

M

L

H

Data

L

H

L

H

Output Level

V

2

V

0

V

3

V

5

Reset signal.

When RSTB=L,

- ON / OFF register becomes set by 0. (display off)

– Display start line register becomes set by 0 (Z-address 0

set,

display from line 0)

After releasing reset, this condition can be changed only by

instruction.

87(85), 88(88)

89(90)

NC No connection. (open)

7

Loading...

Loading...