Samsung KS88P01416, KS88P01424, KS88C01424, KS88C01416, KS57P5616 Datasheet

...

KS57C5616/P5616 PRODUCT OVERVIEW

1 PRODUCT OVERVIEW

OVERVIEW

The KS57C5616/P5616 single-chip CMOS microcontroller is designed for high performance in the application for

Caller-ID, Telephone using Samsung's newest 4-bit CPU core, SAM47 (Samsung Arrangable Microcontrollers).

Featuring a DTMF generator, up-to-960-dot LCD direct drive capability, one 8-bit timer/counter and flexible two

8-bit timer/counters, and serial I/O interface, the KS57C5616/P5616 offer an excellent design solution for a wide

variety of applications requiring DTMF, LCD support.

Up to 43 (including COM/SEG) pins in the 100-pin QFP package can be dedicated to I/O. Nine vectored

interrupts provide a fast response to internal and external events. In addition the advanced CMOS technology a of

the KS57C5616/P5616 ensures low power consumption with a wide operating voltage range.

OTP

The KS57C5616 microcontroller is also available in OTP (One Time Programmable) version, KS57P5616.

KS57P5616 microcontroller has an on-chip 16K-byte one-time-programmable EPROM instead of masked ROM.

The KS57P5616 is comparable to KS57C5616, both in function and in pin configuration.

1-1

PRODUCT OVERVIEW KS57C5616/P5616

FEATURES SUMMARY

Memory

• 16K × 8-bit ROM

• 5,120 × 4-bit RAM (excluding LCD RAM)

I/O Pins

• Input only:4pins (Not including COM/SEG)

6pins (Including COM/SEG)

• I/O:15pins (Not including COM/SEG)

43pins (Including COM/SEG)

Memory-Mapped I/O Structure

• Data memory bank 15

8-bit Basic Timer

• Four interval timer functions

• Watchdog timer

8-bit Timer/Counter

• Programmable 8-bit timer

• External event counter

• Arbitrary clock frequency output

• External clock signal divider

16-Bit Timer/Counter

• Programmable 16-bit timer

• External event counter

• Arbitrary clock frequency output

• External clock signal divider

• Configurable as two 8-bit Timers

• Serial I/O interface clock generator

Watch Timer

• Time interval generation: 0.5 s, 3.9 ms

at 32.768 kHz

• 4 frequency outputs to BUZ pin (0.5, 1, 2, 4 kHz)

at 32.768 kHz

Comparator

• 4-channel mode: Internal reference (4-bit

resolution); 16-step variable reference voltage

• 3-channel mode: External reference

DTMF Generator

• 16 dual-tone for tone dialing

8-bit Serial I/O Interface

• 8-bit transmit/receive mode

• 8-bit receive mode

• LSB-first or MSB-first transmission selectable

LCD Controller/Driver

• 60 SEG x 16 COM terminals

• 8, 12 and 16 com selectable

• COM 8–15: shared with port

• SEG40–59: shared with port

• Two kinds of LCD bias resistor value

Bit Sequential Carrier

• Supports 16-bit serial data transfer in arbitrary

format

Interrupts

• Four external interrupt vectors

• Five internal interrupt vectors

• Two quasi-interrupts

Power-Down Modes

• Idle mode (only CPU clock stops)

• Stop mode (main system oscillation stops)

• Subsystem clock stop mode

Oscillation Sources

• RC, Crystal or Ceramic for system clock

• Oscillation frequency: 0.4–6.0 MHz

• CPU clock divider circuit (by 4, 8, or 64)

Instruction Execution Times

• 1.12, 2.23, 17.88 µs at 3.58 MHz

• 0.67, 1.33, 10.7 µs at 6.0 MHz

• 122 µs at 32.768 kHz (subsystem)

Operating Temperature

• – 40 °C to 85 °C

Operating Voltage Range

• 1.8 V to 5.5 V (except DTMF and Comparator)

• 2 V to 5.5 V (include DTMF)

• 4.0 V to 5.5 V (include Comparator)

Package Type

• 100-pin QFP (1420C)

1-2

KS57C5616/P5616 PRODUCT OVERVIEW

BLOCK DIAGRAM

P7.0/SEG55/CIN0

P7.1/SEG54/CIN1

P7.2/SEG53/CIN2

P7.3/SEG52/CIN3

P1.0-P1.3/

INT0-INT4

P2.0/CLO

P2.1/VLC1

P2.2

P3.0/TCLO0

P3.1/TCLO1

P3.2/TCL0

P3.3/TCL1

P4.0-P4.3/

COM8-COM11

P5.0-P5.3/

COM12-COM15

P6.0-P6.3

SEG59-SEG56/

KS4-KS7

P7.0/SEG55/CIN0

P7.1/SEG54/CIN1

P7.2/SEG53/CIN2

P7.3/SEG52/CIN3

P8.0/SEG51/LCDCK

P8.1/SEG50/LCDSY

P8.2/SEG49

P8.3/SEG48

P9.0-P9.3/

SEG47-SEG44

P10.0-P10.3/

SEG43-SEG40

Comparator

Input Port 1

I/O Port 2

I/O Port 3

I/O Port 4

I/O Port 5

I/O Port 6

I/O Port 7

I/O Port 8

I/O Port 9

I/O Port 10

RESET

Interrupt

Control

Block

Internal

Interrupts

Instruction Dcoder

Arithmetic

and

Logic Unit

8-Bit

Timer/

Counter

XOUT

XIN

XTOUT

XTIN

Clock

Timer/Counter

(Two 8Bit

Timer/Counter)

16-Bit

Instruction

Register

Program

Counter

Program

Status Word

Stack

Pointer

5K x 4-bit

RAM

16KB ROM

Basic

Timer

Watch

Timer

LCD

Driver/

Controller

Serial I/O

I/O Port 0

DTMF

Generator

Watchdog

Timer

VLC1

COM0-COM7

P4.0-P5.3/

COM8-COM15

SEG0-SEG39

P10.3-P6.0/

SEG40-SEG59

P0.0/SCK/KO

P0.1/SO/K1

P0.2/SI/K2

P0.3/BUZ/K3

DTMF

Figure 1-1. KS57C5616 Block Diagram

1-3

PRODUCT OVERVIEW KS57C5616/P5616

P6.0/SEG59/K4

PIN ASSIGNMENTS

SEG9

SEG10

SEG11

SEG12

SEG13

SEG14

SEG15

SEG16

SEG17

SEG18

SEG19

SEG20

SEG21

SEG22

SEG23

SEG24

SEG25

SEG26

SEG27

SEG28

99989796959493929190898887868584838281

SEG8

SEG7

SEG6

SEG5

SEG4

SEG3

SEG2

SEG1

SEG0

DTMF

P0.0/

SCK

/K0

P0.1/SO/K1

P0.2/SI/K2

P0.3/BUZ/K3

V

DD

V

X

OUT

X

TEST

XT

XT

OUT

RESET

P1.0/INT0

P1.1/INT1

P1.2/INT2

P1.3/INT4

P2.0/CLO

P2.1/VLC1

P2.2

P3.0/TCLO0

SS

100

1

2

3

4

5

6

7

8

9

10

11

12

(100-QFP-1420C)

KS57C5616

13

14

15

16

17

IN

18

19

IN

20

21

22

23

24

25

26

27

28

29

30

31323334353637383940414243444546474849

50

SEG29

80

SEG30

79

SEG31

78

SEG32

77

SEG33

76

SEG34

75

SEG35

74

SEG36

73

SEG37

72

SEG38

71

SEG39

70

P10.3/SEG40

69

P10.2/SEG41

68

P10.1/SEG42

67

P10.0/SEG43

66

P9.3/SEG44

65

P9.2/SEG45

64

P9.1/SEG46

63

P9.0/SEG47

62

P8.3/SEG48

61

P8.2/SEG49

60

P8.1/SEG50/LCDSY

59

P8.0/SEG51/LCDCK

58

P7.3/SEG52/CIN3

57

P7.2/SEG53/CIN2

56

P7.1/SEG54/CIN1

55

P7.0/SEG55/CIN0

54

P6.3/SEG56/K7

53

P6.2/SEG57/K6

52

P6.1/SEG58/K5

51

1-4

COM0

COM1

COM2

COM3

COM4

COM5

COM6

COM7

P3.2/TCL0

P3.3/TCL1

P3.1/TCLO1

P4.0/COM8

P4.1/COM9

P4.2/COM10

P4.3/COM11

P5.0/COM12

P5.1/COM13

P5.2/COM14

P5.3/COM15

Figure 1-2. KS57C5616 Pin Assignments (100-QFP Package)

KS57C5616/P5616 PRODUCT OVERVIEW

PIN DESCRIPTIONS

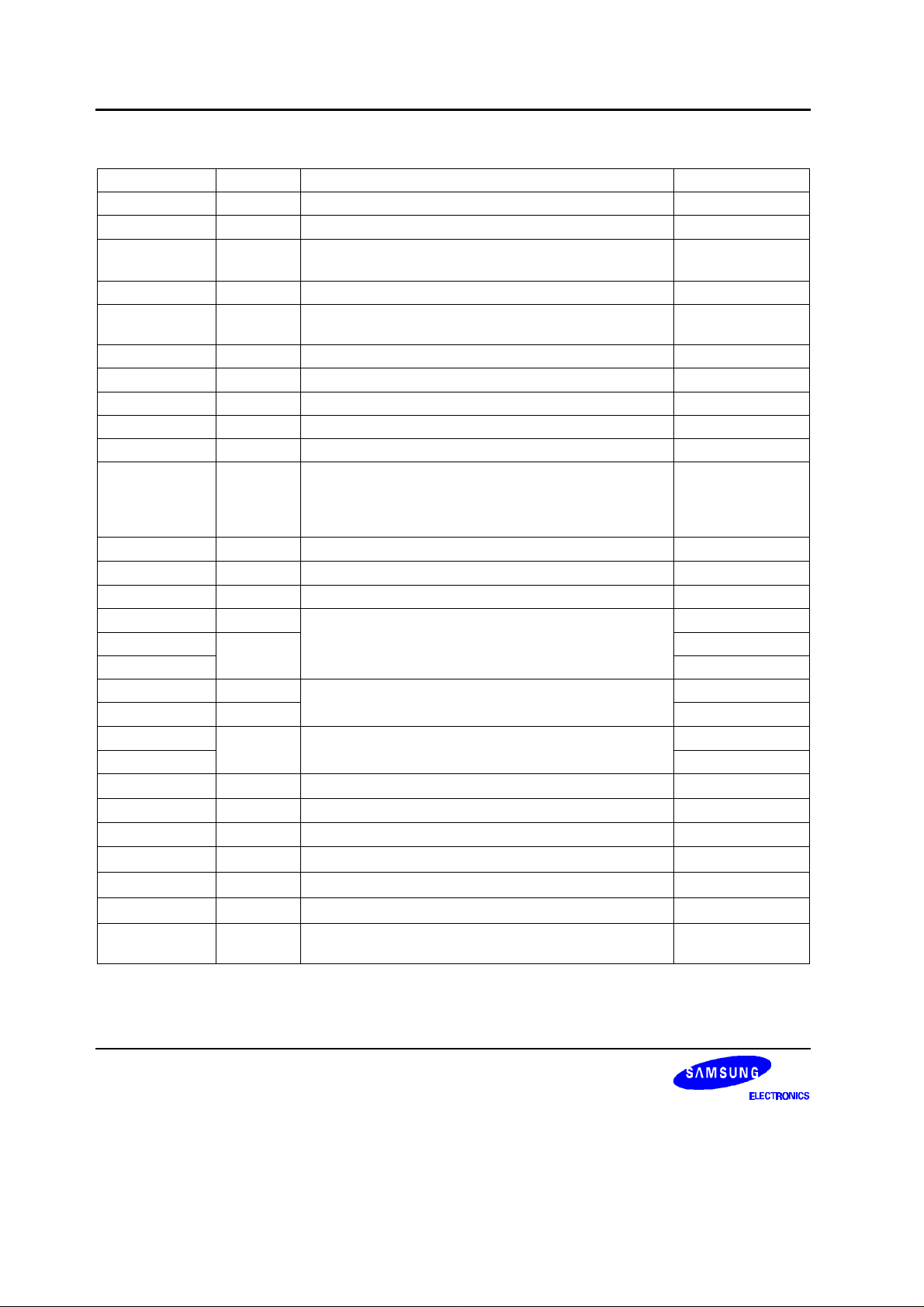

Table 1-1. KS57C5616 Pin Descriptions

Pin Name Pin Type Description Share Pin

P0.0

P0.1

P0.2

P0.3

P1.0

P1.1

P1.2

P1.3

P2.0

P2.1

P2.2

P3.0

P3.1

P3.2

P3.3

P4.0–P4.3

P5.0–P5.3

P6.0–P6.3

I/O 4-bit I/O port.

1-bit and 4-bit read/write and test is possible.

Individual pins are software configurable as input or

output.

SCK/K0

SO/K1

SI/K2

BUZ/K3

Individual pins are software configurable as open-drain or

push-pull output.

4-bit pull-up resistors are software assignable; pull-up

resistors are automatically disabled for output pins.

I 4-bit input port.

1-bit and 4-bit read and test is possible.

4-bit pull-up resistors are software assignable.

INT0

INT1

INT2

INT4

I/O Same as port 0 except that port 2 is a 3-bit I/O port. CLO

VLC1

I/O Same as port 0. TCLO0

TCLO1

TCL0

TCL1

I/O 4-bit I/O ports.

1-, 4-bit or 8-bit read/write and test is possible.

COM8–COM11

COM12–COM15

Individual pins are software configurable as input or

output.

4-bit pull-up resistors are software assignable; pull-up

resistors are automatically disabled for output pins.

I/O Same as P4, P5. SEG59–

SEG56/K4-K7

P7.0–P7.3

SEG55/CIN0–

SEG52/CIN3

P8.0–P8.1 I/O Input ports.

1-, 4-bit or 8-bit read and test is possible.

SEG51/LCDCK

SEG50/LCDSY

4-bit pull-up resistors are software assignable; pull-up

resistors are automatically disabled for output pins.

These pins can not be used as push-pull output. Refer to

the NOTES of Table 10-3. Port Mode Group Flags.

P8.2–P8.3

I/O Same as P4, P5. SEG49

SEG48

P9.0–P9.3

SEG47–SEG44

P10.0–P10.3 I/O Same as P4, P5. SEG43–SEG40

SCK

I/O Serial I/O interface clock signal. P0.0/K0

SO I/O Serial data output. P0.1/K1

1-5

PRODUCT OVERVIEW KS57C5616/P5616

Table 1-1. KS57C5616 Pin Descriptions (Continued)

Pin Name Pin Type Description Share Pin

SI I/O Serial data input. P0.2/K2

BUZ I/O 0.5, 1, 2, or 4 kHz frequency output for buzzer sound. P0.3/K3

INT0, INT1 I External interrupts. The triggering edge for INT0 and

P1.0, P1.1

INT1 is selectable.

INT2 I Quasi-interrupt with detection of rising or falling edges. P1.2

INT4 I External interrupt with a detection of rising and falling

P1.3

edge.

CLO I/O Clock output . P2.0

TCLO0 I/O Timer/counter 0 clock output. P3.0

TCLO1 I/O Timer/counter 1 clock output. P3.1

TCL0 I/O External clock input for timer/counter 0. P3.2

TCL1 I/O External clock input for timer/counter 1. P3.3

CIN0

CIN1

CIN2

CIN3

I/O 4-Channel comparator input

CIN0–CIN2: comparator input only

CIN3: comparator input or external reference input

P7.0/SEG55

P7.1/SEG54

P7.2/SEG53

P7.3/SEG52

DTMF O DTMF output –

LCDCK I/O LCD clock output P8.0/SEG51

LCDSY I/O LCD synchronization clock output. P8.1/SEG50

COM0–COM7 O LCD common signal output. –

COM8–COM11 I/O P4.0–P4.3

COM12–COM15 P5.0–P5.3

SEG0–SEG39 O LCD segment signal output. –

SEG40–SEG59 I/O P10.3–P6.0

K0–K3 I/O External interrupt (triggering edge is selectable) P0.0–P0.3

K4–K7 P6.0–P6.3

V

DD

V

SS

RESET

V

LC1

X

X

,

IN

OUT

XTIN, XT

OUT

TEST I Chip test input pin.

– Main power supply. –

– Ground. –

I Reset signal. –

– LCD power supply. P2.1

– Crystal, Ceramic or RC oscillator pins for system clock. –

– Crystal oscillator pins for subsystem clock. –

–

Hold GND when the device is operating.

NOTE: Pull-up resistors for all I/O ports are automatically disabled if they are configured to output mode.

1-6

KS57C5616/P5616 PRODUCT OVERVIEW

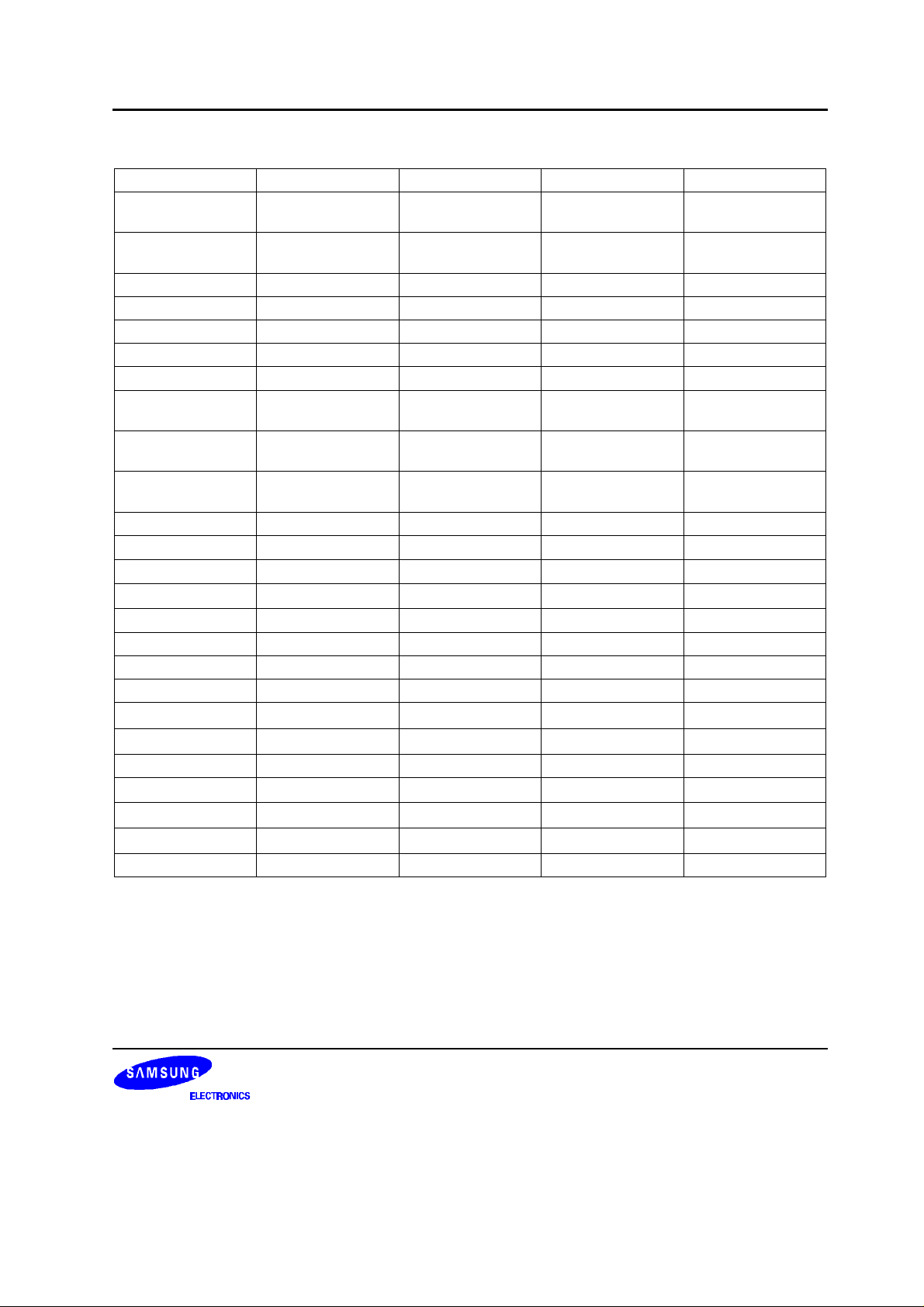

Table 1-2. Supplemental KS57C5616 Pin Data

Pin Names Share Pins I/O Type RESET Value Circuit Type

P0.0–P0.3 SCK/K0, SO/K1,

I/O Input E-4

SI/K2, BUZ/K3

P1.0–P1.3 INT0, INT1 and

I Input A-4

INT2, INT4

P2.0 CLO I/O Input E-4

P2.1 VLC1 I/O Input E-7

P2.2 – I/O Input E-4

P3.0–P3.1 TCLO0, TCLO1 I/O Input E-2

P3.2–P3.3 TCL0, TCL1 I/O Input E-4

P4.0–P4.3

P5.0–P5.3

P6.0–P6.3 SEG59/K4–

COM8–COM11

COM12–COM15

I/O Input H-24

I/O

Input

H-25

SEG56/K7

P7.0–P7.2 SEG55/CIN0–

I/O Input H-26

SEG53/CIN2

P7.3 SEG52/CIN3 I/O Input H-27

P8.0–P8.1 SEG51–SEG50 I/O Input H-28

P8.2–P8.3 SEG49–SEG48 I/O Input H-24

P9.0–P9.3 SEG47–SEG44 I/O Input H-24

P10.0–P10.3 SEG43–SEG40

I/O

Input

H-24

COM0–COM7 – O High H-3

SEG0–SEG39 – O High H-3

DTMF – O High impedance G-7

V

DD

V

SS

RESET

V

LC1

X

X

,

IN

XT

,

IN

OUT

XT

OUT

– – – –

– – – –

– I – B

– – – –

– – – –

– – – –

TEST – I – –

1-7

KS57C5616/P5616 (Preliminary Spec) PRODUCT OVERVIEW

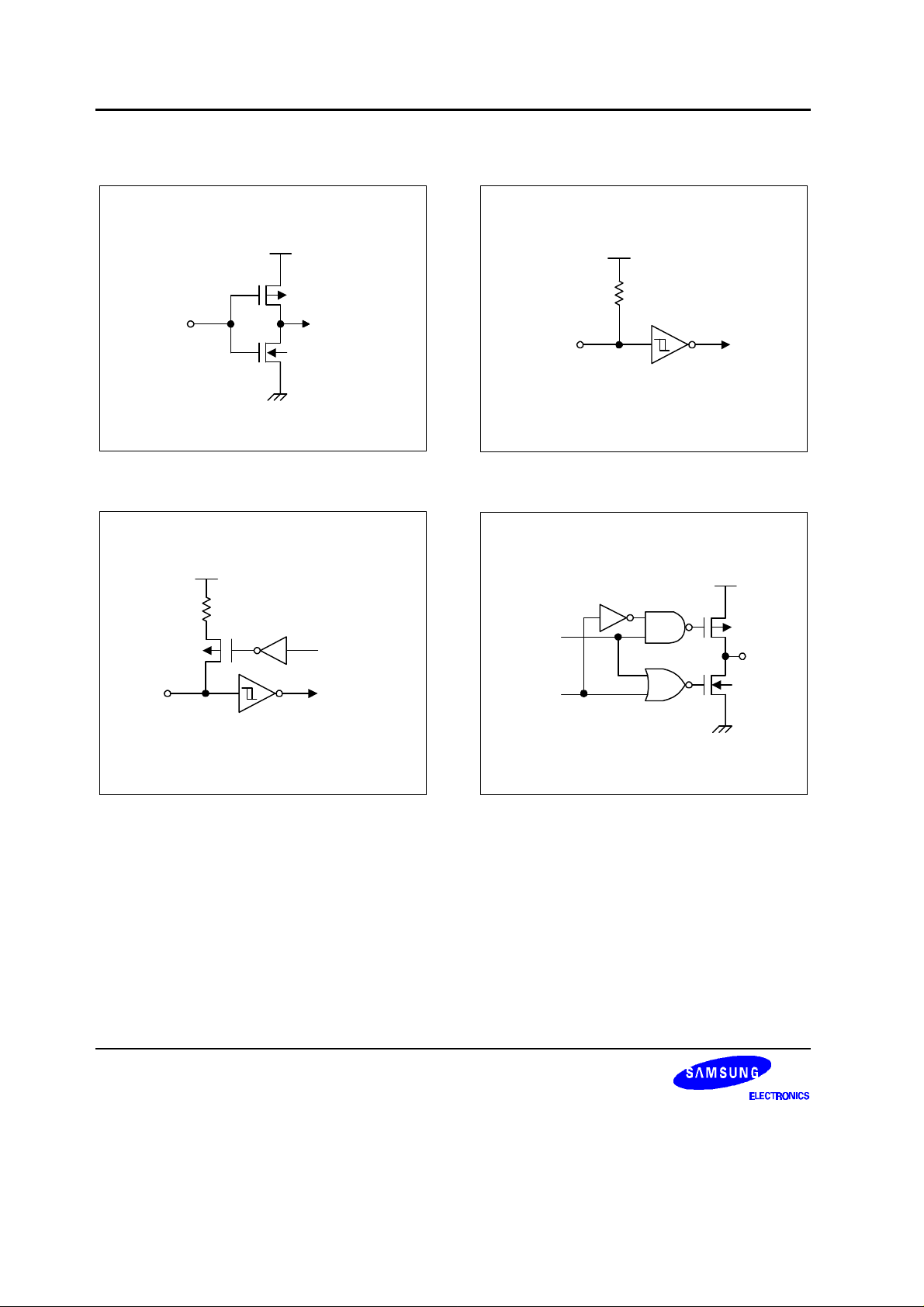

PIN CIRCUIT DIAGRAMS

V

DD

V

DD

P-Channel

In

N-Channel

Figure 1-3. Pin Circuit Type A

DD

V

Pull-Up

Resistor

In

Pull-Up

Resistor

Enable

Pull-Up

Resistor

In

Schmitt Trigger

Figure 1-5. Pin Circuit Type B

Data

Output

DIsable

DD

V

P-CH

Out

N-CH

1-8

Schmitt Trigger

Figure 1-4. Pin Circuit Type A-4

Figure 1-6. Pin Circuit Type C

KS57C5616/P5616 PRODUCT OVERVIEW

V

DD

Data

Output

DIsable

PNE

V

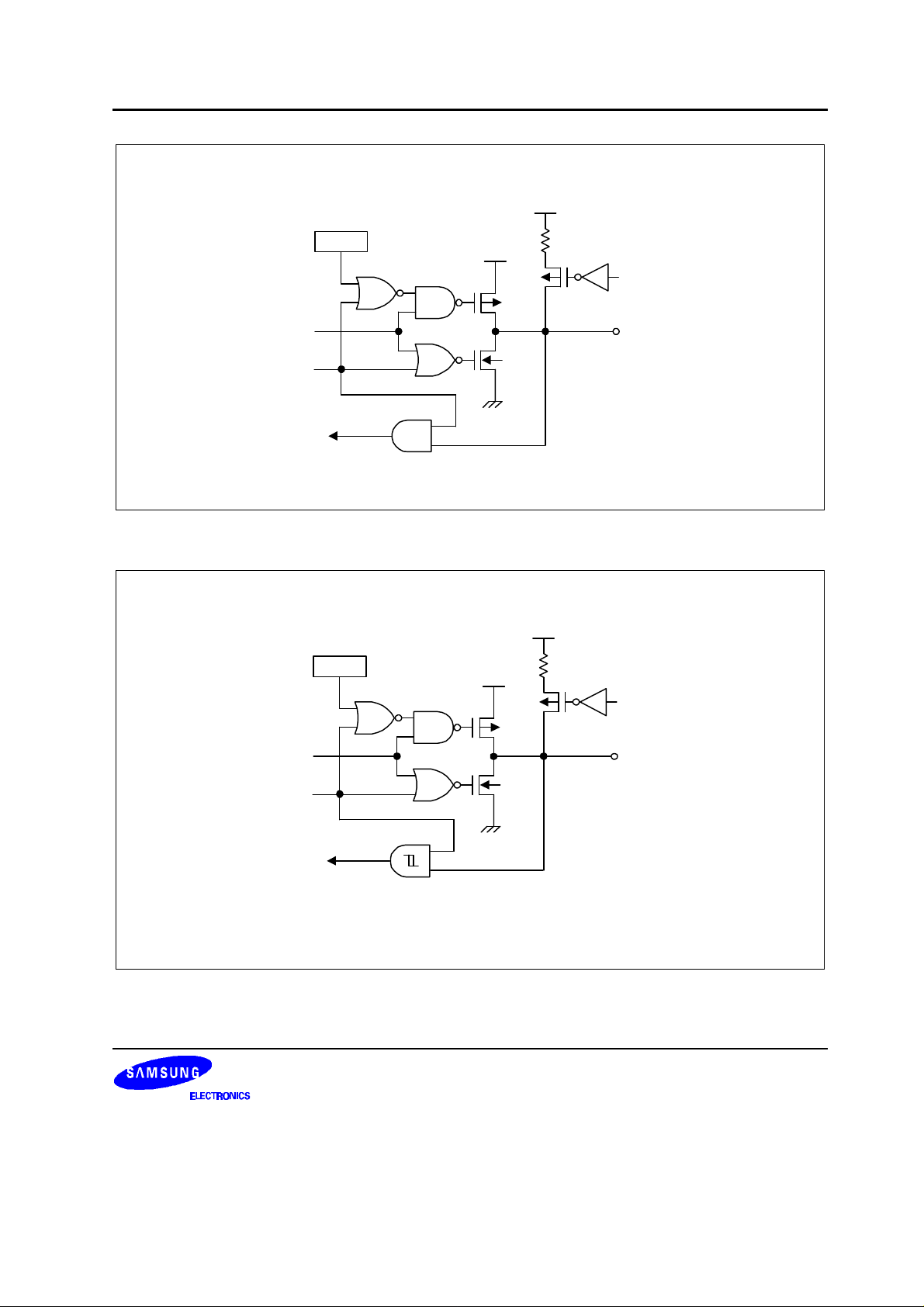

Figure 1-7. Pin Circuit Type E-2

PNE

V

DD

DD

P-CH

N-CH

P-CH

V

DD

Pull-up

Resistor

Pull-up

Resistor

Enable

I/O

Pull-up

Resistor

Pull-up

Resistor

Enable

Data

Output

DIsable

I/O

N-CH

Schmitt Trigger

Figure 1-8. Pin Circuit Type E-4

1-9

PRODUCT OVERVIEW KS57C5616/P5616

V

DD

Data

Output

DIsable

Digital

Input

VLCEN

VLC1

PNE

V

Figure 1-9. Pin Circuit Type E-7

DD

P-CH

N-CH

Pull-up

Resistor

Pull-up

Resistor

Enable

I/O

1-10

KS57C5616/P5616 PRODUCT OVERVIEW

V

LC1

V

LC2

V

LC3

COM/SEG

V

LC4

V

LC5

V

LC6

Figure 1-10. Pin Circuit Type H-3

1-11

PRODUCT OVERVIEW KS57C5616/P5616

V

LC1

V

LC2

V

LC3

SEG/COM

Data

Out

Output

DIsable

V

LC4

V

LC5

V

SS

Figure 1-11. Pin Circuit Type H-23

1-12

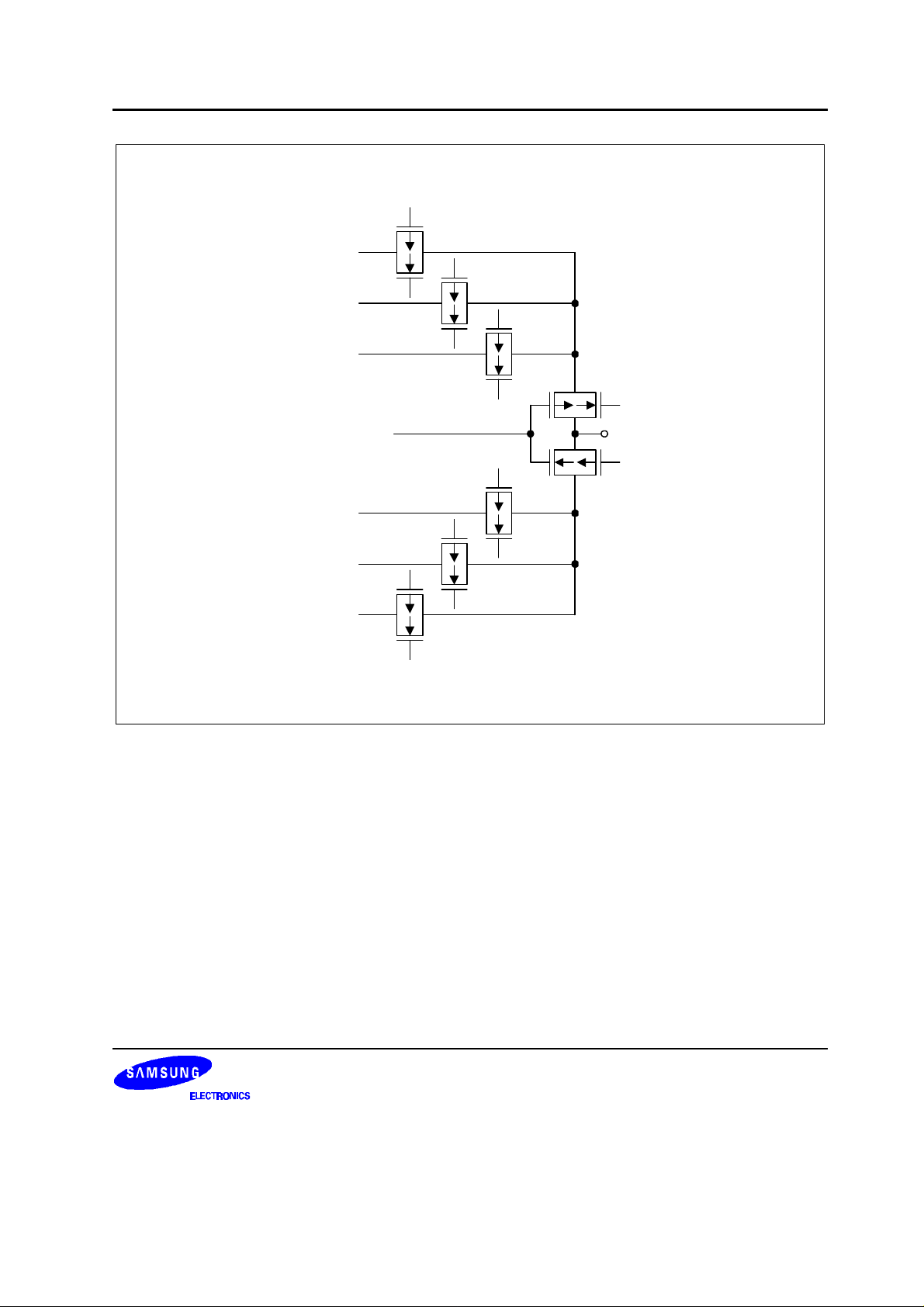

KS57C5616/P5616 PRODUCT OVERVIEW

DD

V

Pull-up

Resistor

Pull-up

Resistor

Enable

COM/SEG

LCD_ON

Circuit

Type H-23

Data

Output

DIsable

COM/SEG

LCD_ON

Data

Output

DIsable

Circuit

Type C

Figure 1-12. Pin Circuit Type H-24

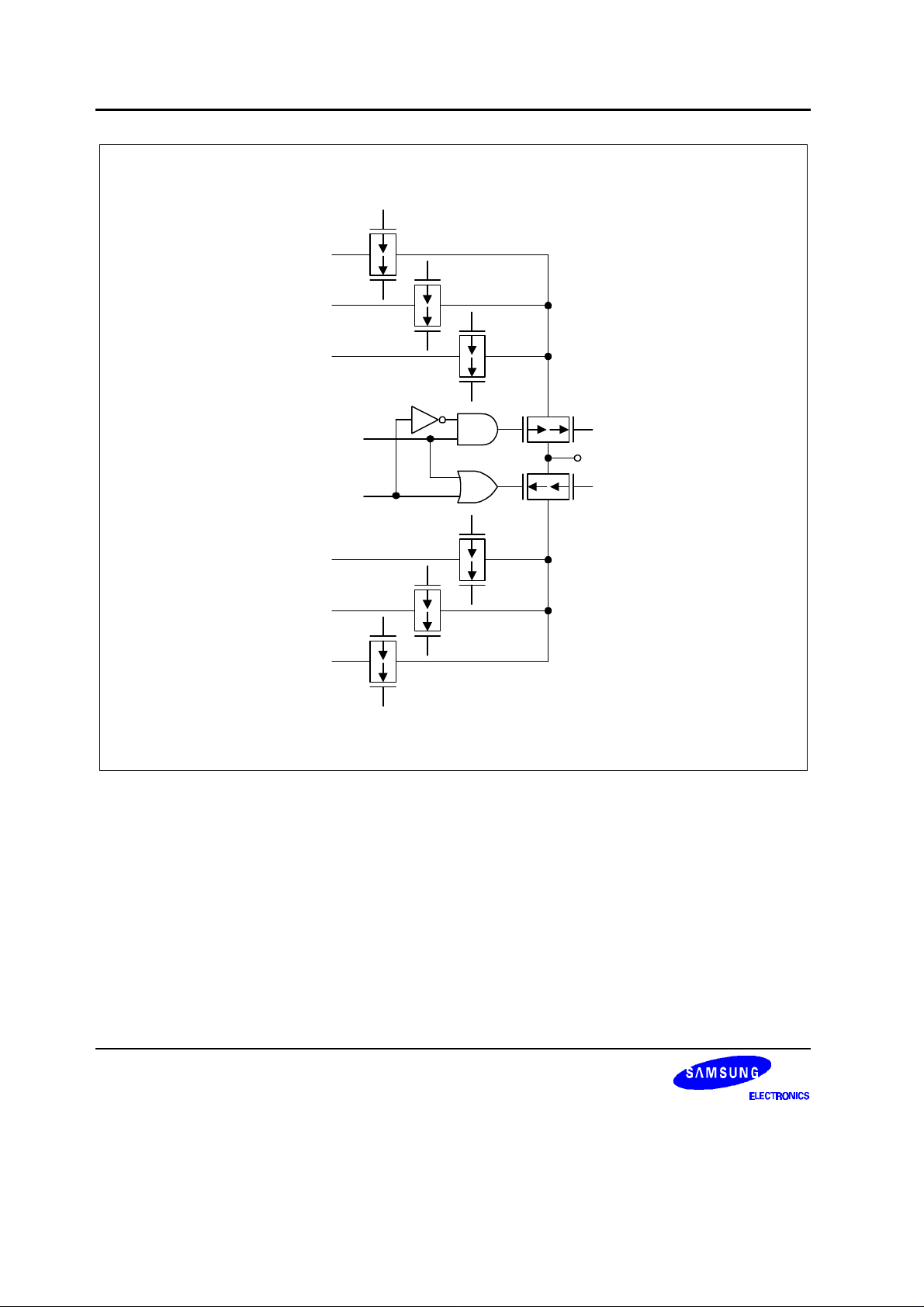

Pull-up

Resistor

Pull-up

Resistor

Enable

Circuit

Type H-23

Circuit

Type C

I/O

VDD

I/O

Figure 1-13. Pin Circuit Type H-25

1-13

Loading...

Loading...