Samsung KS57P21132, KS57C21132, KS57C21124, KS57C21116 Datasheet

KS57C21116/C21124/C21132/P21132 MICROCONTROLLER PRODUCT OVERVIEW

1PRODUCT OVERVIEW

OVERVIEW

The KS57C21116/C21124/C21132 single-chip CMOS microcontroller has been designed for high performance

using Samsung's newest 4-bit CPU core, SAM47 (Samsung Arrangeable Microcontrollers).

With an up-to-1280-dot LCD direct drive capability, segment expandable circuit, 8-bit and 16-bit timer/counter,

and serial I/O, the KS57C21116/C21124/C21132 offers an excellent design solution for a wide variety of

applications which require LCD functions.

Up to 51 pins of the 128-pin QFP package can be dedicated to I/O. Nine vectored interrupts provide fast

response to internal and external events. In addition, the KS57C21116/C21124/C21132's advanced CMOS

technology provides for low power consumption and a wide operating voltage range.

OTP

The KS57C21116/C21124/C21132 microcontroller is also available in OTP (One Time Programmable) version,

KS57P21132. KS57P21132 microcontroller has an on-chip 32-Kbyte one-time-programmable EPROM instead of

masked ROM. The KS57P21132 is comparable to KS57C21116/C21124/C21132, both in function and in pin

configuration except ROM size.

1-1

PRODUCT OVERVIEW KS57C21116/C21124/C21132/P21132 MICROCONTROLLER

FEATURES SUMMARY

Memory

• 3,584 × 4-bit RAM

(Excluding LCD Display

RAM)

• 16,384/24,576/32,768 ×

8-bit ROM

51 I/O Pins

• I/O: 47 pins (32 pins are

configurable as SEG pins)

• Input only: 4 pins

LCD Controller/Driver

• 80 SEG × 16 COM, 88 SEG

× 8 COM Terminals

• Internal resistor circuit for

LCD bias

• 16 Level LCD contrast

control (software)

• Segment expandable circuit

• All dot can be switched

on/off

8-bit Basic Timer

• 4 interval timer functions

• Watch-dog timer

16-Bit Timer/Counter

• Programmable 16-bit timer

• External event counter

• Arbitrary clock frequency

output

• External clock signal divider

• Configurable as two 8-bit

Timers

• Serial I/O interface clock

generator

Watch Timer

• Time interval generation:

0.5 s, 3.9 ms at 32,768 Hz

• 4 frequency outputs to BUZ

pin

• Clock source generation for

LCD

8-bit Serial I/O Interface

• 8-bit transmit/receive mode

• 8-bit receive mode

• LSB-first or MSB-first

transmission selectable

• Internal or external clock

source

Bit Sequential Carrier

• Supports 16-bit serial data

transfer in arbitrary format

Memory-Mapped I/O Structure

• Data memory bank 15

Power-Down Modes

• Idle mode (only CPU clock

stops)

• Stop mode (main system

clock stops)

• Subsystem clock stop mode

Oscillation Sources

• Crystal, Ceramic or RC for

main system clock

• Crystal oscillator for

subsystem clock

• Main system clock

frequency: 0.4–6 MHz

• Subsystem clock frequency:

32.768 kHz

• CPU clock divider circuit

(by 4, 8 or 64)

Instruction Execution Times

8-bit Timer/Counter

• Programmable 8-bit timer

• External event counter

• Arbitrary clock frequency

output

• External clock signal divider

1-2

Comparator

• 3 Channel mode: internal

reference (4-bit resolution)

• 2 Channel mode: external

reference

Interrupts

• Five internal vectored

interrupts

• Four external vectored

interrupts

• Two quasi-interrupts

• 0.67, 1.33, 10.7 µs at 6

MHz

• 0.95, 1.91, 15.3 µs at 4.19

MHz

• 122 µs at 32.768 kHz

Operating Temperature

• – 40 °C to 85 °C

Operating Voltage Range

• 1.8 V to 5.5 V

Package Type

• 128-pin QFP

KS57C21116/C21124/C21132/P21132 MICROCONTROLLER PRODUCT OVERVIEW

FUNCTION OVERVIEW

SAM47 CPU

All KS57-series microcontrollers have the advanced SAM47 CPU core. The SAM47 CPU can directly address up

to 32 K bytes of program memory. The arithmetic logic unit (ALU) performs 4-bit addition, subtraction, logical,

and shift-and-rotate operations in one instruction cycle and most 8-bit arithmetic and logical operations in two

cycles.

CPU REGISTERS

Program Counter

A 15-bit program counter (PC) stores addresses for instruction fetches during program execution. Usually, the PC

is incremented by the number of bytes of the fetched instruction. The one instruction fetch that does not

increment the PC is the 1-byte REF instruction which references instructions stored in a look-up table in the

ROM. Whenever a reset operation or an interrupt occurs, bits PC13 through PC0 are set to the vector address.

Stack Pointer

An 8-bit stack pointer (SP) stores addresses for stack operations. The stack area is located in general-purpose

data memory bank 0. The SP is 8-bit read/writeable and SP bit 0 must always be logical zero.

During an interrupt or a subroutine call, the PC value and the PSW are written to the stack area. When the

service routine has completed, the values referenced by the stack pointer are restored. Then, the next instruction

is executed.

The stack pointer can access the stack despite data memory access enable flag status. Since the reset value of

the stack pointer is not defined in firmware, you use program code to initialize the stack pointer to 00H. This sets

the first register of the stack area to data memory location 0FFH.

PROGRAM MEMORY

In its standard configuration, the 16,384/24,576/32,768 × 8-bit ROM is divided into four areas:

— 16-byte area for vector addresses

— 96-byte instruction reference area

— 16-byte general-purpose area (0010–001FH)

— 16,256/24,448/32,640-byte area for general-purpose program memory

The vector address area is used mostly during reset operations and interrupts. These 16 bytes can alternately be

used as general-purpose ROM.

The REF instruction references 2 x 1-byte or 2-byte instructions stored in reference area locations 0020H–

007FH. REF can also reference three-byte instructions such as JP or CALL. So that a REF instruction can

reference these instructions, however, the JP or CALL must be shortened to a 2-byte format. To do this, JP or

CALL is written to the reference area with the format TJP or TCALL instead of the normal instruction name.

Unused locations in the REF instruction look-up area can be allocated to general-purpose use.

1-3

PRODUCT OVERVIEW KS57C21116/C21124/C21132/P21132 MICROCONTROLLER

DATA MEMORY

Overview

The 3,584-bit data memory has five areas:

— 32 × 4-bit working register area

— 224 × 4-bit general-purpose area in bank 0 which is also used as the stack area

— 256 × 4-bit general-purpose area in bank 1, bank 2,……, bank 13, respectively

— 256 × 5-bit area for LCD data in bank 14

— 128 × 4-bit area in bank 15 for memory-mapped I/O addresses

The data memory area is also organized as sixteen memory banks — bank 0, bank 1, ….., and bank 15. You use

the select memory bank instruction (SMB) to select one of the banks as working data memory.

Data stored in RAM locations are 1-, 4-, and 8-bit addressable. After a hardware reset, data memory initialization

values must be defined by program code.

Data Memory Addressing Modes

The enable memory bank (EMB) flag controls the addressing mode for data memory banks 0, 1, ….., or 15.

When the EMB flag is logical zero, only locations 00H–7FH of bank 0 and bank 15 can be accessed. When the

EMB flag is set to logical one, all sixteen data memory banks can be accessed based on the current SMB value.

Working Registers

The RAM's working register area in data memory bank 0 is also divided into four register banks. Each register

bank has eight 4-bit registers. Paired 4-bit registers are 8-bit addressable.

Register A can be used as a 4-bit accumulator and double register EA as an 8-bit extended accumulator; double

registers WX, WL and HL are used as address pointers for indirect addressing.

To limit the possibility of data corruption due to incorrect register addressing, it is advisable to use bank 0 for

main programs and banks 1, 2, and 3 for interrupt service routines.

LCD Data Register Area

Bit values for LCD segment data are stored in data memory bank 14. Register locations that are not used to store

LCD data can be assigned to general-purpose use.

Bit Sequential Carrier

The bit sequential carrier (BSC) is a 16-bit general register that you can manipulate using 1-, 4-, and 8-bit RAM

control instructions.

Using the BSC register, addresses and bit locations can be specified sequentially using 1-bit indirect addressing

instructions. In this way, a program can generate 16-bit data output by moving the bit location sequentially,

incrementing or decrementing the value of the L register. You can also use direct addressing to manipulate data

in the BSC.

1-4

KS57C21116/C21124/C21132/P21132 MICROCONTROLLER PRODUCT OVERVIEW

CONTROL REGISTERS

Program Status Word

The 8-bit program status word (PSW) controls ALU operations and instruction execution sequencing. It is also

used to restore a program's execution environment when an interrupt has been serviced. Program instructions

can always address the PSW regardless of the current value of data memory access enable flags.

Before an interrupt is processed, the PSW is pushed onto the stack in data memory bank 0. When the routine is

completed, PSW values are restored.

IS1 IS0 EMB ERB

C SC2 SC1 SC0

Interrupt status flags (IS1, IS0), the enable memory bank and enable register bank flags (EMB, ERB), and the

carry flag (C) are 1- and 4-bit read/write or 8-bit read-only addressable. Skip condition flags (SC0–SC2) can be

addressed using 8-bit read instructions only.

Select Bank (SB) Register

Two 4-bit locations called the SB register store address values used to access specific memory and register

banks: the select memory bank register, SMB, and the select register bank register, SRB.

'SMB n' instructions select a data memory bank (0, 1, ….., or 15) and store the upper four bits of the 12-bit data

memory address in the SMB register. The 'SRB n' instruction is used to select register bank 0, 1, 2, or 3, and to

store the address data in the SRB.

The instructions 'PUSH SB' and 'POP SB' move SMB and SRB values to and from the stack for interrupts and

subroutines.

CLOCK CIRCUITS

Main system and subsystem oscillation circuits generate the internal clock signals for the CPU and peripheral

hardware. The main system clock can use a Crystal, Ceramic, or RC oscillation source, or an externallygenerated clock signal. The subsystem clock requires either a crystal oscillator or an external clock source.

Bit settings in the 4-bit power control and system clock mode registers select the oscillation source, the CPU

clock, and the clock used during power-down mode. The internal system clock signal (fxx) can be divided internally to produce four CPU clock frequencies — fx/4, fx/8, fx/64, or fxt/4.

INTERRUPTS

Interrupt requests may be generated internally by on-chip processes (INTB, INTT0, INTT1, and INTS) or

externally by peripheral devices (INT0, INT1, INT4, and INTK). There are two quasi-interrupts: INT2 and INTW.

INT2 detects rising or falling edges of incoming signals and INTW detects time intervals of 0.5 seconds or 3.91

milliseconds. The following components support interrupt processing:

— Interrupt enable flags

— Interrupt request flags

— Interrupt priority registers

— Power-down termination circuit

1-5

PRODUCT OVERVIEW KS57C21116/C21124/C21132/P21132 MICROCONTROLLER

POWER DOWN

To reduce power consumption, there are two power-down modes: idle and stop. The IDLE instruction initiates idle

mode and the STOP instruction initiates stop mode.

In idle mode, only the CPU clock stops while peripherals and the oscillation source continue to operate normally.

Stop mode effects only the main system clock — a subsystem clock, if used, continues oscillating. In stop mode,

main system clock oscillation stops completely, halting all operations except for a few basic peripheral functions.

RESET or an interrupt can be used to terminate either idle or stop mode.

RESET

When a RESET signal occurs during normal operation or during power-down mode, the CPU enters idle mode

when the reset operation is initiated. When the standard oscillation stabilization interval (31.3 ms at 4.19 MHz)

has elapsed, normal CPU operation resumes.

I/O PORTS

The KS57C21116/C21124/C21132 has 13 I/O ports. Pin addresses for all I/O ports are mapped in bank 15 of the

RAM. There are 4 input pins and 47 configurable I/O pins for a total of 51 I/O pins. The contents of I/O port pin

latches can be read, written, or tested at the corresponding address using bit manipulation instructions.

TIMERS and TIMER/COUNTERS

The timer function has four main components: an 8-bit basic interval timer, an 8-bit timer/counter, a 16-bit

timer/counter and a watch timer. The 8-bit basic timer generates interrupt requests at precise intervals, based on

the selected clock frequency and has watch-dog timer function.

The programmable 8-bit and 16-bit timer/counters are used for external event counting, generation of arbitrary

clock frequencies for output, and dividing external clock signals. The 16-bit timer/counter is the source of the

clock signal that is required to drive the serial I/O interface and configurable as two 8-bit timer/counters.

The watch timer has an 8-bit watch timer mode register, a clock selector and a frequency divider circuit. Its

functions include real-time and watch-time measurement, clock generation for the LCD controller and frequency

outputs for buzzer sound.

LCD DRIVER/CONTROLLER

The KS57C21116/C21124/C21132 can directly drive an up-to-1,280-dot LCD panel. The LCD function block has

the following components:

— RAM area for storing display data

— 80 segment output pins (SEG0–SEG79)

— Segment expandable circuit

— 16 common output pins (COM0–COM15)

— 5 operating power supply pins (V

LC1–VLC5

)

— Sixteen level LCD contrast control circuit (software)

Frame frequency, LCD clock, duty, and segment pins used for display output are controlled by bit settings in the

8-bit mode register, LMOD. You use the 4-bit LCD control register, LCON, to turn the LCD display on and off,

and to control current supplied to the dividing resistors. Segment data are output using a direct memory access

method synchronized with the LCD frame frequency (f

LCD

).

Using the main system clock, the LCD panel operates in idle mode; during stop mode, it is turned off. If a

subsystem clock is used as a clock source, the LCD panel will continue to operate during stop and idle modes.

1-6

KS57C21116/C21124/C21132/P21132 MICROCONTROLLER PRODUCT OVERVIEW

SERIAL I/O INTERFACE

The serial I/O interface supports the transmission or reception of 8-bit serial data with an external device. The

serial interface has the following functional components:

— 8-bit mode register

— Clock selector circuit

— 8-bit buffer register

— 3-bit serial clock counter

The serial I/O circuit can be set either to transmit-and-receive or to receive-only mode. MSB-first or LSB-first

transmission is also selectable. The serial interface operates with an internal or an external clock source, or using

the clock signal generated by the 16-bit timer/counter. To modify transmission frequency, the appropriate bits in

the serial I/O mode register (SMOD) must be manipulated.

COMPARATOR

Port 4 can be used as a analog input port for a comparator. The reference voltage for the 3-channel comparator

can be supplied either internally or externally at P4.2. The comparator module has the following components:

— Comparator

— Internal reference voltage generator (4-bit resolution)

— External reference voltage source at P4.2

— Comparator mode register (CMOD)

— Comparison result register (CMPREG)

1-7

PRODUCT OVERVIEW KS57C21116/C21124/C21132/P21132 MICROCONTROLLER

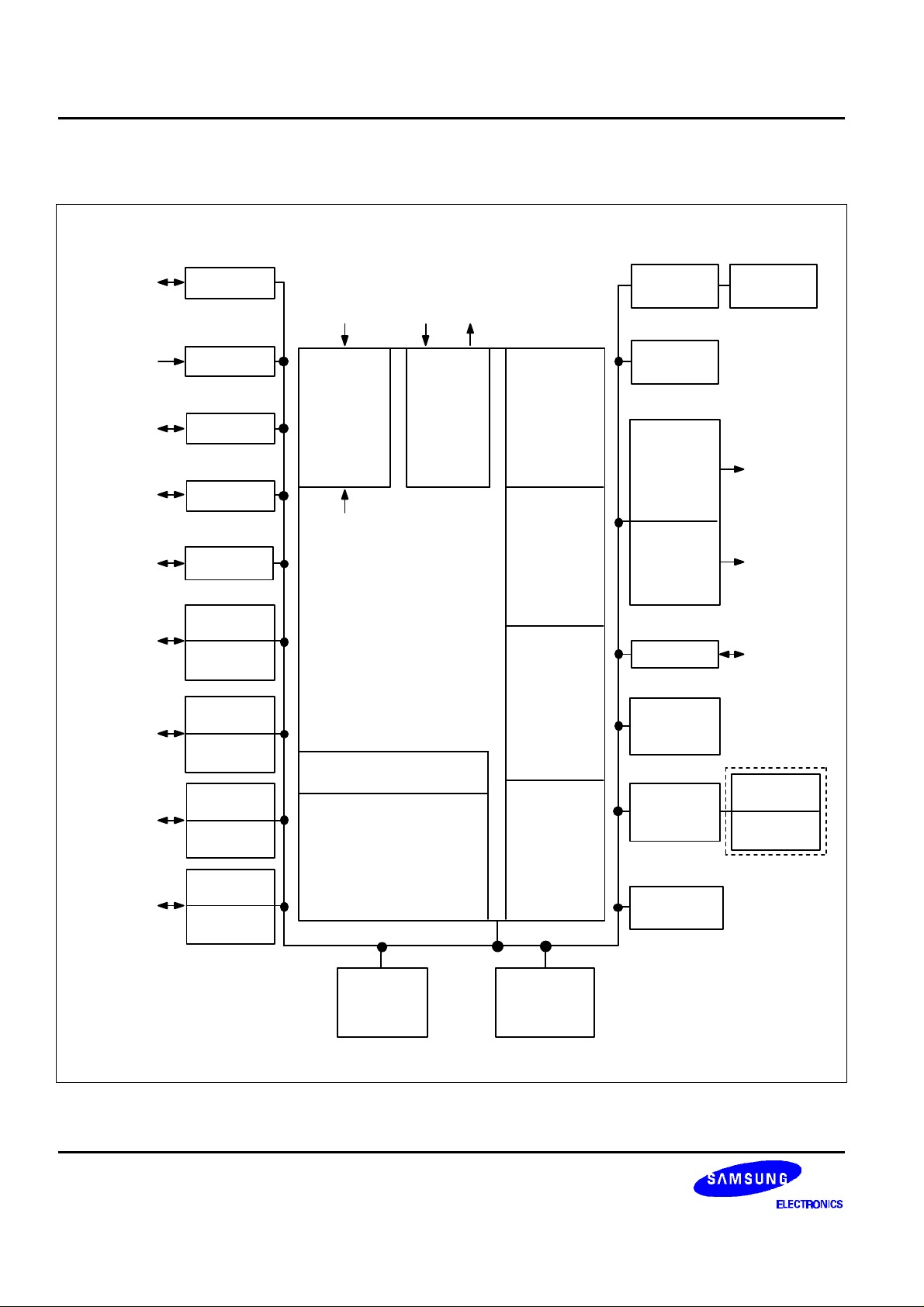

BLOCK DIAGRAM

SCK

/K0/P0.0

SO/K1/P0.1

SI/K2/P0.2

BUZ/K3/P0.3

INT0/P1.0

INT1/P1.1

INT2/P1.2

INT4/P1.3

M/P2.0

LCDFR/P2.1

CLO1/P2.2

CLO2/P2.3

TCLO0/CL/P3.0

TCLO1/P3.1

TCL0/P3.2

TCL1/P3.3

CIN0/P4.0

CIN1/P4.1

CIN2/P4.2

SEG79/K4/P6.0

SEG78/K5/P6.1

SEG77/K6/P6.2

SEG76/K7/P6.3

SEG75-SEG72/

P7.0-P7.3

SEG71-SEG68/

P8.0–P8.3

SEG67-SEG64/

P9.0–P9.3

SEG63-SEG60/

P10.0–P10.3

SEG59-SEG56/

P11.0–P11.3

SEG55-SEG52/

P12.0–P12.3

SEG51-SEG48/

P13.0–P13.3

I/O PORT 0

INPUT PORT 1

I/O PORT 2

I/O PORT 3

I/O PORT 4

I/O PORT 6

I/O PORT 7

I/O PORT 8

I/O PORT 9

I/O PORT 10

I/O PORT 11

I/O PORT 12

I/O PORT 13

RESET

INTERRUPT

CONTROL

BLOCK

INTERNAL

INTERRUPTS

INSTRUCTION DECODER

ARITHMETIC

LOGIC UNIT

XTin

AND

Xin

CLOCK

Xout

XTout

STACK

POINTER

PROGRAM

COUNTER

PROGRAM

STATUS

WORD

FLAGS

BAS IC

TIMER

WATCH

TIMER

LCD

DRIVER/

CONTROLLER

SEGMENT

EXPANDER

SERIAL I/O

8-BIT

TIMER/

COUNTER0

16-BIT

TIMER/

COUNTER1

COMPARATOR

WATCH-DOG

TIMER

VLC1-VLC5

COM0-COM7

COM8-COM15/

SEG87-SEG80

SEG0-SEG47

SEG48-SEG79/

PORT13-PORT6

M/P2.0

LCDFR/P2.1

CL/P3.0/TCLO0

SCK

P0.0 /

P0.1 / SO/K1

P0.2 / SI/K2

8-BIT TIMER/

COUNTER1A

8-BIT TIMER/

COUNTER1B

/K0

1-8

3,584 x 4-BIT

DATA

MEMORY

16/24/32 KBYTE

PROGRAM

MEMORY

Figure 1-1. KS57C21116/C21124/C21132 Simplified Block Diagram

KS57C21116/C21124/C21132/P21132 MICROCONTROLLER PRODUCT OVERVIEW

SEG79/P6.0/K4

SEG78/P6.1/K5

SEG77/P6.2/K6

SEG76/P6.3/K7

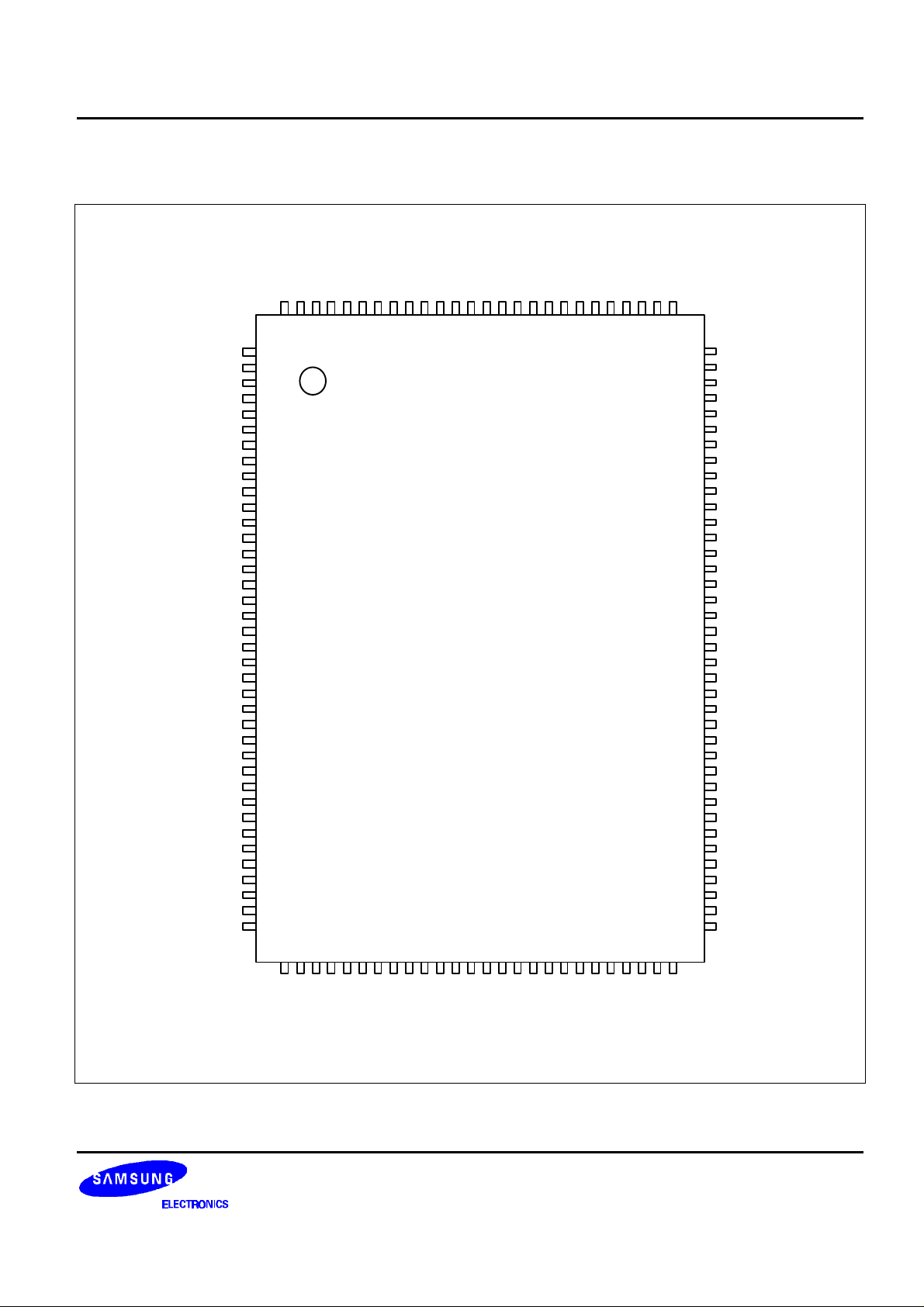

PIN ASSIGNMENTS

SEG85/COM10

SEG84/COM11

SEG83/COM12

SEG82/COM13

SEG81/COM14

SEG80/COM15

SEG0

SEG1

SEG2

SEG3

SEG4

SEG5

SEG6

SEG7

SEG8

SEG9

SEG10

SEG11

SEG12

SEG13

SEG14

SEG15

SEG16

SEG17

SEG18

SEG19

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

COM9/SEG86

COM8/SEG87

COM7

COM6

COM5

COM4

COM3

COM2

COM1

COM0

VLC5

VLC4

VLC3

VLC2

VLC1

P0.0/

P0.1/SO/K1

P0.3/BUZ/K3

P2.1/LCDFR

P3.0/TCLO0/CL

P3.1/TCLO1

/K0

SCK

P0.2/SI/K2

VDD

VSS

X

OUT

XIN

TEST

XTIN

XT

OUT

RESET

P1.0/INT0

P1.1/INT1

P1.2/INT2

P1.3/INT4

P2.0/M

P2.2/CLO1

P2.3/CLO2

P3.2/TCL0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

KS57C21116/C21124/C21132

(128-QFP-1420)

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

SEG20

SEG21

SEG22

SEG23

SEG24

SEG25

SEG26

SEG27

SEG28

SEG29

SEG30

SEG31

SEG32

SEG33

SEG34

SEG35

SEG36

SEG37

SEG38

SEG39

SEG40

SEG41

SEG42

SEG43

SEG44

SEG45

SEG46

SEG47

SEG48/P13.3

SEG49/P13.2

SEG50/P13.1

SEG51/P13.0

SEG52/P12.3

SEG53/P12.2

SEG54/P12.1

SEG55/P12.0

SEG56/P11.3

SEG57/P11.2

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56 5758

59

60

61

62

63

P3.3/TCL1

P4.0/CIN0

P4.1/CIN1

P4.2/CIN2

SEG75/P7.0

SEG74/P7.1

SEG73/P7.2

SEG72/P7.3

SEG71/P8.0

SEG70/P8.1

SEG69/P8.2

SEG68/P8.3

SEG67/P9.0

SEG66/P9.1

SEG65/P9.2

SEG64/P9.3

SEG63/P10.0

SEG62/P10.1

SEG61/P10.2

SEG60/P10.3

SEG59/P11.0

Figure 1-2. KS57C21116/C21124/C21132 128-QFP Pin Assignment

64

SEG58/P11.1

1-9

PRODUCT OVERVIEW KS57C21116/C21124/C21132/P21132 MICROCONTROLLER

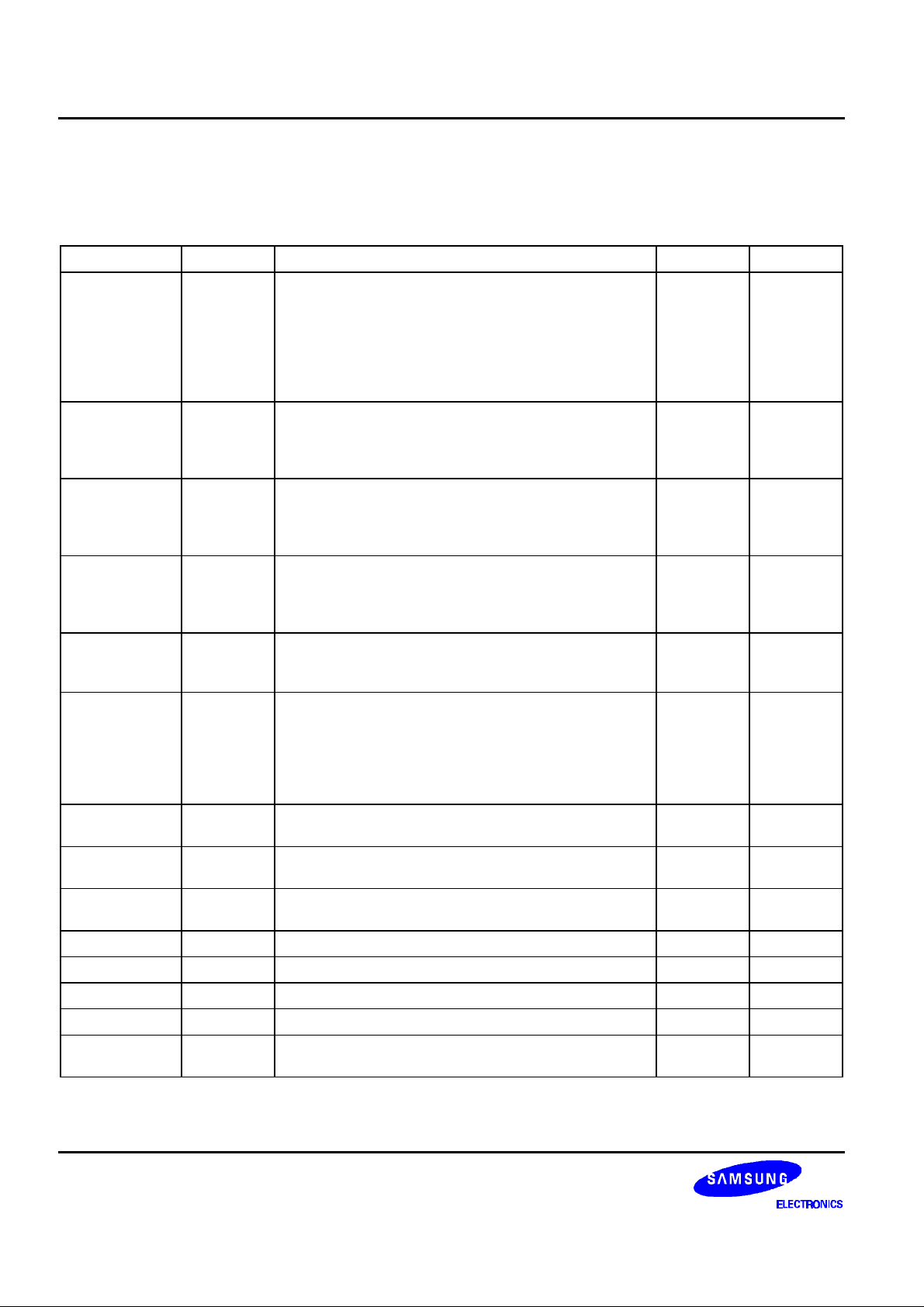

PIN DESCRIPTIONS

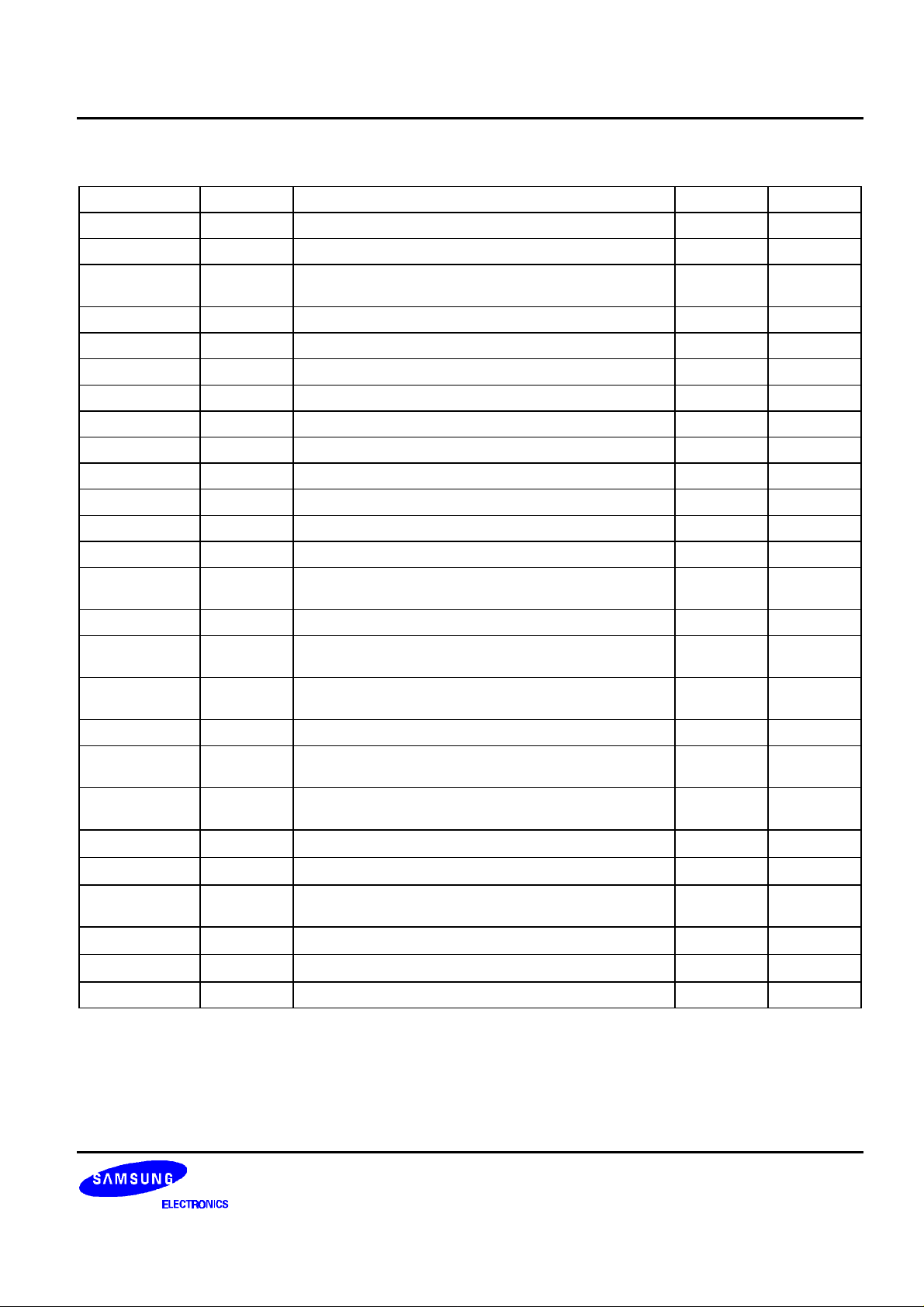

Table 1-1. KS57C21116/C21124/C21132 Pin Descriptions

Pin Name Pin Type Description Number Share Pin

P0.0

P0.1

P0.2

P0.3

P1.0

P1.1

P1.2

P1.3

P2.0

P2.1

P2.2

P2.3

P3.0

P3.1

P3.2

P3.3

P4.0

P4.1

P4.2

P6.0

P6.1

P6.2

P6.3

P7.0–P7.3

P8.0–P8.3

P9.0–P9.3

P10.0–P10.3

P11.0–P11.3

P12.0–P12.3

P13.0–P13.3

SCK

SO I/O Serial data output 17 P0.1

SI I/O Serial data input 18 P0.2

BUZ I/O 2, 4, 8, 16 kHz frequency output for buzzer sound 19 P0.3

K0–K3

K4–K7

I/O 4-bit I/O port.

1-bit and 4-bit read/write and test is possible.

4-bit unit pull-up resisters are assignable to input pins

by software and are automatically disabled for output

16

17

18

19

SCK/K0

SO/K1

SI/K2

BUZ/K3

pins. Each bit pin can be allocated as input or output

(1-bit unit). The N-ch open drain or push-pull output

may be selected by software (1-bit unit).

I 4-bit input port.

1-bit and 4-bit read and test is possible.

4-bit unit pull-up resistors are assignable to input pins

by software.

I/O 4-bit I/O port. 1-bit and 4-bit read/write and test is

possible. I/O function is same as port 0.

I/O 4-bit I/O port. 1-bit and 4-bit read/write and test is

possible. I/O function is same as port 0.

I/O 3-bit I/O port. I/O function is same as port 0 except

that port 4 is 3-bit I/O port.

I/O 4-bit I/O port. 1-, 4-bit and 8-bit read/write and test is

possible. 4-bit unit pull-up resisters are assignable to

input pins by software and are automatically disabled

for output pins. Each bit pin can be allocated as input

or output (1-bit unit). The N-ch open drain or push-

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47–50

INT0

INT1

INT2

INT4

M

LCDFR

CLO1

CLO2

TCLO0/CL

TCLO1

TCL0

TCL1

CIN0

CIN1

CIN2

K4/SEG79

K5/SEG78

K6/SEG77

K7/SEG76

SEG75–72

pull output may be selected by software (4-bit unit).

I/O 4-bit I/O port. 1-, 4-bit and 8-bit read/write and test is

possible. I/O function is same as port 6, 7.

I/O 4-bit I/O port. 1-, 4-bit and 8-bit read/write and test is

possible. I/O function is same as port 6, 7.

I/O 4-bit I/O port. 1-, 4-bit and 8-bit read/write and test is

possible. I/O function is same as port 6, 7.

51–54

55–58

59–62

63–66

67–70

71–74

SEG71–68

SEG67–64

SEG63–60

SEG59–56

SEG55–52

SEG51–48

I/O Serial I/O interface clock signal 16 P0.0

I/O External interrupts with rising/falling edge detection 16–19

43–46

P0.0–P0.3

P6.0–P6.3

1-10

KS57C21116/C21124/C21132/P21132 MICROCONTROLLER PRODUCT OVERVIEW

Table 1-1. KS57C21116/C21124/C21132 Pin Descriptions (Continued)

Pin Name Pin Type Description Number Share Pin

INT0 I External interrupts with rising/falling edge detection 28 P1.0

INT1 I External interrupts with rising/falling edge detection 29 P1.1

INT2 I External quasi-interrupts with rising/falling edge

30 P1.2

detection

INT4 I External interrupts with rising/falling edge detection 31 P1.3

M I/O Alternated signal for SEG driver 32 P2.0

LCDFR I/O Synchronous frame signal for SEG driver 33 P2.1

CLO1 I/O Clock output or operating clock for SEG driver 34 P2.2

CLO2 I/O Clock output or operating clock for SEG driver 35 P2.3

CL I/O Data shift clock for SEG driver 36 P3.0

TCLO0 I/O Timer/counter0 clock output 36 P3.0

TCLO1 I/O Timer/counter1 clock output 37 P3.1

TCL0 I/O External clock input for timer/counter 0 38 P3.2

TCL1 I/O External clock input for timer/counter 1 39 P3.3

CIN0–CIN2 I/O CIN0,1: comparator input only

CIN2: comparator input or external reference input

40, 41

42

P4.0–P4.1

P4.2

SEG0–SEG47 O LCD segment data output 122–75 –

SEG48–

O LCD segment data output 74–43 Port13–6

SEG79

SEG80–

SEG87

O LCD segment data output 2,1,

128–123

COM15–8

COM0–COM7 O LCD common data output 10–3 –

COM8–COM15 O LCD common data output 123–128

SEG87–80

1, 2

V

LC1–VLC5

– LCD power supply. Voltage dividing resistors are

15–11 –

fixed.

V

DD

V

SS

X

in, Xout

– Main power supply 20 –

– Ground 21 –

– Crystal, Ceramic, or RC oscillator signal I/O for main

23, 22 –

system clock.

XT

in, XTout

– Crystal oscillator signal I/O for subsystem clock. 25, 26 –

TEST I Test signal input (must be connected to VSS) 24 –

RESET

I Reset signal 27 –

NOTE: Pull-up resistors for all I/O ports are automatically disabled if they are configured to output mode.

1-11

PRODUCT OVERVIEW KS57C21116/C21124/C21132/P21132 MICROCONTROLLER

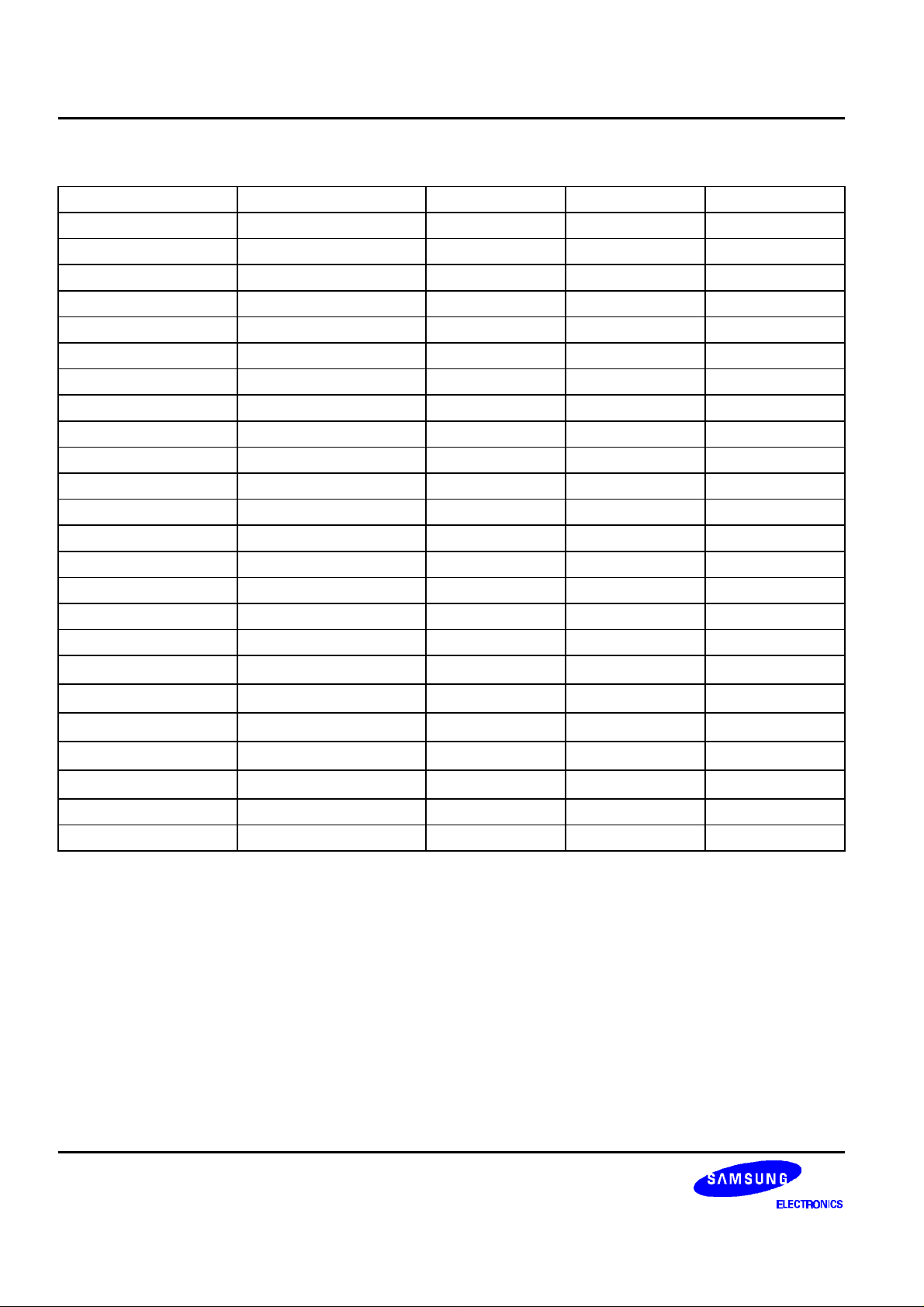

Table 1-2. Overview of KS57C21116/C21124/C21132 Pin Data

Pin Names Share Pins I/O Type Reset Value Circuit Type

P0.0–P0.3 SCK, SO, SI, BUZ/K0–K3 I/O Input E-2

P1.0–P1.3 INT0–INT2, INT4 I Input A-3

P2.0–P2.3 M, LCDFR, CLO1, CLO2 I/O Input E

P3.0–P3.1 TCLO0/CL, TCLO1 I/O Input E

P3.2–P3.3 TCL0, TCL1 I/O Input E-1

P4.0–P4.2 CIN0–CIN2 I/O Input F-4

P6.0–P6.3 K4–K7/SEG79–SEG76

I/O

Input

H-15

P7.0–P7.3 SEG75–SEG72 I/O Input H-8

P8.0–P8.3 SEG71–SEG68 I/O

Input

H-8

P9.0–P9.3 SEG67–SEG64 I/O Input H-8

P10.0–P10.3 SEG63–SEG60

I/O

Input

H-8

P11.0–P11.3 SEG59–SEG56 I/O Input H-8

P12.0–P12.3 SEG55–SEG52

I/O

Input

H-8

P13.0–P13.3 SEG51–SEG48 I/O Input H-8

COM0–COM7 – O Low output

H-4

COM8–COM15 SEG87–SEG80 O Low output H-6

SEG0–SEG47 – O Low output

V

LC1–VLC5

V

DD

V

SS

X

X

,

IN

OUT

XT

XT

,

IN

RESET

OUT

– – – –

– – – –

– – – –

– – – –

– – – –

– I – B

H-5

TEST – I – –

1-12

Loading...

Loading...