Samsung K9F1G16Q0M-YCB0, K9F1G16Q0M-PCB0, K9F1G08U0M-YIB0, K9F1G08U0M-YCB0, K9F1G08U0M-VIB0 Datasheet

...

March. 2003

ELECTRONICS

San 16 Banwol-Ri

Taean-Eup Hwasung- City

Kyungki Do, Korea

Tel.) 82 - 31 - 208 - 6463

Fax.) 82 - 31 -208 - 6799

Gb

11Gb

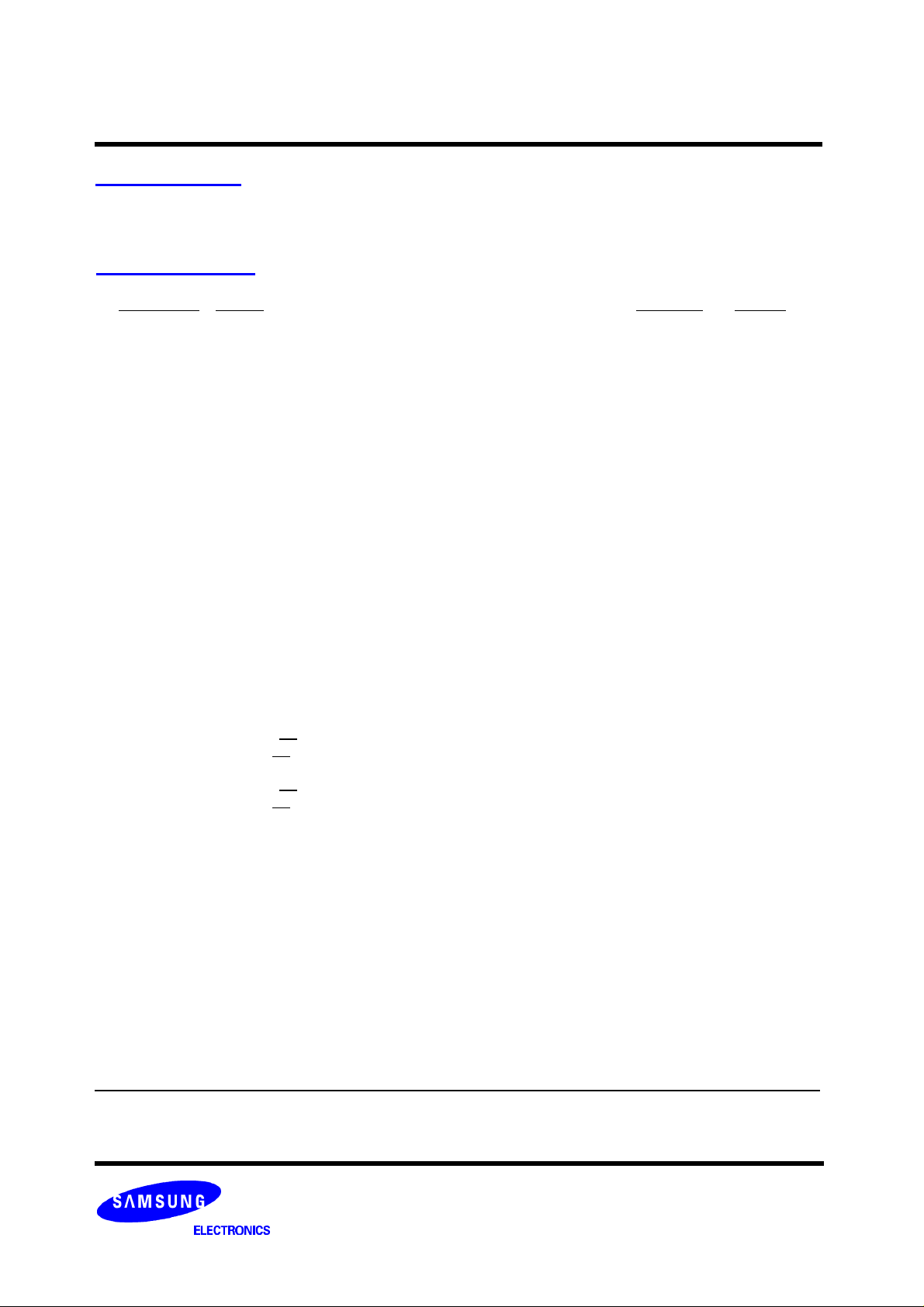

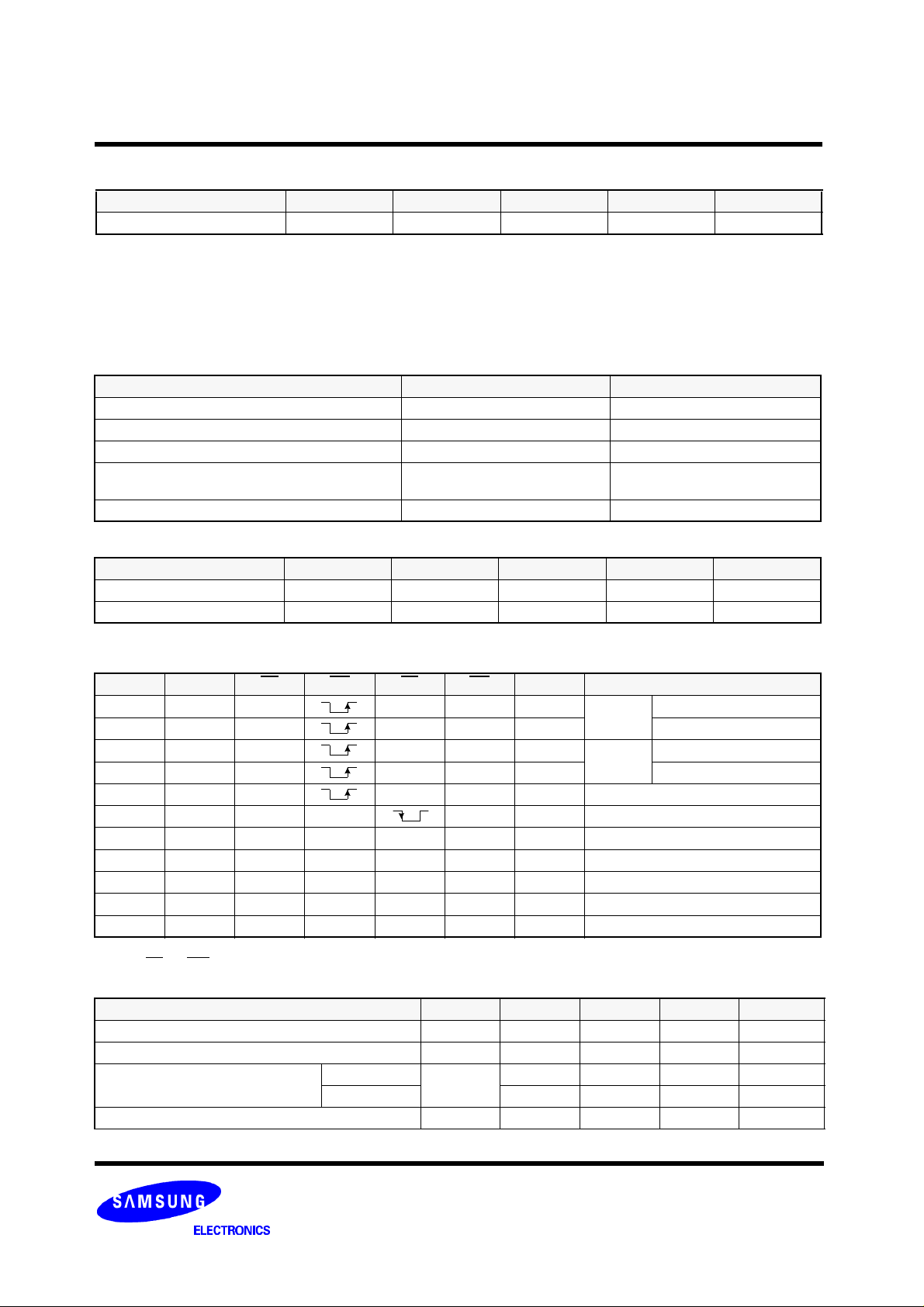

1.8V NAND Flash Errata

1.8V NAND Flash Errata

Description : Some of AC characteristics are not meeting the specification.

> AC characteristics : Refer to Table

Affected Products : K9F1G08Q0M-YCB0/YIB0, K9F1G16Q0M-YCB0/YIB0

K9K2G08Q0M-YCB0/YIB0, K9K2G16Q0M-YCB0/YIB0

Improvement schedule : The components targeted to meet the specification

is scheduled to be av ailable by workweek 25 along

with the final specification values.

Workaround : Relax the relevant timing parameters according to the table.

Table

Parameters

Specification

Relaxed Condition

Sincerely,

chwoosun@sec.samsung.com

Product Planning & Application Eng.

Memory Division

Samsung Electronics Co.

tWC

45

80

tWH

15

20

tWP

25

60

tRC

50

80

tREH

15

20

tRP

25

60

UNIT : ns

tREA

30

60

tCEA

45

75

1

K9F1G08U0M-VCB0,VIB0,FCB0,FIB0

K9F1G08Q0M-YCB0,YIB0,PCB0,PIB0 K9F1G16Q0M-YCB0,YIB0,PCB0,PIB0

K9F1G08U0M-YCB0,YIB0,PCB0,PIB0 K9F1G16U0M-YCB0,YIB0,PCB0,PIB0

Document Title

128M x 8 Bit / 64M x 16 Bit NAND Flash Memory

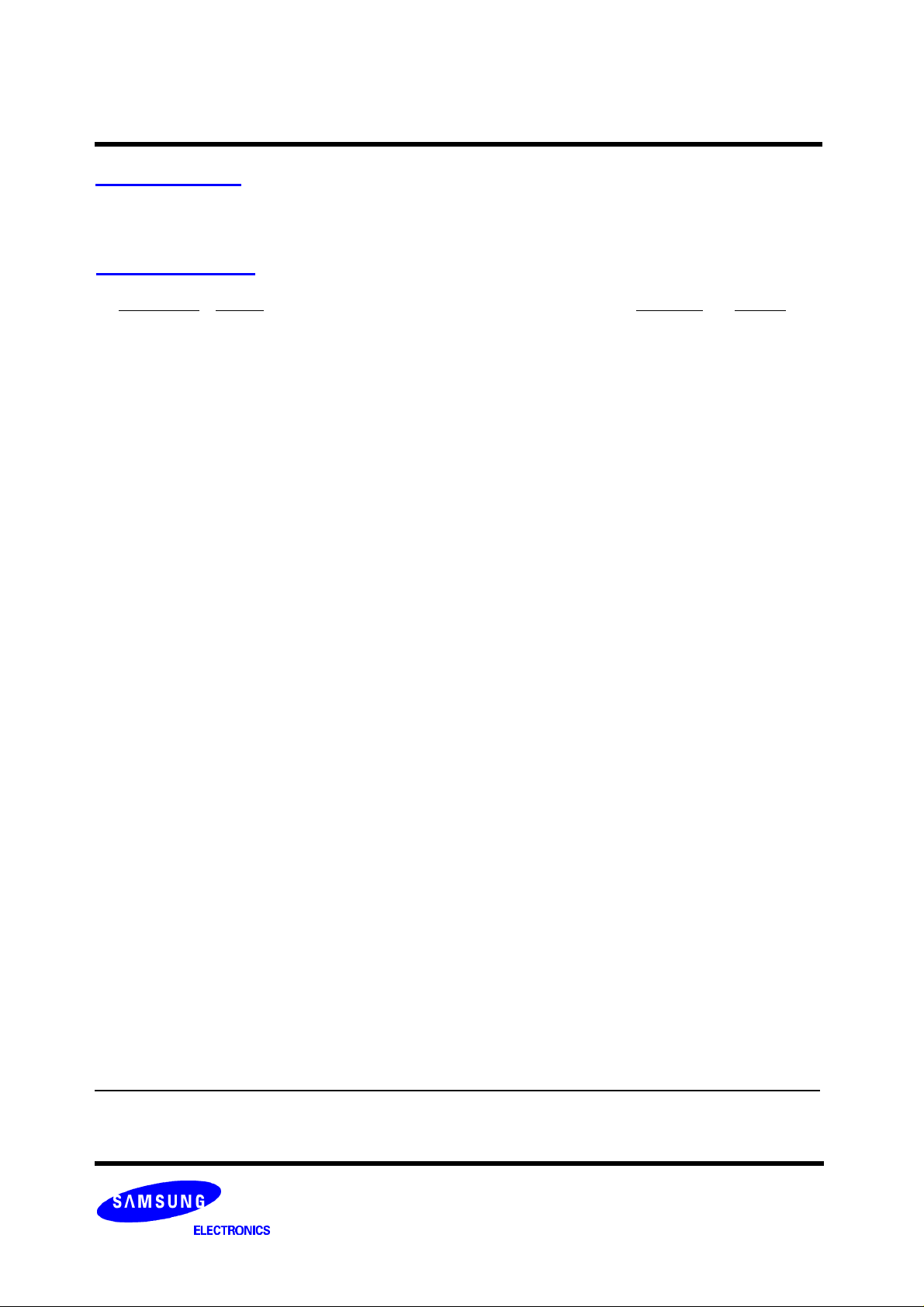

Revision History

FLASH MEMORY

Revision No

0.0

0.1

0.2

0.3

History

1. Initial issue

1. Iol(R/B) of 1.8V is changed.

- min. value : 7mA --> 3mA

- Typ. value : 8mA --> 4mA

2. AC parameter is changed.

tRP(min.) : 30ns --> 25ns

3. A recovery time of minimum 1µs is required before internal circuit gets

ready for any command sequences as shown in Figure 17.

---> A recovery time of minimum 10µs is required before internal circuit gets

ready for any command sequences as shown in Figure 17.

1. ALE status fault in ’Random data out in a page’ timing diagram(page 19)

is fixed.

1. tAR1, tAR2 are merged to tAR.(Page11)

(Before revision) min. tAR1 = 10ns , min. tAR2 = 50ns

(After revision) min. tAR = 10ns

2. min. tCLR is changed from 50ns to 10ns.(Page11)

3. min. tREA is changed from 35ns to 30ns.(Page11)

4. min. tWC is changed from 50ns to 45ns.(Page11)

5. tRHZ is devided into tRHZ and tOH.(Page11)

- tRHZ : RE High to Output Hi-Z

- tOH : RE High to Output Hold

6. tCHZ is devided into tCHZ and tOH.(Page11)

- tCHZ : CE High to Output Hi-Z

- tOH : CE High to Output Hold

Draft Date

July. 5. 2001

Nov. 5. 2001

Dec. 4. 2001

Apr. 25. 2002

Remark

Advance

0.4

0.5

0.6

1. Add the Rp vs tr ,tf & Rp vs ibusy graph for 1.8V device (Page 35)

2. Add the data protection Vcc guidence for 1.8V device - below about

1.1V. (Page 36)

The min. Vcc value 1.8V devices is changed.

K9F1GXXQ0M : Vcc 1.65V~1.95V --> 1.70V~1.95V

Pb-free Package is added.

K9F1G08U0M-FCB0,FIB0

K9F1G08Q0M-PCB0,PIB0

K9F1G08U0M-PCB0,PIB0

K9F1G16U0M-PCB0,PIB0

K9F1G16Q0M-PCB0,PIB0

Nov. 22.2002

Mar. 6.2003

Mar. 13.2003

The attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the

right to change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions about device. If you

have any questions, please contact the SAMSUNG branch office near your office.

SAMSUNG

1

K9F1G08U0M-VCB0,VIB0,FCB0,FIB0

K9F1G08Q0M-YCB0,YIB0,PCB0,PIB0 K9F1G16Q0M-YCB0,YIB0,PCB0,PIB0

K9F1G08U0M-YCB0,YIB0,PCB0,PIB0 K9F1G16U0M-YCB0,YIB0,PCB0,PIB0

Document Title

128M x 8 Bit / 64M x 16 Bit NAND Flash Memory

Revision History

FLASH MEMORY

Revision No

0.7

0.8

Errata is added.(Front Page)-K9F1GXXQ0M

tWC tWP tWH tRC tREH tRP tREA tCEA

Specification 45 25 15 50 15 25 30 45

Relaxed value 80 60 20 60 80 60 60 75

1. The 3rd Byte ID after 90h ID read command is don’t cared.

The 5th Byte ID after 90h ID read command is deleted.

Draft Date

Mar.17. 2003

Apr. 9. 2003

RemarkHistory

The attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the

right to change the specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions about device. If you

have any questions, please contact the SAMSUNG branch office near your office.

SAMSUNG

2

K9F1G08U0M-VCB0,VIB0,FCB0,FIB0

K9F1G08Q0M-YCB0,YIB0,PCB0,PIB0 K9F1G16Q0M-YCB0,YIB0,PCB0,PIB0

K9F1G08U0M-YCB0,YIB0,PCB0,PIB0 K9F1G16U0M-YCB0,YIB0,PCB0,PIB0

FLASH MEMORY

128M x 8 Bit / 64M x 16 Bit NAND Flash Memory

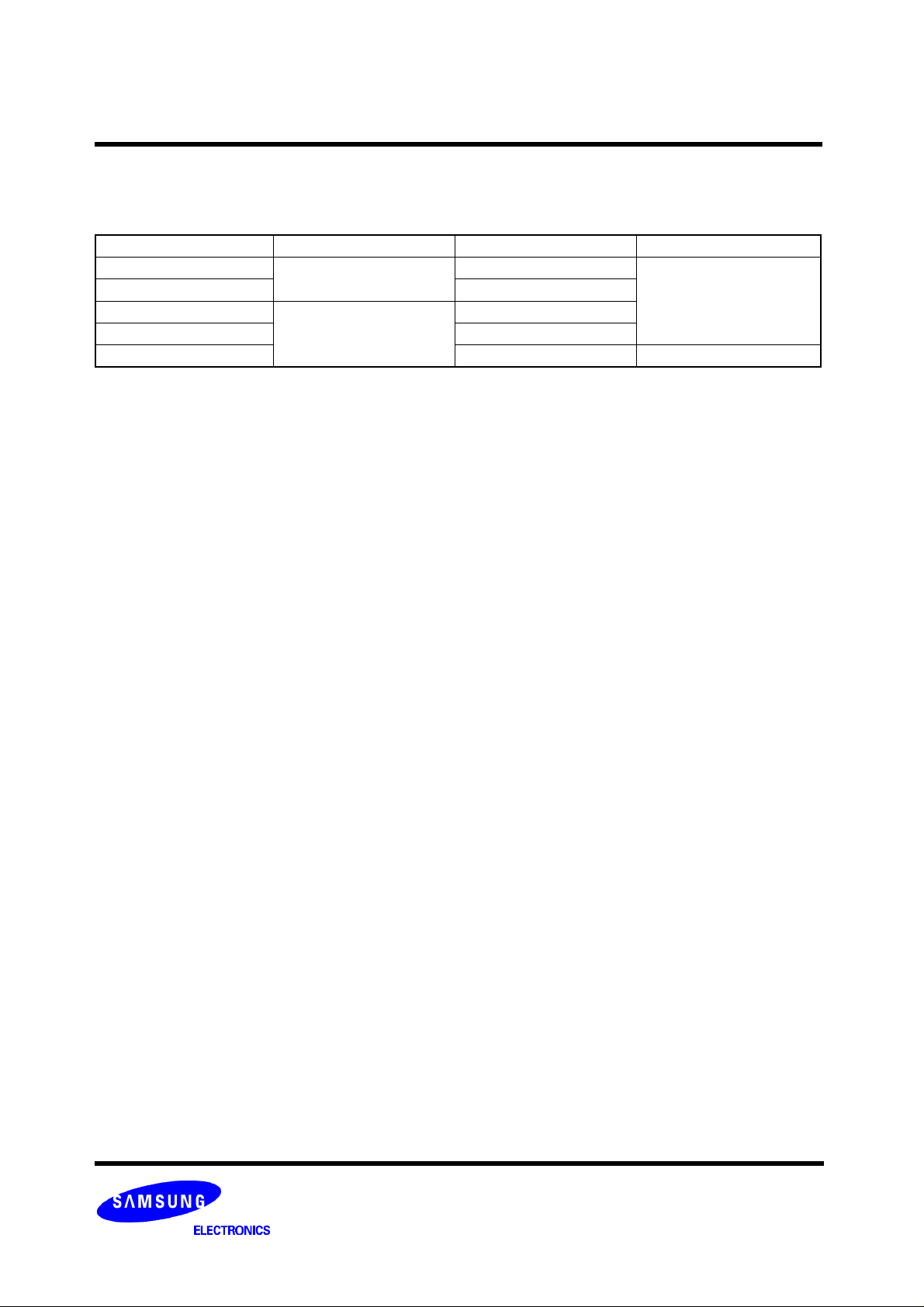

PRODUCT LIST

Part Number Vcc Range Organization PKG Type

K9F1G08Q0M-Y,P

K9F1G16Q0M-Y,P X16

K9F1G08U0M-Y,P

K9F1G16U0M-Y,P X16

K9F1G08U0M-V,F X8 WSOP1

1.70 ~ 1.95V

2.7 ~ 3.6V

FEATURES

X8

X8

TSOP1

• Voltage Supply

-1.8V device(K9F1GXXQ0M): 1.70V~1.95V

-3.3V device(K9F1GXXU0M): 2.7 V ~3.6 V

• Organization

- Memory Cell Array

-X8 device(K9F1G08X0M) : (128M + 4,096K)bit x 8bit

-X16 device(K9F1G16X0M) : (64M + 2,048K)bit x 16bit

- Data Register

-X8 device(K9F1G08X0M): (2K + 64)bit x8bit

-X16 device(K9F1G16X0M): (1K + 32)bit x16bit

- Cache Register

-X8 device(K9F1G08X0M): (2K + 64)bit x8bit

-X16 device(K9F1G16X0M): (1K + 32)bit x16bit

• Automatic Program and Erase

- Page Program

-X8 device(K9F1G08X0M): (2K + 64)Byte

-X16 device(K9F1G16X0M): (1K + 32)Word

- Block Erase

-X8 device(K9F1G08X0M): (128K + 4K)Byte

-X16 device(K9F1G16X0M): (64K + 2K)Word

• Page Read Operation

- Page Size

- X8 device(K9F1G08X0M): 2K-Byte

- X16 device(K9F1G16X0M) : 1K-Word

- Random Read : 25µs(Max.)

- Serial Access : 50ns(Min.)

• Fast Write Cycle Time

- Program time : 300µs(Typ.)

- Block Erase Time : 2ms(Typ.)

• Command/Address/Data Multiplexed I/O Port

• Hardware Data Protection

- Program/Erase Lockout During Power Transitions

• Reliable CMOS Floating-Gate Technology

- Endurance : 100K Program/Erase Cycles

- Data Retention : 10 Years

• Command Register Operation

• Cache Program Operation for High Performance Program

• Power-On Auto-Read Operation

• Intelligent Copy-Back Operation

• Unique ID for Copyright Protection

• Package :

- K9F1GXXX0M-YCB0/YIB0

48 - Pin TSOP I (12 x 20 / 0.5 mm pitch)

- K9F1G08U0M-VCB0/VIB0

48 - Pin WSOP I (12X17X0.7mm)

- K9F1GXXX0M-PCB0/PIB0

48 - Pin TSOP I (12 x 20 / 0.5 mm pitch)- Pb-free Package

- K9F1G08U0M-FCB0/FIB0

48 - Pin WSOP I (12X17X0.7mm)- Pb-free Package

* K9F1G08U0M-V,F(WSOPI ) is the same device as

K9F1G08U0M-Y,P(TSOP1) except package type.

GENERAL DESCRIPTION

Offered in 128Mx8bit or 64Mx16bit, the K9F1GXXX0M is 1G bit with spare 32M bit capacity. Its NAND cell provides the most costeffective solution for the solid state mass storage market. A program operation can be performed in typical 300µs on the 2112byte(X8 device) or 1056-word(X16 device) page and an erase operation can be performed in typical 2ms on a 128K-byte(X8 device)

or 64K-word(X16 device) block. Data in the data page can be read out at 50ns cycle time per byte. The I/O pins serve as the ports for

address and data input/output as well as command input. The on-chip write controller automates all program and erase functions

including pulse repetition, where required, and internal verification and margining of data. Even the write-intensive systems can take

advantage of the K9F1GXXX0M′s extended reliability of 100K program/erase cycles by providing ECC(Error Correcting Code) with

real time mapping-out algorithm. The K9F1GXXX0M is an optimum solution for large nonvolatile storage applications such as solid

state file storage and other portable applications requiring non-volatility.

SAMSUNG

3

K9F1G08U0M-VCB0,VIB0,FCB0,FIB0

K9F1G08Q0M-YCB0,YIB0,PCB0,PIB0 K9F1G16Q0M-YCB0,YIB0,PCB0,PIB0

K9F1G08U0M-YCB0,YIB0,PCB0,PIB0 K9F1G16U0M-YCB0,YIB0,PCB0,PIB0

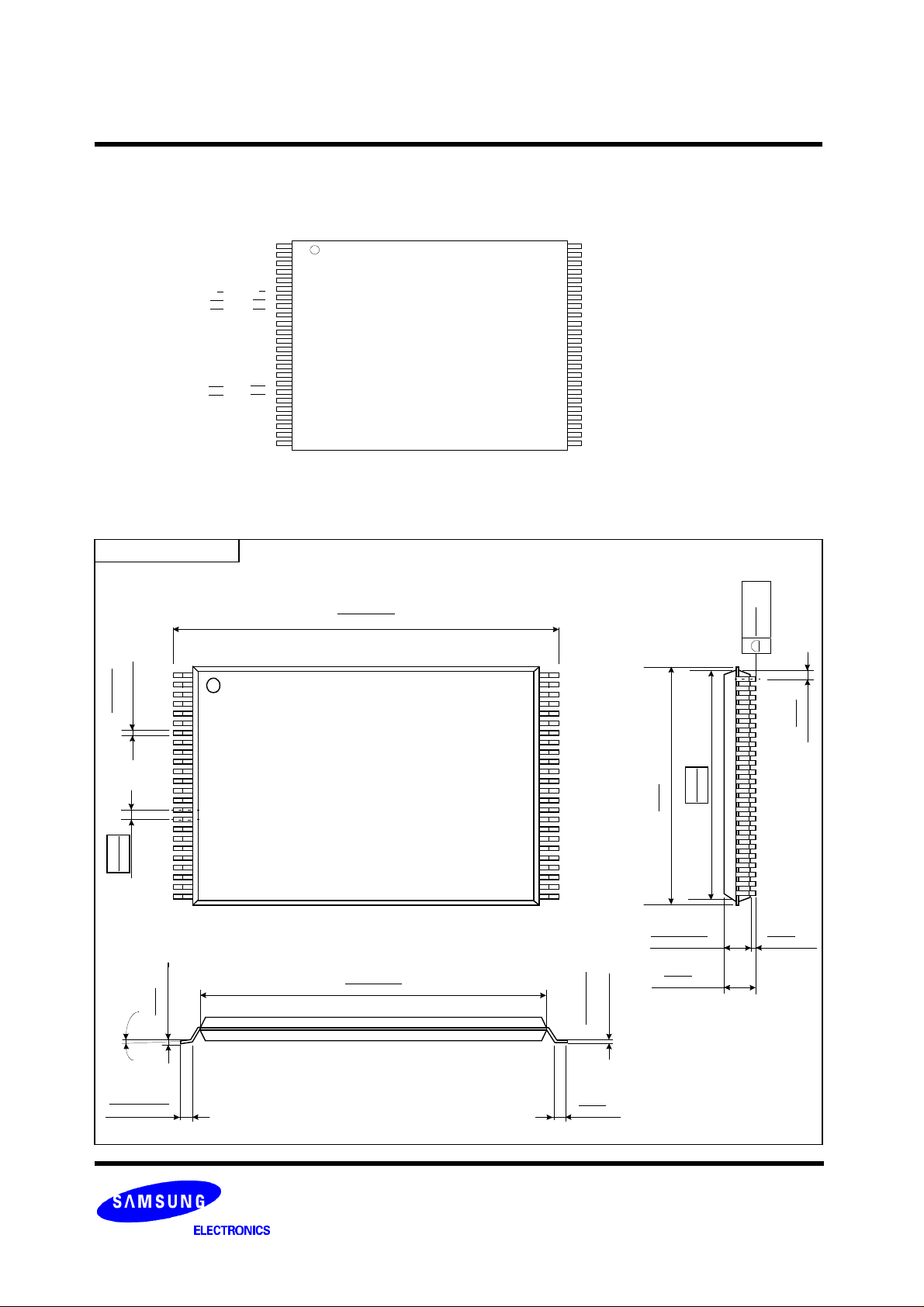

PIN CONFIGURATION (TSOP1)

K9F1GXXX0M-YCB0,PCB0/YIB0,PIB0

X8X16 X16X8

N.C

N.C

N.C

N.C

N.C

N.C

N.C

R/B

RE

N.C

N.C

Vcc

Vss

N.C

N.C

CLE

ALE

WE

WP

N.C

N.C

N.C

N.C

N.C

CE

N.C

N.C

N.C

N.C

N.C

N.C

R/B

RE

CE

N.C

N.C

Vcc

Vss

N.C

N.C

CLE

ALE

WE

WP

N.C

N.C

N.C

N.C

N.C

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48-pin TSOP1

Standard Type

12mm x 20mm

48

N.C

47

N.C

46

N.C

45

I/O7

44

I/O6

43

I/O5

42

I/O4

41

N.C

40

N.C

39

PRE

38

Vcc

37

Vss

36

N.C

35

N.C

34

N.C

33

I/O3

32

I/O2

31

I/O1

30

I/O0

29

N.C

28

N.C

27

N.C

26

N.C

25

PACKAGE DIMENSIONS

48-PIN LEAD/LEAD FREE PLASTIC THIN SMALL OUT-LINE PACKAGE TYPE(I)

FLASH MEMORY

Vss

I/O15

I/O7

I/O14

I/O6

I/O13

I/O5

I/O12

I/O4

N.C

PRE

Vcc

N.C

N.C

N.C

I/O11

I/O3

I/O10

I/O2

I/O9

I/O1

I/O8

I/O0

Vss

48 - TSOP1 - 1220F

#1

+0.003

-0.001

+0.07

-0.03

0.20

0.008

0.50

0.0197

#24

TYP

0.25

0.010

0~8¡Æ

20.00±0.20

0.787±0.008

18.40±0.10

0.724±0.004

#48

#25

Unit :mm/Inch

MAX

0.10

0.004

0.25

0.010

( )

MAX

12.00

0.472

0.488

12.40

1.00±0.05

0.039±0.002

1.20

MAX

+0.075

0.035

+0.003

-0.001

0.125

0.005

0.047

0.05

0.002

MIN

0.45~0.75

0.018~0.030

0.50

( )

0.020

SAMSUNG

4

K9F1G08U0M-VCB0,VIB0,FCB0,FIB0

K9F1G08Q0M-YCB0,YIB0,PCB0,PIB0 K9F1G16Q0M-YCB0,YIB0,PCB0,PIB0

K9F1G08U0M-YCB0,YIB0,PCB0,PIB0 K9F1G16U0M-YCB0,YIB0,PCB0,PIB0

FLASH MEMORY

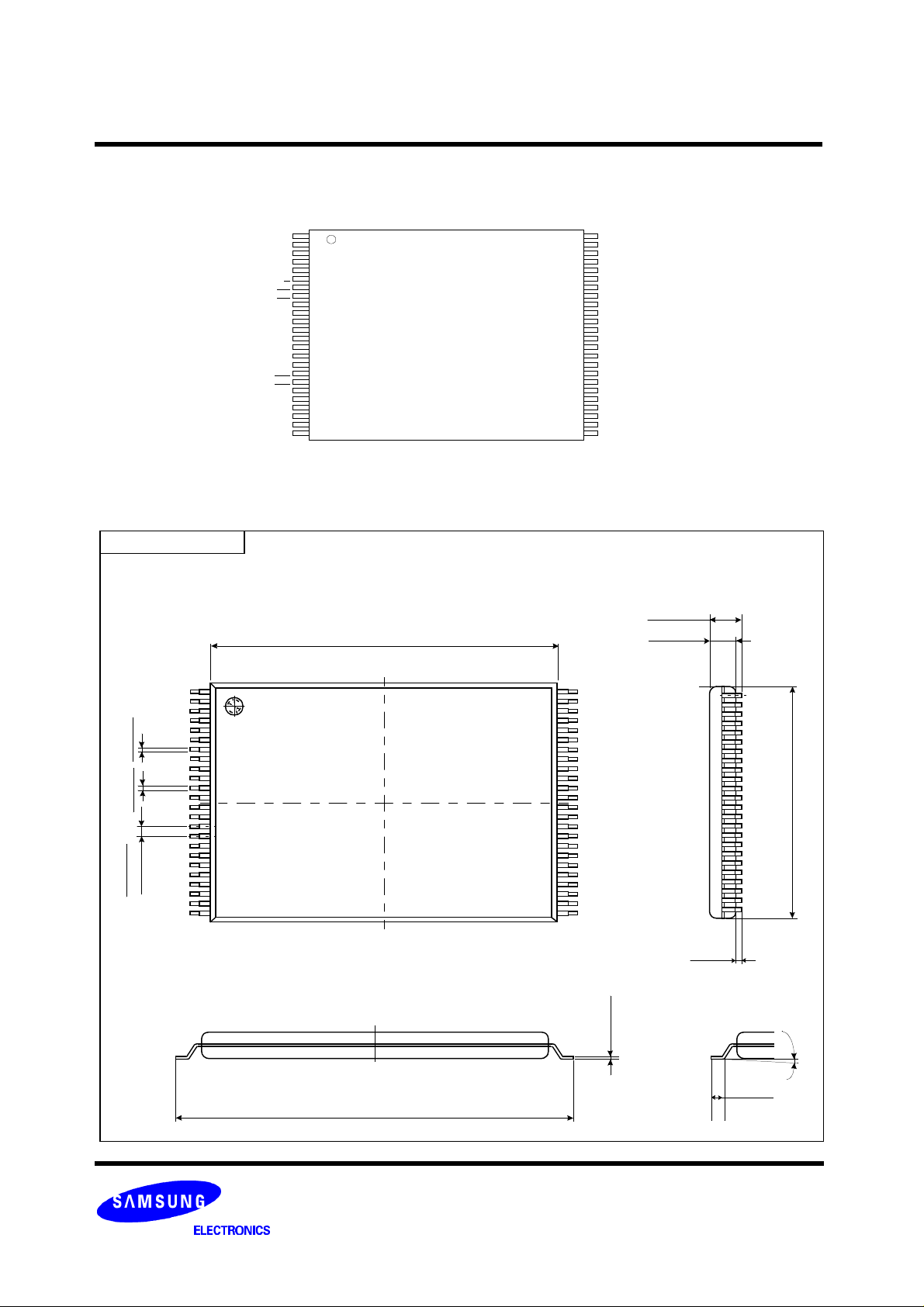

PIN CONFIGURATION (WSOP1)

K9F1G08U0M-VCB0,FCB0/VIB0,FIB0

N.C

N.C

N.C

DNU

N.C

N.C

N.C

R/B

RE

CE

DNU

N.C

Vcc

Vss

N.C

DNU

CLE

ALE

WE

WP

N.C

N.C

DNU

N.C

N.C

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

N.C

47

DNU

46

N.C

45

I/O7

44

I/O6

43

I/O5

42

I/O4

41

N.C

40

DNU

39

N.C

38

Vcc

37

Vss

36

N.C

35

DNU

34

N.C

33

I/O3

32

I/O2

31

I/O1

30

I/O0

29

N.C

28

DNU

27

N.C

26

N.C

25

PACKAGE DIMENSIONS

48-PIN LEAD/LEAD FREE PLASTIC VERY VERY THIN SMALL OUT-LINE PACKAGE TYPE (I)

48 - WSOP1 - 1217F

#1

+0.07

-0.03

0.16

+0.07

-0.03

0.20

0.50TYP

(0.50±0.06)

#24

15.40±0.10

Unit :mm

0.70 MAX

0.58±0.04

#48

12.00±0.10

#25

(0.1Min)

17.00±0.20

+0.075

-0.035

0.10

0

°

~

8

°

0.45~0.75

SAMSUNG

5

K9F1G08U0M-VCB0,VIB0,FCB0,FIB0

K9F1G08Q0M-YCB0,YIB0,PCB0,PIB0 K9F1G16Q0M-YCB0,YIB0,PCB0,PIB0

K9F1G08U0M-YCB0,YIB0,PCB0,PIB0 K9F1G16U0M-YCB0,YIB0,PCB0,PIB0

PIN DESCRIPTION

Pin Name Pin Function

DATA INPUTS/OUTPUTS

I/O0 ~ I/O7

(K9F1G08X0M)

I/O0 ~ I/O15

(K9F1G16X0M)

The I/O pins are used to input command, address and data, and to output data during read operations. The I/

O pins float to high-z when the chip is deselected or when the outputs are disabled.

I/O8 ~ I/O15 are used only in X16 organization device. Since command input and address input are x8 operation, I/O8 ~ I/O15 are not used to input command & address. I/O8 ~ I/O15 are used only for data input and

output.

FLASH MEMORY

CLE

ALE

CE

RE

WE

WP

R/B

PRE

COMMAND LATCH ENABLE

The CLE input controls the activating path for commands sent to the command register. When active high,

commands are latched into the command register through the I/O ports on the rising edge of the WE signal.

ADDRESS LATCH ENABLE

The ALE input controls the activating path for address to the internal address registers. Addresses are

latched on the rising edge of WE with ALE high.

CHIP ENABLE

The CE input is the device selection control. When the device is in the Busy state, CE high is ignored, and

the device does not return to standby mode.

READ ENABLE

The RE input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid

tREA after the falling edge of RE which also increments the internal column address counter by one.

WRITE ENABLE

The WE input controls writes to the I/O port. Commands, address and data are latched on the rising edge of

the WE pulse.

WRITE PROTECT

The WP pin provides inadvertent write/erase protection during power transitions. The internal high voltage

generator is reset when the WP pin is active low.

READY/BUSY OUTPUT

The R/B output indicates the status of the device operation. When low, it indicates that a program, erase or

random read operation is in process and returns to high state upon completion. It is an open drain output and

does not float to high-z condition when the chip is deselected or when outputs are disabled.

POWER-ON READ ENABLE

The PRE controls auto read operation executed during power-on. The power-on auto-read is enabled when

PRE pin is tied to Vcc.

Vcc

Vss GROUND

N.C

POWER

VCC is the power supply for device.

NO CONNECTION

Lead is not internally connected.

NOTE : Connect all VCC and VSS pins of each device to common power supply outputs.

Do not leave VCC or VSS disconnected.

SAMSUNG

6

K9F1G08U0M-VCB0,VIB0,FCB0,FIB0

K9F1G08Q0M-YCB0,YIB0,PCB0,PIB0 K9F1G16Q0M-YCB0,YIB0,PCB0,PIB0

K9F1G08U0M-YCB0,YIB0,PCB0,PIB0 K9F1G16U0M-YCB0,YIB0,PCB0,PIB0

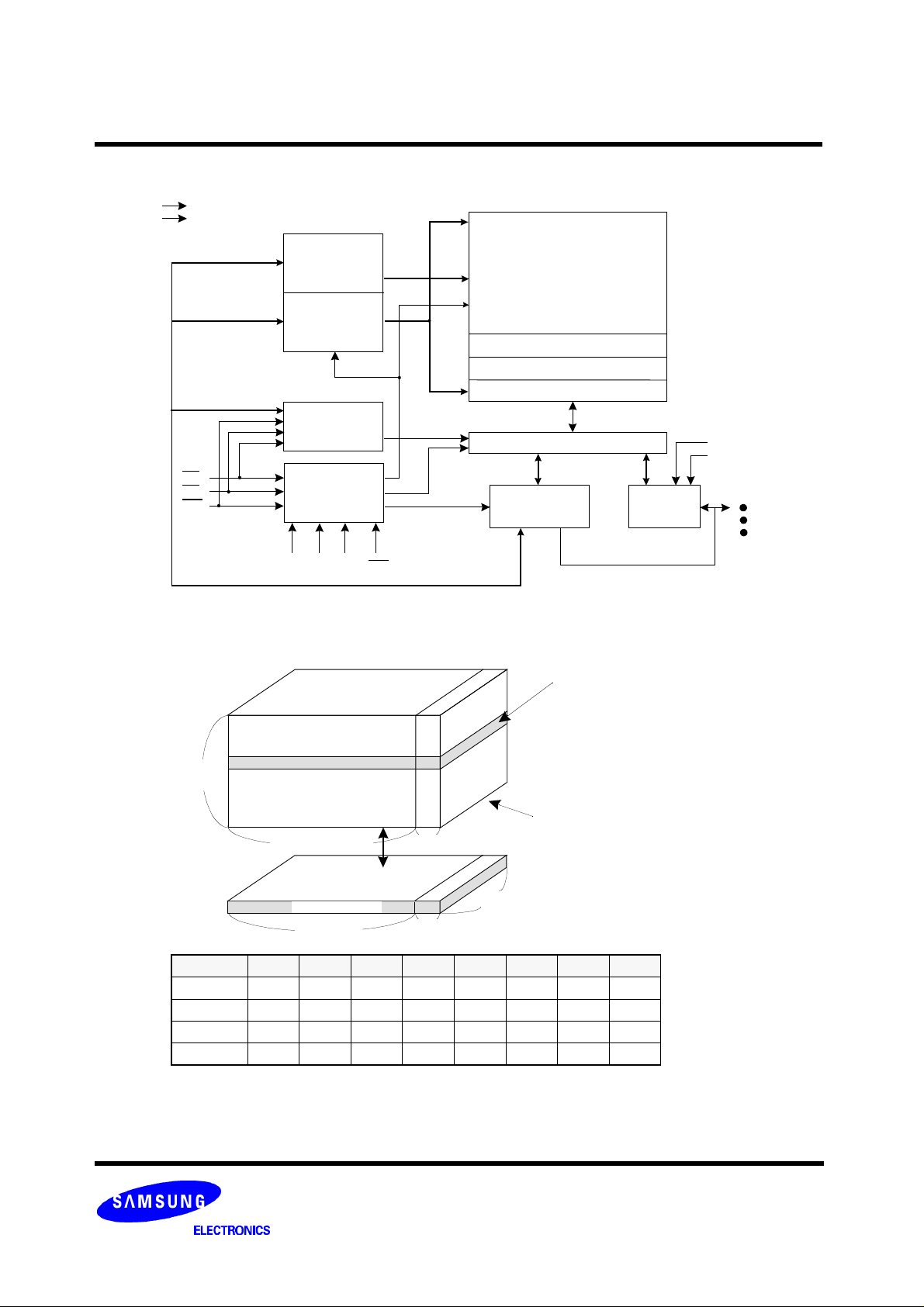

Figure 1-1. K9F1G08X0M (X8) Functional Block Diagram

VCC

VSS

FLASH MEMORY

A12 - A27

A0 - A11

Command

CE

RE

WE

X-Buffers

Latches

& Decoders

Y-Buffers

Latches

& Decoders

Command

Register

Control Logic

& High Voltage

Generator

CLE

ALE PRE

WP

Figure 2-1. K9F1G08X0M (X8) Array Organization

1024M + 32M Bit

NAND Flash

ARRAY

(1024 + 32)Byte x 65536

Data Register & S/A

Cache Register

Y-Gating

I/O Buffers & Latches

Global Buffers

1 Block = 64 Pages

(128K + 4k) Byte

Output

Driver

VCC

VSS

I/0 0

I/0 7

64K Pages

(=1,024 Blocks)

2K Bytes 64 Bytes

Page Register

2K Bytes

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7

1st Cycle A0 A1 A2 A3 A4 A5 A6 A7

2nd Cycle A8 A9 A10 A11 *L *L *L *L

3rd Cycle A12 A13 A14 A15 A16 A17 A18 A19

4th Cycle A20 A21 A22 A23 A24 A25 A26 A27

NOTE : Column Address : Starting Address of the Register.

* L must be set to "Low".

* The device ignores any additional input of address cycles than reguired.

1 Page = (2K + 64)Bytes

1 Block = (2K + 64)B x 64 Pages

= (128K + 4K) Bytes

1 Device = (2K+64)B x 64Pages x 1024 Blocks

= 1056 Mbits

8 bit

I/O 0 ~ I/O 7

64 Bytes

Column Address

Column Address

Row Address

Row Address

SAMSUNG

7

K9F1G08U0M-VCB0,VIB0,FCB0,FIB0

K9F1G08Q0M-YCB0,YIB0,PCB0,PIB0 K9F1G16Q0M-YCB0,YIB0,PCB0,PIB0

K9F1G08U0M-YCB0,YIB0,PCB0,PIB0 K9F1G16U0M-YCB0,YIB0,PCB0,PIB0

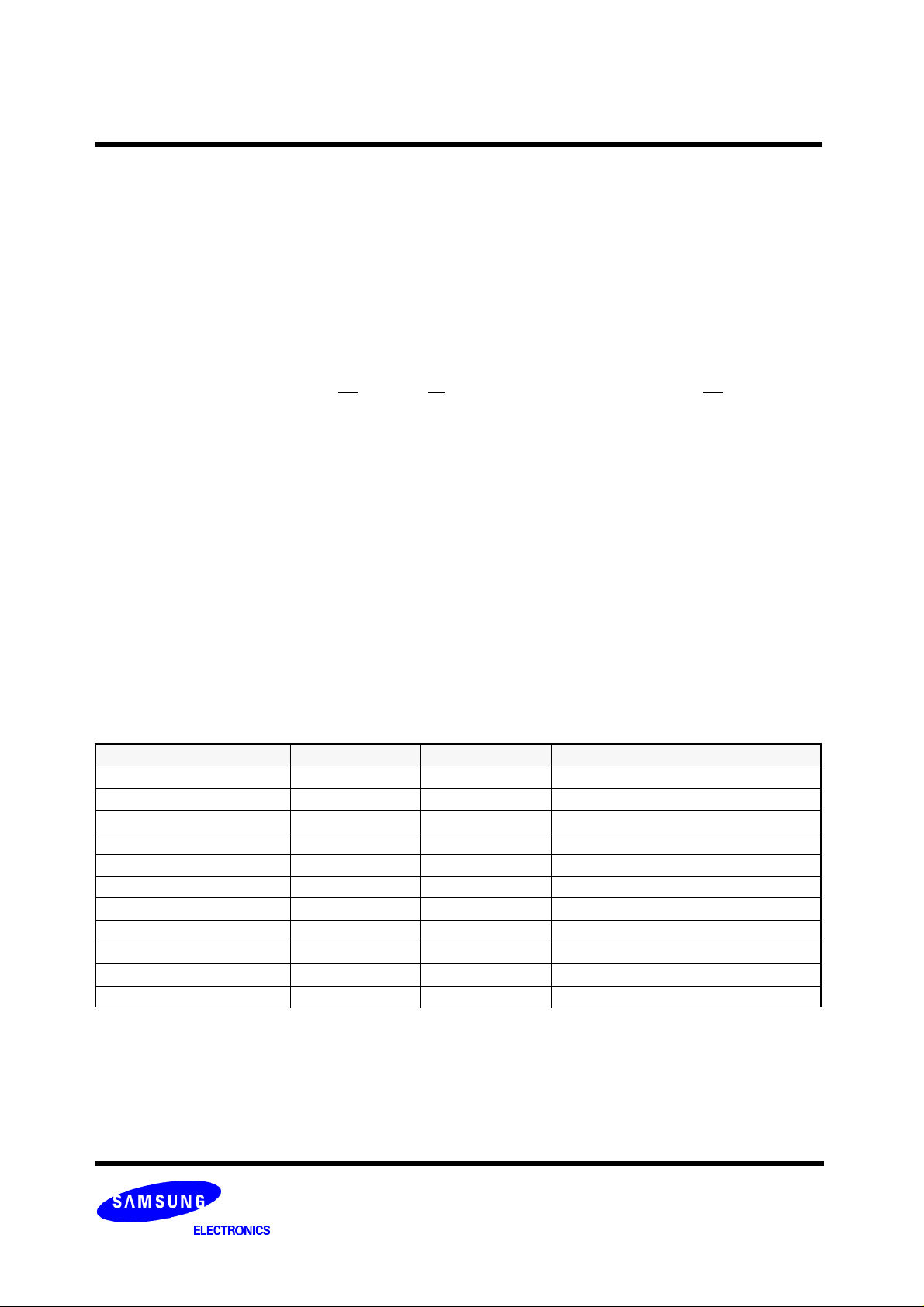

Figure 1-2. K9F1G16X0M (X16) Functional Block Diagram

VCC

VSS

FLASH MEMORY

A11 - A26

A0 - A10

Command

CE

RE

WE

X-Buffers

Latches

& Decoders

Y-Buffers

Latches

& Decoders

Command

Register

Control Logic

& High Voltage

Generator

CLE

ALE PRE

WP

Figure 2-2. K9F1G16X0M (X16) Array Organization

1024M + 32M Bit

NAND Flash

ARRAY

(512 + 64)Word x 65536

Data Register & S/A

Cache Register

Y-Gating

I/O Buffers & Latches

Global Buffers

1 Block = 64 Pages

(64K + 2k) Word

Output

Driver

VCC

VSS

I/0 0

I/0 15

1 Page = (1K + 32)Words

64K Pages

(=1,024 Blocks)

1K Words 32 Words

Page Register

1K Words

I/O 0 I/O 1 I/O 2 I/O 3 I/O 4 I/O 5 I/O 6 I/O 7 I/O8 ~ 15

1st Cycle A0 A1 A2 A3 A4 A5 A6 A7 *L

2nd Cycle A8 A9 A10 *L *L *L *L *L *L

3rd Cycle A11 A12 A13 A14 A15 A16 A17 A18 *L

4th Cycle A19 A20 A21 A22 A23 A24 A25 A26 *L

NOTE : Column Address : Starting Address of the Register.

* L must be set to "Low".

32 Words

I/O 0 ~ I/O 15

1 Block = (1K + 32)Word x 64 Pages

= (64K + 2K) Words

1 Device = (1K+32)Word x 64Pages x 1024 Blocks

= 1056 Mbits

16 bit

8

Column Address

Column Address

Row Address

Row Address

SAMSUNG

K9F1G08U0M-VCB0,VIB0,FCB0,FIB0

K9F1G08Q0M-YCB0,YIB0,PCB0,PIB0 K9F1G16Q0M-YCB0,YIB0,PCB0,PIB0

K9F1G08U0M-YCB0,YIB0,PCB0,PIB0 K9F1G16U0M-YCB0,YIB0,PCB0,PIB0

FLASH MEMORY

Product Introduction

The K9F1GXXX0M is a 1056Mbit(1,107,296,256 bit) memory organized as 65,536 rows(pages) by 2112x8(X8 device) or

1056x16(X16 device) columns. Spare 64(X8) or 32(X16) columns are located from column address of 2048~2111(X8 device) or

1024~1055(X16 device). A 2112-byte(X8 device) or 1056-word(X16 device) data register and a 2112-byte(X8 device) or 1056word(X16 device) cache register are serially connected to each other. Those serially connected registers are connected to memory

cell arrays for accommodating data transfer between the I/O buffers and memory cells during page read and page program operations. The memory array is made up of 32 cells that are serially connected to form a NAND structure. Each of the 32 cells resides in

a different page. A block consists of the 64 pages formed by two NAND structures, totaling 33792 NAND structures of 32 cells. The

program and read operations are executed on a page basis, while the erase operation is executed on a block basis. The memory

array consists of 1024 separately erasable 128K-byte(X8 device) or 64K-word(X16 device) blocks. It indicates that the bit by bit

erase operation is prohibited on the K9F1GXXX0M.

The K9F1GXXX0M has addresses multiplexed into 8 I/Os(X16 device case : lower 8 I/Os). This scheme dramatically reduces pin

counts and allows system upgrades to future densities by maintaining consistency in system board design. Command, address and

data are all written through I/O's by bringing WE to low while CE is low. Those are latched on the rising edge of WE. Command Latch

Enable(CLE) and Address Latch Enable(ALE) are used to multiplex command and address respectively, via the I/O pins. Some commands require one bus cycle. For example, Reset Command, Status Read Command, etc require just one cycle bus. Some other

commands, like page read and block erase and page program, require two cycles: one cycle for setup and the other cycle for execution. The 128M byte(X8 device) or 64M word(X16 device) physical space requires 28(X8) or 27(X16) addresses, thereby requiring

four cycles for addressing: 2 cycles of column address, 2 cycles of row address, in that order. Page Read and Page Program need

the same four address cycles following the required command input. In Block Erase operation, however, only the two row address

cycles are used. Device operations are selected by writing specific commands into the command register. Table 1 defines the specific commands of the K9F1GXXX0M.

The device provides cache program in a block. It is possible to write data into the cache registers while data stored in data registers

are being programmed into memory cells in cache program mode. The program performace may be dramatically improved by cache

program when there are lots of pages of data to be programmed.

The device embodies power-on auto-read feature which enables serial access of data of the 1st page without command and address

input after power-on.

In addition to the enhanced architecture and interface, the device incorporates copy-back program feature from one page to another

page without need for transporting the data to and from the external buffer memory. Since the time-consuming serial access and

data-input cycles are removed, system performance for solid-state disk application is significantly increased.

Table 1. Command Sets

Function 1st. Cycle 2nd. Cycle Acceptable Command during Busy

Read 00h 30h

Read for Copy Back 00h 35h

Read ID 90h Reset FFh - O

Page Program 80h 10h

Cache Program 80h 15h

Copy-Back Program 85h 10h

Block Erase 60h D0h

Random Data Input

Random Data Output

Read Status 70h O

*

*

85h 05h E0h

NOTE : 1. Random Data Input/Output can be executed in a page.

2. Command not specified in command sets table is not permitted to be entered to the device, which can raise erroneous operation.

Caution : Any undefined command inputs are prohibited except for above command set of Table 1.

SAMSUNG

9

K9F1G08U0M-VCB0,VIB0,FCB0,FIB0

K9F1G08Q0M-YCB0,YIB0,PCB0,PIB0 K9F1G16Q0M-YCB0,YIB0,PCB0,PIB0

K9F1G08U0M-YCB0,YIB0,PCB0,PIB0 K9F1G16U0M-YCB0,YIB0,PCB0,PIB0

FLASH MEMORY

ABSOLUTE MAXIMUM RATINGS

Parameter Symbol

Voltage on any pin relative to VSS

Temperature Under Bias

Storage Temperature

Short Circuit Current Ios 5 mA

NOTE :

1. Minimum DC voltage is -0.6V on input/output pins. During transitions, this level may undershoot to -2.0V for periods <30ns.

Maximum DC voltage on input/output pins is VCC,+0.3V which, during transitions, may overshoot to VCC+2.0V for periods <20ns.

2. Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions

as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

K9F1GXXX0M-XCB0

K9F1GXXX0M-XIB0 -40 to +125

K9F1GXXX0M-XCB0

K9F1GXXX0M-XIB0

VIN/OUT -0.6 to + 2.45 -0.6 to + 4.6

VCC -0.2 to + 2.45 -0.6 to + 4.6

TBIAS

TSTG -65 to +150 °C

K9F1GXXQ0M(1.8V) K9F1GXXU0M(3.3V)

Rating

-10 to +125

Unit

V

°C

RECOMMENDED OPERATING CONDITIONS

(Voltage reference to GND, K9F1GXXX0M-XCB0 :TA=0 to 70°C, K9F1GXXX0M-XIB0:TA=-40 to 85°C)

Parameter Symbol

Supply Voltage VCC 1.70 1.8 1.95 2.7 3.3 3.6 V

Supply Voltage VSS 0 0 0 0 0 0 V

K9F1GXXQ0M(1.8V)

Min Typ. Max Min Typ. Max

K9F1GXXU0M(3.3V)

Unit

DC AND OPERATING CHARACTERISTICS(Recommended operating conditions otherwise noted.)

Parameter Symbol Test Conditions

Operat-

Current

Stand-by Current(TTL) ISB1 CE=VIH, WP=PRE=0V/VCC - - 1 - - 1

Stand-by Current(CMOS) ISB2

Input Leakage Current ILI VIN=0 to Vcc(max) - - ±20 - - ±20

Output Leakage Current ILO VOUT=0 to Vcc(max) - - ±20 - - ±20

Input High Voltage VIH - VCC-0.4 -

Input Low Voltage, All inputs VIL - -0.3 - 0.4 -0.3 - 0.8

Output High Voltage Level VOH

Output Low Voltage Level

Output Low Current(R/B) IOL(R/B)

Page Read with

Serial Access

ing

Program ICC2 - - 5 15 - 10 20

Erase ICC3 - - 5 15 - 10 20

tRC=50ns, CE=VIL

ICC1

IOUT=0mA

CE=VCC-0.2,

WP=PRE=0V/VCC

K9F1GXXQ0M :IOH=-100µA

K9F1GXXU0M :IOH=-400µA

K9F1GXXQ0M :IOL=100uA

VOL

K9F1GXXU0M :IOL=2.1mA

K9F1GXXQ0M :VOL=0.1V

K9F1GXXU0M :VOL=0.4V

K9F1GXXQ0M(1.8V) K9F1GXXU0M(3.3V) Unit

Min Typ Max Min Typ Max

- 5 15 - 10 20

- 20 100 - 20 100

VCC+

Vcc-0.1 - - 2.4 - -

- - 0.1 - - 0.4

3 4 - 8 10 - mA

2.0 - VCC+0.3

0.3

mA

µA

V

10

SAMSUNG

K9F1G08U0M-VCB0,VIB0,FCB0,FIB0

K9F1G08Q0M-YCB0,YIB0,PCB0,PIB0 K9F1G16Q0M-YCB0,YIB0,PCB0,PIB0

K9F1G08U0M-YCB0,YIB0,PCB0,PIB0 K9F1G16U0M-YCB0,YIB0,PCB0,PIB0

FLASH MEMORY

VALID BLOCK

Parameter Symbol Min Typ. Max Unit

Valid Block Number NVB 1004 - 1024 Blocks

NOTE :

1. The K9F1GXXX0M may include invalid blocks when first shipped. Additional invalid blocks may develop while being used. The number of valid

blocks is presented with both cases of invalid blocks considered. Invalid blocks are defined as blocks that contain one or more bad bits. Do not erase

or program factory-marked bad blocks. Refer to the attached technical notes for appropriate management of invalid blocks.

2. The 1st block, which is placed on 00h block address, is fully guaranteed to be a valid block and does not require Error Correction.

AC TEST CONDITION

(K9F1GXXX0M-XCB0 :TA=0 to 70°C, K9F1GXXX0M-XIB0:TA=-40 to 85°C

K9F1GXXQ0M : Vcc=1.70V~1.95V, K9F1GXXU0M : Vcc=2.7V~3.6V unless otherwise noted)

Parameter K9F1GXXQ0M K9F1GXXU0M

Input Pulse Levels 0V to Vcc 0.4V to 2.4V

Input Rise and Fall Times 5ns 5ns

Input and Output Timing Levels Vcc/2 1.5V

K9F1GXXQ0M:Output Load (Vcc:1.8V +/-10%)

K9F1GXXU0M:Output Load (Vcc:3.0V +/-10%)

K9F1GXXU0M:Output Load (Vcc:3.3V +/-10%) - 1 TTL GATE and CL=100pF

1 TTL GATE and CL=30pF 1 TTL GATE and CL=50pF

CAPACITANCE(TA=25°C, VCC=1.8V/3.3V, f=1.0MHz)

Item Symbol Test Condition Min Max Unit

Input/Output Capacitance CI/O VIL=0V - 10 pF

Input Capacitance CIN VIN=0V - 10 pF

NOTE : Capacitance is periodically sampled and not 100% tested.

MODE SELECTION

CLE ALE CE WE RE WP PRE Mode

H L L H X X

L H L H X X Address Input(4clock)

H L L H H X

L H L H H X Address Input(4clock)

L L L H H X Data Input

L L L H X X Data Output

X X X X H X X During Read(Busy)

X X X X X H X During Program(Busy)

X X X X X H X During Erase(Busy)

X

X X H X X

NOTE : 1. X can be VIL or VIH.

2. WP and PRE should be biased to CMOS high or CMOS low for standby.

(1)

X

X X X L X Write Protect

(2)

0V/VCC

0V/VCC

Read Mode

Write Mode

(2)

Stand-by

Command Input

Command Input

Program / Erase Characteristics

Parameter Symbol Min Typ Max Unit

Program Time tPROG - 300 700 µs

Dummy Busy Time for Cache Program tCBSY 3 700

Number of Partial Program Cycles

in the Same Page

Block Erase Time tBERS - 2 3 ms

NOTE : 1. Max. time of tCBSY depends on timing between internal program completion and data in

Main Array

Spare Array - - 4 cycles

Nop

- - 4 cycles

µs

11

SAMSUNG

Loading...

Loading...