SAMSUNG K7N163601A Technical data

查询DS_K7N163601A供应商

K7N163601A

K7N161801A

Document Title

512Kx36 & 1Mx18-Bit Pipelined NtRAM

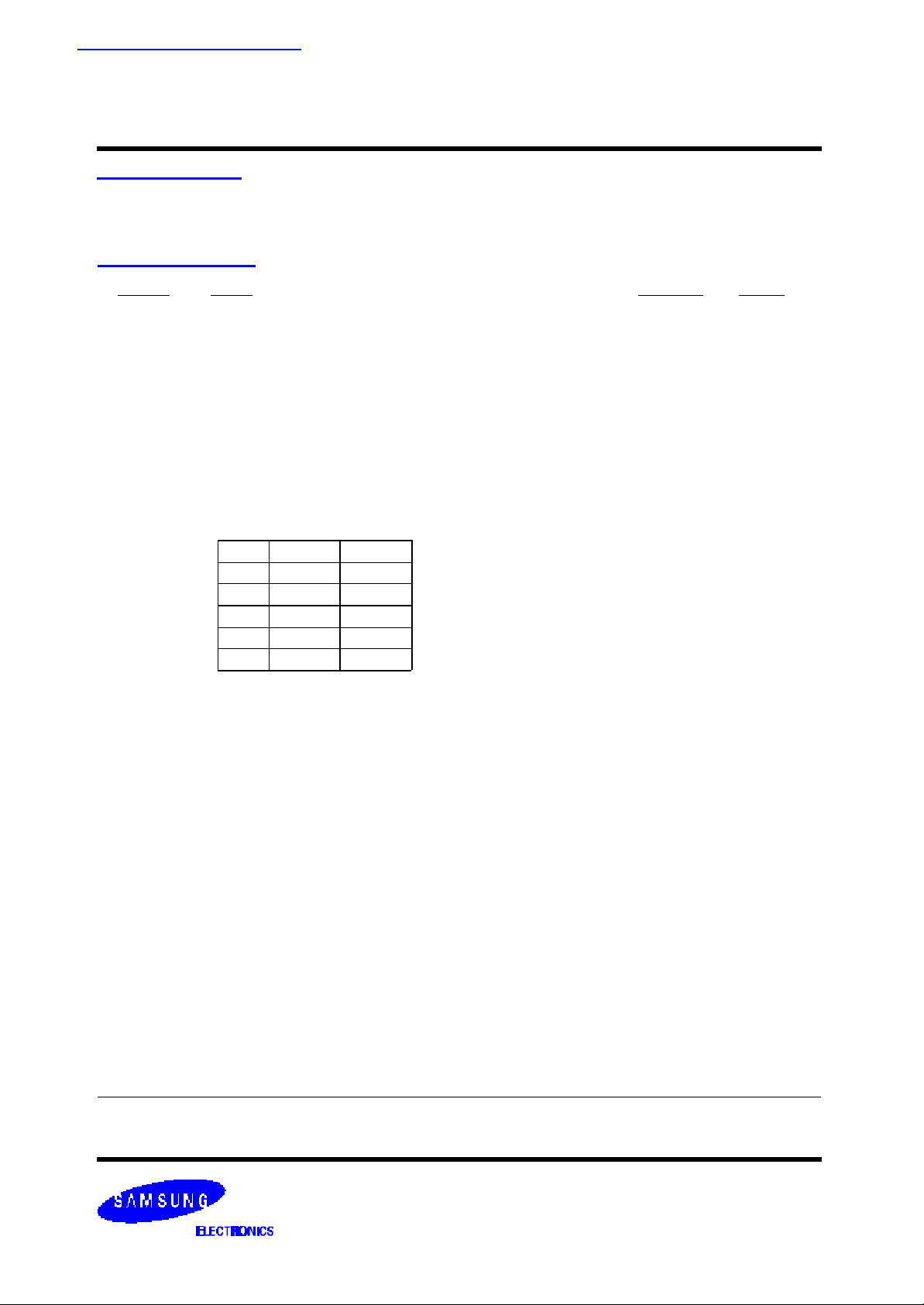

Revision History

Rev. No.

0.0

0.1

0.2

0.3

1.0

2.0

History

1. Initial document.

1. Add JTAG Scan Order

1. Add x32 org and industrial temperature .

2. Add 165FBGA package

1. Speed bin merge.

From K7N1636(32/18)09A to K7N1636(32/18)01A.

2. AC parameter change.

tOH(min)/tLZC(min) from 0.8 to 1.5 at -25

tOH(min)/tLZC(min) from 1.0 to 1.5 at -22

tOH(min)/tLZC(min) from 1.0 to 1.5 at -20

1. Final spec release.

1. Release Icc on page 14.

part # From To

-25 440 470

-22 400 430

-20 370 400

-16 340 350

-13 280 290

512Kx36 & 1Mx18 Pipelined NtRAM

TM

Draft Date

March. 21. 2001

May. 10. 2001

Aug. 30. 2001

Dec. 26. 2001

May. 10 .2002

May. 22. 2002

Remark

Preliminary

Preliminary

Preliminary

Preliminary

Final

Final

TM

2.1

3.0

The attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the

specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions on the parameters of this device. If you have any questions, please contact the SAMSUNG branch office near your office, call or contact Headquarters.

1. Delete 119BGA package.

2. Correct the Ball Size of 165 FBGA.

1. Delete x32 Org.

2. Delete the 225MHz speed bin

April. 04. 2003

Nov. 17, 2003

Final

Final

- 1 -

Nov. 2003

Rev 3.0

K7N163601A

K7N161801A

16Mb NtRAM(Flow Through / Pipelined) Ordering Information

Org. Part Number Mode VDD

512Kx36 & 1Mx18 Pipelined NtRAM

FT ; Access Time(ns)

Pipelined ; Cycle Time(MHz)

TM

Speed

PKG Temp

1Mx18

512Kx36

K7M161825A-QC(I)65/75 FlowThrough 3.3 6.5/7.5 ns

K7N161801A-Q(F)C(I)25/20/16/13 Pipelined 3.3 250/200/167/133MHz

K7N161845A-Q(F)C(I)25/20/16/13 Pipelined 2.5 250/200/167/133MHz

K7M163625A-QC(I)65/75 FlowThrough 3.3 6.5/7.5 ns

K7N163601A-Q(F)C(I)25/20/16/13 Pipelined 3.3 250/200/167/133MHz

K7N163645A-Q(F)C(I)25/20/16/13 Pipelined 2.5 250/200/167/133MHz

Q : 100TQFP

F : 165FBGA

C

; Commercial

Temp.Range

I

; Industrial

Temp.Range

- 2 -

Nov. 2003

Rev 3.0

K7N163601A

K7N161801A

512Kx36 & 1Mx18 Pipelined NtRAM

TM

512Kx36 & 1Mx18-Bit Pipelined NtRAM

• 3.3V+0.165V/-0.165V Power Supply.

• I/O Supply Voltage 3.3V+0.165V/-0.165V for 3.3V I/O

or 2.5V+0.4V/-0.125V for 2.5V I/O.

• Byte Writable Function.

• Enable clock and suspend operation.

• Single READ/WRITE control pin.

• Self-Timed Write Cycle.

• Three Chip Enable for simple depth expansion with no da ta-

contention .

• A interleaved burst or a linear burst mode.

• Asynchronous output enable control.

• Power Down mode.

• 100-TQFP-1420A

• 165FBGA(11x15 ball aray) with body size of 13mmx15mm.

• Operating in commeical and industrial temperature range.

FAST ACCESS TIMES

PARAMETER Symbol -25 -20 -16 -13 Unit

Cycle Time tCYC 4.0 5.0 6.0 7.5 ns

Clock Access Time tCD 2.6 3.2 3.5 4.2 ns

Output Enable Access Time tOE 2.6 3.2 3.5 4.2 ns

TM

GENERAL DESCRIPTIONFEATURES

The K7N163601A and K7N161801A are 18,874,368-bits Synchronous Static SRAMs.

The N tRAMTM, or No Turnaround Random Access Memory utilizes all the bandwidth in any combination of operating cycles.

Address, data inputs, and all control signals except output

enable and linear burst order are synchronized to input clock.

Burst order control must be tied "High or Low".

Asynchronous inputs include the sleep mode enable(ZZ).

Output Enable controls the outputs at any given time.

Write cycles are internally self-timed and initiated by the rising

edge of the clock input. This feature eliminates complex off-chip

write pulse generation

and provides increased timing flexibility for incoming signals.

For read cycles, pipelined SRAM output data is temporarily

stored by an edge triggered output register and then released

to the output buffers at the next rising edge of clock.

The K7N163601A and K7N161801A are implemented with

SAMSUNG′s high performance CMOS technology and is avail-

able in 100pin TQFP and 165FBGA packages. Multiple power

and ground pins minimize ground bounce.

LOGIC BLOCK DIAGRAM

A [0:18]or

A [0:19]

CLK

CKE

CS1

CS2

CS2

ADV

WE

BWx

(x=a,b,c,d or a,b)

OE

ZZ

DQa0 ~ DQd7 or DQa0 ~ DQb8

DQPa ~ DQPd

LOGIC

CONTRO L

ADDRESS

REGISTER

K

CONTROL

REGISTER

LBO

A 0~A1

A2~A 18 or A2~A19

WRITE

ADDRESS

REGISTER

BURST

ADDRESS

COUNTER

ADDRESS

REGISTER

CONTROL

LOGIC

WRITE

A′0~A ′1

36 or 18

K

K

512Kx36, 1Mx18

MEMORY

ARRAY

DATA-IN

REGISTER

DATA-IN

REGISTER

K

OUTPUT

REGISTER

BUFFER

NtRAMTM and No Turnaround Random Access Memory are trademarks of Samsung.

- 3 -

Nov. 2003

Rev 3.0

K7N163601A

K7N161801A

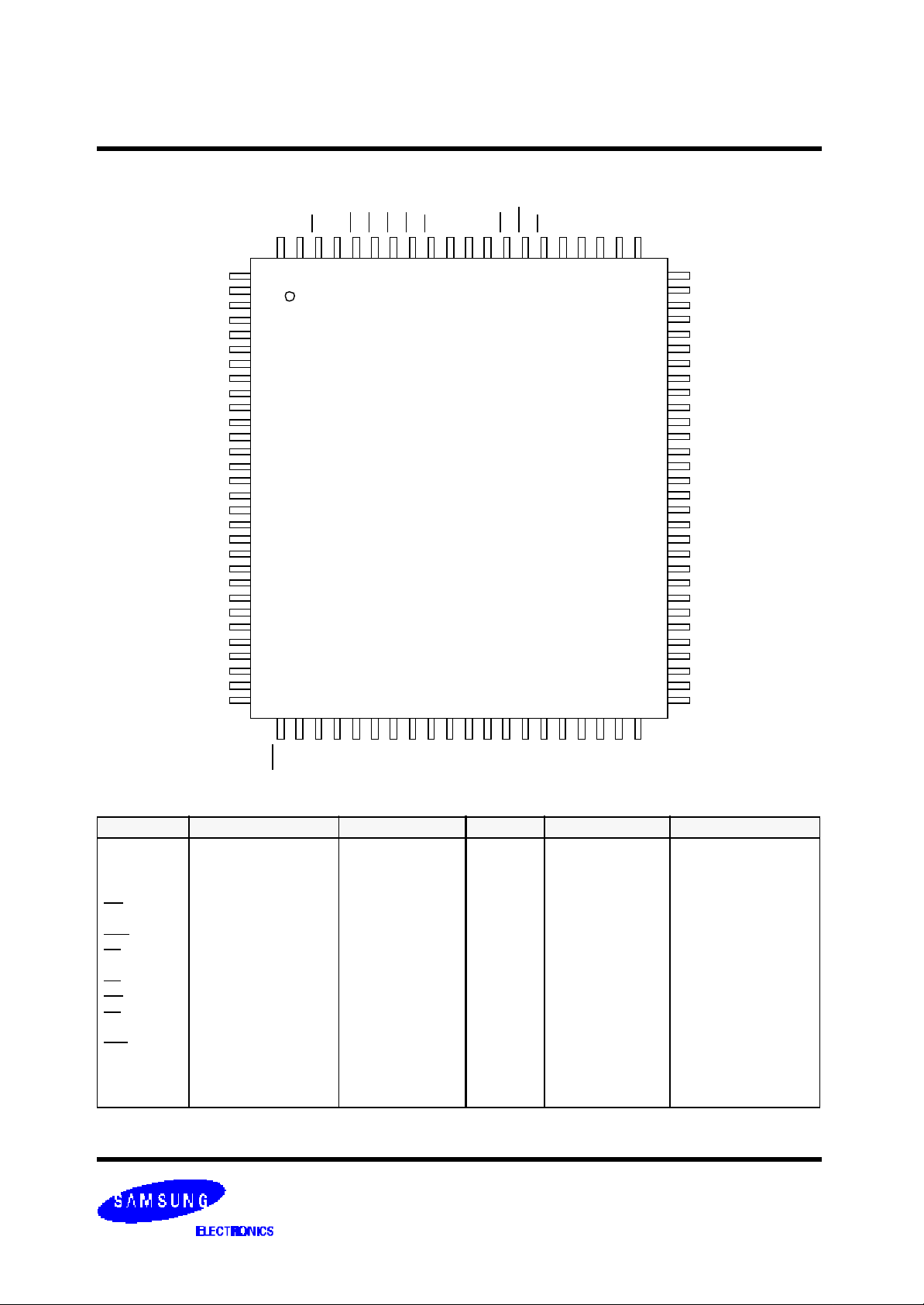

PIN CONFIGURATION(TOP VIEW)

A6

A7

CS 1

512Kx36 & 1Mx18 Pipelined NtRAM

CS 2

BWd

BWc

BWb

BWa

CS 2

VDD

VSS

CLKWECK EOEADV

A18

A17

A881A9

TM

NC/DQPc

DQc0

DQc1

VDDQ

VSSQ

DQc2

DQc3

DQc4

DQc5

VSSQ

VDDQ

DQc6

DQc7

VDD

VDD

VDD

VSS

DQd0

DQd1

VDDQ

VSSQ

DQd2

DQd3

DQd4

DQd5

VSSQ

VDDQ

DQd6

DQd7

NC/ DQPd

99

98

1

100

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31LBO

9796959493

100 Pin TQFP

(20mm x 14mm)

K7N163601A(512Kx36)

36

35

34

33

32

92

9190898887

42

41

40

39

38

37

86

858483

46

45

44

43

82

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

DQPb/NC

DQb7

DQb6

VDDQ

VSSQ

DQb5

DQb4

DQb3

DQb2

VSSQ

VDDQ

DQb1

DQb0

VSS

VDD

VDD

ZZ

DQa7

DQa6

VDDQ

VSSQ

DQa5

DQa4

DQa3

DQa2

VSSQ

VDDQ

DQa1

DQa0

DQPa/NC

A5

VSS

VDD

N.C.

N.C.

A10

N.C.

N.C.

A13

A12

A11

A16

A15

A14

A0

A1

A2

A3

A4

PIN NAME

SYMBOL PIN NAME TQFP PIN NO. SYMBOL PIN NAME TQFP PIN NO.

A0 - A18

ADV

WE

CLK

CKE

CS1

CS2

CS2

BWx(x=a,b,c,d)

OE

ZZ

LBO

Note : 1. A0 and A1 are the two least significant bits(LSB) of the address field and set the internal burst counter if burst is desired.

Address Inputs

Address Advance/Load

Read/Write Control Input

Clock

Clock Enable

Chip Select

Chip Select

Chip Select

Byte Write Inputs

Output Enable

Power Sleep Mode

Burst Mode Control

32,33,34,35,36,37,44

45,46,47,48,49,50,81

82,83,84,99,100

85

88

89

87

98

97

92

93,94,95,96

86

64

31

- 4 -

V DD

V SS

N.C.

DQa0~a7

DQb0~b7

DQc 0~c7

DQd0~d7

DQPa~P d

or NC

V DDQ

V SSQ

Power Supply(+3.3V)

Ground

No Connect

Data Inputs/Outputs

Data Inputs/Outputs

Data Inputs/Outputs

Data Inputs/Outputs

Data Inputs/Outputs

Output Power Supply

(3.3V or 2.5V)

Output Ground

14,15,16,41,65,66,91

17,40,67,90

38,39,42,43

52,53,56,57,58,59,62,63

68,69,72,73,74,75,78,79

2,3,6,7,8,9,12,13

18,19,22,23,24,25,28,29

51,80,1,30

4,11,20,27,54,61,70,77

5,10,21,26,55,60,71,76

Nov. 2003

Rev 3.0

K7N163601A

K7N161801A

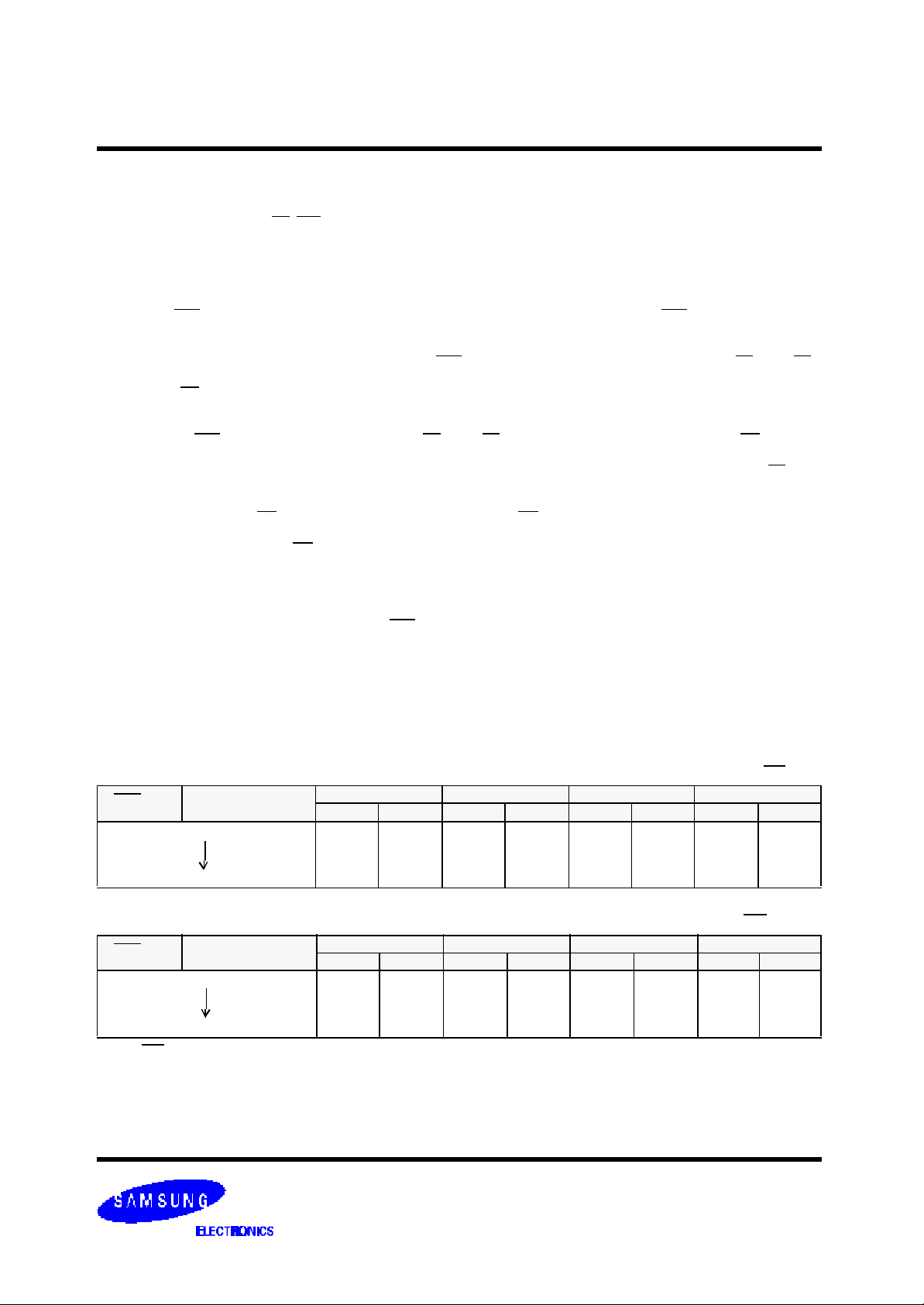

PIN CONFIGURATION(TOP VIEW)

A6

A7

CS 1

99

N.C.

N.C.

N.C.

VDDQ

VSSQ

N.C.

N.C.

DQb8

DQb7

VSSQ

VDDQ

DQb6

DQb5

VDD

VDD

VDD

VSS

DQb4

DQb3

VDDQ

VSSQ

DQb2

DQb1

DQb0

N.C.

VSSQ

VDDQ

N.C.

N.C.

N.C.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

98

100

33

32

31LBO

512Kx36 & 1Mx18 Pipelined NtRAM

CS 2

9796959493

BWb

BWa

CS 2

VDD

VSS

N.C.

N.C.

92

CLKWECK EOEADV

9190898887

86

100 Pin TQFP

(20mm x 14mm)

K7N161801A(1Mx18)

45

44

43

42

41

40

39

38

37

36

35

34

A19

858483

47

46

TM

A18

A881A9

82

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

A10

N.C.

N.C.

VDDQ

VSSQ

N.C.

DQa0

DQa1

DQa2

VSSQ

VDDQ

DQa3

DQa4

VSS

VDD

VDD

ZZ

DQa5

DQa6

VDDQ

VSSQ

DQa7

DQa8

N.C.

N.C.

VSSQ

VDDQ

N.C.

N.C.

N.C.

A5

VSS

VDD

N.C.

N.C.

A11

N.C.

N.C.

A14

A13

A12

A17

A16

A15

A0

A1

A2

A3

A4

PIN NAME

SYMBOL PIN NAME TQFP PIN NO. SYMBOL PIN NAME TQFP PIN NO.

A 0 - A19

ADV

WE

CLK

CKE

CS1

CS2

CS2

BW x(x=a,b)

OE

ZZ

LBO

NOTE : A0 and A1 are the two least significant bits(LSB) of the address field and set the internal burst counter if burst is desired.

Address Inputs

Address Advance/Load

Read/Write Control Input

Clock

Clock Enable

Chip Select

Chip Select

Chip Select

Byte Write Inputs

Output Enable

Power Sleep Mode

Burst Mode Control

32,33,34,35,36,37,44

45,46,47,48,49,50,80

81,82,83,84,99,100

85

88

89

87

98

97

92

93,94

86

64

31

VDD

VSS

N.C.

DQa0~a8

DQb0~b8

VDDQ

VSSQ

- 5 -

Power Supply(+3.3V)

Ground

No Connect

Data Inputs/Outputs

Data Inputs/Outputs

Output Power Supply

(3.3V or 2.5V)

Output Ground

14,15,16,41,65,66,91

17,40,67,90

1,2,3,6,7,25,28,29,30,

38,39,42,43,51,52,53,

56,57,75,78,79,95,96

58,59,62,63,68,69,72,73,74

8,9,12,13,18,19,22,23,24

4,11,20,27,54,61,70,77

5,10,21,26,55,60,71,76

Nov. 2003

Rev 3.0

K7N163601A

K7N161801A

165-PIN FBGA PACKAGE CONFIGURATIONS(TOP VIEW)

K7N163601A(512Kx36)

1 2 3 4 5 6 7 8 9 10 11

512Kx36 & 1Mx18 Pipelined NtRAM

TM

A NC A CS1 BW c BWb

CS2

CKE ADV A A NC

B NC A CS2 BWd BWa CLK WE OE A A NC

C DQPc NC V DDQ VSS VSS VSS VSS VSS VDDQ NC DQPb

D DQc DQc V DDQ VDD VSS VSS VSS VDD VDDQ DQb DQb

E DQc DQc V DDQ VDD VSS VSS VSS VDD VDDQ DQb DQb

F DQc DQc V DDQ VDD VSS VSS VSS VDD VDDQ DQb DQb

G DQc DQc V DDQ VDD VSS VSS VSS VDD VDDQ DQb DQb

H NC VDD NC V DD VSS VSS VSS VDD NC NC ZZ

J DQd DQd V DDQ VDD VSS VSS VSS VDD VDDQ DQa DQa

K DQd DQd V DDQ VDD VSS VSS VSS VDD VDDQ DQa DQa

L DQd DQd V DDQ VDD VSS VSS VSS VDD VDDQ DQa DQa

M DQd DQd V DDQ VDD VSS VSS VSS VDD VDDQ DQa DQa

N DQPd NC V DDQ VSS NC NC NC VSS VDDQ NC DQPa

P NC NC A A TDI A1* TDO A A A NC

R LBO NC A A TMS A0* TCK A A A A

Note : * A0 and A1 are the two least significant bits(LSB) of the address field and set the internal burst counter if burst is desired.

PIN NAME

SYMBOL PIN NAME SYMBOL PIN NAME

A

A0,A1

ADV

WE

CLK

CKE

CS1

CS2

CS2

BWx

(x=a,b,c,d)

OE

ZZ

LBO

TCK

TMS

TDI

TDO

Address Inputs

Burst Address Inputs

Address Advance/Load

Read/Write Control Input

Clock

Clock Enable

Chip Select

Chip Select

Chip Select

Byte Write Inputs

Output Enable

Power Sleep Mode

Burst Mode Control

JTAG Test Clock

JTAG Test Mode Select

JTAG Test Data Input

JTAG Test Data Output

VDD

VSS

N.C.

DQa

DQb

DQc

DQd

DQPa~Pd

VDDQ

- 6 -

Power Supply

Ground

No Connect

Data Inputs/Outputs

Data Inputs/Outputs

Data Inputs/Outputs

Data Inputs/Outputs

Data Inputs/Outputs

Output Power Supply

Nov. 2003

Rev 3.0

K7N163601A

K7N161801A

165-PIN FBGA PACKAGE CONFIGURATIONS(TOP VIEW)

K7N161801A(1Mx18)

1 2 3 4 5 6 7 8 9 10 11

512Kx36 & 1Mx18 Pipelined NtRAM

TM

A NC A CS1 BWb NC

CS2

CKE ADV A A A

B NC A CS2 NC BWa CLK WE OE A A NC

C NC NC V DDQ VSS VSS VSS VSS VSS VDDQ NC DQPa

D NC DQb V DDQ VDD VSS VSS VSS VDD VDDQ NC DQa

E NC DQb V DDQ VDD VSS VSS VSS VDD VDDQ NC DQa

F NC DQb V DDQ VDD VSS VSS VSS VDD VDDQ NC DQa

G NC DQb V DDQ VDD VSS VSS VSS VDD VDDQ NC DQa

H NC VDD NC V DD VSS VSS VSS VDD NC NC ZZ

J DQb NC V DDQ VDD VSS VSS VSS VDD VDDQ DQa NC

K DQb NC V DDQ VDD VSS VSS VSS VDD VDDQ DQa NC

L DQb NC V DDQ VDD VSS VSS VSS VDD VDDQ DQa NC

M DQb NC V DDQ VDD VSS VSS VSS VDD VDDQ DQa NC

N DQPb NC V DDQ VSS NC NC NC VSS VDDQ NC NC

P NC NC A A TDI A1* TDO A A A NC

R LBO NC A A TMS A0* TCK A A A A

Note : * A0 and A1 are the two least significant bits(LSB) of the address field and set the internal burst counter if burst is desired.

PIN NAME

SYMBOL PIN NAME SYMBOL PIN NAME

A

A0,A1

ADV

WE

CLK

CKE

CS1

CS2

CS2

BWx

(x=a,b)

OE

ZZ

LBO

TCK

TMS

TDI

TDO

Address Inputs

Burst Address Inputs

Address Advance/Load

Read/Write Control Input

Clock

Clock Enable

Chip Select

Chip Select

Chip Select

Byte Write Inputs

Output Enable

Power Sleep Mode

Burst Mode Control

JTAG Test Clock

JTAG Test Mode Select

JTAG Test Data Input

JTAG Test Data Output

VDD

VSS

N.C.

DQa

DQb

DQPa, Pb

VDDQ

- 7 -

Power Supply

Ground

No Connect

Data Inputs/Outputs

Data Inputs/Outputs

Data Inputs/Outputs

Output Power Supply

Nov. 2003

Rev 3.0

K7N163601A

K7N161801A

512Kx36 & 1Mx18 Pipelined NtRAM

TM

FUNCTION DESCRIPTION

The K7N163601A and K7N161801A are NtRAMTM designed to sustain 100% bus bandwidth by eliminating turnaround cycle when

there is transition from Read to Write, or vice versa.

All inputs (with the exception of OE, LBO and ZZ) are synchronized to rising clock edges.

All read, write and deselect cycles are initiated by the ADV input. Subsequent burst addresses can be internally generated by the

burst advance pin (ADV). ADV should be driven to Low once the device has been deselected in order to load a new address for next

operation.

Clock Enable(CKE) pin allows the operation of the chip to be suspended as long as necessary. When CKE is high, all synchronous

inputs are ignored and the internal device registers will hold their previous values.

NtRAMTM latches external address and initiates a cycle, when CKE, ADV are driven to low and all three chip enables(CS1, CS2, CS2)

are active .

Output Enable(OE ) can be used to disable the output at any given time.

Read operation is initiated when at the rising edge of the clock, the address presented to the address inputs are latched in the

address register, CKE is driven low, all three chip enables(CS 1, CS2 , CS2) are active, the write enable input signals WE are driven

high, and ADV driven low.The internal array is read between the first rising edge and the second rising edge of the clock and the data

is latched in the output register. At the second clock edge the data is driven out of the SRAM. Also during read operation OE must

be driven low for the device to drive out the requested data.

Write operation occurs when WE is driven low at the rising edge of the clock. BW[d:a] can be used for byte write operation. The pipelined NtRAMTM uses a late-late write cycle to utilize 100% of the bandwidth.

At the first rising edge of the clock, WE and address are registered, and the data associated with that address is required two cycle

later.

Subsequent addresses are generated by ADV High for the burst access as shown below. The starting point of the burst seguence is

provided by the external address. The burst address counter wraps around to its initial state upon completion.

The burst sequence is determined by the state of the LBO pin. When this pin is low, linear burst sequence is selected.

And when this pin is high, Interleaved burst sequence is selected.

During normal operation, ZZ must be driven low. When ZZ is driven high, the SRAM will enter a Power Sleep Mode after 2 cycles. At

this time, internal state of the SRAM is preserved. When ZZ returns to low, the SRAM normally operates after 2 cycles of wake up

time.

BURST SEQUENCE TABLE (Interleaved Burst, LBO=High)

LBO PIN HIGH

First Address

Fourth Address

Case 1 Case 2 Case 3 Case 4

A1 A0 A1 A0 A1 A0 A1 A0

0

0

1

1

0

1

0

1

0

0

1

1

1

0

1

0

1

1

0

0

0

1

0

1

1

1

0

0

1

0

1

0

BQ TABLE (Linear Burst, LBO=Low)

LBO PIN LOW

First Address

Fourth Address

Note : 1. LBO pin must be tied to High or Low, and Floating State must not be allowed.

Case 1 Case 2 Case 3 Case 4

A1 A0 A1 A0 A1 A0 A1 A0

0

0

1

1

0

1

0

1

0

1

1

0

1

0

1

0

1

1

0

0

0

1

0

1

1

0

0

1

1

0

1

0

- 8 -

Nov. 2003

Rev 3.0

Loading...

Loading...