Samsung K4D263238D-QC50, K4D263238D-QC40 Datasheet

K4D263238D

128M DDR SDRAM

128Mbit DDR SDRAM

1M x 32Bit x 4 Banks

Double Data Rate Synchronous DRAM

with Bi-directional Data Strobe and DLL

Revision 1.3

July 2002

-1-

Rev. 1.3 (Jul. 2002)

K4D263238D

Revision History

Revision 1.3 (July 18, 2002)

• Changed power dissipation from 2.0W to 1.8W

Revision 1.2 (June 17, 2002)

• Removed K4D263238D-QC55 from the spec.

• 183/166MHz were supported in K4D263238D-QC50.

Revision 1.1 (May 24, 2002)

• Removed K4D263238D-QC45/60 from the spec

Revision 1.0 (May 20, 2002)

• Define DC spec.

Revision 0.0 (April 23, 2002)- Target spec

• Define target spec.

128M DDR SDRAM

-2-

Rev. 1.3 (Jul. 2002)

K4D263238D

1M x 32Bit x 4 Banks Double Data Rate Synchronous DRAM

with Bi-directional Data Strobe and DLL

FEATURES

128M DDR SDRAM

• 2.5V ± 5% power supply

• SSTL_2 compatible inputs/outputs

• 4 banks operation

• MRS cycle with address key programs

-. Read latency 3,4 (clock)

-. Burst length (2, 4, 8 and Full page)

-. Burst type (sequential & interleave)

• Full page burst length for sequential burst type only

• Start address of the full page burst should be even

• All inputs except data & DM are sampled at the positive

going edge of the system clock

• Differential clock input

• No Write Interrupted by Read function

• Data I/O transactions on both edges of Data strobe

• DLL aligns DQ and DQS transitions with Clock transition

• Edge aligned data & data strobe output

• Center aligned data & data strobe input

• DM for write masking only

• Auto & Self refresh

• 32ms refresh period (4K cycle)

• 100pin TQFP package

• Maximum clock frequency up to 250MHz

• Maximum data rate up to 500Mbps/pin

ORDERING INFORMATION

Part NO. Max Freq. MaxDataRate Interface Package

K4D263238D-QC40 250MHz 500Mbps/pin

K4D263238D-QC50 200MHz 400Mbps/pin

SSTL_2 100 TQFP

GENERAL DESCRIPTION

FOR 1M x 32Bit x 4 Bank DDR SDRAM

The K4D263238D is 134,217,728 bits of hyper synchronous data rate Dynamic RAM organized as 4 x 1,048,576 words by

32 bits, fabricated with SAMSUNG

extremely high performance up to 2.0GB/s/chip. I/O transactions are possible on both edges of the clock cycle. Range of

operating frequencies, programmable burst length and programmable latencies allow the device to be useful for a variety

of high performance memory system applications.

′s high performance CMOS technology. Synchronous features with Data Strobe allow

-3-

Rev. 1.3 (Jul. 2002)

K4D263238D

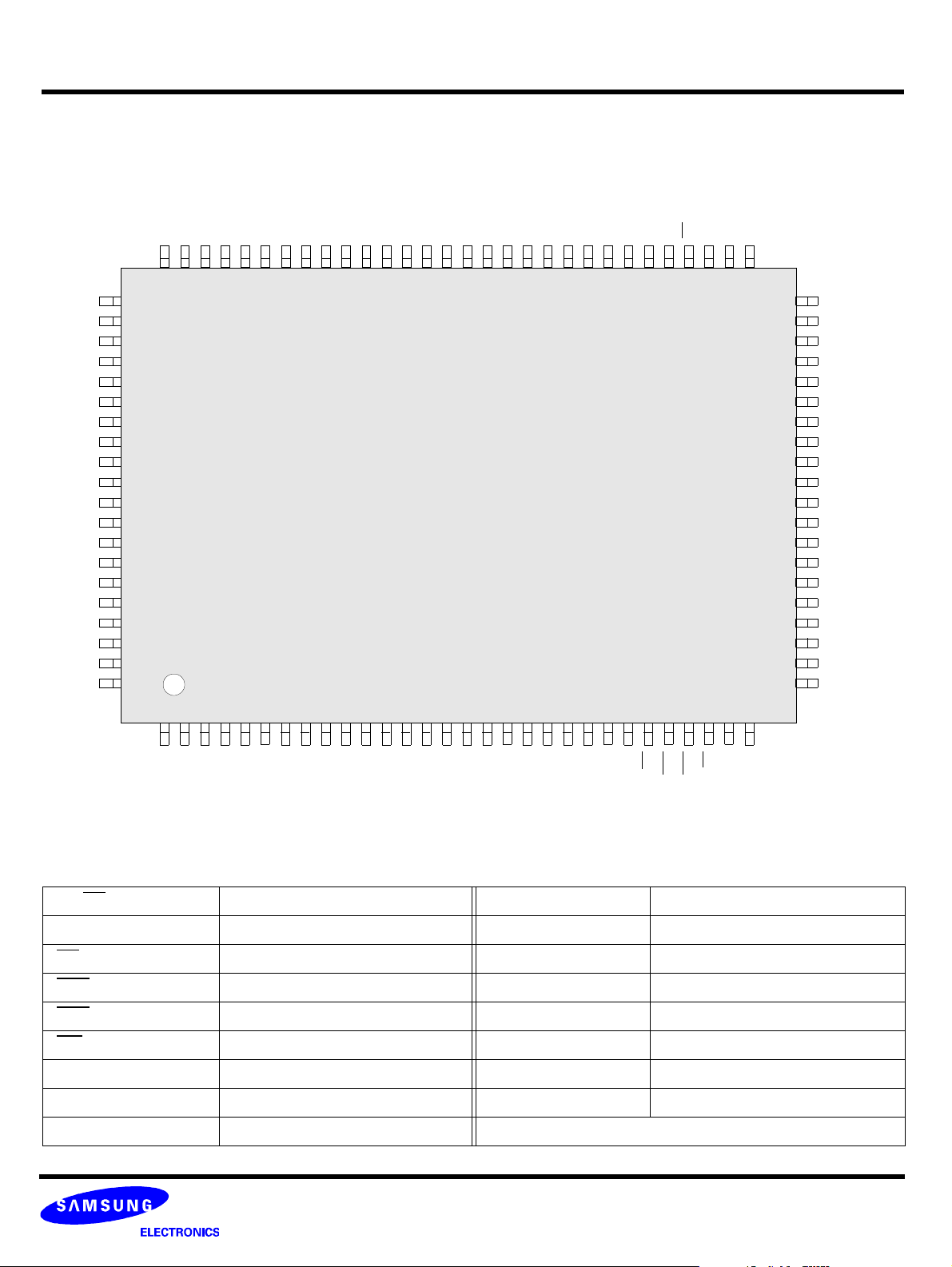

PIN CONFIGURATION (Top View)

128M DDR SDRAM

DQ29

VSSQ

DQ30

DQ31

VSS

VDDQ

N.C

N.C

N.C

N.C

N.C

VSSQ

RFU

DQS

VDDQ

VDD

DQ0

DQ1

VSSQ

DQ2

DQ28

VDDQ

DQ27

DQ26

VSSQ

DQ25

DQ24

VDDQ

DQ15

DQ14

VSSQ

DQ13

DQ12

VDDQ

VSS

VDD

DQ11

DQ10

VSSQ

DQ9

DQ8

VDDQ

VREF

DM3

DM1

8079787776757473727170696867666564636261605958575655545352

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

1

2

3

4

5

6

7

8

9

101112131415161718192021222324252627282930

100 Pin TQFP

20 x 14 mm

2

0.65mm pin Pitch

CKCKCKE

MCL

A8(AP)

51

50

A7

49

A6

48

A5

47

A4

46

VSS

45

A9

44

N.C

43

N.C

42

N.C

41

N.C

40

N.C

39

N.C

38

N.C

37

A11

36

A10

35

VDD

34

A3

33

A2

32

A1

31

A0

DQ3

VDDQ

DQ4

DQ5

VSSQ

DQ6

DQ7

DQ16

VDDQ

VSS

DQ17

DQ18

VSSQ

VDD

DQ19

VDDQ

DQ20

DQ21

DQ22

DQ23

VSSQ

VDDQ

WE

DM0

DM2

CAS

RAS

CS

BA0

BA1

PIN DESCRIPTION

CK,CK Differential Clock Input BA0,BA1 Bank Select Address

CKE Clock Enable A

CS

RAS

CAS

WE

Chip Select DQ0 ~DQ31 Data Input/Output

Row Address Strobe VDD Power

Column Address Strobe VSS Ground

Write Enable VDDQ Power for DQ′s

DQS Data Strobe V

DMi Data Mask MCL Must Connect Low

RFU Reserved for Future Use

0 ~A11 Address Input

SSQ Ground for DQ′s

-4-

Rev. 1.3 (Jul. 2002)

K4D263238D

INPUT/OUTPUT FUNCTIONAL DESCRIPTION

Symbol Type Function

The differential system clock Input.

CK, CK

*1

CKE Input

CS

Input

Input

All of the inputs are sampled on the rising edge of the clock except

′sandDM′s that are sampled on both edges of the DQS.

DQ

Activates the CK signal when high and deactivates the CK signal

when low. By deactivating the clock, CKE low indicates the Power

down mode or Self refresh mode.

CS

enables the command decoder when low and disabled the command decoder when high. When the command decoder is disabled,

new commands are ignored but previous operations continue.

128M DDR SDRAM

RAS

CAS

WE

Input

Input

Input

Latches row addresses on the positive going edge of the CK with

RAS

low. Enables row access & precharge.

Latches column addresses on the positive going edge of the CK with

CAS

low. Enables column access.

Enables write operation and row precharge.

Latches data in starting from CAS

,WEactive.

DQS Input/Output Data input and output are synchronized with both edge of DQS.

Data In mask. Data In is masked by DM Latency=0 when DM is high

0 ~DM3 Input

DM

in burst write. DM0 for DQ0 ~DQ7, DM1 for DQ8 ~DQ15, DM2 for

16 ~DQ23, DM3 for DQ24 ~DQ31.

DQ

DQ0 ~DQ31 Input/Output Data inputs/Outputs are multiplexed on the same pins.

BA

0,BA1 Input Selects which bank is to be active.

Row/Column addresses are multiplexed on the same pins.

0 ~A11 Input

A

V

DD/VSS Power Supply Power and ground for the input buffers and core logic.

V

DDQ/VSSQ Power Supply

Row addresses : RA0 ~RA11, Column addresses : CA0 ~CA7.

Column address CA

8 is used for auto precharge.

Isolated power supply and ground for the output buffers to provide

improved noise immunity.

V

REF Power Supply Reference voltage for inputs, used for SSTL interface.

MCL Must Connect Low Must connect Low

*1 : The timing reference point for the differential clocking is the cross point of CK and CK.

For any applications using the single ended clocking, apply V

REF to CK pin.

-5-

Rev. 1.3 (Jul. 2002)

K4D263238D

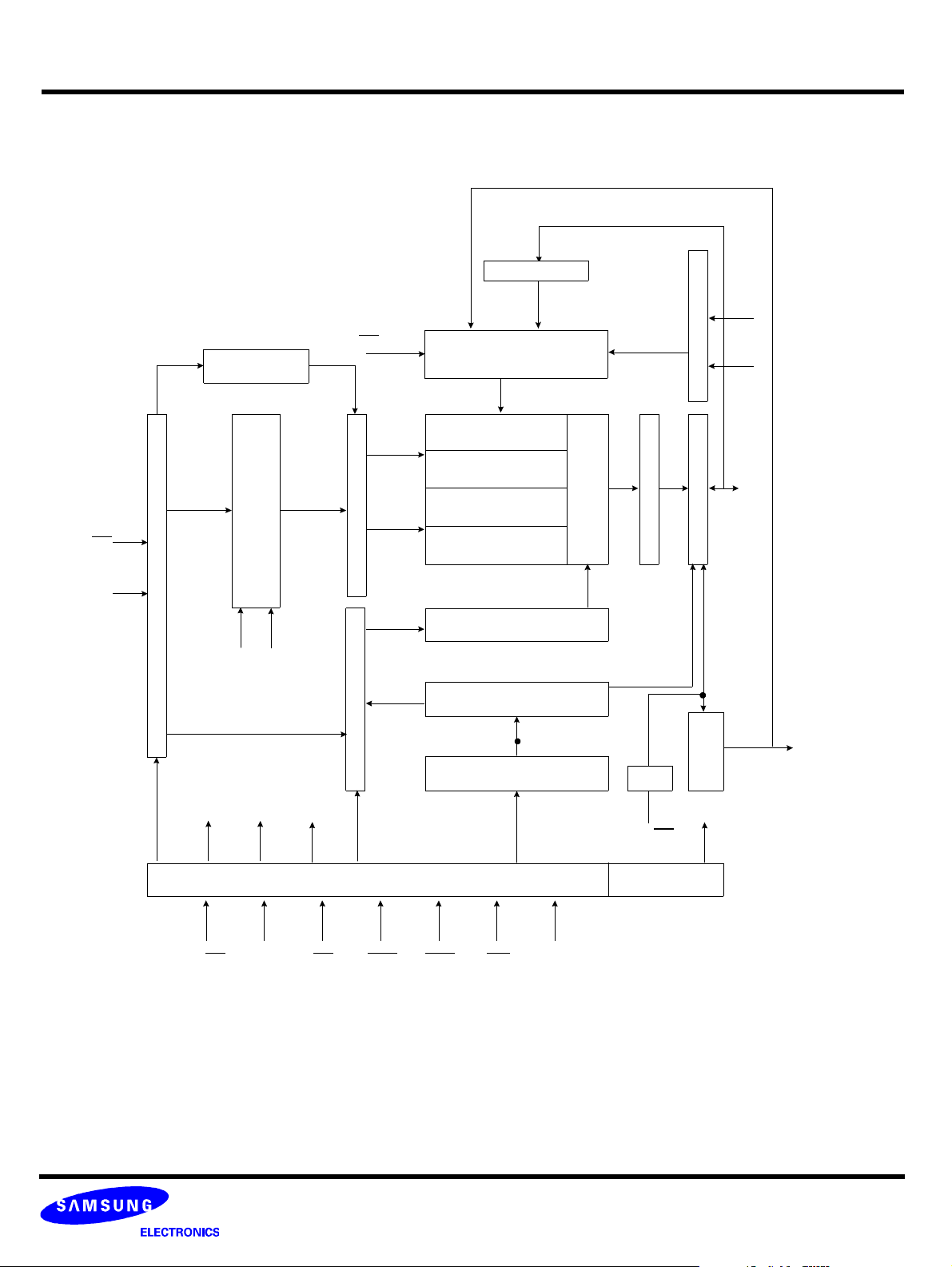

BLOCK DIAGRAM (1Mbit x 32I/O x 4 Bank)

128M DDR SDRAM

32

Intput Buffer

LWE

CK,CK

ADDR

LCKE

Address Register

Bank Select

LRAS

Row Buffer

LRAS

LCBR

Refresh Counter

CK, CK

Row Decoder

LCBR

LWE

Col. Buffer

LCAS

Data Input Register

Serial to parallel

64

1Mx32

1Mx32

1Mx32

1Mx32

Column Decoder

Latency & Burst Length

Programming Register

LWCBR

Sense AMP

2-bit prefetch

64 32

DLL

CK,CK

Output BufferI/O Control

Gen.

LDMi

x32

DQi

Strobe

Data Strobe

LDMi

CK,CK

Timing Register

CKE CS RAS CAS WE DMi

-6-

Rev. 1.3 (Jul. 2002)

Loading...

Loading...