ROHM BU9897GUL-W Technical data

A

High Reliability Series Serial EEPROMs

WL-CSP EEPROM family

I2C BUS

BU9897GUL-W

●Description

BU9897GUL-W is a serial EEPROM of I

Memory density is 128Kbit (16,384×8bit) , compact package VCSP50L2.

●Features

1) Completely conforming to the world standard I

All controls available by 2 ports of serial clock (SCL) and serial data (SDA)

2) Other devices than EEPROM can be connected to the same port, saving microcontroller port.

3) 1.7 ~ 5.5V single power source action most suitable for battery use.

4) FAST MODE 400kHz at 1.7 ~ 5.5V

5) Page write mode useful for initial value write at factory shipment.

6) Auto erase and auto end function at data rewrite.

7) Low current consumption

At write operation (5.0V) : 0.5mA (Typ.)

At read operation (5.0V) : 0.2mA (Typ.)

At standby operation (5.0V) : 0.1µA (Typ.)

8) Write mistake prevention function

Write (write protect) function added

Write mistake prevention function at low voltage

9) Data rewrite up to 1,000,000 times

10) Data kept for 40 years

11) Noise filter built in SCL / SDA terminal

12) Shipment data all address FFh

●Page write

2

C BUS interface method.

2

C BUS.

No.10001EAT24

Product number Number of pages

BU9897GUL-W 64Byte

●Absolute maximum ratings (Ta=25℃)

Parameter symbol Ratings Unit

Impressed voltage VCC -0.3 ~ 6.5 V

Permissible dissipation Pd 220 *1 mW

Storage temperature range Tstg -65 ~ 125 ℃

Action temperature range Topr -40 ~ 85 ℃

Terminal voltage - -0.3 ~ VCC+1.0 *2 V

*1 When using at Ta=25℃or higher, 2.2mW to be reduced per 1℃

*2 The Max value of Terminal Voltage is not over 6.5V.

●Recommended operating conditions

Parameter Symbol Ratings Unit

Power source voltage VCC 1.7 ~ 5.5

Input voltage VIN 0 ~ VCC

V

www.rohm.com

© 2011 ROHM Co., Ltd. All rights reserved.

1/16

2011.10 - Rev.

BU9897GUL-W

A

●Memory cell characteristics (Ta=25℃, Vcc=1.7~5.5V)

Parameter

Min. Typ. Max.

Limits

Number of data rewrite times *1 1,000,000 - - Times

Data hold years *1 40 - - Years

*1 Not 100% TESTED

●Electrical characteristics (Unless otherwise specified Ta=-40~85℃, V

Parameter Symbol

Min Typ. Max.

Limits

Technical Note

Unit

CC=1.7~5.5V)

Unit Condition

"H" Input Voltage1 V

"L" Input Voltage1 V

"L" Output Voltage1 V

"L" Output Voltage2 V

0.7V

IH1

-0.3 - 0.3Vcc V

IL1

- - 0.4 V IOL=3.0mA, 2.5V≦VCC≦5.5V(SDA)

OL1

- - 0.2 V IOL=0.7mA, 1.7V≦VCC<2.5V(SDA)

OL2

- VCC+1.0 V

CC

Input Leakage Current ILI -1 - 1 µA VIN=0V ~ VCC

Output Leakage Current ILO -1 - 1 µA V

I

CC1

- - 2.5 mA

Current consumption

at action

I

- - 0.5 mA

CC2

=0V ~ VCC(SDA)

OUT

VCC=5.5V , f

=400kHz, tWR=5ms

SCL

Byte Write, Page Write

V

=5.5V , f

CC

=400kHz

SCL

Random read, Current read,

Sequential read

Standby Current ISB - - 2.0 µA VCC=5.5V , SDA・SCL=VCC, WP=GND

○This product is not designed for protection against radioactive rays.

●Action timing characteristics(Unless otherwise specified Ta=-40 ~ 85℃、V

Parameter Symbol

=1.7 ~ 5.5V)

CC

Limits

Min. Typ. Max.

Unit

SCL Frequency fSCL - - 400 kHz

Data clock "High" time tHIGH 0.6 - - µs

Data clock "Low" time tLOW 1.2 - - µs

SDA, SCL rise time *1 tR - - 0.3 µs

SDA, SCL fall time *1 tF - - 0.3 µs

Start condition hold time tHD:STA 0.6 - - µs

Start condition setup time tSU:STA 0.6 - - µs

Input data hold time tHD:DAT 0 - - ns

Input data setup time tSU:DAT 100 - - ns

Output data delay time tPD 0.1 - 0.9 µs

Output data hold time tDH 0.1 - - µs

Stop condition data setup time tSU:STO 0.6 - - µs

Bus release time before transfer start tBUF 1.2 - - µs

Internal write cycle time tWR - - 5 ms

Noise removal valid period (SDA,SCL terminal) tI - - 0.1 µs

WP hold time tHD:WP 0 - - ns

WP setup time tSU:WP 0.1 - - µs

WP valid time tHIGH:WP 1.0 - - µs

*1 : Not 100% TESTED

www.rohm.com

© 2011 ROHM Co., Ltd. All rights reserved.

2/16

2011.10 - Rev.

BU9897GUL-W

A

A

A

A

A

g

g

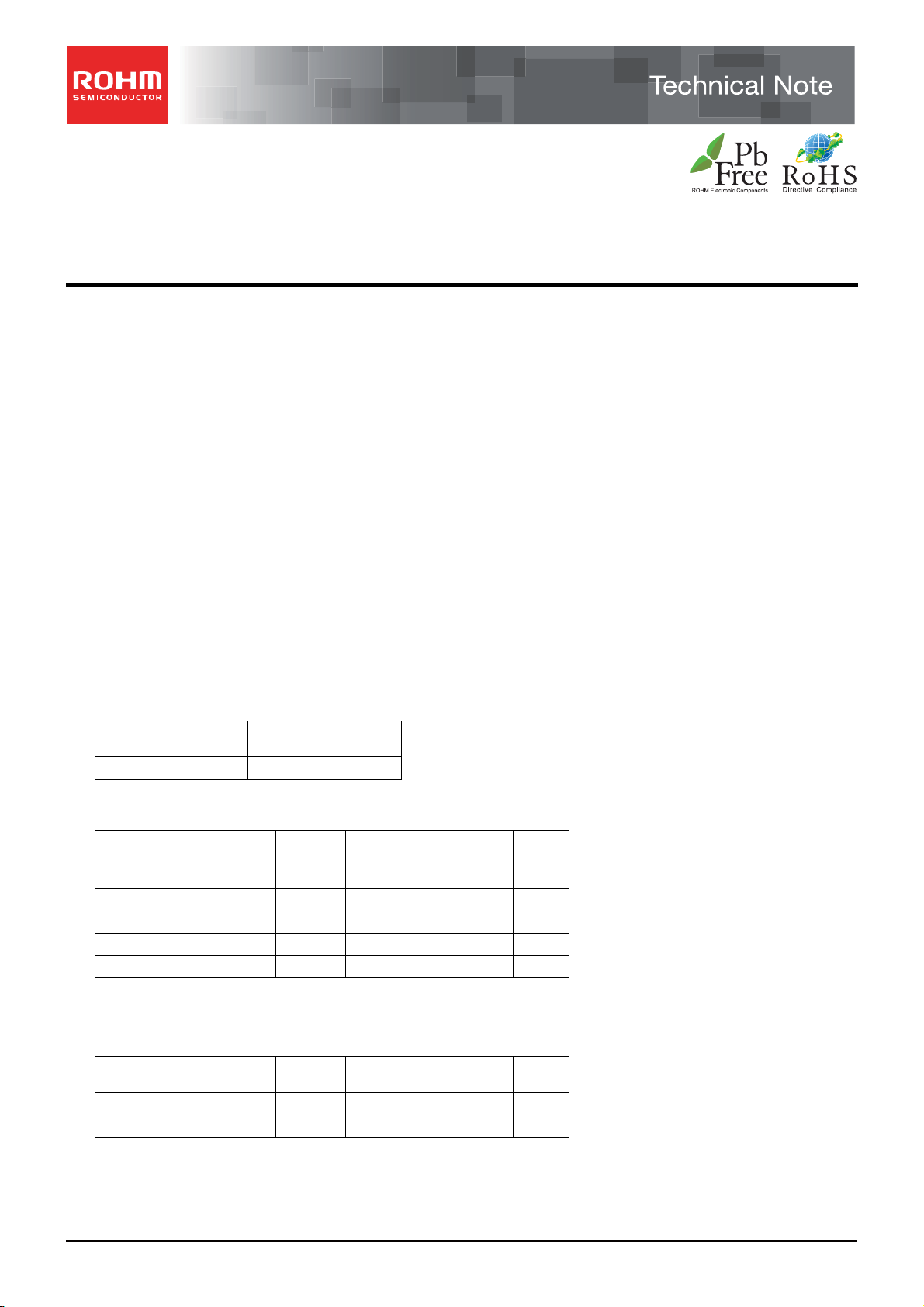

●Sync data input/output timing

SCL

SDA

(Input)

SDA

(Output)

○Input read at the rise edge of SCL

○Data output in sync with the fall of SCL

tHD :STA tHD :DAT

tBUF

Fig.1-(a) Sync data input / output timing

SCL

tSU :STA tSU :STO tHD :STA

SDA

START BIT

Fig.1-(b) Start - stop bit timing

SCL

SDA

WRITE DATA(n)

D0

ACK

STOP

CONDITION

Fig.1-(c) Write cycle timing

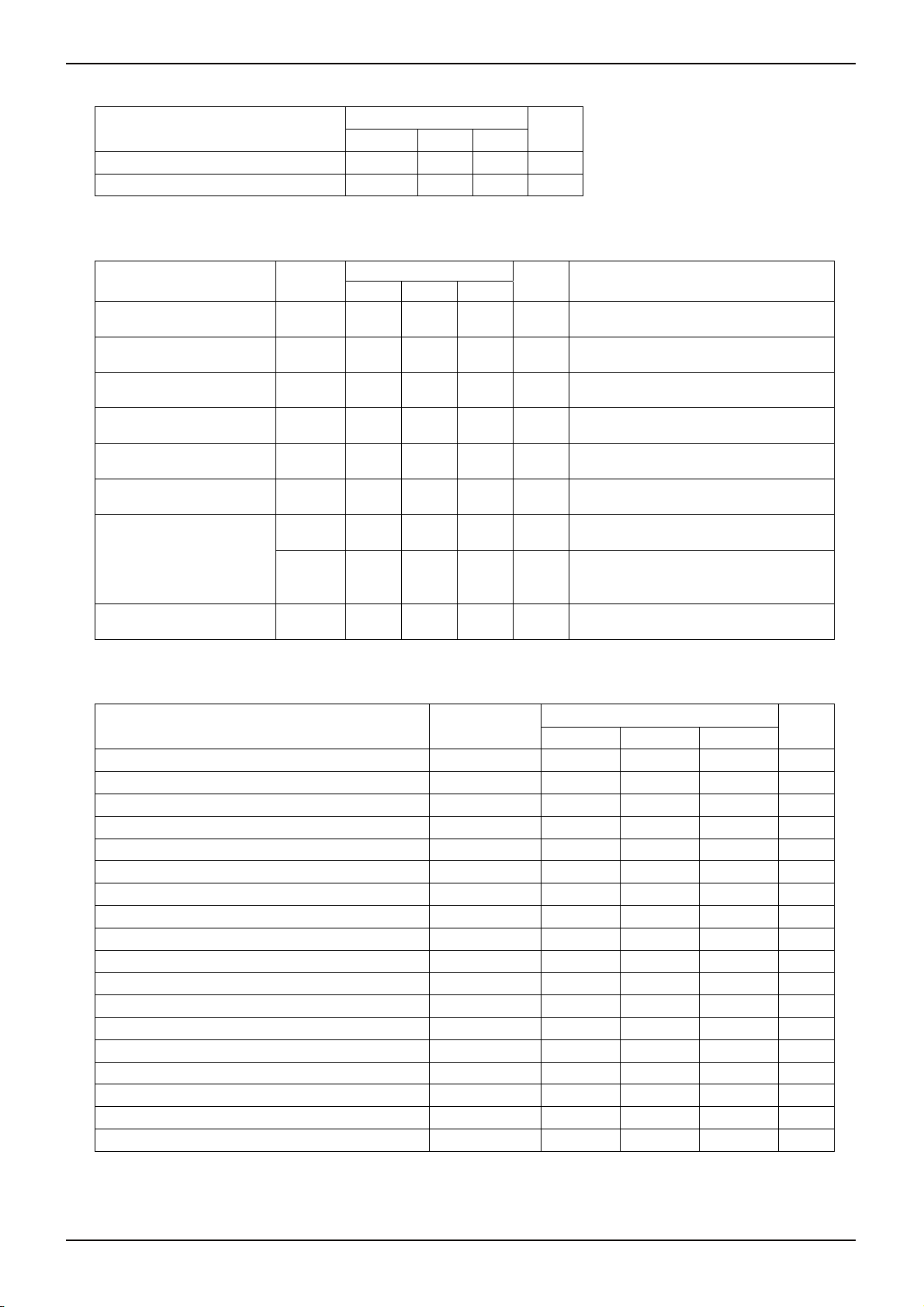

●Block diagram

1

A0

A1

2

A2

3

GND

High voltage

generating circuit

tSU :DAT

Adddress

decoder

tR tF

tHIGH

tLOW

tPD tDH

tWR

START

CONDITION

128Kbit EEPROM array

14bit

14bit

START STOP

Control circuit

SCL

SD

WP

SCL

SDA

STOP BIT

WP

Slave - word

address register

Power source

volta

e detection

Fig.2 Block diagram

Technical Note

DATA(1)

D1 D0ACK

tSU:WP

Fig.1-(d) WP timing at write execution

DATA(1)

D1 D0

○At write execution, in the area from the D0 taken clock rise

of the first DATA(1), to tWR, set WP= 'LOW'.

○By setting WP "HIGH" in the area, write can be cancelled.

When it is set WP = 'HIGH' during tWR, write is forcibly ended,

and data of address under access is not guaranteed, therefore write it

once again.

Fig.1-(e) WP timing at write cancel

8bit

Data

ister

re

ACK

CK

DATA(n)

tHIGH:WP

DATA(n)

8

7

6

5 4

Vcc

WP

SCL

SDA

CK

Stop condition

CK

tWR

tHD:WP

tWR

www.rohm.com

© 2011 ROHM Co., Ltd. All rights reserved.

3/16

2011.10 - Rev.

BU9897GUL-W

A

A

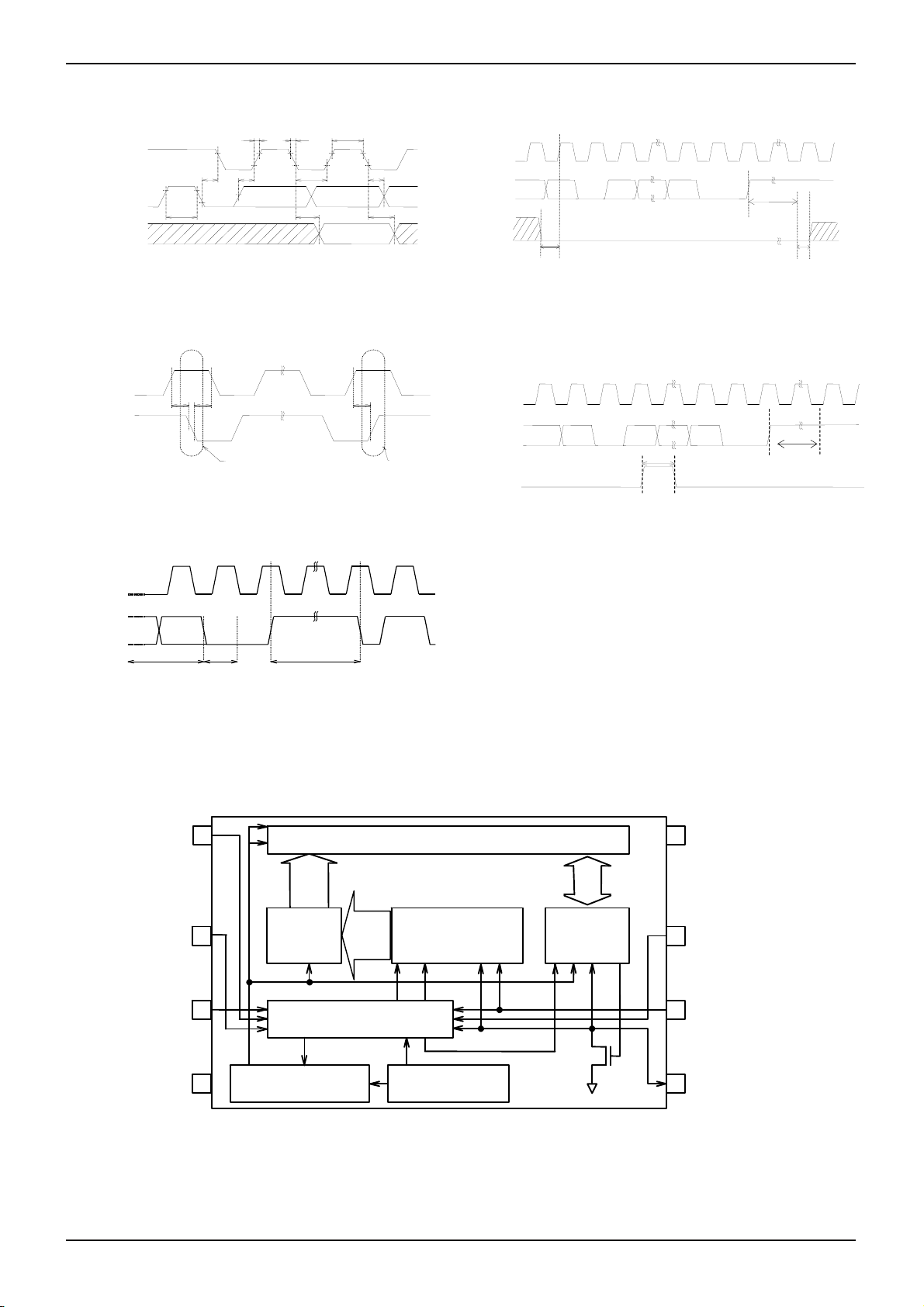

●Pin assignment and description

Land No.

Terminal

name

C4 GND - Please set this OPEN. Please don’t connect this GND.

C3 A1 Input Slave address

C

VSS

A2

A1

VSS

B

SDA

A0

VSS

SCL WP

1

2

Vcc

34

VSS

Fig.3 BU9897GUL-W(bottom view)

Input / output Function

Technical Note

C2 A2 input Slave address

C1 GND

B4 GND

-

-

Reference voltage of all input / output

Please set this OPEN. Please don’t connect this GND.

B3 A0 input Slave address

B1 SDA Input / output Slave and word address, Serial data input serial data output

A4 GND

A3 Vcc

-

-

Please set this OPEN. Please don’t connect this GND.

Power Supply

A2 WP input Write protect terminal

A1 SCL input Serial clock input

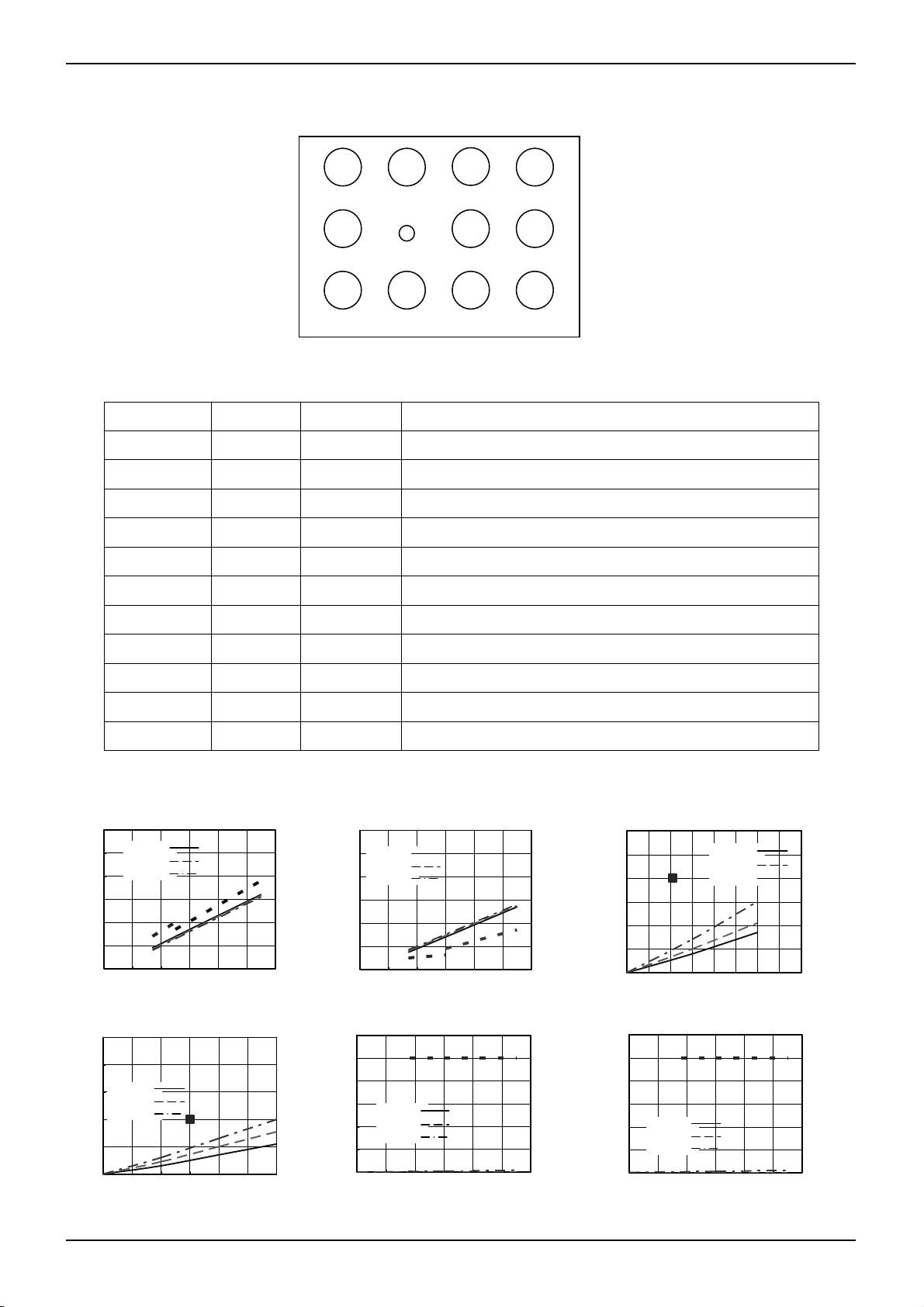

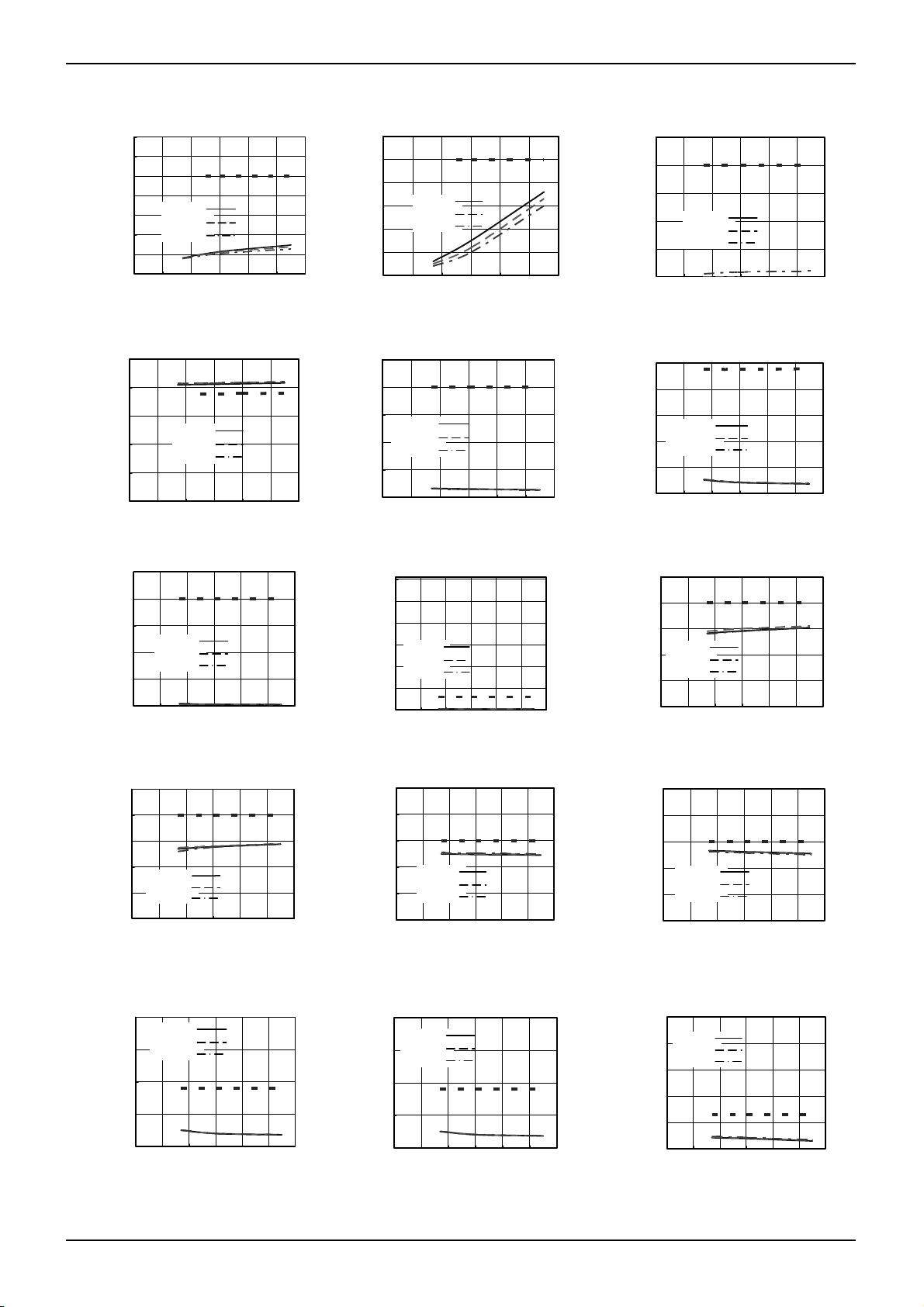

●Characteristic data (The following values are Typ. ones.)

6

Ta=-40℃

5

Ta=25℃

(V)

IH

Ta=85℃

4

3

2

H INPUT VOLTAGE : V

1

0

0123456

1

(V)

0.8

OL

Ta=-40℃

0.6

Ta=25℃

Ta=85℃

0.4

SPEC

SUPPLY VOLTAGE : Vcc(V)

Fig.4 'H' input voltage V

(A0,A1,A2,SCL,SDA,WP)

SPEC

0.2

L OUTPUT VOLTAGE : V

0

0123456

L OUTPUT CURRENT : I

Fig.7 'L' output voltage VOL-IOL(Vcc=2.5V)

IH

(mA)

OL

6

5

Ta=-40℃

(V)

Ta=25℃

IL

Ta=85℃

4

3

2

L INPUT VOLTAGE : V

1

0

0123456

SUPPLY VOLTAGE : Vcc(V)

Fig.5 'L' input voltage V

(A0,A1,A2,SCL,SDA,WP)

1.2

(uA)

LI

0.8

0.6

0.4

0.2

INPUT LEAK CURRENT : I

1

0

0123456

SPEC

Ta=-40℃

Ta=25℃

Ta=85℃

SUPPLYVOLTAGE : Vcc(V)

Fig.8 Input leak current I

SPEC

IL

(A0,A1,A2,SCL,WP)

LI

0.6

0.5

(V)

L OUTPUT VOLTAGE : V

OL

(uA)

LO

OUTPUT LEAK CURRENT : I

0.4

0.3

0.2

0.1

0

1.2

0.8

0.6

0.4

0.2

SPEC

012345678

L OUTPUT CURR ENT : I

Fig.6 'L' output voltage VOL-IOL(Vcc=1.7V)

1

Ta=-40℃

Ta=25℃

Ta=85℃

0

0123456

SUPPLY VOLTAGE : Vcc(V)

Fig.9 Output leak current I

Ta=-40℃

Ta=25℃

Ta=85℃

SPEC

(mA)

OL

(SDA)

LO

www.rohm.com

© 2011 ROHM Co., Ltd. All rights reserved.

4/16

2011.10 - Rev.

BU9897GUL-W

A

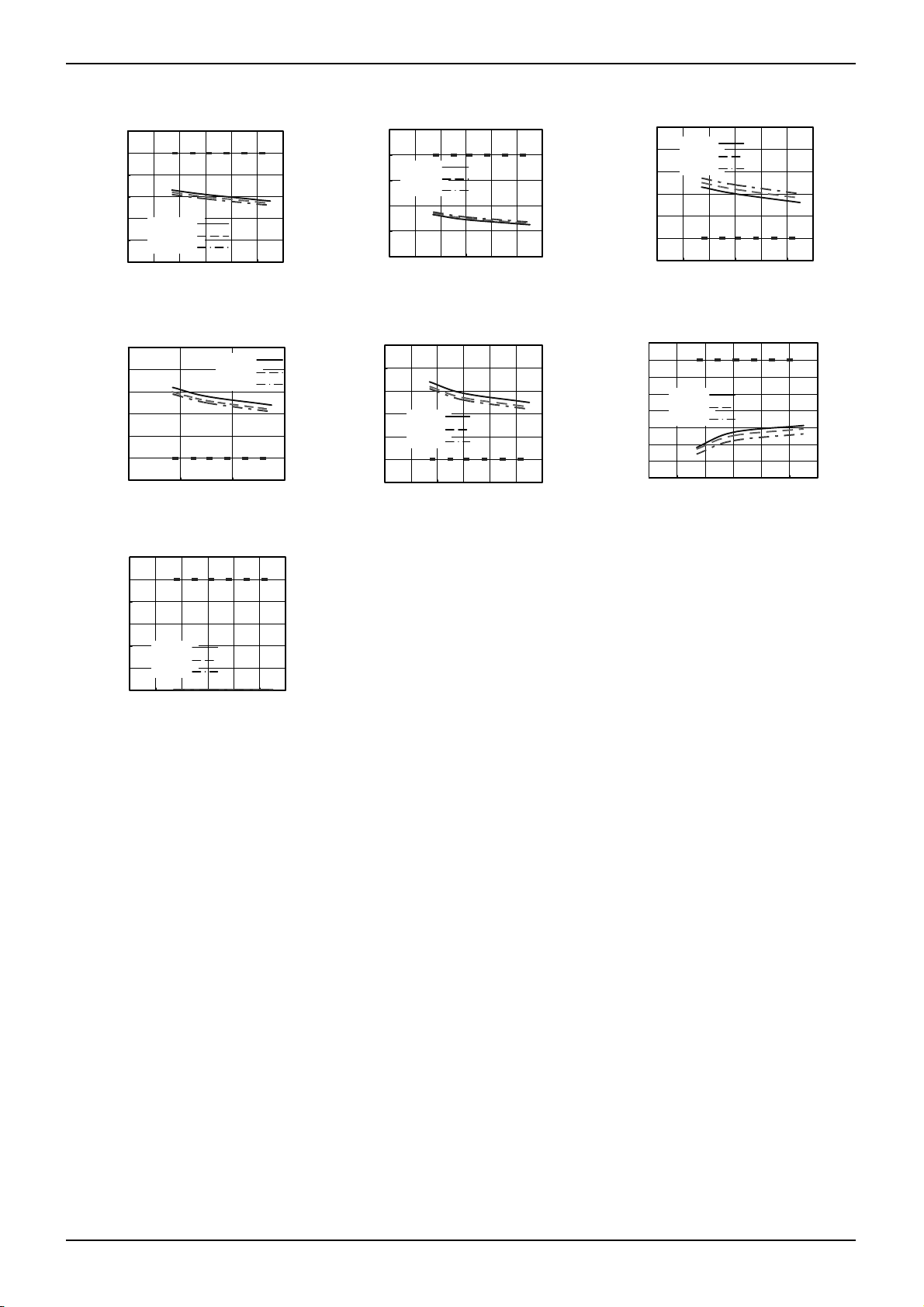

●Characteristic data (The following values are Typ. ones.)

2.5

3.5

3

2

2.5

1.5

2

Ta=-40℃

Ta=-40℃

Ta=25℃

1.5

Ta=25℃

1

Ta=85℃

Ta=85℃

1

AT WRITING : Icc1(mA)

0.5

CURRENT CONSUMPTION

AT WRITING : Icc1(mA)

0.5

CURRENT CONSUMPTION

0

0

0123456

0123456

SUPPLY VOLTAGE : Vcc(V)

SUPPLY VOLTAGE : Vcc(V)

Fig.10 Current consumption at WRITE operation ICC1

10000

SPEC

SPEC

(fscl=400kHz)

0.6

0.5

0.4

0.3

0.2

AT READING : Icc2(mA)

0.1

CURRENT CONSUMPTION

Fig.11 Current consumption at READ operation I

Ta=-40℃

Ta=25℃

Ta=85℃

0

0123456

5

1000

100

10

1

SCL FREQUENCY : fscl(kHZ)

0.1

0123456

SUPPLY VOLTAGE : Vcc(V)

Fig.13 SCL frequency f

(us)

5

HD : STA

4

3

Ta=-40℃

2

Ta=25℃

Ta=85℃

1

0

START CONDITION HOLD TIME : t

0123456

SUPPLY VOLTAGE : Vcc(V)

Ta=-40℃

Ta=25℃

Ta=85℃

SPEC

SPEC

SCL

4

(uA)

HIGH

3

Ta=-40℃

Ta=25℃

2

Ta=85℃

1

DATA CLK H TIME : t

0

0123456

SUPPLY VOLTAGE : Vcc(V)

Fig.14 Data clock High Period t

5.9

4.9

3.9

2.9

Ta=-40℃

Ta=25℃

1.9

Ta=85℃

START CONDITION

0.9

SET UP TIME : tSU:STA(uA)

-0.1

0123456

Fig.16 Start Condition Hold Time t

HD : STA

Fig.17 Start Condition Setup Time t

50

(ns)

0

HD :DAT

-50

-100

-150

INPUT DATA HOLD TIME : t

-200

0123456

Fig.19 Input Data Hold Time

SPEC

Ta=-40℃

Ta=25℃

Ta=85℃

SUPPLY VOLTAGE : Vcc(V)

t

HD : DAT

(LOW)

300

(ns)

200

SU: DAT

100

0

-100

-200

INPUT DATA SE T UP TIME : t

0123456

Fig.20 Input Data Setup Time

(us)

4

Ta=-40℃

PD

Ta=25℃

3

Ta=85℃

2

SPEC

(us)

PD

4

3

2

Ta=-40℃

Ta=25℃

Ta=85℃

1

1

0

OUTPUT DATA DELAY TIME : t

0123456

SUPPLY VOLTAGE : Vcc(V)

' Data output delay time

Fig.22 'L

tPD0

OUTPUT DATA DELAY TIME : t

0

0123456

Fig.23 'H' Data output delay time

SPEC

SUPPLY VOLTAGE : Vcc(V)

(fscl=400kHz)

SPEC

SPEC

SUPPLY VOLTAGE : Vcc(V)

SPEC

Ta=-40℃

Ta=25℃

Ta=85℃

SUPPLY VOLTAGE : Vcc(V)

t

SPEC

SUPPLY VOLTAGE : Vcc(V)

SU: DAT

SU : STA

(HIGH)

tPD1

HIGH

Technical Note

2.5

SPEC

SPEC

SPEC

SPEC

SPEC

HD : DAT

SU : DAT

SB

LOW

(HIGH)

(LOW)

t

BUF

2

(uA)

SB

1.5

Ta=-40℃

1

Ta=25℃

Ta=85℃

0.5

STANBY CURRENT : I

0

0123456

SUPPLY VOLTAGE : Vcc(V)

2

CC

(ns)

HD: STA

INPUT DATA HOLD TIME : t

(ns)

SU : DAT

INPUT DATA SET UP TIME : t

Fig.12 Stanby operation I

5

(us)

4

LOW

3

Ta=-40℃

Ta=25℃

2

Ta=85℃

1

DATA CLK L TIME : t

0

0123456

SUPPLY VOLTAGE : Vcc(V)

Fig.15 Data clock Low Period t

50

0

-50

Ta=-40℃

-100

Ta=25℃

Ta=85℃

-150

-200

0123456

SUPPLY VOLTAGE : Vcc(V)

Fig.18 Input Data Hold Time t

300

200

100

0

Ta=-40℃

Ta=25℃

-100

Ta=85℃

-200

0123456

SUPPLY VOLTAGE : Vcc(V)

Fig.21 Input Data setup time t

5

(us)

Ta=-40℃

BUF

4

Ta=25℃

Ta=85℃

3

2

BUS OPEN TIME

1

BEFORE TRANSMISSION : t

0

0123456

SUPPLY VOLTAGE : Vcc(V)

Fig.24 BUS open time before transmission

www.rohm.com

© 2011 ROHM Co., Ltd. All rights reserved.

5/16

2011.10 - Rev.

BU9897GUL-W

A

●Characteristic data (The following values are Typ. ones.)

6

5

(ms)

WR

4

3

2

INTERNAL WRITING

CYCLE TIME : t

1

0

0123456

Fig.25 Internal writing cycle time

SPEC

Ta=-40℃

Ta=25℃

Ta=85℃

SUPPLY VOLTAGE : Vcc(V)

t

WR

1

0.8

Ta=-40℃

(SCL H) (us)

Ta=25℃

l

0.6

Ta=85℃

0.4

NOISE REDUCTION

0.2

EFECTIVE TIME : t

0

0123456

SUPPLY VOLTAG E : Vcc(V)

Fig.26 Noise reduction efection time

0.6

0.5

0.4

(SDA H)(us)

l

0.3

0.2

NOISE REDUCTION

0.1

EFECTIVE TIME : t

0

0246

SUPPLY VOLATGE : Vcc(V)

Fig.28 Noise resuction efecctive time

1.2

(us)

1

HIGH : WP

0.8

0.6

0.4

Ta=-40℃

Ta=25℃

0.2

WP EFFECTIVE TIME : t

Ta=85℃

0

0123456

SUPPLYVOLTAGE : Vcc(V)

Fig.31 WP efective time

SPEC

SPEC

Ta=-40℃

Ta=25℃

Ta=85℃

t

HIGH : WP

(SDA H)

t

l

0.6

0.5

0.4

(SAD L)(us)

l

0.3

Ta=-40℃

Ta=25℃

0.2

NOISE REDUCTION

Fig.29 Noise reduction efective time t

Ta=85℃

0.1

EFFECTIVE TIME : t

0

0123456

SUPPLY VOLTAGE : Vcc(V)

SPEC

SPEC

(SCL H)

t

l

SDA L

(

l

Technical Note

0.6

Ta=-40℃

0.5

Ta=25℃

Ta=85℃

0.4

(SCL L)(us)

l

0.3

0.2

NOISE REDUCTION

0.1

EFECTIVE TIME : t

0

0123456

Fig.27 Noise reduction efective time

0.2

0.1

(us)

0

SU : WP

-0.1

-0.2

-0.3

-0.4

WP SET UP TIME : t

-0.5

-0.6

0123456

)

SPEC

SUPPLY VOLTAGE : Vcc(V)

SPEC

Ta=-40℃

Ta=25℃

Ta=85℃

SUPPLY VOLTAGE : Vcc(V)

Fig.30 WP setup time

t

SU : WP

t

(SCL L)

l

www.rohm.com

© 2011 ROHM Co., Ltd. All rights reserved.

6/16

2011.10 - Rev.

Loading...

Loading...