Serial-in / Parallel-out Driver Series

Serial / Parallel

4-input Drivers

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

●Description

Serial-in-parallel-out driver incorporates a built-in shift register and a latch circuit to control a maximum of 24 LED by a 4-line

interface, linked to a microcontroller.

A single external resistor can set the output current value of the constant current up to a maximum of 50mA. (BD7851FP only)

CMOS open drain output type products can drive the maximum current of 25mA.

●Features

1) LED can be driven directly.

2) Parallel output of a maximum of 24 bit

3) Operational on low voltage (2.7V to 5.5V)

4) Cascade connection is possible (BU2050F and BU2092F,BU2092FV are not acceptable)

●Application

For AV equipment such as, audio stereo sets, videos and TV sets, PCs, control microcontroller mounted equipment.

●Product line-up

Parameter BU2050F BU2092F BU2092FV BU2099FV BD7851FP BU2152FS Unit

Output current 25 25 25 25 50 25 mA

Output line 8 12 12 12 16 24 line

Output type CMOS Open drain

Package SOP14 SOP18 SSOP-B20 SSOP-B20 HSOP25 SSOP-A32 -

Constant

current

CMOS -

No.09051EAT03

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

1/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

Technical Note

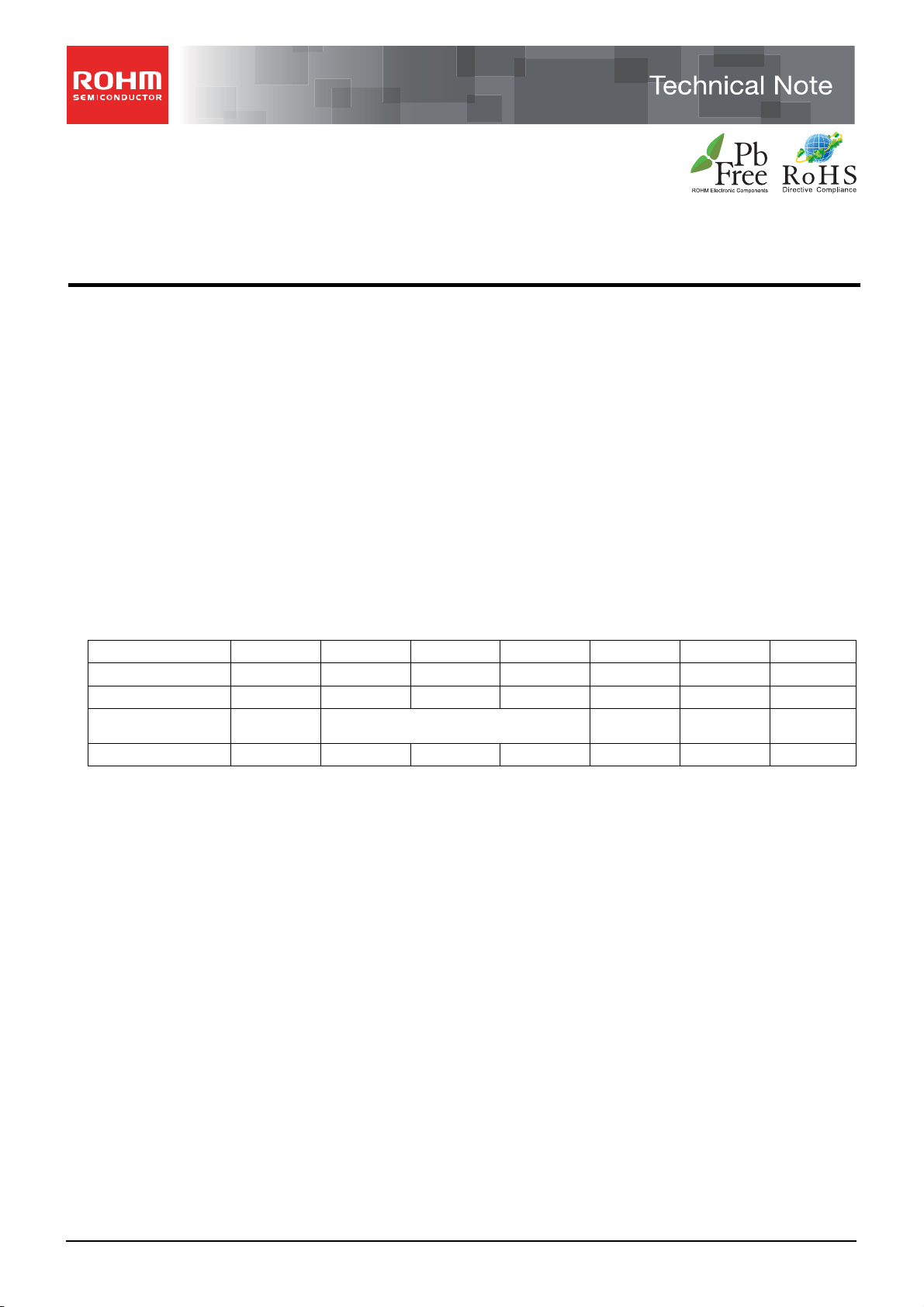

●Thermal derating curve

700

600

500

400

300

BU2050F

BU2099FV

700

600

500

400

300

BU2092F

BU2092FV

200

Power dissipation Pd [mW]

1600

1400

1200

1000

Power dissipation Pd [mW]

100

800

600

400

200

0

25 50

Ambient temperature Ta [℃]

0

25 50

Ambient temperature Ta [℃]

85℃

75 100

85℃

75 100

125 150

BD7851FP

BU2152FS

125 150

175

175

200

Power dissipation Pd [mW]

100

0

25 50

75 100

Ambient temperature Ta [℃]

125 150

175

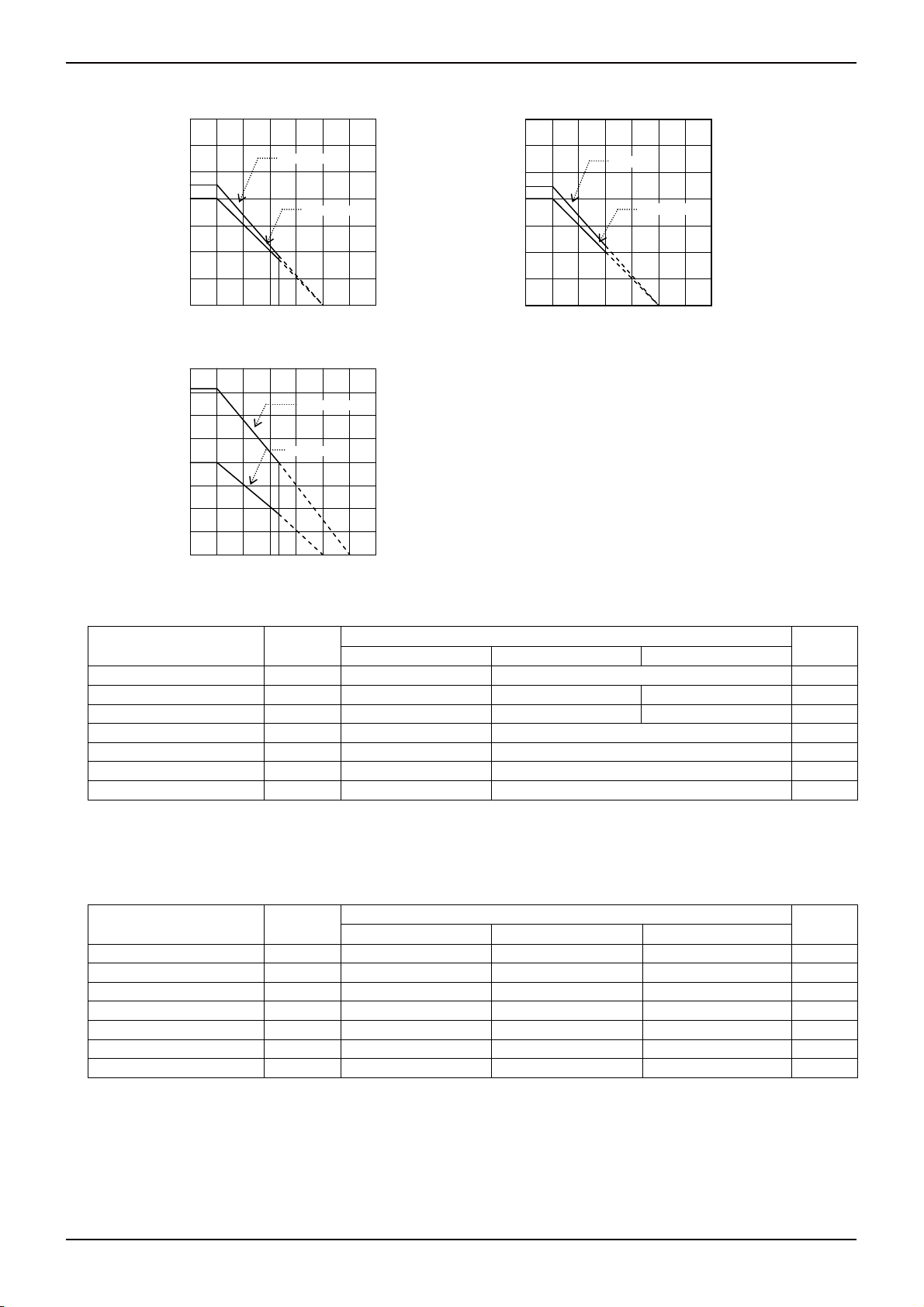

●Absolute maximum ratings (Ta=25℃)

Parameter Symbol

BU2050F BU2092F BU2092FV

Limits

Unit

Power Supply Voltage VDD -0.3 to +7.0 -0.3 to +7.0 V

Power dissipation 1 Pd1 450 *1 450 (SOP) *2 400 (SSOPB) *3 mW

Power dissipation 2 Pd2 - 550 (SOP) *4 650 (SSOPB) *5 mW

Input Voltage VIN VSS-0.3 to VDD+0.5 VSS-0.3 to VDD+0.3 V

Output Voltage Vo VSS-0.3 to VDD+0.5 VSS to +25.0 V

Operating Temperature Topr -40 to +85 -25 to +75 ℃

Storage Temperature Tstg -55 to +125 -55 to +125 ℃

*1 Reduced by 4.5mW/℃ over 25℃

*2 Reduced by 4.5mW/℃ over 25℃

*3 Reduced by 4.0mW/℃ over 25℃

*4 Reduced by 5.5mW/℃ for each increase in Ta of 1℃ over 25℃ (When mounted on a board 50mm×50mm×1.6mm Glass-epoxy PCB).

*5 Reduced by 6.5mW/℃ for each increase in Ta of 1℃ over 25℃ (When mounted on a board 70mm×70mm×1.6mm Glass-epoxy PCB).

Parameter Symbol

BU2099FV BD7851FP BU2152FS

Limits

Unit

Power Supply Voltage VDD -0.3 to +7.0 0 to +7.0 -0.3 to +7.0 V

Power dissipation 1 Pd1 400 (SSOPB) *6 1450 *7 800 *8 mW

Power dissipation 2 Pd2 650 (SSOPB) *9 - - mW

Input Voltage VIN VSS-0.3 to VDD+0.3 -0.3 to VCC+0.3 VSS-0.3 to VDD+0.3 V

Output Voltage Vo VSS to +25.0 0 to +10 VSS-0.3 to VDD+0.3 V

Operating Temperature Topr -40 to +85 -30 to +85 -25 to +85 ℃

Storage Temperature Tstg -55 to +125 -55 to +150 -55 to +125 ℃

*6 Reduced by 4.5mW/℃ over 25℃

*7 Reduced by 11.6mW/℃ over 25℃

*8 Reduced by 8.0mW/℃ over 25℃

*9 Reduced by 6.5mW/℃ for each increase in Ta of 1℃ over 25℃ (When mounted on a board 70mm×70mm×1.6mm Glass-epoxy PCB).

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

2/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

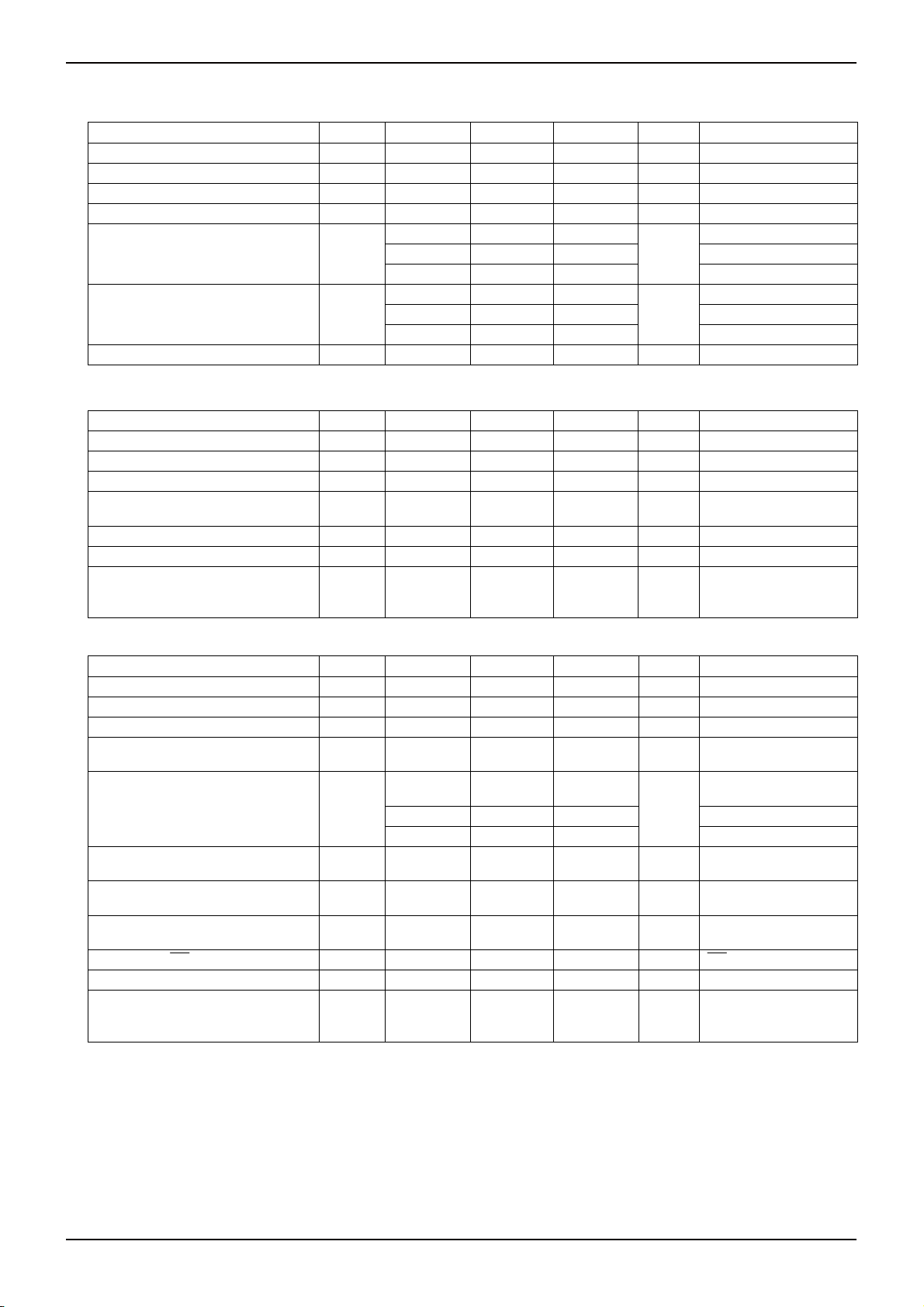

●Electrical characteristics

BU2050F (Unless otherwise noted, Ta=25℃, VDD=4.5 to 5.5V)

Parameter Symbol Min. Typ. Max. Unit Condition

Power Supply Voltage VDD 4.5 - 5.5 V

Input high-level Voltage VIH 0.7VDD - VDD V

Input low-level Voltage VIL VSS - 0.3VDD V

Input Hysteresis VHYS - 0.5 - V

V

DD-1.5 - VDD

Output high-level Voltage VOHD

VDD-1.0 - VDD

V

VDD-0.5 - VDD

V

SS - 1.5

Output low-level Voltage VOLD

VSS - 0.8

V

VSS - 0.4

Quiescent Current IDD - - 0.1 mA

BU2092F/BU2092FV (Unless otherwise noted, Ta=25℃, V

=0V, VDD=5.0V/3.0V)

SS

Parameter Symbol Min. Typ. Max. Unit Condition

Power Supply Voltage VDD 2.7 - 5.5 V

Input high-level Voltage VIH

3.5 / 2.5

- - V

Input low-level Voltage VIL - - 1.5 / 0.4 V

Output low-level Voltage VOL - - 2.0 / 1.0 V

Output high-level disable Current IOZH - - 10.0 μA

Output low-level disable Current IOZL - - -5.0 μA

Quiescent Current IDD - - 5.0 / 3.0 μA

BU2099FV (Unless otherwise noted, Ta=25℃, V

=0V, VDD=5.0V/3.0V)

SS

Parameter Symbol Min. Typ. Max. Unit Condition

Power Supply Voltage VDD 2.7 - 5.5 V

Input high-level Voltage VIH 3.5 / 2.1 - - V

Input low-level Voltage VIL - - 1.5 / 0.9 V

Output high-level Voltage (SO) VOH

V

/ V

DD-0.3

- - V

DD-0.5

- - 1.0

Output low-level Voltage 1 (Qx) VOL1

- - 1.5

V

- - 2.0

Output low-level Voltage 2 (SO) VOL2 - - 0.4 / 0.3 V

Output high-level disable Current

(Qx)

Output low-level disable Current

(Qx)

IPULLDOWN (OE)

OZH - - 10 μA VO=25.0V

I

OZL - - -5.0 μA VO=0V

I

IPD - - 150 / 60 μA

Low Voltage Reset VCLR 1.1 - 2.4 V

Quiescent Current IDD - - 200 μA

Technical Note

IOH=-25mA

IOH=-15mA

OH=-10mA

I

IOL=25mA

IOL=15mA

OL=10mA

I

VIH=VDD, VIL=VSS

DD=5V/3V

V

DD=5V/3V

V

DD=5V/3V,

V

OL=20mA/5mA

I

VO=25.0V

VO=0V

VIN=VSS or VDD

(VDD=5V/3V)

OUTPUT:OPEN

DD=5V/3V

V

VDD=5V/3V

V

DD=5V/3V,

OH=-400μA/-100μA

I

DD=5V/3V,

V

OL1=10mA/5mA

I

DD=5V, IOL1=15mA

V

VDD=5V, IOL1=20mA

DD=5V/3V,

V

OL2=1.5mA/0.5mA

I

OE= VDD, VDD=5V/3V

VIN=VSS or VDD,

VDD=5V

OUTPUT:OPEN

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

3/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

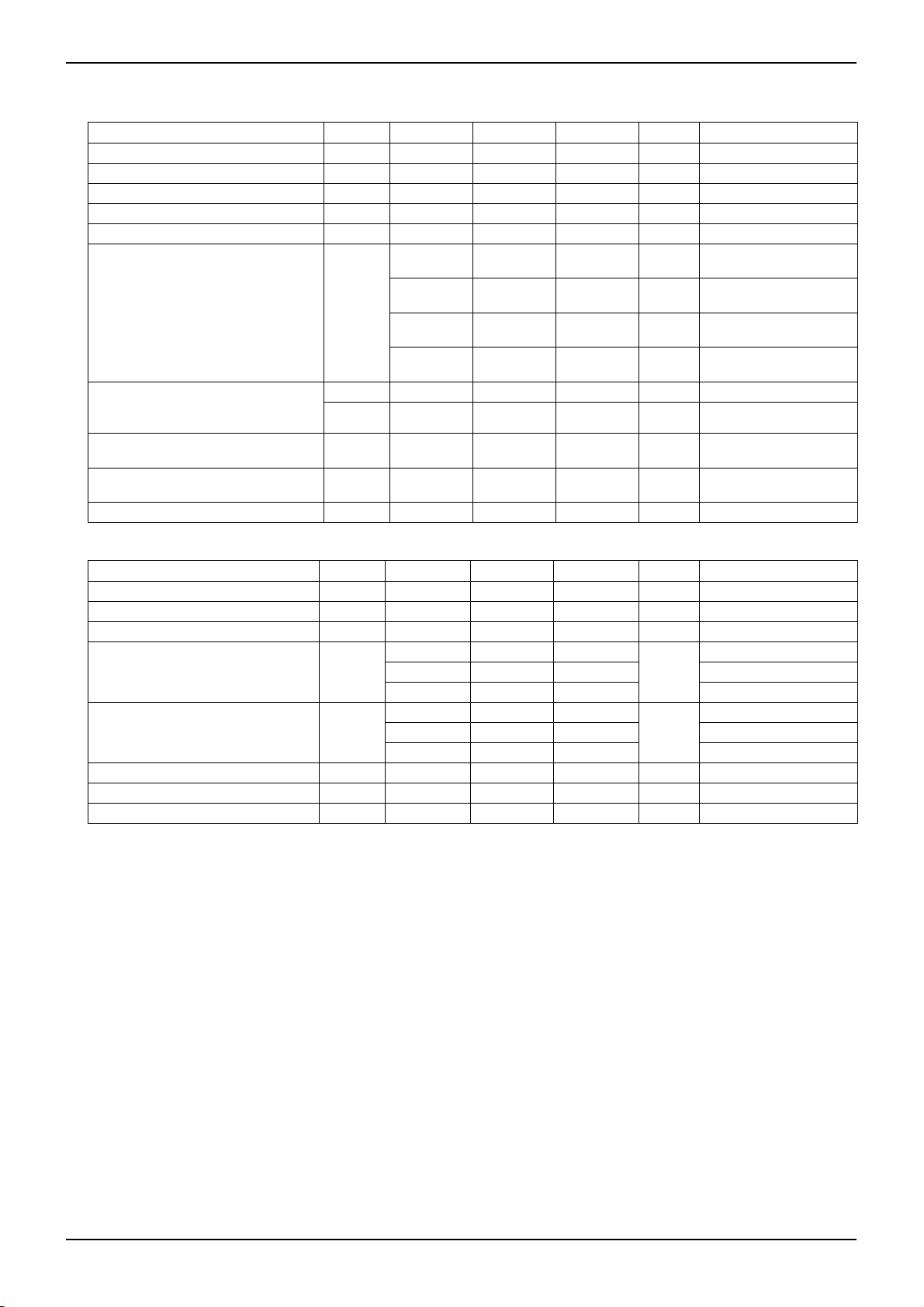

●Electrical characteristics

BD7851FP (Unless otherwise noted, Ta=25℃, VCC=5.0V)

Parameter Symbol Min. Typ. Max. Unit Condition

Power Supply Voltage VDD 4.5 - 5.5 V

Input high-level Voltage VIH

0.8×VCC

- - V

Input low-level Voltage VIL - - 0.2×VCC V

Output high-level Voltage VOH VCC-0.5 - - V

Output low-level Voltage VOL - - 0.5 V

- 0.7 1.0 mA

- 1.8 3.0 mA

Quiescent Current ICC

- 4.0 6.5 mA

- 30 40 mA

Reference Current Output Current

(including the equation between

each bit)

Equation between each bit of

Reference Current Output Current

Change rate of reference current

output current for output voltage

Iolc1 48 55 62 mA

Iolc2 5.0 5.9 6.8 mA VOUT=2.0V, R=13kΩ

Δiolc - ±1 ±6 %

CC - ±1 ±6 %/V

IΔV

Output Leak Current IOH - 0.01 0.8 μA

BU2152FS (Unless otherwise noted, Ta=25℃, V

=2.7 to 5.5V)

DD

Parameter Symbol Min. Typ. Max. Unit Condition

Power Supply Voltage VDD 2.7 - 5.5 V

Input high-level Voltage VIH

2.0

- - V

Input low-level Voltage VIL - - 0.6 V

VDD-1.5 - -

Output high-level Voltage VOH

VDD-1.0 - -

V

VDD-0.5 - -

- - 1.5

Output low-level Voltage VOL

- - 1.0

V

- - 0.8

Quiescent Current IDDST - - 5 μA

Input high-level Current IIH

-

- 1 μA

Input low-level Current IIL - - 1 μA

Technical Note

OH=-1mA

I

IOL=1mA

R=13kΩ

OUT1~OUT16:OFF

R=1.3kΩ

OUT1~OUT16:OFF

R=13kΩ

OUT1~OUT16:ON

R=1.3kΩ

OUT1~OUT16:ON

VOUT=2.0V, R=1.3kΩ

OUTn=2.0V, R=1.3kΩ

V

(1bit : ON)

OUT=2.0 to 3.0V,

V

R=1.3kΩ

VOUT=10V

DD=5V

V

VDD=5V

IOH=-25mA

OH=-15mA

I

IOH=-10mA

IOL=25mA

OL=15mA

I

IOL=10mA

V

IL=VSS, VIH=VDD

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

4/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

A

A

A

A

f

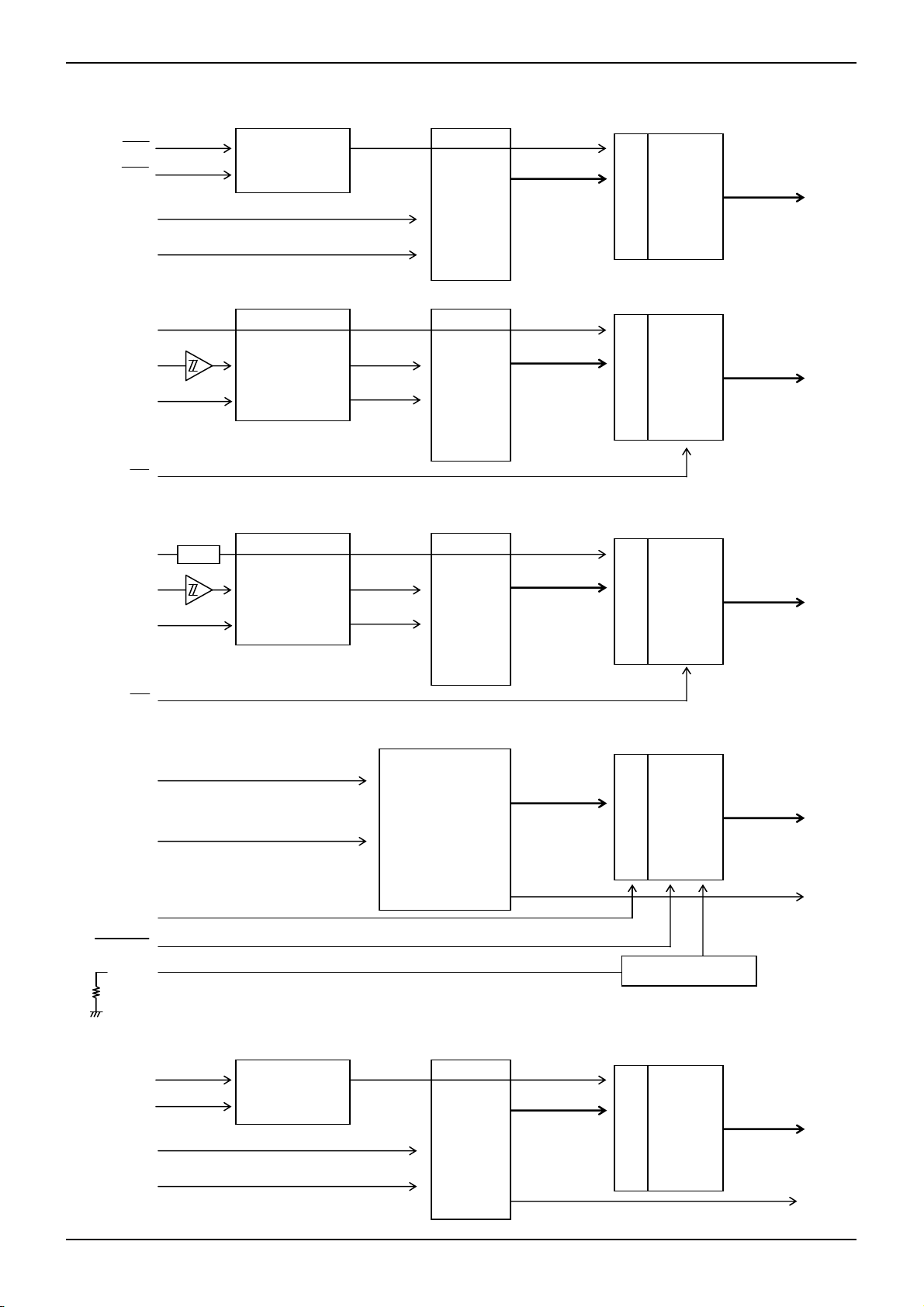

●Block diagram

BU2050F

STB

CLR

CLOCK

Controller

Shift

Register

8bit

DAT

BU2092F/BU2092FV

LCK

CLOCK

DAT

Controller

Shift

Register

12bit

OE

BU2099FV

LCK

CLOCK

DAT

LPF

Controller

Shift

Register

12bit

OE

BD7851FP

S_IN

CLOCK

Shift

Register

16bit

LATCH

ENABLE

R_Ire

BU2152FS

STB

CLB

CLOCK

DAT

Controller

Shift

Register

24bit

Technical Note

L

a

t

c

h

L

a

t

c

h

L

a

t

c

h

L

a

t

c

h

Current Adjustment

L

a

t

c

h

Write

Buffer

Write

Buffer

Write

Buffer

Write

Buffer

Write

Buffer

P1~P8

Q0~Q11

Q0~Q11

OUT1~OUT16

SOUT

P1~P24

SO

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

5/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

t

t

Technical Note

●Operating description

(1) Data clear

When the reset terminal (CLR, CLB) is set to “L”, the content of all latch circuits are set to “H”, and all parallel outputs are

initialised. (For model with reset terminal only)

(2) Data transfer

Serial data is sequentially input to the shift register during the rise of the clock time (strobe signal is not active). When

the strobe signal is active, the content of the shift register are transferred to the latch circuit.

(3) Cascade connection

Serial input data is output from the serial output through the shift register, regardless of the strobe signal.

(except for BU2050F,

BU2092F/BU2092FV)

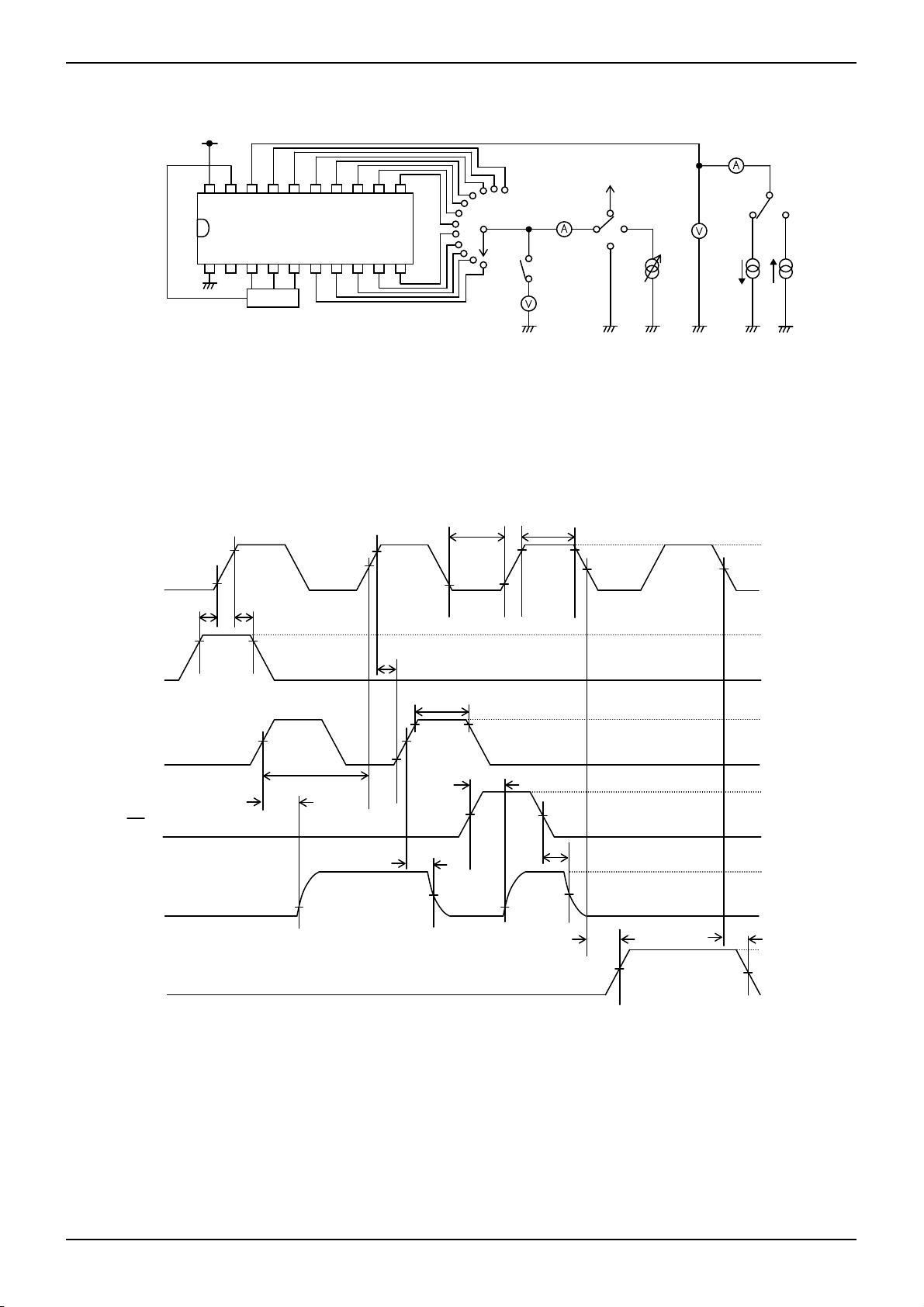

●Application circuit

VDD

MPU

VSS

C1

(*)

VDD

Serial data input

Clock input

Strobe input

Latch input

P1 P2 Pn-2 Pn-1 Pn

VSS

Serial data outpu

VDD

Serial data input

Clock input

Strobe input

Latch input

P1 P2 Pn-2 Pn-1 Pn

VSS

Serial data outpu

(*C1 must be placed as close to the terminal as possible.)

Fig. 1

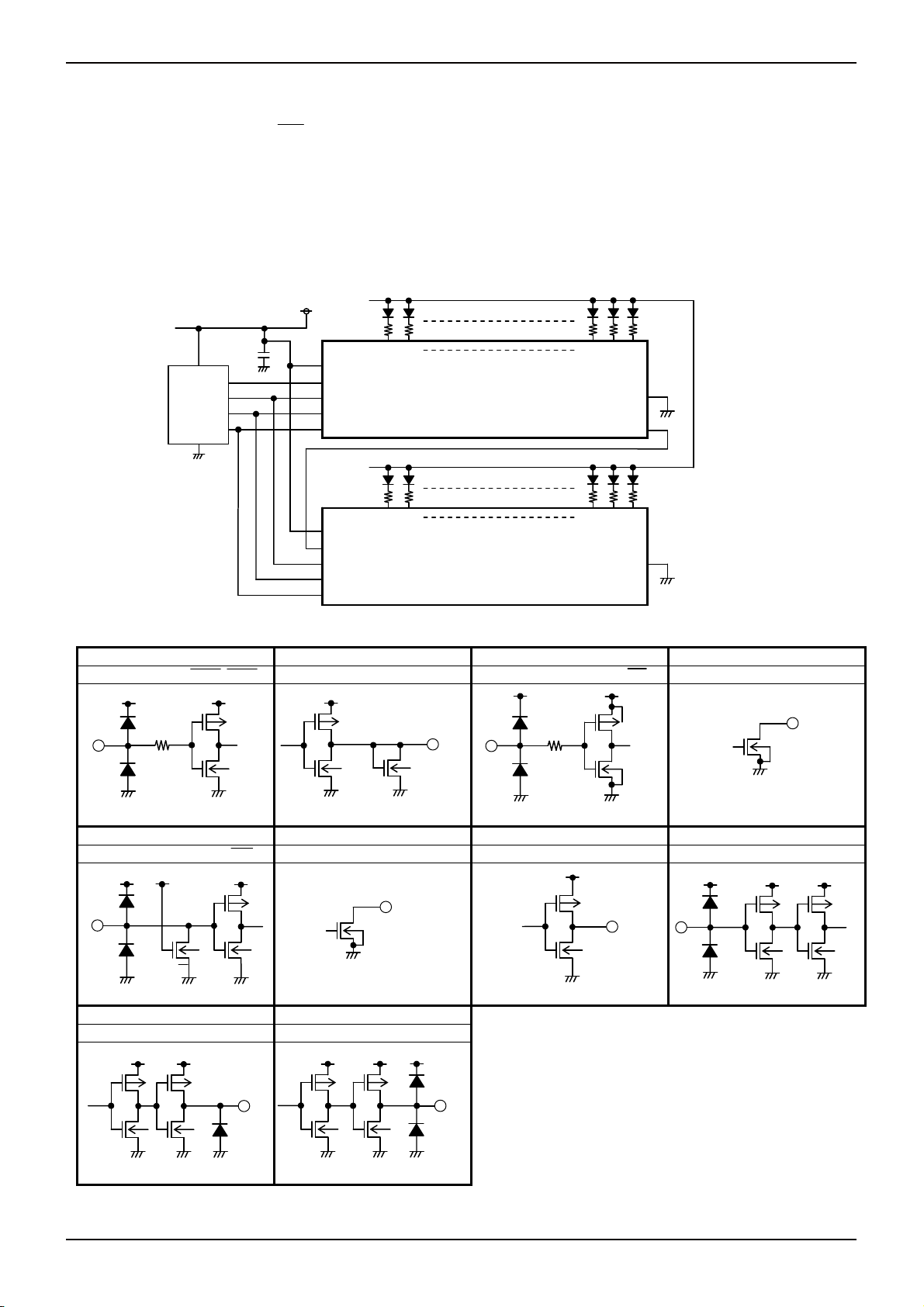

●Interfaces

BU2050F BU2050F BU2092F/BU2092FV BU2092F/BU2092FV

DATA, CLOCK, STB, CLR P1~P8 DATA, CLOCK, LCK, OE Q0~Q11

V

INPUT

V

DD

DD

OUTPUT

IN

VDD

V

DD

GND(VSS)

GND(VSS)

GND(VSS)

GND(VSS)

GND(VSS)

GND(VSS)

GND(VSS)

BU2099FV BU2099FV BU2099FV BU2152FS

DATA, CLOCK, LCK, OE Q0~Q11 SO CLOCK, DATA, STB, CLB

VDD

VDD

IN

VDD

OUT

V

DD

OUT

VDD

V

DD VDD

GND(VSS)

(only OE pin)

GND(VSS)

GND(VSS)

GND(VSS)

GND(VSS)

GND(VSS)

GND(VSS)

BU2152FS BU2152FS

P1~P28 SO

V

V

DD VDD

DD VDD VDD

VSS

VSS

VSS

GND(VSS)

GND(VSS) GND(VSS)

OUT

GND(VSS)

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

6/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

【BU2050F】

●Pin descriptions

Pin No. Pin Name Function

1 P3

2 P4

Parallel Data Output

3 P5

4 VSS GND

5 P6

6 P7

Parallel Data Output

7 P8

8 DATA Serial Data Input

9 CLK Clock Signal Input

Strobe Signal Input

10 STB

In case of “L”, the data of shift register outputs.

In case of “H”, all parallel outputs and data of latch circuit do not change.

Reset Signal Input

11 CLR

In case of “L”, the data of latch circuit reset, and all parallel output (P1~P8) can be L.

Normally CLR=H

12 P1

13 P2

Parallel Data output

14 VDD Power Supply

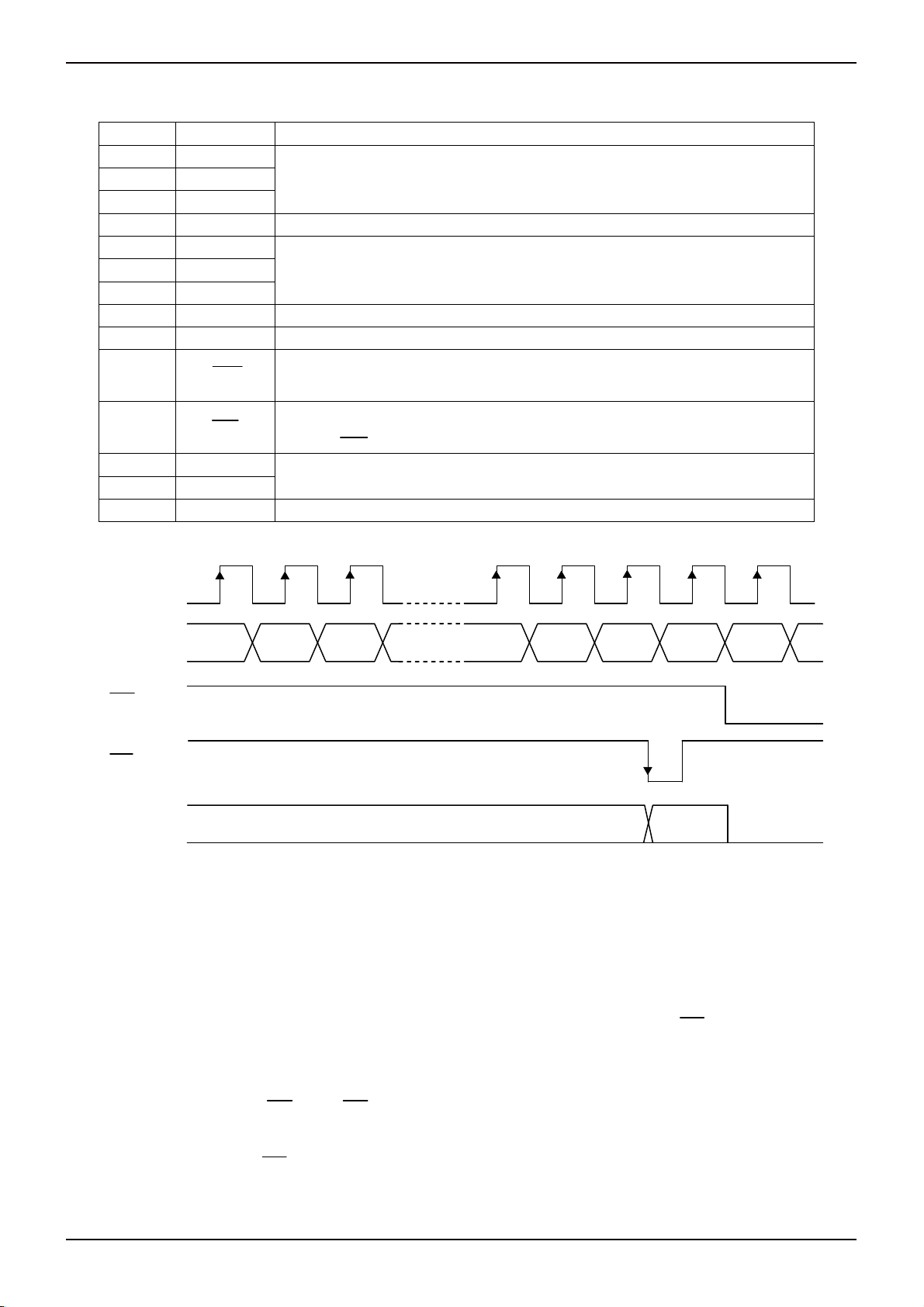

●Timing chart

CLK

Technical Note

DATA

DATA8 DATA7 DATA6 DATA2 DATA1

CLR

STB

Pn

Previous DATA DATA

“L”

Fig. 2

1. After the power is turned on and the voltage is stabilized, STB should be activated, after clocking 8 data bits into the

DATA pin.

th

2. Pn parallel output data of the shift register is set after the 8

clock by the STB.

3. Since the STB is level latch, data is retained in the “L” section and renewed in the “H” section of the STB.

[Function explanation]

・ A latch circuit has the reset function, which is common in all bits. In case of CLR terminal is “L”, the latch

circuit is reset non-synchronously without the other input condition, and all parallel output can be “L”.

・ A serial data inputted from DATA terminal is read in shift register with synchronized rising of clock.

In case of STB is “L” (CLR is ”H”), transmit the data which read in the shift register to latch circuit, and

outputs from the parallel data output terminal (P1~P8).

In case of STB is “H”, all parallel outputs and the data of latch do not change.

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

7/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

R

●Switching characteristics (Unless otherwise specified, VDD=4.5 to 5.5V, Ta=25℃)

Parameter Symbol

Min. Typ. Max.

Limit

Unit Condition

Set up time (DATA-CLK) tSD 20 - - ns -

Hold time (DATA-CLK) tHD 20 - - ns -

t

30 - - ns -

Set up time CLK)STB(

Hold time CLK)STB(

Propagation P8)P1CLR( ~

Propagation P8)P1STB( ~

Propagation

P8)P1CLR( ~

Maximum clock frequency f

SSTB

t

30 - - ns -

HSTB

t

- - 100 ns P1~P8 terminal load 20pF or less

PDPCK

t

- - 80 ns P1~P8 terminal load 20pF or less

PDPSTB

t

- - 80 ns P1~P8 terminal load 20pF or less

PDPCLR

5 - - MHz -

MAX

●Switching Time Test Waveform

CLK

tSD

f

MAX

1 2 8 9 10 11 12

DATA

tHD

STB

CLR

t

HSTB

t

SSTB

P8

P1

t

PDPSTB

Fig. 3

t

PDPCL

t

PDPCK

Technical Note

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

8/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

A

【BU2092F/BU2092FV】

●Pin descriptions

Pin No. Pin Name I/O Function

1 VSS - GND

2 DATA I Serial Data Input

3 CLOCK I Shift clock of DATA (Rising Edge Trigger)

4 LCK I Latch clock of DATA (Rising Edge Trigger)

Technical Note

5~11,

14~18

Q0~Q11 O

12, 13 N.C. - Non connected

17 OE I Output Enable (“H” level : output FET is OFF)

18 VDD - Power Supply

●Timing chart

CLOCK

DATA

DATA11 DATA10 DATA9 DATA1 DATA0

LCK

OE

Qx

“H”

Previous DAT

1. After the power is turned on and the voltage is stabilized, LCK should be activated, after clocking 12 data bits into

the DATA terminal.

2. Qx parallel output data of the shift register is set after the 12

3. Since the LCK is a label latch, data is retained in the “L” section and renewed in the “H” section of the LCK.

4. Data retained in the internal latch circuit is output when the OE is in the “L” section.

[Truth Table]

Input

CLOCK DATA LCK OE

× × × H Output (Q0~Q11) Disable

× × × L Output (Q0~Q11) Enable

L × ×

H × ×

× × × The data of shift register has no change.

× × × The data of shift register is transferred to the storage register.

× × × The data of storage register has no change.

Parallel Data Output (Nch Open Drain FET)

Latch Data L H

Output FET ON OFF

DATA11~0

Note) Diagram shows a status where a pull-up resistor is connected to output.

Fig. 4

th

clock by the LCK.

Function

Store “L” in the first stage data of shift register, the previous stage data in the

others. (The conditions of storage register and output have no change.)

Store “H” in the first stage data of shift register, the previous stage data in the

others. (The conditions of storage register and output have no change.)

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

9/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

●Switching characteristics (Unless otherwise specified, VDD=5V, VSS=0V, Ta=25℃)

Limit

Parameter

Symbol

Unit

Min. Typ. Max. VDD(V)

Technical Note

Condition

Minimum Clock Pulse Width

Minimum Latch Pulse Width

(LCK)

Setup Time

(LCK→CLOCK)

Setup Time

(DATA→CLOCK)

Hold Time

(CLOCK→DATA)

Propagation

(LCK→OUTPUT QX)

Propagation

w

t

tw

(LCK)

s

t

su

t

t

H

PLZ

t

(LCK)

tPZL

(LCK)

PLZ

t

1000 - - ns 3

500 - - ns 5

1000 - - ns 3

500 - - ns 5

400 - - ns 3

200 - - ns 5

400 - - ns 3

200 - - ns 5

400 - - ns 3

200 - - ns 5

- 90 - ns 3

- 55 - ns 5

RL=5kΩ

CL=10pF

- 115 - ns 3 R

- 50 - ns 5

CL=10pF

- 70 - ns 3 R

- 45 - ns 5

C

-

-

-

-

-

L=5kΩ

L=5kΩ

L=10pF

( OE →OUTPUT QX)

●Switching Time Test Circuit

tPZL

Pulse

Gen.

Pulse

Gen.

Pulse

Gen.

Pulse

Gen.

- 80 - ns 3 R

- 35 - ns 5

VDD

CLOCK

LCK

DATA

OE

GND (Vss)

±25V

RL

Q0

CL

GND (Vss)

±25V

RL

Q11

CL

GND (Vss)

Fig. 5

L=5kΩ

C

L=10pF

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

10/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

)

)

)

)

)

【BU2092F/BU2092FV】

●Switching Time Test Waveforms

90%

90%

t

W

t

W

90% 90%

CLOCK

10%

tSU

10%

tH

10%

DATA

90% 90%

t

S

LCK

50%

10%

90%

50%

tW(CLK)

90%

OE

t

(LCK) t

PLZ

PZL

(LCK)

50%

t

PLZ

Qx

10%

50%

10%

Fig. 6

50%

50%

Technical Note

VDD

GND (VSS

VDD

GND (VSS

VDD

GND (VSS

VDD

t

PZL

GND (VSS

VDD

GND (VSS

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

11/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

【BU2099FV】

●Pin descriptions

Pin No. Pin Name I/O Function

1 VSS - GND

2 N.C. - Non connected

3 DATA I Serial Data Input

4 CLOCK I Shift clock of Shift register (Rising Edge Trigger)

5 LCK I Latch clock of Storage register (Rising Edge Trigger)

Technical Note

Parallel Data Output (Nch Open Drain FET)

Latch Data L H

Output FET ON OFF

6~17

Q0

~Q11

(Qx)

O

18 SO O Serial Data Output

19 OE I Output Enable Control Input *OE pin is pulled down to Vss.

20 VDD - Power Supply

●Timing chart

CLOCK

DATA

DATA12 DATA11 DATA10 DATA2 DATA1

LCK

OE

Qx

“H”

Previous DATA DATA

SO

Previous

DATA 11

Previous

DATA 11

Fig. 7

1. After the power is turned on and the voltage is stabilized, LCK should be activates, after clocking 12 data bits into

the DATA terminal.

2. Qx parallel output data of the shift register is set after the 12

th

clock by the LCK.

3. Since the LCK is a label latch, data is retained in the “L” section and renewed in the “H” section of the LCK.

4. Data retained in the internal latch circuit is output when the OE is in the “L” section.

5. The final stage data of the shift register is output to the SO by synchronizing with the rise time of the CLOCK.

[Truth Table]

Input

CLOCK DATA LCK

OE

Function

× × × H All the output data output “H” with pull-up.

× × × L The Q0~Q11 output can be enable and output the data of storage register.

L × ×

H × ×

× × ×

Store “L” in the first stage data of shift register, the previous stage data in the

others. (The conditions of storage register and output have no change.)

Store “H” in the first stage data of shift register, the previous stage data in the

others. (The conditions of storage register and output have no change.)

The data of shift register has no change.

SO outputs the final stage data of shift register with synchronized falling

edge of CLOCK, not controlled by OE.

× ×

× ×

*The Q0~Q11 output have a Nch open drain Tr. The Tr is ON when data from shift register is “L”, and Tr is OFF when data is “H”.

× The data of shift register is transferred to the storage register.

× The data of storage register has no change.

DATA12

DATA11

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

12/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

【BU2099FV】

●Switching characteristics (Unless otherwise specified, VDD=5V, VSS=0V, Ta=25℃)

Parameter Symbol

Minimum Clock Pulse Width

(CLOCK)

Minimum Latch Pulse Width

(LCK)

Setup Time

(LCK→CLOCK)

Setup Time

(DATA→CLOCK)

Hole Time

(CLOCK→DATA)

Propagation

(SO)

Propagation

(LCK→QX) *

Propagation

→QX) *

(

QE

Noise Pulse Suppression

Time (LCK) *

*Reference value

t

W

tW

(LCK)

t

S

t

su

t

H

t

PLH

t

PHL

t

PLZ

(LCK)

t

PZL

(LCK)

t

PLZ

t

PZL

t

I

Min. Typ. Max. VDD(V)

1000 - - ns 3

500 - - ns 5

1000 - - ns 3

500 - - ns 5

400 - - ns 3

200 - - ns 5

400 - - ns 3

200 - - ns 5

400 - - ns 3

200 - - ns 5

- - 500 ns 3 -

- - 250 ns 5 -

- 360 - ns 3

- 170 - ns 5

- 260 - ns 3 R

- 175 - ns 5

- 115 - ns 3

- 85 - ns 5

- 175 - ns 3 R

- 65 - ns 5

- 30 ns -

- 20 ns -

Limit

Unit

●Input Voltage Test Circuit

RL =10kΩ

●Switching Time Test Circuit

GND

(Vss)

VDD

P. G.

VIH

VIL

GND

Fig. 8

+25V

RL =5kΩ

C

L =10pF

GND

(Vss)

GND

(Vss)

P. G.

Fig. 9

+25V

RL =5kΩ

CL =10pF

GND

(Vss)

Technical Note

Condition

-

-

-

-

-

RL=5kΩ

L=10pF

C

L=5kΩ

L=10pF

C

R

L=5kΩ

L=10pF

C

L=5kΩ

L=10pF

C

-

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

13/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

【BU2099FV】

●Output Voltage Test Circuit

VDD

12

SW3

GND

(Vss)

P. G.

SW1

1

Test condition

V

OL1 :Set all data “L”. SW1=”ON”, SW2=”3”, SW3=”1”~”12”.

V

OL2 :Set output data “L” to SO and SW4 is positioned to “2”, then voltage is measured at IOL2.

V

OH :Set output data “H” to SO and SW4 is positioned to “1”, then voltage is measured at IOH.

GND

(Vss)

Fig. 10

●Switching Time Test Waveforms

t

(LCK)

W

10%

90%

t

PLZ

50%

CLOCK

10%

90%

DATA

tSU

90% 90%

tH

LCK

t

OE

PLZ

(LCK)

50%

t

2

S

50%

10%

90%

10%

t

S

tW (CLK)

90%

50%

t

PZL

t

W

90% 90%

50%

t

PZL

Qx

10%

50%

10%

50%

SO

Fig. 11

±25V

1

2

GND

(Vss)

50%

t

PLH

50%

Technical Note

SW2

3

IOL1

GND

(Vss)

GND

(Vss)

50%

50%

1

GND

(Vss)

t

PHL

SW4

IOL2IOH

GND

(Vss)

VDD

GND (VSS)

V

GND (VSS)

V

GND (VSS)

V

DD

GND (VSS)

V

GND (VSS)

VDD

GND (VSS)

2

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

14/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

【BD7851FP】

●Pin descriptions

Pin No. Pin Name Function

1 GND Ground

2 R_Iref Reference Current Output Current setting

3 LATCH Latch Signal Input

4 S_IN Serial Data Input

5~15

OUT16

~OUT6

Reference Current Output

16 P_GND Ground for Driver

17~21

OUT5

~OUT1

Reference Current Output

22 SOUT Serial Data Output

23 CLOCK Clock Input

24 ENABLE ENABLE

25 VCC VCC

●Timing chart

CLOCK

S_IN

DATA16 DATA15 DATA14 DATA2 DATA1

LATCH

ENABLE

OUTn

Previous DATA DATA

SOUT

Previous

DATA15

Previous

DATA14

Previous

DATA2

Previous

DATA1

Fig. 12

1. After the power is turned on and the voltage is stabilized, LATCH should be activated, after clocking 16 data bits

into the S_IN terminal.

2. OUTn parallel output data of the shift register is set after the 16

3. The final stage data of the shift register is outputted to the SOUT by synchronizing with the rise time of the

CLOCK.

4. Since the LATCH is a label latch, data is retained in the “L” section and renewed in the “H” section of the LATCH.

5. Data retained in the internal latch circuit is outputted when the ENABLE is in the “L” section. When the ENABLE

is in the “H” section, data is fixed in the “H” section.

th

clock by the LATCH.

DATA16

Technical Note

DATA15 DATA14

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

15/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

【BD7851FP】

●Timing characteristics (Unless otherwise specified, VCC=5V, Ta=25℃)

Parameter Symbol

Min. Typ. Max.

Limit

Unit Condition

Frequency CLOCK fclk - - 10 MHz

Pulse Width CLOCK twh 20 50 - ns CLOCK

Pulse Width LATCH twh 40 50 - ns LATCH

Pulse Width ENABLE tw 30 - - ns ENABLE

Rise Time / Fall Time tr / tf - 30 100 ns CLOCK

Setup Time tSU

Hold Time th

Rise Time tr

Fall Time tf

t

pLH

Propagation

t

pHL

30 50 -

30 50 - LATCH-CLOCK

30 50 -

30 50 - LATCH-CLOCK

- 300 -

- - 50 SOUT

- 300 -

- - 50 SOUT

- 400 650

- 300 400

ns

ns

ns

ns

ns

S_IN-CLOCK

S_IN-CLOCK

OUTn

OUTn

CLK-SOUT, LATCH

ENABLE-OUTn

CLK-SOUT, LATCH

ENABLE-OUTn

●Reference Current of Output Current

250

200

150

[mA]

OUT

I

100

[Condition]

Vcc=5.0V, Vo=5.0V, Ta=25℃

The reference current of output current is determined by the

external resistor.

(between 2pin and GND )

50

0

0.1 1 10 100

R_Iref [kΩ]

*This is a data for the standard sample, not guaranteed the characteristic.

Fig. 13

●R_Iref-VOUT

[V]

OUT

V

1.6

1.4

1.2

1.0

0.8

0.6

0.4

0.2

[Condition]

Vcc=5.0V, Ta=27℃, all bit : ON

0.0

1 10 100

R_Iref [kΩ]

*Notes the increase of consumption current Icc, in case sets the voltage of VOUT lower. See the graph above.

Fig. 14

Technical Note

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

16/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

_

_

_

_

【BD7851FP】

●Test Circuit 1

GND

LATCH

S_IN

1

R

R

Iref

2

LATCH

3

S

IN

4

OUT16

5

6

OUT15

BD7851FP

Vcc

ENABLE

CLOCK

SOUT

OUT1

OUT2

25

24

23

22

21

20

Vcc

7

8

9

10

11

12

13

OUT14

OUT13

OUT12

OUT11

OUT10

OUT9

OUT8

OUT3

OUT4

OUT5

P_GND

OUT6

OUT7

19

18

17

16

15

14

P_GND

Fig. 15

●Test Circuit 2

LATCH

S_IN

GND

1

R

R

Iref

2

LATCH

3

S

IN

4

OUT16

5

6

OUT15

BD7851FP

Vcc

ENABLE

CLOCK

SOUT

OUT1

OUT2

25

24

23

22

21

20

Vcc

7

8

9

10

11

12

13

OUT14

OUT13

OUT12

OUT11

OUT10

OUT9

OUT8

OUT3

OUT4

OUT5

P_GND

OUT6

OUT7

19

18

17

16

15

14

P_GND

*R=51Ω (note : R_Iref=1.3kΩ) , C=15pF

Fig. 16

Technical Note

ENABLE

CLOCK

SOUT

VE

ENABLE

CLOCK

SOUT

VE

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

17/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

【BD7851FP】

●Switching Time Test Waveforms

tr

CLOCK

S_IN

0.2×VCC

tSU

0.8×VCC 0.8×VCC

LATCH

OUTn

ENABLE

tWh

0.8×VCC 0.8× VCC

0.2×VCC

th

th

tf

0.8×VCC

t

wh

0.8×VCC

0.2×VCC

t

SU

t

pHL・tpLH

90%

10%

t

pHL

90%

t

0.8×VCC

f

SOUT

t

pHL・tpLH

0.8×VCC

0.2×VCC

t

f・tr

Fig. 17

Technical Note

t

pHL

90%

10%

t

w

10%

tr

0.2×VCC

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

18/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

【BU2152FS】

●Pin descriptions

Pin

No.

Pin Name I/O Function

1 VSS - Ground

2 CLK I Clock Input

3 VSS - Ground

4 DATA I Serial Data Input

5~28 P1~P24 O Parallel Data Output

29 SO O Cascade Output

30 STB I Strobe Signal Input active “L”

31 CLB I Clear Signal Input active “L”

32 VDD - Power Supply

●Timing chart

CLK

DATA

DATA24 DATA23 DATA22 DATA2 DATA1

STB

Pn

Previous DATA DATA

SO

Previous

DATA24

Previous

DATA23

Previous

DATA2

Previous

DATA1

Fig. 18

1. After the power is turned on and the voltage is stabilized, STB should be activated, after clocking 24 data bits into

the DATA terminal.

2. Pn parallel output data of the shift register is set after the 24

th

clock by the LCK.

3. Since the STB is a label latch, data is retained in the “H” section and renewed in the “L” section of the STB.

4. The final stage data of the shift register is outputted to the SO by synchronizing with the rise time of the CLOCK.

[Truth Table]

Input

CLK STB CLB

× × L

H H

L

H

The data of the shift register shifts 1bit, and the data of the latch circuit and

L H

All the data of the latch circuit are set to “H” (data of shift register does not

change), all the parallel outputs are “H”.

Serial data of DATA pin are latched to the shift register.

At this time, the data of the latch circuit does not change.

The data of the shift register are transferred to the latch circuit, and the data of

the latch circuit are outputted from the parallel output pin.

Function

parallel output also change.

DATA24

Technical Note

DATA23 DATA22

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

19/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

【BU2152FS】

●Switching characteristics (Unless otherwise specified, VDD=2.7 to 5.5V, VSS=0V, Ta=25℃)

Limit

Parameter Symbol

Unit Condition

Min. Typ. Max.

Technical Note

Maximum Clock Frequency f

Setup Time 1 t

Hold Time 1 t

Setup Time 2 t

Hold Time 2 t

Setup Time 3 t

Hold Time 3 t

Setup Time 4 t

Hold Time 4 t

Output Delay Time 1* t

Output Delay Time 2* t

Output Delay Time 3* t

*50pF of load is attached.

5 - - MHz

MAX

20 - - ns DATA-CLK

SU1

20 - - ns CLK-DATA

HD1

30 - - ns STB-CLK

SU2

30 - - ns CLK-STB

HD2

30 - - ns CLB-CLK

SU3

30 - - ns CLK-CLB

HD3

30 - - ns STB-CLB

SU4

30 - - ns CLB-STB

HD4

- - 100 ns CLK-P1~P24

PD1

- - 80 ns STB-P1~P24

PD2

- - 80 ns CLB-P1~P24

PD3.

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

20/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

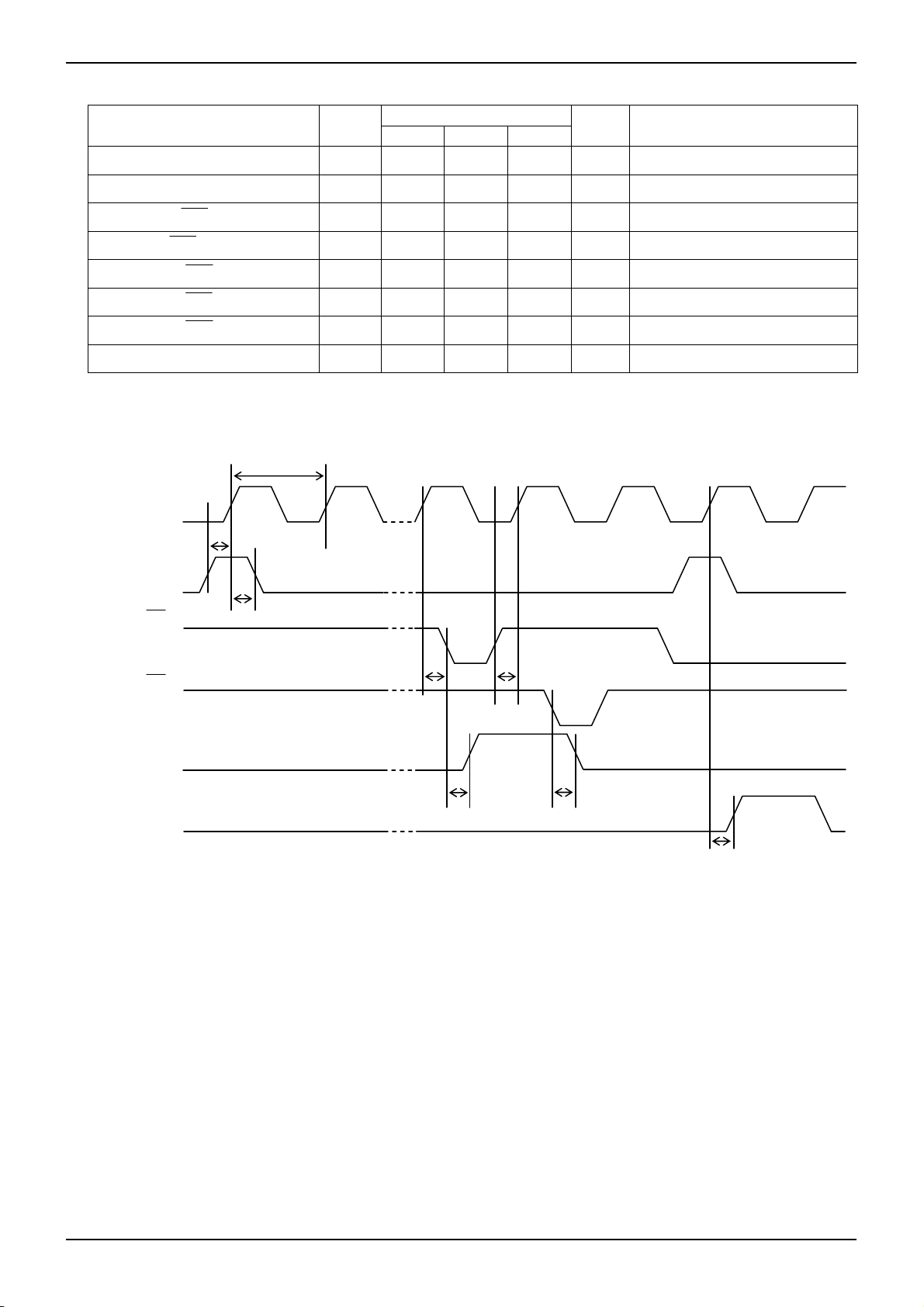

●Switching characteristic conditions

○Setup/Hold Time (DATA-CLOCK, STB-CLOCK, CLB-CLOCK)

tr

CLOCK

DATA

10%

t

SU1

90%

50%

t

HD1

90%

10%

t

r

50%

Technical Note

STB

CLB

○Setup/Hold Time (STB-CLB)

CLB

STB

Fig. 19 Switching characteristic conditions 1

○Output Delay Time (CLOCK-P1~P24)

CLOCK

50%50%

t

HD2

t

HD3

50%

t

SU4

t

HD4

50%

t

SU2

50%50%

t

SU3

t

PD1

P1~P24

○Output Delay Time (STB-P1~P24)

STB

P1~P24

○ Output Delay Time (CLB-P1~P24)

CLB

50%

t

PD2

50%

t

PD3

50%

Fig. 20 Switching characteristic conditions 2

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

21/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

●Notes for use

1. Absolute maximum ratings

An excess in the absolute maximum ratings, such as supply voltage, temperature range of operating conditions, etc., can

break down the devices, thus making impossible to identify breaking mode, such as a short circuit or an open circuit. If any

over rated values will expect to exceed the absolute maximum ratings, consider adding circuit protection devices, such as

fuses.

2. Connecting the power supply connector backward

Connecting of the power supply in reverse polarity can damage IC. Take precautions when connecting the power supply

lines. An external direction diode can be added.

3. Power supply lines

Design PCB layout pattern to provide low impedance GND and supply lines. To obtain a low noise ground and supply line,

separate the ground section and supply lines of the digital and analog blocks. Furthermore, for all power supply terminals to

ICs, connect a capacitor between the power supply and the GND terminal. When applying electrolytic capacitors in the circuit,

not that capacitance characteristic values are reduced at low temperatures.

4. GND voltage

The potential of GND pin must be minimum potential in all operating conditions.

5. Thermal design

Use a thermal design that allows for a sufficient margin in light of the power dissipation (Pd) in actual operating conditions.

6. Inter-pin shorts and mounting errors

Use caution when positioning the IC for mounting on printed circuit boards. The IC may be damaged if there is any

connection error or if pins are shorted together.

7. Actions in strong electromagnetic field

Use caution when using the IC in the presence of a strong electromagnetic field as doing so may cause the IC to malfunction.

8. Testing on application boards

When testing the IC on an application board, connecting a capacitor to a pin with low impedance subjects the IC to stress.

Always discharge capacitors after each process or step. Always turn the IC's power supply off before connecting it to or

removing it from a jig or fixture during the inspection process. Ground the IC during assembly steps as an antistatic measure.

Use similar precaution when transporting or storing the IC.

9. Ground Wiring Pattern

When using both small signal and large current GND patterns, it is recommended to isolate the two ground patterns, placing

a single ground point at the ground potential of application so that the pattern wiring resistance and voltage variations caused

by large currents do not cause variations in the small signal ground voltage. Be careful not to change the GND wiring pattern

of any external components, either.

10. Unused input terminals

Connect all unused input terminals to VDD or VSS in order to prevent excessive current or oscillation.

Insertion of a resistor (100kΩ approx.) is also recommended.

Technical Note

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

22/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

●Ordering part number

B U 2 0 9 2 F V - E 2

Technical Note

Part No. Part No.

Package

2050

2092

2099

7851

2152

SOP14

8.7± 0.2

(MAX 9.05 include BURR)

14

8

<Tape and Reel information>

6.2± 0.3

4.4± 0.2

1

7

0.3MIN

0.15± 0.1

SOP18

1.5± 0.1

1.27

0.11

11.2± 0.2

(MAX 11.55 include BURR)

18

0.4± 0.1

0.1

(Unit : mm)

<Tape and Reel information>

10

7.8± 0.3

5.4± 0.2

91

1.8± 0.1

0.11

1.27

0.4± 0.1

0.1

0.3MIN

0.15± 0.1

(Unit : mm)

SSOP-B20

6.5 ± 0.2

20

11

<Tape and Reel information>

6.4 ± 0.3

4.4 ± 0.2

1

10

0.3Min.

0.15 ± 0.1

1.15 ± 0.1

0.1± 0.1

0.65

0.1

0.22 ± 0.1

(Unit : mm)

F : SOP14

: SOP18

FV : SSOP-B20

FP : HSOP25

FS : SSOP-A32

Quantity

Direction

of feed

Quantity

Direction

of feed

Quantity

Direction

of feed

Packaging and forming specification

E2: Embossed tape and reel

Embossed carrier tapeTape

2500pcs

E2

The direction is the 1pin of product is at the upper left when you hold

()

reel on the left hand and you pull out the tape on the right hand

Reel

Embossed carrier tapeTape

2000pcs

E2

The direction is the 1pin of product is at the upper left when you hold

()

reel on the left hand and you pull out the tape on the right hand

Reel

Embossed carrier tapeTape

2500pcs

E2

The direction is the 1pin of product is at the upper left when you hold

()

reel on the left hand and you pull out the tape on the right hand

Reel

1pin

Order quantity needs to be multiple of the minimum quantity.

∗

1pin

Order quantity needs to be multiple of the minimum quantity.

∗

1pin

Order quantity needs to be multiple of the minimum quantity.

∗

Direction of feed

Direction of feed

Direction of feed

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

23/24

2009.06 - Rev.A

BU2050F,BU2092F,BU2092FV,BU2099FV,BD7851FP,BU2152FS

HSOP25

13.6 ± 0.2

(MAX 13.95 include BURR)

2.75 ± 0.1

25 14

7.8 ± 0.3

1.9 ± 0.1

0.11

5.4 ± 0.2

1

1.95 ± 0.1

0.8

12.0 ± 0.2

0.36 ± 0.1

13

0.3Min.

0.25 ± 0.1

S

0.1 S

(Unit : mm)

<Tape and Reel information>

Embossed carrier tapeTape

Quantity

Direction

of feed

2000pcs

E2

The direction is the 1pin of product is at the upper left when you hold

()

reel on the left hand and you pull out the tape on the right hand

Reel

1pin

Order quantity needs to be multiple of the minimum quantity.

∗

SSOP-A32

13.6± 0.2

(MAX 13.95 include BURR)

32

5.4± 0.2

7.8± 0.3

1

1.8± 0.1

0.11

0.36± 0.1

0.8

17

0.3MIN

16

0.15± 0.1

0.1

(Unit : mm)

<Tape and Reel information>

Embossed carrier tapeTape

Quantity

Direction

of feed

2000pcs

E2

The direction is the 1pin of product is at the upper left when you hold

()

reel on the left hand and you pull out the tape on the right hand

Reel

1pin

Order quantity needs to be multiple of the minimum quantity.

∗

Technical Note

Direction of feed

Direction of feed

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

24/24

2009.06 - Rev.A

Notes

No copying or reproduction of this document, in part or in whole, is permitted without the

consent of ROHM Co.,Ltd.

The content specied herein is subject to change for improvement without notice.

The content specied herein is for the purpose of introducing ROHM's products (hereinafter

"Products"). If you wish to use any such Product, please be sure to refer to the specications,

which can be obtained from ROHM upon request.

Examples of application circuits, circuit constants and any other information contained herein

illustrate the standard usage and operations of the Products. The peripheral conditions must

be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specied in this document.

However, should you incur any damage arising from any inaccuracy or misprint of such

information, ROHM shall bear no responsibility for such damage.

The technical information specied herein is intended only to show the typical functions of and

examples of application circuits for the Products. ROHM does not grant you, explicitly or

implicitly, any license to use or exercise intellectual proper ty or other rights held by ROHM and

other par ties. ROHM shall bear no responsibility whatsoever for any dispute arising from the

use of such technical information.

Notice

The Products specied in this document are intended to be used with general-use electronic

equipment or devices (such as audio visual equipment, ofce-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specied in this document are not designed to be radiation tolerant.

While ROHM always makes efforts to enhance the quality and reliability of its Products, a

Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard

against the possibility of physical injury, re or any other damage caused in the event of the

failure of any Product, such as derating, redundancy, re control and fail-safe designs. ROHM

shall bear no responsibility whatsoever for your use of any Product outside of the prescribed

scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or

system which requires an extremely high level of reliability the failure or malfunction of which

may result in a direct threat to human life or create a risk of human injury (such as a medical

instrument, transpor tation equipment, aerospace machiner y, nuclear-reactor controller,

fuel-controller or other safety device). ROHM shall bear no responsibility in any way for use of

any of the Products for the above special purposes. If a Product is intended to be used for any

such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specied herein that may

be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to

obtain a license or permit under the Law.

Thank you for your accessing to ROHM product informations.

More detail product informations and catalogs are available, please contact us.

ROHM Customer Support System

www.rohm.com

© 2009 ROHM Co., Ltd. All rights reserved.

http://www.rohm.com/contact/

R0039

A

Loading...

Loading...