Page 1

REJ09B0124-0110

M16C/6N Group

(M16C/6NK, M16C/6NM)

16

Hardware Manual

RENESAS 16-BIT SINGLE-CHIP MICROCOMPUTER

M16C FAMILY / M16C/60 SERIES

Before using this material, please visit our website to verify that this is the most

updated document available.

Rev. 1.10

Revision date: Jul. 01, 2005

www.renesas.com

Page 2

Keep safety first in your circuit designs!

•

Renesas Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with

them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

Notes regarding these materials

• These materials are intended as a reference to assist our customers in the selection of the

Renesas Technology Corporation product best suited to the customer's application; they do

not convey any license under any intellectual property rights, or any other rights, belonging

to Renesas Technology Corporation or a third party.

• Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts,

programs, algorithms, or circuit application examples contained in these materials.

• All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these

materials, and are subject to change by Renesas Technology Corporation without notice

due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product

listed herein.

The information described here may contain technical inaccuracies or typographical errors.

Renesas Technology Corporation assumes no responsibility for any damage, liability, or

other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corporation by

various means, including the Renesas Technology Corporation Semiconductor home page

(http://www.renesas.com).

• When using any or all of the information contained in these materials, including product

data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information

and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

• Renesas Technology Corporation semiconductors are not designed or manufactured for

use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas

Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation,

vehicular, medical, aerospace, nuclear, or undersea repeater use.

• The prior written approval of Renesas Technology Corporation is necessary to reprint or

reproduce in whole or in part these materials.

• If these products or technologies are subject to the Japanese export control restrictions,

they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/

or the country of destination is prohibited.

• Please contact Renesas Technology Corporation for further details on these materials or

the products contained therein.

Page 3

How to Use This Manual

1. Introduction

This hardware manual provides detailed information on the M16C/6N Group (M16C/6NK, M16C/6NM) of

microcomputers.

Users are expected to have basic knowledge of electric circuits, logical circuits and microcomputers.

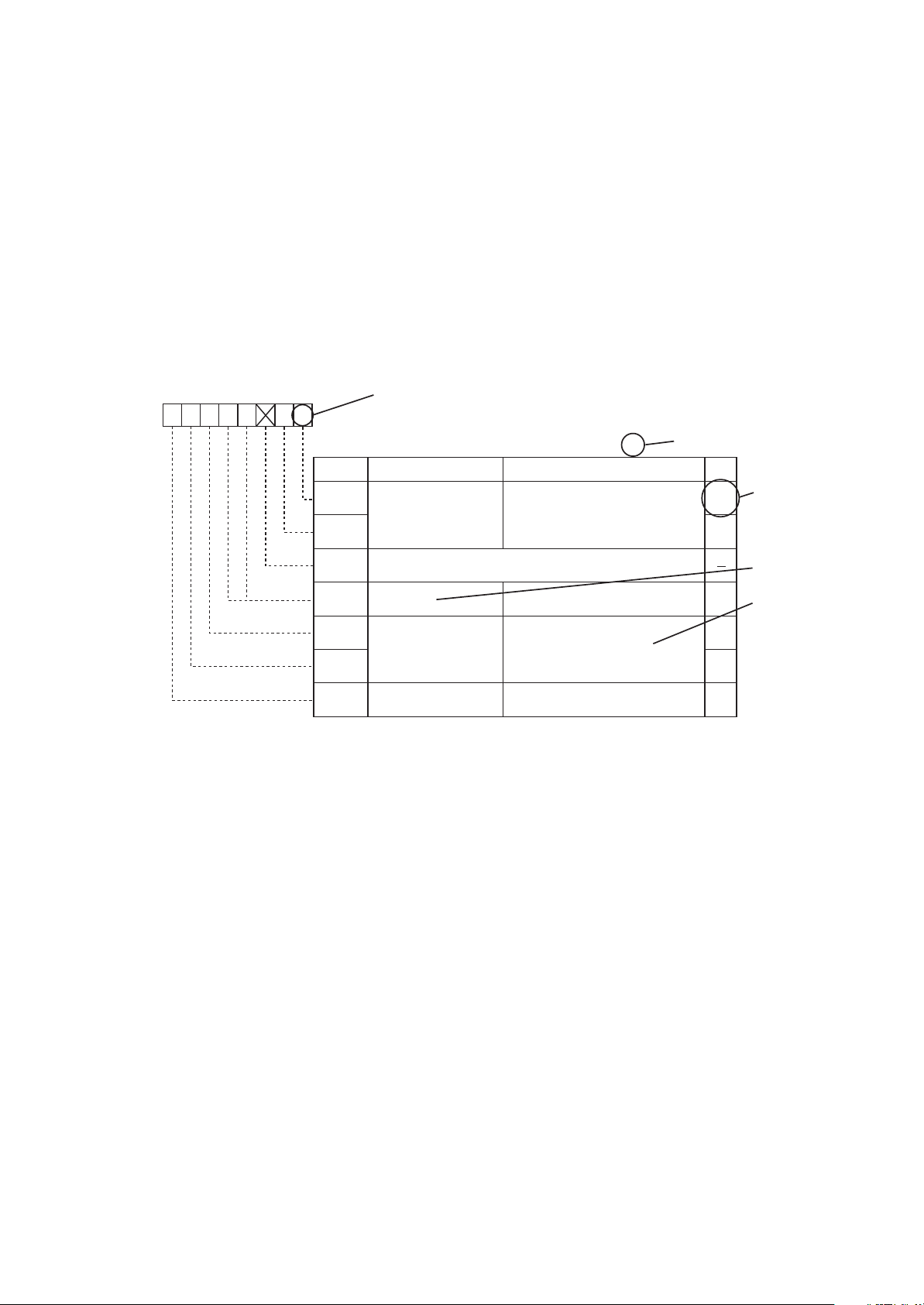

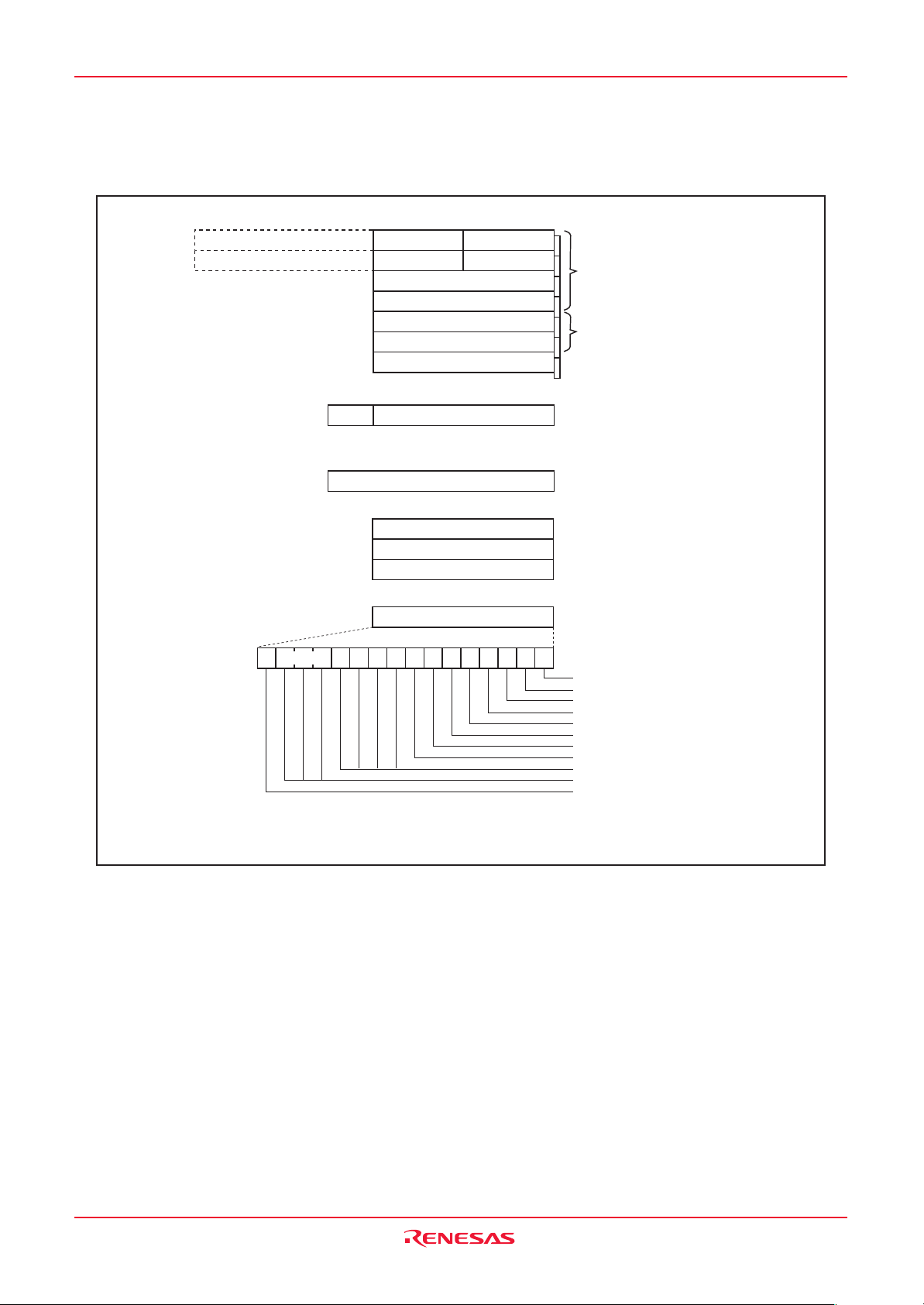

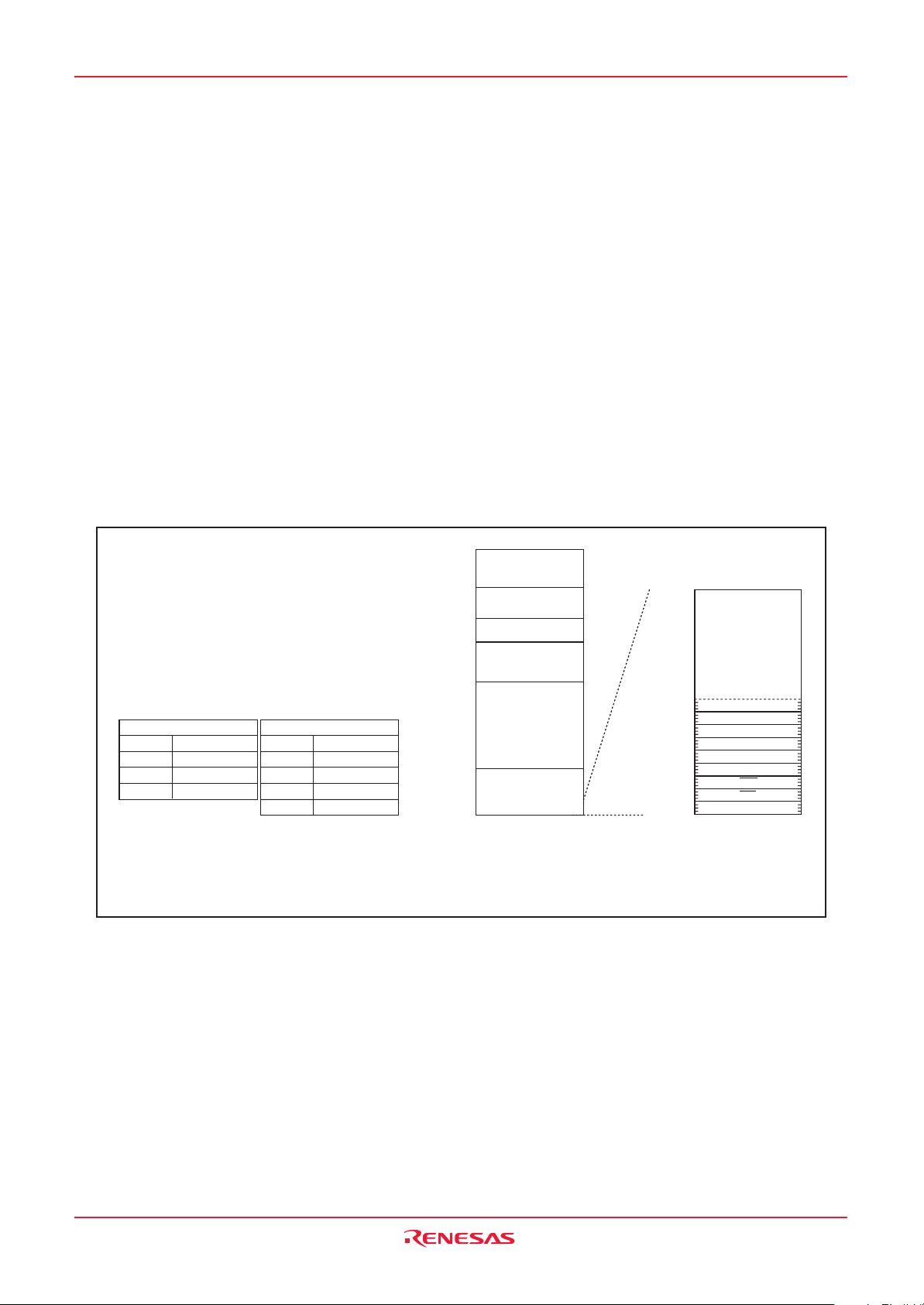

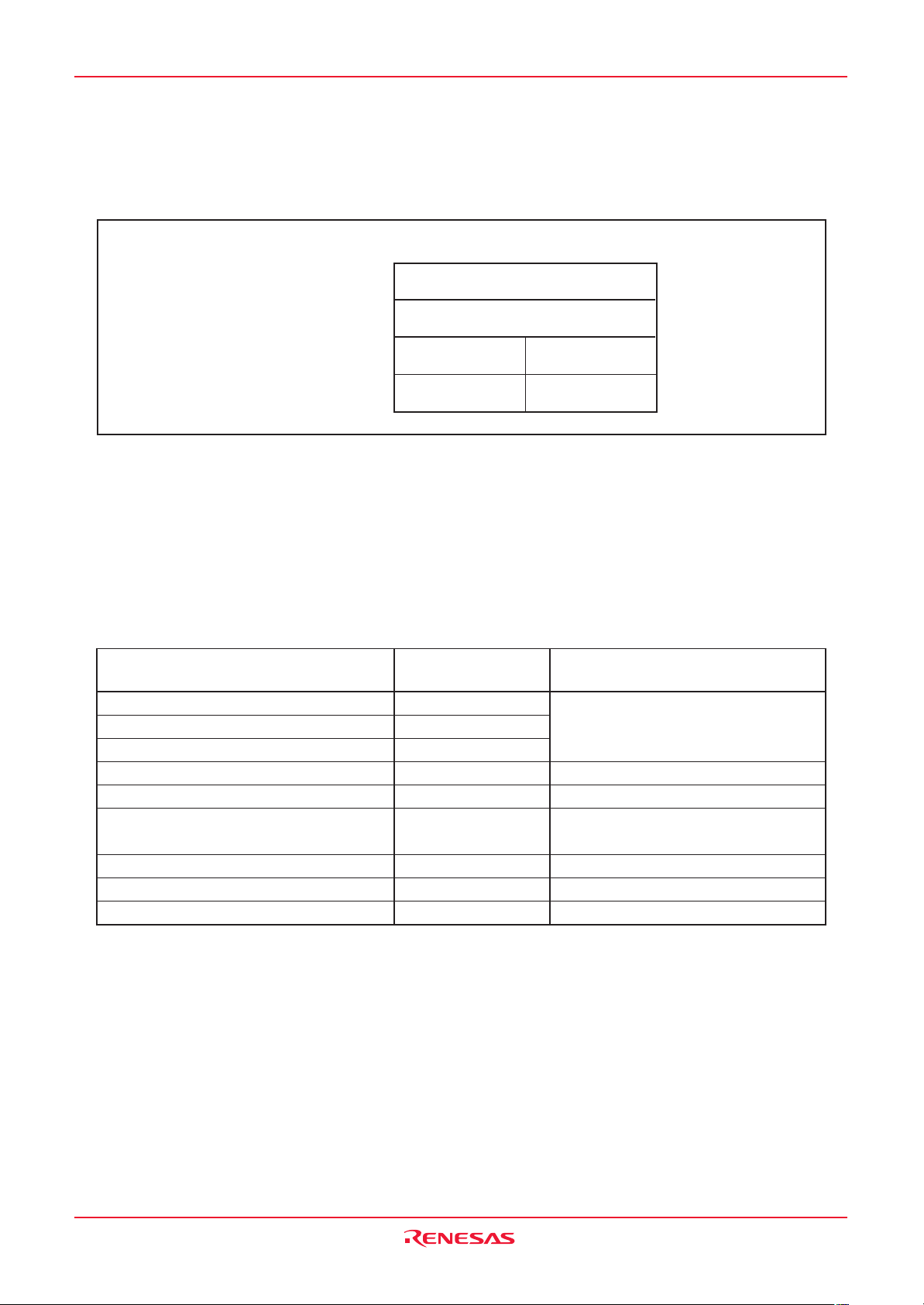

2. Register Diagram

The symbols, and descriptions, used for bit function in each register are shown below.

XXX Register

b7 b6 b5 b4 b3 b2 b1 b0

00

Symbol

XXX

XXX

(b2)

(b4-b3)

*1

Symbol

XXX

Bit

0

1

-

-

Bit Name

XXX Bit

Nothing is assigned. When write, set to "0",

When read, its content is indeterminate.

Reserved Bit Set to "0"

Address

XXX

Function

b1b0

0 0: XXX

0 1: XXX

1 0: Do not set a value

1 1: XXX

After Reset

00h

*5

RW

RW

RW

WO

*2

*3

*4

XXX5

XXX

XXX

XXX Bit

6

7

XXX Bit

Function varies depending on

mode of operation

0: XXX

1: XXX

*1

Blank:Set to “0” or “1” according to the application

0 : Set to “0”

1 : Set to “1”

X : Nothing is assigned

*2

RW : Read and write

RO : Read only

WO: Write only

– : Nothing is assigned

*3

• Reserved bit

Reserved bit. Set to specified value.

*4

• Nothing is assigned

Nothing is assigned to the bit concerned. As the bit may be use for future functions, set to “0” when

writing to this bit.

• Do not set to this value

The operation is not guaranteed when a value is set.

• Function varies depending on mode of operation

Bit function varies depending on peripheral function mode.

Refer to respective register for each mode.

*5

Follow the text in each manual for binary and hexadecimal notations.

RW

RW

RO

Page 4

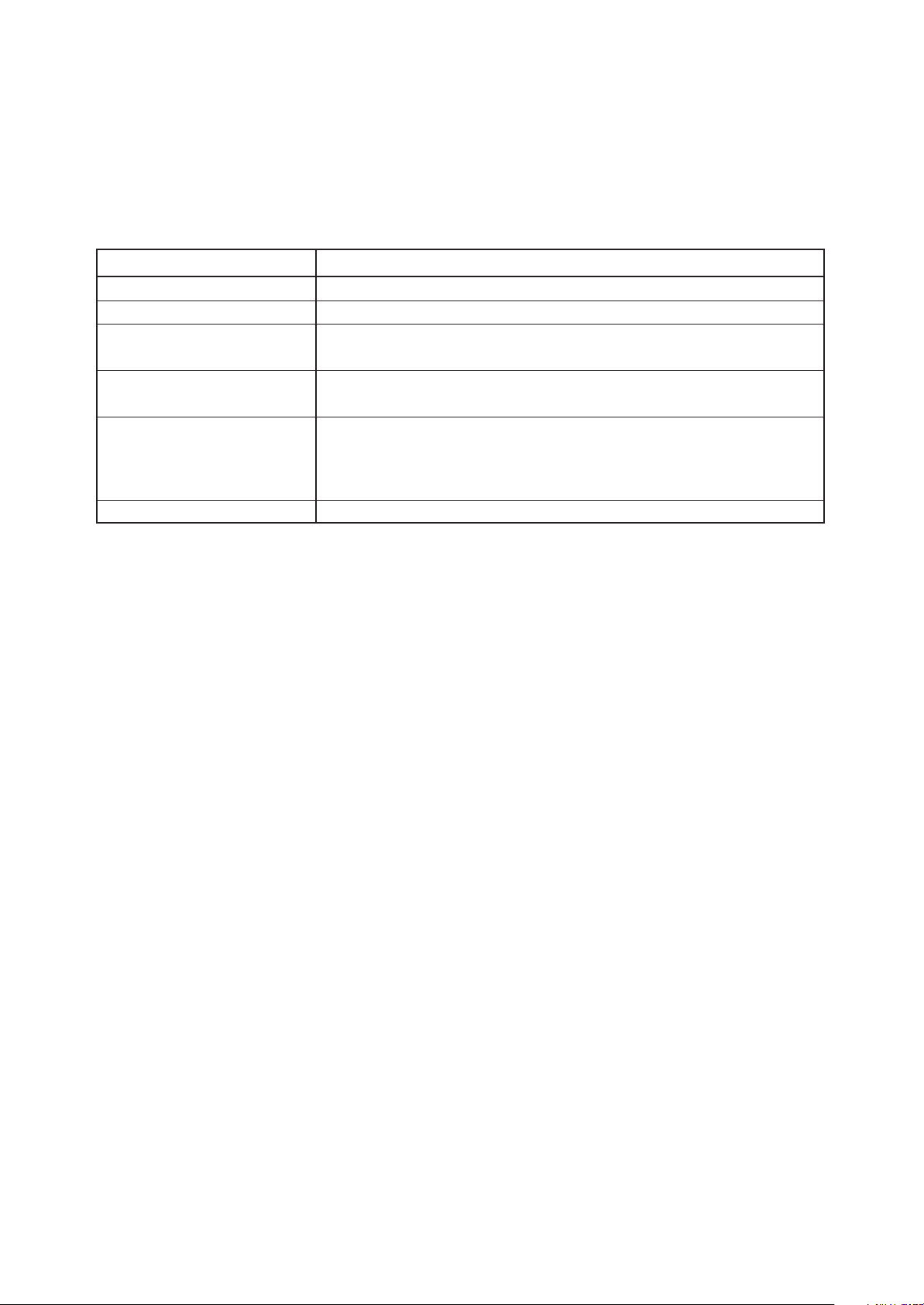

3. M16C Family Documents

The following documents were prepared for the M16C family

Document Contents

Short Sheet Hardware overview

Data Sheet Hardware overview and electrical characteristics

Hardware Manual Hardware specifications (pin assignments, memory maps, peripheral

specifications, electrical characteristics, timing charts)

Software Manual Detailed description of assembly instructions and microcomputer

performance of each instruction

Application Note • Application examples of peripheral functions

• Sample programs

• Introduction to the basic functions in the M16C family

• Programming method with Assembly and C languages

RENESAS TECHNICAL UPDATE

Preliminary report about the specification of a product, a document, etc.

NOTE:

1. Before using this material , please visit our website to verify that this is the most updated document

available.

(1)

.

Page 5

Table of Contents

SFR Page Reference ............................................................................................................ B-1

1. Overview ............................................................................................................................... 1

1.1 Applications ..................................................................................................................................................1

1.2 Performance Outline ....................................................................................................................................2

1.3 Block Diagram .............................................................................................................................................. 4

1.4 Product List ..................................................................................................................................................5

1.5 Pin Configuration .........................................................................................................................................6

1.6 Pin Description ............................................................................................................................................. 8

2. Central Processing Unit (CPU) ........................................................................................... 10

2.1 Data Registers (R0, R1, R2, and R3) ........................................................................................................ 10

2.2 Address Registers (A0 and A1) .................................................................................................................. 10

2.3 Frame Base Register (FB) ......................................................................................................................... 11

2.4 Interrupt Table Register (INTB) .................................................................................................................. 11

2.5 Program Counter (PC) ............................................................................................................................... 11

2.6 User Stack Pointer (USP), Interrupt Stack Pointer (ISP) ........................................................................... 11

2.7 Static Base Register (SB) .......................................................................................................................... 11

2.8 Flag Register (FLG) ................................................................................................................................... 11

2.8.1 Carry Flag (C Flag) ............................................................................................................................ 11

2.8.2 Debug Flag (D Flag) .......................................................................................................................... 11

2.8.3 Zero Flag (Z Flag) .............................................................................................................................. 11

2.8.4 Sign Flag (S Flag) .............................................................................................................................. 11

2.8.5 Register Bank Select Flag (B Flag).................................................................................................... 11

2.8.6 Overflow Flag (O Flag)....................................................................................................................... 11

2.8.7 Interrupt Enable Flag (I Flag) ............................................................................................................. 11

2.8.8 Stack Pointer Select Flag (U Flag)..................................................................................................... 11

2.8.9 Processor Interrupt Priority Level (IPL) .............................................................................................. 11

2.8.10 Reserved Area ................................................................................................................................. 11

3. Memory ............................................................................................................................... 12

4. Special Function Register (SFR)......................................................................................... 13

5. Reset ................................................................................................................................... 29

5.1 Hardware Reset .........................................................................................................................................29

5.1.1 Reset on a Stable Supply Voltage ..................................................................................................... 29

5.1.2 Power-on Reset ................................................................................................................................. 29

5.2 Software Reset ..........................................................................................................................................29

5.3 Watchdog Timer Reset ............................................................................................................................... 29

5.4 Oscillation Stop Detection Reset ............................................................................................................... 29

6. Processor Mode ..................................................................................................................32

7. Clock Generating Circuit .....................................................................................................35

7.1 Types of Clock Generating Circuit ............................................................................................................. 35

7.1.1 Main Clock ......................................................................................................................................... 43

7.1.2 Sub Clock........................................................................................................................................... 44

7.1.3 On-chip Oscillator Clock .................................................................................................................... 45

7.1.4 PLL Clock ........................................................................................................................................... 45

A-1

Page 6

7.2 CPU Clock and Peripheral Function Clock ................................................................................................ 47

7.2.1 CPU Clock and BCLK ........................................................................................................................47

7.2.2 Peripheral Function Clock .................................................................................................................. 47

7.3 Clock Output Function ............................................................................................................................... 47

7.4 Power Control ............................................................................................................................................ 48

7.4.1 Normal Operation Mode..................................................................................................................... 48

7.4.2 Wait Mode .......................................................................................................................................... 50

7.4.3 Stop Mode.......................................................................................................................................... 52

7.5 Oscillation Stop and Re-oscillation Detection Function ............................................................................. 57

7.5.1 Operation When CM27 Bit = 0 (Oscillation Stop Detection Reset) .................................................... 57

7.5.2 Operation When CM27 Bit = 1 (Oscillation Stop, Re-oscillation Detection Interrupt) ........................ 57

7.5.3 How to Use Oscillation Stop and Re-oscillation Detection Function .................................................. 58

8. Protection ............................................................................................................................59

9. Interrupt ............................................................................................................................... 60

9.1 Type of Interrupts ....................................................................................................................................... 60

9.2 Software Interrupts ..................................................................................................................................... 61

9.2.1 Undefined Instruction Interrupt........................................................................................................... 61

9.2.2 Overflow Interrupt .............................................................................................................................. 61

9.2.3 BRK Interrupt ..................................................................................................................................... 61

9.2.4 INT Instruction Interrupt ..................................................................................................................... 61

9.3 Hardware Interrupts ................................................................................................................................... 62

9.3.1 Special Interrupts ...............................................................................................................................62

9.3.2 Peripheral Function Interrupts............................................................................................................ 62

9.4 Interrupts and Interrupt Vector ...................................................................................................................63

9.4.1 Fixed Vector Tables ............................................................................................................................ 63

9.4.2 Relocatable Vector Tables .................................................................................................................63

9.5 Interrupt Control .........................................................................................................................................65

9.5.1 I Flag ..................................................................................................................................................67

9.5.2 IR Bit .................................................................................................................................................. 67

9.5.3 ILVL2 to ILVL0 Bits and IPL ............................................................................................................... 67

9.5.4 Interrupt Sequence ............................................................................................................................ 68

9.5.5 Interrupt Response Time.................................................................................................................... 69

9.5.6 Variation of IPL when Interrupt Request is Accepted ......................................................................... 69

9.5.7 Saving Registers ................................................................................................................................ 70

9.5.8 Returning from an Interrupt Routine .................................................................................................. 71

9.5.9 Interrupt Priority ................................................................................................................................. 71

9.5.10 Interrupt Priority Resolution Circuit .................................................................................................. 71

______

9.6 INT Interrupt ...............................................................................................................................................73

______

9.7 NMI Interrupt ..............................................................................................................................................77

9.8 Key Input Interrupt .....................................................................................................................................77

9.9 CAN0/1 Wake-up Interrupt ......................................................................................................................... 77

9.10 Address Match Interrupt ........................................................................................................................... 78

10. Watchdog Timer ................................................................................................................ 80

10.1 Count Source Protective Mode ................................................................................................................81

A-2

Page 7

11. DMAC ................................................................................................................................ 82

11.1 Transfer Cycle .......................................................................................................................................... 87

11.1.1 Effect of Source and Destination Addresses .................................................................................... 87

11.1.2 Effect of Software Wait ..................................................................................................................... 87

11.2 DMA Transfer Cycles ................................................................................................................................ 89

11.3 DMA Enable ............................................................................................................................................. 90

11.4 DMA Request ...........................................................................................................................................90

11.5 Channel Priority and DMA Transfer Timing ..............................................................................................91

12. Timers ............................................................................................................................... 92

12.1 Timer A .....................................................................................................................................................94

12.1.1 Timer Mode ......................................................................................................................................98

12.1.2 Event Counter Mode ........................................................................................................................99

12.1.3 One-shot Timer Mode ....................................................................................................................104

12.1.4 Pulse Width Modulation (PWM) Mode ...........................................................................................106

12.2 Timer B................................................................................................................................................... 109

12.2.1 Timer Mode .................................................................................................................................... 112

12.2.2 Event Counter Mode ...................................................................................................................... 113

12.2.3 Pulse Period and Pulse Width Measurement Mode ...................................................................... 114

13. Three-Phase Motor Control Timer Function .................................................................... 117

14. Serial I/O ......................................................................................................................... 128

14.1 UARTi.....................................................................................................................................................128

14.1.1 Clock Synchronous Serial I/O Mode ..............................................................................................138

14.1.2 Clock Asynchronous Serial I/O (UART) Mode ...............................................................................146

14.1.3 Special Mode 1 (I2C Mode) ............................................................................................................154

14.1.4 Special Mode 2 .............................................................................................................................. 163

14.1.5 Special Mode 3 (IE Mode) ............................................................................................................. 168

14.1.6 Special Mode 4 (SIM Mode) (UART2) ........................................................................................... 170

14.2 SI/Oi .......................................................................................................................................................175

14.2.1 SI/Oi Operation Timing................................................................................................................... 179

14.2.2 CLK Polarity Selection ................................................................................................................... 179

14.2.3 Functions for Setting an SOUTi Initial Value .................................................................................. 180

15. A/D Converter ..................................................................................................................181

15.1 Mode Description ...................................................................................................................................185

15.1.1 One-shot Mode .............................................................................................................................. 185

15.1.2 Repeat Mode ................................................................................................................................. 187

15.1.3 Single Sweep Mode .......................................................................................................................189

15.1.4 Repeat Sweep Mode 0 .................................................................................................................. 191

15.1.5 Repeat Sweep Mode 1 .................................................................................................................. 193

15.2 Function ................................................................................................................................................. 195

15.2.1 Resolution Select Function ............................................................................................................ 195

15.2.2 Sample and Hold ........................................................................................................................... 195

15.2.3 Extended Analog Input Pins........................................................................................................... 195

15.2.4 External Operation Amplifier (Op-Amp) Connection Mode ............................................................195

15.2.5 Current Consumption Reducing Function ...................................................................................... 196

15.2.6 Output Impedance of Sensor under A/D Conversion..................................................................... 196

16. D/A Converter.................................................................................................................. 198

17. CRC Calculation.............................................................................................................. 200

A-3

Page 8

18. CAN Module .................................................................................................................... 202

18.1 CAN Module-Related Registers ............................................................................................................. 203

18.1.1 CAN Message Box......................................................................................................................... 203

18.1.2 Acceptance Mask Registers........................................................................................................... 203

18.1.3 CAN SFR Registers .......................................................................................................................203

18.2 CANi Message Box ................................................................................................................................ 204

18.3 Acceptance Mask Registers...................................................................................................................206

18.4 CAN SFR Registers ...............................................................................................................................207

18.5 Operational Modes ................................................................................................................................. 213

18.5.1 CAN Reset/Initialization Mode ....................................................................................................... 213

18.5.2 CAN Operation Mode..................................................................................................................... 214

18.5.3 CAN Sleep Mode ........................................................................................................................... 214

18.5.4 CAN Interface Sleep Mode ............................................................................................................ 214

18.5.5 Bus Off State.................................................................................................................................. 215

18.6 Configuration CAN Module System Clock ............................................................................................. 216

18.7 Bit Timing Configuration ......................................................................................................................... 216

18.8 Bit-rate ................................................................................................................................................... 217

18.9 Acceptance Filtering Function and Masking Function............................................................................218

18.10 Acceptance Filter Support Unit (ASU)..................................................................................................219

18.11 Basic CAN Mode ..................................................................................................................................220

18.12 Return from Bus off Function ...............................................................................................................221

18.13 Time Stamp Counter and Time Stamp Function ..................................................................................221

18.14 Listen-Only Mode ................................................................................................................................. 221

18.15 Reception and Transmission................................................................................................................222

18.15.1 Reception ..................................................................................................................................... 223

18.15.2 Transmission ................................................................................................................................ 224

18.16 CAN Interrupt .......................................................................................................................................225

19. Programmable I/O Ports ................................................................................................. 226

19.1 PDi Register ........................................................................................................................................... 227

19.2 Pi Register, PC14 Register ....................................................................................................................227

19.3 PURj Register ........................................................................................................................................ 227

19.4 PCR Register .........................................................................................................................................227

20. Flash Memory Version .................................................................................................... 238

20.1 Memory Map ..........................................................................................................................................239

20.1.1 Boot Mode...................................................................................................................................... 240

20.2 Functions to Prevent Flash Memory from Rewriting .............................................................................. 240

20.2.1 ROM Code Protect Function .......................................................................................................... 240

20.2.2 ID Code Check Function ................................................................................................................ 240

20.3 CPU Rewrite Mode ................................................................................................................................ 242

20.3.1 EW0 Mode ..................................................................................................................................... 243

20.3.2 EW1 Mode ..................................................................................................................................... 243

20.3.3 FMR0, FMR1 Registers ................................................................................................................. 244

20.3.4 Precautions on CPU Rewrite Mode ............................................................................................... 248

20.3.5 Software Commands ..................................................................................................................... 250

20.3.6 Data Protect Function .................................................................................................................... 255

20.3.7 Status Register (SRD Register) .....................................................................................................255

20.3.8 Full Status Check ........................................................................................................................... 257

A-4

Page 9

20.4 Standard Serial I/O Mode ...................................................................................................................... 259

20.4.1 ID Code Check Function ................................................................................................................ 259

20.4.2 Example of Circuit Application in Standard Serial I/O Mode .......................................................... 263

20.5 Parallel I/O Mode ................................................................................................................................... 264

20.5.1 User ROM and Boot ROM Areas ................................................................................................... 264

20.5.2 ROM Code Protect Function .......................................................................................................... 264

20.6 CAN I/O Mode ........................................................................................................................................ 265

20.6.1 ID Code Check Function ................................................................................................................ 265

20.6.2 Example of Circuit Application in CAN I/O Mode ...........................................................................268

21. Electrical Characteristics ................................................................................................. 269

22. Usage Precaution............................................................................................................ 279

22.1 SFR ........................................................................................................................................................ 279

22.2 External Clock ........................................................................................................................................ 280

22.3 PLL Frequency Synthesizer ...................................................................................................................281

22.4 Power Control ........................................................................................................................................ 282

22.5 Oscillation Stop, Re-oscillation Detection Function ............................................................................... 284

22.6 Protection ............................................................................................................................................... 285

22.7 Interrupt .................................................................................................................................................. 286

22.7.1 Reading Address 00000h............................................................................................................... 286

22.7.2 Setting SP ......................................................................................................................................286

_______

22.7.3 NMI Interrupt ..................................................................................................................................286

22.7.4 Changing Interrupt Generate Factor ..............................................................................................287

22.7.5 INT Interrupt ................................................................................................................................... 287

22.7.6 Rewrite Interrupt Control Register ................................................................................................. 288

22.7.7 Watchdog Timer Interrupt .............................................................................................................. 288

22.8 DMAC .................................................................................................................................................... 289

22.8.1 Write to DMAE Bit in DMiCON Registe.......................................................................................... 289

22.9 Timers .................................................................................................................................................... 290

22.9.1 Timer A........................................................................................................................................... 290

22.9.2 Timer B........................................................................................................................................... 294

22.10 Thee-Phase Motor Control Timer Function .......................................................................................... 296

22.11 Serial I/O ..............................................................................................................................................297

22.11.1 Clock Synchronous Serial I/O Mode ............................................................................................ 297

22.11.2 Special Modes .............................................................................................................................. 298

22.11.3 SI/Oi ............................................................................................................................................. 299

22.12 A/D Converter ...................................................................................................................................... 300

22.13 CAN Module ......................................................................................................................................... 302

22.13.1 Reading CiSTR Register.............................................................................................................. 302

22.13.2 Performing CAN Configuration .................................................................................................... 304

22.13.3 Suggestions to Reduce Power Consumption .............................................................................. 305

22.13.4 CAN Transceiver in Boot Mode.................................................................................................... 306

22.14 Programmable I/O Ports ...................................................................................................................... 307

22.15 Dedicated Input Pin .............................................................................................................................. 308

22.16 Electrical Characteristic Differences Between Mask ROM and Flash Memory Version Microcomputers ......309

22.17 Mask ROM Version ............................................................................................................................. 310

_____

A-5

Page 10

22.18 Flash Memory Version ......................................................................................................................... 311

22.18.1 Functions to Prevent Flash Memory from Rewriting .................................................................... 311

22.18.2 Stop Mode.................................................................................................................................... 311

22.18.3 Wait Mode .................................................................................................................................... 311

22.18.4 Low Power Dissipation Mode and On-Chip Oscillator Low Power Dissipation Mode ................. 311

22.18.5 Writing Command and Data......................................................................................................... 311

22.18.6 Program Command...................................................................................................................... 311

22.18.7 Lock Bit Program Command ........................................................................................................ 311

22.18.8 Operation Speed .......................................................................................................................... 312

22.18.9 Prohibited Instructions ................................................................................................................. 312

22.18.10 Interrupt...................................................................................................................................... 312

22.18.11 How to Access............................................................................................................................ 312

22.18.12 Rewriting in User ROM Area...................................................................................................... 312

22.18.13 DMA Transfer .............................................................................................................................312

22.19 Flash Memory Programming Using Boot Program .............................................................................. 313

22.19.1 Programming Using Serial I/O Mode ........................................................................................... 313

22.19.2 Programming Using CAN I/O Mode ............................................................................................. 313

22.20 Noise .................................................................................................................................................... 314

Appendix 1. Package Dimensions ........................................................................................ 315

Register Index .......................................................................................................................317

Specifications written in this manual are believed to be accurate, but are not guaranteed to be entirely free

of error. Specifications in this manual may be changed for functional or performance improvements.

Please make sure your manual is the latest edition.

A-6

Page 11

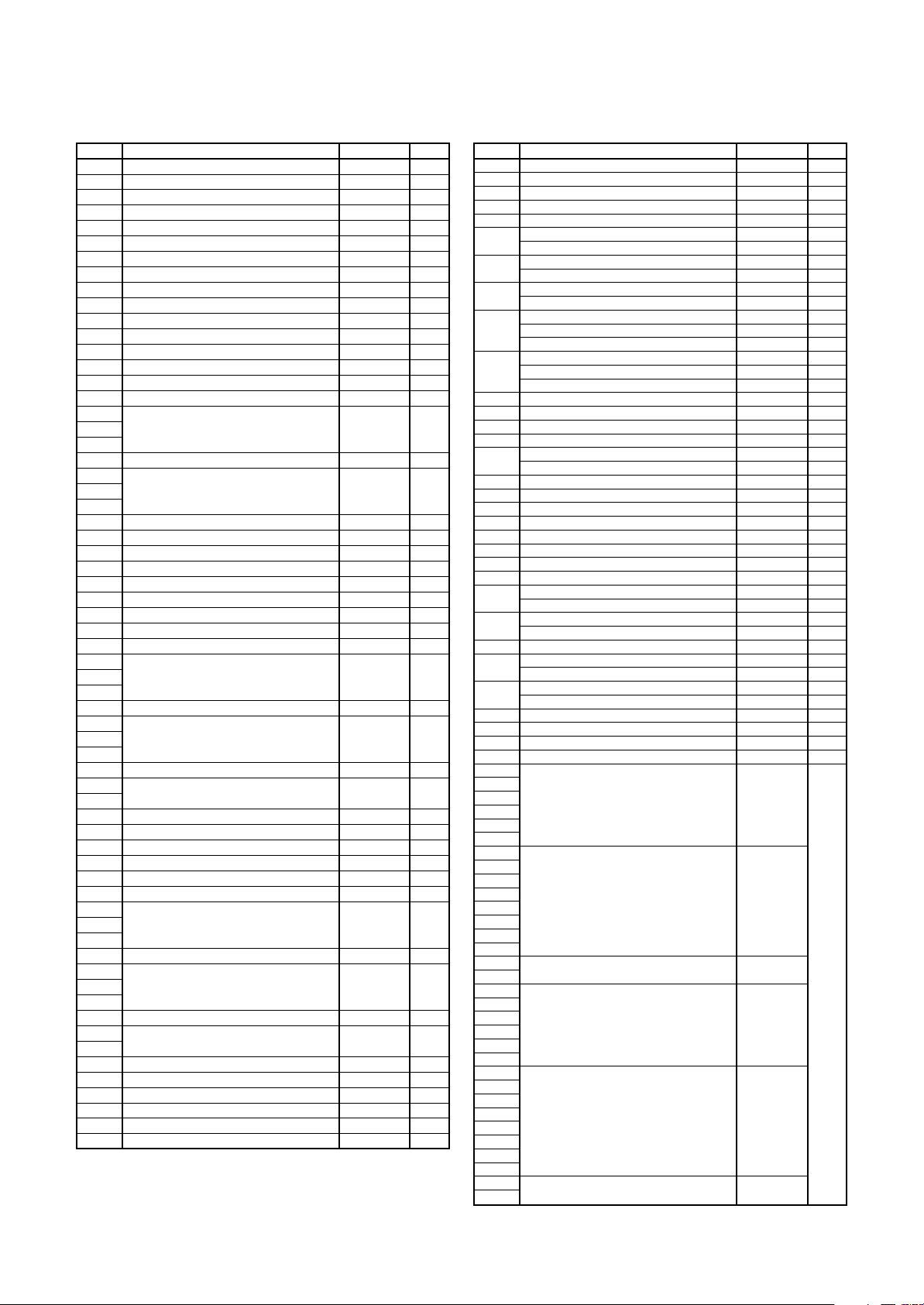

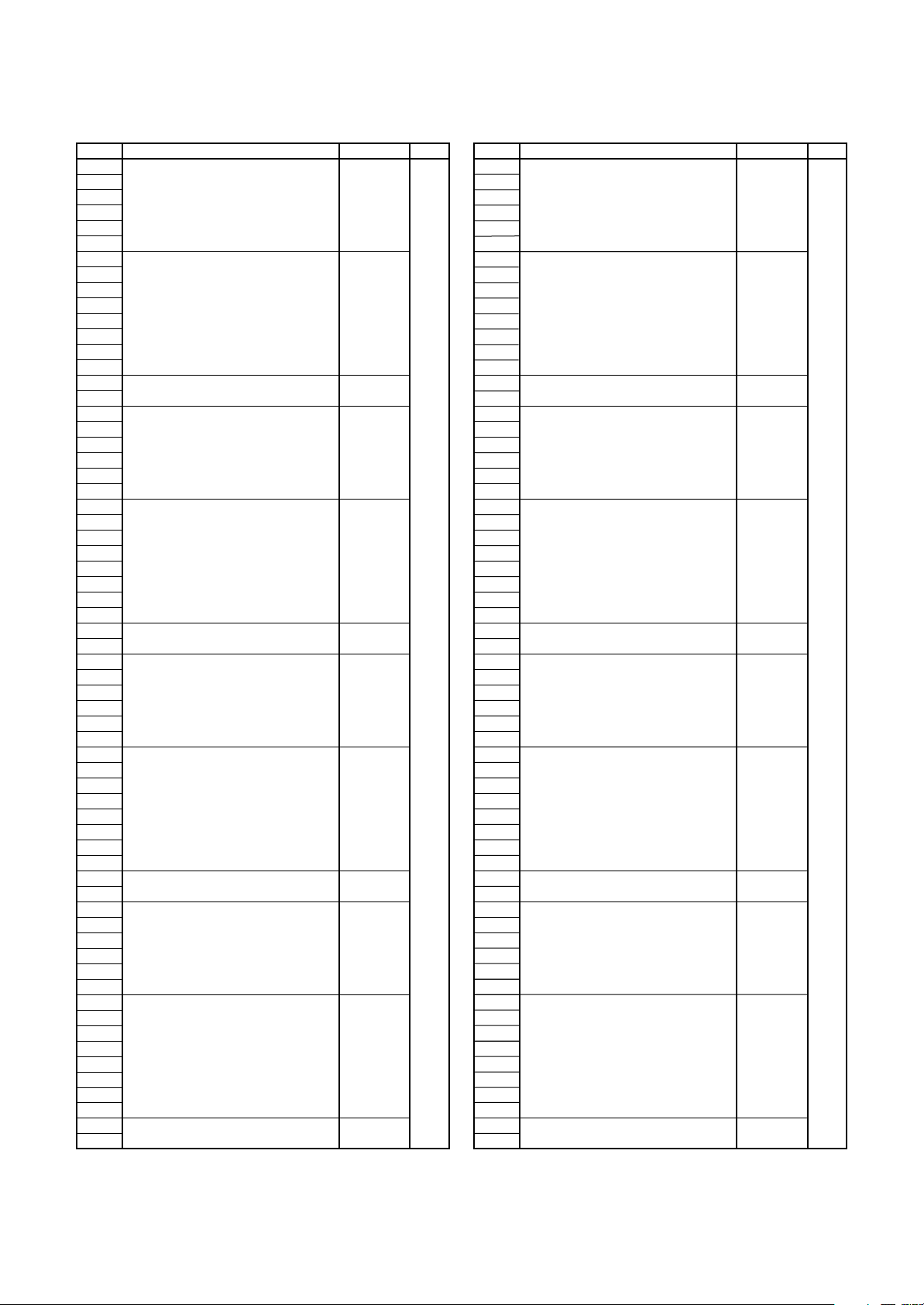

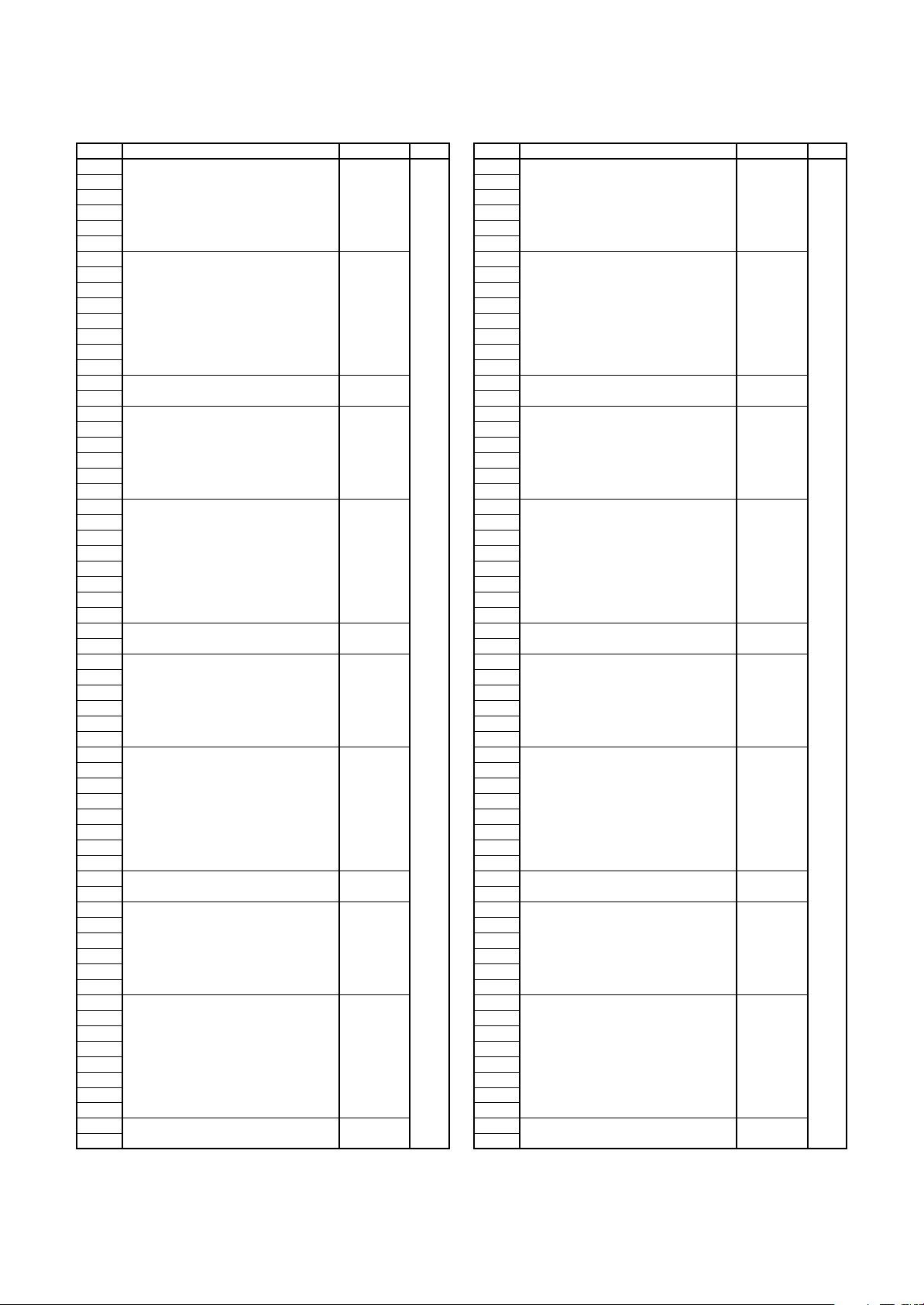

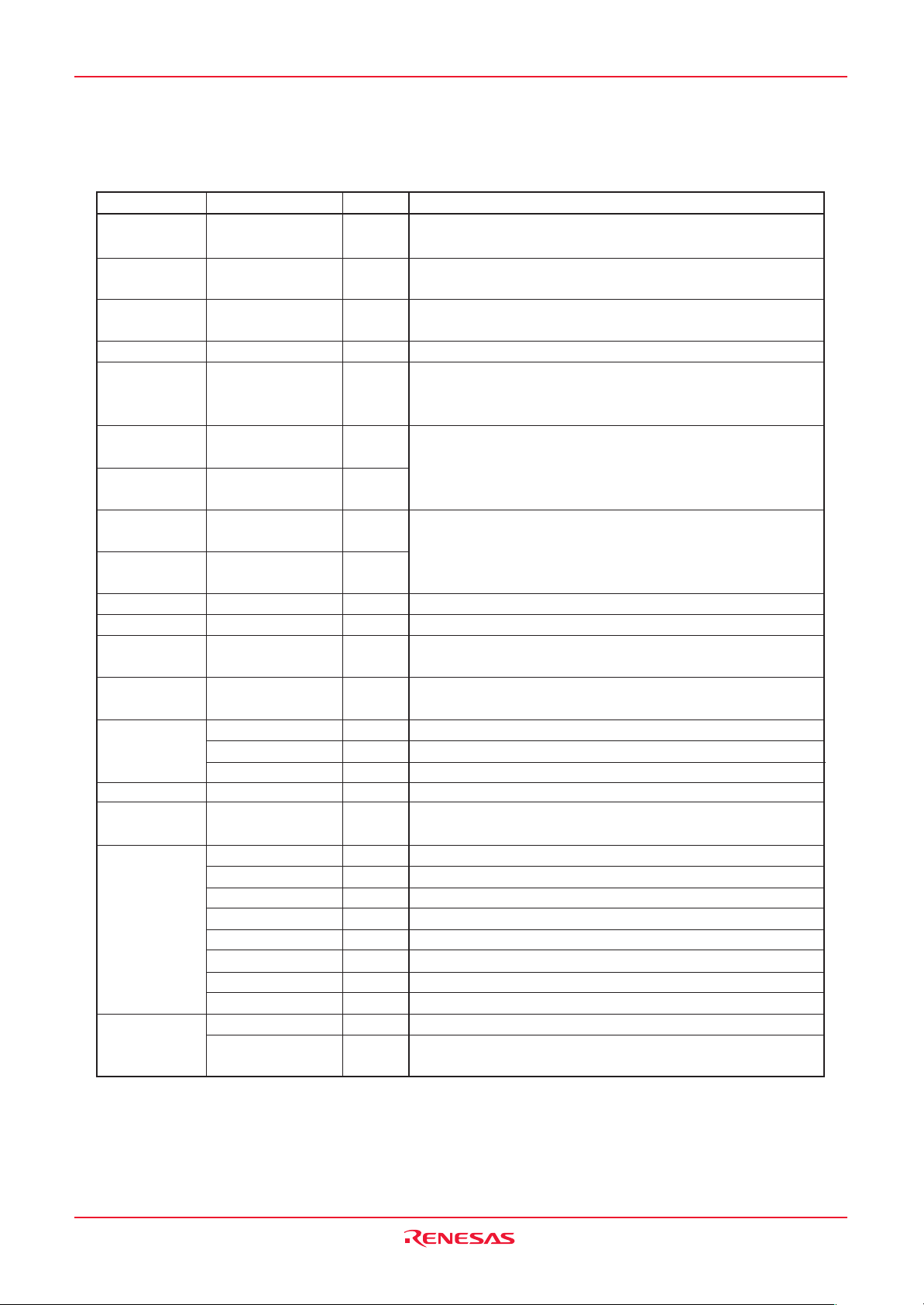

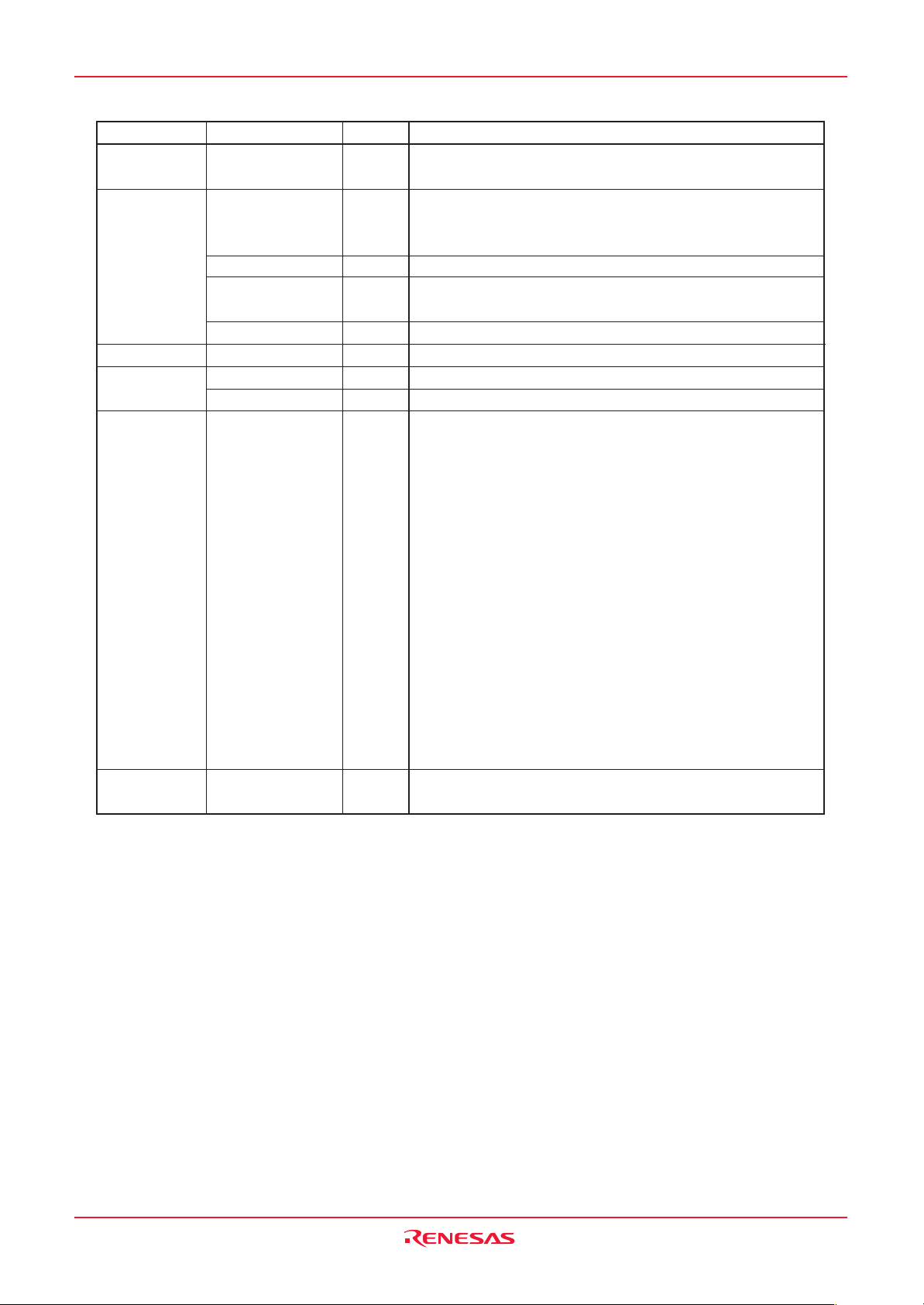

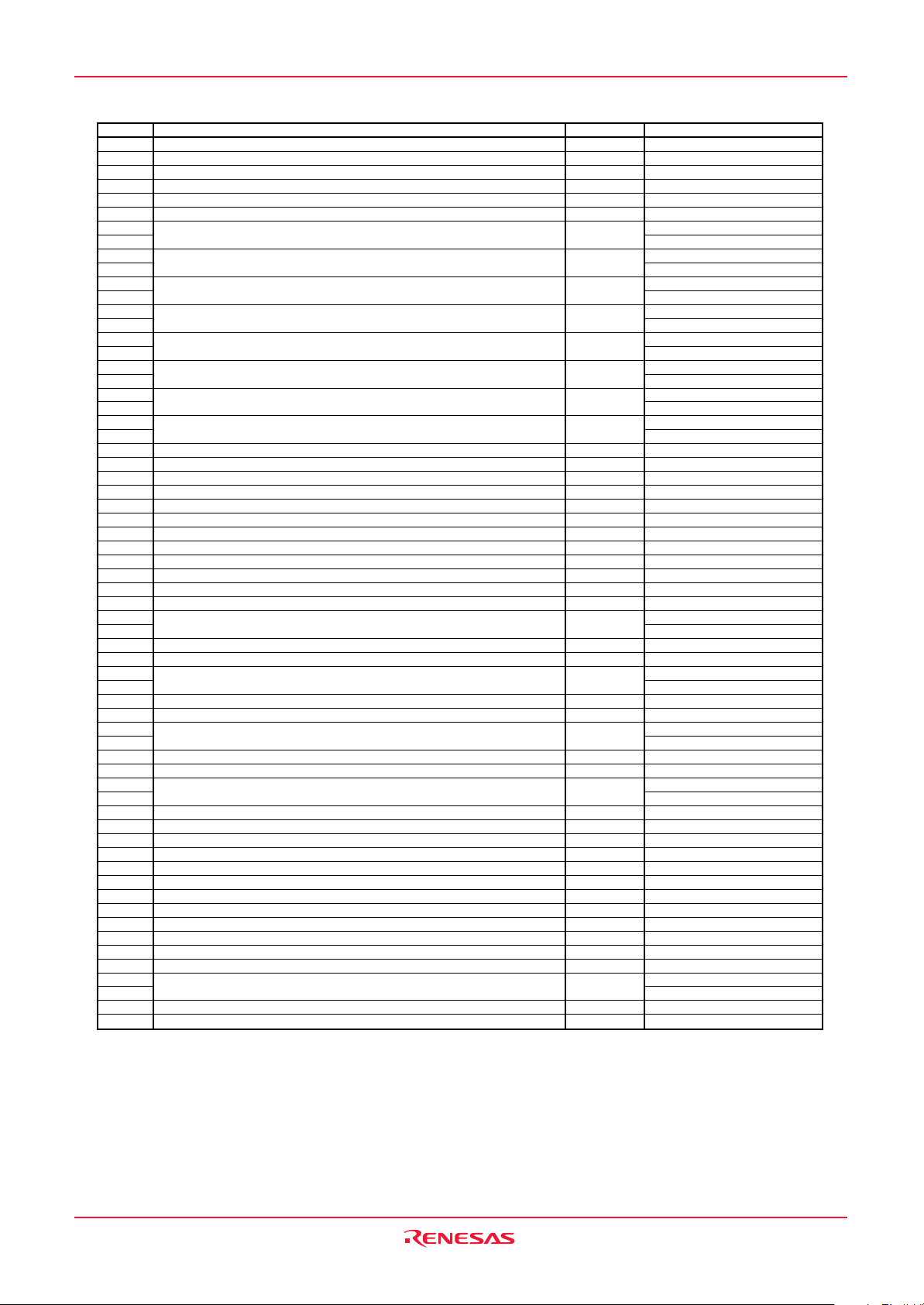

SFR Page Reference

Address Register Symbol Page

C01WKIC

C0RECIC

C0TRMIC

INT3IC

TB5IC

S5IC

TB4IC

U1BCNIC

TB3IC

U0BCNIC

C1RECIC

S4IC

INT5IC

C1TRMIC

S3IC

INT4IC

U2BCNIC

DM0IC

DM1IC

C01ERRIC

ADIC

KUPIC

S2TIC

S2RIC

S0TIC

S0RIC

S1TIC

S1RIC

TA0IC

TA1IC

TA2IC

INT7IC

TA3IC

INT6IC

TA4IC

TB0IC

S6IC

TB1IC

INT8IC

TB2IC

INT0IC

INT1IC

INT2IC

0040h

0041h

0042h

0043h

0044h

0045h

0046h

0047h

0048h

0049h

004Ah

004Bh

004Ch

004Dh

004Eh

004Fh

0050h

0051h

0052h

0053h

0054h

0055h

0056h

0057h

0058h

0059h

005Ah

005Bh

005Ch

005Dh

005Eh

005Fh

0060h

0061h

0062h

0063h

0064h

0065h

0066h

0067h

0068h

0069h

006Ah

006Bh

006Ch

006Dh

006Eh

006Fh

0070h

0071h

0072h

0073h

0074h

0075h

0076h

0077h

0078h

0079h

007Ah

007Bh

007Ch

007Dh

007Eh

007Fh

65

65

65

66

65

65

65

65

65

65

66

66

66

66

66

66

65

65

65

65

65

65

65

65

65

65

65

65

65

65

66

66

66

66

65

65

65

66

66

65

66

66

66

204

205

CAN0/1 Wake-up Interrupt Control Register

CAN0 Successful Reception Interrupt Control Register

CAN0 Successful Transmission Interrupt Control Register

INT3 Interrupt Control Register

Timer B5 Interrupt Control Register

SI/O5 Interrupt Control Register

Timer B4 Interrupt Control Register

UART1 Bus Collision Detection Interrupt Control Register

Timer B3 Interrupt Control Register

UART0 Bus Collision Detection Interrupt Control Register

CAN1 Successful Reception Interrupt Control Register

SI/O4 Interrupt Control Register

INT5 Interrupt Control Register

CAN1 Successful Transmission Interrupt Control Register

SI/O3 Interrupt Control Register

INT4 Interrupt Control Register

UART2 Bus Collision Detection Interrupt Control Register

DMA0 Interrupt Control Register

DMA1 Interrupt Control Register

CAN0/1 Error Interrupt Control Register

A/D Conversion Interrupt Control Register

Key Input Interrupt Control Register

UART2 Transmit Interrupt Control Register

UART2 Receive Interrupt Control Register

UART0 Transmit Interrupt Control Register

UART0 Receive Interrupt Control Register

UART1 Transmit Interrupt Control Register

UART1 Receive Interrupt Control Register

Timer A0 Interrupt Control Register

Timer A1 Interrupt Control Register

Timer A2 Interrupt Control Register

INT7 Interrupt Control Register

Timer A3 Interrupt Control Register

INT6 Interrupt Control Register

Timer A4 Interrupt Control Register

Timer B0 Interrupt Control Register

SI/O6 Interrupt Control Register

Timer B1 Interrupt Control Register

INT8 Interrupt Control Register

Timer B2 Interrupt Control Register

INT0 Interrupt Control Register

INT1 Interrupt Control Register

INT2 Interrupt Control Register

CAN0 Message Box 0: Identifier / DLC

CAN0 Message Box 0: Data Field

CAN0 Message Box 0: Time Stamp

CAN0 Message Box 1: Identifier / DLC

CAN0 Message Box 1: Data Field

CAN0 Message Box 1: Time Stamp

Address Register Symbol Page

0000h

0001h

0002h

0003h

Processor Mode Register 0

0004h

Processor Mode Register 1

0005h

System Clock Control Register 0

0006h

0007h

The blank areas are reserved.

System Clock Control Register 1

0008h

0009h

Address Match Interrupt Enable Register

000Ah

Protect Register

000Bh

000Ch

Oscillation Stop Detection Register

000Dh

000Eh

Watchdog Timer Start Register

000Fh

Watchdog Timer Control Register

0010h

0011h

Address Match Interrupt Register 0

0012h

0013h

0014h

0015h

Address Match Interrupt Register 1

0016h

0017h

0018h

0019h

001Ah

001Bh

001Ch

PLL Control Register 0

001Dh

001Eh

Processor Mode Register 2

001Fh

0020h

0021h

DMA0 Source Pointer

0022h

0023h

0024h

0025h

DMA0 Destination Pointer

0026h

0027h

0028h

DMA0 Transfer Counter

0029h

002Ah

002Bh

002Ch

DMA0 Control Register

002Dh

002Eh

002Fh

0030h

0031h

DMA1 Source Pointer

0032h

0033h

0034h

0035h

DMA1 Destination Pointer

0036h

0037h

0038h

DMA1 Transfer Counter

0039h

003Ah

003Bh

003Ch

DMA1 Control Register

003Dh

003Eh

003Fh

PM0

PM1

CM0

CM1

AIER

PRCR

CM2

WDTS

WDC

RMAD0

RMAD1

PLC0

PM2

SAR0

DAR0

TCR0

DM0CON

SAR1

DAR1

TCR1

DM1CON

32

33

37

38

79

59

39

81

81

79

79

42

41

86

86

86

85

86

86

86

85

B-1

Page 12

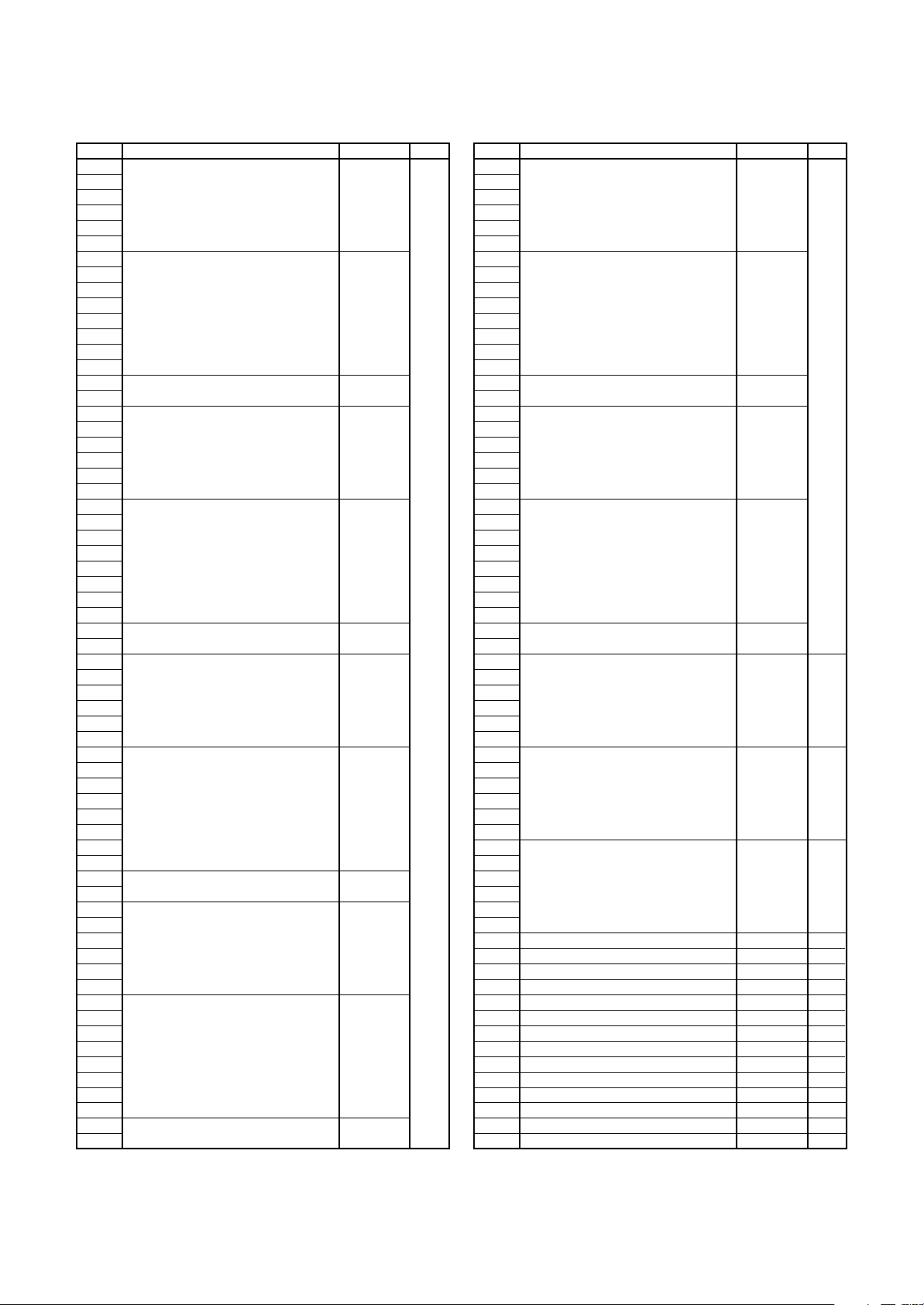

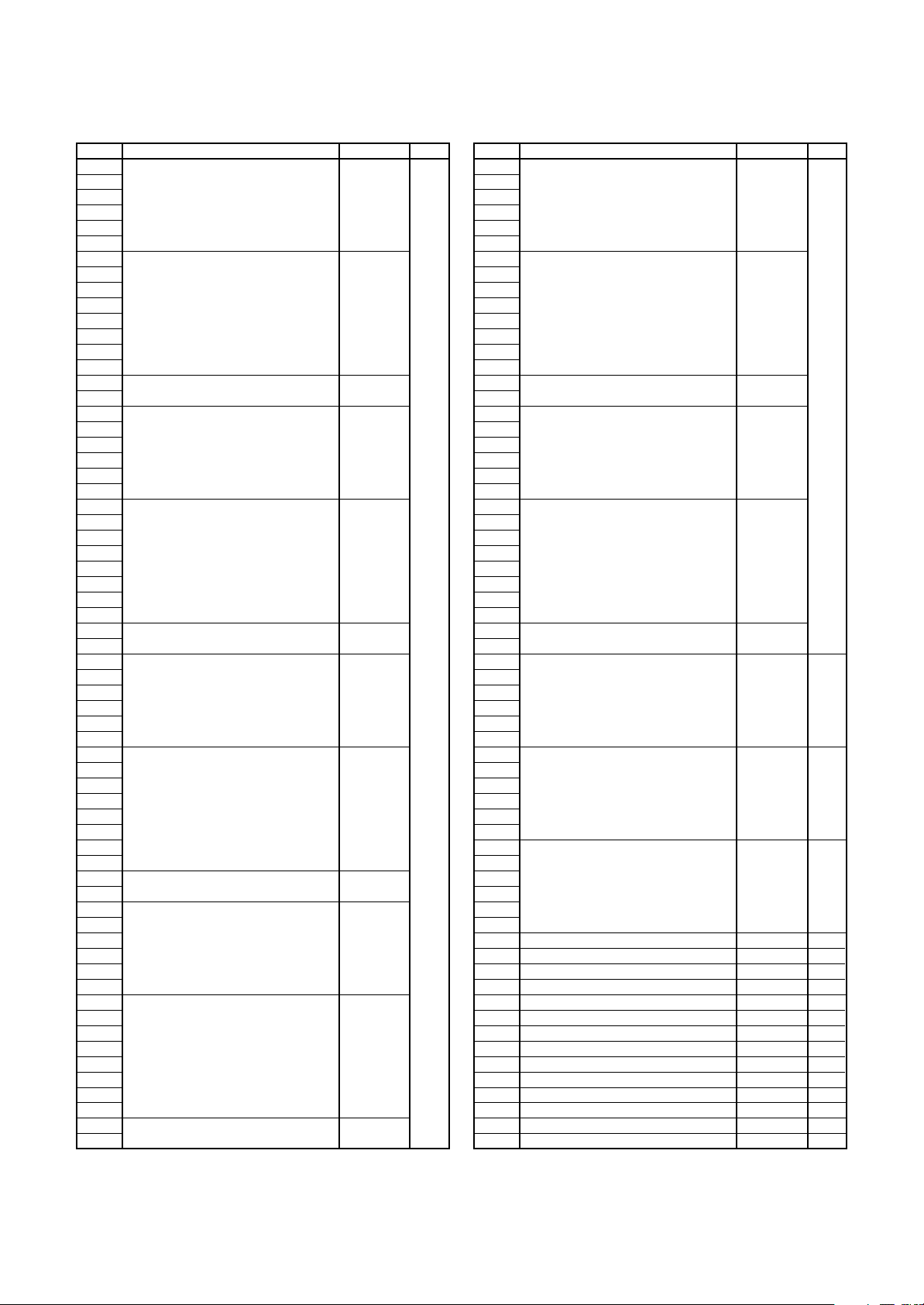

Address Register Symbol Page

Address Register Symbol Page

00C0h

00C1h

00C2h

00C3h

00C4h

00C5h

00C6h

00C7h

00C8h

00C9h

00CAh

00CBh

00CCh

00CDh

00CEh

00CFh

00D0h

00D1h

00D2h

00D3h

00D4h

00D5h

00D6h

00D7h

00D8h

00D9h

00DAh

00DBh

00DCh

00DDh

00DEh

00DFh

00E0h

00E1h

00E2h

00E3h

00E4h

00E5h

00E6h

00E7h

00E8h

00E9h

00EAh

00EBh

00ECh

00EDh

00EEh

00EFh

00F0h

00F1h

00F2h

00F3h

00F4h

00F5h

00F6h

00F7h

00F8h

00F9h

00FAh

00FBh

00FCh

00FDh

00FEh

00FFh

204

205

CAN0 Message Box 6: Identifier / DLC

CAN0 Message Box 6: Data Field

CAN0 Message Box 6: Time Stamp

CAN0 Message Box 7: Identifier / DLC

CAN0 Message Box 7: Data Field

CAN0 Message Box 7: Time Stamp

CAN0 Message Box 8: Identifier / DLC

CAN0 Message Box 8: Data Field

CAN0 Message Box 8: Time Stamp

CAN0 Message Box 9: Identifier / DLC

CAN0 Message Box 9: Data Field

CAN0 Message Box 9: Time Stamp

0080h

0081h

0082h

CAN0 Message Box 2: Identifier / DLC

0083h

0084h

0085h

0086h

0087h

0088h

0089h

CAN0 Message Box 2: Data Field

008Ah

008Bh

008Ch

008Dh

008Eh

CAN0 Message Box 2: Time Stamp

008Fh

0090h

0091h

0092h

CAN0 Message Box 3: Identifier / DLC

0093h

0094h

0095h

0096h

0097h

0098h

0099h

CAN0 Message Box 3: Data Field

009Ah

009Bh

009Ch

009Dh

009Eh

CAN0 Message Box 3: Time Stamp

009Fh

00A0h

00A1h

00A2h

CAN0 Message Box 4: Identifier / DLC

00A3h

00A4h

00A5h

00A6h

00A7h

00A8h

00A9h

CAN0 Message Box 4: Data Field

00AAh

00ABh

00ACh

00ADh

00AEh

CAN0 Message Box 4: Time Stamp

00AFh

00B0h

00B1h

00B2h

CAN0 Message Box 5: Identifier / DLC

00B3h

00B4h

00B5h

00B6h

00B7h

00B8h

00B9h

CAN0 Message Box 5: Data Field

00BAh

00BBh

00BCh

00BDh

00BEh

CAN0 Message Box 5: Time Stamp

00BFh

204

205

B-2

Page 13

Address Register Symbol Page

C0GMR

C0LMAR

C0LMBR

Address Register Symbol Page

0140h

0141h

0142h

0143h

0144h

0145h

0146h

0147h

0148h

0149h

014Ah

014Bh

014Ch

014Dh

014Eh

014Fh

0150h

0151h

0152h

0153h

0154h

0155h

0156h

0157h

0158h

0159h

015Ah

015Bh

015Ch

015Dh

015Eh

015Fh

0160h

0161h

0162h

0163h

0164h

0165h

0166h

0167h

0168h

0169h

016Ah

016Bh

016Ch

016Dh

016Eh

016Fh

0170h

0171h

0172h

0173h

0174h

0175h

0176h

0177h

0178h

0179h

017Ah

017Bh

017Ch

017Dh

017Eh

017Fh

204

205

206

206

206

CAN0 Message Box 14: Identifier /DLC

CAN0 Message Box 14: Data Field

CAN0 Message Box 14: Time Stamp

CAN0 Message Box 15: Identifier /DLC

CAN0 Message Box 15: Data Field

CAN0 Message Box 15: Time Stamp

CAN0 Global Mask Register

CAN0 Local Mask A Register

CAN0 Local Mask B Register

0100h

0101h

0102h

CAN0 Message Box 10: Identifier / DLC

0103h

0104h

0105h

0106h

0107h

0108h

0109h

CAN0 Message Box 10: Data Field

010Ah

010Bh

010Ch

010Dh

010Eh

CAN0 Message Box 10: Time Stamp

010Fh

0110h

0111 h

0112h

CAN0 Message Box 11: Identifier / DLC

0113h

0114h

0115h

0116h

0117h

0118h

0119h

CAN0 Message Box 11: Data Field

011Ah

011Bh

011Ch

011Dh

011Eh

CAN0 Message Box 11: Time Stamp

011Fh

0120h

0121h

0122h

CAN0 Message Box 12: Identifier / DLC

0123h

0124h

0125h

0126h

0127h

0128h

0129h

CAN0 Message Box 12: Data Field

012Ah

012Bh

012Ch

012Dh

012Eh

CAN0 Message Box 12: Time Stamp

012Fh

0130h

0131h

0132h

The blank areas are reserved.

CAN0 Message Box 13: Identifier / DLC

0133h

0134h

0135h

0136h

0137h

0138h

0139h

CAN0 Message Box 13: Data Field

013Ah

013Bh

013Ch

013Dh

013Eh

CAN0 Message Box 13: Time Stamp

013Fh

204

205

B-3

Page 14

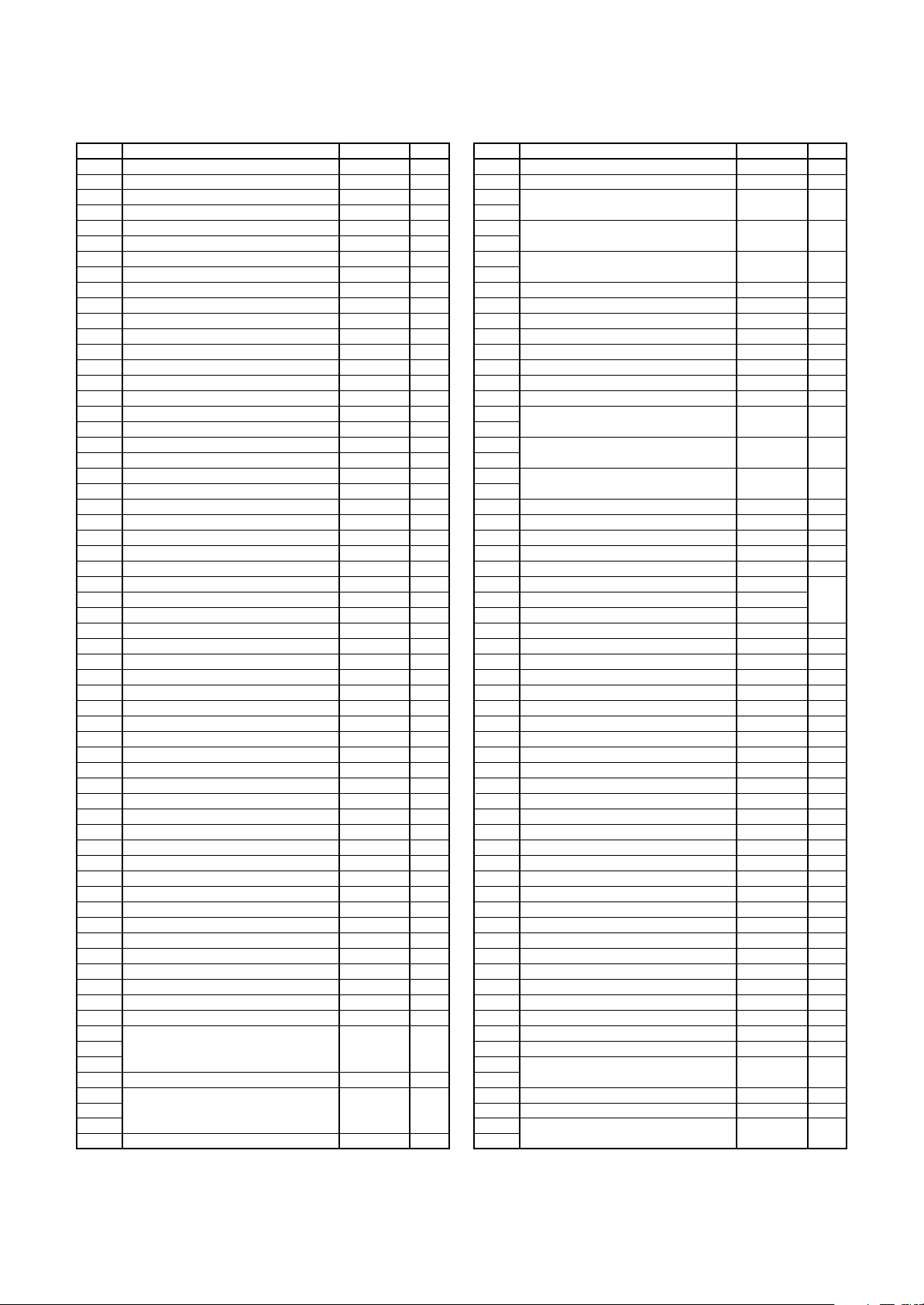

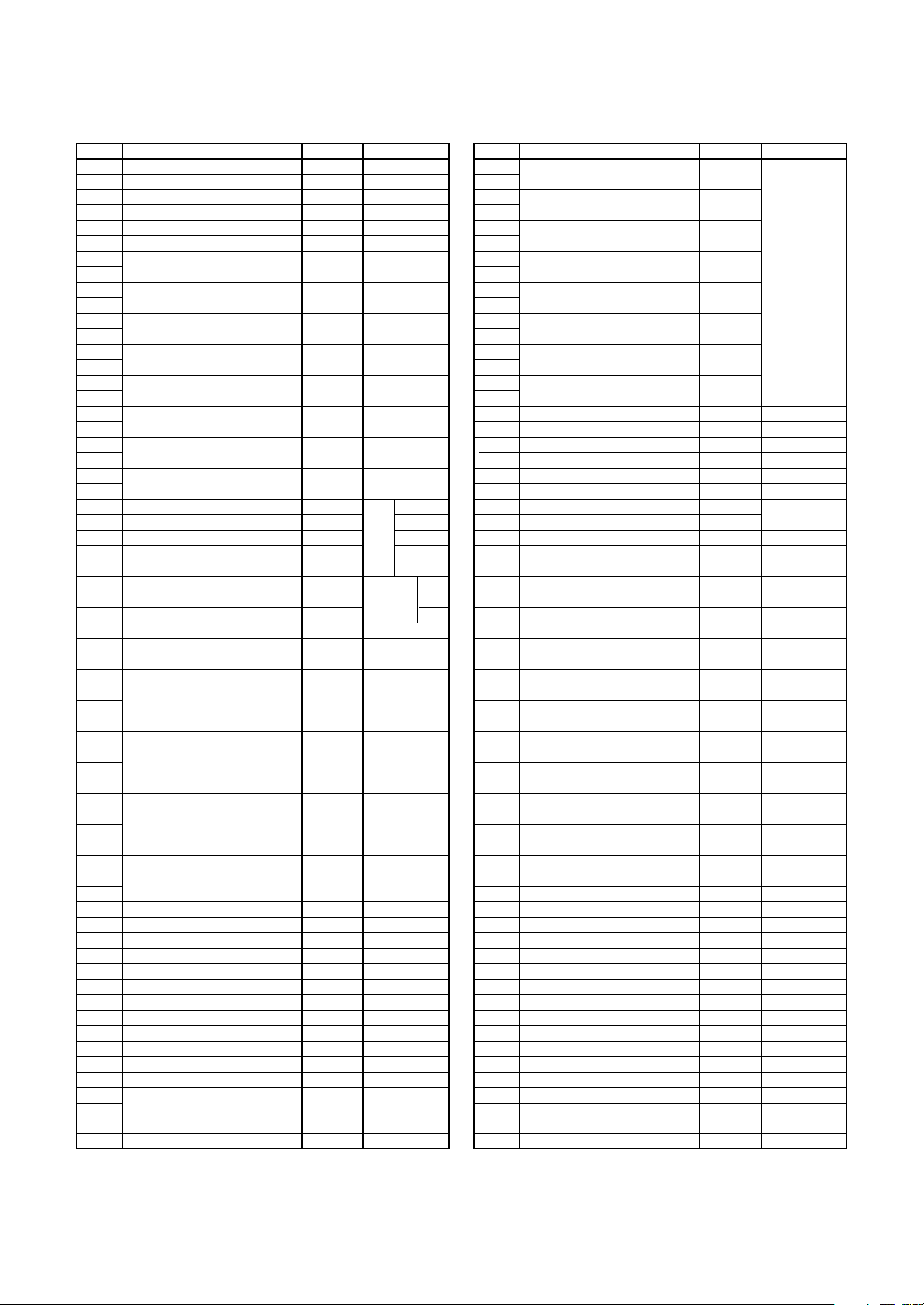

Address Register Symbol Page

Address Register Symbol Page

TBSR

TA11

TA21

TA41

INVC0

INVC1

IDB0

IDB1

DTT

ICTB2

IFSR2

TB3

TB4

TB5

S6TRR

S6C

S6BRG

S3456TRR

TB3MR

TB4MR

TB5MR

IFSR0

IFSR1

S3TRR

S3C

S3BRG

S4TRR

S4C

S4BRG

S5TRR

S5C

S5BRG

U0SMR4

U0SMR3

U0SMR2

U0SMR

U1SMR4

U1SMR3

U1SMR2

U1SMR

U2SMR4

U2SMR3

U2SMR2

U2SMR

U2MR

U2BRG

U2TB

U2C0

U2C1

U2RB

01C0h

01C1h

01C2h

01C3h

01C4h

01C5h

01C6h

01C7h

01C8h

01C9h

01CAh

01CBh

01CCh

01CDh

01CEh

01CFh

01D0h

01D1h

01D2h

01D3h

01D4h

01D5h

01D6h

01D7h

01D8h

01D9h

01DAh

01DBh

01DCh

01DDh

01DEh

01DFh

01E0h

01E1h

01E2h

01E3h

01E4h

01E5h

01E6h

01E7h

01E8h

01E9h

01EAh

01EBh

01ECh

01EDh

01EEh

01EFh

01F0h

01F1h

01F2h

01F3h

01F4h

01F5h

01F6h

01F7h

01F8h

01F9h

01FAh

01FBh

01FCh

01FDh

01FEh

01FFh

111

122

122

122

119

120

121

121

121

123

76

110

110

110

176

176

176

177

110

112

113

115

74

75

176

176

176

176

176

176

176

176

176

137

136

136

135

137

136

136

135

137

136

136

135

133

132

132

133

134

132

Timer B3, B4, B5 Count Start Flag

Timer A1-1 Register

Timer A2-1 Register

Timer A4-1 Register

Three-Phase PWM Control Register 0

Three-Phase PWM Control Register 1

Three-Phase Output Buffer Register 0

Three-Phase Output Buffer Register 1

Dead Time Timer

Timer B2 Interrupt Occurrence Frequency Set Counter

Interrupt Cause Select Register 2

Timer B3 Register

Timer B4 Register

Timer B5 Register

SI/O6 Transmit/Receive Register

SI/O6 Control Register

SI/O6 Bit Rate Generator

SI/O3, 4, 5, 6 Transmit/Receive Register

Timer B3 Mode Register

Timer B4 Mode Register

Timer B5 Mode Register

Interrupt Cause Select Register 0

Interrupt Cause Select Register 1

SI/O3 Transmit/Receive Register

SI/O3 Control Register

SI/O3 Bit Rate Generator

SI/O4 Transmit/Receive Register

SI/O4 Control Register

SI/O4 Bit Rate Generator

SI/O5 Transmit/Receive Register

SI/O5 Control Register

SI/O5 Bit Rate Generator

UART0 Special Mode Register 4

UART0 Special Mode Register 3

UART0 Special Mode Register 2

UART0 Special Mode Register

UART1 Special Mode Register 4

UART1 Special Mode Register 3

UART1 Special Mode Register 2

UART1 Special Mode Register

UART2 Special Mode Register 4

UART2 Special Mode Register 3

UART2 Special Mode Register 2

UART2 Special Mode Register

UART2 Transmit/Receive Mode Register

UART2 Bit Rate Generator

UART2 Transmit Buffer Register

UART2 Transmit/Receive Control Register 0

UART2 Transmit/Receive Control Register 1

UART2 Receive Buffer Register

0180h

0181h

0182h

0183h

0184h

0185h

0186h

0187h

0188h

0189h

018Ah

018Bh

018Ch

018Dh

018Eh

018Fh

0190h

0191h

0192h

0193h

0194h

0195h

0196h

0197h

0198h

0199h

019Ah

019Bh

019Ch

019Dh

019Eh

019Fh

01A0h

01A1h

01A2h

01A3h

01A4h

01A5h

01A6h

01A7h

01A8h

01A9h

01AAh

01ABh

01ACh

01ADh

01AEh

01AFh

01B0h

01B1h

01B2h

01B3h

01B4h

01B5h

The blank areas are reserved.

Flash Memory Control Register 1

01B6h

01B7h

Flash Memory Control Register 0

01B8h

01B9h

Address Match Interrupt Register 2

01BAh

01BBh

Address Match Interrupt Enable Register 2

01BCh

01BDh

Address Match Interrupt Register 3

01BEh

01BFh

FMR1

FMR0

RMAD2

AIER2

RMAD3

244

244

79

79

79

B-4

Page 15

Address Register Symbol Page

C0AFS

C1AFS

PCLKR

CCLKR

Address Register Symbol Page

0240h

0241h

0242h

0243h

0244h

0245h

0246h

0247h

0248h

0249h

024Ah

024Bh

024Ch

024Dh

024Eh

024Fh

0250h

0251h

0252h

0253h

0254h

0255h

0256h

0257h

0258h

0259h

025Ah

025Bh

025Ch

025Dh

025Eh

025Fh

0260h

0261h

0262h

0263h

0264h

0265h

0266h

0267h

0268h

0269h

026Ah

026Bh

026Ch

026Dh

026Eh

026Fh

0270h

0271h

0272h

0273h

0274h

0275h

0276h

0277h

0278h

0279h

027Ah

027Bh

027Ch

027Dh

027Eh

027Fh

212

212

40

41

204

205

CAN0 Acceptance Filter Support Register

CAN1 Acceptance Filter Support Register

Peripheral Clock Select Register

CAN0/1 Clock Select Register

CAN1 Message Box 0: Identifier / DLC

CAN1 Message Box 0: Data Field

CAN1 Message Box 0:Time Stamp

CAN1 Message Box 1: Identifier / DLC

CAN1 Message Box 1: Data Field

CAN1 Message Box 1:Time Stamp

0200h

CAN0 Message Control Register 0

CAN0 Message Control Register 1

0201h

CAN0 Message Control Register 2

0202h

0203h

CAN0 Message Control Register 3

0204h

CAN0 Message Control Register 4

0205h

CAN0 Message Control Register 5

0206h

CAN0 Message Control Register 6

0207h

CAN0 Message Control Register 7

0208h

The blank areas are reserved.

CAN0 Message Control Register 8

0209h

CAN0 Message Control Register 9

020Ah

CAN0 Message Control Register 10

020Bh

CAN0 Message Control Register 11

020Ch

CAN0 Message Control Register 12

020Dh

CAN0 Message Control Register 13

020Eh

CAN0 Message Control Register 14

020Fh

CAN0 Message Control Register 15

0210h

CAN0 Control Register

0211h

0212h

CAN0 Status Register

0213h

0214h

CAN0 Slot Status Register

0215h

0216h

CAN0 Interrupt Control Register

0217h

0218h

CAN0 Extended ID Register

0219h

021Ah

CAN0 Configuration Register

021Bh

021Ch

CAN0 Receive Error Count Register

021Dh

CAN0 Transmit Error Count Register

021Eh

CAN0 Time Stamp Register

021Fh

0220h

CAN1 Message Control Register 0

0221h

CAN1 Message Control Register 1

0222h

CAN1 Message Control Register 2

0223h

CAN1 Message Control Register 3

0224h

CAN1 Message Control Register 4

0225h

CAN1 Message Control Register 5

0226h

CAN1 Message Control Register 6

0227h

CAN1 Message Control Register 7

0228h

CAN1 Message Control Register 8

0229h

CAN1 Message Control Register 9

022Ah

CAN1 Message Control Register 10

022Bh

CAN1 Message Control Register 11

022Ch

CAN1 Message Control Register 12

022Dh

CAN1 Message Control Register 13

022Eh

CAN1 Message Control Register 14

022Fh

CAN1 Message Control Register 15

0230h

CAN1 Control Register

0231h

0232h

CAN1 Status Register

0233h

0234h

CAN1 Slot Status Register

0235h

0236h

CAN1 Interrupt Control Register

0237h

0238h

CAN1 Extended ID Register

0239h

023Ah

CAN1 Configuration Register

023Bh

023Ch

CAN1 Receive Error Count Register

023Dh

CAN1 Transmit Error Count Register

023Eh

CAN1 Time Stamp Register

023Fh

C0MCTL0

C0MCTL1

C0MCTL2

C0MCTL3

C0MCTL4

C0MCTL5

C0MCTL6

C0MCTL7

C0MCTL8

C0MCTL9

C0MCTL10

C0MCTL11

C0MCTL12

C0MCTL13

C0MCTL14

C0MCTL15

C0CTLR

C0STR

C0SSTR

C0ICR

C0IDR

C0CONR

C0RECR

C0TECR

C0TSR

C1MCTL0

C1MCTL1

C1MCTL2

C1MCTL3

C1MCTL4

C1MCTL5

C1MCTL6

C1MCTL7

C1MCTL8

C1MCTL9

C1MCTL10

C1MCTL11

C1MCTL12

C1MCTL13

C1MCTL14

C1MCTL15

C1CTLR

C1STR

C1SSTR

C1ICR

C1IDR

C1CONR

C1RECR

C1TECR

C1TSR

207

208

209

210

210

210

211

212

212

212

207

208

209

210

210

210

211

212

212

212

B-5

Page 16

Address Register Symbol Page

Address Register Symbol Page

02C0h

02C1h

02C2h

02C3h

02C4h

02C5h

02C6h

02C7h

02C8h

02C9h

02CAh

02CBh

02CCh

02CDh

02CEh

02CFh

02D0h

02D1h

02D2h

02D3h

02D4h

02D5h

02D6h

02D7h

02D8h

02D9h

02DAh

02DBh

02DCh

02DDh

02DEh

02DFh

02E0h

02E1h

02E2h

02E3h

02E4h

02E5h

02E6h

02E7h

02E8h

02E9h

02EAh

02EBh

02ECh

02EDh

02EEh

02EFh

02F0h

02F1h

02F2h

02F3h

02F4h

02F5h

02F6h

02F7h

02F8h

02F9h

02FAh

02FBh

02FCh

02FDh

02FEh

02FFh

204

205

CAN1 Message Box 6: Identifier / DLC

CAN1 Message Box 6: Data Field

CAN1 Message Box 6: Time Stamp

CAN1 Message Box 7: Identifier / DLC

CAN1 Message Box 7: Data Field

CAN1 Message Box 7: Time Stamp

CAN1 Message Box 8: Identifier / DLC

CAN1 Message Box 8: Data Field

CAN1 Message Box 8: Time Stamp

CAN1 Message Box 9: Identifier / DLC

CAN1 Message Box 9: Data Field

CAN1 Message Box 9: Time Stamp

0280h

0281h

0282h

CAN1 Message Box 2: Identifier / DLC

0283h

0284h

0285h

0286h

0287h

0288h

0289h

CAN1 Message Box 2: Data Field

028Ah

028Bh

028Ch

028Dh

028Eh

CAN1 Message Box 2: Time Stamp

028Fh

0290h

0291h

0292h

CAN1 Message Box 3: Identifier / DLC

0293h

0294h

0295h

0296h

0297h

0298h

0299h

CAN1 Message Box 3: Data Field

029Ah

029Bh

029Ch

029Dh

029Eh

CAN1 Message Box 3: Time Stamp

029Fh

02A0h

02A1h

02A2h

CAN1 Message Box 4: Identifier / DLC

02A3h

02A4h

02A5h

02A6h

02A7h

02A8h

02A9h

CAN1 Message Box 4: Data Field

02AAh

02ABh

02ACh

02ADh

02AEh

CAN1 Message Box 4: Time Stamp

02AFh

02B0h

02B1h

02B2h

CAN1 Message Box 5: Identifier / DLC

02B3h

02B4h

02B5h

02B6h

02B7h

02B8h

02B9h

CAN1 Message Box 5: Data Field

02BAh

02BBh

02BCh

02BDh

02BEh

CAN1 Message Box 5: Time Stamp

02BFh

204

205

B-6

Page 17

Address Register Symbol Page

C1GMR

C1LMAR

C1LMBR

Address Register Symbol Page

0340h

0341h

0342h

0343h

0344h

0345h

0346h

0347h

0348h

0349h

034Ah

034Bh

034Ch

034Dh

034Eh

034Fh

0350h

0351h

0352h

0353h

0354h

0355h

0356h

0357h

0358h

0359h

035Ah

035Bh

035Ch

035Dh

035Eh

035Fh

0360h

0361h

0362h

0363h

0364h

0365h

0366h

0367h

0368h

0369h

036Ah

036Bh

036Ch

036Dh

036Eh

036Fh

0370h

0371h

0372h

0373h

0374h

0375h

0376h

0377h

0378h

0379h

037Ah

037Bh

037Ch

037Dh

037Eh

037Fh

204

205

206

206

206

CAN1 Message Box 14: Identifier / DLC

CAN1 Message Box 14: Data Field

CAN1 Message Box 14: Time Stamp

CAN1 Message Box 15: Identifier / DLC

CAN1 Message Box 15: Data Field

CAN1 Message Box 15: Time Stamp

CAN1 Global Mask Register

CAN1 Local Mask A Register

CAN1 Local Mask B Register

0300h

0301h

0302h

CAN1 Message Box 10: Identifier / DLC

0303h

0304h

0305h

0306h

0307h

0308h

0309h

CAN1 Message Box 10: Data Field

030Ah

030Bh

030Ch

030Dh

030Eh

CAN1 Message Box 10: Time Stamp

030Fh

0310h

0311h

0312h

CAN1 Message Box 11: Identifier / DLC

0313h

0314h

0315h

0316h

0317h

0318h

0319h

CAN1 Message Box 11: Data Field

031Ah

031Bh

031Ch

031Dh

031Eh

CAN1 Message Box 11: Time Stamp

031Fh

0320h

0321h

0322h

CAN1 Message Box 12: Identifier / DLC

0323h

0324h

0325h

0326h

0327h

0328h

0329h

CAN1 Message Box 12: Data Field

032Ah

032Bh

032Ch

032Dh

032Eh

CAN1 Message Box 12: Time Stamp

032Fh

0330h

0331h

0332h

The blank areas are reserved.

CAN1 Message Box 13: Identifier / DLC

0333h

0334h

0335h

0336h

0337h

0338h

0339h

CAN1 Message Box 13: Data Field

033Ah

033Bh

033Ch

033Dh

033Eh

CAN1 Message Box 13: Time Stamp

033Fh

204

205

B-7

Page 18

Address Register Symbol Page

Address Register Symbol Page

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

ADCON2

ADCON0

ADCON1

DA0

DA1

DACON

PC14

PUR3

P0

P1

PD0

PD1

P2

P3

PD2

PD3

P4

P5

PD4

PD5

P6

P7

PD6

PD7

P8

P9

PD8

PD9

P10

P11

PD10

PD11

P12

P13

PD12

PD13

PUR0

PUR1

PUR2

PCR

03C0h

03C1h

03C2h

03C3h

03C4h

03C5h

03C6h

03C7h

03C8h

03C9h

03CAh

03CBh

03CCh

03CDh

03CEh

03CFh

03D0h

03D1h

03D2h

03D3h

03D4h

03D5h

03D6h

03D7h

03D8h

03D9h

03DAh

03DBh

03DCh

03DDh

03DEh

03DFh

03E0h

03E1h

03E2h

03E3h

03E4h

03E5h

03E6h

03E7h

03E8h

03E9h

03EAh

03EBh

03ECh

03EDh

03EEh

03EFh

03F0h

03F1h

03F2h

03F3h

03F4h

03F5h

03F6h

03F7h

03F8h

03F9h

03FAh

03FBh

03FCh

03FDh

03FEh

03FFh

184

184

183,186,188

190,192,194

199

199

199

234

236

234

234

233

233

234

234

233

233

234

234

233

233

234

234

233

233

234

234

233

233

234

234

233

233

234

234

233

233

235

235

235

236

A/D Register 0

A/D Register 1

A/D Register 2

A/D Register 3

A/D Register 4

A/D Register 5

A/D Register 6

A/D Register 7

A/D Control Register 2

A/D Control Register 0

A/D Control Register 1

D/A Register 0

D/A Register 1

D/A Control Register

Port P14 Control Register

Pull-Up Control Register 3

Port P0 Register

Port P1 Register

Port P0 Direction Register

Port P1 Direction Register

Port P2 Register

Port P3 Register

Port P2 Direction Register

Port P3 Direction Register

Port P4 Register

Port P5 Register

Port P4 Direction Register

Port P5 Direction Register

Port P6 Register

Port P7 Register

Port P6 Direction Register

Port P7 Direction Register

Port P8 Register

Port P9 Register

Port P8 Direction Register

Port P9 Direction Register

Port P10 Register

Port P11 Register

Port P10 Direction Register

Port P11 Direction Register

Port P12 Register

Port P13 Register

Port P12 Direction Register

Port P13 Direction Register

Pull-up Control Register 0

Pull-up Control Register 1

Pull-up Control Register 2

Port Control Register

0380h

Count Start Flag

0381h

Clock Prescaler Reset Flag

0382h

One-Shot Start Flag

0383h

Trigger Select Register

0384h

Up/Down Flag

0385h

0386h

Timer A0 Register

0387h

0388h

The blank areas are reserved.

Timer A1 Register

0389h

038Ah

Timer A2 Register

038Bh

038Ch

Timer A3 Register

038Dh

038Eh

Timer A4 Register

038Fh

0390h

Timer B0 Register

0391h

0392h

Timer B1 Register

0393h

0394h

Timer B2 Register

0395h

Timer A0 Mode Register

0396h

Timer A1 Mode Register

0397h

Timer A2 Mode Register

0398h

Timer A3 Mode Register

0399h

Timer A4 Mode Register

039Ah

Timer B0 Mode Register

039Bh

Timer B1 Mode Register

039Ch

Timer B2 Mode Register

039Dh

Timer B2 Special Mode Register

039Eh

039Fh

UART0 Transmit/Receive Mode Register

03A0h

UART0 Bit Rate Generator

03A1h

03A2h

UART0 Transmit Buffer Register

03A3h

UART0 Transmit/Receive Control Register 0

03A4h

UART0 Transmit/Receive Control Register 1

03A5h

03A6h

UART0 Receive Buffer Register

03A7h

03A8h

UART1 Transmit/Receive Mode Register

03A9h

UART1 Bit Rate Generator

03AAh

UART1 Transmit Buffer Register

03ABh

03ACh

UART1 Transmit/Receive Control Register 0

03ADh

UART1 Transmit/Receive Control Register 1

03AEh

UART1 Receive Buffer Register

03AFh

03B0h

UART Transmit/Receive Control Register 2

03B1h

03B2h

03B3h

03B4h

03B5h

03B6h

03B7h

03B8h

DMA0 Request Cause Select Register

03B9h

03BAh

DMA1 Request Cause Select Register

03BBh

03BCh

CRC Data Register

03BDh

03BEh

CRC Input Register

03BFh

TABSR

CPSRF

ONSF

TRGSR

UDF

TA0

TA1

TA2

TA3

TA4

TB0

TB1

TB2

TA0MR

TA1MR

TA2MR

TA3MR

TA4MR

TB0MR

TB1MR

TB2MR

TB2SC

U0MR

U0BRG

U0TB

U0C0

U0C1

U0RB

U1MR

U1BRG

U1TB

U1C0

U1C1

U1RB

UCON

DM0SL

DM1SL

CRCD

CRCIN

96,111,124

97,111

97

97,124

96

95

95

122

95

122

95

95

122

110

110

110

122

95

98

125

100

102,125

105

102

107

102,125

110,112

113,115

125

123

133

132

132

133

134

132

133

132

132

133

134

132

135

84

85

200

200

B-8

Page 19

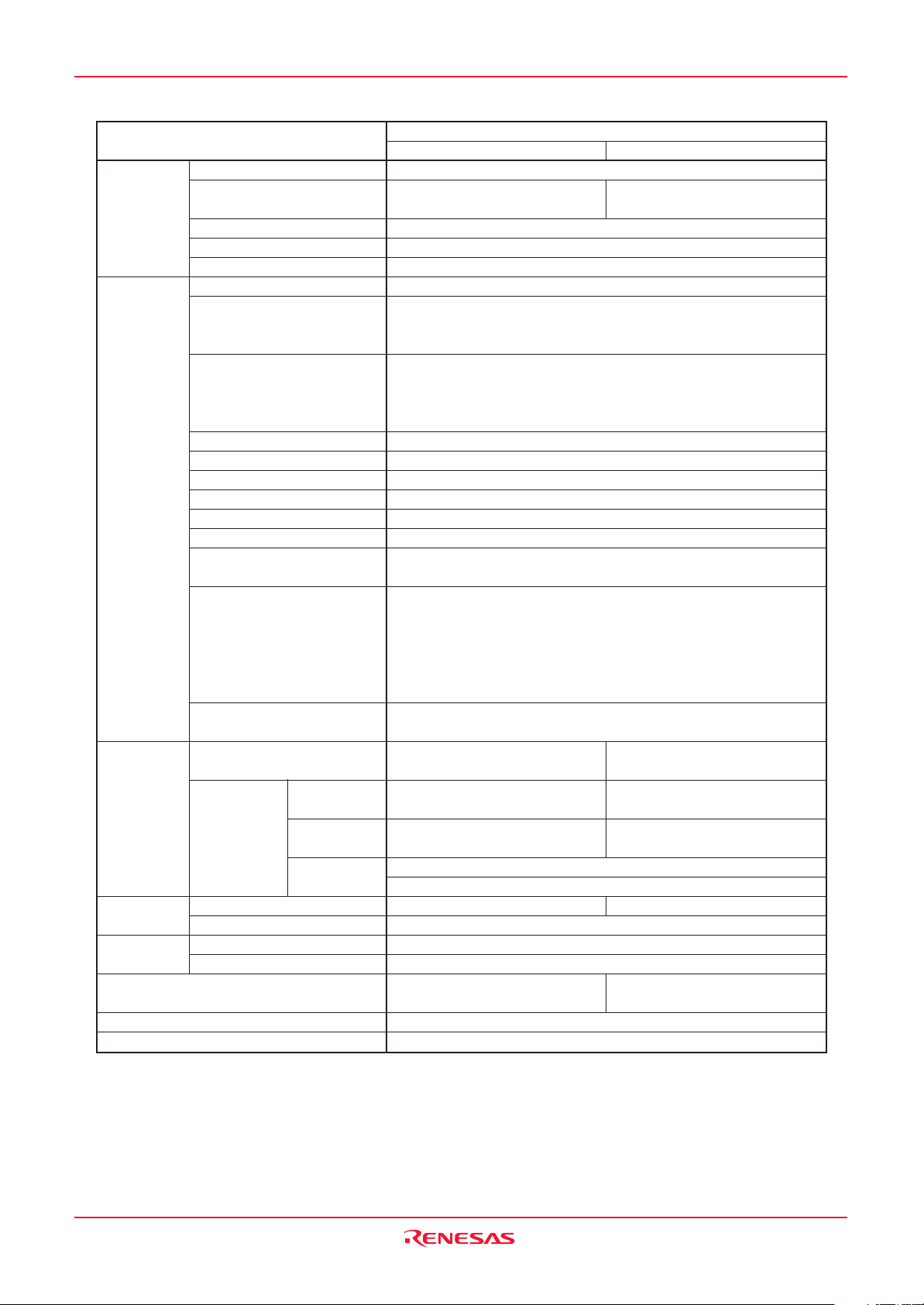

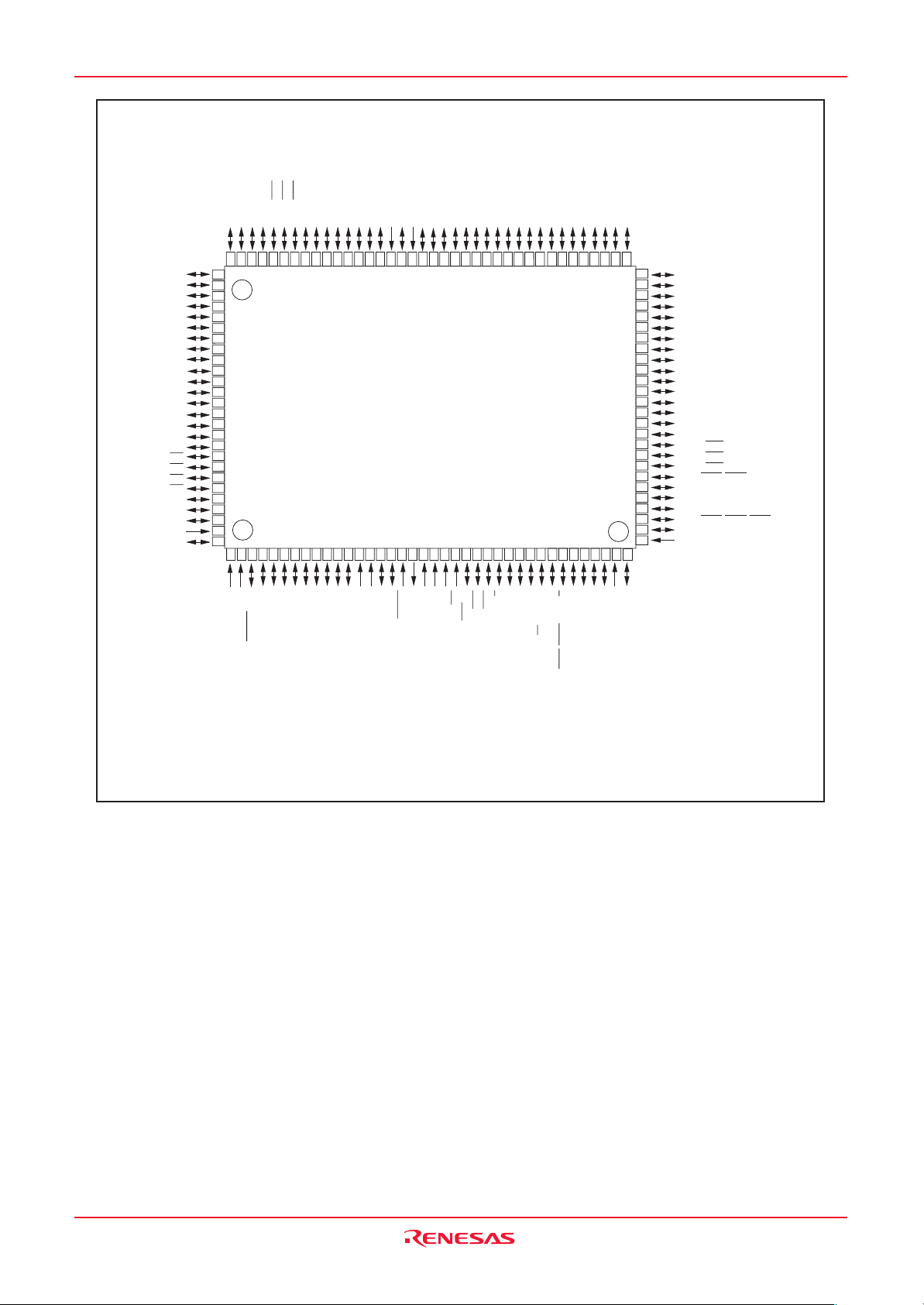

M16C/6N Group (M16C/6NK, M16C/6NM)

Under development

This document is under development and its contents are subject to change

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

1. Overview

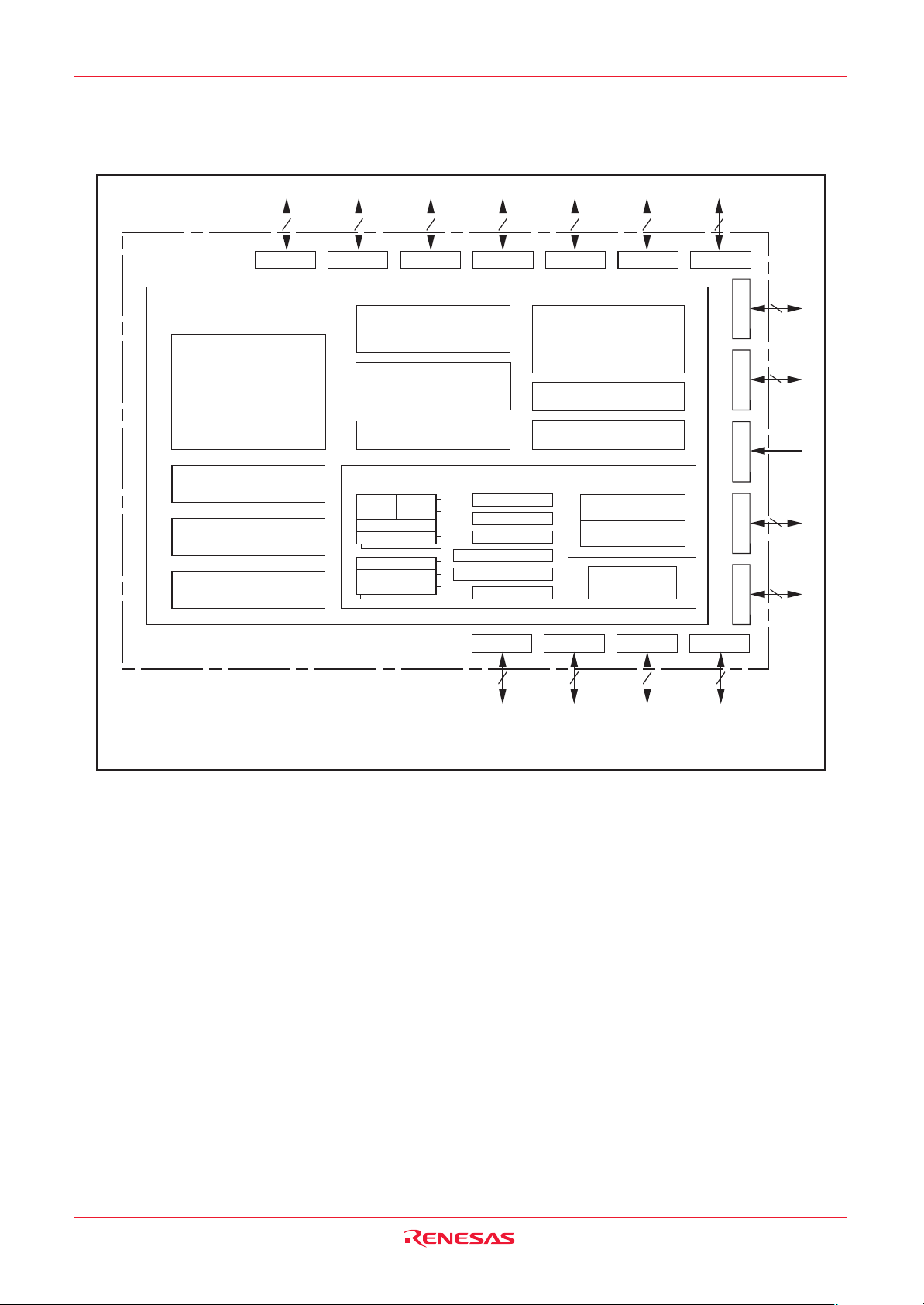

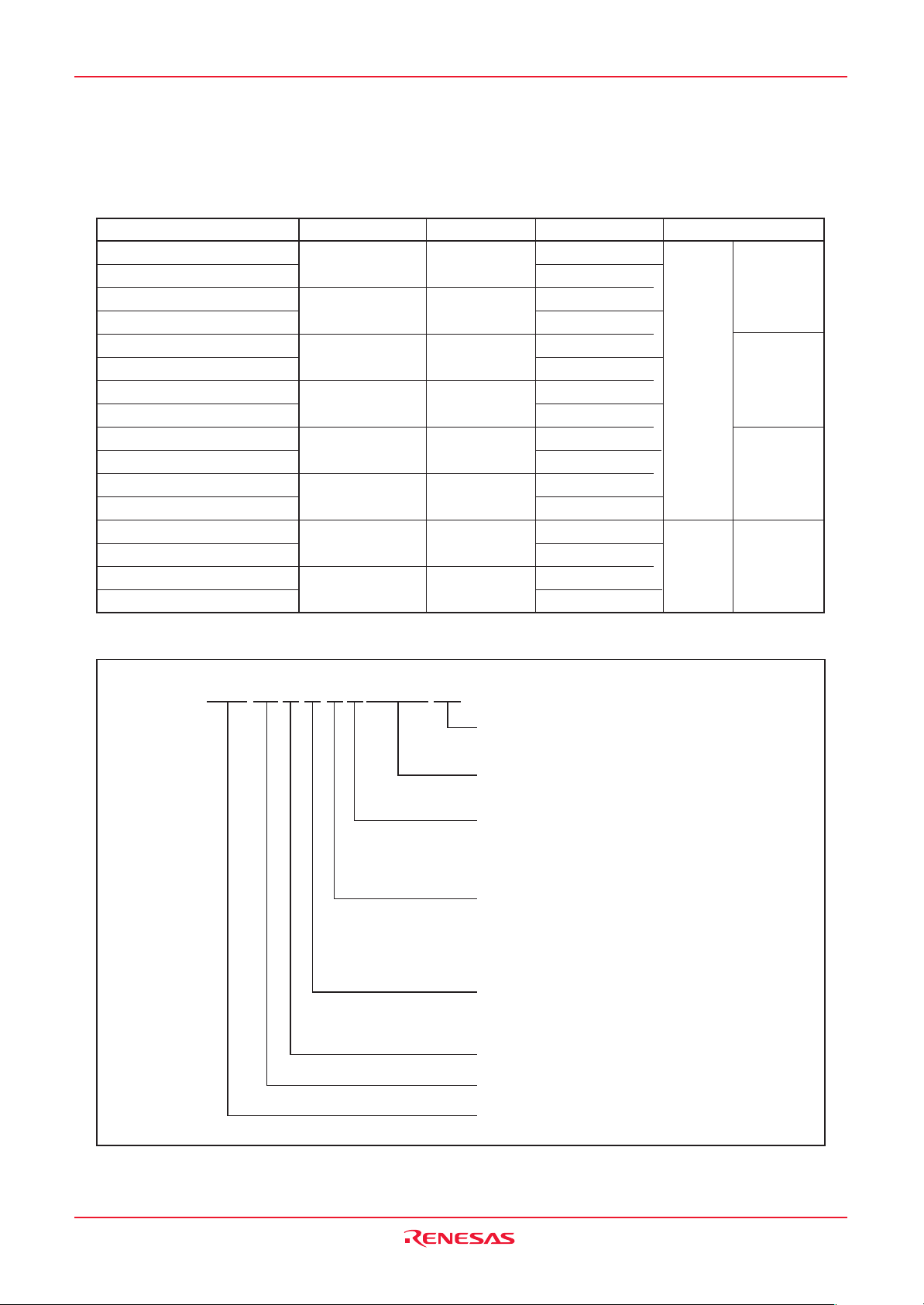

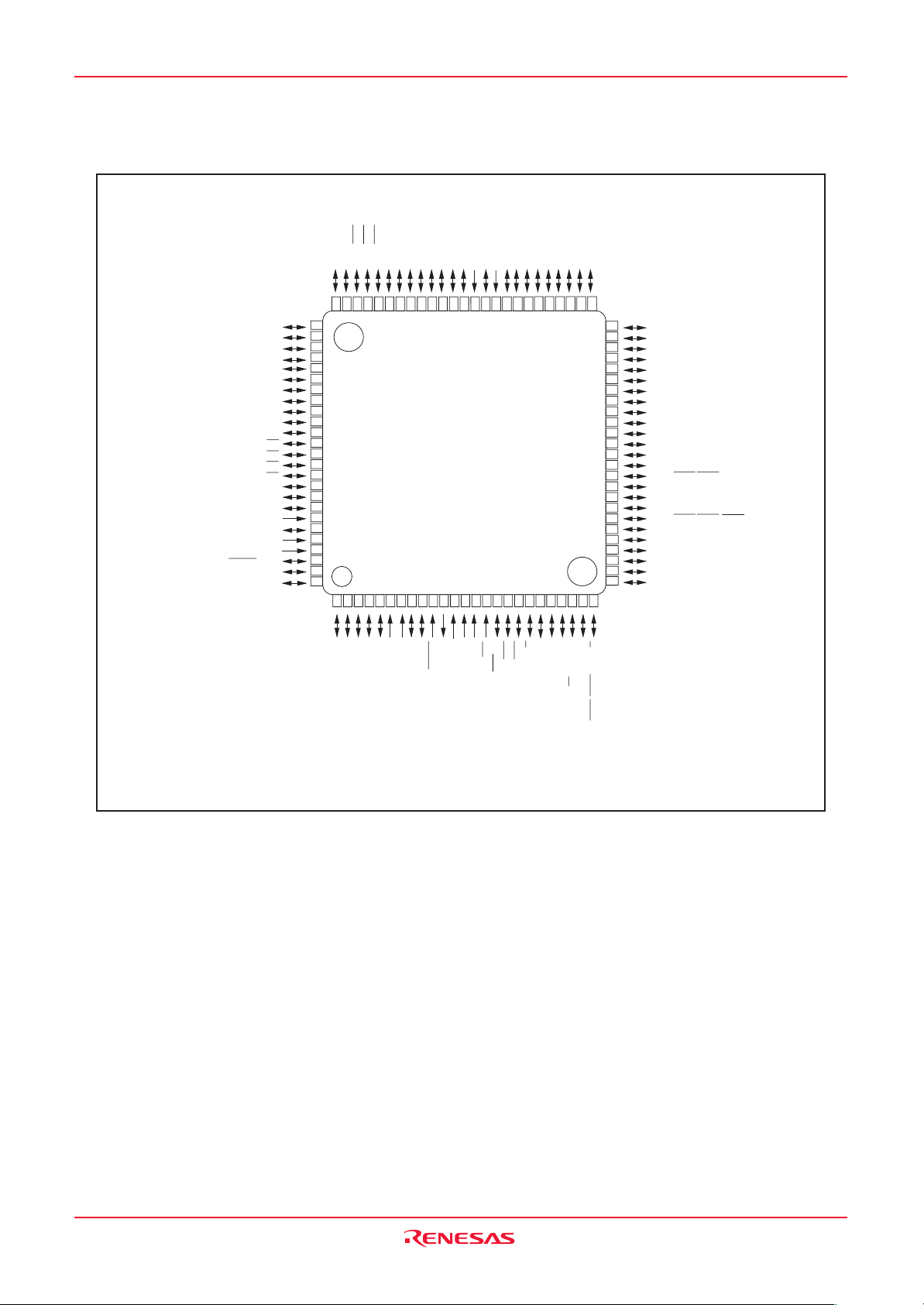

The M16C/6N Group (M16C/6NK, M16C/6NM) of single-chip microcomputers are built using the

high-performance silicon gate CMOS process using an M16C/60 Series CPU core and are packaged in

100-pin and 128-pin plastic molded LQFP. These single-chip microcomputers operate using sophisticated

instructions featuring a high level of instruction efficiency. With 1 Mbyte of address space, they are capable