Page 1

查询M38230G1-XXXFP供应商

3823 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

DESCRIPTION

The 3823 group is the 8-bit microcomputer based on the 740 family core technology.

The 3823 group has the LCD drive control circuit, an 8-channel A/

D converter, a serial interface, a watchdog timer, a ROM correction function, and as additional functions.

The various microcomputers in the 3823 group include variations

of internal memory size and packaging. For details, refer to the

section on part numbering.

FEATURES

●Basic machine-language instructions ...................................... 71

●The minimum instruction execution time ........................... 0.4 µs

(at f(XIN) = 10 MHz, High-speed mode)

●Memory size

ROM ............................................................... 16 K to 60 K bytes

RAM.................................................................640 to 2560 bytes

●ROM correction function .............................. 32 bytes ✕ 2 blocks

●Watchdog timer .............................................................. 8-bit ✕ 1

●Programmable input/output ports ............................................ 49

●Input ports .................................................................................. 5

●

Software pull-up/pull-down resistors (Ports P0-P7 except port P40)

●Interrupts ................................................. 17 sources, 16 vectors

(includes key input interrupt)

●Key Input Interrupt (Key-on Wake-Up) ...................................... 8

●Timers........................................................... 8-bit ✕ 3, 16-bit ✕ 2

●Serial interface ............ 8-bit ✕ 1 (UART or Clock-synchronized)

●A/D converter ............ 10-bit ✕ 8 channels or 8-bit ✕ 8 channels

REJ03B0146-0202

Rev.2.02

Jun.19.2007

●LCD drive control circuit

Bias...................................................................................1/2, 1/3

Duty ...........................................................................1/2, 1/3, 1/4

Common output.......................................................................... 4

Segment output ........................................................................ 32

●Main clock generating circuits.............. Built-in feedback resistor

(connect to external ceramic resonator or quartz-crystal oscillator)

●Sub-clock generating circuits

(connect to external quartz-crystal oscillator or on-chip oscillator)

●Power source voltage

In frequency/2 mode (f(XIN) ≤ 10 MHz) ................... 4.5 to 5.5 V

In frequency/2 mode (f(XIN) ≤ 8 MHz) ..................... 4.0 to 5.5 V

In frequency/4 mode (f(XIN) ≤ 10 MHz) ................... 2.5 to 5.5 V

In frequency/4 mode (f(XIN) ≤ 8 MHz) ..................... 2.0 to 5.5 V

In frequency/4 mode (f(XIN) ≤ 5 MHz) ..................... 1.8 to 5.5 V

In frequency/8 mode (f(XIN) ≤ 10 MHz) ................... 2.5 to 5.5 V

In frequency/8 mode (f(XIN) ≤ 8 MHz) ..................... 2.0 to 5.5 V

In frequency/8 mode (f(XIN) ≤ 5 MHz) ..................... 1.8 to 5.5 V

In low-speed mode .................................................... 1.8 to 5.5 V

●Power dissipation

In frequency/2 mode ............................................... 18 mW (std.)

(at f(XIN) = 8 MHz, Vcc = 5 V, Ta = 25 °C)

In low-speed mode at XCIN ................................................ 18 µW (std.)

(at f(XIN) stopped, f(XCIN) = 32 kHz, Vcc = 2.5 V, Ta = 25 °C)

In low-speed mode at on-chip oscillator .................. 35 µW (std.)

(at f(XIN) stopped, f(XCIN) = stopped, Vcc = 2.5 V, Ta = 25 °C)

●Operating temperature range..................................– 20 to 85 °C

APPLICATIONS

Camera, audio equipment, household appliances, consumer electronics, etc.

Rev.2.02 Jun 19, 2007 page 1 of 73

REJ03B0146-0202

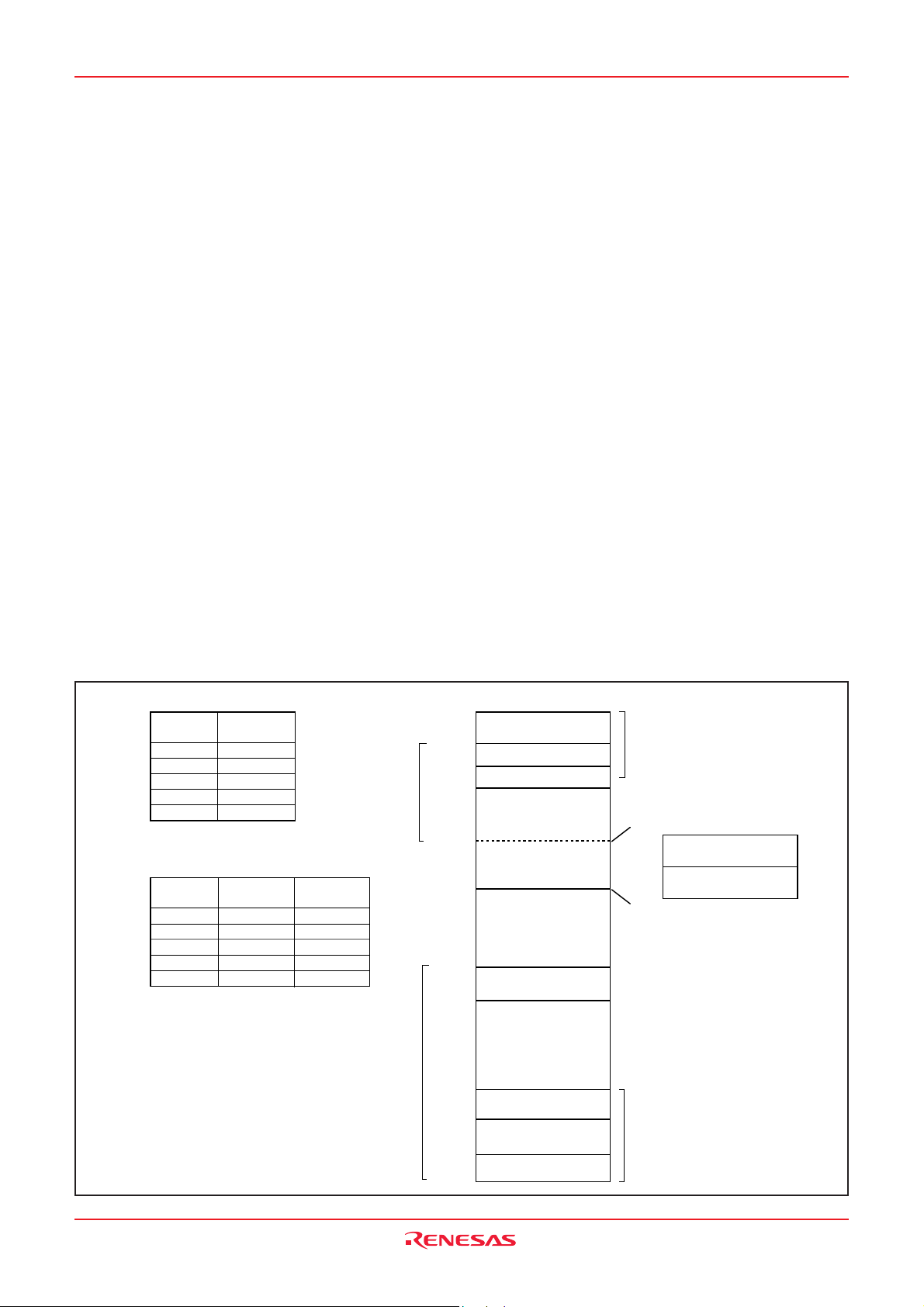

Page 2

3823 Group

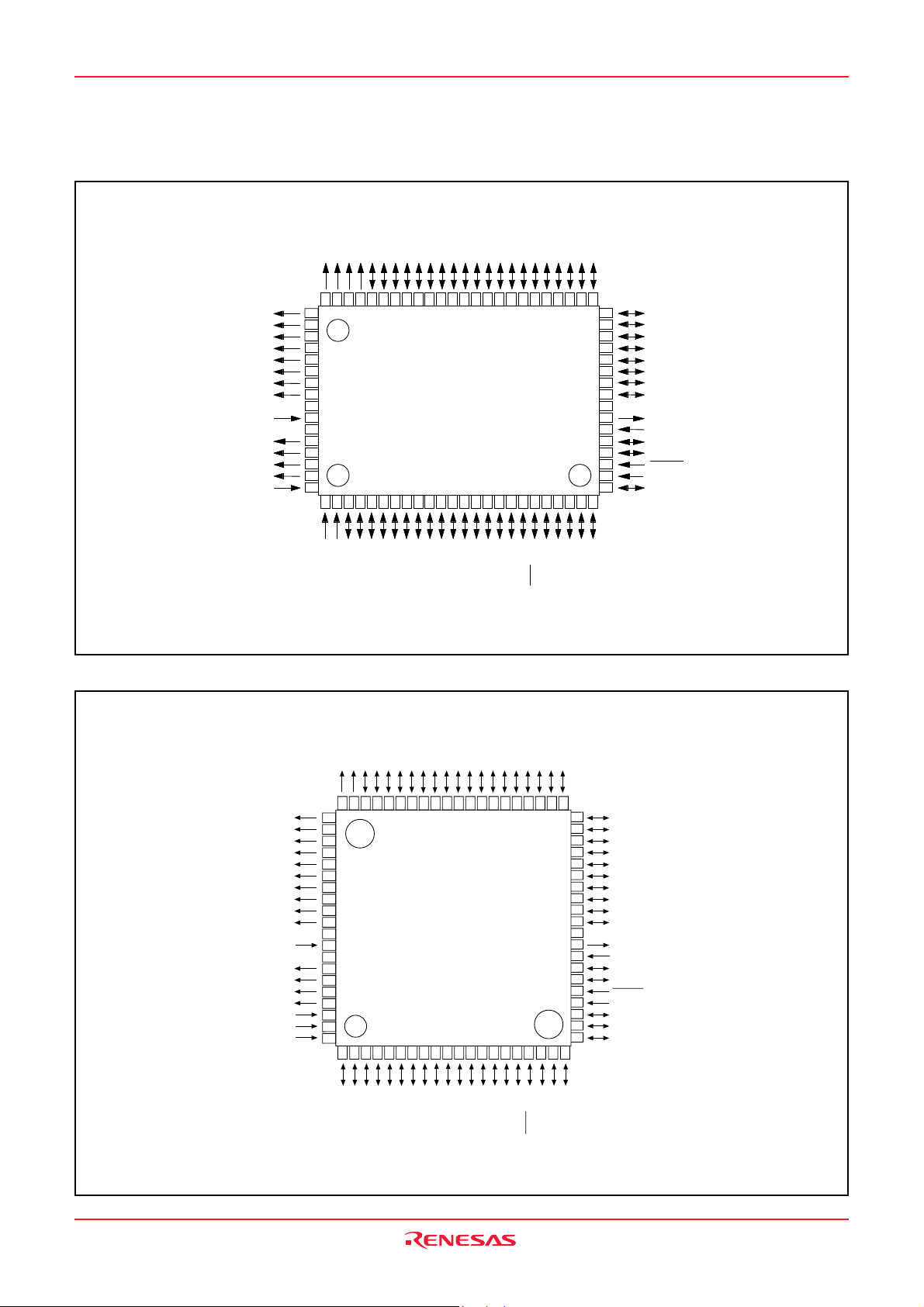

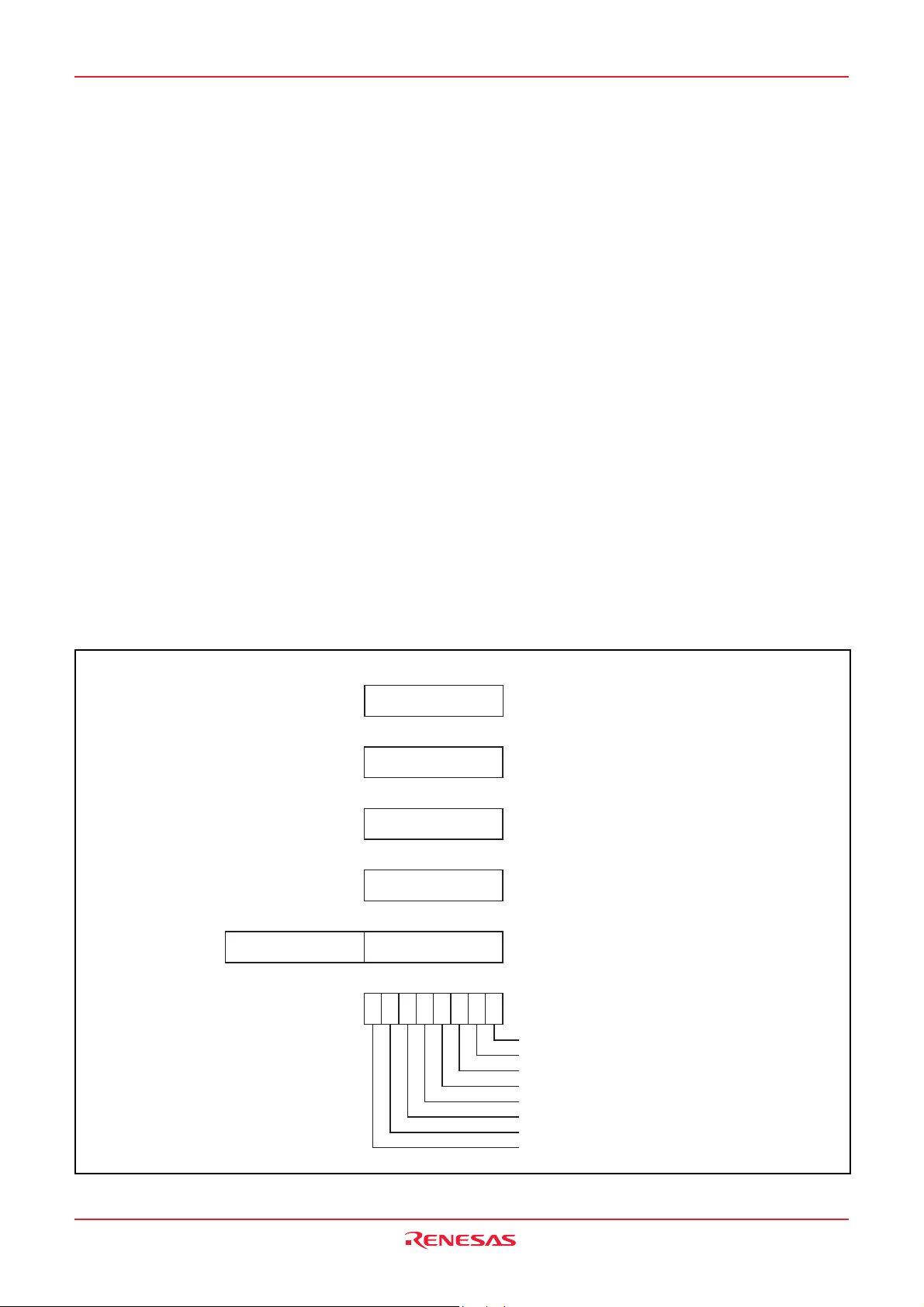

PIN CONFIGURATION (TOP VIEW)

8

9

G

G

S

E

S

E

E

S E G

7

6 5

S E G

S E G

S E G

S E G

S E G

SEG

S E G

V

A

C O M

C O M

C O M

C O M

V

C C

R E F

S

V

V L

6 6

6

5

6 7

4

6 8

6 9

3

7 0

2

1

7 1

7 2

0

7 3

7 4

7 5

S

3

7 6

2

7 7

1

7 8

0

7 9

8 0

3

1 234567891 01 112 1 314151 6171 819202 122 2 32 4

1

7

2

L

L

N

V

V

/

7

6

P

A

Package code : PRQP0080GB-A (80P6N-A) (80-pin plastic-molded QFP)

2

3

6

4

5

1

1

1

1

1

G

G

G

G

0

1

G

S

E

G

1

1

/

/

/

/

/

G

4

5

0

6

7

3

3

3

3

S E

S

0

S E

S E

S E

S E

S E

P

P

P

P

P

1

9

0

7

8

2

1

2

1

1

G

G

G

G

G

/

/

/

/

/

3

4

5

1

2

0

0

0

0

0

S E

S E

S E

S E

P

P

P

P

P

M 3 8 2 3 X G X - X X X F P

M 3 8 2 3 X G X F P

1

6

5

4

3

2

N

/

6

6

P

A

A

1

N

N

N

N

N

/

/

/

/

/

5

4

3

2

1

6

6

6

6

6

P

P

P

P

P

A

A

A

A

A

0

0

T

T

N

R

R

O

/

T

/

/

0

7

6

6

5

5

/

/

P

5

4

P

A D

P

U

R T

5

5

P

P

C N T

C N T

2

3

2

2

G

G

/

/

6

7

0

0

S E

S E

S E

P

P

3

1

0

T

P

P

/

/

/

1

3

2

5

5

5

P

I N

P

P

R T

8

5

6

7

9

0

4

2

2

2

G

G

G

/

/

/

1

2

0

1

1

1

S E

S E

S E

P

P

P

2

T

K

T

C

O

S

S

/

/

/

0

6

Y

5

4

P

I N

P

L

R

S

/

7

4

P

U

D

1

2

2

2

3

3

G

G

G

G

G

/

/

/

/

/

3

4

5

6

7

1

1

1

1

1

S E

S E

S E

S E

P

P

P

P

P

414243444546474849505152535455565758596061626364

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

0

1

D

D

T

T

X

X

T

R

/

/

/

/

5

4

3

2

4

4

4

4

P

P

P

P

I N

I N

P 20/ K W

P21/KW

P22/KW

P23/KW

P24/KW

P25/KW

P26/KW

P27/KW

V

SS

X

OUT

X

IN

P 70/ X

P 71/ X

R E S E T

P4

0

P41/φ

C O U T

C I N

0

1

2

3

4

5

6

7

Fig. 1 M3823XGX-XXXFP pin configuration

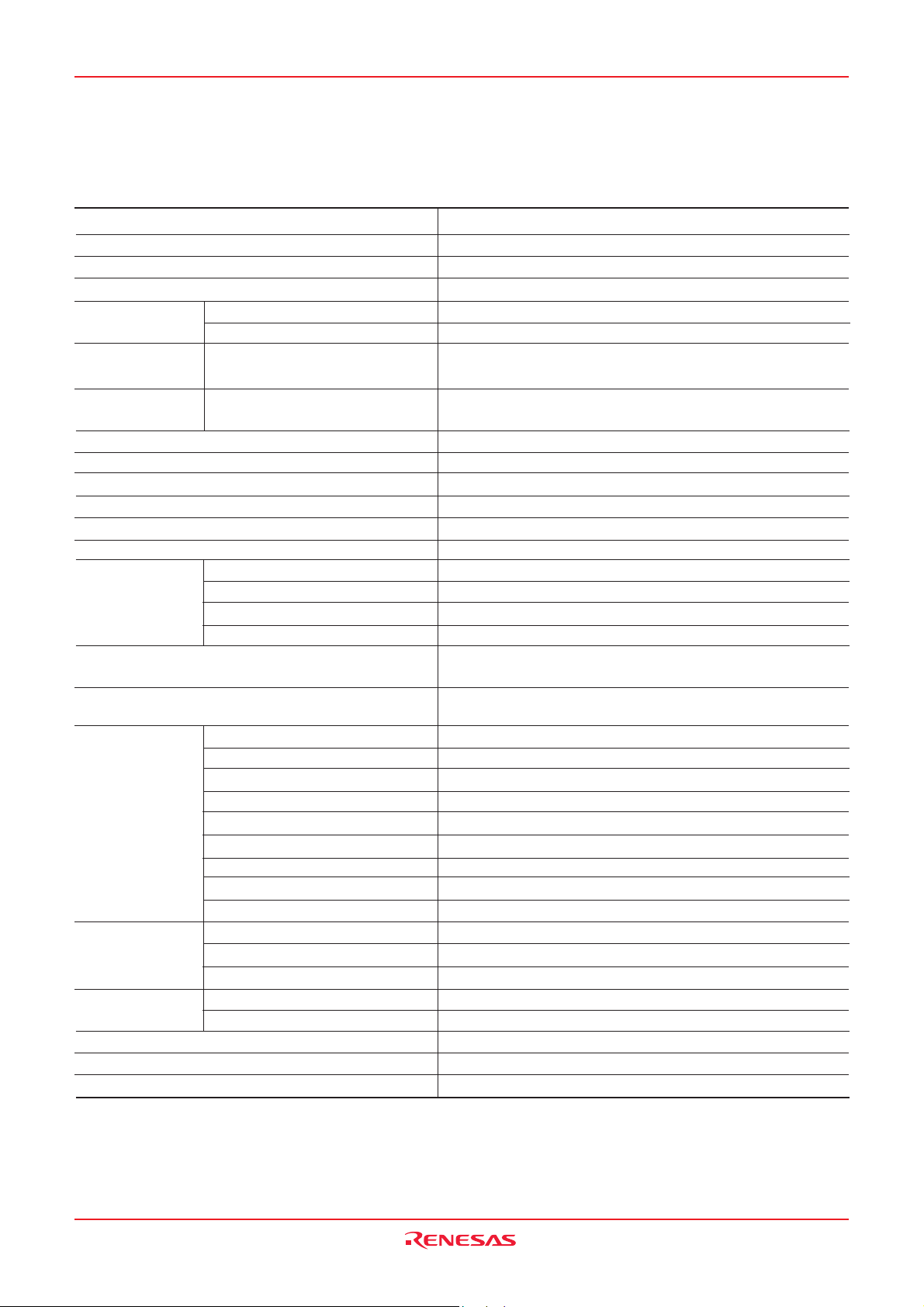

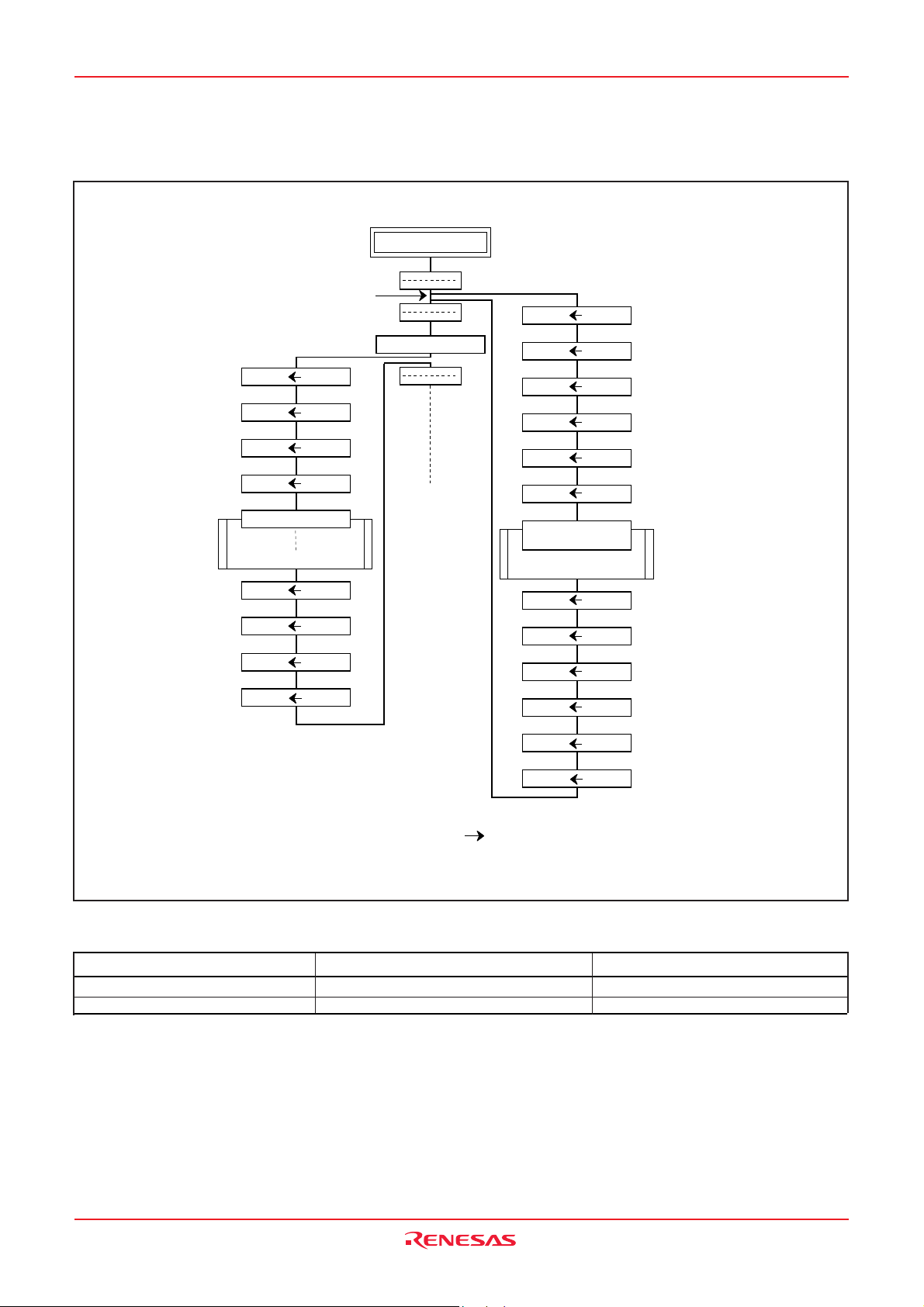

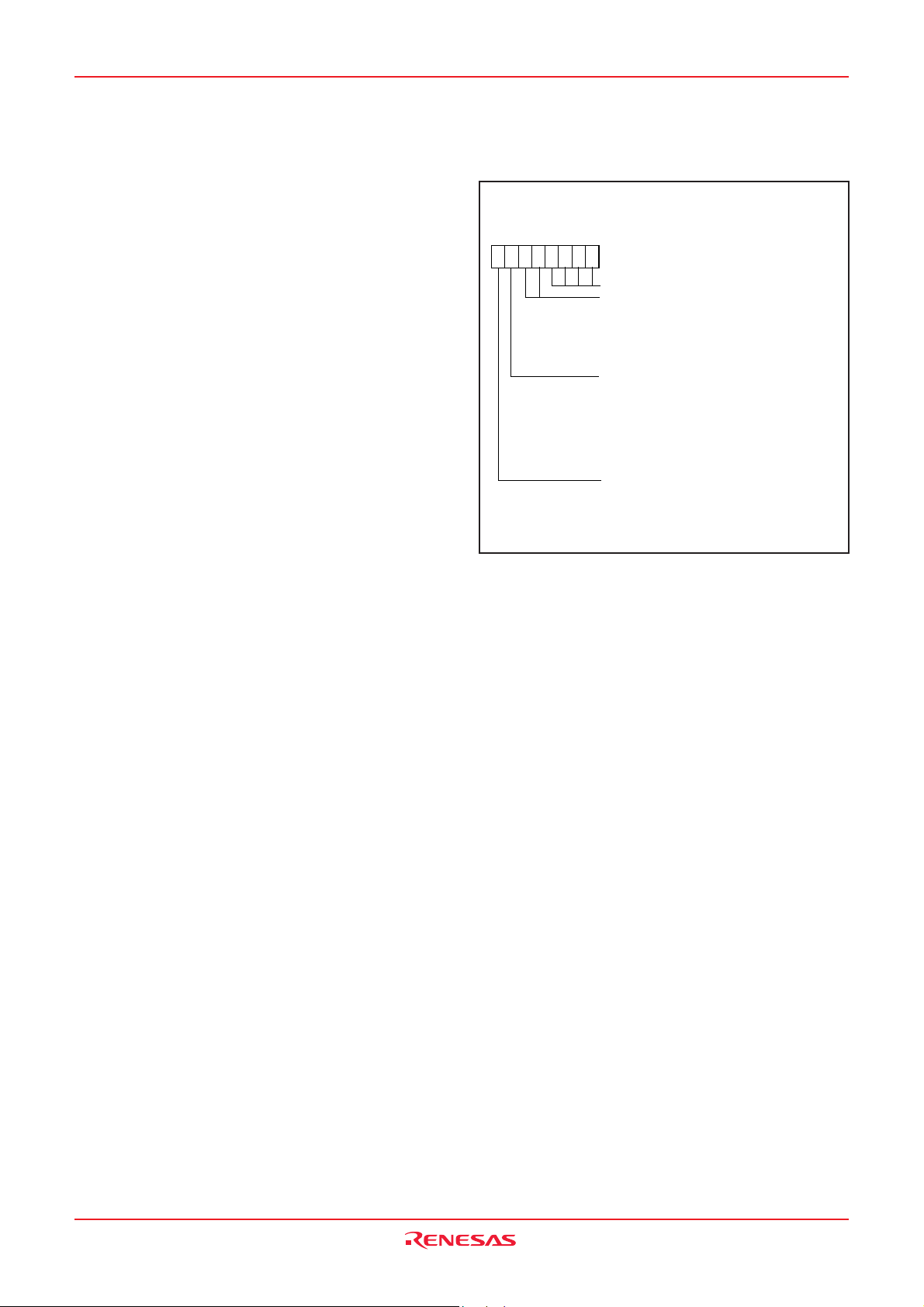

PIN CONFIGURATION (TOP VIEW)

SEG

SEG

SEG

SEG

SEG

SEG

SEG

SEG

SEG

SEG

V

AV

COM

COM

COM

COM

V

REF

V

V

V

61

9

62

8

63

7

64

6

65

5

66

4

67

3

68

2

1

69

70

0

CC

71

72

SS

73

3

74

2

75

1

76

0

77

L3

78

L2

79

L1

80

Package code : PLQP0080KB-A (80P6Q-A) (80-pin plastic-molded LQFP)

16

15

14

13

10

SEG

60

11

SEG

59

12

/SEG

4

P3

58

/SEG

5

P3

57

/SEG

6

P3

56

/SEG

7

P3

55

/SEG

0

P0

54

17

/SEG

1

P0

53

18

/SEG

2

P0

52

19

/SEG

3

P0

51

20

/SEG

4

P0

50

M3823XGX-XXXHP

M3823XGXHP

2

5

3

/AN

3

P6

6

2

/AN

2

P6

7

1

/AN

1

P6

8

0

/AN

0

P6

9

/ADT

7

P5

10

OUT

/T

6

P5

11

1

/CNTR

5

P5

1

7

/AN

7

P6

6

/AN

6

P6

3

5

/AN

5

P6

4

4

/AN

4

P6

22

21

/SEG

/SEG

6

5

P0

P0

49

48

13

12

0

/CNTR

4

P5

1

/RTP

3

P5

23

/SEG

7

P0

47

14

0

/RTP

2

P5

24

/SEG

0

P1

46

15

3

/INT

1

P5

25

/SEG

1

P1

45

16

2

/INT

0

P5

26

/SEG

2

P1

44

17

OUT

/S

RDY

/S

7

P4

27

/SEG

3

P1

43

18

CLK

/S

6

P4

28

/SEG

4

P1

42

19

D

X

/T

5

P4

29

/SEG

5

P1

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

D

X

/R

4

P4

P16/SEG

P17/SEG

P20/KW

P21/KW

P22/KW

P23/KW

P24/KW

P25/KW

P26/KW

P27/KW

V

SS

X

OUT

X

IN

P70/X

COUT

P71/X

CIN

RESET

P4

0

P41/φ

P42/INT

P43/INT

30

31

0

1

2

3

4

5

6

7

0

1

Fig. 2 M3823XGX-XXXHP pin configuration

Rev.2.02 Jun 19, 2007 page 2 of 73

REJ03B0146-0202

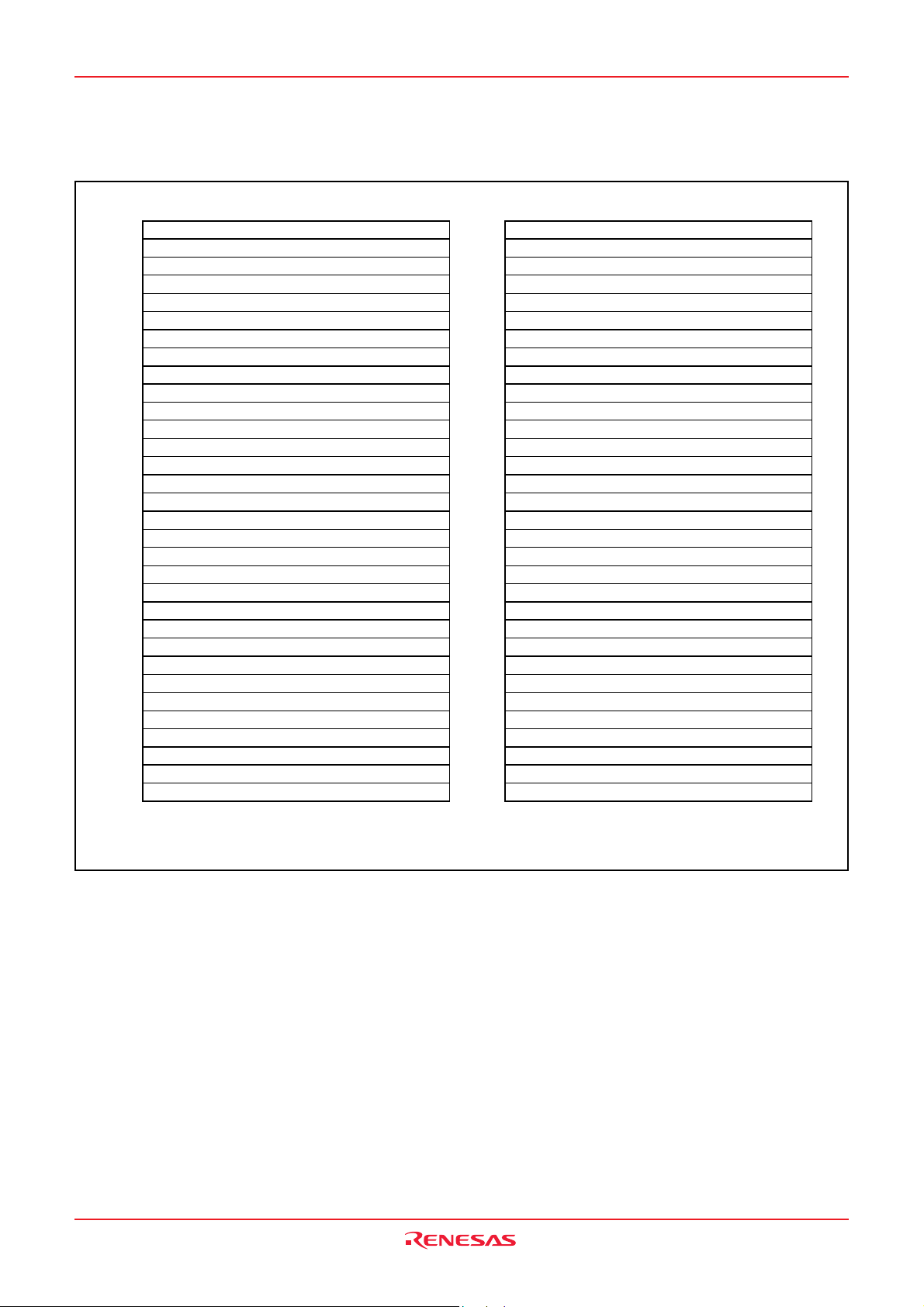

Page 3

3823 Group

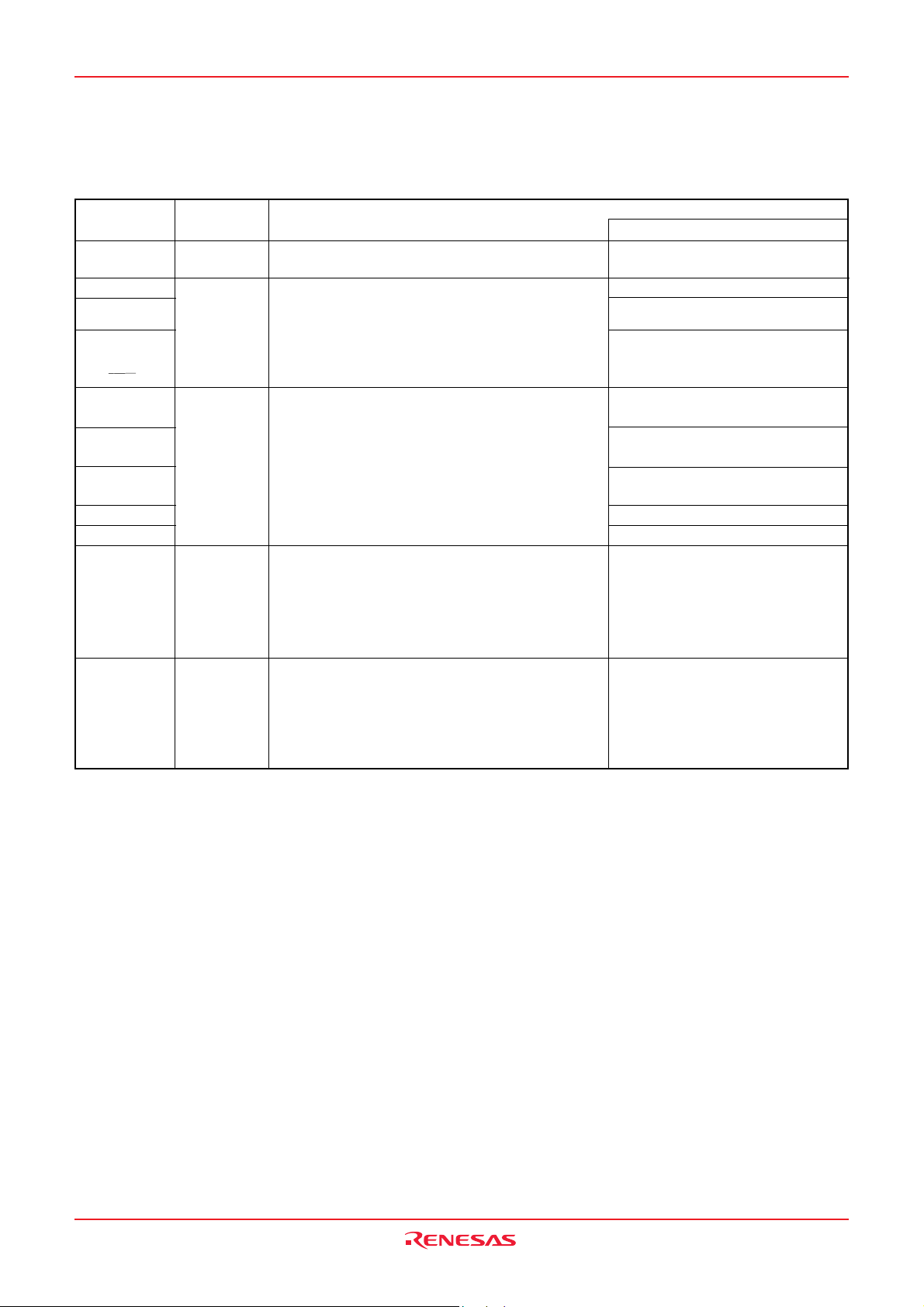

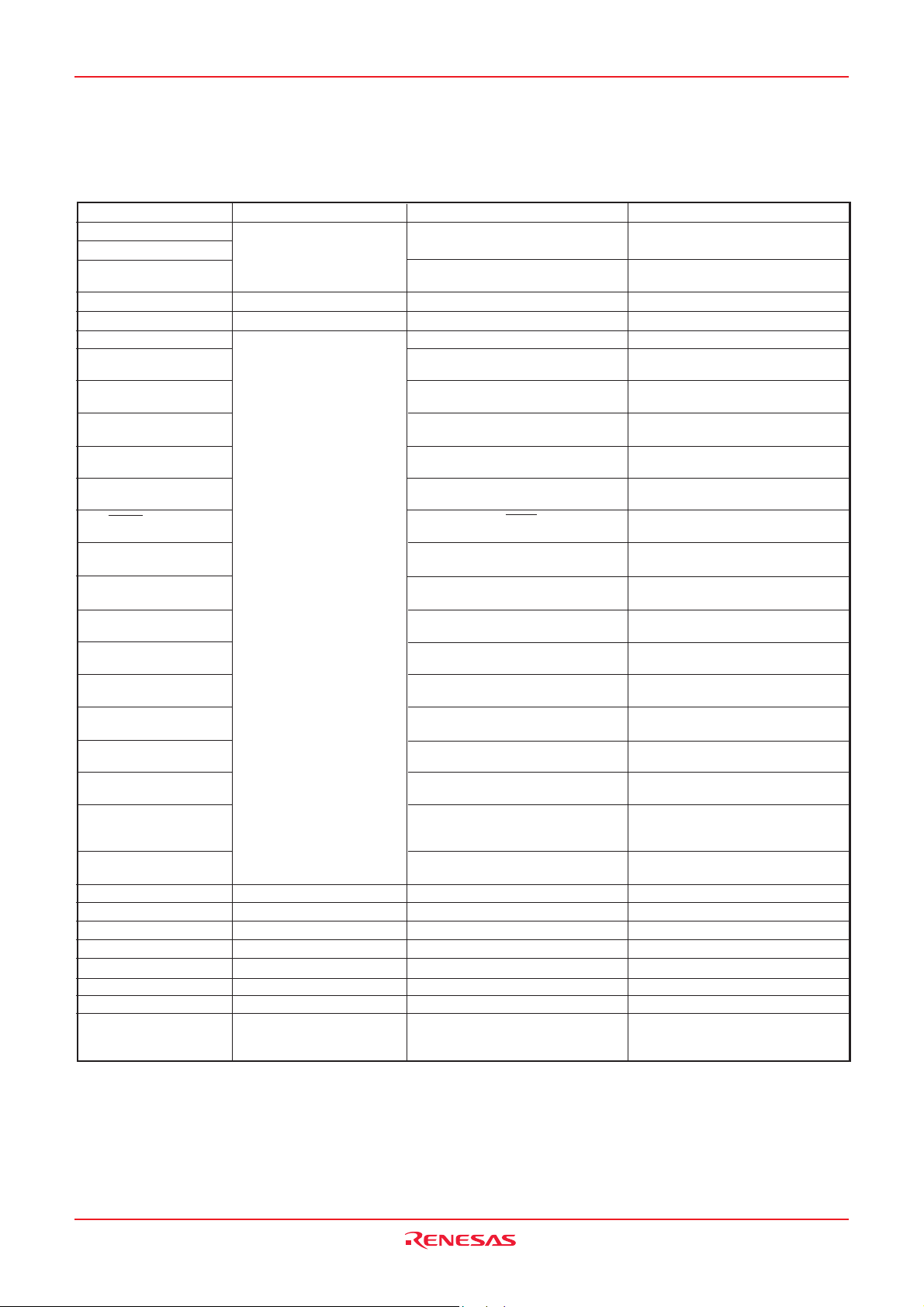

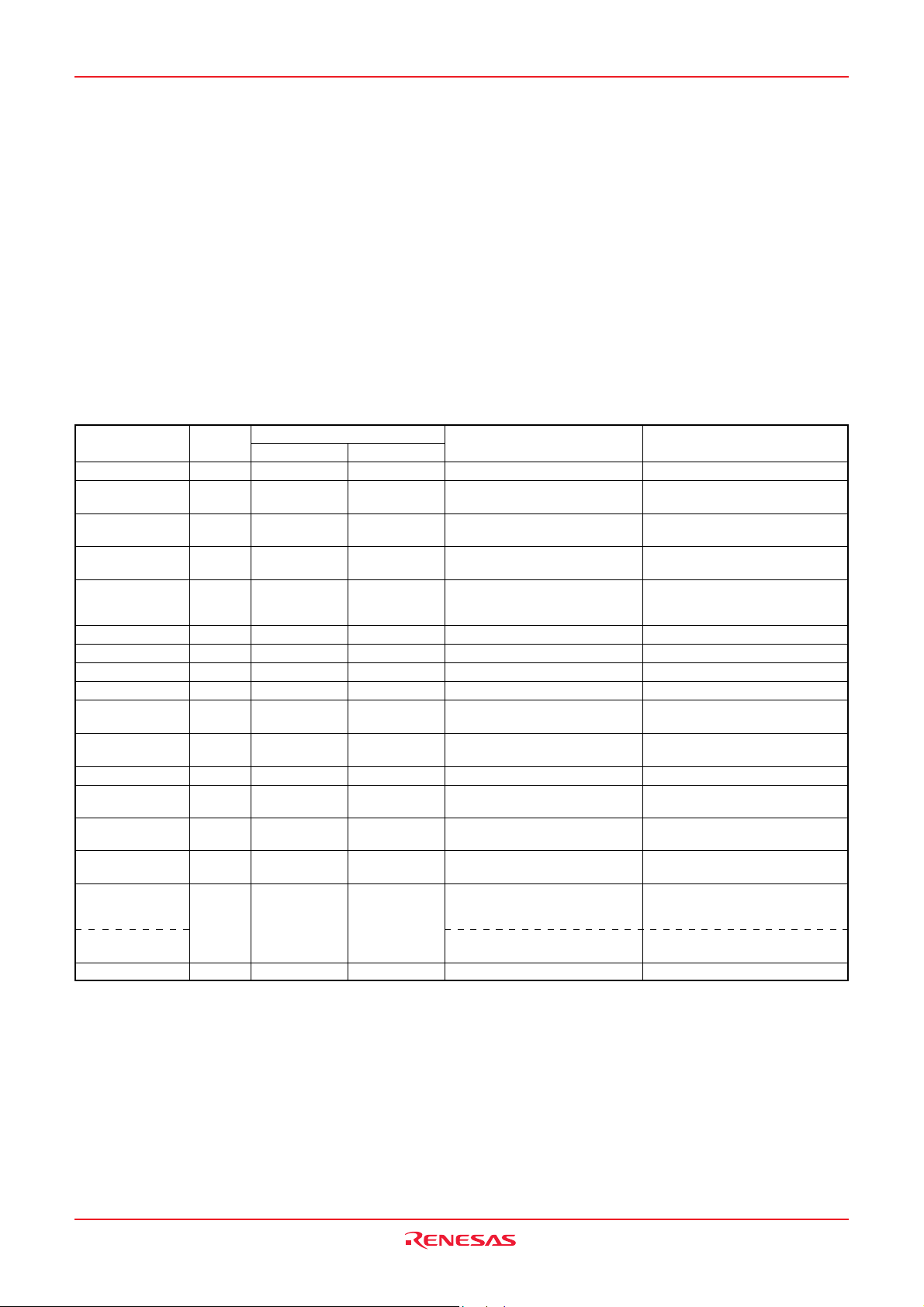

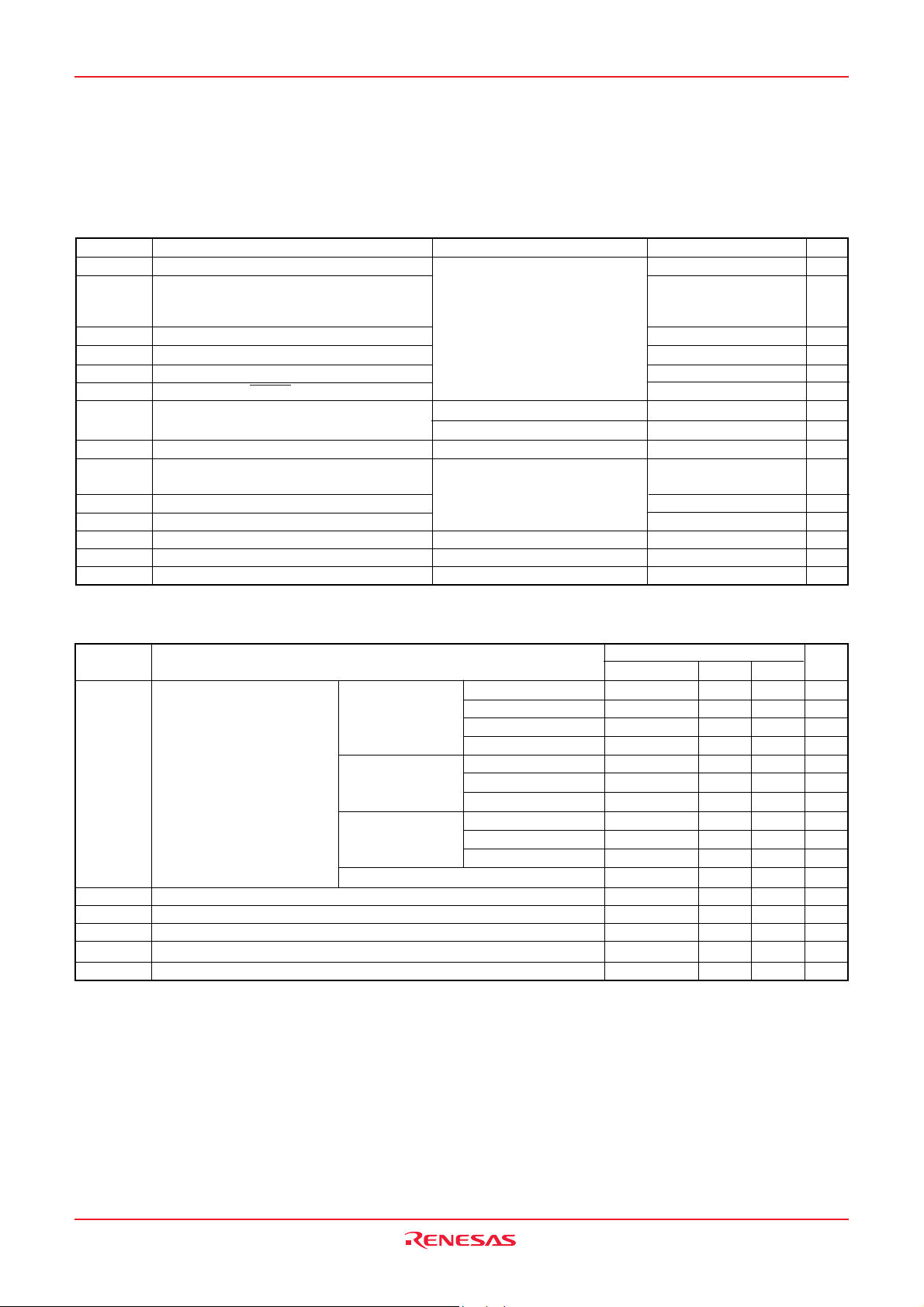

Table 1 Performance overview

Parameter

Number of basic instructions

Instruction execution time

Oscillation frequency

Memory sizes ROM

RAM

Input port P34-P37, P40

I/O port P0-P2, P41-P47, P5, P6, P70, P71

Interrupt

Timer

Serial interface

A/D converter

Watchdog timer

ROM correction function

LCD drive control Bias

circuit

Main clock generating circuits

Sub-clock generating circuits

Power source voltage In frequency/2 mode (f(XIN) ≤ 10MHz)

Power dissipation In frequency/2 mode

Input/Output Input/Output withstand voltage

characteristics

Operating temperature range

Device structure

Package

Duty

Common output

Segment output

In frequency/2 mode (f(XIN) ≤ 8MHz)

In frequency/4 mode (f(XIN) ≤ 10MHz)

In frequency/4 mode (f(XIN) ≤ 8MHz)

In frequency/4 mode (f(XIN) ≤ 5MHz)

In frequency/8 mode (f(XIN) ≤ 10MHz)

In frequency/8 mode (f(XIN) ≤ 8MHz)

In frequency/8 mode (f(XIN) ≤ 5MHz)

In low-speed mode

In low-speed mode at XCIN

In low-speed mode at on-chip oscillator

Output current

Function

71

0.4 µs (Minimum instruction, f(XIN) 10 MHz, High-speed mode)

10 MHz (Maximum)

16 K to 60 K bytes

640 to 2560 bytes

4-bit ✕ 1, 1-bit ✕ 1

(4 pins sharing SEG)

8-bit ✕ 5, 7-bit ✕ 1, 2 bit ✕ 1

(16 pins sharing SEG)

17 sources, 16 vectors (includes key input interrupt)

8-bit ✕ 3, 16-bit ✕ 2

8-bit ✕ 1 (UART or Clock-synchronized)

10-bit ✕ 8 channels or 8 bit ✕ 8 channels

8-bit ✕ 1

32 bytes ✕ 2 blocks

1/2, 1/3

2, 3, 4

4

32

Built-in feedback resistor

(connect to external ceramic rasonator or quartz-crystal oscillator)

Built-in feedback resistor

(connect to external quartz-crystal oscillator or on-chip oscillator)

4.5 to 5.5V

4.0 to 5.5V

2.5 to 5.5V

2.0 to 5.5V

1.8 to 5.5V

2.5 to 5.5V

2.0 to 5.5V

1.8 to 5.5V

1.8 to 5.5V

Std. 18 mW (Vcc = 5V, f(XIN) = 8MHz, Ta = 25 °C)

Std. 18 µW (Vcc = 2.5V, f(XIN) = stopped, f(XCIN) = 32kHz, Ta = 25 °C)

Std. 35 µW (Vcc = 2.5V, f(XIN) = stopped, f(XCIN) = stopped, Ta = 25 °C)

VCC

10mA

-20 to 85 °C

CMOS sillicon gate

80-pin plastic molded LQFP/QFP

Rev.2.02 Jun 19, 2007 page 3 of 73

REJ03B0146-0202

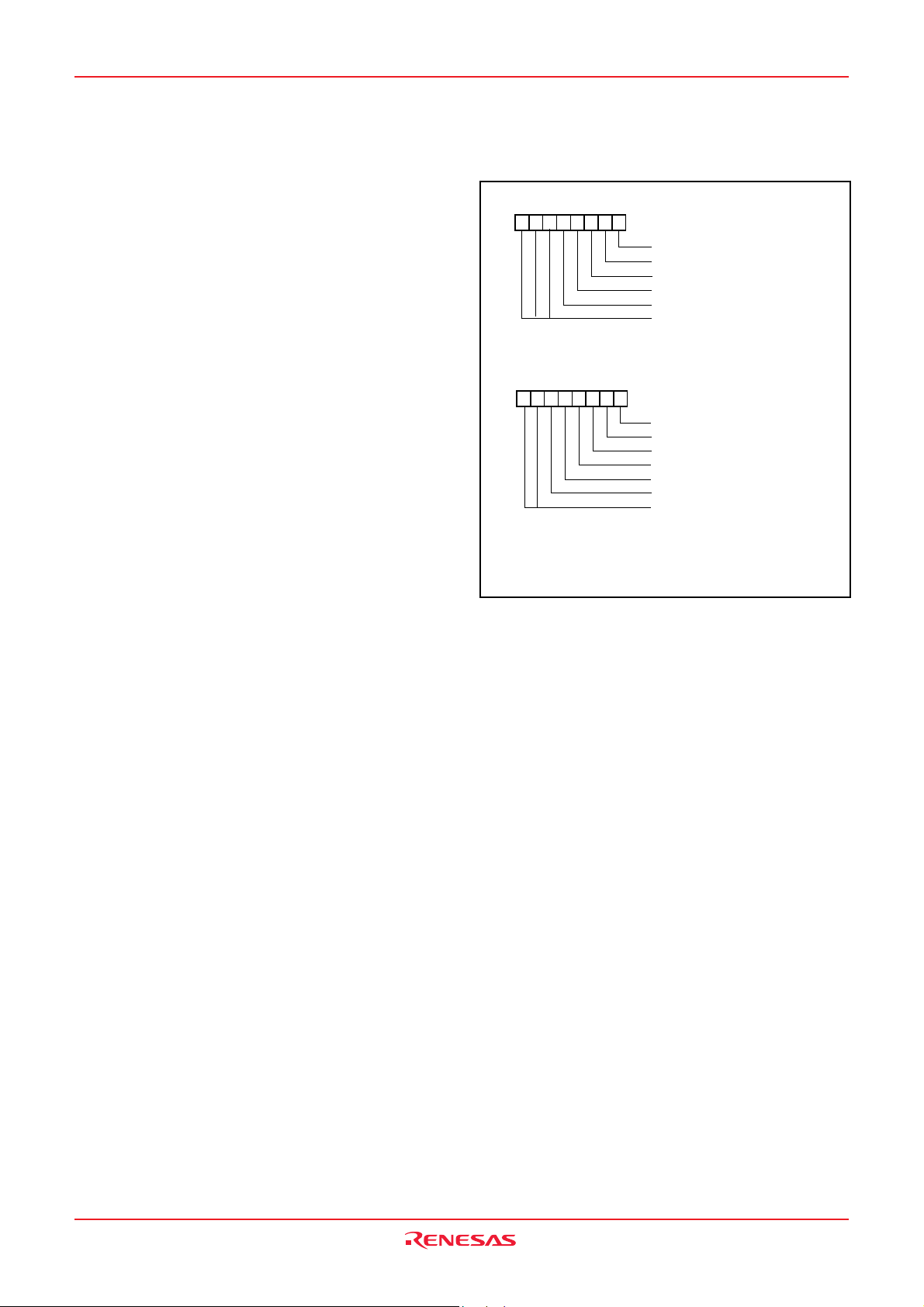

Page 4

3823 Group

K

e y o n w a k e u

p

R

e a l t i m e p o r t f u n c t i o

n

I

N

T

2

,

I N

T

3

C

N T

R

0

,

C N T

R

1

O

U

T

A

D

T

I

N

T0,

I N

T

1

φ

,

X

C

I

N

R

T

P

0

,

R T

P

1

D

a t a b u

s

C

P

U

A

X

Y

S

C

H

C

L

P

S

E

S

E

T

V

C

C

V

S

S

R

e s e t I n p u

t

5

V

)

(

0 V

)

O

M

R

A

M

L

C D d i s p l a y

R

A M

(

1 6 b y t e s

)

2

5

7

1

3

0

/

O

P

o

r

t

P

5

P

4 ( 8

)

/

O

P

o

r

t

P

4

I

/ O P o r t P

2

2

(

8

)

I

/ O P o r t P

0

0

(

8

)

I

/ O P o r t P

1

1

(

8

)

P

6 ( 8

)

I

n p u t P o r t P

3

3

(

4

)

I

/ O P o r t P

6

P

5 ( 8

)

I

/ O P o r t P

7

7

(

2

)

8

0

7

9

8

7

6

5

7

4

7

0

6

9

6

8

7

6

5

4

3

2

6

1

6

0

5

9

4

7

4

8

4

9

5

0

5

1

5

2

3

5

4

3

9

0

1

4

2

4

3

4

4

4

5

4

6

3

1

3

2

3

3

4

3

5

3

6

7

8

5

5

6

5

7

8

9

2

0

2

1

2

2

3

2

4

1

7

1

8

2

6

2

7

1

2

4

5

7

7

3

2

1

0

1

1

1

2

1

3

1

4

1

5

6

C

l o c k g e n e r a t i n

g

c

i r c u i

t

M

a i n C l o c k n p u t

X

I

N

M

a i n C l o c k

O

u t p u t

X

O

U

T

X

C

O

U

T

u b - C l o c k u t p u

t

X

C

I

N

S

u b - C l o c k

I

n p u t

I

/

O

(

8

)

R

E

F

A

V

S

S

(

0

V

)

A

/ D c o n v e r t e

r

(

1

0

/

8

)

i

m

e

r

X

(

1

6

)

T

i m e r Y ( 1 6

)

i

m

e

r

1

(

8

)

T

i m e r 2 ( 8

)

T

i m e r 3 ( 8

)

C

D

r

i

v

e

c

o

n

t

r

o

l

i

r

c

u

i

t

V

L

1

V

L

2

V

L

3

C

O

M

0

C

O

M

1

C

O

M

2

C

O

M

3

E

G

0

E

G

1

E

G

2

E

G

3

E

G

4

S

E

G

5

S

E

G

6

S

E

G

7

S

E

G

8

S

E

G

9

S

E

G

1

0

S

E

G

1

1

φ

C

I

N

C

O

U

T

2

8

2

9

O

n - c h i

p

o

s c i l l a t o

r

R

O M o r r e c t i o n u n c t i o

n

W

a t c h d o

g

t

i m e

r

R

e s e

t

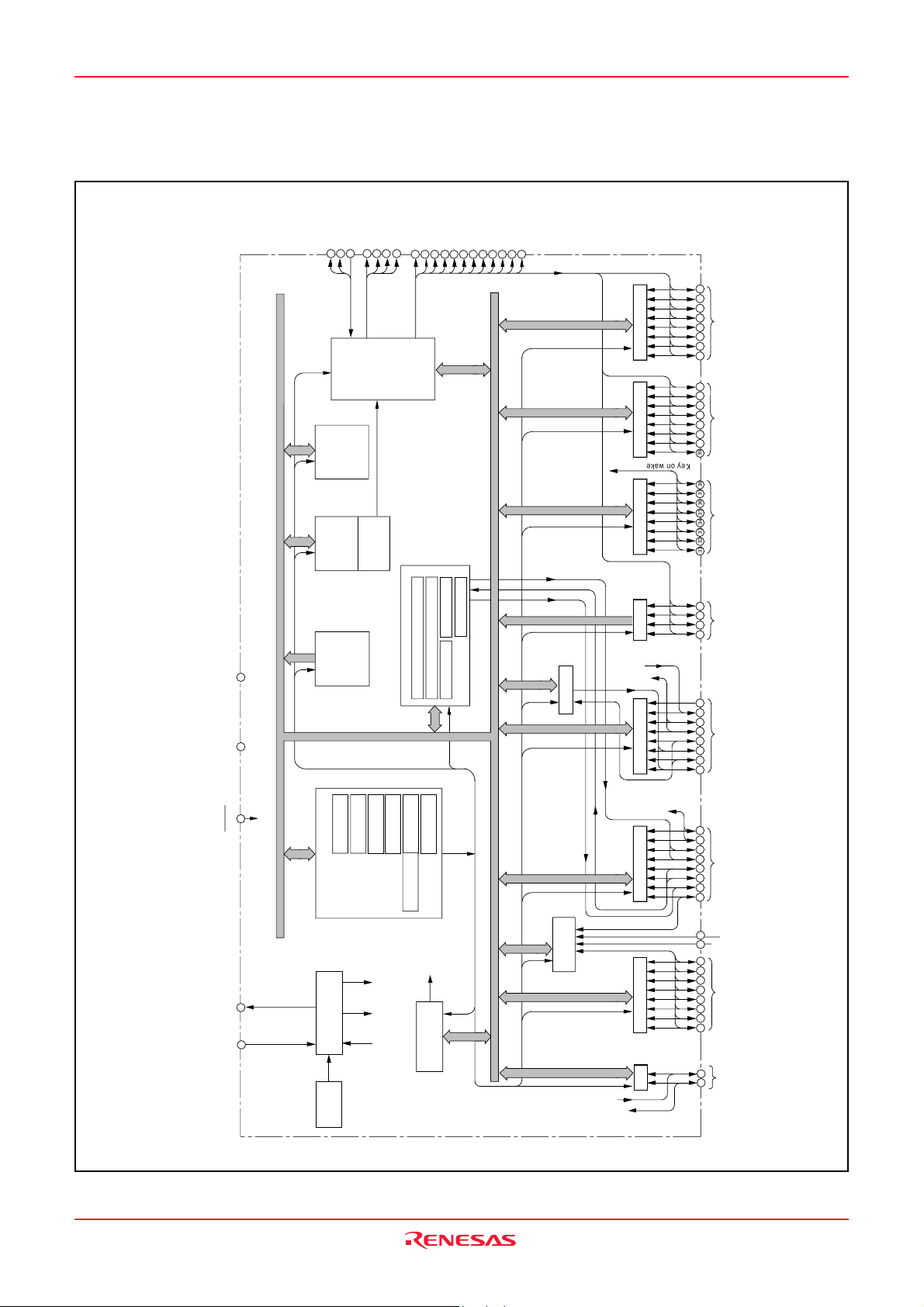

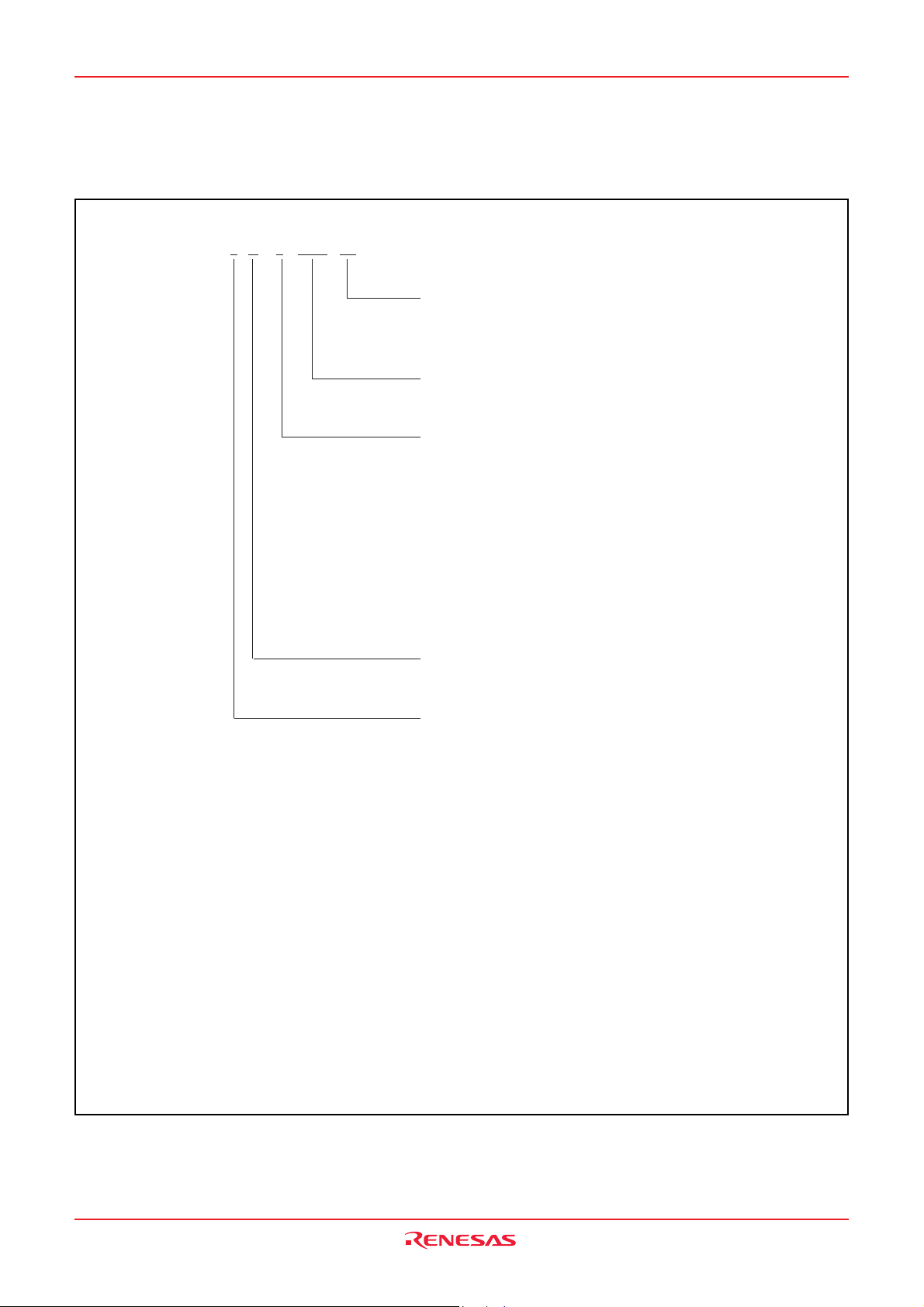

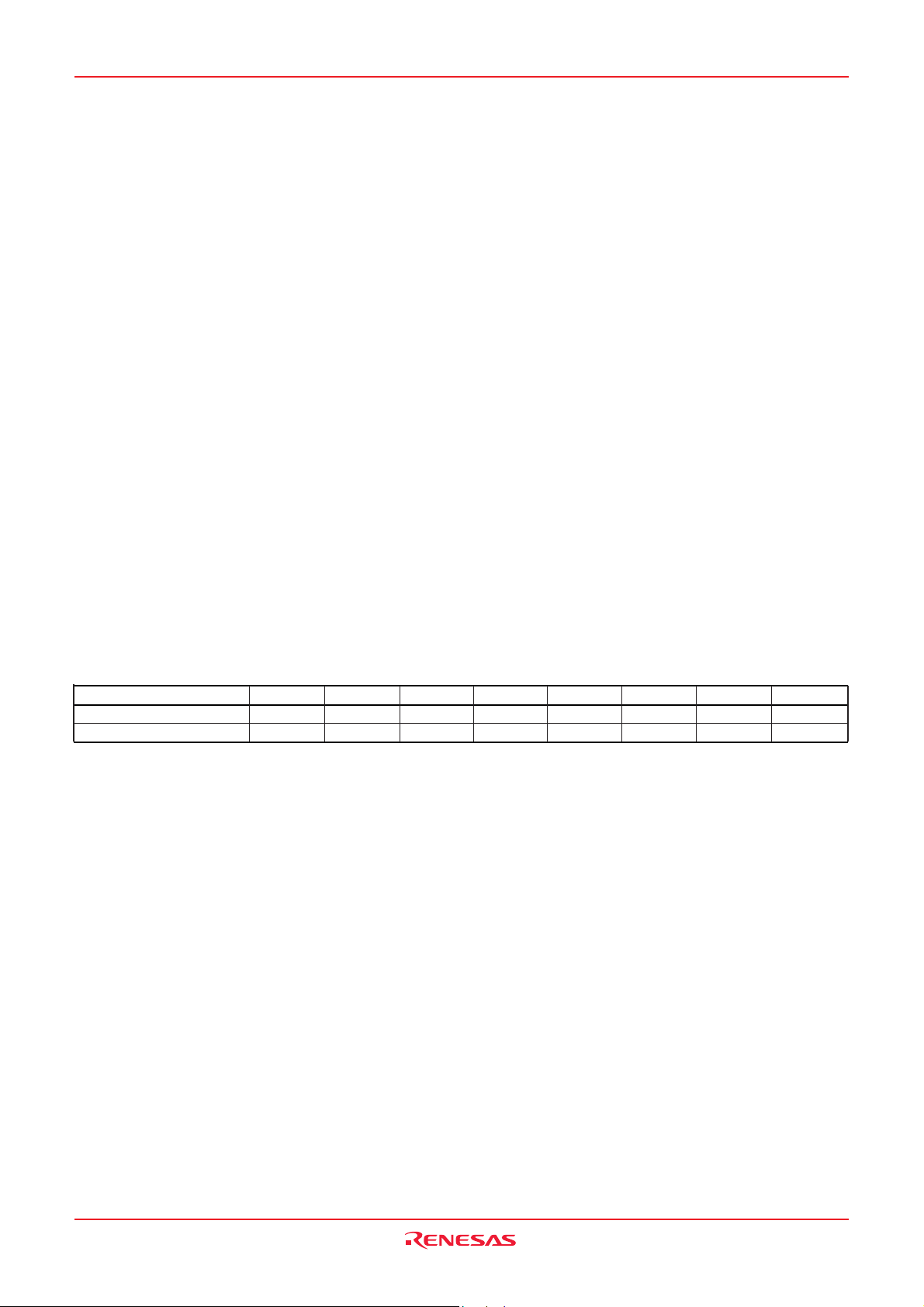

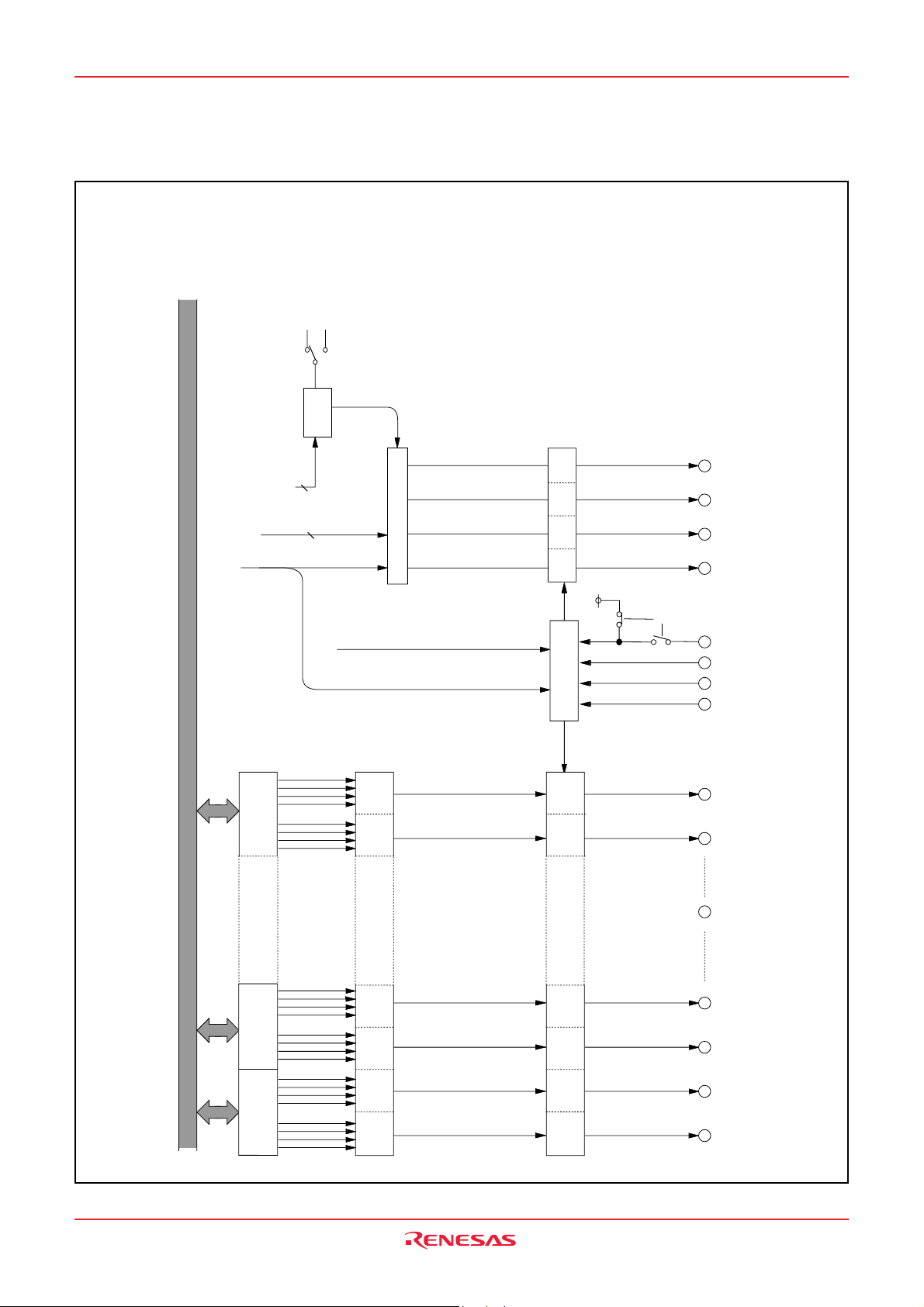

FUNCTIONAL BLOCK DIAGRAM (Package type : PLQP0080KB-A)

Fig. 3 Functional block diagram

Rev.2.02 Jun 19, 2007 page 4 of 73

REJ03B0146-0202

Page 5

3823 Group

PIN DESCRIPTION

Table 2 Pin description (1)

VCC, VSS

VREF

AVSS

RESET

XIN

XOUT

VL1–VL3

COM0–COM

SEG0–SEG

P00/SEG16–

P07/SEG23

P10/SEG24–

P17/SEG31

P20/KW0 –

P27/KW7

P34/SEG12 –

P37/SEG

15

FunctionPin Name

Power source •Apply voltage of power source to VCC, and 0 V to VSS. (For the limits of VCC, refer to “Recom-

Analog reference voltage

Analog power

source

Reset input

Clock input

Clock output

LCD power

source

Common output

3

11

Segment output

I/O port P0

I/O port P1

I/O port P2

Input port P3

mended operating conditions”).

•Reference voltage input pin for A/D converter.

•GND input pin for A/D converter.

•Connect to VSS.

•Reset input pin for active “L”.

•Input and output pins for the main clock generating circuit.

•Feedback resistor is built in between XIN pin and XOUT pin.

•Connect a ceramic resonator or a quartz-crystal oscillator between the XIN and XOUT pins to set

the oscillation frequency.

•If an external clock is used, connect the clock source to the XIN pin and leave the XOUT pin open.

•This clock is used as the oscillating source of system clock.

•Input 0 ≤ VL1 ≤ VL2 ≤ VL3 voltage.

•Input 0 – VL3 voltage to LCD.

•LCD common output pins.

•COM2 and COM3 are not used at 1/2 duty ratio.

•COM3 is not used at 1/3 duty ratio.

•LCD segment output pins.

•8-bit I/O port.

•CMOS compatible input level.

•CMOS 3-state output structure.

•I/O direction register allows each port to be individually

programmed as either input or output.

•Pull-down control is enabled.

•8-bit I/O port.

•CMOS compatible input level.

•CMOS 3-state output structure.

•I/O direction register allows each pin to be individually

programmed as either input or output.

•Pull-up control is enabled.

•4-bit input port.

•CMOS compatible input level.

•Pull-down control is enabled.

Function except a port function

•LCD segment output pins

•Key input (key-on wake-up) interrupt

input pins

•LCD segment output pins

Rev.2.02 Jun 19, 2007 page 5 of 73

REJ03B0146-0202

Page 6

3823 Group

Table 3 Pin description (2)

P40

P41/φ

P42/INT0,

P43/INT1

P44/RXD,

P45/TXD,

P46/SCLK,

P47/SRDY/SOUT

P50/INT2,

P51/INT3

P52/RTP0,

P53/RTP1

P54/CNTR0,

P55/CNTR1

P56/TOUT

P57/ADT

P60/AN0–

P67/AN7

P70/XCOUT,

P71/XCIN

Name

Input port P4

I/O port P4

I/O port P5

I/O port P6

I/O port P7

FunctionPin

•1-bit Input port.

•CMOS compatible input level.

•7-bit I/O port.

•CMOS compatible input level.

•CMOS 3-state output structure.

•I/O direction register allows each pin to be individually

programmed as either input or output.

•Pull-up control is enabled.

•8-bit I/O port.

•CMOS compatible input level.

•CMOS 3-state output structure.

•I/O direction register allows each pin to be individually

programmed as either input or output.

•Pull-up control is enabled.

•8-bit I/O port.

•CMOS compatible input level.

•CMOS 3-state output structure.

•I/O direction register allows each pin to be individually

programmed as either input or output.

•Pull-up control is enabled.

•2-bit I/O port.

•CMOS compatible input level.

•CMOS 3-state output structure.

•I/O direction register allows each pin to be individually

programmed as either input or output.

•Pull-up control is enabled.

Function except a port function

•QzROM program power pin

•φ clock output pin

•Interrupt input pins

•Serial interface function pins

•Interrupt input pins

•Real time port function pins

•Timer X, Y function pins

•Timer 2 output pins

•A/D trigger input pins

•A/D conversion input pins

•Sub-clock generating circuit I/O pins.

(Connect a resonator. External clock

cannot be used.)

Rev.2.02 Jun 19, 2007 page 6 of 73

REJ03B0146-0202

Page 7

3823 Group

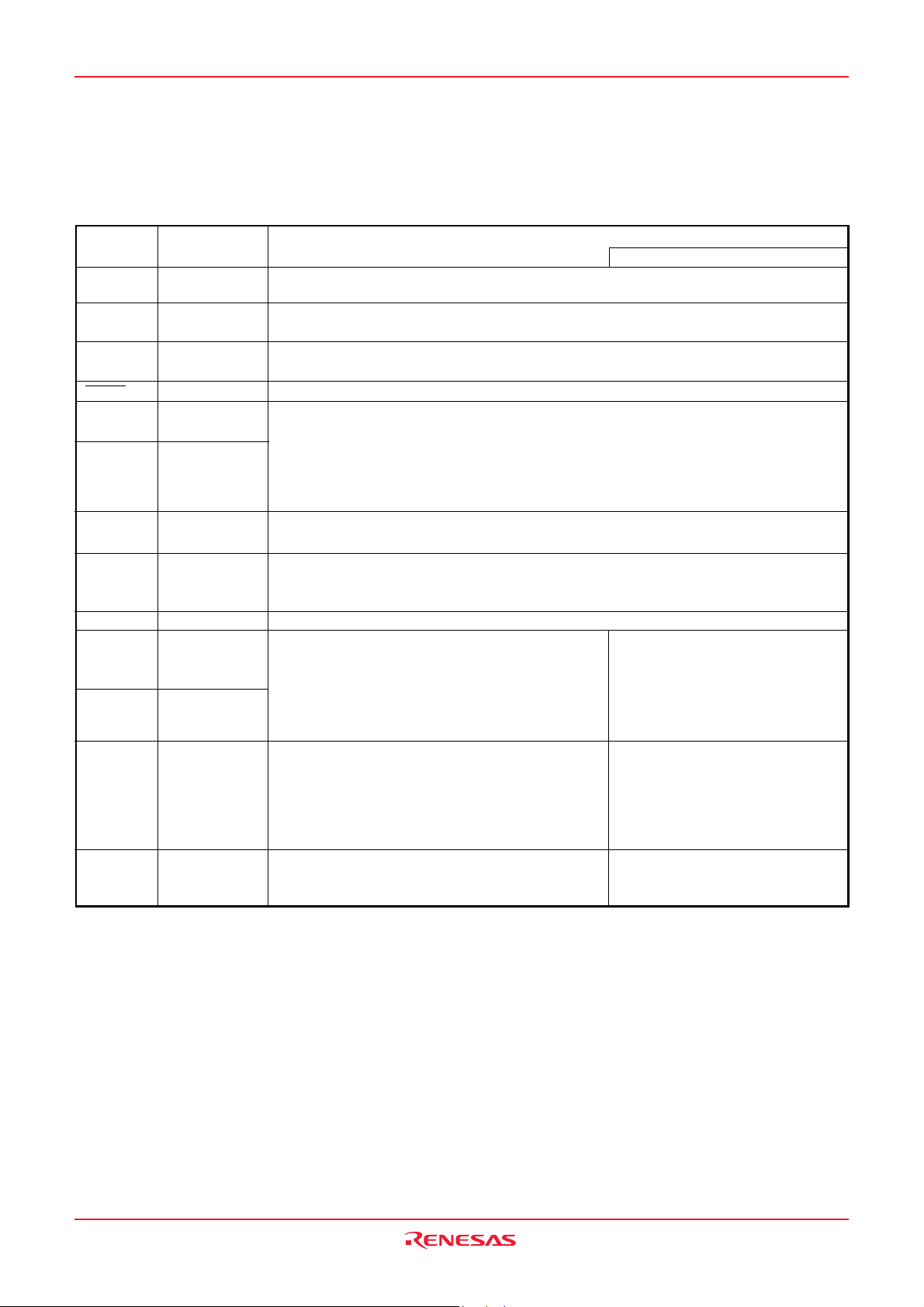

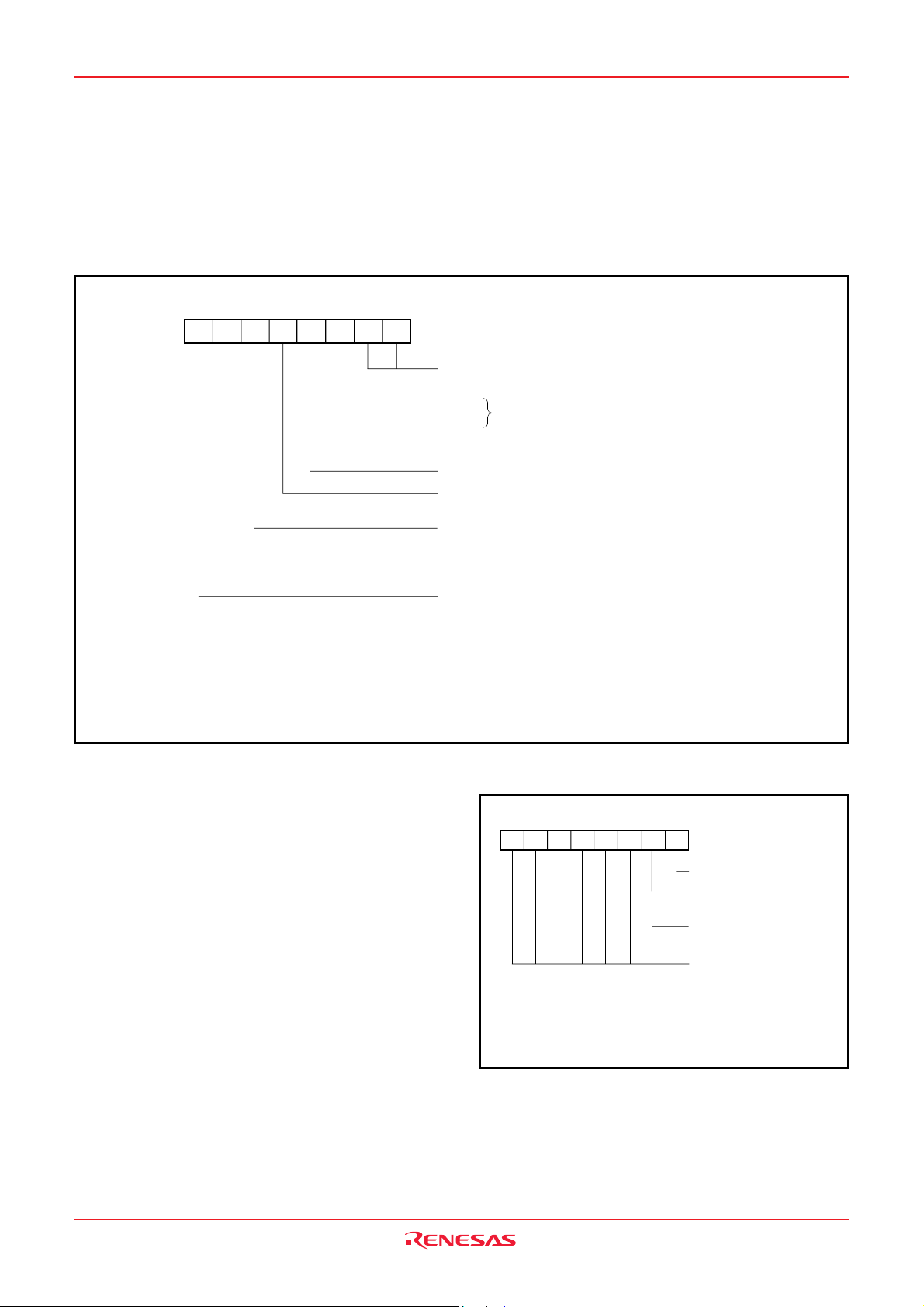

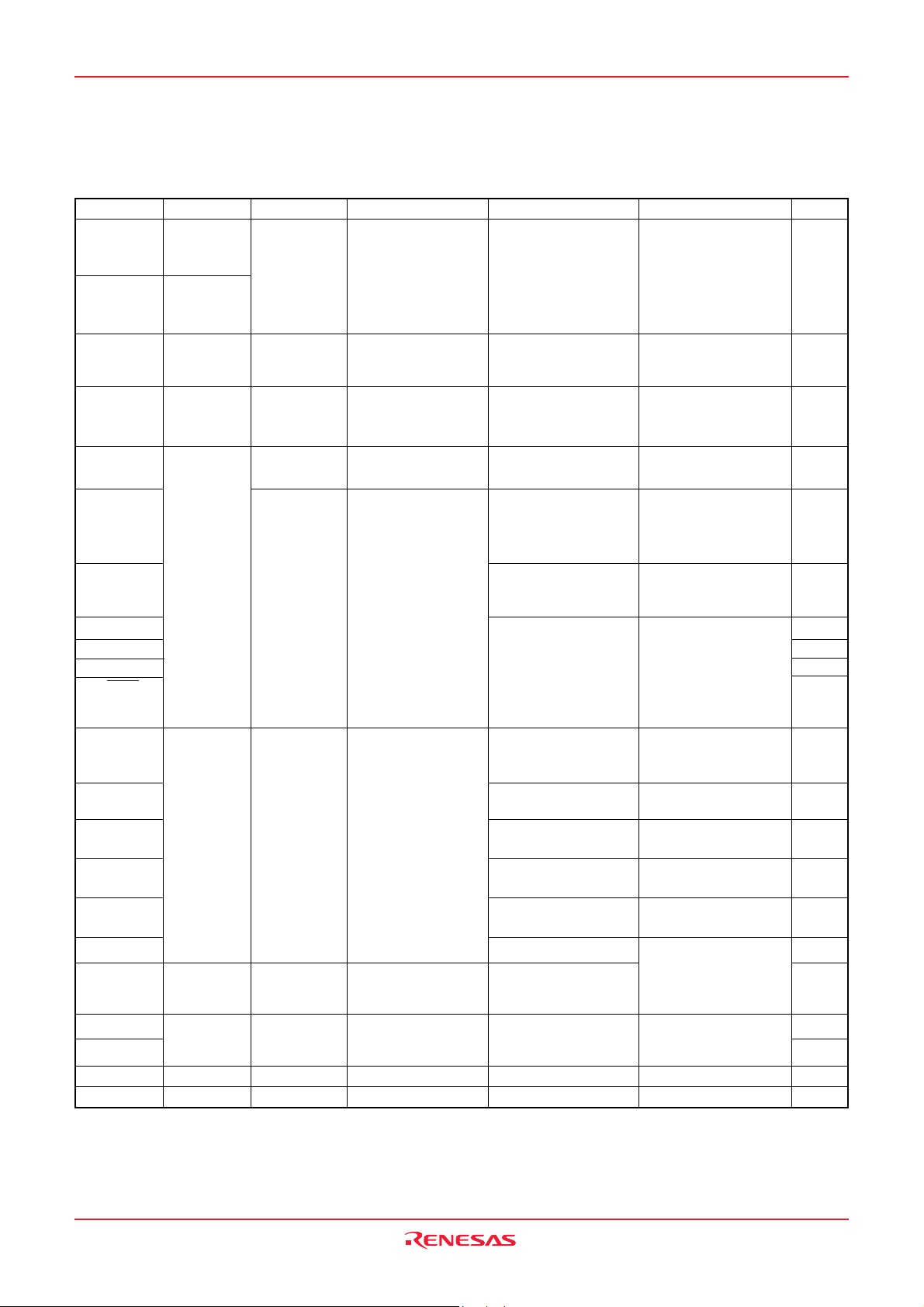

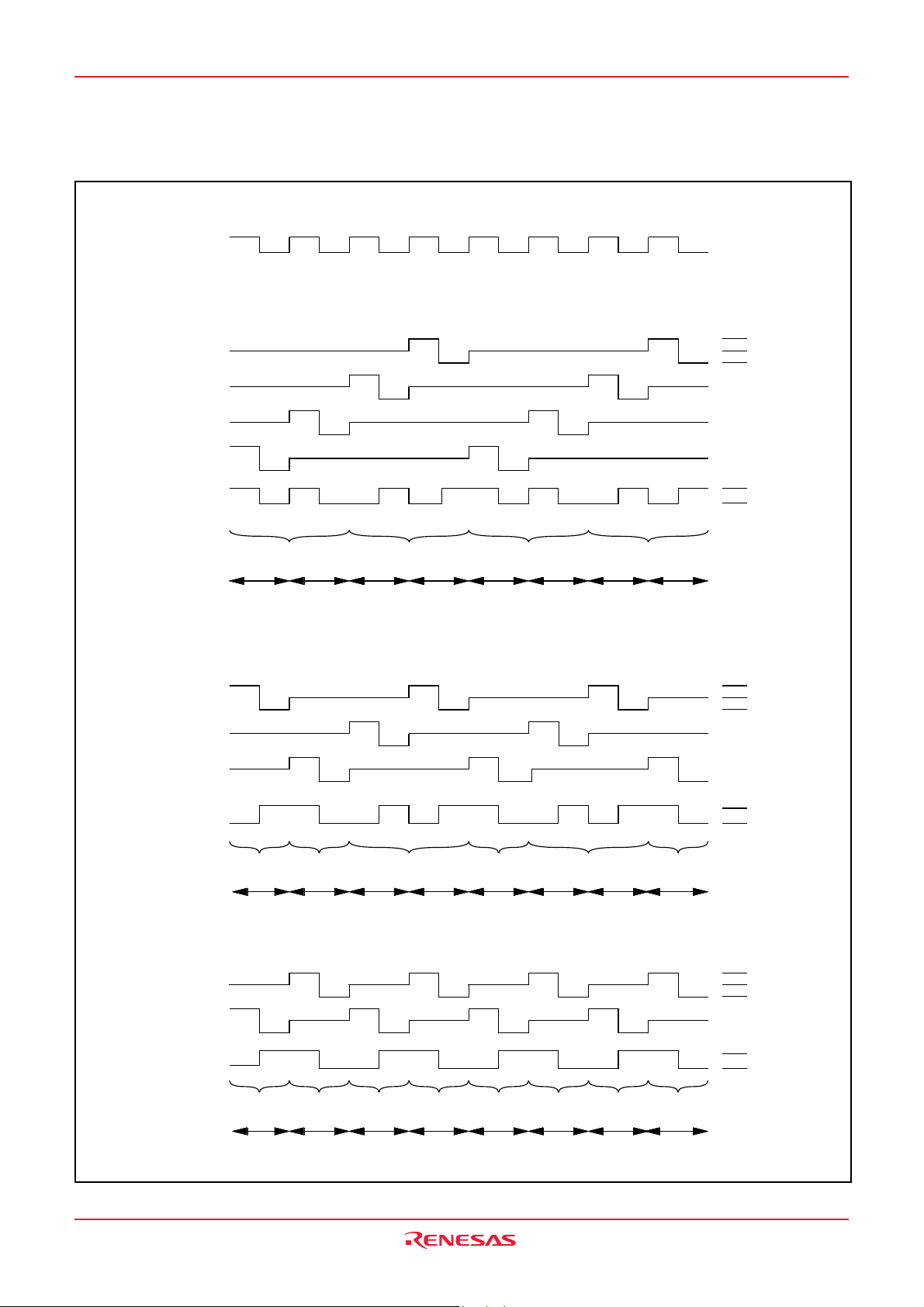

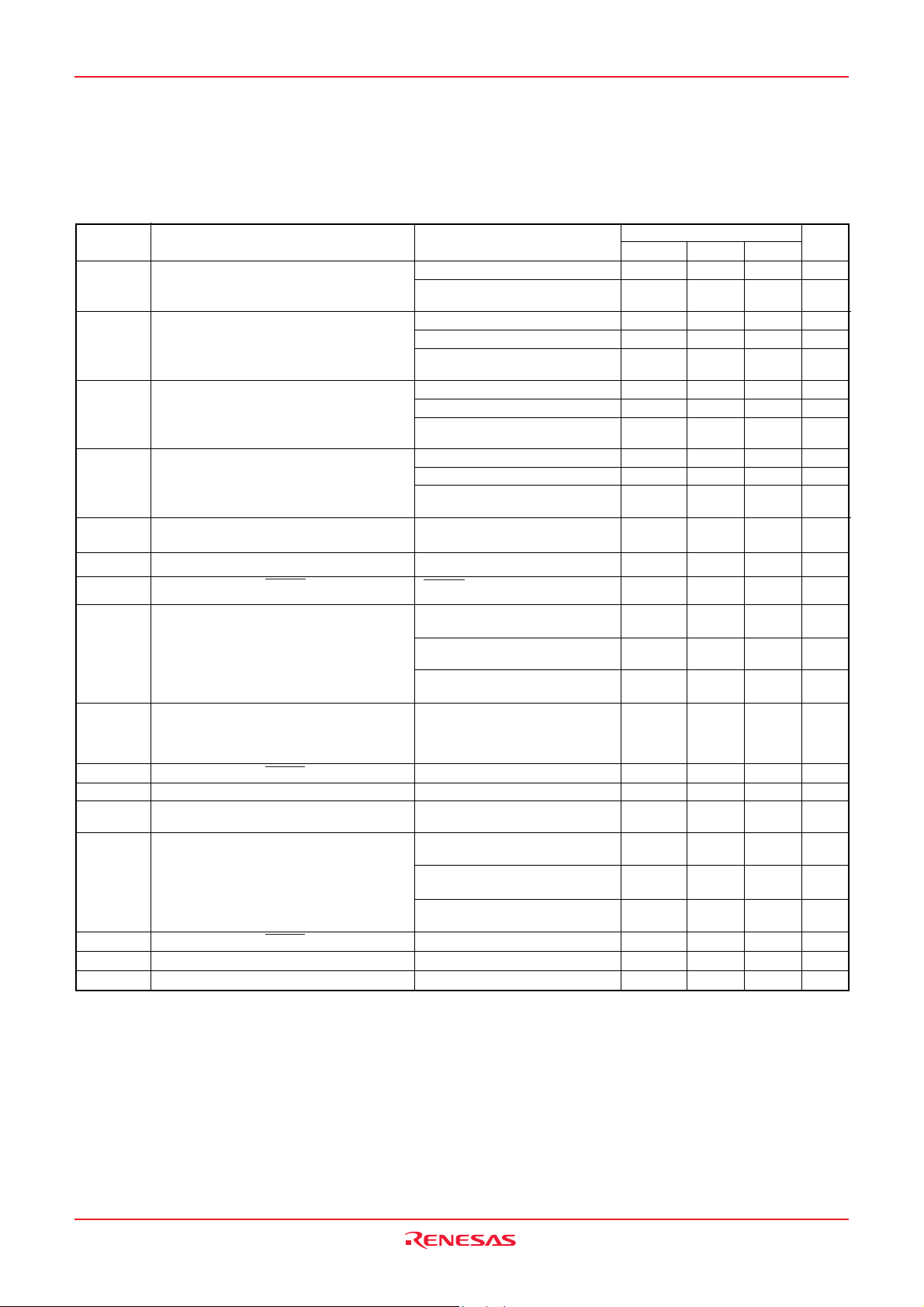

PART NUMBERING

Product M38234 G 6 -XXX FP

Package code

FP : PRQP0080GB-A package

HP : PLQP0080KB-A package

ROM number

Omitted in the shipped in blank version.

ROM/PROM size

1 : 4096 bytes

2 : 8192 bytes

3 : 12288 bytes

4 : 16384 bytes

5 : 20480 bytes

6 : 24576 bytes

7 : 28672 bytes

8 : 32768 bytes

The first 128 bites and the last 2 bytes of ROM are

reserved areas ; they cannot be used.

9 : 36864 bytes

A : 40960 bytes

B : 45056 bytes

C : 49152 bytes

D : 53248 bytes

E : 57344 bytes

F : 61440 bytes

Memory type

G : QzROM version

RAM size

0 : 192 bytes

1 : 256 bytes

2 : 384 bytes

3 : 512 bytes

4 : 640 bytes

5 : 768 bytes

6 : 896 bytes

7 : 1024 bytes

8 : 1536 bytes

9 : 2048 bytes

A : 2560 bytes

Fig. 4 Part numbering

Rev.2.02 Jun 19, 2007 page 7 of 73

REJ03B0146-0202

Page 8

3823 Group

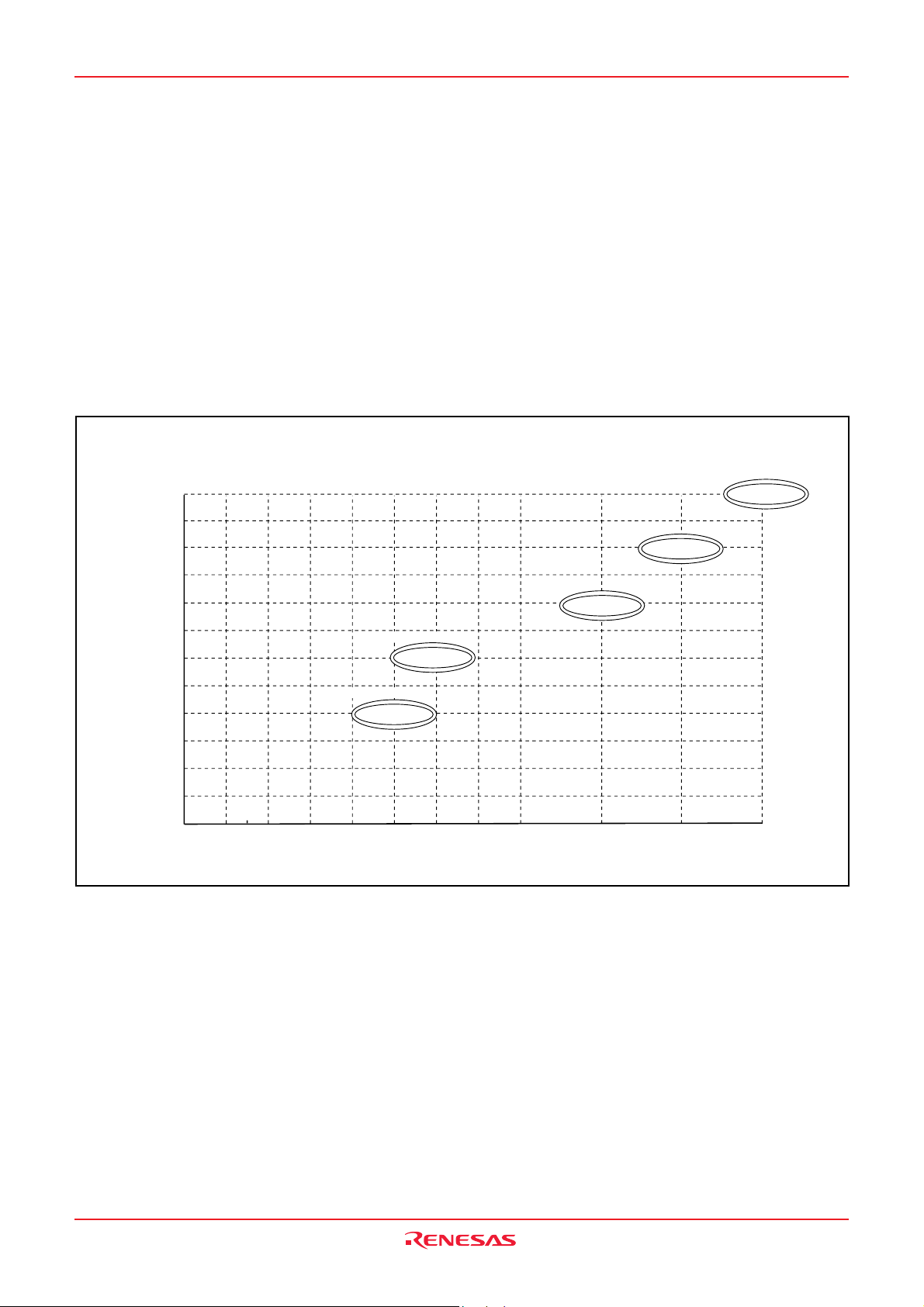

GROUP EXPANSION

Mitsubishi plans to expand the 3823 group as follows:

Memory Type

Support for QzROM version.

Memory Size

ROM size ........................................................... 16 K to 60 K bytes

RAM size ............................................................ 640 to 2560 bytes

Memory Expansion Plan

ROM size (bytes)

60K

56K

48K

40K

32K

28K

24K

20K

16K

Mass production

M38235G6

Mass production

M38234G4

Package

PRQP0080GB-A........................ 0.8 mm-pitch plastic molded QFP

PLQP0080KB-A....................... 0.5 mm-pitch plastic molded LQFP

Mass production

M3823AGF

Mass production

M38239GC

Mass production

M38238G8

12K

8K

4K

192

Fig. 5 Memory expansion plan

256 384 512 640 768 896

RAM size (bytes)

1,024

1,536 2,048

2,560

Rev.2.02 Jun 19, 2007 page 8 of 73

REJ03B0146-0202

Page 9

3823 Group

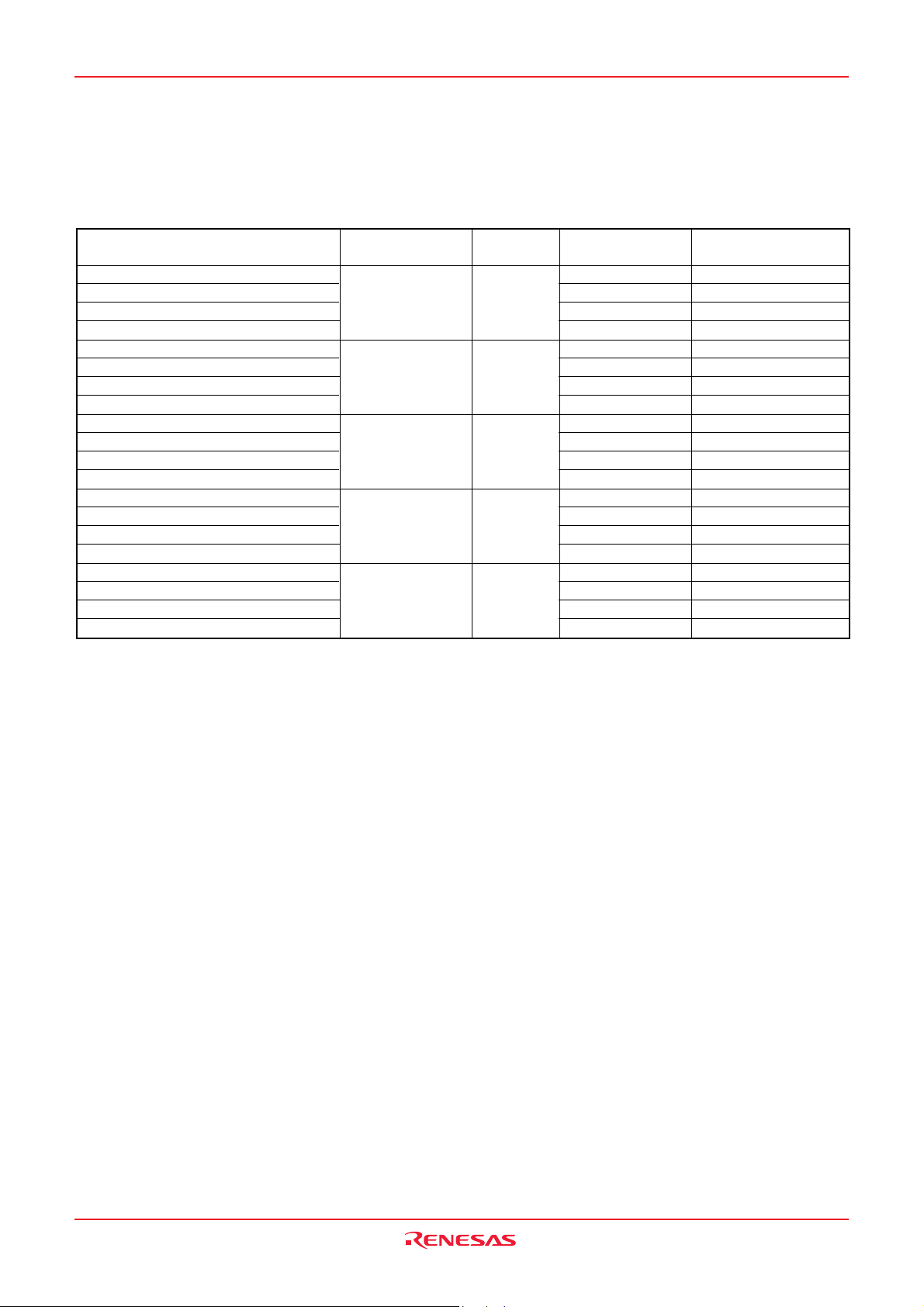

Currently products are listed below.

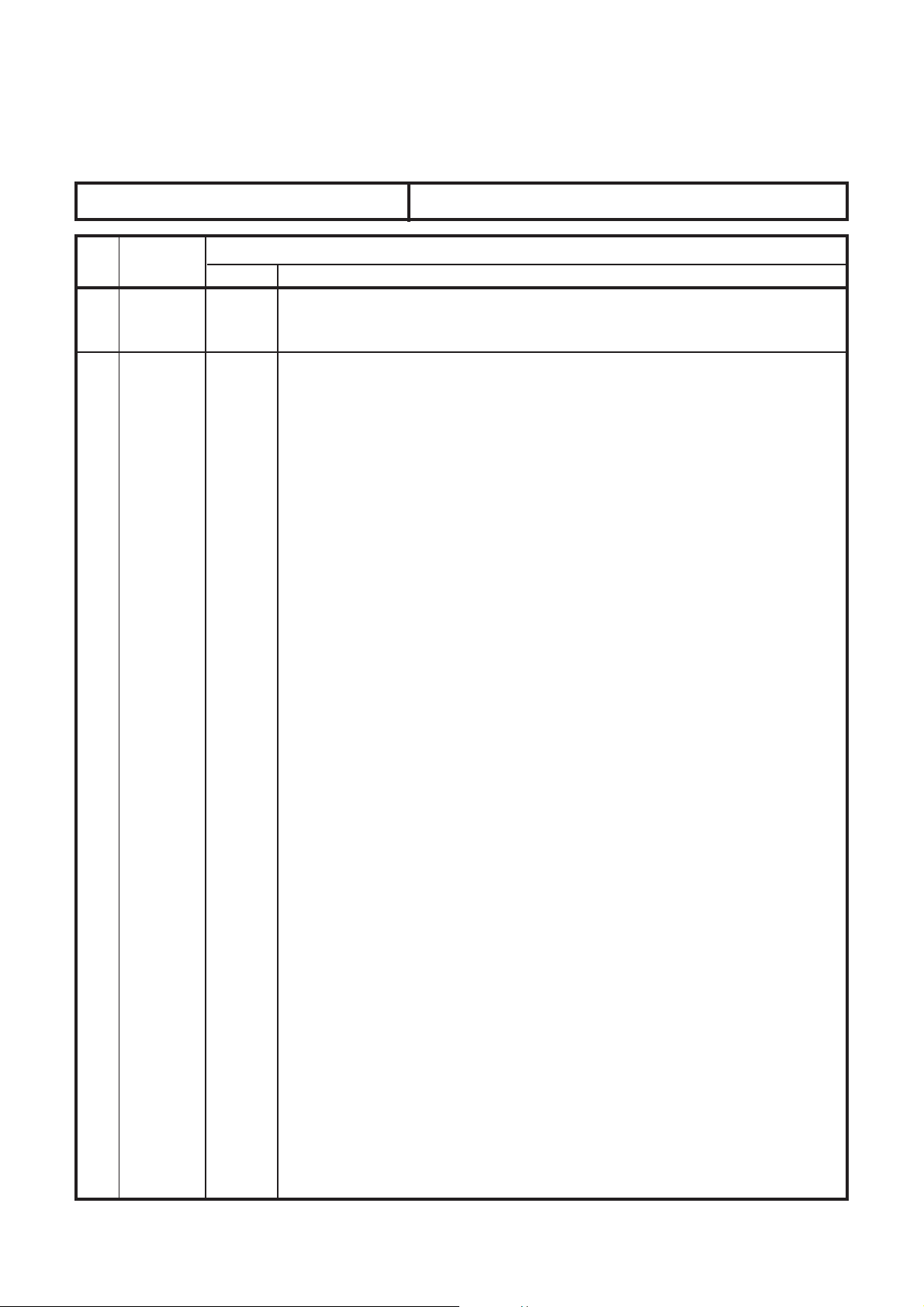

Table 4 List of products

Part No.

M3823AGF-XXXFP

M3823AGF-XXXHP

M3823AGFFP

M3823AGFHP

M38239GC-XXXFP

M38239GC-XXXHP

M38239GCFP

M38239GCHP

M38238G8-XXXFP

M38238G8-XXXHP

M38238G8FP

M38238G8HP

M38235G6-XXXFP

M38235G6-XXXHP

M38235G6FP

M38235G6HP

M38234G4-XXXFP

M38234G4-XXXHP

M38234G4FP

M38234G4HP

Note 1: RAM size includes RAM for LCD display and ROM corrections.

Note 2: RAM size includes RAM for LCD display.

ROM size (bytes)

size for User in ( )

61440

(61310)

49152

(49022)

32768

(32638)

24576

(24446)

16384

(16254)

ROM

RAM size

(bytes)

2560

(Note 1)

2048

(Note 2)

1536

(Note 2)

768

(Note 2)

640

(Note 2)

PRQP0080GB-A

PLQP0080KB-A

PRQP0080GB-A

PLQP0080KB-A

PRQP0080GB-A

PLQP0080KB-A

PRQP0080GB-A

PLQP0080KB-A

PRQP0080GB-A

PLQP0080KB-A

PRQP0080GB-A

PLQP0080KB-A

PRQP0080GB-A

PLQP0080KB-A

PRQP0080GB-A

PLQP0080KB-A

PRQP0080GB-A

PLQP0080KB-A

PRQP0080GB-A

PLQP0080KB-A

RemarksPackage

Blank

Blank

Blank

Blank

Blank

Blank

Blank

Blank

Blank

Blank

Rev.2.02 Jun 19, 2007 page 9 of 73

REJ03B0146-0202

Page 10

3823 Group

FUNCTIONAL DESCRIPTION

CENTRAL PROCESSING UNIT (CPU)

The 3823 group uses the standard 740 family instruction set. Refer to the table of 740 family addressing modes and machine

instructions or the 740 Family Software Manual for details on the

instruction set.

Machine-resident 740 family instructions are as follows:

The FST and SLW instruction cannot be used.

The STP, WIT, MUL, and DIV instruction can be used.

The central processing unit (CPU) has six registers. Figure 6

shows the 740 Family CPU register structure.

[Accumulator (A)]

The accumulator is an 8-bit register. Data operations such as data

transfer, etc., are executed mainly through the accumulator.

[Index Register X (X)]

The index register X is an 8-bit register. In the index addressing

modes, the value of the OPERAND is added to the contents of

register X and specifies the real address.

[Index Register Y (Y)]

The index register Y is an 8-bit register. In partial instruction, the

value of the OPERAND is added to the contents of register Y and

specifies the real address.

[Stack Pointer (S)]

The stack pointer is an 8-bit register used during subroutine calls

and interrupts. This register indicates start address of stored area

(stack) for storing registers during subroutine calls and interrupts.

The low-order 8 bits of the stack address are determined by the

contents of the stack pointer. The high-order 8 bits of the stack address are determined by the stack page selection bit. If the stack

page selection bit is “0” , the high-order 8 bits becomes “0016”. If

the stack page selection bit is “1”, the high-order 8 bits becomes

“0116”.

The operations of pushing register contents onto the stack and

popping them from the stack are shown in Figure 7.

Store registers other than those described in Table 4 with program

when the user needs them during interrupts or subroutine calls.

[Program Counter (PC)]

The program counter is a 16-bit counter consisting of two 8-bit

registers PCH and PCL. It is used to indicate the address of the

next instruction to be executed.

b7

b0

A Accumulator

b7

b0

X Index register X

b7

b0

Y Index register Y

b7 b0

S Stack pointer

b7b15 b0

H

PC

L

Program counterPC

b7 b0

N VTBDIZC Processor status register (PS)

Carry flag

Zero flag

Interrupt disable flag

Decimal mode flag

Break flag

Index X mode flag

Overflow flag

Negative flag

Fig. 6 740 Family CPU register structure

Rev.2.02 Jun 19, 2007 page 10 of 73

REJ03B0146-0202

Page 11

3823 Group

e

O n - g o i n g R o u t i n

P u s h r e t u r n a d d r e s s

o n s t a c k

P O P re t u r n

a d d r e s s f r o m s t a c k

I n t e r r u p t r e q u e s t

M ( S )( P CH)

S ) –

( S )

M ( S )( P CL)

S ) –

( S )

S u b r o u t i n e

E x e c u t e R T S

S ) +

( S )

( P CL)M ( S )

S ) +

( S )

( P CH)M ( S )

( N o t e )

(

(

1

(

(

M ( S )( P CH)

E x e c u t e J S R

1

1

1

( S )

( S ) – 1

M ( S )( P CL)

S ) –

( S )

(

M ( S )( P S )

S ) –

( S )

(

I n t e r r u p t

S e r v i c e R o u t i n e

E x e c u t e R T I

S ) +

( S )

(

( P S )M ( S )

S ) +

( S )

(

( P CL)M ( S )

S ) +

( S )

(

P u s h r e t u r n a d d r e s s

o n s t a c k

1

P u s h c o n t e n t s o f p r o c e s s o r

s t a t u s r e g i s t e r o n s t a c k

1

I F l a g i s s e t f r o m “ 0 ” t o “ 1 ”

F e t c h t h e j u m p v e c t o r

1

P O P c o n t e n t s o f

p r o c e s s o r s t a t u s

r e g i s t e r f r o m s t a c k

1

P O P r e t u r n

a d d r e s s

1

f r o m s t a c k

( P CH)M ( S )

N o t e: C o n d i t i o n f o r a c c e p t a n c e o f a n i n t e r r u p t I n t e r r u p t e n a b l e f l a g i s “ 1 ”

Fig. 7 Register push and pop at interrupt generation and subroutine call

Table 5 Push and pop instructions of accumulator or processor status register

Push instruction to stack

Accumulator

Processor status register

I n t e r r u p t d i s a b l e f l a g i s “ 0 ”

PHA

PHP

Pop instruction from stack

PLA

PLP

Rev.2.02 Jun 19, 2007 page 11 of 73

REJ03B0146-0202

Page 12

3823 Group

[Processor status register (PS)]

The processor status register is an 8-bit register consisting of 5

flags which indicate the status of the processor after an arithmetic

operation and 3 flags which decide MCU operation. Branch operations can be performed by testing the Carry (C) flag , Zero (Z) flag,

Overflow (V) flag, or the Negative (N) flag. In decimal mode, the Z,

V, N flags are not valid.

•Bit 0: Carry flag (C)

The C flag contains a carry or borrow generated by the arithmetic

logic unit (ALU) immediately after an arithmetic operation. It can

also be changed by a shift or rotate instruction.

•Bit 1: Zero flag (Z)

The Z flag is set if the result of an immediate arithmetic operation

or a data transfer is “0”, and cleared if the result is anything other

than “0”.

•Bit 2: Interrupt disable flag (I)

The I flag disables all interrupts except for the interrupt

generated by the BRK instruction.

Interrupts are disabled when the I flag is “1”.

•Bit 3: Decimal mode flag (D)

The D flag determines whether additions and subtractions are

executed in binary or decimal. Binary arithmetic is executed when

this flag is “0”; decimal arithmetic is executed when it is “1”.

Decimal correction is automatic in decimal mode. Only the ADC

and SBC instructions can be used for decimal arithmetic.

•Bit 4: Break flag (B)

The B flag is used to indicate that the current interrupt was

generated by the BRK instruction. The BRK flag in the processor

status register is always “0”. When the BRK instruction is used to

generate an interrupt, the processor status register is pushed

onto the stack with the break flag set to “1”.

•Bit 5: Index X mode flag (T)

When the T flag is “0”, arithmetic operations are performed

between accumulator and memory. When the T flag is “1”, direct

arithmetic operations and direct data transfers are enabled

between memory locations.

•Bit 6: Overflow flag (V)

The V flag is used during the addition or subtraction of one byte

of signed data. It is set if the result exceeds +127 to -128. When

the BIT instruction is executed, bit 6 of the memory location

operated on by the BIT instruction is stored in the overflow flag.

•Bit 7: Negative flag (N)

The N flag is set if the result of an arithmetic operation or data

transfer is negative. When the BIT instruction is executed, bit 7 of

the memory location operated on by the BIT instruction is stored

in the negative flag.

Table 6 Set and clear instructions of each bit of processor status register

Set instruction

Clear instruction

C flag

SEC

CLC

Z flag

–

–

I flag

SEI

CLI

D flag

SED

CLD

B flag

–

–

T flag

SET

CLT

V flag

–

CLV

N flag

–

–

Rev.2.02 Jun 19, 2007 page 12 of 73

REJ03B0146-0202

Page 13

3823 Group

[CPU Mode Register (CPUM)] 003B16

The CPU mode register contains the stack page selection bit and

the internal system clock selection bit.

The CPU mode register is allocated at address 003B

16.

b7

Note 1: In low speed mode (X

switch bit is set to "0".

2: In frequency/2/4/8 mode, X

3: When the system clock φ is divided by 4 of f(X

in the CPU mode extension register to “1”.

4: When using the on-chip oscillator in low-speed mode, set the bit 7 in the CPU mode register to “1” after setting the

bit 0 in the CPU mode extension register to “1”.

Fig. 8 Structure of CPU mode register

b0

CPU mode register

(CPUM (CM) : address 003B

Processor mode bits

b1 b0

0 0 : Single-chip mode

0 1 :

1 0 :

1 1 :

Stack page selection bit

0 : 0 page

1 : 1 page

Not used (returns “1” when read)

(Do not write “0” to this bit)

C

Port X

0 : I/O port function (stop oscillating)

1 : X

Main clock (X

0 : Oscillating

1 : Stopped

Main clock division ratio selection bit

0 : f(X

1 : f(X

Internal system clock selection bit

0 : X

1 : X

CIN

is selected as the system clock φ), X

IN-XOUT

oscillation does not stop even if the main clock (XIN-X

IN

), set the bit 6 in the CPU mode register to “0” after setting the bit 1

16

)

Not available

switch bit

(Note 1)

CIN–XCOUT

oscillating function

IN

–

X

OUT

) stop bit (Note 2)

IN

)/2 (frequency/2 mode), or

IN

)/8 (frequency/8 mode)

IN–XOUT

selected (frequency/2/4/8 mode)

CIN–XCOUT,

or on-chip oscillator selected (low-speed mode) (Note 4)

CIN-XCOUT

f(X

IN

)/4 (frequency/4 mode) (Note 3)

oscillation does not stop even if the port XC

OUT

) stop bit is set to "1".

[CPU Mode Extension Register (EXPCM)] 002B

16

f(XIN) divided by 4 for the system clock f and the on-chip oscillator

for the system clock f in low-speed mode can be selected by setting the CPU mode extension register. When the system clock f is

divided by 4 of f(XIN), set the bit 6 in the CPU mode register to “0”

after setting the bit 1 in the CPU mode extension register to “1”.

When using the on-chip oscillator in low-speed mode, set the bit 7

in the CPU mode register to “1” after setting the bit 0 in the CPU

mode extension register to “1”.

Rev.2.02 Jun 19, 2007 page 13 of 73

REJ03B0146-0202

b7

Note

1 : The on-chip oscillator is selected for the operation clock in low-speed mod regardless

CIN-XCOUT

of X

2 : Valid only when the main clock division ratio selection bit (bit 6 in the CPU mode

register) is set to "0".

When "1" (frequency/8 mode) is selected for the main clock division ratio selection bit or

when the internal system clock selection bit is set to 1, set "0" to the frequency/4 mode

control bit.

.

b0

CPU mode extension register

(EXPCM : address 002B

On-chip oscillator control bit

0 : On-chip oscillator not used

(On -chip oscillator sotpping)

1 : On-chip oscillator used (Note 1)

(On -chip oscillator oscillating)

Frequency/4 mode control bit (Note 2)

0 : Frequency/2 mode φ = f(X

1 : Frequency/4 mode φ = f(X

Not used (returns “0” when read)

(Do not write “1” to this bit)

Fig. 9 Structure of CPU mode extension register

16

)

IN

)/2

IN

)/4

Page 14

3823 Group

B F

RAM

R A M

A d d

4

6

8

2

0

C

C

R O M

R O M

A d d

A d d

FF

F F D C

FFFE

FFFF

XXXX

ZZZZ

RAM

R O M

RAM f

ROM

SFR

N

d

I

R

Z

S

R

LCD displ

RAM

R A M

R A M

F

A

A

F

Y Y Y Y

MEMORY

Special Function Register (SFR) Area

The Special Function Register area in the zero page contains control registers such as I/O ports and timers.

RAM

RAM is used for data storage and for stack area of subroutine

calls and interrupts.

ROM

The first 128 bytes and the last 2 bytes of ROM are reserved for

device testing and the rest is user area for storing programs.

Interrupt Vector Area

The interrupt vector area contains reset and interrupt vectors.

Zero Page

The 256 bytes from addresses 000016 to 00FF16 are called the

zero page area. The internal RAM and the special function register (SFR) are allocated to this area.

The zero page addressing mode can be used to specify memory

and register addresses in the zero page area. Access to this area

with only 2 bytes is possible in the zero page addressing mode.

Special Page

The 256 bytes from addresses FF0016 to FFFF16 are called the

special page area. The special page addressing mode can be

used to specify memory addresses in the special page area.

Access to this area with only 2 bytes is possible in the special

page addressing mode.

ROM Code Protect Address

“0016” is written into ROM code protect address (other than the

user ROM area) when selecting the protect bit write by using a serial programmer or selecting protect enabled for writing shipment

by Renesas Technology corp.. When “0016” is set to the ROM

code protect address, the protect function is enabled, so that reading or writing from/to QzROM is disabled by a serial programmer.

As for the QzROM product in blank, the ROM code is protected by

selecting the protect bit write at ROM writing with a serial programmer.

As for the QzROM product shipped after writing, “0016” (protect

enabled) or “FF16” (protect disabled) is written into the ROM code

protect address when Renesas Technology corp. performs writing.

The writing of “0016" or “FF16” can be selected as ROM option

setup (“MASK option” written in the mask file converter) when ordering.

area

s i z

( b y t e s )

6 4 0

7 6 8

1 5 3 6

2 0 4 8

2 5 6 0

a r e

s i z

( b y t e s )

1 6 3 8

2 4 5 7

3 2 7 6

4 9 1 5

6 1 4 4

r e s s

e

a

r e s

e

X X X X

0 2

0 3 3 F

0 6 3 F

0 8 3 F

0 A3 F

Y Y Y Y

0 0

A 0 0 0

8 0 0 0

4 0 0 0

10 0 0

1 6

1 6

1 6

1 6

1 6

1 6

r e s

s

1 6

1 6

0

1 6

1 6

1 6

1 6

Z Z Z Z

0 8

A 0 8 0

8 0 8 0

4 0 8 0

10 8 0

s

1 6

1 6

0

1 6

1 6

1 6

1 6

0000

0040

0050

0100

0A40

16

16

16

16

16

16

1 6

e s e r v e d R O M a r e

16

00

16

1 6

16

e s e r v e d R O M a r e

16

area

ay

area

or

correction

o t u s e

nterru pt vecto r area

ero page

0A00

16

1 f o r R O M c o r r e c t i o

0A1

16

2

0

1 6

0

2 f o r R O M c o r r e c t i o

3

0

1 6

a

p e c i a l p a g

a

e

n

n

Fig. 10 Memory map diagram

Rev.2.02 Jun 19, 2007 page 14 of 73

REJ03B0146-0202

Page 15

3823 Group

A

B

C

D

E

F

A

B

C

D

E

F

A

B

C

D

E

F

A

B

C

D

E

F

I

)

T i

)

T i

)

I

(INTEDGE)

C P U

)

I

(IREQ1)

I

(IREQ2)

I

)

T i

)

T i

)

T i

)

T i

)

T i

)

T i

)

T i

)

Ti

M)

(CKOUT)

S

)

LCD

(LM)

A D

)

A D

)

P

)

P

)

P

)

P

)

P

)

P

)

P

)

P

)

P

)

P

)

P

)

P

)

P

)

P

)

S

)

Serial I/O

(SIO1CON)

UART

(UARTCON)

Baud

(BRG)

P U L L

)

P U L L

)

T

( T B

)

P

)

R O M

)

R O M

)

R O M

)

R O M

)

R O M

)

T

)

T

)

C P U

)

T

)

RRF

(RRFR)

Periph

(EXP)

A D

)

W

(WDT)

N

0 0 0 01

0 0 0 11

0 0 0 21

0 0 0 31

0 0 0 41

0 0 0 51

0 0 0 61

0 0 0 71

0 0 0 81

0 0 0 91

0 0 0

0 0 0

0 0 0

0 0 0

000

0 0 0

0 0 1 01

0 0 1 11

0 0 1 21

0 0 1 31

0 0 1 41

0 0 1 51

0 0 1 61

0 0 1 71

001816

001916

001

0 0 1

0 0 1

001

001

0 0 1

o r t P 0 r e g i s t e r ( P 0

6

o r t P 0 d i r e c t i o n r e g i s t e r ( P 0 D

6

o r t P 1 r e g i s t e r ( P 1

6

o r t P 1 d i r e c t i o n r e g i s t e r ( P 1 D

6

o r t P 2 r e g i s t e r ( P 2

6

o r t P 2 d i r e c t i o n r e g i s t e r ( P 2 D

6

o r t P 3 r e g i s t e r ( P 3

6

6

o r t P 4 r e g i s t e r ( P 4

6

o r t P 4 d i r e c t i o n r e g i s t e r ( P 4 D

6

o r t P 5 r e g i s t e r ( P 5

1 6

o r t P 5 d i r e c t i o n r e g i s t e r ( P 5 D

1 6

o r t P 6 r e g i s t e r ( P 6

1 6

o r t P 6 d i r e c t i o n r e g i s t e r ( P 6 D

1 6

o r t P 7 r e g i s t e r ( P 7

16

o r t P 7 d i r e c t i o n r e g i s t e r ( P 7 D

1 6

c o r r e c t i o n a d d r e s s 1 h i g h - o r d e r r e g i s t e r ( R C A 1 H

6

c o r r e c t i o n a d d r e s s 1 l o w - o r d e r r e g i s t e r ( R C A 1 L

6

c o r r e c t i o n a d d r e s s 2 h i g h - o r d e r r e g i s t e r ( R C A 2 H

6

c o r r e c t i o n a d d r e s s 2 l o w - o r d e r r e g i s t e r ( R C A 2 L

6

c o r r e c t i o n e n a b l e r e g i s t e r ( R C R

6

6

r e g i s t e r A ( P U L L A

6

r e g i s t e r B ( P U L L B

6

r a n s m i t / R e c e i v e b u f f e r r e g i s t e

e r i a l I / O s t a t u s r e g i s t e r ( S I O S T S

16

1 6

1 6

16

16

1 6

control register

control register

rate generator

m e r X l o w - o r d e r r e g i s t e r ( T X L

0 0 2 01

6

m e r X h i g h - o r d e r r e g i s t e r ( T X H

0 0 2 11

6

m e r Y l o w - o r d e r r e g i s t e r ( T Y L

0 0 2 21

6

m e r Y h i g h - o r d e r r e g i s t e r ( T Y H

0 0 2 31

6

m e r 1 r e g i s t e r ( T 1

0 0 2 41

6

m e r 2 r e g i s t e r ( T 2

0 0 2 51

6

m e r 3 r e g i s t e r ( T 3

0 0 2 61

6

m e r X m o d e r e g i s t e r ( T X M

0 0 2 71

6

m e r Y m o d e r e g i s t e r ( T Y M

0 0 2 81

6

0 0 2 91

6

0 0 2

0 0 2

002

002

002

0 0 2

0 0 3 01

0 0 3 11

0 0 3 21

0 0 3 31

0 0 3 41

0 0 3 51

0 0 3 61

/ R B

r

0 0 3 71

003816

003916

003

0 0 3

003

003

003

0 0 3

mer 12 3 mode register (T123

1 6

φ output control register

m o d e e x p a n s i o n r e g i s t e r ( E X P C M

1 6

e m p o r a r y d a t a r e g i s t e r 0 ( T D 0

16

e m p o r a r y d a t a r e g i s t e r 1 ( T D 1

16

e m p o r a r y d a t a r e g i s t e r 2 ( T D 2

16

1 6

register

6

6

6

6

6

6

6

6

eral function expansion register

c o n t r o l r e g i s t e r ( A D C O N

c o n v e r s i o n h i g h - o r d e r r e g i s t e r ( A D H

c o n v e r s i o n l o w - o r d e r r e g i s t e r ( A D L

atchdog timer register

e g m e n t o u t p u t e n a b l e r e g i s t e r ( S E G

mode register

16

nterrupt edge selection register

m o d e r e g i s t e r ( C P U M

1 6

16

nterrupt request register 1

16

nterrupt request register 2

n t e r r u p t c o n t r o l r e g i s t e r 1 ( I C O N 1

16

n t e r r u p t c o n t r o l r e g i s t e r 2 ( I C O N 2

1 6

o t e : D o n o t a c c e s s t o t h e S F R a r e a i n c l u d i n g n o t h i n g

Fig. 11 Memory map of special function register (SFR)

Rev.2.02 Jun 19, 2007 page 15 of 73

REJ03B0146-0202

.

Page 16

3823 Group

P

PULL

A

b7b

P

D i

PULL

B

b7b

N

PULL

PULL

I/O PORTS

Direction Registers (ports P2, P4

1-P47, and

P5-P7)

The 3823 group has 49 programmable I/O pins arranged in seven

I/O ports (ports P0–P2, P41–P47 and P5-P7). The I/O ports P2,

P41–P47 and P5-P7 have direction registers which determine the

input/output direction of each individual pin. Each bit in a direction

register corresponds to one pin, and each pin can be set to be input port or output port.

When “0” is written to the bit corresponding to a pin, that pin becomes an input pin. When “1” is written to that bit, that pin becomes an output pin.

If data is read from a pin set to output, the value of the port output

latch is read, not the value of the pin itself. Pins set to input are

floating. If a pin set to input is written to, only the port output latch

is written to and the pin remains floating.

Direction Registers (ports P0 and P1)

Ports P0 and P1 have direction registers which determine the input/output direction of each individual port.

Each port in a direction register corresponds to one port, each port

can be set to be input or output. When “0” is written to the bit 0 of

a direction register, that port becomes an input port. When “1” is

written to that port, that port becomes an output port. Bits 1 to 7 of

ports P0 and P1 direction registers are not used.

0

register

(PULLA: address 001616)

00–P07 pull-down

P1

0

–P17 pull-down

P2

0

–P27 pull-up

P3

4

–P37 pull-down

P7

0

, P71 pull-up

Not used (return “0” when read)

0

register

(PULLB : address 001716)

41–P43 pull-up

P4

4

–P47 pull-up

P5

0

–P53 pull-up

P5

4

–P57 pull-up

P6

0

–P63 pull-up

P6

4

–P67 pull-up

Not used (return “0” when read)

ote: The contents of

do not affect ports programmed as the output port.

register A and

s a b l

0 :

1 : E n a b l e

e

register B

Fig. 12 Structure of PULL register A and PULL register B

Ports P3 and P40

These ports are only for input.

Pull-up/Pull-down Control

By setting the PULL register A (address 001616) or the PULL register B (address 001716), ports except for port P40 can control

either pull-down or pull-up (pins that are shared with the segment

output pins for LCD are pull-down; all other pins are pull-up) with

a program.

However, the contents of PULL register A and PULL register B do

not affect ports programmed as the output ports.

Rev.2.02 Jun 19, 2007 page 16 of 73

REJ03B0146-0202

Page 17

3823 Group

Table 7 List of I/O port function

Pin

P00/SEG16–

P07/SEG23

P10/SEG24–

P17/SEG31

Name

Port P0

Port P1

Input/Output

Input/output,

individual ports

I/O Format

CMOS compatible

input level

CMOS 3-state output

Non-Port Function

LCD segment output

Related SFRs

PULL register A

Segment output enable

register

Diagram No.

(1)

P20/KW0–

P27/KW7

P34/SEG12–

P37/SEG15

P40

P41/φ

P42/INT0,

Port P2

Port P3

Port P4

Input/output,

individual bits

Input

Input

Input/output,

individual bits

CMOS compatible

input level

CMOS 3-state output

CMOS compatible

input level

CMOS compatible

input level

CMOS compatible

input level

CMOS 3-state output

Key input (key-on

wake-up) interrupt

input

LCD segment output

QzROM program

power pin

φ clock output

XCIN frequency signal

output

External interrupt input

P43/INT1

P44/RXD

P45/TXD

Serial I/O function

input/output

P46/SCLK

P47/S

RDY/SOUT

P50/INT2,

P51/INT3

Port P5

Input/output,

individual bits

CMOS compatible

input level

External interrupt input

CMOS 3-state output

P52/RTP0,

P53/RTP1

P54/CNTR0

P55/CNTR1

P56/TOUT

P57/ADT

P60/AN0–

P67/AN7

Port P6

Input/output,

individual bits

CMOS compatible

input level

Real time port

function output

Timer X function I/O

Timer Y function input

Timer 2 function output

A/D trigger input

A/D conversion input

CMOS 3-state output

P70/XCOUT

P71/XCIN

COM0–COM3

SEG0–SEG11

Notes 1: For details of how to use double function ports as function I/O ports, refer to the applicable sections.

2: When an input level is at an intermediate potential, a current will flow from V

Especially, power source current may increase during execution of the STP and WIT instructions.

Fix the unused input pins to “H” or “L” through a resistor.

Port P7

Common

Segment

Input/output,

individual bits

Output

Output

CMOS compatible

input level

CMOS 3-state output

LCD common output

LCD segment output

Sub-clock

generating circuit I/O

CC to VSS through the input-stage gate.

PULL register A

Interrupt control register 2

PULL register A

Segment output enable

register

PULL register B

φ

output control register

Peripheral function

extension register

PULL register B

Interrupt edge selection

register

PULL register B

Serial I/O control register

Serial I/O status register

UART control register

Peripheral function

extension register

PULL register B

Interrupt edge selection

register

PULL register B

Timer X mode register

PULL register B

Timer X mode register

PULL register B

Timer Y mode register

PULL register B

Timer 123 mode register

PULL register B

A/D control register

PULL register A

CPU mode register

LCD mode register

(2)

(3)

(4)

(5)

(2)

(6)

(7)

(8)

(9)

(2)

(10)

(11)

(12)

(13)

(12)

(14)

(15)

(16)

(17)

(18)

Rev.2.02 Jun 19, 2007 page 17 of 73

REJ03B0146-0202

Page 18

3823 Group

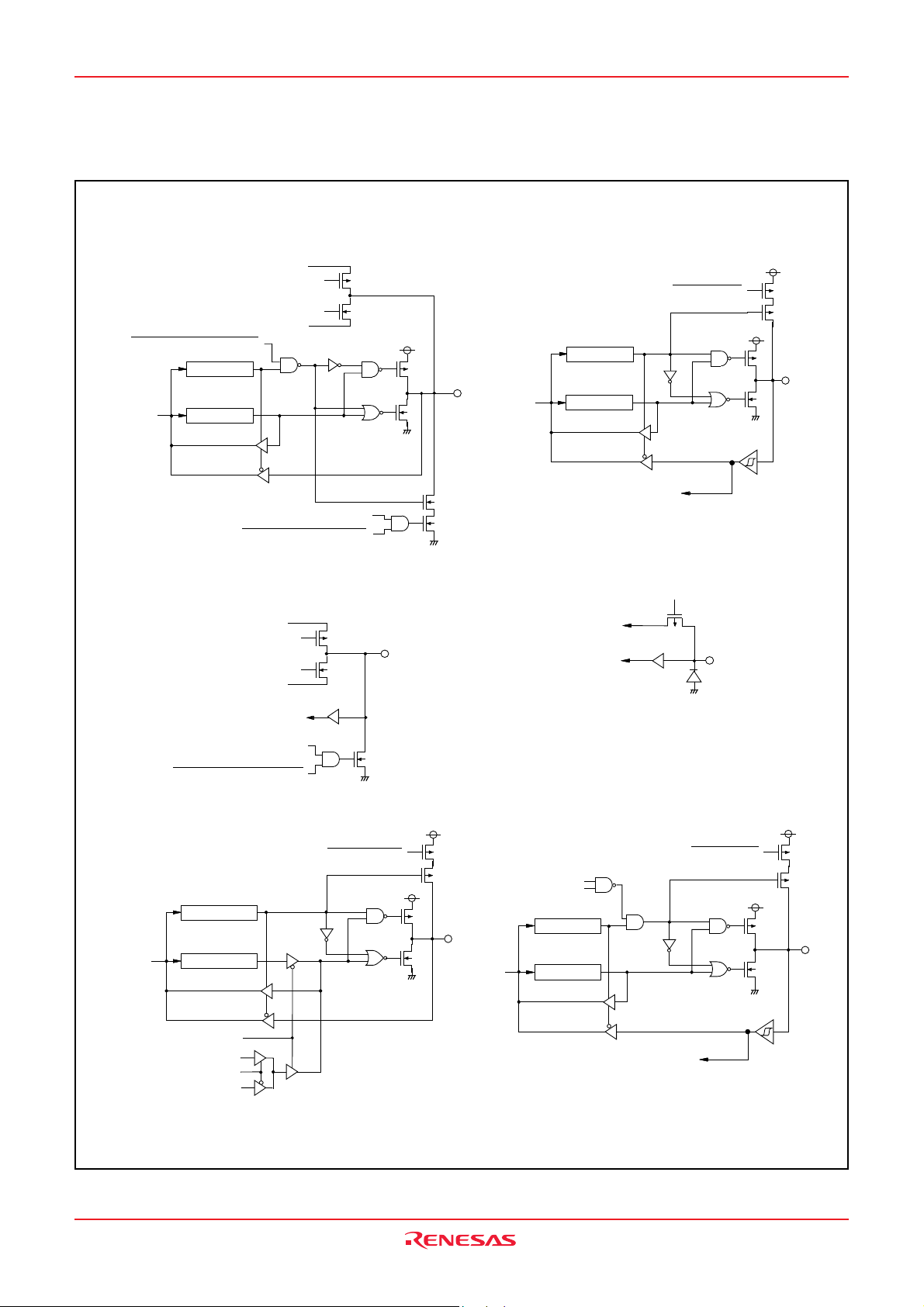

(

)

t

(1) Ports P0, P1

S e g m e n t o u t p u t e n a b l e b i t

D a t a b u s

N o t e : B i t 0 o f d i r e c t i o n r e g i s t e r .

( 3 ) P o r t s P 34– P 3

N o t e

D i r e c t i o n r e g i s t e r

P o r t l a t c h

7

V

L 2

/ V

L 3

V

L 1

/ V

S S

P u l l - d o w n c o n t r o l

Segment output enable bit

V

L 2

/ V

L 3

VL1/V

SS

( 2 ) P o r t s P 2 , P 42, P 43, P 50, P 5

D i r e c t i o n r e g i s t e r

Data bus Port latch

Key input (Key-on wake-up) interrupt input

( 4 ) P o r t P 4

QZROM programmable

power source

INT

0

–INT3 interrupt input

0

Data bus

1

Pull-up control

S e g m e n t o u t p u t e n a b l e b i

(5) Port P4

1

D a t a b u s

φ o u t p u t c o n t r o l b i t

X

CIN

frequency signal

O u t p u t c l o c k s e l e c t i o n b i t

Pull-down control

D i r e c t i o n r e g i s t e r

Port latch

φ

D a t a b u s

Pull-up control

( 6 ) P o r t P 4

4

Serial I/O enable bit

R e c e i v e e n a b l e b i t

Direction register

Data bus Port latch

Pull-up control

Serial I/O input

Fig. 13 Port block diagram (1)

Rev.2.02 Jun 19, 2007 page 18 of 73

REJ03B0146-0202

Page 19

3823 Group

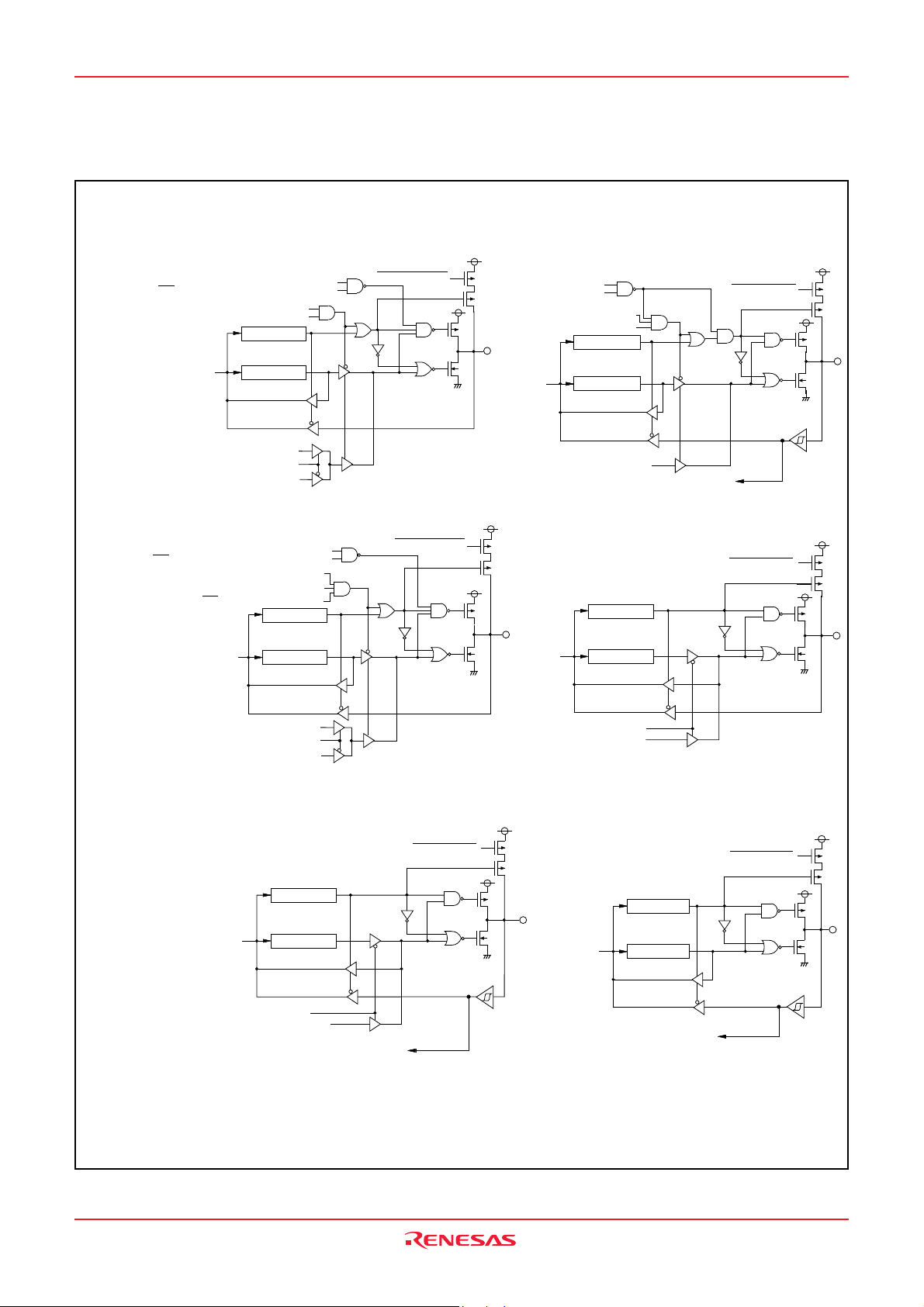

S

(

)

( 7 ) P o r t P 4

5

P-Channel output disabled selection bit

P 45/ T x D , P 47/ S

R D Y

/ S

O U T

P - c h a n n e l o u t p u t d i s a b l e b i t

Serial I/O enable bit

Transmit enable bit

D i r e c t i o n r e g i s t e r

D a t a b u s

P o r t l a t c h

As y n c h r o n o u s s e r i a l I / O o u t p u t

Sy n c h r o n o u s s e r i a l I / O o u t p u t p i n s e l e c t i o n b i t

e r i a l I / O o u t p u

s y n c h r o n o u s o r a s y n c h r o n o u s

(9) Port P4

7

P-Channel output disabled selection bit

P 45/ T x D , P 47/ S

R D Y

/ S

O U T

P - c h a n n e l o u t p u t d i s a b l e b i t

Serial I/O mode selection bit

Serial I/O enable bit

S

RDY,SOUT

output enable bit

D i r e c t i o n r e g i s t e r

D a t a b u s

Port latch

P u l l - u p c o n t r o l

( 8 ) P o r t P 4

synchronized selection bit

Serial I/O enable bit

Serial I/O mode selection bit

D a t a b u s

6

Serial I/O clock-

P u l l - u p c o n t r o l

Serial I/O enable bit

Direction register

Port latch

S e r i a l I / O c l o c k o u t p u t

t

(10) Ports P5

2, P53

S e r i a l I / O c l o c k i n p u t

Pull-up control

Pull-up control

Direction register

Port latchData bus

Synchronous serial I/O output

Synchronous serial I/O output pin s election bit

S e r i a l I / O r e a d y o u t p u t

( 1 1 ) P o r t P 5

4

D i r e c t i o n r e g i s t e r

P o r t l a t c hD a t a b u s

T i m e r X o p e r a t i n g m o d e b i t

(Pulse output mode selection)

T i m e r o u t p u t

CNTR

0

interrupt input

Pull-up control

R e a l t i m e p o r t c o n t r o l b i t

D a t a f o r r e a l t i m e p o r t

( 1 2 ) P o r t s P 5

D a t a b u s

5 ,

P 5

7

Direction register

Port latch

CNTR

1

A/D trigger interrupt input

interrupt input

Pull-up control

Fig. 14 Port block diagram (2)

Rev.2.02 Jun 19, 2007 page 19 of 73

REJ03B0146-0202

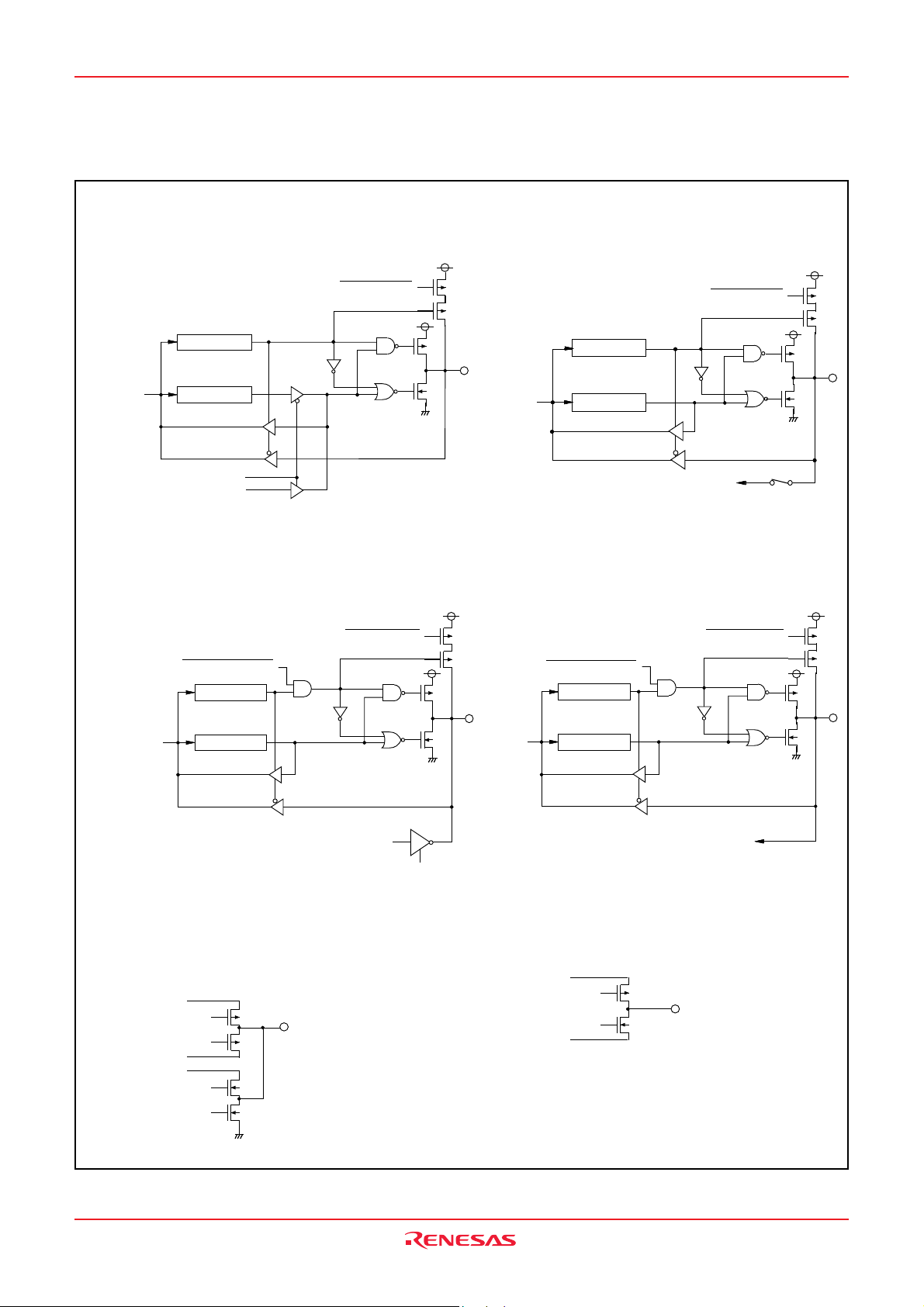

Page 20

3823 Group

( 1 3 ) P o r t P 56

D a t a b u s

U

o u t p u t c o n t r o l b i

TO

T

( 1 5 ) P o r t P 70

D i r e c t i o n r e g i s t e r

P o r t l a t c h

T i m e r o u t p u t

s w i t c h b i

P o r t X

C

D i r e c t i o n r e g i s t e r

t

s w i t c h b i t + P u l l - u p c o n t r o

P o r t X

( 1 4 ) P o r t P 6

P u l - u p c o n t r o l

Data bus

Direction register

Port latch

A / D c o n v e r s i o n i n p u t

P u l l - u p c o n t r o l

A n a l o g i n p u t p i n s e l e c t i o n b i t

( 1 6 ) P o r t P 71

s w i t c h b i t + P u l l - u p c o n t r o

C

t

l

Port X

P o r t X

C switch bit

Direction register

C

l

D a t a b u s

P o r t l a t c h

( 1 7 ) C O M0– C O M3

L 3

V

VL

2

VL

1

Fig. 15 Port block diagram (3)

O s c i l l a t i o n c i r c u i t

P o r t P 71

P o r t XC s w i t c h b i t

T h e g a t e i n p u t s i g n a l o f e a c h t r a n s i s t o r i s

c o n t r o l l e d b y t h e L C D d u t y r a t i o a n d t h e

b i a s v a l u e .

D a t a b u s

( 1 8 ) S E G0– S E G1

VL

2/

VL

3

VL

1/

VS

S

Port latch

S u b - c l o c k g e n e r a t i n g c i r c u i t i n p u t

1

T h e v o l t a g e a p p l i e d t o t h e s o u r c e s o f

P - c h a n n e l a n d N - c h a n n e l t r a n s i s t o r s

i s t h e c o n t r o l l e d v o l t a g e b y t h e b i a s

v a l u e .

Rev.2.02 Jun 19, 2007 page 20 of 73

REJ03B0146-0202

Page 21

3823 Group

Termination of unused pins

• Termination of common pins

I/O ports: Select an input port or an output port and follow

each processing method.

Output ports: Open.

Input ports: If the input level become unstable, through current

flow to an input circuit, and the power supply current

may increase.

Especially, when expecting low consumption current

(at STP or WIT instruction execution etc.), pull-up or

pull-down input ports to prevent through current

(built-in resistor can be used). Pull-down the P40/

(VPP) pin.

We recommend processing unused pins through a

resistor which can secure IOH(avg) or IOL(avg).

Because, when an I/O port or a pin which have an

output function is selected as an input port, it may

operate as an output port by incorrect operation etc.

Rev.2.02 Jun 19, 2007 page 21 of 73

REJ03B0146-0202

Page 22

3823 Group

Table 8 Termination of unused pins

Pin

P00/SEG16–P17/SEG23

P10/SEG24–P17/SEG31

P20/KW0–P27/KW7

P34/SEG12–P37/SEG15

P40/(VPP)

P41/φ

P42/INT0

P43/INT1

P44/RxD

P45/TxD

P46/SCLK

P47/SRDY/SOUT

P50/INT2

P51/INT3

P52/RTP0

P53/RTP1

P54/CNTR0

P55/CNTR1

P56/TOUT

P57/ADT

P60/AN0–P67/AN7

P70/XCOUT

P71/XCIN

VL3 (Note)

VL2 (Note)

VL1 (Note)

COM0–COM3

SEG0–SEG

AVSS

VREF

XOUT

Note : The termination of VL3, VL2 and VL1 is applied when the bit 3 of the LCD mode register is “0”

11

Termination 1 (recommend)

I/O port

Input port

Input port (pull-down)

I/O port

Connect to VSS

Connect to VSS

Connect to VSS

Open

Open

Connect to VSS

Connect to VCC or VSS

When an external clock is

input to the XIN pin, leave

the XOUT pin open.

When selecting SEG output, open.

When selecting KW function, perform

termination of input port.

When selecting SEG output, open.

When selecting φ output, open.

When selecting INT0 function,

perform termination of input port.

When selecting INT1 function,

perform termination of input port.

When selecting RXD function,

perform termination of input port.

When selecting TXD function,

perform termination of output port.

When selecting external clock input,

perform termination of input port.

When selecting SRDY function,

perform termination of output port.

When selecting INT2 function,

perform termination of input port.

When selecting INT3 function,

perform termination of input port.

When selecting RTP0 function,

perform termination of output port.

When selecting RTP1 function,

perform termination of output port.

When selecting CNTR0 input function,

perform termination of input port.

When selecting CNTR1 function,

perform termination of input port.

When selecting TOUT function,

perform termination of output port.

When selecting ADT function,

perform termination of input port.

When selecting AN function, these

pins can be opened. (A/D conversion

result cannot be guaranteed.)

Do not select XCIN-XCOUT oscillation

function by program.

Termination 2

–

–

–

–

–

–

–

–

–

Termination 3

–

–

–

–

–

–

–

–

–

When selecting internal clock output,

perform termination of output port.

When selecting SOUT function,

perform termination of output port.

–

–

–

–

When selecting CNTR0 output function,

perform termination of output port.

–

–

–

–

–

–

–

–

–

–

–

–

–

Rev.2.02 Jun 19, 2007 page 22 of 73

REJ03B0146-0202

Page 23

3823 Group

INTERRUPTS

The 3823 group interrupts are vector interrupts with a fixed priority scheme, and generated by 16 sources among 17 sources: 8

external, 8 internal, and 1 software.

The interrupt sources, vector addresses

are shown in Table 9.

Each interrupt except the BRK instruction interrupt has the interrupt request bit and the interrupt enable bit. These bits and the

interrupt disable flag (I flag) control the acceptance of interrupt requests. Figure 16 shows an interrupt control diagram.

Table 9 Interrupt vector addresses and priority

Interrupt Source

Reset (Note 2)

INT0

INT1

Serial I/O

reception

Serial I/O

transmission

Timer X

Timer Y

Timer 2

Timer 3

CNTR0

CNTR1

Timer 1

INT2

INT3

Key input

(Key-on wake-up)

ADT

A/D conversion

BRK instruction

Notes1: Vector addresses contain interrupt jump destination addresses.

2: Reset function in the same way as an interrupt with the highest priority.

Priority

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

(1)

, and interrupt priority

Vector Addresses (Note 1)

LowHigh

FFFD16

FFFB16

FFF916

FFF716

FFF516

FFF316

FFF116

FFEF16

FFED16

FFEB16

FFE916

FFE716

FFE516

FFE316

FFE116

FFDF16

FFDD16

FFFC16

FFFA16

FFF816

FFF616

FFF416

FFF216

FFF016

FFEE16

FFEC16

FFEA16

FFE816

FFE616

FFE416

FFE216

FFE016

FFDE16

FFDC16

An interrupt requests is accepted when all of the following

conditions are satisfied:

• Interrupt disable flag.................................“0”

• Interrupt disable request bit .....................“1”

• Interrupt enable bit................................... “1”

Though the interrupt priority is determined by hardware, priority

processing can be performed by software using the above bits

and flag.

Interrupt Request

Generating Conditions

At reset

At detection of either rising or

falling edge of INT0 input

At detection of either rising or

falling edge of INT1 input

At completion of serial interface

data reception

At completion of serial interface

transmit shift or when transmission buffer is empty

At timer X underflow

At timer Y underflow

At timer 2 underflow

At timer 3 underflow

At detection of either rising or

falling edge of CNTR0 input

At detection of either rising or

falling edge of CNTR1 input

At timer 1 underflow

At detection of either rising or

falling edge of INT2 input

At detection of either rising or

falling edge of INT3 input

At falling of conjunction of input

level for port P2 (at input mode)

At falling of ADT input

At completion of A/D conversion

At BRK instruction execution

Non-maskable

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

Valid when serial interface is se-

lected

Valid when serial interface is se-

lected

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

External interrupt

(Valid at falling)

Valid when ADT interrupt is selected, External interrupt

(Valid at falling)

Valid when A/D interrupt is selected

Non-maskable software interrupt

Remarks

Rev.2.02 Jun 19, 2007 page 23 of 73

REJ03B0146-0202

Page 24

3823 Group

t

t

t

I n t e r r u p t r e q u e s t b i

I n t e r r u p t e n a b l e b i

I n t e r r u p t d i s a b l e f l a g ( I )

Fig. 16 Interrupt control diagram

B R K i n s t r u c t i o n

R e s e

i n t e r r u p t r e q u e s t

Interrupt Disable Flag

The interrupt disable flag is assigned to bit 2 of the processor status register. This flag controls the acceptance of all interrupt

requests except for the BRK instruction. When this flag is set to

“1”, the acceptance of interrupt requests is disabled. When it is set

to “0”, acceptance of interrupt requests is enabled. This flag is set

to “1” with the SET instruction and set to “0” with the CLI instruction.

When an interrupt request is accepted, the contents of the processor status register are pushed onto the stack while the interrupt

disable flag remaines set to “0”. Subsequently, this flag is automatically set to “1” and multiple interrupts are disabled.

To use multiple interrupts, set this flag to “0” with the CLI instruction within the interrupt processing routine.

The contents of the processor status register are popped off the

stack with the RTI instruction.

Interrupt Request Bits

Once an interrupt request is generated, the corresponding interrupt request bit is set to “1” and remaines “1” until the request is

accepted. When the request is accepted, this bit is automatically

set to “0”.

Each interrupt request bit can be set to “0”, but cannot be set to

“1”, by software.

Interrupt Enable Bits

The interrupt enable bits control the acceptance of the corresponding interrupt requests. When an interrupt enable bit is set to

“0”, the acceptance of the corresponding interrupt request is disabled. If an interrupt request occurs in this condition, the

corresponding interrupt request bit is set to “1”, but the interrupt

request is not accepted. When an interrupt enable bit is set to “1”,

acceptance of the corresponding interrupt request is enabled.

Each interrupt enable bit can be set to “0” or “1” by software.

The interrupt enable bit for an unused interrupt should be set to

“0”.

Interrupt Source Selection

The following combinations can be selected by the interrupt

source selection bit of the AD control register (bit 6 of the address

003916).

• ADT or A/D conversion (refer Table 9)

Rev.2.02 Jun 19, 2007 page 24 of 73

REJ03B0146-0202

Page 25

3823 Group

b

b

I

I N T

i

( I N T E D G E

A

)

I

I N T

i

I

I N T

i

N

d

( I R E Q

C

)

( I C O N

E

)

I

C N T R

i

(IREQ

D16)

I

CNTR

d

(ICON

F16)

F

b7b

b7b

b

b

b7b

7

n t e r r u p t e d g e s e l e c t i o n r e g i s t e

0

: a d d r e s s 0 0 3

n t e r r u p t e d g e s e l e c t i o n b i

0

I N T

1

i n t e r r u p t e d g e s e l e c t i o n b i t

I N T

2

i n t e r r u p t e d g e s e l e c t i o n b i t

3

i n t e r r u p t e d g e s e l e c t i o n b i t

I N T

N o t u s e d ( r e t u r n “ 0 ” w h e n r e a d )

0

n t e r r u p t r e q u e s t r e g i s t e r

1 : a d d r e s s 0 0 3

n t e r r u p t r e q u e s t b i

0

1

i n t e r r u p t r e q u e s t b i t

I N T

S e r i a l I / O r e c e i v e i n t e r r u p t r e q u e s t b i t

S e r i a l I / O t r a n s m i t i n t e r r u p t r e q u e s t b i t

T i m e r X i n t e r r u p t r e q u e s t b i t

T i m e r Y i n t e r r u p t r e q u e s t b i t

T i m e r 2 i n t e r r u p t r e q u e s t b i t

T i m e r 3 i n t e r r u p t r e q u e s t b i t

r

1 6

t

a l l i n g e d g e a c t i v

0 :

e

1 : R i s i n g e d g e a c t i v e

1

1 6

7

t

0

n t e r r u p t r e q u e s t r e g i s t e r

2 : address 003

n t e r r u p t r e q u e s t b i

0

1

i n t e r r u p t r e q u e s t b i t

C N T R

2

t

T i m e r 1 i n t e r r u p t r e q u e s t b i t

I N T

2

i n t e r r u p t r e q u e s t b i t

3

i n t e r r u p t r e q u e s t b i t

I N T

K e y i n p u t i n t e r r u p t r e q u e s t b i t

A D T / A D c o n v e r s i o n i n t e r r u p t r e q u e s t b i t

N o t u s e d ( r e t u r n s “ 0 ” w h e n r e a d )

o i n t e r r u p t r e q u e s t i s s u e

0 :

1 : I n t e r r u p t r e q u e s t i s s u e d

0

nterrupt control register 1

1 : a d d r e s s 0 0 3

n t e r r u p t e n a b l e b i

I N T

0

1

i n t e r r u p t e n a b l e b i t

1 6

S e r i a l I / O r e c e i v e i n t e r r u p t e n a b l e b i t

S e r i a l I / O t r a n s m i t i n t e r r u p t e n a b l e b i t

T i m e r X i n t e r r u p t e n a b l e b i t

T i m e r Y i n t e r r u p t e n a b l e b i t

T i m e r 2 i n t e r r u p t e n a b l e b i t

T i m e r 3 i n t e r r u p t e n a b l e b i t

t

0

nterrupt control register 2

2 : address 003

0

interrupt enable bit

CNTR

1

interrupt enable bit

Timer 1 interrupt enable bit

INT

2

interrupt enable bit

3

interrupt enable bit

INT

Key input interrupt enable bit

ADT/AD conversion interrupt enable bit

Not used (returns “0” when read)

(Do not write “1” to this bit.)

0 : Interrupts disable

1 : Interrupts enabled

Fig. 17 Structure of interrupt-related registers

Rev.2.02 Jun 19, 2007 page 25 of 73

REJ03B0146-0202

Page 26

3823 Group

Interrupt Request Generation, Acceptance,

and Handling

Interrupts have the following three phases.

(i) Interrupt Request Generation

An interrupt request is generated by an interrupt source (external interrupt signal input, timer underflow, etc.) and the

corresponding request bit is set to “1”.

(ii) Interrupt Request Acceptance

Based on the interrupt acceptance timing in each instruction

cycle, the interrupt control circuit determines acceptance conditions (interrupt request bit, interrupt enable bit, and interrupt

disable flag) and interrupt priority levels for accepting interrupt

requests. When two or more interrupt requests are generated

simultaneously, the highest priority interrupt is accepted. The

value of interrupt request bit for an unaccepted interrupt remains the same and acceptance is determined at the next

interrupt acceptance timing point.

(iii) Handling of Accepted Interrupt Request

The accepted interrupt request is processed.

Figure 18 shows the time up to execution in the interrupt processing routine, and Figure 19 shows the interrupt sequence.

Figure 20 shows the timing of interrupt request generation, interrupt request bit, and interrupt request acceptance.

Interrupt Handling Execution

When interrupt handling is executed, the following operations are

performed automatically.

(1) Once the currently executing instruction is completed, an inter-

rupt request is accepted.

(2) The contents of the program counters and the processor status

register at this point are pushed onto the stack area in order

from 1 to 3.

1. High-order bits of program counter (PCH)

2. Low-order bits of program counter (PCL)

3. Processor status register (PS)

(3) Concurrently with the push operation, the jump address of the

corresponding interrupt (the start address of the interrupt processing routine) is transferred from the interrupt vector to the

program counter.

(4) The interrupt request bit for the corresponding interrupt is set

to “0”. Also, the interrupt disable flag is set to “1” and multiple

interrupts are disabled.

(5) The interrupt routine is executed.

(6) When the RTI instruction is executed, the contents of the reg-

isters pushed onto the stack area are popped off in the order

from 3 to 1. Then, the routine that was before running interrupt

processing resumes.

As described above, it is necessary to set the stack pointer and