REALTEK RTL8305S Datasheet

RTL8305S

RTL8305S

5-PORT 10/100 MBPS SINGLE CHIP

SWITCH CONTROLLER

1. Features..................................................................................................................................................................................... 2

2. General Description .................................................................................................................................................................. 2

3. Block Diagram.......................................................................................................................................................................... 3

4. Pin Assignments........................................................................................................................................................................ 4

5. Pin Descriptions........................................................................................................................................................................ 6

5.1 Media Connection Pins ....................................................................................................................................................... 6

5.2 Mode Pins ........................................................................................................................................................................... 6

5.3 Port4 Related Pins............................................................................................................................................................... 7

5.4 LED Pins............................................................................................................................................................................. 8

5.5 Power Pins .......................................................................................................................................................................... 8

5.6 Miscellaneous Pins.............................................................................................................................................................. 8

5.7 Reserved Pins...................................................................................................................................................................... 8

6. Functional Description.............................................................................................................................................................. 9

6.1 Introduction......................................................................................................................................................................... 9

6.2 Switch Core Functional Overview...................................................................................................................................... 9

6.2.1 Address Search, Learning and Aging........................................................................................................................... 9

6.2.2 Buffer Management.................................................................................................................................................... 10

6.2.3 Data Reception........................................................................................................................................................... 10

6.2.4 Data Forwarding......................................................................................................................................................... 10

6.2.5 Flow Control ...............................................................................................................................................................11

6.2.6 Back-off Algorithm.....................................................................................................................................................11

6.2.7 Inter-Frame Gap..........................................................................................................................................................11

6.2.8 Illegal Frame ...............................................................................................................................................................11

6.2.9 Broadcast Storm Control.............................................................................................................................................11

6.3 Physical Layer Functional Overview.................................................................................................................................11

6.3.1 Auto-negotiation .........................................................................................................................................................11

6.3.2 10Base-T Transmit Function.......................................................................................................................................11

6.3.3 10Base-T Receive Function ........................................................................................................................................11

6.3.4 Link Monitor...............................................................................................................................................................11

6.3.5 100Base-TX Transmit Function................................................................................................................................. 12

6.3.6 100Base-TX Receive Function .................................................................................................................................. 12

6.3.7 Power Saving Mode................................................................................................................................................... 12

6.4 LED................................................................................................................................................................................... 12

6.5 MII Port............................................................................................................................................................................. 13

6.5.1 General Description ................................................................................................................................................... 13

6.5.2 MII/SNI PHY Mode................................................................................................................................................... 16

6.5.3 MII MAC Mode......................................................................................................................................................... 16

7. Electrical Characteristics......................................................................................................................................................... 18

7.1 Absolute Maximum Ratings ............................................................................................................................................. 18

7.2 Operating Range ............................................................................................................................................................... 18

7.3 DC Characteristics (0°C<Ta<60°C, 3.15V<Vcc<3.45V) ................................................................................................. 18

7.4 AC Characteristics (0°C<Ta<60°C, 3.15V<Vcc<3.45V) ................................................................................................. 19

7.5 Digital Timing Characteristics .......................................................................................................................................... 20

7.6 Thermal Data..................................................................................................................................................................... 20

8. Application Information.......................................................................................................................................................... 21

9. System Application Diagram .................................................................................................................................................. 22

10. Mechanical Dimensions........................................................................................................................................................ 23

2002/02/19 Rev. 1.2

1

1. Features

RTL8305S

5-port integrated switch with physical layer and

transceiver for 10Base-T and 100Base-TX with

5-port 10/100M UTP or

4-port 10/100M UTP + 1-port MII/SNI

PHY mode MII/SNI interface for router application

MAC mode MII interface for HomeLAN/100Base-FX

application

1Mbit internal RAM for packet buffer

Internal 1K look-up table entries

25MHz crystal or OSC input

Supports broadcast storm filtering function

Support full duplex 802.3x flow control and half

duplex back-pressure flow control

LED indicators for link/activity, speed, full/half duplex

and collision

LEDs blinking upon reset for LED diagnostics

Unmanaged operation by strapping upon reset

Power saving with cable detection

Low power consumption at 3.3V operating voltage

128-pin PQFP package

Non-blocking wire-speed reception and transmission

Fully compliant with IEEE 802.3/802.3u

2. General Description

The RTL8305S is a highly integrated layer 2 single chip switch controller which incorporates 5 MACs (Media Access

Controller), 5 physical layer transceivers, 1-Mbit SRAM and 1K-entry look-up table into one single chip.

The RTL8305S contains 5 ports, and each one provides support for a 10Base-T (10Mbps) or 100Base-TX (100Mbps) network

connection. The fifth port (port 4) can be configured as a MII/SNI to work with a routing engine, HomePHY or a fiber

transceiver for a 100Base-FX application. And each operation mode can be easily set up by hardware strapping upon restart or

power-on.

The RTL8305S is designed for a stand-alone switch system through hardware strapping upon reset to achieve unmanaged

operation and can be easily integrated with xDSL/Cable modem router. With the least peripheral components and using a

25MHz crystal, the RTL8305S has the best system cost structure. The integrated RTL8305S chip benefits from low power

consumption and ease of use for SOHO 5-port switch or xDSL/Cable router applications.

2002/02/19 Rev. 1.2

2

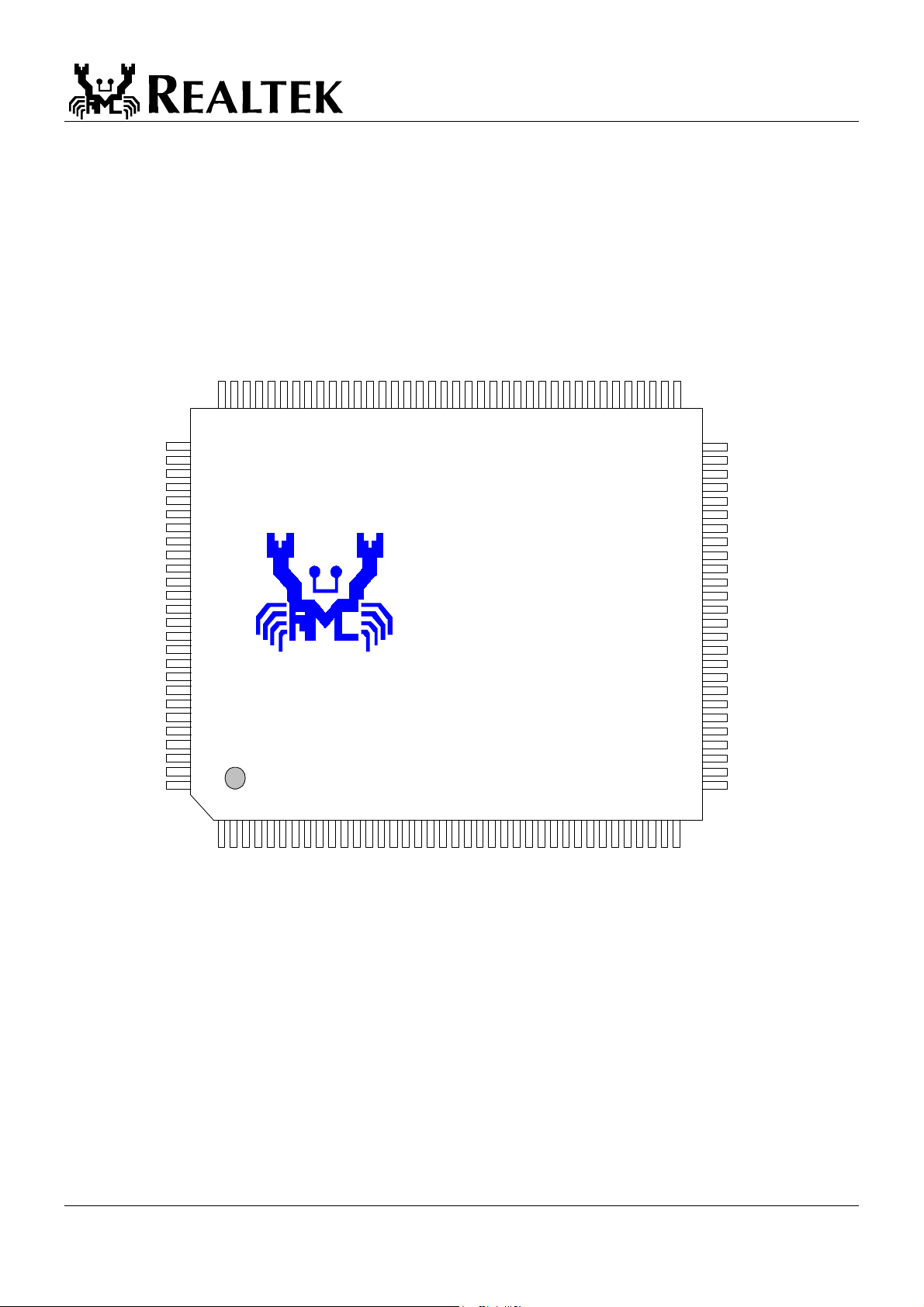

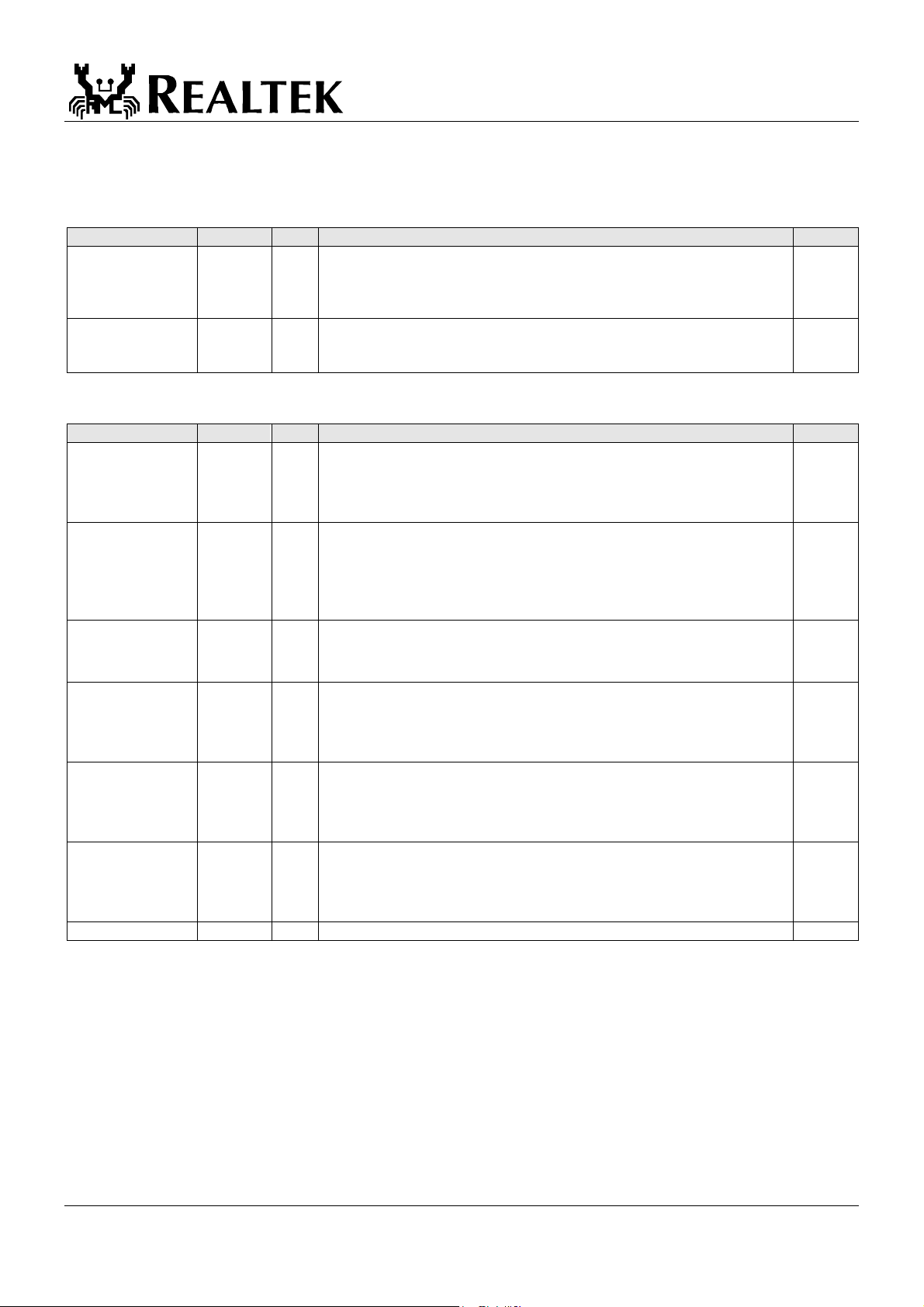

3. Block Diagram

RTL8305S

ENBRDCTRL

ENFCTRL

ENBKPRS

RESET#

NWAYHALF#

IBREF

RXIP/N[0]

TXOP/N[0]

RXIP/N[1]

TXOP/N[1]

RXIP/N[2]

TXOP/N[2]

RXIP/N[3]

TXOP/N[3]

RXIP/N[4]

TXOP/N[4]

TXC/RXC

TXEN/RXDV

TXD/RXD

RXC/TXC

RXDV/TXEN

RXD/TXD

COL

P4MODE[1:0]

Waveform

Shaping

10BASE-T/

100BASE-TX

PHYceiver

10BASE-T/

100BASE-TX

PHYceiver

10BASE-T/

100BASE-TX

PHYceiver

10BASE-T/

100BASE-TX

PHYceiver

10BASE-T/

100BASE-TX

PHYceiver

MII

MAC

mode

Out-

put

MII

PHY

mode

Revers

circuit

MAC0

MAC1

MAC2

MAC3

MAC4

Switch

Engine

0

Switch

Engine

1

Switch

Engine

2

Switch

Engine

3

Switch

Engine

4

Global functions

1K-entry

Look-up

Table

Packet Buffer

Space

Page Pointer

Space

Buffer Manager

LED

controller

X1

X2

CK25MOUT

RAMFAIL#

16K x 64 bits memory

P4LNKSTA#

P4DUPSTA#

P4SPDSTA#

P4FLCTRL#

SEL_MIIMAC#

ENP4LED

DIS_RST_BLNK#

LED_BLNK_TIME

LED_ACT[4:0]

LED_DUP[4:0]

LED_SPD[4:0]

2002/02/19 Rev. 1.2

3

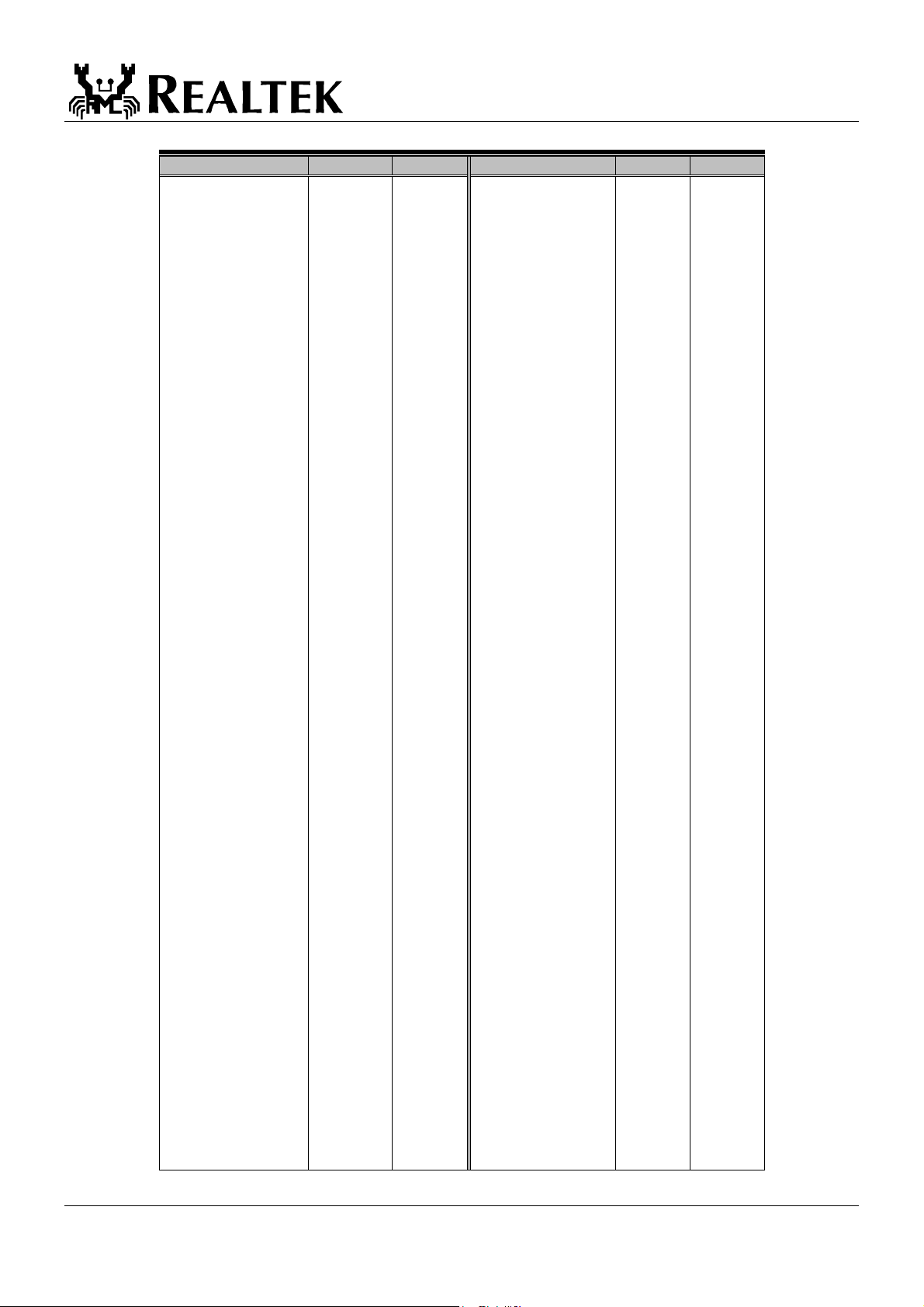

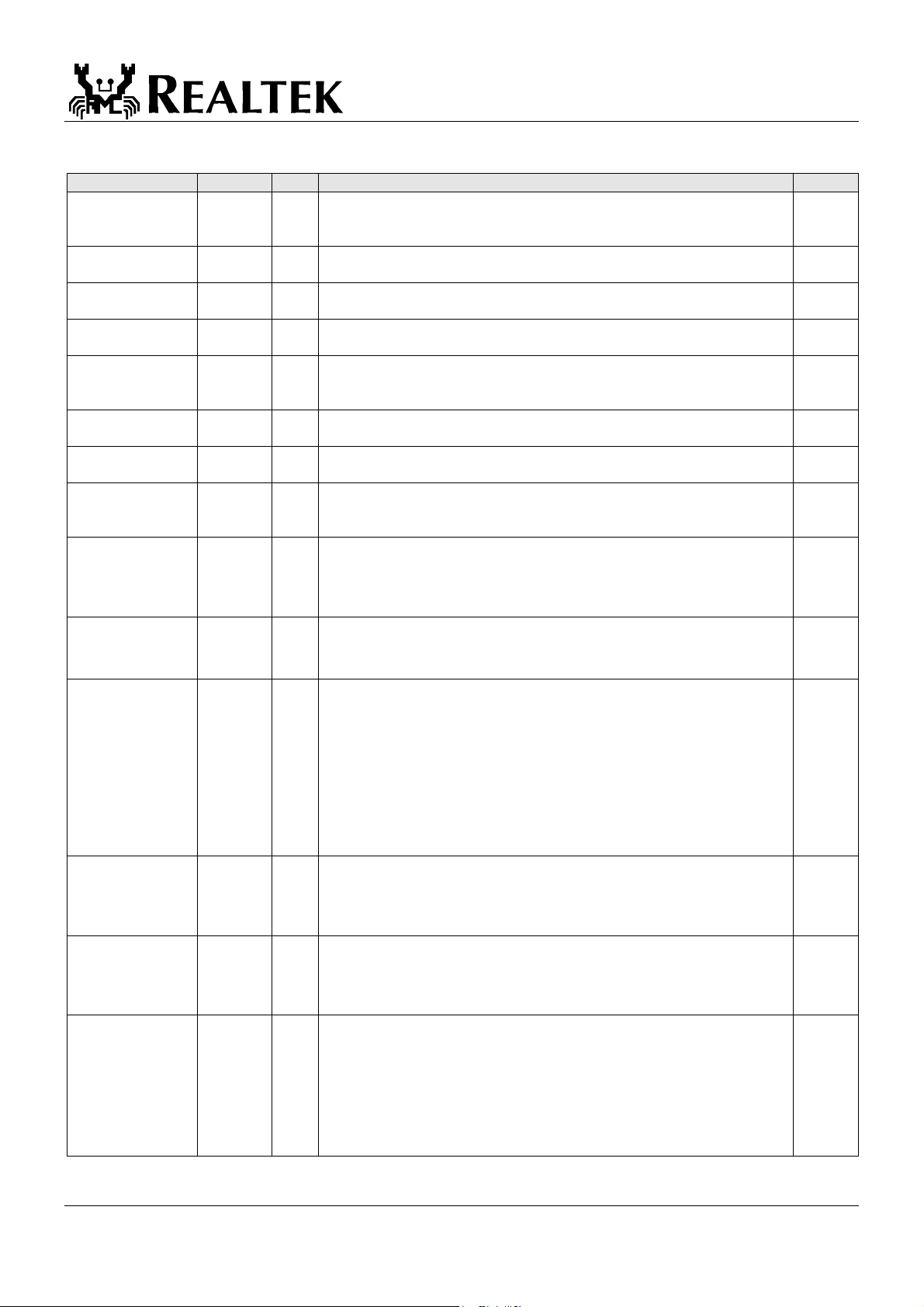

4. Pin Assignments

RTL8305S

LED_DUP[0]

LED_ACT[0]

LED_SPD[0]

VDD

LED_DUP[1]

LED_ACT[1]

LED_SPD[1]

LED_DUP[2]

LED_ACT[2]

GND

LED_SPD[2]

VDD

LED_DUP[3]

LED_ACT[3]

LED_SPD[3]

LED_DUP[4]

LED_ACT[4]

LED_SPD[4]

TEST#

GND

AGND

IBREF

AVDD

RVDD

RXIN[0]

RXIP[0]

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

GND

NC

102

101

1

2

VDD

100

3

NC

NCNCGNDNCNC

P4MODE[0]

P4MODE[1]

989799

949693

9

8

7

654

ENP4LED

DIS_RST_BLNK#

90

919592

12

13

10

11

NC

LED_BLNK_TIMENCNC

NC

89

88

VDD

NC

NC

868587

828481

ENBRDCTRL

NC

ENFCTRL

GND

ENBKPRS

78

77

798380

NWAYHALF#

NC

747375

76

RTL8305S

08042T1

050A TAIWAN

22

21

20

19

18

17

16

15

14

23

24

25

26

27

28

29

30

31

RESERVED

CK25MOUT

VDD

NCNCNC

707269

34

33

32

MRXD[3]/MTXD[3]

SEL_MIIMAC#

MRXD[2]/MTXD[2]

GND

677168

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

37

36

35

38

MGND

MRXD[1]/MRXD[1]

VDD

MRXD[0]/MTXD[0]

MRXDV/MTXEN

MRXC/MTXC

MCOL

MTXD[3]/MRXD[3]

MTXD[2]/MRXD[2]

MTXD[1]/MRXD[1]

MTXD[0]/MRXD[0]

VDD

MTXEN/MRXDV

MTXC/MRXC

GND

P4LNKSTA#

P4DUPSTA#

P4SPDSTA#

P4FLCTRL#

X2

X1

VDD

TESTDATA

TESTCLK

RESET#

GND

DD

TVDD

TGND

RGND

TVDD

TXOP[0]

TXON[0]

TVDD

TXON[1]

TGND

RGND

TXOP[1]

RVDD

RXIP[1]

RXIN[1]

RVDD

RXIN[2]

TGND

RGND

RXIP[2]

TVDD

TXOP[2]

TXON[2]

TGND

TXON[3]

TXOP[3]

RGND

RXIP[3]

RVDD

RVDD

RXIN[3]

RGND

RXIP[4]

RXIN[4]

TGND

TXOP[4]

TVDD

MVDD

TXON[4]

2002/02/19 Rev. 1.2

4

' I ' stands for inputs; 'O' stands for outputs; 'A' stands for analog; 'D' stands for digital

Name Pin No. Type Name Pin No. Type

RGND

TGND

TXOP[0]

TXON[0]

TVDD

TVDD

TXON[1]

TXOP[1]

TGND

RGND

RXIP[1]

RXIN[1]

RVDD

RVDD

RXIN[2]

RXIP[2]

RGND

TGND

TXOP[2]

TXON[2]

TVDD

TVDD

TXON[3]

TXOP[3]

TGND

RGND

RXIP[3]

RXIN[3]

RVDD

RVDD

RXIN[4]

RXIP[4]

RGND

TGND

TXOP[4]

TXON[4]

TVDD

MVDD

GND

RESET#

TESTCLK

TESTDATA

VDD

X1

X2

P4FLCTRL#

P4SPDSTA#

P4DUPSTA#

P4LNKSTA#

GND

MTXC/MRXC

MTXEN/MRXDV

VDD

MTXD[0]/MRXD[0]

MTXD[1]/MRXD[1]

MTXD[2]/MRXD[2]

MTXD[3]/MRXD[3]

MCOL

MRXC/MTXC

MRXDV/MTXEN

MRXD[0]/MTXD[0]

VDD

MRXD[1]/MTXD[1]

MGND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61,

62

63

64

AGND

AGND

AO

AO

AVDD

AVDD

AO

AO

AGND

AGND

AI

AI

AVDD

AVDD

AI

AI

AGND

AGND

AO

AO

AVDD

AVDD

AO

AO

AGND

AGND

AI

AI

AVDD

AVDD

AI

AI

AGND

AGND

AO

AO

AVDD

DVDD

DGND

I/O

DVDD

DGND

I/O

DVDD

I/O

I/O

DVDD

DGND

GND

MRXD[2]/MTXD[2]

MRXD[3]/MTXD[3]

SEL_MIIMAC#

RESERVED

VDD

CK25MOUT

NC

NC

NC

NC

NWAYHALF#

ENFCTRL

ENBKPRS

GND

ENBRDCTRL

NC

NC

NC

NC

NC

NC

VDD

NC

LED_BLNK_TIME

DIS_RST_BLNK#

ENP4LED

NC,

NC

GND

NC

NC

P4MODE[1]

P4MODE[0]

NC

VDD

NC

GND

LED_DUP[0]

LED_ACT[0]

I

LED_SPD[0]

I

VDD

LED_DUP[1]

LED_ACT[1]

I

LED_SPD[1]

O

LED_DUP[2]

I

LED_ACT[2]

I

GND

I

LED_SPD[2]

I

VDD

LED_DUP[3]

LED_ACT[3]

O

LED_SPD[3]

LED_DUP[4]

O

LED_ACT[4]

O

LED_SPD[4]

O

TEST#

O

GND

AGND

IBREF

I

AVDD

I

RVDD

RXIN[0]

I

RXIP[0]

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

RTL8305S

DGND

I

I

O

I

DVDD

O

I

I

I

DGND

I

DVDD

I

I

I

DGND

I

I

DVDD

DGND

O

O

O

DVDD

O

O

O

O

O

GND

O

DVDD

O

O

O

O

O

O

O

DGND

AGND

A

AVDD

AVDD

AI

AI

2002/02/19 Rev. 1.2

5

RTL8305S

5. Pin Descriptions

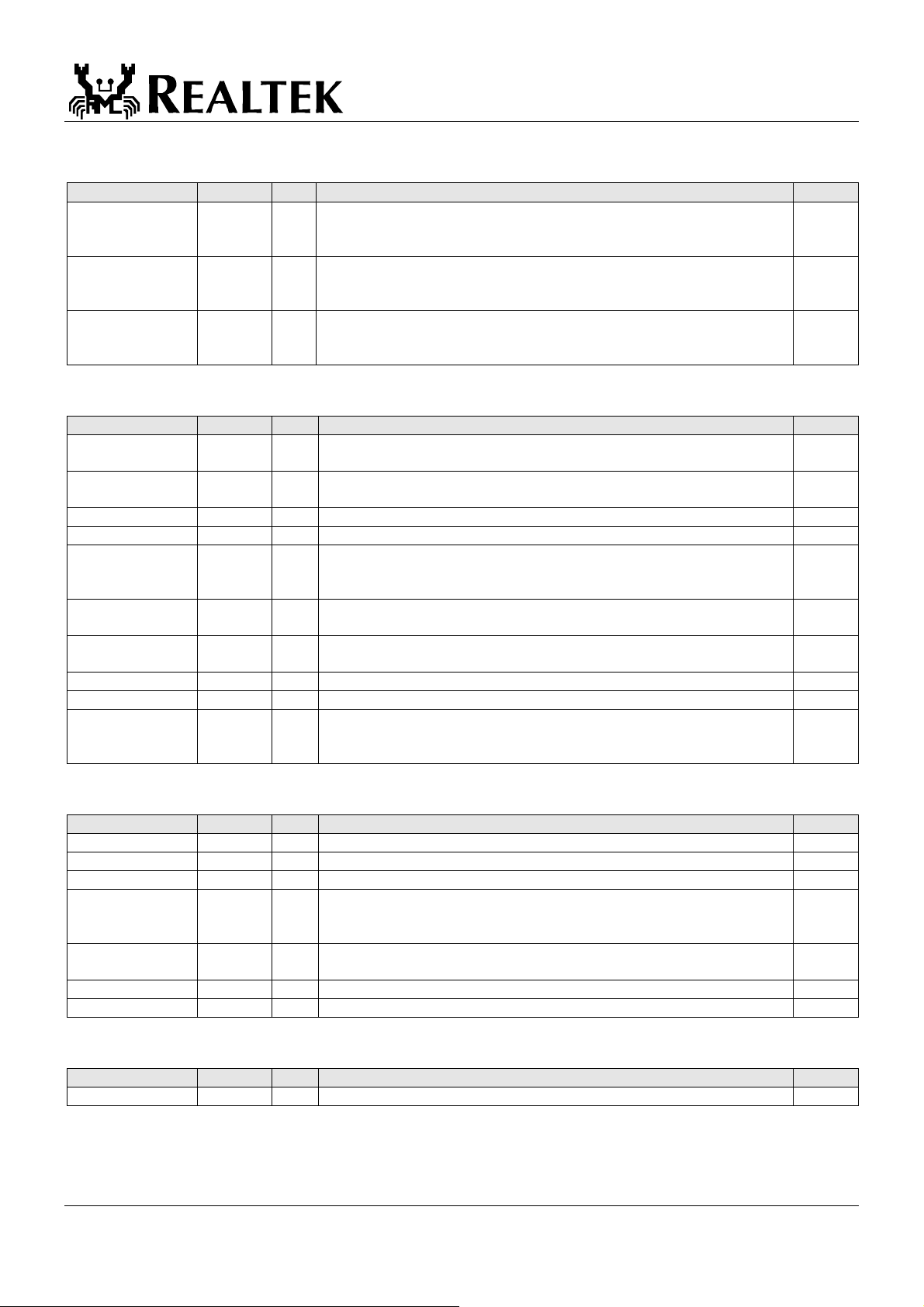

5.1 Media Connection Pins

Pin Name Pin No. Type Description Default

RXIP[4:0]

RXIN[4:0]

TXOP[4:0]

TXON[4:0]

5.2 Mode Pins

Pin Name Pin No. Type Description Default

ENBKPRS 78 I Enable Back Pressure: This pin has no effect on port4 if it is operated as

ENFCTRL 77 I Enable Flow Control: The RTL8305S will advertise its ability with flow

ENBRDCTRL 80 I Enable Broadcast Control: This is for the UTP and MII port.

LED_BLNK_TIME 89 I LED Blinking Time: This pin controls the blinking speed of the activity

DIS_RST_BLNK# 90 I Disable Reset Blinking: This pin controls the blinking of LEDs during

NWAYHALF# 76 I Nway Half Duplex: This pin advertises Nway ability to the link partner.

TEST# 121 O Te st : An internal test pin

11,12,15

16,27,28

31,32,127

128

3,4,7,8

19,20,23

24,35,36

AI

Differential Receive Data Input

AO

Differential Transmit Data Output

an MII port.

1: Enable (UTP ports only)

0: Disable

control during auto-negotiation. This pin has no effect on port4 if it is operated

as an MII port.

1: Enable Flow control (UTP ports only)

0: Disable

1: Enable

0: Disable

and collision LEDs.

1: 43ms

0: 120ms

reset and power up. Set to 0, the LEDs will not blink on reset or power up.

1: Enable

0: Disable

Setting this pin to 0 will advertise an Nway ability with 10/100 half duplex only.

1: Nway ability supports full duplex

0: Nway ability supports half duplex only

1

1

1

1

1

1

2002/02/19 Rev. 1.2

6

RTL8305S

5.3 Port4 Related Pins

Pin Name Pin No. Type Description Default

MRXD[3:0]

/MTXD[3:0]

MRXDV/MTXEN 60 I For MII MAC mode, this pin represents MRXDV, MII receive data valid.

MRXC/MTXC 59 I/O For MII MAC mode, it is receive clock, MRXC (acts as input).

MCOL 58 I/O For MII MAC mode, this pin represents collision (acts as input)

MTXD[3:0]

/MRXD[3:0]

MTXEN/MRXDV 52 O For MII MAC mode, this pin represents MTXEN, MII transmit enable.

MTXC/MRXC 51 I/O For MII MAC mode, this pin is a transmit clock, MTXC (acts as input).

P4MODE[1:0] 97,98 I Select Port 4 Operating Mode: 00: SNI PHY mode

P4LNKSTA# 49 I Port 4 Link Status: When P4MODE[1]=1 (UTP/MII MAC mode), this

P4DPXSTA# 48 I Active Low Duplex Status: 1: Half duplex

P4SPDSTA# 47 I Active Low Speed Status: 1: 10Mbps

P4FLCTRL# 46 I Active Low Flow Control Enable: When P4 is operated in UTP mode,

ENP4LED 91 I Enable Port 4 LED: In UTP applications, this pin should be floating to

SEL_MIIMAC# 68 O Select MII MAC: When P4MODE[1]=1, this pin indicates whether UTP

67,66,63

61

57,56,55

54

I For MII MAC mode, these pins are MRXD[3:0], MII receive data nibble.

For MII PHY mode, these pins are MTXD[3:0], MII transmit data nibble.

For SNI PHY mode, MTXD[0] is serial transmit data.

For MII PHY mode, this pin represents MTXEN, MII transmit enable.

For MII/SNI PHY mode, it is transmit clock, MTXC (acts as output).

For MII/SNI PHY mode, this pin represents collision (acts as output)

O For MII MAC mode, these pins are MTXD[3:0], MII transmit data nibble.

For MII PHY mode, these pins are MRXD[3:0], MII receive data nibble.

For SNI PHY mode, MRXD[0] is serial receive data.

For MII PHY mode, this pin represents MRXDV, MII receive data valid.

For MII/SNI PHY mode, this pin is a receive clock, MRXC (acts as output).

01: MII PHY mode

1x: UTP / MII MAC mode

pin decides the link status of the MII port. If both UTP and MII MAC are

linked OK, UTP has higher priority.

When P4MODE[1]=0 (PHY mode), this pin decides link status of Port4.

0: Full duplex

When P4 is operated in UTP mode, this pin has no effect.

0: 100Mbps

This pin must be kept floating for the three applications listed below.

This is because the speed is either determined by auto-negotiation or

fixed at 1M/10M Hz.

1. For UTP mode, speed is determined by the auto-negotiation procedure.

2. For HomePNA (MII MAC mode), speed is determined by RXC and

TXC from HomePHY running at 1Mbps.

3. For SNI PHY mode, speed is dedicated to 10MHz clock rate.

this pin has no effect.

1: Disable

0: Enable

drive the LEDs of port 4.

1: Drive LED pins of port4

0: Tri-state LED pins of port4

path or MII MAC path is selected.

1: UTP is selected

0: MII port is selected

While P4MODE[1]=1, the RTL8305S supports UTP/MII MAC auto-detect

function via the link status of P4 UTP and the status of P4LINKSTA# with

priority UTP over MII.

11

1

1

1

1

1

2002/02/19 Rev. 1.2

7

RTL8305S

5.4 LED Pins

Pin Name Pin No. Type Description Default

LED_ACT[4:0] 119,116

111,108

104

LED_DPX[4:0] 118,115

110,107

103

LED_SPD[4:0] 120,117

113,109

105

O Active low (Link + Activity) LED pins.

O Active low (Fullduplex + Collision) LED pins.

O Active low Speed100 LED pins.

1

1

1

5.5 Power Pins

Pin Name Pin No. Type Description Default

TVDD 5,6,21

22,37

RVDD 13,14,29

30,126

AVDD 125 P 3.3V Analog Power

MVDD 38 P 3.3V Internal RAM Power

VDD 43,53,62

70,87,100

106,114

RGND 1,10,17

26,33

TGND 2,9,18

25,34

AGND 123 P Analog GND

MGND 64 P Internal RAM GND

GND 39,50,65

79,94,102

112,122

P 3.3V Analog Transmit Power

P 3.3V Analog Receive Power

P 3.3V Digital Power

P Analog Ground

P Analog Ground

P Digital GND

5.6 Miscellaneous Pins

Pin Name Pin No. Type Description Default

X1 44 I 25MHz crystal or oscillator clock input

X2 45 O To crystal input. When using an oscillator this pin should be kept floating.

CK25MOUT 71 O 25MHz clock output

RESET# 40 I Active low reset signal. To complete the reset function, this pin must be

asserted for at least 10ms. After reset, about 30ms is needed for the

RTL8305S to complete the internal test function and initialization.

IBREF 124 A Control transmit output waveform Vpp. This pin should be grounded

through a 1.96KΩ resistor.

TESTCLK 41 I Test clock

TESTDATA 42 I/O Test data

5.7 Reserved Pins

Pin Name Pin No. Type Description Default

RESERVED 69 I This pin is reserved for internal use and should be left floating.

2002/02/19 Rev. 1.2

8

1

Loading...

Loading...