Realtek RTL8201CP Schematic [ru]

RTL8201CP

SINGLE-CHIP/SINGLE-PORT

10/100M FAST ETHERNET PHYCEIVER

(With Auto Crossover)

DATASHEET

Rev. 1.1

26 September 2003

Track ID: JATR-1076-21

RTL8201CP

Datasheet

COPYRIGHT

©2003 Realtek Semiconductor Corp. All rights reserved. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means without the written permission of Realtek Semiconductor Corp.

DISCLAIMER

Realtek provides this document “as is”, without warranty of any kind, neither expressed nor implied, including, but not limited to, the particular purpose. Realtek may make improvements and/or changes in this document or in the product described in this document at any time. This document could include technical inaccuracies or typographical errors.

TRADEMARKS

Realtek is a trademark of Realtek Semiconductor Corporation. Other names mentioned in this document are trademarks/registered trademarks of their respective owners.

USING THIS DOCUMENT

This document is intended for the software engineer’s reference and provides detailed programming information.

Though every effort has been made to ensure that this document is current and accurate, more information may have become available subsequent to the production of this guide. In that event, please contact your Realtek representative for additional information that may help in the development process.

REVISION HISTORY

Revision |

Release Date |

Summary |

1.0 |

2003/06/09 |

First release. |

1.1 |

2003/09/26 |

Minor cosmetic changes. |

|

|

Modify LED Pin behavior. |

Single-Chip/Port 10/100 Fast Ethernet PHYceiver |

ii |

Track ID: JATR-1076-21 Rev. 1.1 |

|

|

|

|

RTL8201CP |

|

|

|

|

|

Datasheet |

|

|

|

|

|

|

|

|

|

Table of Contents |

|

|

|

1. |

GENERAL DESCRIPTION ............................................................................................................................................... |

|

|

1 |

|

2. |

FEATURES .......................................................................................................................................................................... |

|

|

1 |

|

3. |

BLOCK DIAGRAM............................................................................................................................................................ |

|

|

2 |

|

4. |

PIN ASSIGNMENTS........................................................................................................................................................... |

|

|

3 |

|

5. |

PIN DESCRIPTION............................................................................................................................................................ |

|

|

4 |

|

|

5.1. |

MII INTERFACE ........................................................................................................................................................... |

|

|

4 |

|

5.2. |

SNI (SERIAL NETWORK INTERFACE) 10MBPS ONLY ................................................................................................... |

|

5 |

|

|

5.3. |

CLOCK INTERFACE ...................................................................................................................................................... |

|

|

5 |

|

5.4. |

10MBPS/100MBPS NETWORK INTERFACE ................................................................................................................... |

|

|

5 |

|

5.5. |

DEVICE CONFIGURATION INTERFACE .......................................................................................................................... |

|

|

6 |

|

5.6. |

LED INTERFACE/PHY ADDRESS CONFIGURATION ...................................................................................................... |

|

|

6 |

|

5.7. |

POWER AND GROUND PINS.......................................................................................................................................... |

|

|

7 |

|

5.8. |

RESET AND OTHER PINS .............................................................................................................................................. |

|

|

7 |

6. |

REGISTER DESCRIPTIONS............................................................................................................................................ |

|

|

8 |

|

|

6.1. |

REGISTER 0 BASIC MODE CONTROL REGISTER ........................................................................................................... |

|

|

8 |

|

6.2. |

REGISTER 1 BASIC MODE STATUS REGISTER............................................................................................................... |

|

|

9 |

|

6.3. |

REGISTER 2 PHY IDENTIFIER REGISTER 1................................................................................................................... |

|

|

9 |

|

6.4. |

REGISTER 3 PHY IDENTIFIER REGISTER 2................................................................................................................... |

|

|

9 |

|

6.5. |

REGISTER 4 AUTO-NEGOTIATION ADVERTISEMENT REGISTER (ANAR) ................................................................... |

|

10 |

|

|

6.6. |

REGISTER 5 AUTO-NEGOTIATION LINK PARTNER ABILITY REGISTER (ANLPAR)..................................................... |

10 |

||

|

6.7. |

REGISTER 6 AUTO-NEGOTIATION EXPANSION REGISTER (ANER) ............................................................................ |

|

11 |

|

|

6.8. |

REGISTER 16 NWAY SETUP REGISTER (NSR)............................................................................................................ |

|

|

12 |

|

6.9. |

REGISTER 17 LOOPBACK, BYPASS, RECEIVER ERROR MASK REGISTER (LBREMR)................................................ |

12 |

||

|

6.10. |

REGISTER 18 RX_ER COUNTER (REC) .................................................................................................................... |

|

|

13 |

|

6.11. |

REGISTER 19 SNR DISPLAY REGISTER...................................................................................................................... |

|

|

13 |

|

6.12. |

REGISTER 25 TEST REGISTER .................................................................................................................................... |

|

|

13 |

7. |

FUNCTIONAL DESCRIPTION ...................................................................................................................................... |

|

|

14 |

|

|

7.1. |

MII AND MANAGEMENT INTERFACE ......................................................................................................................... |

|

|

14 |

|

7.1.1. |

Data Transition .................................................................................................................................................... |

|

|

14 |

|

7.1.2. |

Serial Management.............................................................................................................................................. |

|

|

15 |

|

7.2. |

AUTO-NEGOTIATION AND PARALLEL DETECTION...................................................................................................... |

|

|

16 |

|

7.2.1. Setting the Medium Type and Interface Mode to MAC ........................................................................................ |

|

16 |

||

|

7.2.2. UTP Mode and MII Interface............................................................................................................................... |

|

|

16 |

|

|

7.2.3. UTP Mode and SNI Interface............................................................................................................................... |

|

|

17 |

|

|

7.2.4. Fiber Mode and MII Interface ............................................................................................................................. |

|

|

17 |

|

|

7.3. |

FLOW CONTROL SUPPORT ......................................................................................................................................... |

|

|

17 |

|

7.4. |

HARDWARE CONFIGURATION AND AUTO-NEGOTIATION............................................................................................ |

|

18 |

|

|

7.5. |

LED AND PHY ADDRESS CONFIGURATION ............................................................................................................... |

|

|

19 |

|

7.6. |

SERIAL NETWORK INTERFACE ................................................................................................................................... |

|

|

20 |

|

7.7. |

POWER DOWN, LINK DOWN, POWER SAVING, AND ISOLATION MODES ..................................................................... |

|

20 |

|

|

7.8. |

MEDIA INTERFACE..................................................................................................................................................... |

|

|

20 |

|

7.8.1. |

100Base-TX.......................................................................................................................................................... |

|

|

20 |

|

7.8.2. 100Base-FX Fiber Mode Operation .................................................................................................................... |

|

|

21 |

|

|

7.8.3. |

10Base-T TX/RX................................................................................................................................................... |

|

|

21 |

|

7.9. |

REPEATER MODE OPERATION.................................................................................................................................... |

|

|

22 |

|

7.10. |

RESET, AND TRANSMIT BIAS ..................................................................................................................................... |

|

|

22 |

|

7.11. |

3.3V POWER SUPPLY AND VOLTAGE CONVERSION CIRCUIT ...................................................................................... |

|

22 |

|

|

7.12. |

FAR END FAULT INDICATION...................................................................................................................................... |

|

|

22 |

|

|

|

|

||

Single-Chip/Port 10/100 Fast Ethernet PHYceiver |

iii |

Track ID: JATR-1076-21 |

Rev. 1.1 |

||

|

|

|

|

RTL8201CP |

|

|

|

|

Datasheet |

|

|

|

|

|

8. |

CHARACTERISTICS ...................................................................................................................................................... |

23 |

||

|

|

8.1. |

DC CHARACTERISTICS .............................................................................................................................................. |

23 |

|

|

8.1.1. |

Absolute Maximum Ratings ................................................................................................................................. |

23 |

|

|

8.1.2. |

Operating Conditions .......................................................................................................................................... |

23 |

|

|

8.1.3. |

Power Dissipation................................................................................................................................................ |

23 |

|

|

8.1.4. |

Input Voltage: Vcc................................................................................................................................................ |

23 |

|

|

8.2. |

AC CHARACTERISTICS .............................................................................................................................................. |

24 |

|

|

8.2.1. MII Transmission Cycle Timing ........................................................................................................................... |

24 |

|

|

|

8.2.2. MII Reception Cycle Timing ................................................................................................................................ |

25 |

|

|

|

8.2.3. SNI Transmission Cycle Timing ........................................................................................................................... |

27 |

|

|

|

8.2.4. SNI Reception Cycle Timing ................................................................................................................................ |

28 |

|

|

|

8.2.5. |

MDC/MDIO Timing ............................................................................................................................................. |

29 |

|

|

8.3. |

CRYSTAL CHARACTERISTICS ..................................................................................................................................... |

30 |

|

|

8.4. |

TRANSFORMER CHARACTERISTICS............................................................................................................................ |

30 |

9. |

MECHANICAL DIMENSIONS....................................................................................................................................... |

31 |

||

|

|

9.1. |

MECHANICAL DIMENSIONS NOTES............................................................................................................................ |

32 |

|

|

|

|

|

|

List of Tables |

|

Table 1. |

MII Interface ................................................................................................................................. |

4 |

Table 2. |

SNI (Serial Network Interface) 10Mbps Only.............................................................................. |

5 |

Table 3. |

Clock Interface.............................................................................................................................. |

5 |

Table 4. |

10Mbps/100Mbps Network Interface ........................................................................................... |

5 |

Table 5. |

Device Configuration Interface..................................................................................................... |

6 |

Table 6. LED Interface/PHY Address Configuration................................................................................. |

6 |

|

Table 7. |

Power and Ground Pins ................................................................................................................ |

7 |

Table 8. |

Reset and Other Pins..................................................................................................................... |

7 |

Table 9. |

Register 0 Basic Mode Control Register ...................................................................................... |

8 |

Table 10. |

Register 1 Basic Mode Status Register......................................................................................... |

9 |

Table 11. |

Register 2 PHY Identifier Register 1 ............................................................................................ |

9 |

Table 12. |

Register 3 PHY Identifier Register 2 ............................................................................................ |

9 |

Table 13. |

Register 4 Auto-Negotiation Advertisement Register (ANAR) ................................................. |

10 |

Table 14. |

Register 5 Auto-Negotiation Link Partner Ability Register (ANLPAR).................................... |

10 |

Table 15. |

Register 6 Auto-Negotiation Expansion Register (ANER) ........................................................ |

11 |

Table 16. |

Register 16 NWay Setup Register (NSR)................................................................................... |

12 |

Table 17. |

Register 17 Loopback, Bypass, Receiver Error Mask Register (LBREMR).............................. |

12 |

Table 18. |

Register 18 RX_ER Counter (REC) ........................................................................................... |

13 |

Table 19. |

Register 19 SNR Display Register.............................................................................................. |

13 |

Table 20. |

Register 25 Test Register ............................................................................................................ |

13 |

Table 21. |

Serial Management ..................................................................................................................... |

15 |

Table 22. |

Setting the Medium Type and Interface Mode to MAC............................................................. |

16 |

Table 23. |

UTP Mode and MII Interface ..................................................................................................... |

16 |

Table 24. |

UTP Mode and SNI Interface ..................................................................................................... |

17 |

Table 25. |

Fiber Mode and MII Interface..................................................................................................... |

17 |

Single-Chip/Port 10/100 Fast Ethernet PHYceiver |

iv |

Track ID: JATR-1076-21 Rev. 1.1 |

|

|

RTL8201CP |

|

|

Datasheet |

Table 26. Auto-Negotiation Mode Pin Settings |

.......................................................................................... 18 |

|

Table 27. Power Saving Mode Pin Settings................................................................................................ |

20 |

|

Table 28. Absolute Maximum Ratings ....................................................................................................... |

23 |

|

Table 29. Operating Conditions.................................................................................................................. |

23 |

|

Table 30. Power Dissipation ....................................................................................................................... |

23 |

|

Table 31. Input Voltage: Vcc...................................................................................................................... |

23 |

|

Table 32. MII Transmission Cycle Timing................................................................................................. |

24 |

|

Table 33. MII Reception Cycle Timing...................................................................................................... |

25 |

|

Table 34. |

SNI Transmission Cycle Timing ................................................................................................ |

27 |

Table 35. |

SNI Reception Cycle Timing...................................................................................................... |

28 |

Table 36. MDC/MDIO Timing................................................................................................................... |

29 |

|

Table 37. |

Crystal Specifications ................................................................................................................. |

30 |

Table 38. |

Transformer Specifications......................................................................................................... |

30 |

|

List of Figures |

|

Figure 1. |

Block Diagram............................................................................................................................. |

2 |

Figure 2. |

Pin Assignments .......................................................................................................................... |

3 |

Figure 3. |

Read Cycle................................................................................................................................. |

15 |

Figure 4. |

Write Cycle................................................................................................................................ |

15 |

Figure 5. LED and PHY Address Configuration ...................................................................................... |

19 |

|

Figure 6. |

LED Definitions ........................................................................................................................ |

19 |

Figure 7. |

MII Transmission Cycle Timing-1 ............................................................................................ |

24 |

Figure 8. |

MII Transmission Cycle Timing-2 ............................................................................................ |

25 |

Figure 9. |

MII Reception Cycle Timing-1 ................................................................................................. |

26 |

Figure 10. |

MII Reception Cycle Timing-2 ................................................................................................. |

26 |

Figure 11. |

SNI Transmission Cycle Timing-1............................................................................................ |

27 |

Figure 12. |

SNI Transmission Cycle Timing-2............................................................................................ |

27 |

Figure 13. |

SNI Reception Cycle Timing-1 ................................................................................................. |

28 |

Figure 14. |

SNI Reception Cycle Timing-2 ................................................................................................. |

28 |

Figure 15. MDC/MDIO Timing.................................................................................................................. |

29 |

|

Figure 16. |

MDC/MDIO MAC to PHY Transmission Without Collision................................................... |

29 |

Figure 17. MDC/MDIO PHY to MAC Reception Without Error .............................................................. |

30 |

|

Single-Chip/Port 10/100 Fast Ethernet PHYceiver |

v |

Track ID: JATR-1076-21 Rev. 1.1 |

RTL8201CP

Datasheet

1.General Description

The RTL8201CP is a single-chip/single-port PHYceiver with an MII (Media Independent Interface)/SNI (Serial Network Interface). It implements all 10/100M Ethernet Physical-layer functions including the Physical Coding Sublayer (PCS), Physical Medium Attachment (PMA), Twisted Pair Physical Medium Dependent Sublayer (TP-PMD), with an auto crossover detection function, 10Base-Tx Encoder/Decoder, and Twisted Pair Media Access Unit (TPMAU).

A PECL (Pseudo Emitter Coupled Logic) interface is supported to connect with an external 100Base-FX fiber optical transceiver. The chip utilizes an advanced CMOS process to meet low voltage and low power requirements. With on-chip DSP (Digital Signal Processing) technology, the chip provides excellent performance under all operating conditions.

The RTL8201CP can be used for applications such as those for a Network Interface Adapter, MAU (Media Access Unit), CNR (Communication and Network Riser), ACR (Advance Communication Riser), an Ethernet hub, and an Ethernet switch. In addition, it can be used in any embedded system with an Ethernet MAC that needs a UTP physical connection or Fiber PECL interface to an external 100Base-FX optical transceiver module.

2.Features

The Realtek RTL8201CP is a Fast Ethernet PHYceiver with selectable MII or SNI interface to the MAC chip. It provides the following features:

Pin-to-pin compatible with the RTL8201BL Supports MII and 7-wire SNI (Serial Network Interface)

10/100Mbps operation Full/half duplex operation

Twisted pair or fiber mode output Auto-Negotiation

Supports power down mode

Supports operation under Link Down Power Saving mode

Supports Base Line Wander (BLW) compensation

Supports auto crossover detection (new RTL8201CP function)

Supports repeater mode Adaptive Equalization Network status LEDs Flow control support

25MHz crystal/oscillator as clock source IEEE 802.3/802.3u compliant

Supports IEEE 802.3u clause 28; 1.8V operation with 3.3V IO signal tolerance

Low dual power supply, 1.8V and 3.3V; 1.8V is generated by an internal regulator

0.18µm CMOS process 48-pin LQFP package

Single-Chip/Port 10/100 Fast Ethernet PHYceiver |

1 |

Track ID: JATR-1076-21 Rev. 1.1 |

RTL8201CP

Datasheet

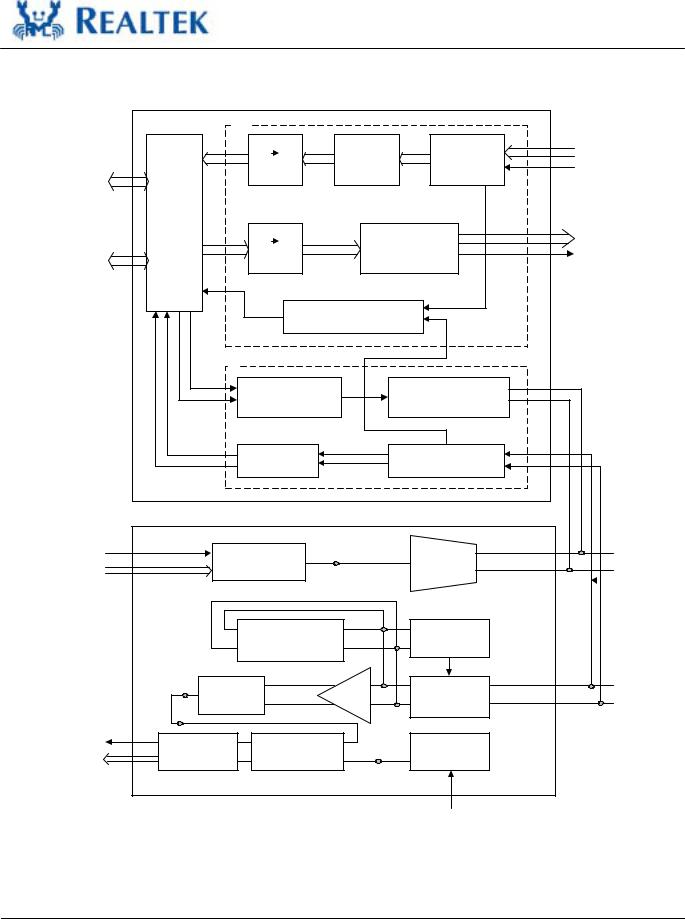

3.Block Diagram

|

|

100M |

|

|

|

|

|

|

5B 4B |

Data |

Descrambler |

RXD |

|

MII |

|

Decoder |

Alignment |

RXC 25M |

||

|

|

|||||

|

|

|

|

|

||

Interface |

10/100 |

|

|

|

|

|

|

|

|

|

|

||

|

half/full |

|

|

|

|

|

|

Switch |

4B 5B |

|

|

TXD |

|

SNI |

Logic |

Scrambler |

||||

Encoder |

TXC 25M |

|||||

Interface |

|

|

|

|

|

|

|

|

10/100M Auto-negotiation |

|

|||

|

|

|

Control Logic |

Link pulse |

|

|

|

|

|

|

|

||

|

|

10M |

|

|

|

|

|

TXC10 |

Manchester coded |

10M Output waveform |

|

||

|

TXD10 |

|

||||

|

|

waveform |

|

shaping |

|

|

|

RXC10 |

|

|

|

|

|

|

RXD10 |

Data Recovery |

|

Receive low pass filter |

|

|

TXC 25M |

|

Parrallel |

TD+ |

3 Level |

TXO+ |

|

TXD |

|

to Serial |

|

Driver |

TXO - |

|

|

|

Variable Current |

|

|

||

|

|

Baseline |

|

Peak |

|

|

|

|

wander |

|

|

||

|

|

|

Detect |

|

||

|

|

Correction |

|

|

||

|

|

|

|

|

||

|

MLT-3 |

3 Level |

Adaptive |

RXIN+ |

||

|

to NRZI |

Comparator |

Equalizer |

RXIN- |

||

RXC 25M |

Serial to |

ck |

Slave |

Master |

|

|

RXD |

Parrallel |

data |

PLL |

PPL |

|

|

|

|

|

Control |

|

|

|

|

|

|

Voltage |

|

|

|

|

|

|

|

25M |

|

|

Figure 1. Block Diagram

Single-Chip/Port 10/100 Fast Ethernet PHYceiver |

2 |

Track ID: JATR-1076-21 Rev. 1.1 |

RTL8201CP

Datasheet

4.Pin Assignments

37.ANE

38.DUPLEX

39.SPEED

40.RPTR

41.LDPS

42.RESETB

43.ISOLATE

44.MII/SNIB

45.DGND

46.X1

47.X2

48.DVDD33

AVDD33 |

|

AGND |

|

TPTX+ |

|

TPTX- |

|

PWFBOUT |

|

TPRX+ |

|

TPRX- |

|

AGND |

|

RTSET |

|

NC |

|

MDIO |

|

MDC |

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

36. |

|

35. |

|

34. |

|

33. |

|

32. |

|

31. |

|

30. |

|

29. |

|

28. |

|

27. |

|

26. |

|

25. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RTL8201CP

1. COL |

2. TXEN |

3. TXD3 |

4. TXD2 |

5. TXD1 |

6. TXD0 |

7. TXC |

8. PWFBIN |

9. LED0/ PHYAD0 |

10. LED1/ PHYAD1 |

11. DGND |

12. LED2/ PHYAD2 |

|

|

|

|

|

|

|

|

|

|

|

|

Figure 2. Pin Assignments

24.RXER /FXEN

23.CRS

22.RXDV

21.RXD0

20.RXD1

19.RXD2

18.RXD3

17.DGND

16. RXC

15.LED4/

PHYAD4

14. DVDD33

13.LED3/

PHYAD3

Single-Chip/Port 10/100 Fast Ethernet PHYceiver |

3 |

Track ID: JATR-1076-21 Rev. 1.1 |

RTL8201CP

Datasheet

5.Pin Description

LI: |

Latched Input during Power up or Reset |

O: Output |

I: Input |

IO: |

Bi-directional input and output |

P: Power |

|

5.1. MII Interface

|

|

|

Table 1. MII Interface |

Name |

Type |

Pin No. |

Description |

TXC |

O |

7 |

Transmit Clock. |

|

|

|

This pin provides a continuous clock as a timing reference for TXD[3:0] and |

|

|

|

TXEN. |

TXEN |

I |

2 |

Transmit Enable. |

|

|

|

The input signal indicates the presence of valid nibble data on TXD[3:0]. |

TXD[3:0] |

I |

3, 4, 5, 6 |

Transmit Data. |

|

|

|

The MAC will source TXD[0..3] synchronous with TXC when TXEN is |

|

|

|

asserted. |

RXC |

O |

16 |

Receive Clock. |

|

|

|

This pin provides a continuous clock reference for RXDV and RXD[0..3] |

|

|

|

signals. RXC is 25MHz in 100Mbps mode and 2.5Mhz in 10Mbps mode. |

COL |

O |

1 |

Collision Detect. |

|

|

|

COLis asserted high when a collision is detected on the media. |

CRS |

O |

23 |

Carrier Sense. |

|

|

|

This pin’s signal is asserted high if the media is not in IDEL state. |

RXDV |

O |

22 |

Receive Data Valid. |

|

|

|

This pin’s signal is asserted high when received data is present on the |

|

|

|

RXD[3:0] lines. The signal is de-asserted at the end of the packet. The signal is |

|

|

|

valid on the rising edge of the RXC. |

RXD[3:0] |

O |

18, 19, 20, 21 |

Receive Data. |

|

|

|

These are the four parallel receive data lines aligned on the nibble boundaries |

|

|

|

driven synchronously to the RXC for reception by the external physical unit |

|

|

|

(PHY). |

RXER/ |

O/LI |

24 |

Receive Error. |

FXEN |

|

|

If a 5B decode error occurs, such as invalid /J/K/, invalid /T/R/, or invalid |

|

|

|

symbol, this pin will go high. |

|

|

|

Fiber/UTP Enable. |

|

|

|

During power on reset, this pin status is latched to determine the media mode to |

|

|

|

operate in. |

|

|

|

1: Fiber mode |

|

|

|

0: UTP mode |

|

|

|

An internal weak pull low resistor, sets this to the default of UTP mode. It is possible |

|

|

|

to use an external 5.1KΩpull high resistor to enable fiber mode. |

|

|

|

After power on, the pin operates as the Receive Error pin. |

MDC |

I |

25 |

Management Data Clock. |

|

|

|

This pin provides a clock synchronous to MDIO, which may be asynchronous |

|

|

|

to the transmit TXC and receive RXC clocks. The clock rate can be up to |

|

|

|

2.5MHz. |

MDIO |

IO |

26 |

Management Data Input/Output. |

|

|

|

This pin provides the bi-directional signal used to transfer management |

|

|

|

information. |

Single-Chip/Port 10/100 Fast Ethernet PHYceiver |

4 |

Track ID: JATR-1076-21 Rev. 1.1 |

RTL8201CP

Datasheet

5.2. SNI (Serial Network Interface) 10Mbps Only

Table 2. SNI (Serial Network Interface) 10Mbps Only

Name |

Type |

Pin No. |

Description |

COL |

O |

1 |

Collision Detect. |

RXD0 |

O |

21 |

Received Serial Data. |

CRS |

O |

23 |

Carrier Sense. |

RXC |

O |

16 |

Receive Clock. |

|

|

|

Resolved from received data. |

TXD0 |

I |

6 |

Transmit Serial Data. |

TXC |

O |

7 |

Transmit Clock |

|

|

|

Generated by PHY. |

TXEN |

I |

2 |

Transmit Enable. |

|

|

|

For MAC to indicate transmit operation. |

5.3. Clock Interface

|

|

|

Table 3. Clock Interface |

Name |

Type |

Pin No. |

Description |

X2 |

O |

47 |

25MHz Crystal Output. |

|

|

|

This pin provides the 25MHz crystal output. It must be left open when an |

|

|

|

external 25MHz oscillator drives X1. |

X1 |

I |

46 |

25MHz Crystal Input. |

|

|

|

This pin provides the 25MHz crystal input. If a 25MHz oscillator is used, connect |

|

|

|

X1 to the oscillator’s output (see 8.3 Crystal Characteristics, page 30 for clock |

|

|

|

source specifications. |

5.4. 10Mbps/100Mbps Network Interface

Table 4. 10Mbps/100Mbps Network Interface

Name |

Type |

Pin No. |

Description |

TPTX+ |

O |

34 |

Transmit Output. |

TPTX- |

O |

33 |

Differential transmit output pair shared by 100Base-TX, 100Base-FX and |

|

|

|

10Base-T modes. When configured as 100Base-TX, output is an MLT-3 encoded |

|

|

|

waveform. When configured as 100Base-FX, the output is pseudo-ECL level. |

RTSET |

I |

28 |

Transmit Bias Resistor Connection. |

|

|

|

This pin should be pulled to GND by a 2KΩ (1%) resistor to define driving |

|

|

|

current for the transmit DAC. The resistance value may be changed, depending |

|

|

|

on experimental results of the RTL8201CP. |

TPRX+ |

I |

31 |

Receive Input. |

TPRX- |

I |

30 |

Differential receive input pair shared by 100Base-TX, 100Base-FX, and |

|

|

|

10Base-T modes. |

Single-Chip/Port 10/100 Fast Ethernet PHYceiver |

5 |

Track ID: JATR-1076-21 Rev. 1.1 |

|

|

|

|

RTL8201CP |

|

|

|

|

|

Datasheet |

|

|

|

|

|

|

|

5.5. Device Configuration Interface |

|||||

|

|

|

|

Table 5. Device Configuration Interface |

|

|

Name |

Type |

Pin No. |

Description |

|

|

ISOLATE |

I |

43 |

Set high to isolate the RTL8201CP from the MAC. This will also isolate the MDC/MDIO |

|

|

|

|

|

management interface. In this mode, the power consumption is minimum. This pin can be |

|

|

|

|

|

directly connected to GND or VCC. |

|

|

RPTR |

I |

40 |

Set high to put the RTL8201CP into repeater mode. This pin can be directly |

|

|

|

|

|

connected to GND or VCC. |

|

|

SPEED |

LI |

39 |

This pin is latched to input during a power on or reset condition. Set high to put |

|

|

|

|

|

the RTL8201CP into 100Mbps operation. This pin can be directly connected to GND |

|

|

|

|

|

or VCC. |

|

|

DUPLEX |

LI |

38 |

This pin is latched to input during a power on or reset condition. Set high to |

|

|

|

|

|

enable full duplex. This pin can be directly connected to GND or VCC. |

|

|

ANE |

LI |

37 |

This pin is latched to input during a power on or reset condition. Set high to |

|

|

|

|

|

enable Auto-negotiation mode, set low to force mode. This pin can be directly |

|

|

|

|

|

connected to GND or VCC. |

|

|

LDPS |

I |

41 |

Set high to put the RTL8201CP into LDPS mode. This pin can be directly connected |

|

|

|

|

|

to GND or VCC. See 7.7 Power Down, Link Down, Power Saving, and Isolation |

|

|

|

|

|

Modes, page 20, for more information. |

|

|

MII/SNIB |

LI/O |

44 |

This pin is latched to input during a power on or reset condition. Pull high to set |

|

|

|

|

|

the RTL8201CP into MII mode operation. Set low for SNI mode. This pin can be |

|

|

|

|

|

directly connected to GND or VCC. |

|

5.6. LED Interface/PHY Address Configuration

These five pins are latched into the RTL8201CP during power up reset to configure the PHY address [0:4] used for the MII management register interface. In normal operation, after initial reset, they are used as driving pins for status indicator LEDs. The driving polarity, active low or active high, is determined by each latched status of the PHY address [4:0] during power-up reset. If the latched status is High, then it will be active low. If the latched status is Low, then it will be active high. See section 7.5 LED and PHY Address Configuration, page 19, for more information.

Table 6. LED Interface/PHY Address Configuration

Name |

Type |

Pin No. |

Description |

PHYAD0/ |

LI/O |

9 |

PHY Address [0]. |

LED0 |

|

|

Link LED. |

|

|

|

Lit when linked. |

PHYAD1/ |

LI/O |

10 |

PHY Address [1]. |

LED1 |

|

|

Full Duplex LED. |

|

|

|

Lit when in Full Duplex operation. |

PHYAD2/ |

LI/O |

12 |

PHY Address [2]. |

LED2 |

|

|

10 ACT LED. |

|

|

|

Blinking when transmitting or receiving data in 10Base-T mode. |

PHYAD3/ |

LI/O |

13 |

PHY Address [3]. |

LED3 |

|

|

ACT LED. |

|

|

|

Blinking when transmitting or receiving data at 100Base-T or Fiber Mode. |

PHYAD4/ |

LI/O |

15 |

PHY Address [4]. |

LED4 |

|

|

Collision LED. |

|

|

|

Blinks when collisions occur. |

Single-Chip/Port 10/100 Fast Ethernet PHYceiver |

6 |

Track ID: JATR-1076-21 Rev. 1.1 |

RTL8201CP

Datasheet

5.7. Power and Ground Pins

|

|

|

Table 7. Power and Ground Pins |

Name |

Type |

Pin No. |

Description |

AVDD33 |

P |

36 |

3.3V Analog power input. |

|

|

|

3.3V power supply for analog circuit; should be well decoupled. |

AGND |

P |

29, 35 |

Analog Ground. |

|

|

|

Should be connected to a larger GND plane. |

DVDD33 |

P |

14, 48 |

3.3V Digital Power input. |

|

|

|

3.3V power supply for digital circuit. |

DGND |

P |

11, 17, 45 |

Digital Ground. |

|

|

|

Should be connected to a larger GND plane. |

5.8. Reset and Other Pins

|

|

|

Table 8. Reset and Other Pins |

Name |

Type |

Pin No. |

Description |

RESETB |

I |

42 |

RESETB |

|

|

|

Set low to reset the chip. For a complete reset, this pin must be asserted low |

|

|

|

for at least 10ms. |

PWFBOUT |

O |

32 |

Power Feedback Output. |

|

|

|

Be sure to connect a 22uF tantalum capacitor for frequency compensation and |

|

|

|

a 0.1uF capacitor for noise de-coupling. Then connect this pin through a |

|

|

|

ferrite bead to PWFBIN (pin8). The connection method is outlined in |

|

|

|

7.11 3.3V Power Supply and Voltage Conversion Circuit, page 22.. |

PWFBIN |

I |

8 |

Power Feedback Input: see the PWFBOUT description above. |

NC |

|

27 |

Not Connected. |

Single-Chip/Port 10/100 Fast Ethernet PHYceiver |

7 |

Track ID: JATR-1076-21 Rev. 1.1 |

Loading...

Loading...