!ladleIhaeK

•

ervlce

TRS-BO®

DISK/VIDEO

[AND

EXPANSION

Catalog Numbers:

l'

•

1

,

INTERFACE

FLOPPY

DISK

26-3806/3807

DRIVE

UNIT)

..

.;-:

'"

CUSTOM MANUFACTURED FOR RADIO SHACK. A DIVISION OF TANDY CORPORATION

Contents

"ill

1IINTRODUCTION

GENERAL.

SYSTEM OVERVIEW . . • . . . . . . . . . . . . . . . . . . . . . • • . . . . . . . . • • • . . . . . . . . • . . .

SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . . • • . . . . . . . . . . • . . . . . . . . . . . . . . 1-4

. . . . . . . . • . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . • • . . 1-1

2/DISASSEMBLY INSTRUCTIONS. . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . .

TOP CASE

MAIN P.C. BOARD

POWER SUPPLY P.C. BOARD

DISK DRIVE UNIT

FRONT PANEL ASSEMBLY

.................................•••........••.........

...........................•.........•.•...........

......•..................•.•.........•......

..................•••.........••.................•.

...........•..................................

3/PREVENTIVE MAINTENANCE . . . . . .. . . . . . . . . . . . .. . . . . . . . . . . . . . .

ADJUSTMENT

SYSTEM CLOCK

POWER SUPPLY

....•..............................•.•.......•.......

........••......................................

4/THEORY OF OPERATION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

CPU

...........................•.........••........•.........•..

ADDRESS DECODING AND BANK SELECTION CIRCUIT

MEMORY MAP

I/O

MAP

CLOCK GENERATOR CIRCUIT 4-5

SYSTEM BUS INTERFACE CIRCUIT

CRT INTERFACE AND CONTROL CIRCUIT

FLICKER SUPPRESSING CIRCUIT . . . . . . . . . . . . . . . . . • • • . . . . . . . . . . . . . . . . . • • . 4-11

FDD

INTERFACE SIGNALS

FDD

CONTROL CIRCUIT. . . . . . . . . . • . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

POWER

SUPPLY

....•...............................•................

.....•.........•..........••.........•........••.........

...........•••........••.........•......

........•............•..................••..

AND RESET CIRCUIT

............................••.......

..

..

..

1-1

1-2

2-1

2-1

2-1

2-1

2-2

2-2

3-1

3-1

3-1

3-2

4-1

4-2

4-3

4-3

4-4

4-6

4-8

4-11

4-13

4-16

5/TROUBLESHOOTING .. . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . .

TROUBLESHOOTING FLOWCHART

CHECKING PROCEDURE

....................•..........•........•......

6/EXPLODED VIEW AND PARTS

EXPLODED VIEW

ELECTRICAL PARTS LIST

MECHANICAL/ASSEMBLY PARTS. . . . . . . . . . . . . . . . • • . . . . . . . . . . . . . . . . . . . . . .

7/P.C.

APPENDIX

BOARD

MAIN P.C. BOARD ,

MAIN P.C. BOARD -- REVISED

POWER SUPPLY P.C. BOARD

SCHEMATIC DIAGRAM

AI

•..................................................

VIEWS AND SCHEMATIC DIAGRAM 7-1

....................••.........•..........•.....

INSTALLATION OF ADDITIONAL DISK DRIVE

.....•..................................

LIST.

......•......

.••..........•........••...................

...............................••...........

UNIT.

APPENDIX B/CONNECTOR PIN ASSIGNMENTS. . . . . . . . . . . . . . . . . . . .

SYSTEM BUS CONNECTOR

RF

MODULATOR

..............................••...................•

..

..

5-1

5-1

5-2

6-1

6-1

6-2

6-13

7-1

7-3

7-5

7-6

A-1

B-1

B-1

B-2

APPENDIX C/SERVICING THE FDD UNIT" """""" """"" """" """"" """" """

PART1"MECHANICAL

1-1 INSTALLATION/REMOVALOFCOMPONENTS" " " " " " _ " " " " " " " " " " " " " " " " " " " "

1-2 ADJUSTMENT" " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " C-7

1-3 SPECIAL MAINTENANCE TOOLS" " " " " " " "__" " " _" " " " " " " " " " " " " " " " " " " "

1-4 MAINTENANCE" " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " "

PART2"ELECTRICAL SECTION" " " " " " " " " " " " " " " " _ " " " " " " " " " " " " " " " " " " " " " " " "

2-1

GENERAL DESCRIPTION" " " " " " "

2-2 BLOCK

2-3

ELECTRICAL DIAGRAM" "__" " " " " " " " " " " " " " " " " " " "__" " " " " " " " " " _ " " _

2-4

INDEPENDENT LSI CONRGURATION " " " " " " " " " " " " _ " " _• " " " " " " " _ " " " " . " C-19

2-5 INPUT SIGNAL LINES (CPU TO FDD) "

2-6 OUTPUT SIGNAL LINES

PART3"CIRCUIT DlAGRAM_ " " " " " " . " " " " " " " " " " "..".." " " " " " " " " " " " " " "

PART4"TROUBLESHOOTING" " " " " " " " " ".•__

4-1 PROCESSING SOFT

4-2

FLOPPY DISK

4-3

TROUBLESHOOTING

PART5"EXPLODED VIEW AND PARTS LIST. " . " " " . " " " . " ".." " " " " " "

PART 6. SPECIAL MAINTENANCE TOOLS " " " " " " " " " " . " " " " " " " " " " " " " . " " " " " " " " . C-57

SECTION"

DIAGRAM"

DRIVE

" " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " " "

"""""

" " " " " " " "__" " " " " " " " " " " " " " " " " "__" " " " " " " " " " " " C-17

(FDD

TO CPU)

ERRORS"

FOR

PROCEDURES"

" " ".." " " _" " " " " " " " " " _" " " " "..".." " " " "

REPAIR" " " " " . " " " " " " " "__" _" " " " " " " " " " " " " " "

""""""

.....

"""""""""""""""""""""""

" " "__" " " " " " " " " " " • " " • ".." " " " "

" " " " " ".." _" _"__" " " " " ".." " " " "••" C-37

__

" " " " " " "

" " " " " " " " " " ".." " . " " " _" " _" "

""""""

...

" " " " " " C-17

•."...

" " " " " " " " C-47

C-1

C-1

C-1

C-15

C-15

C-1"7

C-1

C-23

C-29

C-33

C-35

C-35

C-36

B

Note: The expansion drive unit (Radio Shack Catalog Number 26-3807)isexactly

of

the

DiskNideo

Interface. When servicing

the

26-3807, refertothe

drive unit

the

sameas

portionofthis service manual.

the

built-in drive unit

j,

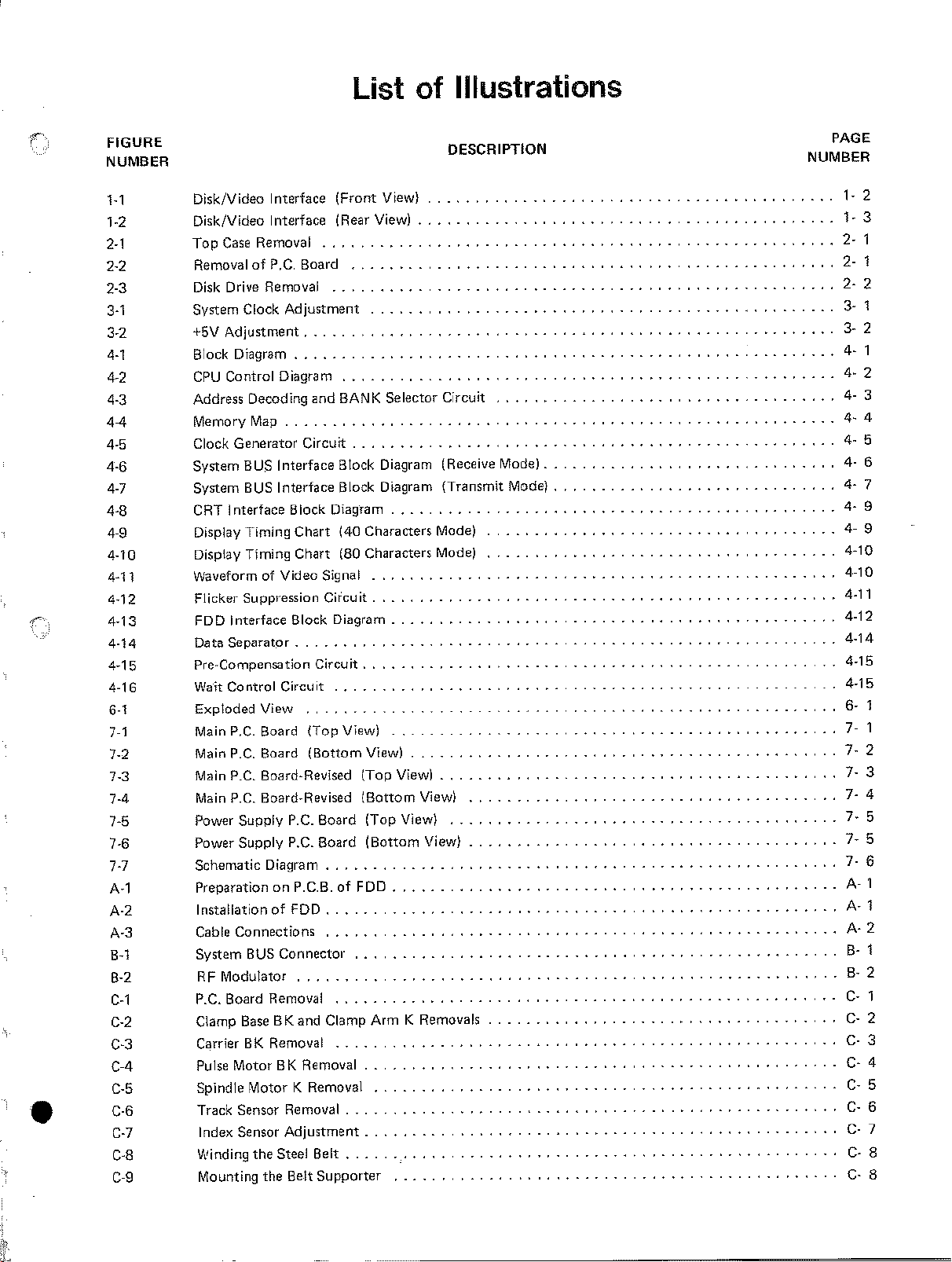

List

of

Illustrations

•

FIGURE

NUMBER

H

1-2

2-1

2-2

2-3

3-1

3-2

4-1

4-2

4-3

4-4

4-5

4-6

4-7

4-8

4-9

4-10

4-11

4-12

4-13

4-14

4-15

4-16

6-1

7-1

7-2

7-3

7-4

7-5

7-6

7-7

A-l

A-2

A-3

8-1

8-2

C-l

C-2

C-3

C-4

C-5

C-6

C-7

C-8

C-9

DESCRIPTiON

Disk/Video

Disk/Video

Top

Case

Removal

Disk Drive Removal .

System

+5V

Block Diagram .

CPU

Address Decoding and

Memory

Clock Generator

System

System BUS Interface Block Diagram

CRT

Display

Display

Waveform

Flicker

FDD

Data

Pre-Compensation

Wait

Exploded

Main

Main

Main P.C. Board-Revised

Main P.C. Board-Revised

Power

Power

Schematic Diagram

PreparationonP.C.B.ofFDD

InstallationofFDD

Cable

System BUS Connector .

Modulator

RF

P.C. Board Removal .

Clamp

Carrier

Pulse

Spindle

Track

Index Sensor

Winding

Mounting

Interface

Interface (Rear

Removal .

of

P.C. Board <

Clock

Adjustment

Adjustment.

Control

Interface

Interface

Separator.

Control

P.C.

P.C.

Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Map.

BUS

Interface

Timing

Timing

of

Video

Suppression

Circuit

View

Board

Board

Supply

Supply

Connections .

BaseBKand Clamp

BK

Removal

Motor

BK Removal

Motor

Sensor Removal .

Adjustment

the

Steel

the

(Front

View}

View)

. . . . . . . . . . . . . . . . . .

••••••••••••••••••••••••••••••••••••••••••••••••••

. .

..

. < • •

BANK

Selector

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Circuit.

Block

Chart

Chart (80 Characters Mode) . . . . . . . . . .

Block

. . . . . . . . . . . . . . . . . . . . . .

(Top

(Bottom

P.C. Board

P.C. Board

. . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Block

Diagram (Receive

Diagram .

(40 Characters Mode) . .

Signal . .

Circuit.

Diagram.

Circuit.

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . .

View)

View)

(Top

(Bottom

(Top

(Bottom

. . . . . . . . .

Arm

..

Circuit

{Transmit

. . . . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . . . . . . . . .

View)

. . . . . . . . . . . . . . . . . . . . . .

View)

View)

View)

K Removals . . . . . . . . . . . . . . . . . .

. . . . . .

. . . . . . . . . .

. .

••••••••••••••••••••••••••••••••••••••

Mode).

. . . . . . . . . . . . . . .

..

. . . . . . . . . . . . . . . . . . . . . . .

Mode} .

. . . . . . . . . . . .

..

< • • • •

..

. . . . . . .

. .

..

. .

. . . . . . . . .

•••••••••••••••••••

. .

.

.............................................

K Removal . .

.

Belt

Belt

Supporter

.

.

NUMBER

PAGE

1-

1- 3

2- 1

2-

2-

3-

3-

4- 1

44-

.

44-

44-

4-

4- 9

4-10

4-10

4-11

4-12

4-14

4-15

4-15

6-

7- 1

7- 2

7-

7- 4

.

7- 5

.

7- 5

7-

A-

A- 1

A- 2

8- 1

8-

C-

C-

C-

C-

CC-

C-

C-

C-

2

1

2

1

2

2

3

4

5

6

7

9

1

3

6

1

2

1

2

3

4

5

6

7

8

8

FIGURE

NUMBER

DESCRIPTION

PAGE

NUMBER

C-lO

C-1l

C-12

C-13

C-14

C-15

C-16

c-n

C-18

CC-20

C-2l

C-22

C·23

C-24

C-25

C-26

C-27

C-28

C-29

C-30

C-31

C-32

C·33

C-34

C-35

C-36

C-37

C·38

C-39

CAD

C-41

C-42

C-43

C-44

CA5

CA6

C-47

19

Mounting

Tensioning

Confirmationofthe

Fixing

WaveformofIndex Pulse.._ 0

WaveformofHead

Motor

Track00Adjustment

Interrupter

Block Diagram

Electrical Diagram

Pin

Block DiagramofControl

Pin

Block DiagramofRead

Block DiagramofDrive"Select

Side

the

Pulse

Motor

the

Belt.

_ 0

Belt

Gaps

the

Track00Stopper

Output

Speed

Adjustment.

. 0

•••••••

Timing

0.....

Chart

...

0 0 • • • • • 0

ConfigurationofControl

ConfigurationofRead

LSI

Select

Circuit

...

0 0

K . 0 0

...

..

0 0 • • • • • • • 0

•••••••••

. . . .

0

0 0

•••••••••••

...

•••

0 0

•••••••••••

•••••••

0 0 • • 0

0

.....

0

•••••

0••0

••••••••••••••••

LSI.

LSI.

LSI

Circuit.

••••••••••••

0 0 • •

. . . 0

•••••

••••••••••••

Head Positioning Circuit 0 0

Timing

Write Circuit

Timing

Timing

Data

Motor

Chart

for

and

Chart

for

Chart

for

Recording

ON Circuit 0

the

Direction

Erase Circuit

and

.....

Step

Write Circuit

Erase Circuit 0 _ • 0 • 0

Procedure

•••

0

•••••

0

••

Signal

0 0

••

Index Circuit

of

TP2-4

Waveform

Track00Detection

WaveformofTP2-2Pin

Protect

Write

Read

Amplifier

Timing

Chart

Circuit Diagram

Test

System

Exploded

Exploded

Exploded

PoCo

Special

ViewofMain Unit . . . 0

ViewofClamp BaseBKand

ViewofPulse

Board.

Meintenance

Pin . 0

Circuit 0

Circuit

for

Circuit

Read

0.....

....

..

Amplifier

• • 0

Hook-up

Motor

. . . . 0 • 0

Tool.

0

.

0

0

•••••••

Circuit

0

_ .

. 0

Carrier A

BK.

. 0 • • • • • 0 • • • •

••

0 0 _ • 0

0

••••

0

0••0••0••0

0

•••••••••••••

••••••

0 0

••••

0 0 0

••••

0 0••0

0 0••0

••

••••

0

••••••••••

0

••••

0 0

0 0••0 • • 0

0

•••

0 • • • • • • • • • • • • • • • • 0••0

•••••••

...

•••••••

•••••••

••••

•••••

0••0 • 0 • • • • • 0

0 0••0

0

•••••••

0

••••

..

•••••

0 0

•••••••••

•••••

0

••

0

0••0

•••••••

0

•••••

••••

0 0

••••

••

0 • • • • • 0

0 0 • • • • • • •

0 0 • 0

••••

0

0

0

•••••

••••

0 • 0

0 • 0

•••••

••

•••

0 0

0

0

•••••••

••••

•••

0 0

•••••••

o.

0

••••••

••••

0

0

0 0

0••0

•••••••••

•••••••

•••••

•••••

c· 9

C· 9

C·10

••••

C-l0

C-"

C-ll

C-

12

C-

13

C-14

c·n

C-18

C-19

C-20

C-22

0

C-22

•••••

0

•••

0

C-23

•••

C-23

C-24

C-25

C-26

C-26

C-27

C-27

C-28

C-29

C-29

C-29

C-30

C-3l

C·31

C-32

C-33

C-36

CA7

C-48

C·49

C-50

C-57

List of Tables

TABLE

NUMBER

4-1

4,2 Signals from

4-3

4-4

4-5

4-6 Descriptionofthe

B-1

Col

I/O Port Description 4· 4

the

PPI

Function

Functionofthe

FDG

Function Table ' 4-13

System Bus Connector Pin Assignments

Pin AssignmentsofControl

Table 4- 7

DESCRIPTION

PAGE

NUMBER

Portable Computer 4- 6

Principal Signals _ 4- 8

Principal Terminals . . . . . . . . . . . . . . . . 4-13

..

. . . . . . . . . . . . . S- 1

LSI.

. . . . . . . . . . . . . . . . . . . . . . . .

C-21

1/lntroduction

This manualisprepared for

of

this manual should be acquainted

Controller) and M5W1793·02P FDG

This manual consistsofseven sections and three appendices:

• The Introduction gives general information on

etc.

• Section 1 describes disassembly procedures.

• Section 2 describes preventive maintenance and adjustment.

• Section 3 describes general theory

• Section 4 describes how to troubleshoot

• Section 5 provides a parts list and an exploded view

• Section 6 provides schematics,

Interface.

• Appendix A provides instructionsfor installing an additional disk drive unit.

• Appendix B provides technical information for connector signals.

• Appendix C provides service information on

the

TRS-80 Disk/Video Interface technicians workinginthe

with

Z-80 CPU, 8255

(Floppy

of

P.C.

Disk

Controller).

the

the TRS-80 Disk/Video Interface operation.

the

TRS-80 DisklVideo Interface.

board diagrams and silk screen viewofthe

the

built-in FDD unit.

PPI

(Programmable Peripheral Interface), HD6845S CRTe

TRS"80 Disk/Video Interface suchasspecifications,

of

the

TRS·80 Disk/Video Interface.

General

field or repair centers. The user

s~itch

P,C.

boardsofthe

TRS-80 DisklVideo

{CRT

functions,

By

utilizing

of

the

The TRS-80 DisklVideo Interface consists

• Interface circuit; Transfers data and commands to

• Floppy disk drive unit: Drives 5-1/4 inch single-sided, double density floppy disk.

• Floppy disk controller (FDC): Controls driving

e Central processing unit (CPU) and memory; Controls interface circuit, floppy disk controller and CRT controller.

To connect

Install

side of the

connector located on

the

TRS-80 DisklVideo Interface with

TRS-80 Portable Computer.

of:

the

TRS-80 Disk/Video Interface to

the

adapter socket provided with

TRS-80 Portable Computer. Connect one sideofthe cable to

the

bottom

sideofthe

the

Disk/Video Interface.

the

TAS·80 Portable Computer,

the

TAS-80 Portable Computer.

of

the

floppy disk drive unit.

the

Portable Computer, use

Disk/Video Interface on

the

user can fully realize

the

connector cable supplied as an accessory.

the

System Bus Connector locatedonthe

the

adapter socket and

the

other

the

capabilities

sidetothe

bottom

same

•

1-1

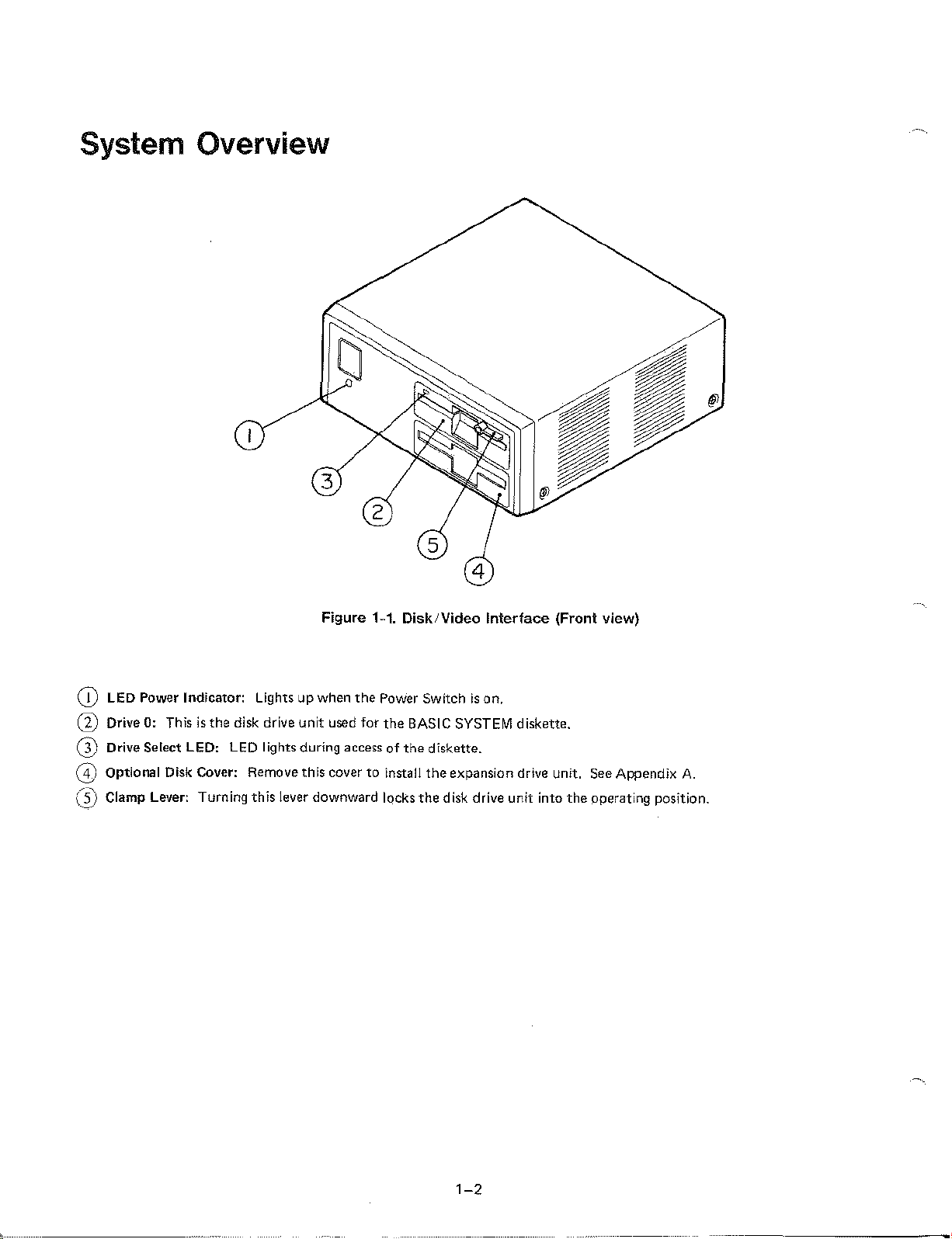

System Overview

Figure 1-1. Disk/Video Interface (Front view)

CD

LED

Power Indicator: Lights up when

mDrive 0: This

(})

Drive Select LED: LED lights during accessofthe

CD

Optional Disk Cover: Remove this covertoinstall

is

the

disk drive unit used for

the

Power Switch

the

o Clamp Lever: Turning this lever downward locks

is

on.

BASIC SYSTEM diskette.

diskette.

the

expansion drive unit. See Appendix

the

disk drive unit into

the

A.

operating position.

1-2

4

5

6

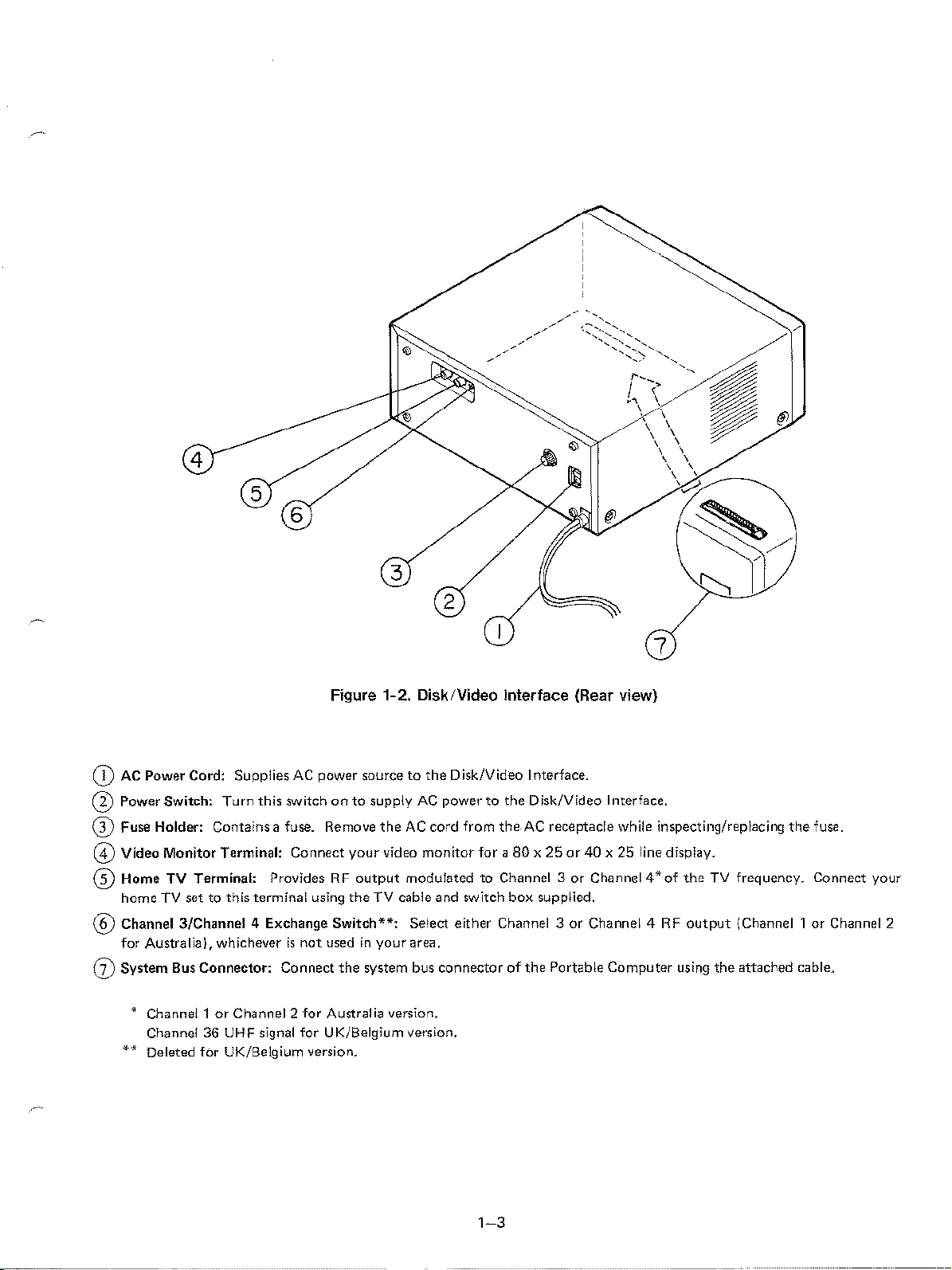

Figure 1-2. DiskiVideo Interface (Rear view)

CD

AC Power Cord: Supplies AC power sourcetothe

G)

PowerSwitch:

CD

Fuse Holder: Contains a fuse. Remove

(±)

Video

Monitor

G)

Home TV Terminal: ProvidesRFoutput

TV

home

@)

Channel 3/Channel 4 Exchange

for Australia), whicheverisnot

(j) System Bus Connector: Connect

Turn

this switchonto supplyACpower to the Disk/Video Interface.

Terminal:

set to this terminal using

Connect

usedinyour

your

theTVcable and switch box supplied.

Switch*"':

the

system bus connectorofthe

3

2

Disk/Video

theACcord from

video

monitor

modulated to Channel 3orChannel 4*ofthe

Select either Channel 3 or Channel 4 RF

area.

for a80x25or40x25line display.

Interface.

theACreceptacle while inspecting/replacing

Portable Computer using

7

the

fuse.

TV

frequency. Connect your

output

(ChannellorChannel 2

the

attached cable.

~

Channel 1orChannel 2 'for Australia version.

Channel 36 UHF signal for UK/Belgium version.

""_.

Deleted for UK/Belgium version.

1-3

Specifications

Operating Voltage:

Power

Consumption:

Operating

Operating Humidity Range:

Dimensions(Wx H x O):

Weight:

Disk

Spindle

Seek Time

Average Access Time

Motor Starting Time

Data Density

Track Density

Number

NumberofSectors

Bytes/Sector

CRT

Display Mode

Display

RF

Modulation

Output

Horizontal Scanning Frequency

Vertical Scanning Frequency

Drive:

j nterface;

Output

RF

Output

Temperature

Rotation

of

attribution

Speed

Tracks

Channel

Ratio

Impedance

Level

Range:

120

Volts AC for USA

220

VoltsACfor

240

VoltsACfor UK and Australia

66

Watts

~

40°C

S"C

20to80%

430x125x300

8 kg

(17.7lbs)

and

Canada

Belgium

mm

(16-15/16"x4-15/16"x11-10/12")

Single,sided, double density

300 R.P.M.

6 msec.

88

msec.

500

msec.

5536

B.P.I.

48

T.P.1.

40

18

256

Bytes

40 columns x 25 linesor80 column x25lines

Normal,

VHF3or

VHF1or

UHF36channel

75%

75 ohms

62.5

15.625

60.1 Hz

Typ.

dBti

Blink,

4 channel

2 channel

(67.3

kHz

ReverseorReverse

for

USA/Canada

for

Australia

for

UK/Belgium

dBf)

Typ.

and

Blink

1-4

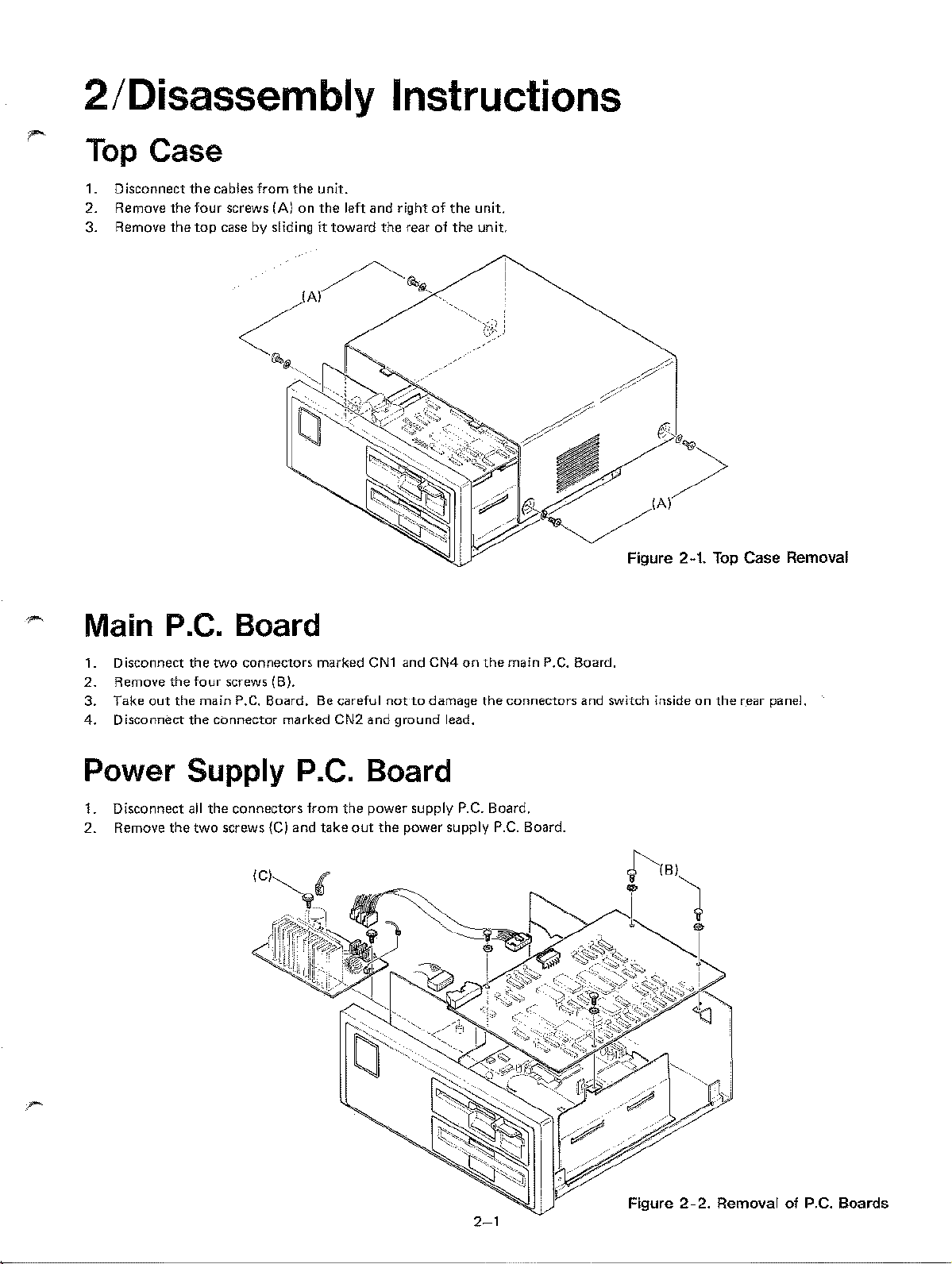

2/Disassembly Instructions

Top Case

1. 0 isconnect

2. Remove

3. Remove

the

the

Main P

the

cables from

four

screws (A)onthe

top

case by slidingittoward

.C.

Board

the

unit.

left

and

rightofthe

the

rear of

the

unit.

unit.

Figure 2

-1.

Top

Case Removal

1. Disconnect the two connectors marked eN1 and CN4onthe

2. Remove the

3.

Take

4. Disconnectthe connector marked CN2 and ground lead.

out

four

screws (B).

the

main P,C. Board. Be careful

nottodamage

the

Power Supply P.C. Board

1. Disconnect

2. Remove

all

the

two screws

the

connectors from

{C)

and take

the

power supply P.C. Board.

out

the

power supply

main P.C. Board.

connectors

P.C.

Board.

and

switch insideonthe

rear panel.

2-1

Figure

2-2.

Removal of

P.C.

Boards

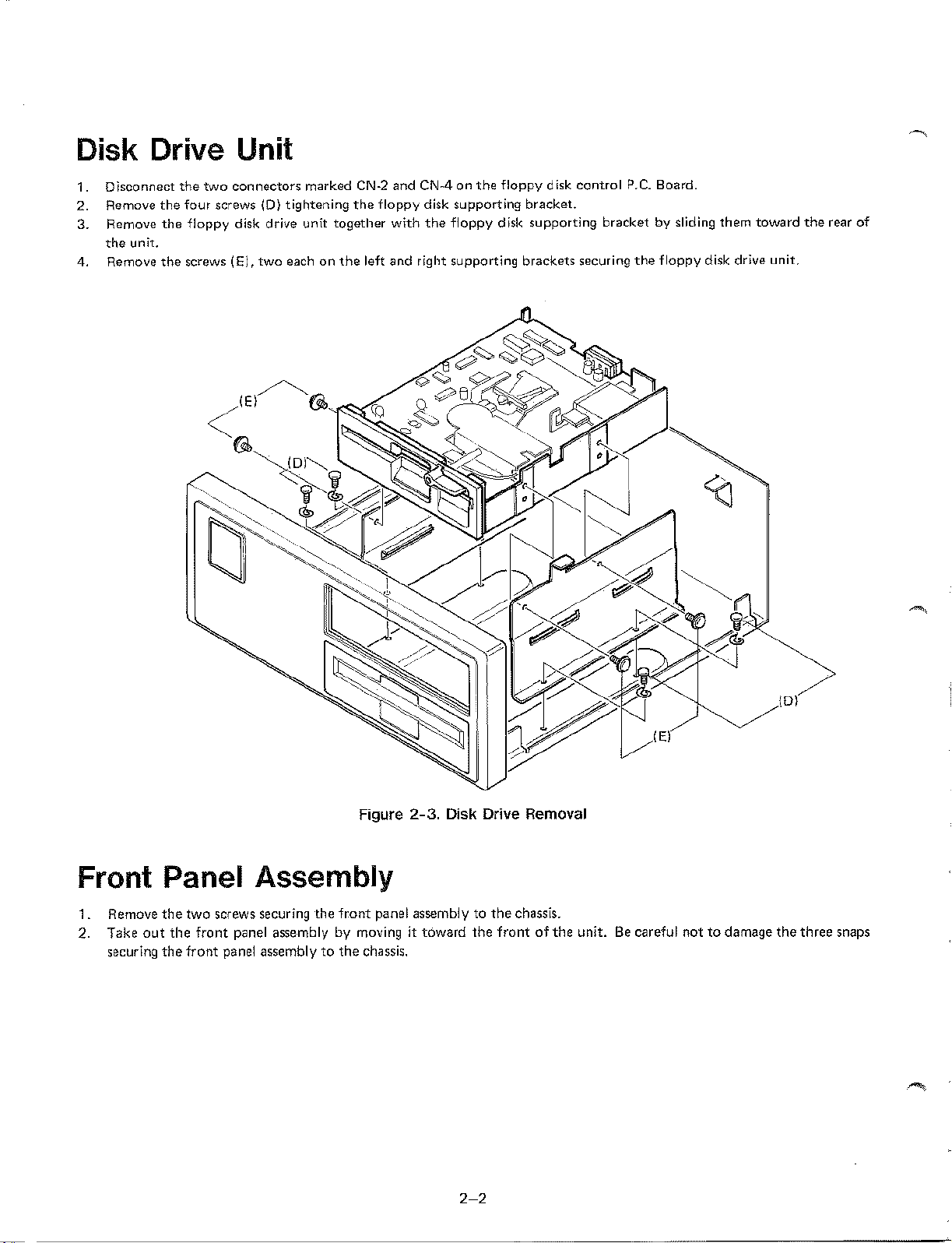

Disk Drive Unit

1. Disconnect

2. Remove

3. Remove

the

unit.

4. Remove

the

two

connectors marked eN-2 and

the

four screws

the

floppy disk drive unit together

the

screws (E), two each on

(0)

tightening

tr

CNAonthe

the

floppy disk supporting bracket.

with

the

floppy

the

left and right supporting brackets securing

floppy disk control P.C. Board.

disk supporting bracketbysliding them

the

floppy disk drive unit.

toward

the

rear

of

Figure

Front Panel Assembly

1.

Remove

2. Take

securing

out

the

the

the

two

front

front

screws securing

panel assemblybymoving it

panel assemblytothe

the

front

chassis.

panel assemblytothe

2-3.

Disk Drive Removal

toward

the

frontofthe

chassis.

unit.Becareful nottodamage

{D{

the

three snaps

2-2

3/Preventive Maintenance

To

ensure

the

proper

operationofthe

of

the

cleaning

Radio Shack's Universal Disk Drive head cleaning kit for S-1/4-lnch disks works well for this purpose. The kit includes

special cleaning disks

magnetic recording head.

and

one

bottle

Cleaning the Head

To

clean

the

magnetic head, use a lint-free

carefullytoremove all accumulated oxide and dirt.

CAUTION:

other than 91% Isopropyl alcohol may damage the head.

Extreme care

Rough or abrasive

must

be exercisedtoprevent

Adjustment

Disk/Video Interface,

of cleaning solution.

clothorcotton

cloth

should

notbeusedtoclean the magnetic recording head.

the

head

the

from

being damaged (do

only

scheduled preventive maintenance requiredisperiodic

swab moistened with 91% Isopropyl alcohol. Wipe

Useofcleaning solvents

not

scratch or strike

the

head).

the

two

head

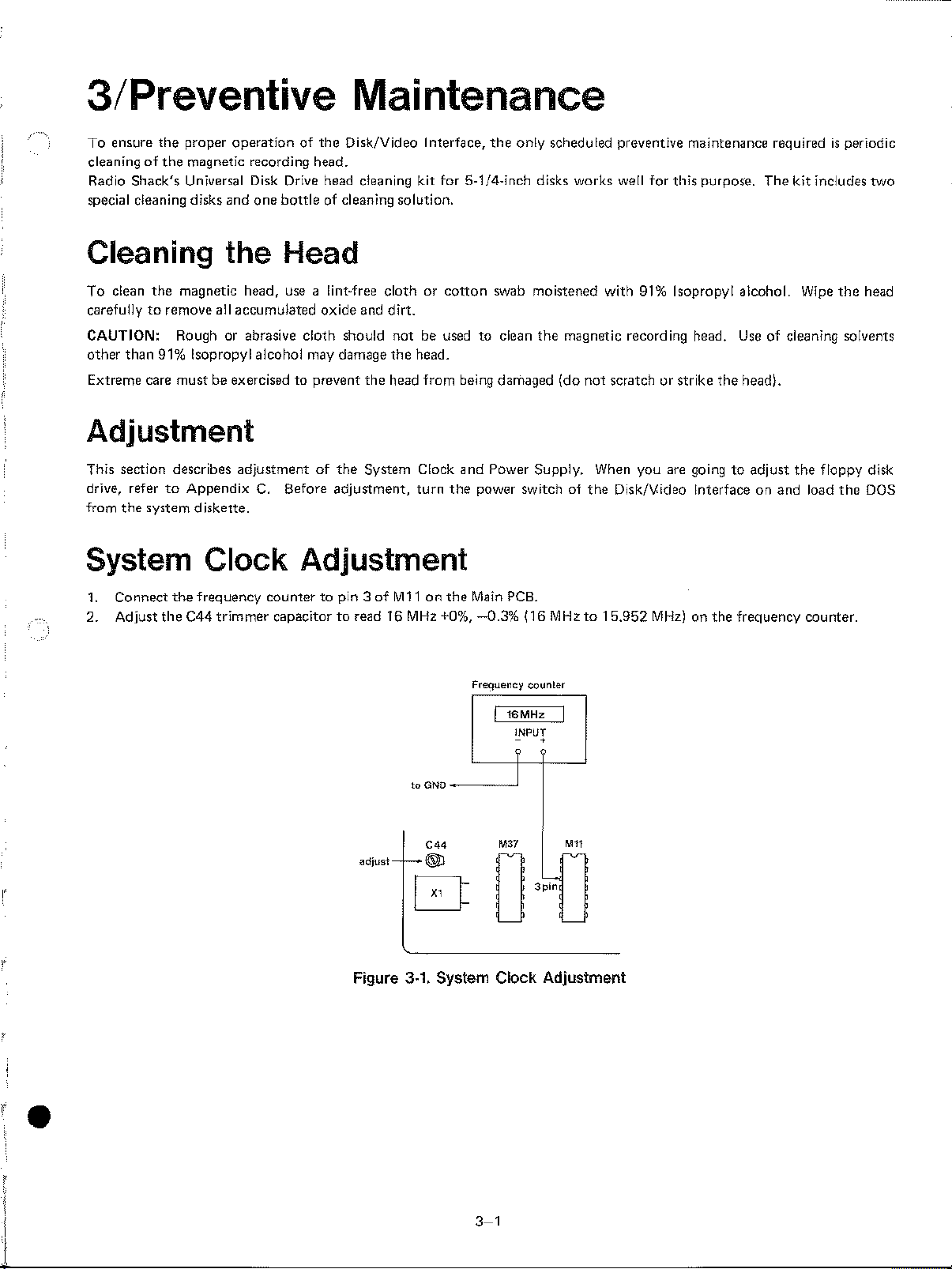

This section describes

to

system

the

the

Appendix

diskette.

Clock

frequency

C44

trimmer

drive, refer

from

the

System

1.

Connect

2.

Adjust

adjustmentofthe

C.

Before

adjustment,

Adjustment

countertopin3of

capacitortoread16MHz

System Clock

turn

Mllonthe

to

GND

adjust

and

Power Supply. When you are goingtoadjust

the

power switch of

Main PCB.

+0%,

-0.3%

Frequency

o

16MHz

INPUT

?

--ll

MO<

(16

MHzto15,952

counter

•

3pin

-

the

Disk/V.ideo Interfaceonand

MHz)onthe

the

floppy disk

load

the

frequency counter.

DOS

J

Figure 3·1. System Clock Adjustment

•

i

I

3-1

+5V

Adjustment

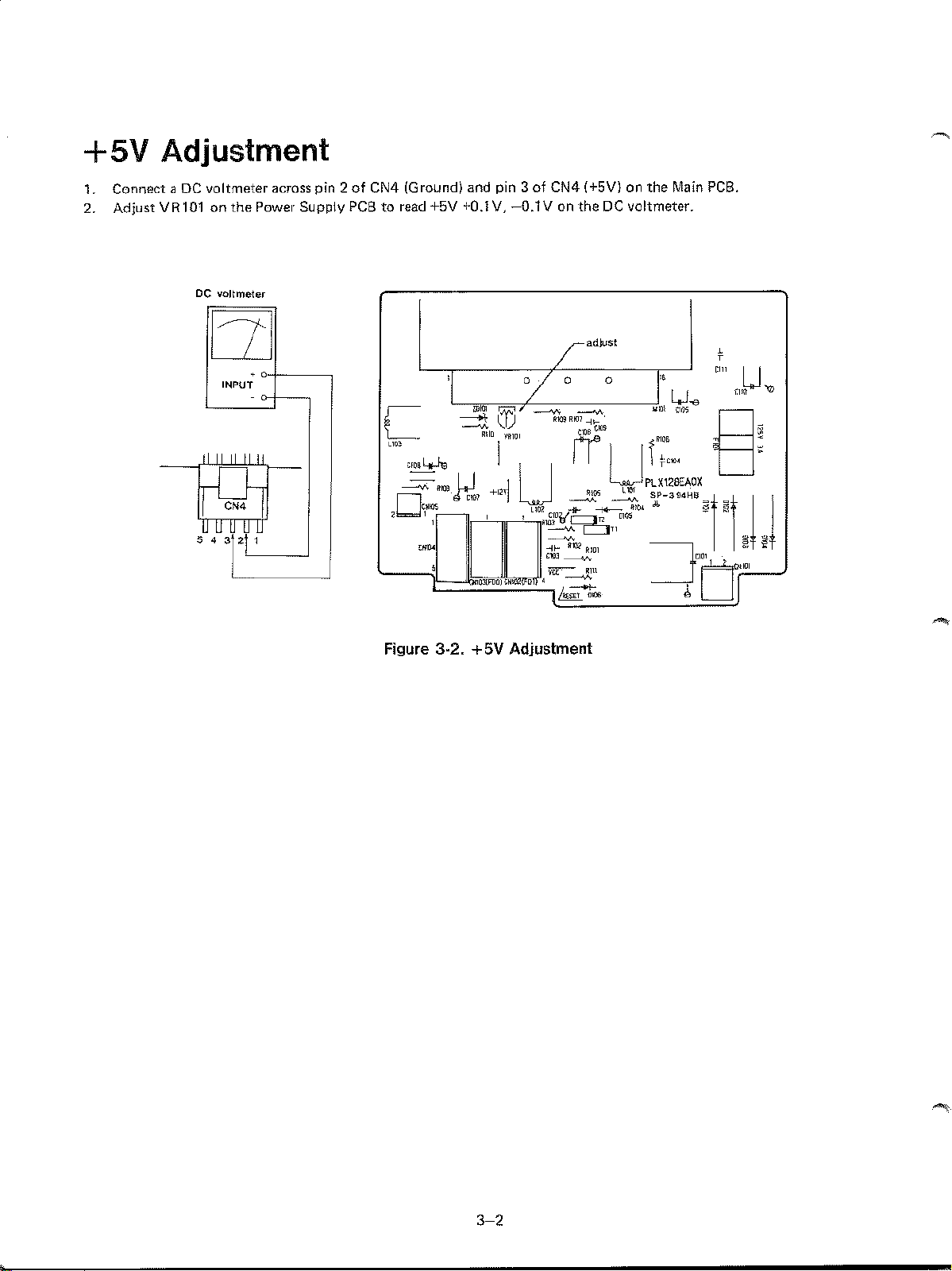

1. Connect a DC voltmeter

2. AdjustVR101onthe

DC

voltmeter

OJ

• 0

INPUT

"

'"

'"

~4

5 J4U3

!

'!

'

across

pin 2ofCN4

Power Supply

(Ground~

PCBtoread +5V

and pin 3ofCN4 (+5V) on

+0.1V,-0.1

V on

theDCvoltmeter.

/ad)US!

the

Main

PCB.

Figure 3-2.

+5V

Adjustment

3-2

4/Theory

of

Operation

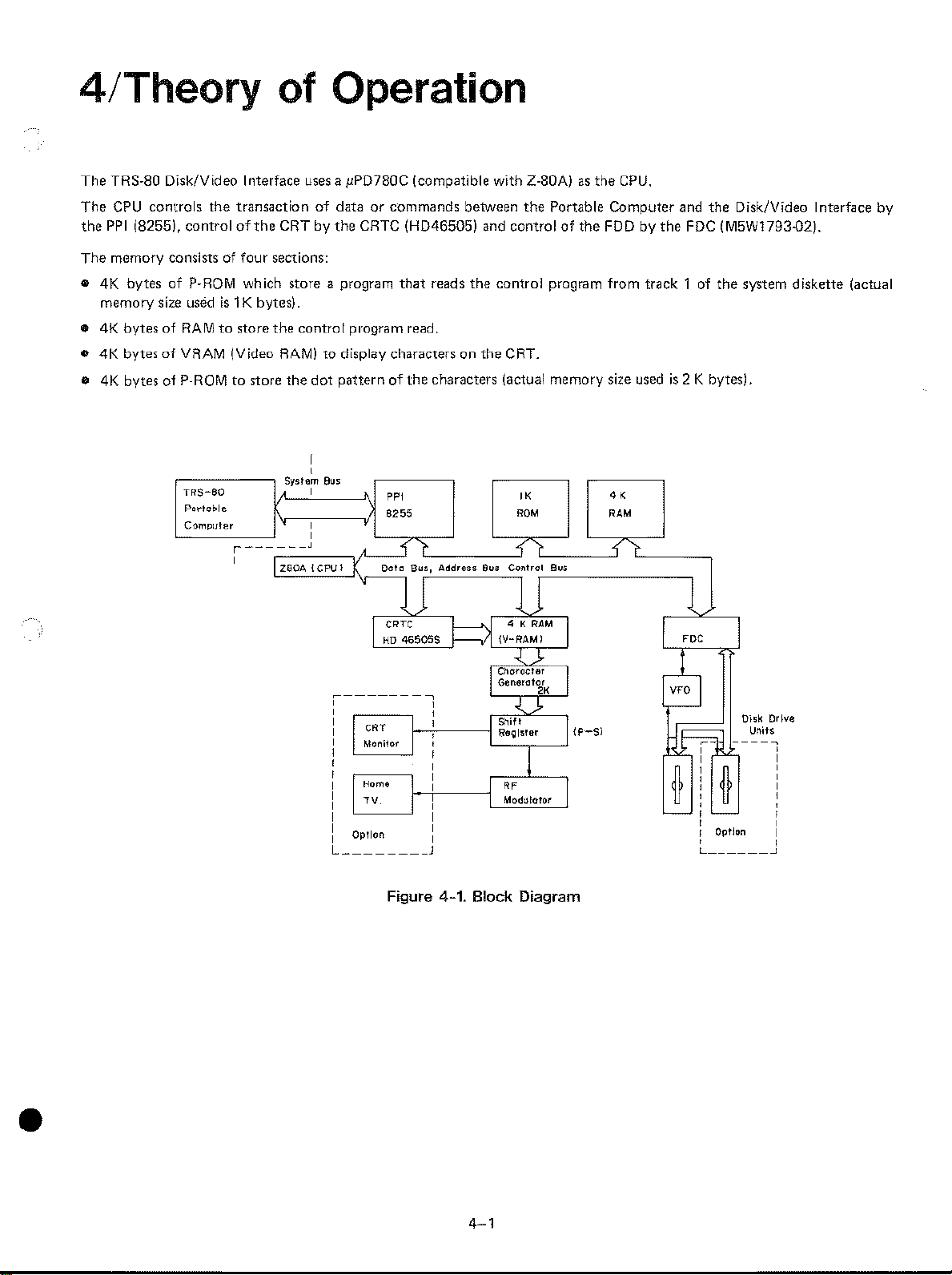

The TRS-80 DisklVideo Interface uses a pPD780C (compatible with Z-80A)asthe

The

CPU

controls

the

PPI

(8255),

The memory consists of four sections:

•

4K

bytesofP-ROM which

memory size usedis1K bytes) .

• 4K

bytesofRAMtostore

e

4K

bytesofVRAM

e

4K

bytes of P-ROM to store

the

transactionofdataorcommands

control

TRS~60

Portable

Computer

afthe

CRT

by the

CRTe

(HD46505) and controlofthe FDDbythe

store

a program

the

control

(Video RAM)todisplay characters on the CRT.

the

Systgm Bus

r

,

- -"

Z80A

program read.

dot

patternofthe

,

,

,

(CPUl

'"

8255

K Doto

that

reads

characters (actual memory size usedis2 K bytes),

."

BUS,

Add.ess

between

the

control

8us

the

Portable

program

"

ROM

<,

Cont.ol Bus

11 11

CRTCI==:>f

HD

46505$

~-------,

, ,

I

CRT

Monito' I

,

IHome

"

OpTion

________

I

I

,

,

,

,

,

,

,

,

,

I

,

,

J L

4 K

RAM

1I,'-RAMI

"'-J.

Chorocter

Gene.g!o.

"

"'-J.

Shift

Re~l",e.

j

ModulO-lor

"

lP-S)

CPU.

Computer

from

track 1 of

"

,,"

n-

and

FOG

eo'

8

0

,

,

,

fr,fr

,

,

~

,

,

,

the

Disk/Video Interface by

(M5W1793-C2).

the

system

diskette

I

Isk D.lve

0

Unit.

--,

--

,

,

,

,

,

,

,

--"

,

,

,

,

-

OpTion

____

(actual

•

Figure 4-1. Block Diagram

4-1

This section provides circuit descriptions of

the

0 isk/Video Iriterface,dividing it into the following eleven parts:

•

CPU

• Address Decoding and Bank Selection Circuit

• Memory Map

• I/O Map

• Clock Generator Circuit

• System Bus Interface Circuit

• CRT

• Flicker Suppressing Circuit

• FDD Interface Signals

• FDD Control Circuit

• Power Supply and Reset Circuit

Interface and Control Circuit

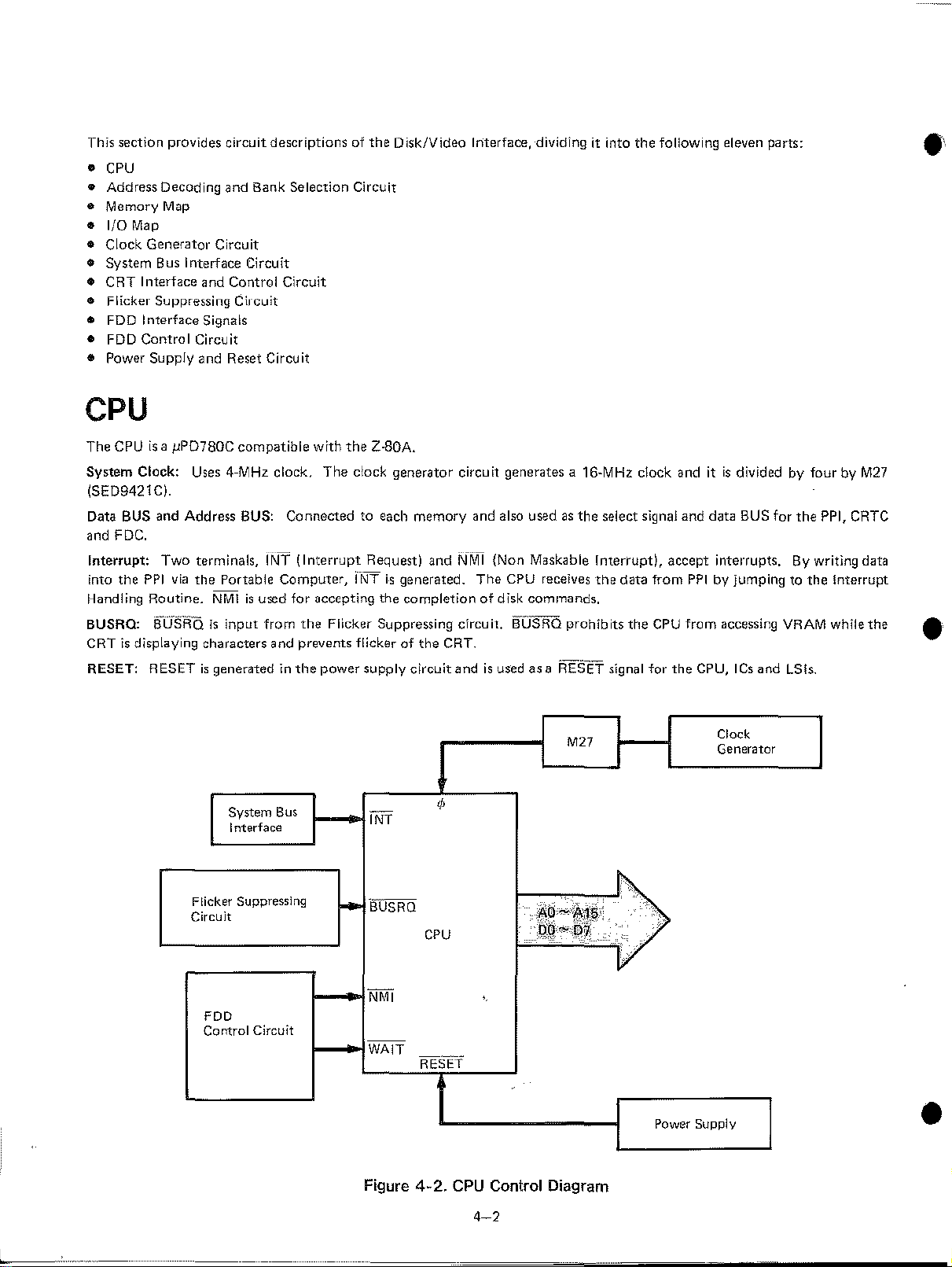

CPU

The CPUisa j1PD780C compatible

System Clock: Uses 4-MHz clock,

(SED9421C).

Data BUS and Address BUS: Connected

and FDC.

Two

Interrupt:

into the

Handling Routine.

BUSRQ:

CRT

RESET: RESET

PPI

is

displaying characters and prevents flickerofthe

terminals, INT(Interrupt

via

the

Portable Computer, (NTisgenerated.

NMIisused for accepting the completionofdisk commands.

SUSRQ

is

input from

is

generated in

with

the

Z-80A.

The

clock generator circuit generates a 16-MHz

to

Request) and

the

Flicker Suppressing circuit.

the

power supply circuit andisused as a

each memory and also usedasthe

i\fMl

(Non Maskable Interrupt), accept interrupts.

The

CPU receives

EfUSRO

CRT.

prohibits

RESET

dock

and itisdivided by four by

select signal and data BUS for

the

data

from

PPI

by jumpingtothe

the

CPU

from accessing VRAM while

signal for

the

CPU,

ICs

and LSls.

the

PPI, CRTC

By

writing data

M27

Interrupt

the

•

•

System

Flicker Suppressing

Circuit

FDD

Control Circuit

Bus

Interface

~

INT

'BUSRQ

--

NMI

--

WAIT

Figure

q,

CPU

RESET

4-2.

,

CPU

Control Diagram

'2"

M27

L'L'

Clock

Generator

<

Power

Supply

•

---------------------------------,--------

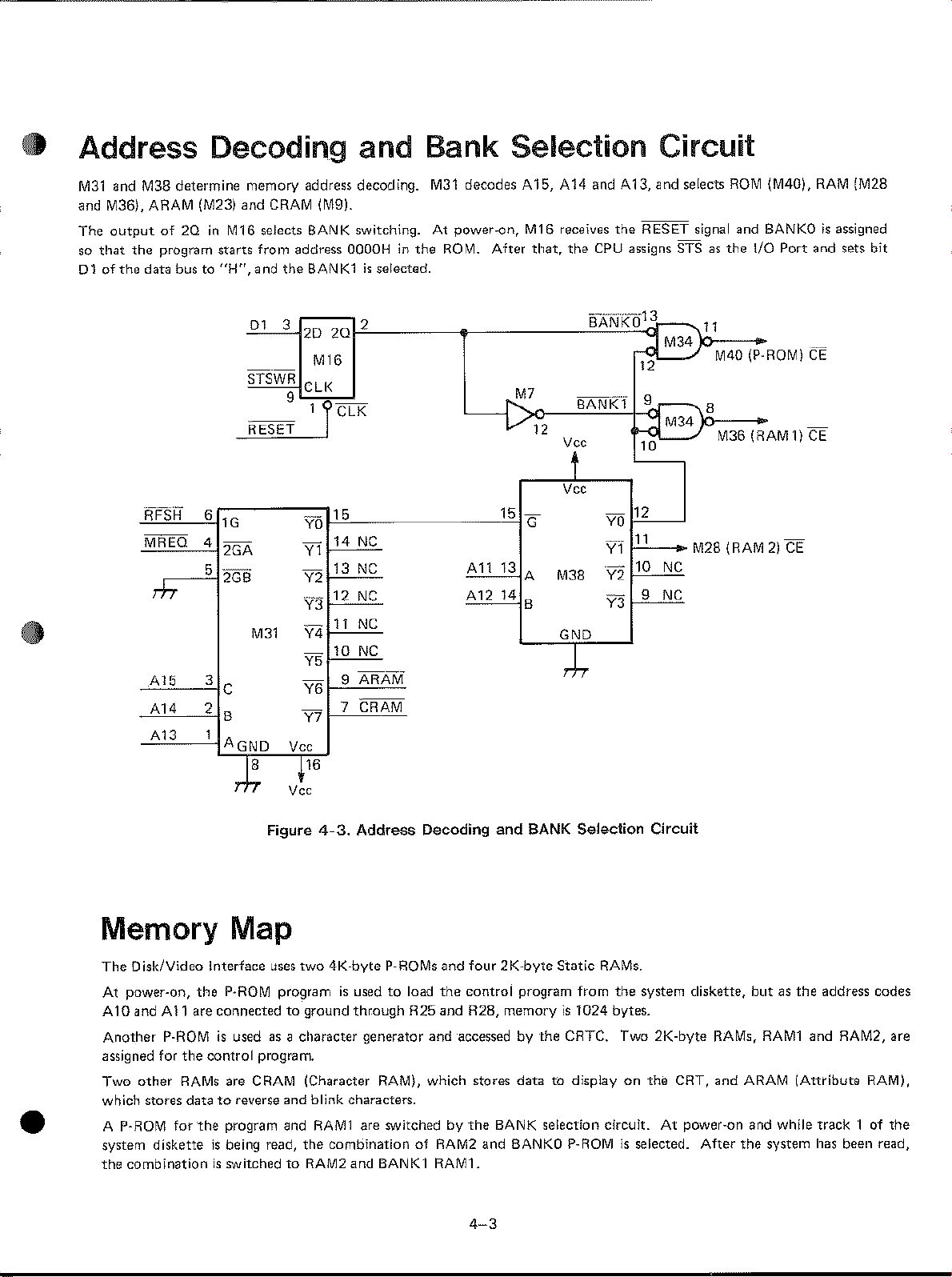

• Address Decoding and Bank Selection Circuit

M31

and

M38

determine memory address decoding. M31 decodes

and

M36l,

ARAM

The

outputof20inM16 selects BANK switching. At power-on, M16 receives

that

so

01ofthe

the

data bus to

(M23) and

program starts from address

"H",and

CRAM

the

(M9).

BANK1is

COOOHinthe

selected.

ROM. After

A15,

that,

A14

and A13, and selects ROM (M40), RAM (M28

the

RESET signal and

the

CPU

assigns STS as

BANKOisassigned

the

110

Port and sets bit

•

RFS'i-l

MREQ

m

A15 3

A14 2

A13

01 3 2

_.-

STSWR

RESET

6

1G

--

4

2GA

5

2GE!

M31

C

8

1

AGND

~

2D

elK

9

-

'13

-

Y6

Y7

V"

)'6

Vc

M16

1 J

YO

Y1

Y2

Y4

Y5

c

20

15

14

13

12

11

10

elK

9

7

NC

NC

NC

NC

NC

ARAM

CRAM

All

A12

15

13

14

M7

G

A

8

12

vr

v"

M38

GNO

J,-

BA'N'k6

BANK""

YO

'11

-

Y2

Y3

13

...d

12

9

...;,j

10

12

11

10

9

M34;

M34

NC

NC

11

8

,r

M28

M40 (p.

M36(R

(RAM

ROM)

cl~

AM1)CE

2)

CE

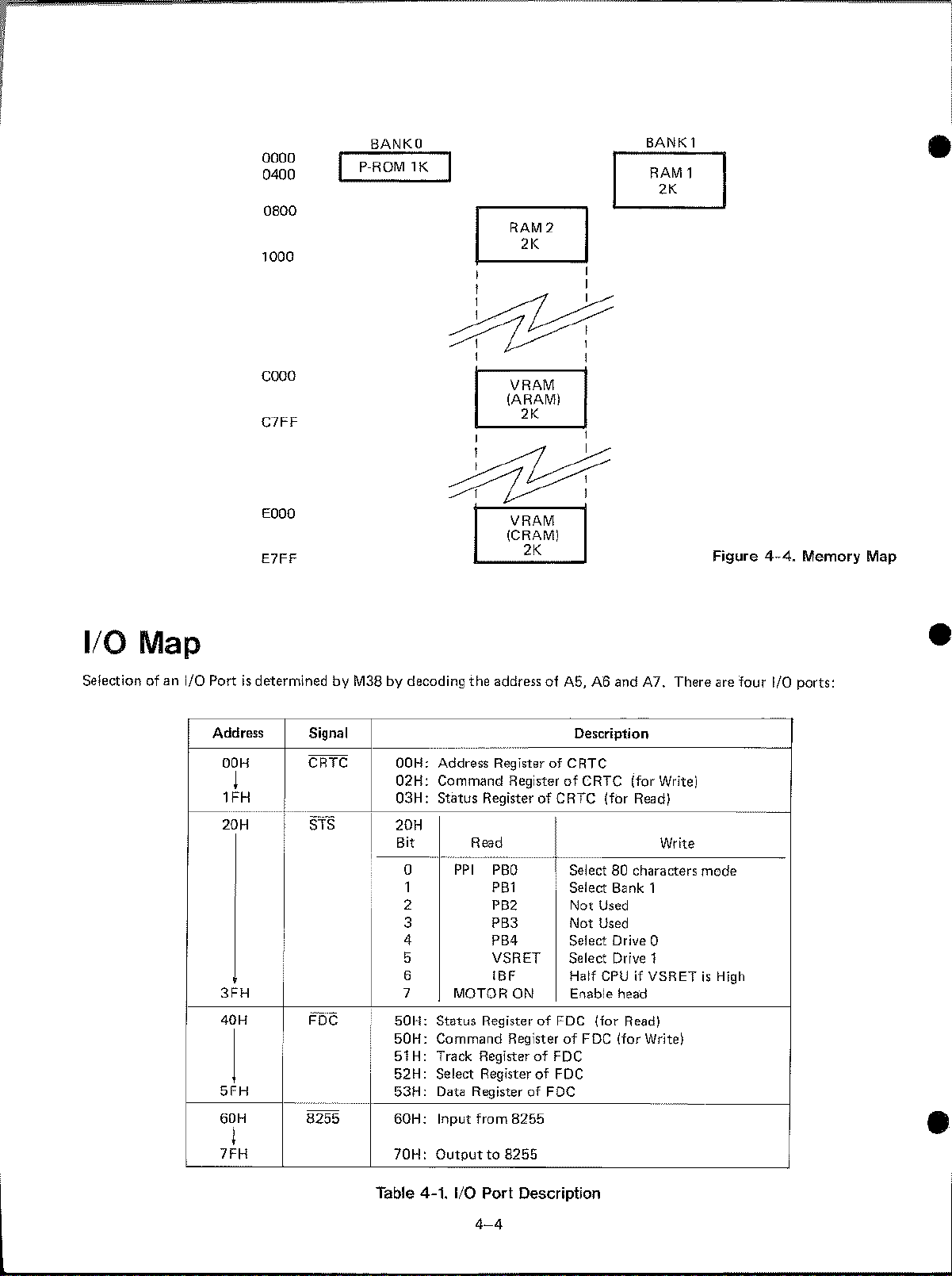

Memory Map

The DisklVideo Interface uses two 4K-byte P-ROMs and four 2K-byte Static

At power-on,

A10 and

Another

assigned for

Two other

which stores datatoreverse and blink characters.

• A P·ROM for

system disketteisbeing read,

the

Ali

P-ROMisusedasa character generator and accessed by

AAMs

combinationisswitchedtoRAM2

Figure

the

P·ROM

are connectedtoground through A25 and A28, memory

the

control program.

are

CRAM

the

program and

4-3.

Address Decoding and BANK Selection Circuit

programisusedtoload

(Character

RAM1

the

combinationofRAM2

RAM),

are switched by

and

BANK1

the

control program from

which stores datatodisplay on

the

BANK

and

BANKO

RAM1.

4-3

RAMs.

the

system diskette,

is

1024 bytes.

the

CRTC. Two 2K-byte

the

CRT, and

selection circuit. At power-on and while track 1 of

P-ROMisselected. After

RAMs,

the

butasthe

RAMi and RAM2, are

ARAM

system has been read,

address codes

(Attribute

RAM).

the

.----------------------~

-

0000

0400

0800

1000

CODO

C7FF

EDOO

E7FF

BANKO

P-ROM 1K

~

L..:..:.-J

I I

~

~

I I

VRAM

(ARAM)

2K

VRAM

(CRAM)

2K

~

~

BANKl

Figure

4-4.

Memory Map

•

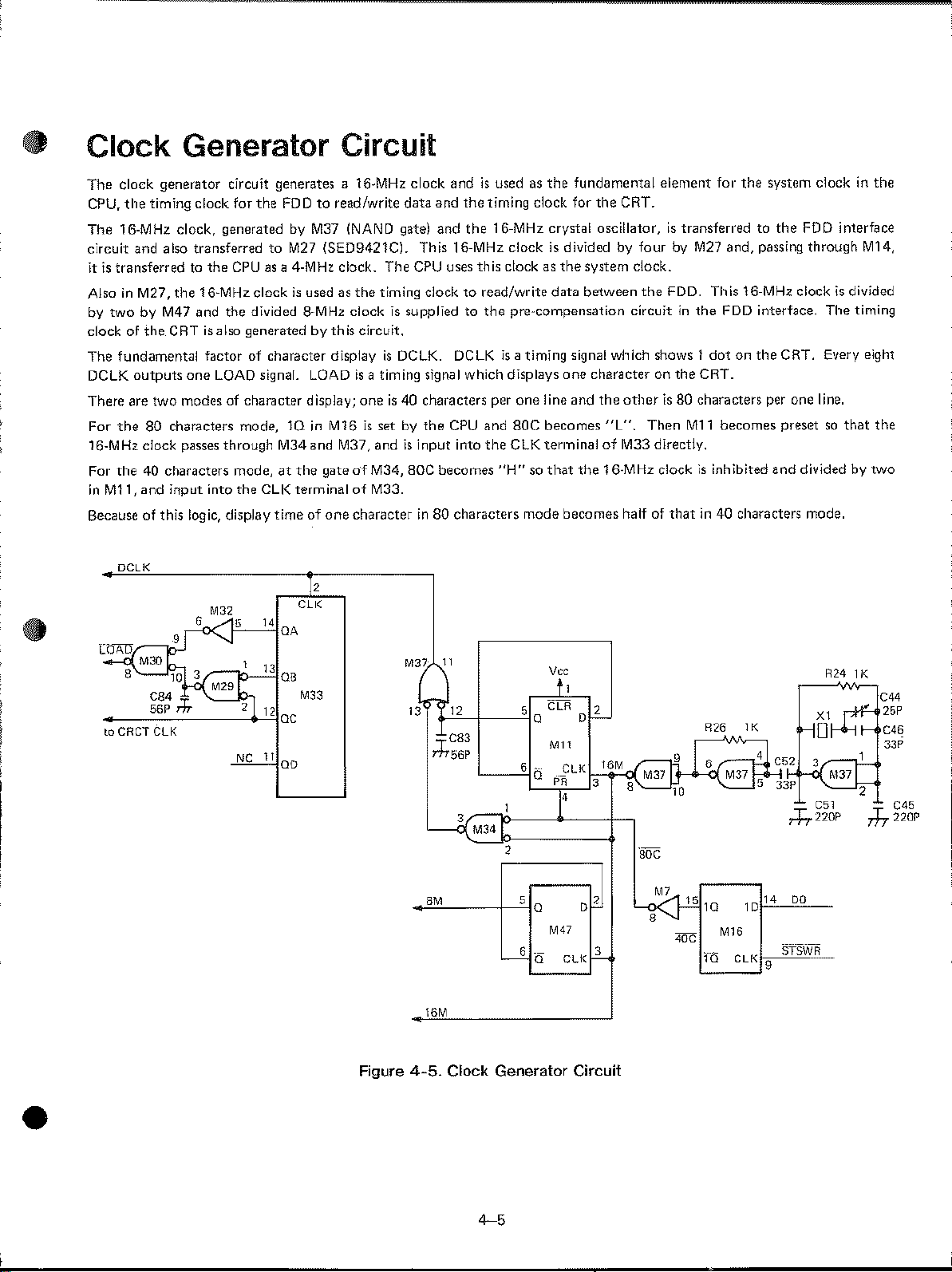

I/O Map

Selection ofanI/O PortisdeterminedbyM38bydecoding

Address

DOH

j 02H:

1FH

20H

3FH

40H

5FH

GOH

j

7FH

Signal

eRTC

S1'S

FO'C

8255

DOH:

03H:

20H

Bit

0

1

2 PB2

3 PB3 Not Used

4 PB4 Select Drive 0

5

6

7

50H:

50H:

51H:

52H: Select Register

53H: Data Register

......

60H:

70H:

---------- ---------'''-

Address RegisterofeRTC

Command

Status

""'-'-

Status

Command

Track RegisterofFDG

Input from

Outputto8255

the

addressofA5, A6 and A7. There are

Description

RegisterofCRTC

Register

Read Write

PPI

MOTOR

RegisterofFOG

of

CRTe

PBO

PB1

VSRET

IBF

I

ON

RegisterofFOG

of

FOC

of

FOe

8255

Select80characters mode

Select Bank 1

Not Used

Select Drive 1

Half

Enable head

(for

(for

Read)

CPUifVSRETisHigh

(for

Read)

(for

Write)

Write)

,~""

four

----

•

1(0 ports:

•

Table 4-1. I/O

Port

4-4

Description

• Clock Generator Circuit

The

clock generator circuit generates a l6-MHz clock andisusedasthe

CPU,

the

•

timing clock for

The l6-MHz clock, generated by

circuit

and also transferredtoM27 (SED9421C). This

it

is

transferred to

in

Also

by

clock of

The fundamental factor of character display

DCLK

There are

For

16-MHz ciock passes through

For

in

Because of

M27,

twobyM47 and the divided 8-MHz clockissuppliedtothe

the

outputs

two

the

80

the

40 characters mode,atthe

Ml1,

and

DClK

to CRCT

ClK

the

the

l6-MHz clockisused as

CRT isalso generatedbythis circuit.

one

modes of character display;

characters mode, 1QinM16isset by

input

into the

this logic, display

G

the

FDDtoread/write

M37

(NAND gate) and

CPUasa 4-MHz clock. The

the

lOAD

M32

signal.

ClK

5

2

NC

lOADisa timing signal which displays

M34and

timeofone

14

0A

13

08

12

0C

11

00

M37, andisinput

gateofM34,

terminalofM33.

characterin80

2

ClI<

M33

data

CPU

timing clocktoread/write

is

DCLK. DCLKisa timing signal which shows 1

oneis40

BOC

M37

"

fundamental element for

and

the

timing clock for

the

l6-MHz crystal oscillator,istransferredtothe

l6-MHz

uses this clock as

characters per

the

CPU

into

becomes

characters mode becomes half of

n

clockisdividedbyfourbyM27 and, passing

the

system clock.

data

between

pre-compensation circuitinthe

one

one

line and

and

BOC

becomes

the

elK

terminalofM33 dIrectly.

"H"sothat

the

Vee

,

ClR

Mn

PR

D 2

,

"

C83

Jr

56P

3

C:l<>----''---+_

M34

5 a

6 b

2

the

CRT.

the

FDD. This l6-MHz clockisdivided

FDD interface. The timing

dotonthe

characteronthe

the

otheris80

"l".

Then

16-MHz clockisinhibited

CRT.

characters per one line.

Mll

becomes presetsothat

thatin40

the

system clock in

FOD interface

through

CRT. Every eight

and

dividedbytwo

characters mode.

R24 1K

I

f-'~

e51

220P

r+r

the

M14,

the

r-+

C44

25P

046

33'

•

Figure

8M

>OM

4-5.

Clock Generator Circuit

5 Q

6 Q

4-5

elK

D'

M7

15

8

3

'DC

10

f6

1D

M>O

CCK

14

9

DD

STSWR

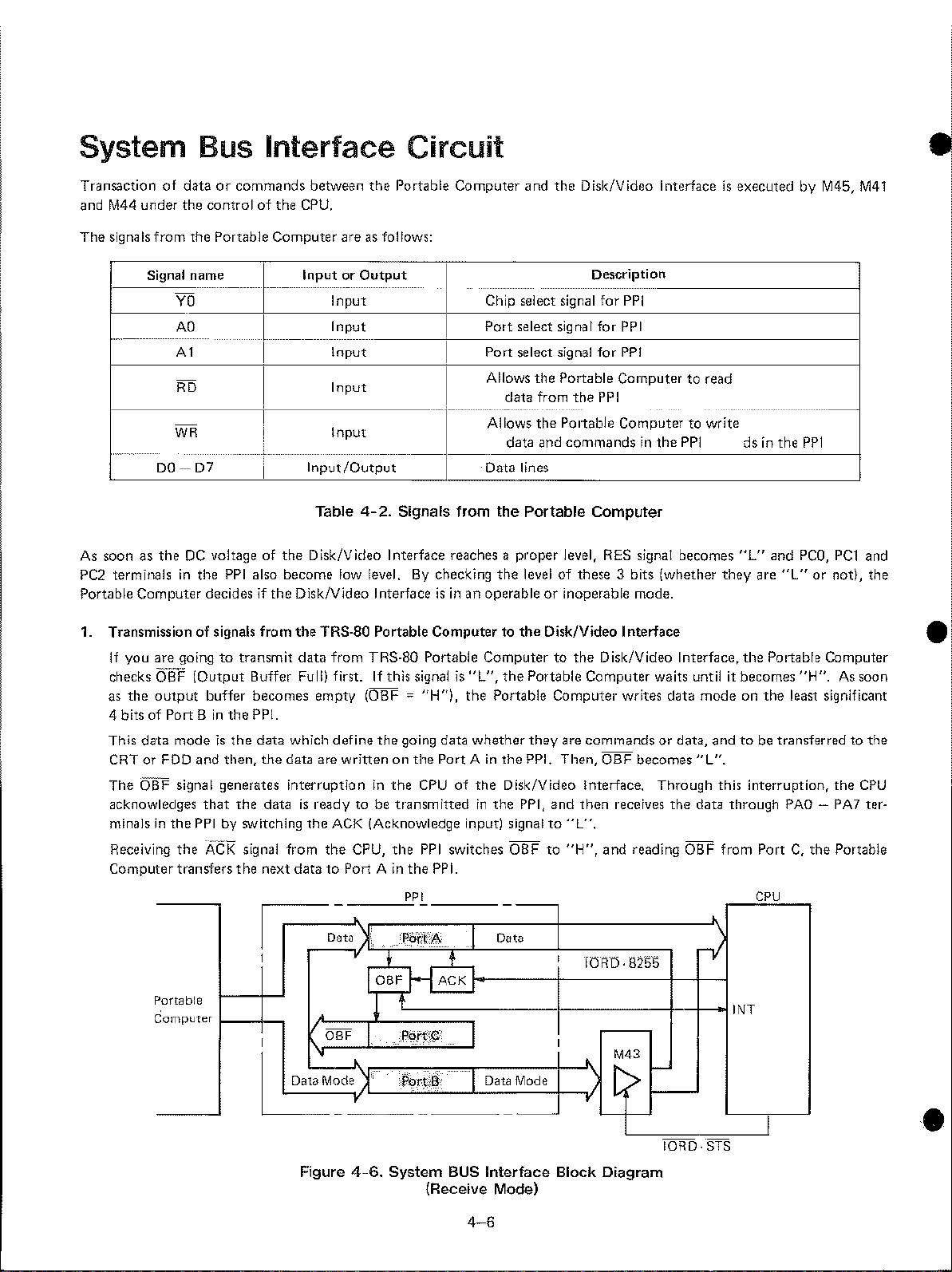

System Bus Interface Circuit •

Transactionofdataorcommands

and M44

The

under

signaIsfrom

Signal name

the

controlofthe

the

Portable

------------

Computer

1

__________

-----

YO

AD

Al

-

RD

-

WR

I

As

soon as

PC2 terminalsinthe

Portable

1. Transmission of signals

If

checks

as

4 bits

This

CRTorFDD

The

acknowledges

Computer

00-

the

DC

Computer

you

are goingtotransmit

O'i3F

the

output

of

PortBin

data

modeisthe

OSF

signal generates

minals

in

the

Receiving

the

transfers

D7

voltageofthe

decides if

(Output

buffer

and

that

PPI

A'CK

I

-------------

I

i

PPI

also

become

the

from

Buffer Full) first.Ifthis

becomes

the

PPI.

data

which

then,

the

data

interruptioninthe

the

dataisready to be

by switching

signal

from

the

next

between

CPU,

the

are

as tollows:

Portable

Computer

and

the

Disk/Video Interfaceisexecuted

-

lnputorOutput

Input

Input

Input

Input

Input

Input/Output

Table

4-2.

Signals

Disk/Video Interface reaches a

low level, By checking

Disk/Video Interfaceisinanoperableorinoperable mode.

the

TRS-SO

data

empty

are

the

the

datatoPort Ainthe

Portable

from

TRS·8D Portable

(OBF

define

the

writtenonthe

ACK

(Acknowledge input) signal

CPU,

Computertothe

signal

'"

"H"),

going

CPU

transmittedinthe

the

PPI

PPI.

Chip select signal

Port

Port

I

Allows

Allows

Data lines

from

Computertothe

is

"L",

the

data

whether

PortAin

o'f

the

switches

select signal

select signal

the

data

from

the

data and commandsinthe

the Portable Computer

proper

the

levelofthese 3 bits (whether

the

Portable

Portable

they

the

PPI.

Disk/Video Interface,

PPI,

OSFto"H",

Description

for

PPI

for

PPI

for

PPJ

Portable

Portable

level, RES signal becomes

Disk/Video

Computer

are

Then,

and

to

"L",

Computertoread

the

PPI

Computertowrite

Interlace

Disk/Video Interface,

Computer

commandsordata,

OBF

then

and

waits until it becomes "H".

writes

becomes

Through

receives

reading OSF from PortC,the

PPI

data

the

"L".

data

ds in

the

"L"

and

they

are

"L"

the

Portable Computer

modeonthe

andtobe transferredtothe

this interruption,

through

by M45,

M41

-

ppj

PCO,

PC1

and

or

not),

As

soon

least significant

the

CPU

PAD

- PA7 ter-

Portable

the

•

Portable

Computer

f--+--,

~

- -

-"

Data

•

OBF [

-"

ala

Mode

- -

Figure

PPI

~':,

'eo",,,,

'-'-;J-@

IOBF

[

ACK

T

X'

'PCin;g;:'

?0,\50

[

I Data

,

4-6.

System

BUS

(Receive Mode)

4-6

---,

Data

Mode

--

Interface

,

fORD·8is'5

,

t?

Block Diagram

lORD·

rY

STS

CPU

INT

i

•

•

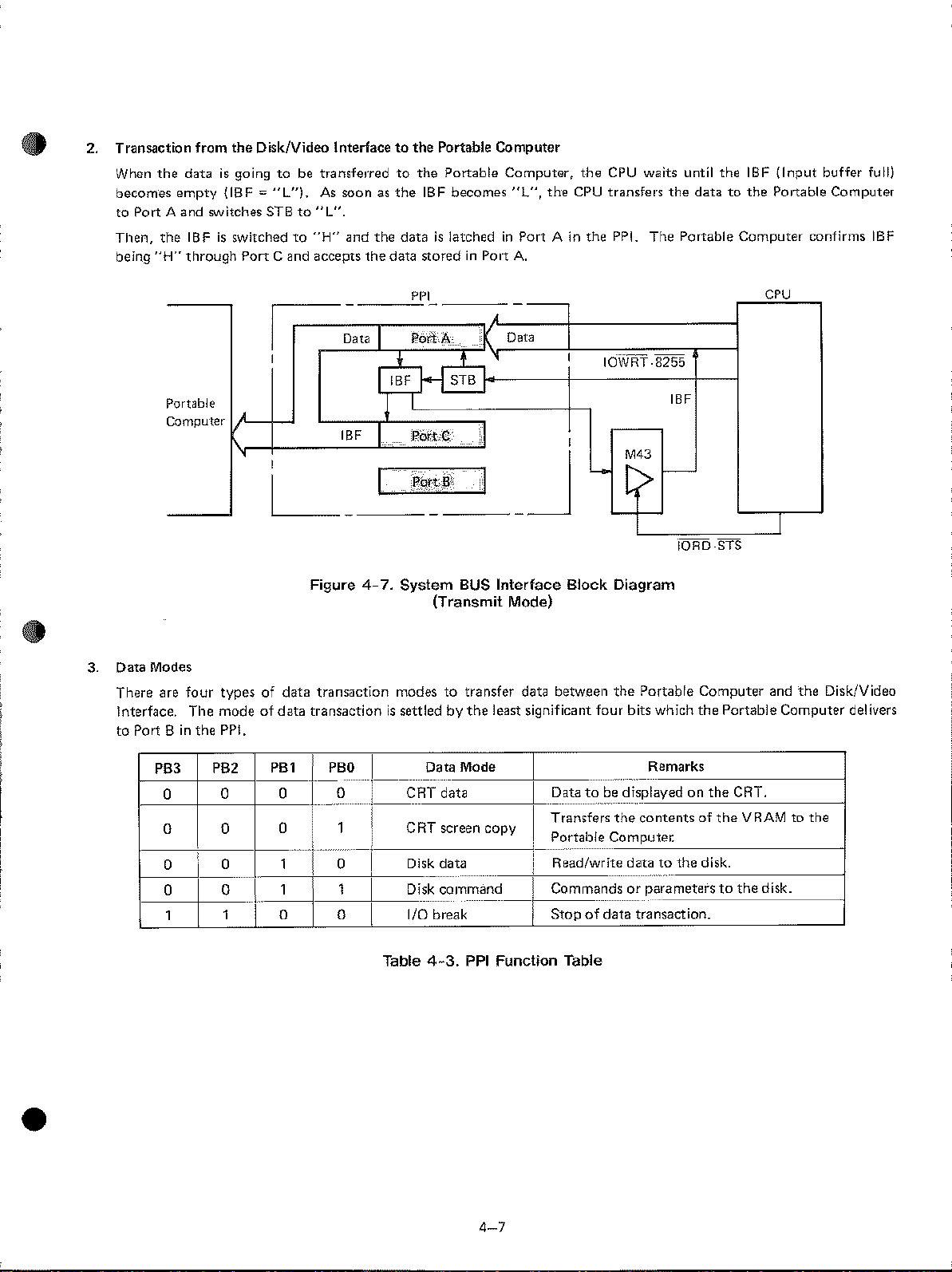

2.

Transaction from the Disk!Video Interlacetothe

When

the

dataisgoingtobe transferredtothe

becomes empty (ISF

to

Port A and switches STS

Then,

the

ISFisswitched

being

"H"

through

'"

"L"),

Port

C and accepts

As soon as

to

"L".

to

"H"

and

the

Portable Computer

Portable Computer,

the

ISF becomes

the

dataislatchedinPort Ainthe PPI. The Portable Computer confirms ISF

data storedinPort

"L",

A.

the

the

CPU

CPU

waits until the ISF (Input buffer full)

transfel's

the

datatothe

Portable Computer

•

Portable

Computer

3. Data Modes

There are four typesofdata

Interface. The mode

to

Port Binthe PPJ.

fr==o'"

I

I

IBF

I

~I

IBF STB

I

I

L_

Figure4-7. System BUS Interface Block Diagram

transaction modestotransfer data between

of

data

transactionissettled by

PPI

-

poihl\.

:Rottiei:'

i~~:ty~)i

-

(Transmit Mode)

--

,

,K

Data

'

I

I

_J

the

least significant four bits which

I

I

L..

IOWRT·8255

IBF

f---

[?

IORD·STS

the

Portable Computer and

the

CPU

1

the

Disk/Video

Portable Computer

del

ivers

•

f--~PB=3--+_P~B~2--1_P_B_'_J~B?

1

__

o=----+_~o_+--=o-L

o

o

°

1--

-+--0-+-,

0

1--o-+-co,-···.J

,

i"

"

'1''''''0'''-1

0'

...

I

...

Eata_M_O_d'

_,~,_~_~T

I I Transfers

CRT screen copy

________

Disk data ! Read/write datatothe

~o'1D'/iO-~~bc'::~k-0:~~~.

Table

4-3.

__

+

1__

data L

-+'

II

"'"

PPI Function Table

4-7

Remarks

..

~.~~~~?""~_:

Portable

Commandsorparameterstothe

Stopofdata

__

?.i,~played

the

contentsofthe

C~o~m",:,pu~t~'~I

transaction.

on

the

CRT.

VRAMtothe

disk.

~~-----1

disk.

--j

CRT

The

is

storedinthe

becomes

M9isthe ARAM

when

terminalsofM23

When

in

M18and assigns A3·A

On

the

Jines

M15

When the character display

ANOsthe

64

in

M2

the

zontal sync) signal generatedinCATeisalso input

input signals.

When using a CRT monitor, this composite video signal

to

61.25

controls switching of

Table

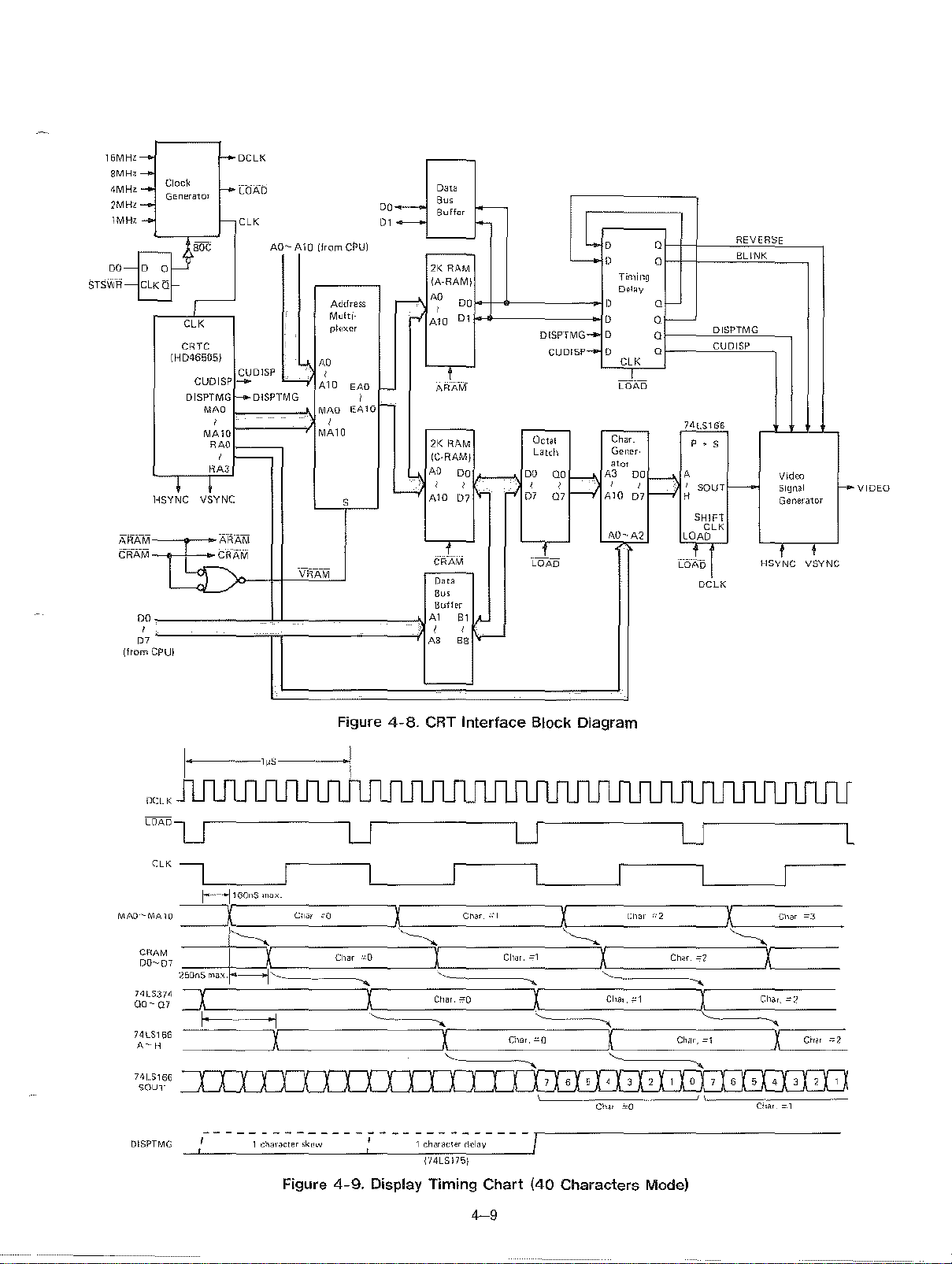

Figure

Figure 4·9 shows

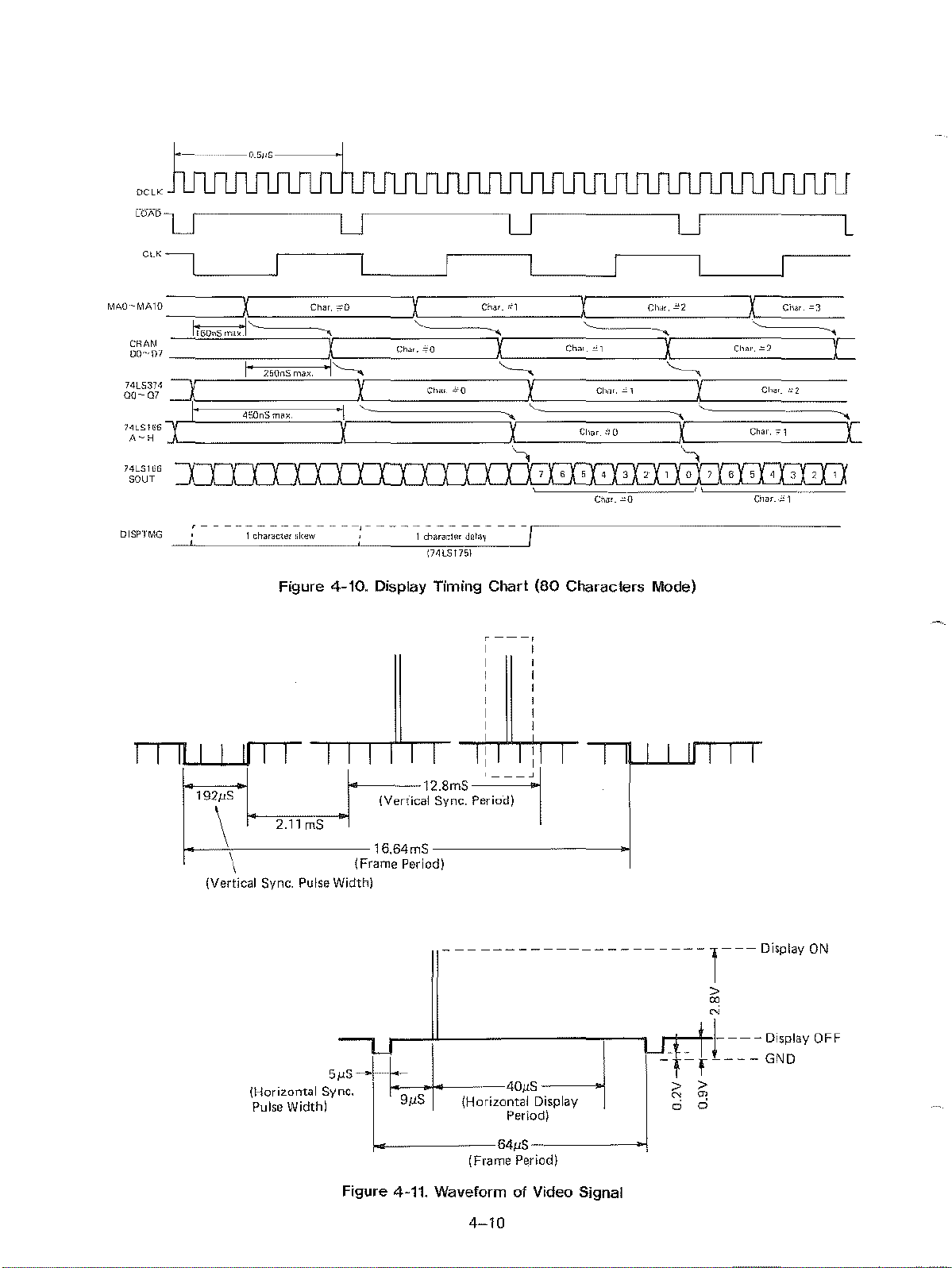

Figure 4·11 shows

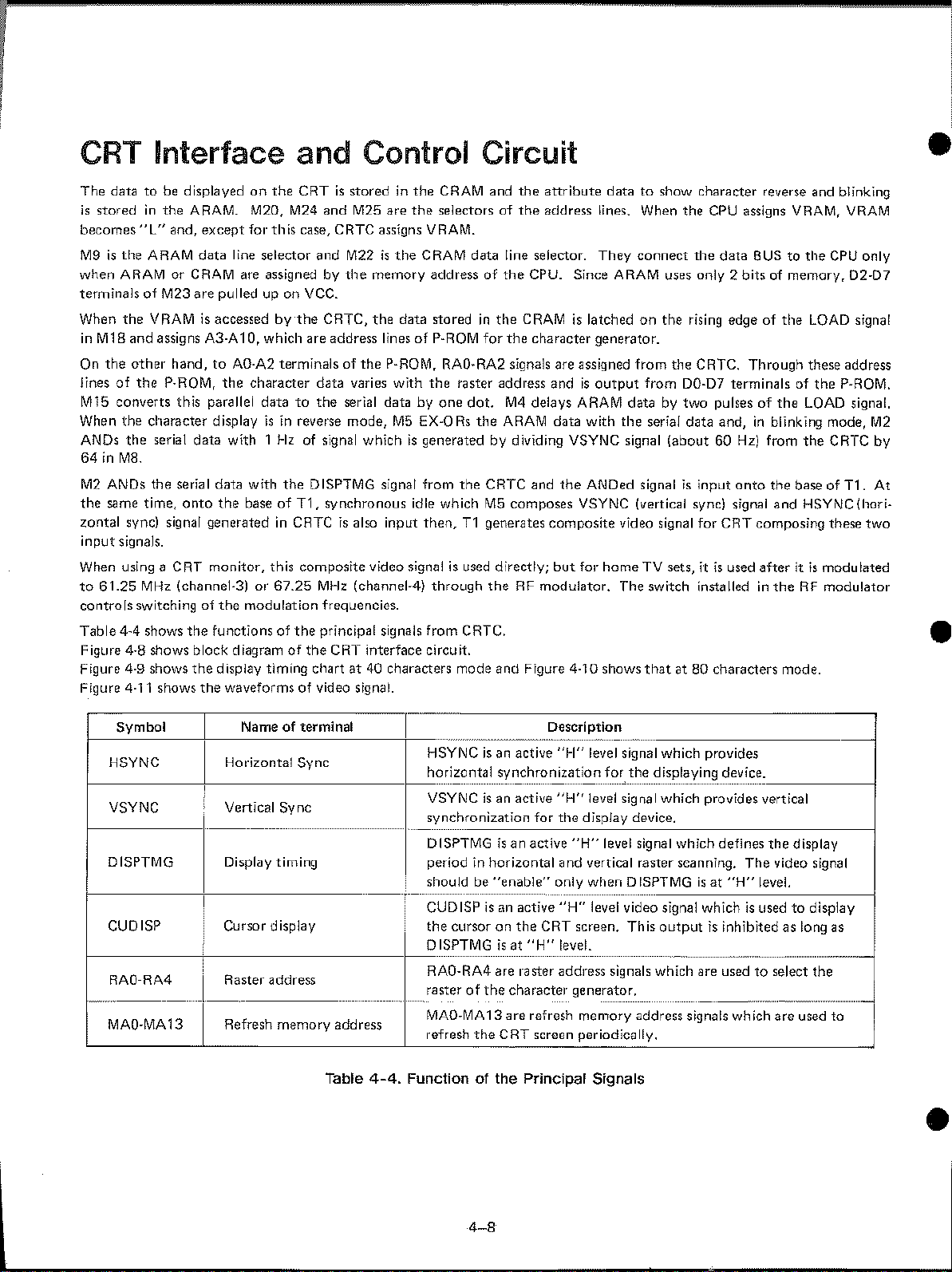

Interface and Control Circuit

datatobe displayedonthe

ARAM. M20, M24

"L"

and,

except

for

data

line selector and

ARAMorCRAM

are pulled up on vee.

the

VRAMisaccessed by

other

hand,toAO·A2 terminalsofthe

of

the

P·ROM,

converts this parallel datatothe

serial

data

M8.

ANDs the serial data with

same time,

4A

4·8

onto

MHz

(channel-3) or

shows

the

shows block diagramofthe

the

are

10,

the

character data varies with

with 1Hzof signal whichisgenerated by dividing V$YNC signal (about 60

the

baseofT1,

the

modulation frequencies.

functions of

display timing chartat40 characters mode and Figure 4·10 shows

the

waveformsofvideo signal.

CRTisstoredinthe

and

M25

are

the

this

case,

CRTe

assigns VRAM.

M22isthe

assignedbythe

the

CRTe,

which are address lines of p.

isinrevel'se mode,

the

DISPTMG signal from

67.25

MHz

the

principal signals from CRTC,

memory addressofthe

the

serial data by

synchronous idle whichM5composes VSYNG (vertical sync) signal and HSYNC (hori-

(channel·4) through

CRT interface circuit.

CRAM data line selector.

data storedinthe

P·ROM, RAO·RA2 signals are assigned

the

M5

EX-ORs

then,T1generates composite video signal for CRT composing these

CRAM and

selectorsofthe

ROM

raster address andisoutput

one

dot.

the

is

used directly;

the

attribute

address lines. When

CPU. Since

CRAMislatchedonthe rising edge of

for

the

character generator.

M4

delays ARAM databytwo

the

ARAM data with

GRTC and

the

the

ANOed signalisinput

but

for home TV sets, itisused after itIsmodulated

RF modulator. The switch installedintheRFmodulator

datatoshow

They

connect

ARAM

from

from

the

serial data and,inblinking mode,

thatat80

character

the

CPU assigns VRAM, VRAM

the

uses

only2bitsofmemory,

the GRTG. Through these address

00·07

characters mode.

reverse and blinking

data

BUStothe

the

terminals of

pulsesofthe

Hz)

from

onto

the baseofT1. At

LOAD

the

LOAD

the

CPU

02-07

P-ROM.

signal.

GRTG

only

signal

•

M2

by

two

•

of

Symbol Name

HSYNC Horizontal Sync

VSYNC

OISPTMG Display timing

CUOISP Cursor display

Vertical Sync

terminal

i DISPTMG

RAO-RA4

MAO-MA13

Raster address

Refresh memory address

Table

uuuu"''''.,

..........~..

HSYNC

horizontal synchronization

VSYNC

synchronization for the display device.

-----

DISPTMGisan active

period

should

CUOISP

the

RAO-RA4 are raster address signals which are used

..

.......

4-4.

rasterofthe

MAO-MA13are refresh memory address signaIswh ich are used

refresh

Functionofthe Principal

is

is

in

be

is

cursoronthe

the

Description

,

an active

an active

horizontal and vertical raster scanning. The video signal

"enable"

an active

is

CRT screen periodically.

"1-1"

"H"

only when OISPTMGisat

"H"

CRT screen. This

at

"H"

level.

character generator.

-

level signal which provides

fO!'

the

displaying device.

level signal which provides vertical

"H"

level signal which defines

level video signal whichisusedtodisplay

outputisinhibited as long as

--------

_

...

_-,,-,-,-""'-,~,-,-

Signals

"H"

the

level.

to

select the

display

to

•

4-8

Hl---{>

~H

Cloct<

~,-

GEnerato,

Hl_

H'

.....

r--~80C

- C C

co

-

STSWR

CLKQ

~

,----

"<

Cine

(HD46505)

CUDISP

DISPTMG

MAO

MAW

HSY~C

AYNC

'~;Ll

(from

00

,

CPUI

"

E5

4DCLK

r-<"

WAD

'"

CUDISP

-

__

DISPTMG ,

,

eM

,

-

eM

AO~

A10

e..,

VnAM

0","

00

01

(frQm

CPU)

Add"ss

Multi-

pl"xcr

M

,

AW

eM

fAl0

MM

,

MAlO

,

-

0",

...

--

Buffer

____

2K

RAM

lA-RAMI

M

~

,

AW

ARTjijiff

2K

RAM

IC-RAM)

M

,

--"I

AW

(j\~M

Dot'

"",

Buffor

,

"

AO

CO

"

co

"'

"'

eo

-

,

.,

SOUT

SHIFT

DCLK

DISPTMG

CUDISP

'"

REVERO;E

BLINK

'---<

HSytc

VideQ

Si~n.1

Generator

,

VSYNC

-

VIDEO

L

0 0

'---<

"

D 0

,

.....

,

~

......

C

C

M

"0

DISPTMG

CUDISP

Octol

Latch

co

GO

,

,

07

t--&-AD

m

Timing

Del,y

eLK

["dAD

Chof.

GQ"O"

ator

,

AO'-A2

co

,

-..,

---

m

"

,

f--

Q

Q

74l.$166

A

,

~

l.OAD

c6-A01.

,

'<-

D(:LK

ClK

I~~

74lS374

00-

01

74LS1ofl

A-·

H

7~1..s166

SOUl'

DiSPTMG

Figure

I--·,e----l

160

r"

'1

"S"'0'_

x X

~-----------------

Figure

4-9.

4-8.

CRT

Interface Block Diagram

u u

1_-----'

Cho,,"n

'-

,

----------,----------

1 oh"co",., ,Icl,y

1'14lS175i

Display

Timing Chart

1_-

~

~

'---------

(40

Cha,

Characters Mode)

u L

1_-

Ch"",_l

",---------1

"0

\

Ci,.,

X

Ch"

-_2

4-9

---

----0_5I'S-----.1

OCLK

w'"U,.------,U------,U,.----U'----;L

eLK,

'----

I I 1

__

14LS1li6

SOUT

DISP'I'MG

Figure 4-10. Display Timing Chart

192pS

\ 1---,;,-;.1'1

1---\-------16.64mS------------I

\ (Frame Period)

(Vertical Sync.

~

=m:S

Pulse Width)

4 3 2 6 5

(80

Characters Mode)

r

---,

I

I

,,--12.8ms-'-------~.,

(Vertical Sync. Period)

~

3

Cil1l'_·~1

~---~~------~

(Horizontal Sync. L

Pulse Widthl 9jJS (Horizontal Display

5"S~--~

Figure 4-11. Waveform

·-40pS-

64

--

(Frame Period)

4~1O

~

Periodl

5

11

--------1

of

Video Signal

------~-1---

>

ro

~

__

l---~Di;PlayOFF

-rr----

> >

C'!

0:

o 0

Display

GNO

ON

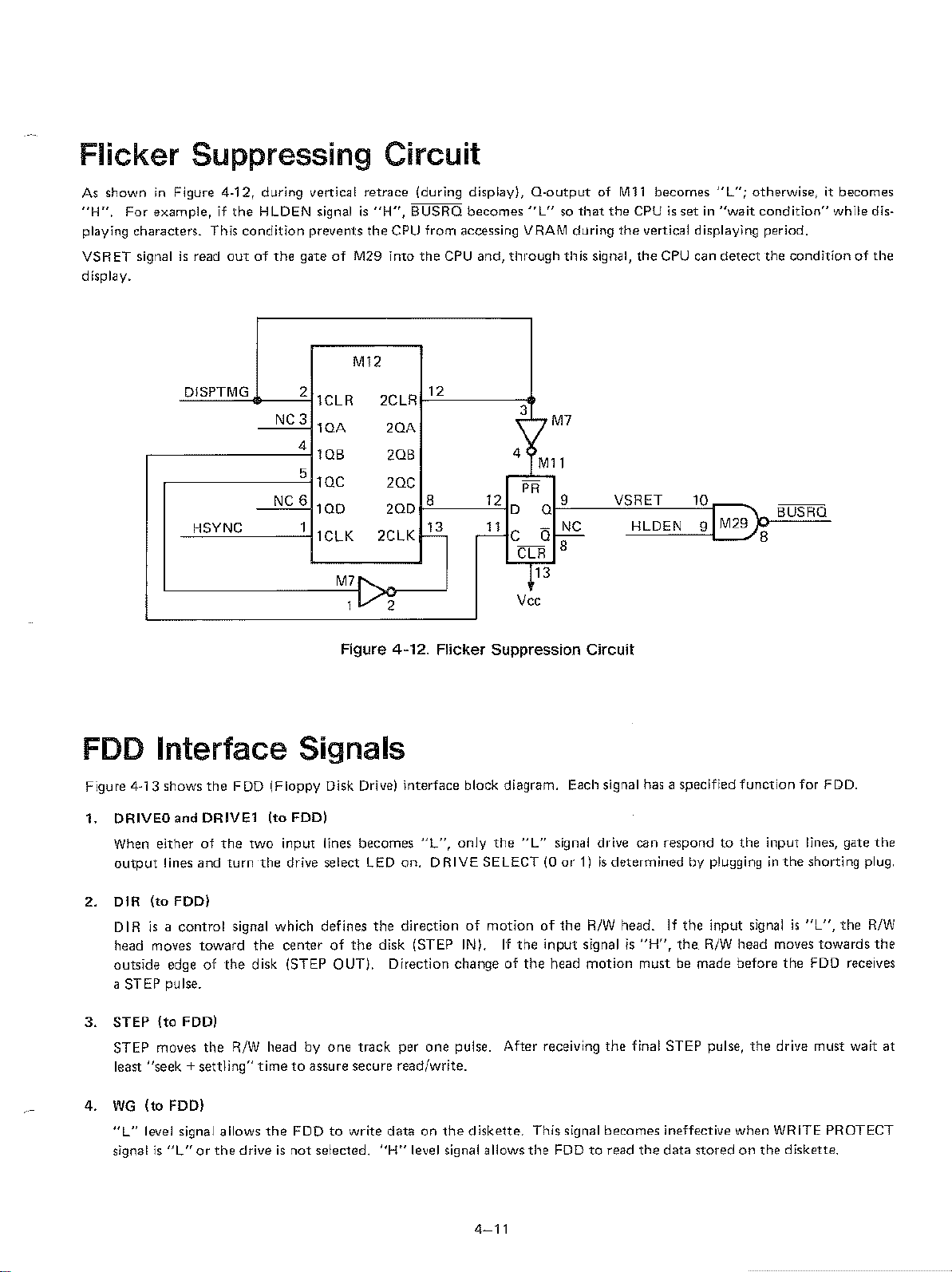

Flicker Suppressing Circuit

As

showninFigure

"H",

For

example,ifthe

playing characters. This

VSRET

display.

signalisread

4-12,

during

HLDEN

condition

outofthe

vertical

signalis"H",

prevents

gateofM29

retrace

the

M12

CPU

into

(during

BUSRQ

from

the

CPU and,

becomes

accessing VRAM during

display),

through

Q-output

"L"sothat

this

of

Mll

becomes

the

CPUissetin"wait

the

vertical displaying period.

signal,

the

CPU can

"L";

otherwise,itbecomes

condition"

detect

the

conditionofthe

whIle dis-

DISPTMG 2

FDD

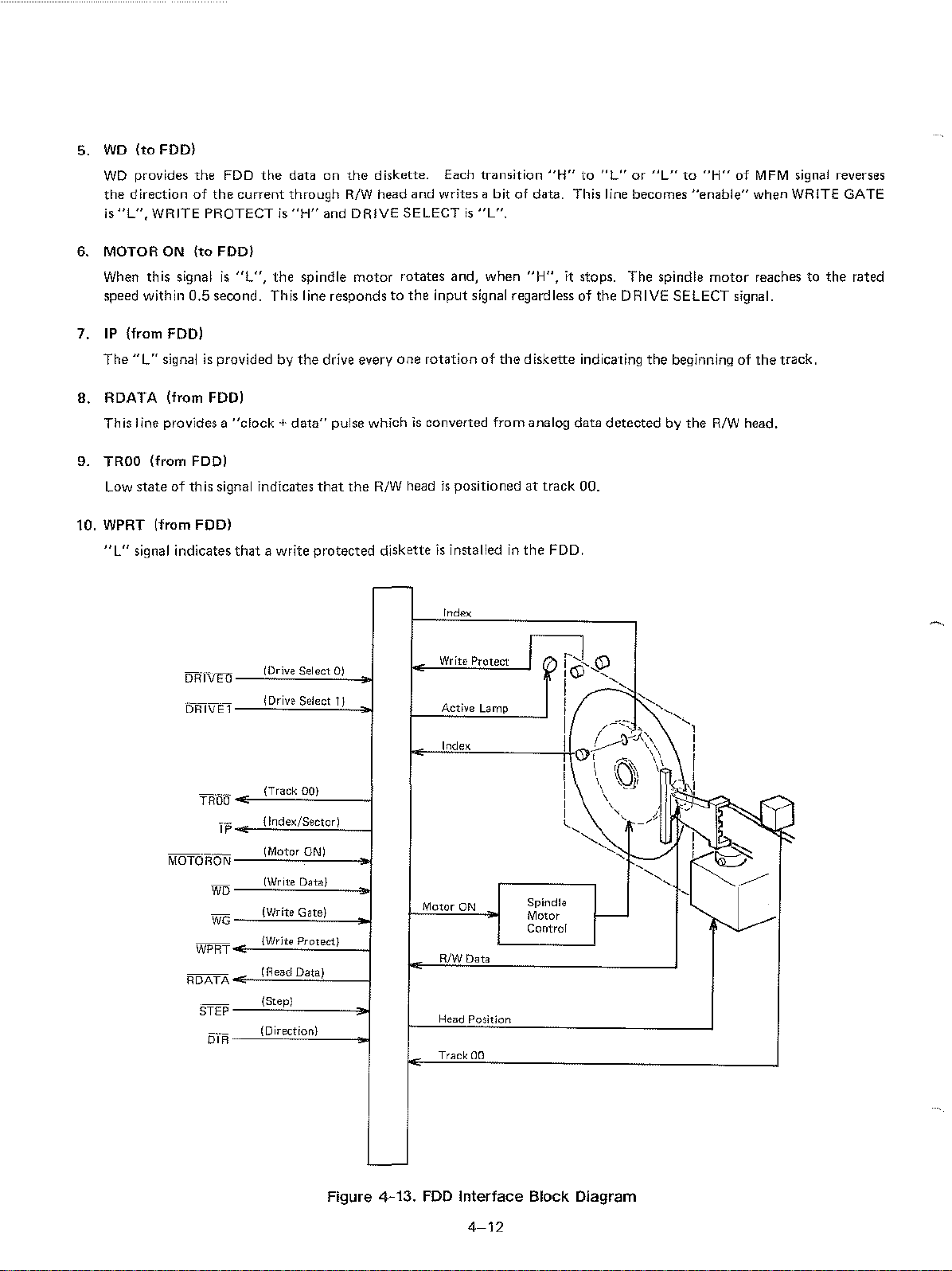

Figure 4"13 shows

1,

Interface Signals

DRIVEO

When eitherofthe

output

and

lines

HSYNC

the

DRIVE1

and

turn

FDD

two

lelR

NC3

lOA

4

lOB

5

lOC

NC

6

100

1

lCLK

(Floppy

(to

the

Disk Drive) interface block diagram. Each signal has a specified

Fool

input

lines

drive select LED

20A

20B

20C

200

12

8

I-'-"

12

.-'-'

~

4 Ml1

PR

0

0

C 0

CLR

+13

V"

M7

9 VSRET 10

I-""'-

8

2CLR

2CLK

M7

;1/2

Figure 4-12. Flicker Suppression Circuit

becomes

on.

"L",

DRIVE

only

SELECT (0

the

"L"

signal drive can respondtothe

or1)is

determined

HLDEN

91

M29

by plugginginthe

BUSRO

B

function

input

for FDD.

lines, gate

shorting plug.

the

2.

OIR

DIRisa

head moves

outside

a STEP pulse.

3.

STEP

STEP moves

least

4.

WG

"L"

signal

(to

Fool

control

edgeofthe

{to

Fool

"seek+settling"

(to

FDO)

level signal allows

is

"L"orthe

signal which defines

toward

the

R/W headbyone

driveisnot

the

directionofmotionofthe

the

centerofthe

disk (STEP OUT). Direction changeofthe

timetoassure secure

the

FDOtowrite

selected.

disk (STEP

track

read/write.

dataonthe

"H"

IN~.

per

one

pulse. After receiving

diskette.

level signal allows

I'f

the

the

R/W

head.Ifthe

input

signal

is

"H",

head

motion

This signal becomes ineffective when WRITE PROTECT

FDOtoread

must

the

final STEP pulse,

the

input

the

R/W

head moves

be made before

data

storedonthe

signalis"L",

towards

the

FDD receives

the

drive must

diskette.

the

R/W

the

wait

at

5.

WO

(to

FOO)

WD

provides

the

directionofthe

is

"L",

the

FDD

the

dataonthe

current

through

WRITE PROTECTis"H"

diskette. Each transition

R!W

head and writes a bitofdata. This line becomes

and DRIVE SELECTis"L".

"H"

to

"L"or"L"

to

"H"

"enable"

of

MFM

signal reverses

when WRITE GATE

6. MOTOR ON

When this signal

speed within

7.

IP

(from FDOl

The

"L"

signalisprovidedbythe

8.

ROATA (from FOOl

This line provides a

TROD

9.

(from

Low

stateofthis signal indicates

10. WPRT (from

"L"

signal indicates

(to

FOO)

is

"L",

the

spindle

0.5

second. This line respondstothe

"clock+data"

motor

drive

everyone

pulse whichisconverted from analog data

Fool

that

the

Fool

that

a write pl"Otected disketteisinstalledinthe

DR

IVEa_--"I

D~c~i,"e"S~e"'

"C",,,O"'~..J

I"Otates

and, when

input

signal regardlessofthe DRIVE SELECT signal.

rotationofthe

R!W

headispositionedattrack 00.

-

Index

Active Lamp

"H",

it stops. The spindle

diskette indica'ting

detectedbythe

FDD,

the

beginning of

motor

R/W

reachestothe

the

track.

head.

rated

TFi'oo

WD

WPRT

RDATA

STEP

OrR

(Track 00)

~---'-=="'----I

_

_

,,'~Wc"'c,"cDe"~'~"''-_..J

{Write Protect)

~--"'==="-----I

(Read Data)

~====---I

_

_

"(S~''''P~I

(Dirsction)

-==="--~

-;..J

-

Figure 4-13.

Motor

ON

R!W

Data

Head

POSition

Track 00

FDD

Interface Block Diagram

Spindle

Motor

Control

4-12

FDD

Control Circuit

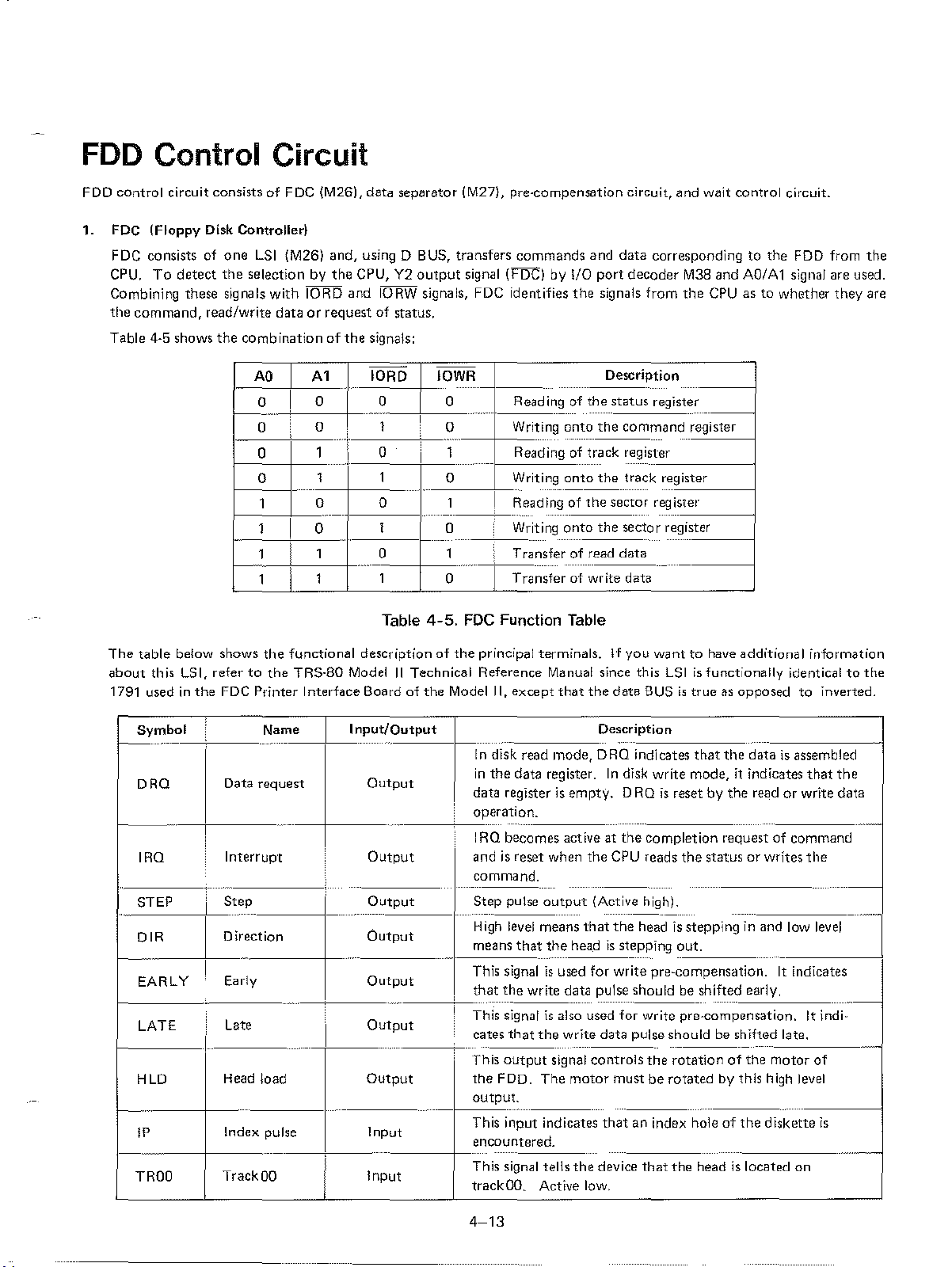

FDD cOntrol

1.

FOe (Floppy Disk Controller)

FOe

CPU.

Combining

the

Table 4-5 shows

circuit

consists of

To

detect

these

command,

consists

one

the

signals

read/write dataorrequestofstatus.

the

I--'---t--

l-~,~,

I--\-,c-

+_0_-1

I--

\--\-'---1--+,

1-1----'--+

of

FOe (M26), data separator (M27), pre-compensation

LSI (M26) and, using 0 BUS, transfers

selectionbythe

with

lORD

combinationofthe

AO

+!

_c

o , 0

o J

1 0 0 1 I Reading of

--+!

-C

,

1 I 1 0 Transfer of read

1 1

CPU, Y2

and

IORW signals, FOG identifies

signals:

Al

O

_+_

1 1

"'----j--,c---j

O

lORD

I----'C=---t- -

0 I 0 1__Rc'c'=dcin_g

,1

+----:0----:+'

----f-

-=----+---=

lOT

Table

output

signal (FOG) by

IOWR

0 Writing

-,

-r---:c

__

I

1_--=O

__

0-

4-5.

FOe Function Table

--

__

+_Writin

Writing

-+-

-1----'-'

commands

..

__

?ft~~_status

onto

-

R

eading 0

g

ont_o_'_h_etrack

_

onto

ransfer of write data

and

data

liD

port

the

signals

Description

the

command register

f k .

trac

the

sector register'

the

sector

data

circuit,

re,g':":':'

and

wait

control

correspondingtothe

decoder M38 and

from

the

CPUasto

regjst~r

_

---1

re,gc"c":'

__

-I

C

re···g·

,,-,-,-,

--l

----I

AD/A1

circuit.

FDD from

signa! are used.

whether

they

the

are

The

table

below shows

about

this LSI, refertothe

1791 usedinthe

Symbol

I---

--

DRQ

the

functional descriptionofthe

TRS-80 ModelIITechnical Reference Manual since this

FDC Printer Interface Boardofthe

Name

Data request

1

IRQ Interrup't

-

STEP

"

DI~:~tion

I-

EARLY Early

LATE

i

1-

Step

Late

I

HLD

I-

IP

-.

TROO

Head load

Index pulse

-----

Track

00

Input/Output

Output

Output

Output

Output

!

Output

,,,.-

Input

I

Output

Output

Input

principal terminals. I'f

Model II,

-

-

except

that

In

disk read mode,

in

the

data register.Indisk write mode, it indicates

data registerisemptY. DRQis

operation.

IRO becomes activeatthe

andisreset when the CPU reads

command.

----

Step pulse

-

High

means

This signalisused for write pre-compensation.

that

This signalisalso used for write prs·compensation. It indicates

This oUtput signal controls

the

output.

This input indicates

encountered.

This signal tells

trackOO. Active low.

output

level

means

that

the

headisstepping

the

write data pulse should be shifted eariy.

thatthe

FDD. The

wl'ite data pulse should be shifted late.

motor

the

you

wanttohave additional information

LSIisfunctionally identicaltothe

the

data

BUSistrueasopposedtoinverted.

Description

ORO

indicates

completion requestofcommand

..

_--

(Active high).

..

_-.

that

the

headisstepping in and low

mustberotatedbythis high

that

an index holeofthe

device

that

that

resetbythe

the

__

.-

out.

the

rotationofthe

the

headislocated

statusorwrites

the

dataisassembled

readorwrite data

---

-

that

the

It indicates

motor

level

diskette

on

the

..~--

-

--

level

--

of

is

-

4-13

j

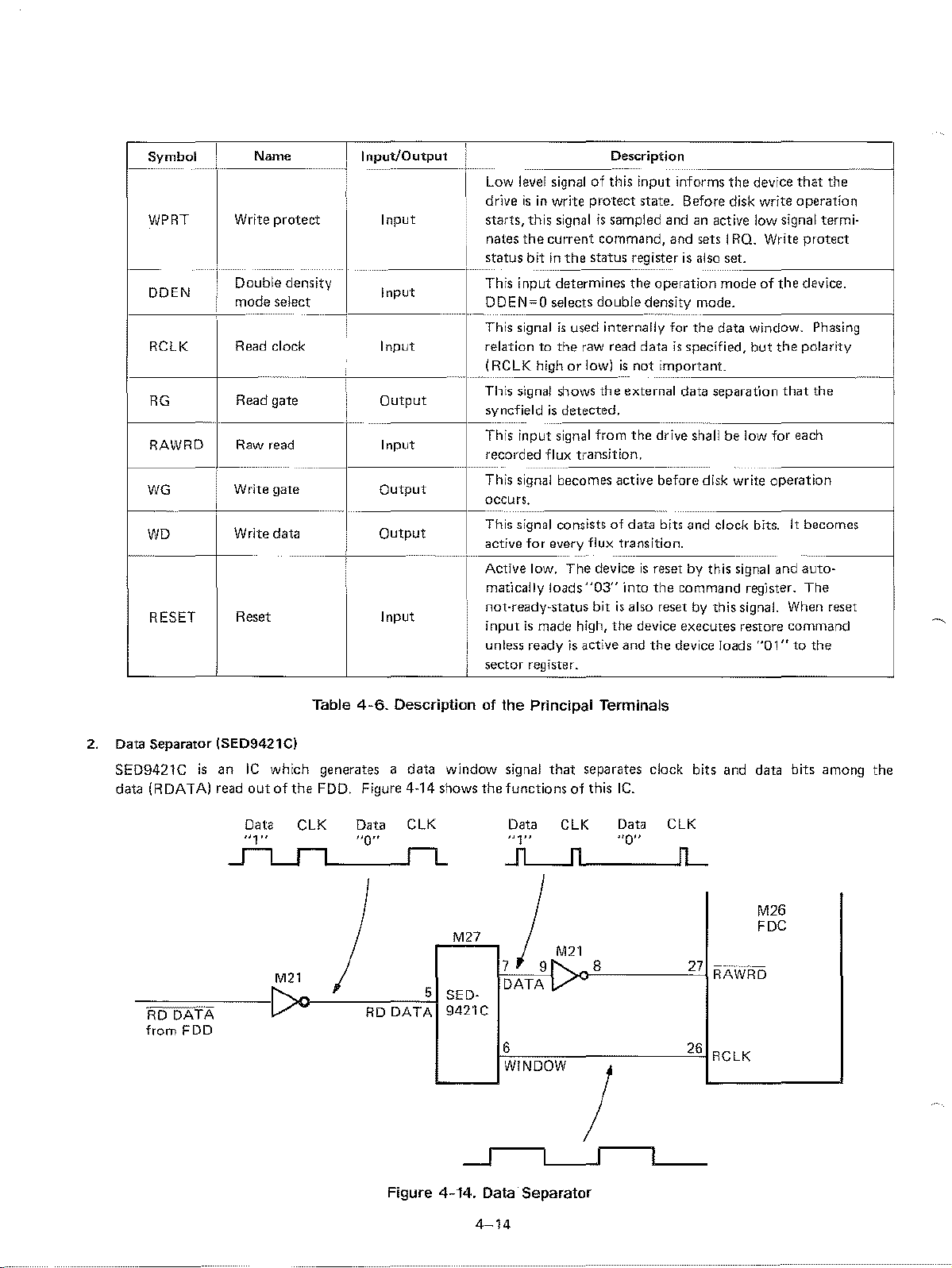

Symbol

- -----

WPRT

--

DDEN

RClK

RG

RAWRD Raw read

WG

Name

Write

protect

Double density

mode select

Read clock

Read gate

Write gate

-

-----

f---

WD

RESET

Write data

Reset

Input/Output

Input

Input

Input

Output

Input

Output

Output

Input

low

level signalofthis input informs

drive

is

in write

starts, this signalissampled and an active low signal termi·

nates

the

current

status

bitinthe

This input determines

DDEN",O selects

This signalisused internally for

relationtothe

(RClK

This signal shows

syncfield

This input signal from

recorded flux transition.

This signal becomes active before disk write

occurs.

This signal consistsofdata bits and clock bits. It becomes

active for every flux transition .

Active low.

matically loads

not·ready"status

inputismade high,

unless readyisactive and

sector register.

highorlow)isnot important.

is

~

detected.

--------

I.

-"'-

..

I

Description

protect

command, and sets I

status registerisalso set.

double

raw read dataisspecified,

the

The

deviceisresetbythis signal and

"03"

bitisalso I'eset by this signal. When reset

the

device

state. Before disk write operation

RQ.

Write pr-otect

the

operation

density mode.

external data separat"lon

the

drive shallbelow for each

into

the

the

device executes restore command

the

modeofthe

the

data windoW. Phasing

but

operation

command register.

device loads

"01"tothe

the

that

that

the

device.

polarity

the

auto·

The

.~..~

-

2. Data

Separator

SE09421C

data (RDATA) read

·AD

from FDD

is

DATA

(SED9421C)

an

IC

which generates a

outofthe

Data

"1"

M21

Table

FDO. Figure

ClK

/

4-6.

Description of the Principal Terminals

data

Data

RD

4·14

ClK

DATA

window signal

shows

the

M27

5

SED·

9421C

7

6

that

functionsofthis

Data

"1"

Jl

)

DATA

WINDOW

ClK

nl-_---.JIL

M21

9

separates clock bits and data bits among the

IC.

Data

ClK

"0"

M26

FDC

----

8

27

26

RAWRD

RCLK

-

Figure 4-14. Data Separator

4-14

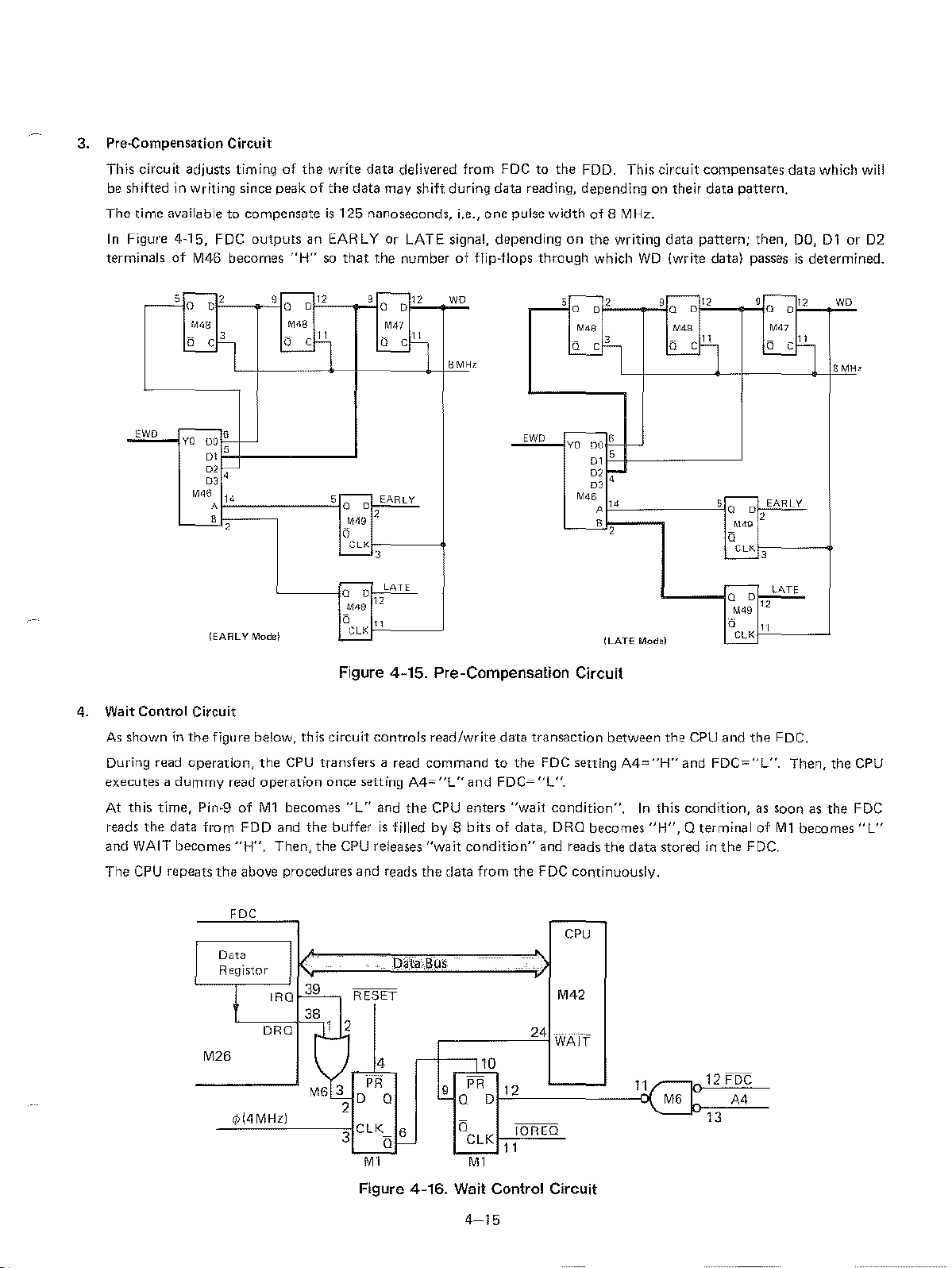

3.

Pre.compensation

This circuit adjusts timingofthe

be

shifted in writing since peakofthe

The

time availabletocompensate

In

Figme 4,15, FOC

terminals

of

Circuit

M46 becomes

write

data

delivered from FOGtothe

data

may shift during data reading, dependingontheir data pattern.

is

125

nanoseconds, i.e., one pulse width

outputsanEAR LYOrLATE signal, dependingonthe writing data pattern; then,

"H"

so

that

the

numberofflip-flops through which

FDO. This circuit compensates data which will

of

8

MHz.

WD

(write data) passesisdetermined.

DO,

01or02

-,

o e

---'

M(,g

E....::l

~

EWD

YODO6

0'

"

",

co

M'15

A

"

,

IEARLYModel

4. Wait Control Circuit

As

shown in

During read

executes a

At

this

reads

and WAIT becomes

The

CPU

time,

the

repeats

the

figure below, this circuit controls read/write

operation,

dummy

Pin-9

data from

the

-

9 0 D

M,j8

"

91112

~1

-""

5~

,

the

GPU

read

operation

o'f

M1

becomes

Foo

and

"H",

Then,

above procedures and reads

0

~

~

Q 0

M49

Q

~

Figure 4-15. Pre-Compensation Circuit

transfers a read

once setting

"L"

the

bufferis'filled

the

CPU

o 0

M41

I,

~

2EARLY

,

LATE

"

11

A4="L"

and

the

releases

we

8MH

commandtothe

and

CPU

enters

by

8 bits

"wait

condition"

the

data from the FOC coll'tinuously.

~~2

M",

~l

-

'WO

YODO6

"

co

"

M45

A

0

data

transaction between the

FOG

setting

FOC="L".

"wait

condition".Inthis condition,asSoon as

of

data,

ORO

becomes

and reads

~

'Q

M"

~l

,

I;-

"

,

ILATE

Mode)

A4="H"

"H",

the

data storedinthe

9-12

M"

Q

~3

,..--------,

~

0,

o 0 "

M"

-1

EARLY

LATE

e

"

sr;;--

WO

8

~M4~1:2

Q

1"1

L5

CPU

and

the

FOG.

and

FOC="L".

Q terminal oi' Ml becomes

Then, the

the

FoC.

Mel

CPU

FOC

"L"

ORO

M26

~

M~;~

_

...:£.¢

'C14",M~H:.:',-)

----01

3

eLK

~I"-

MI

Figure 4-16. Wait Control CirCUit

CPU

r-

d

9 aPR0

6

Q

4-15

--'2C'j4

WATf

10

12

g---'::===---'6(~~~J~~'

f

elK

IOREO

11

MI

lll'M6

A4

~2=F~D~e==

13

Power Supply and Reset Circuit

The power supply circuit consists of a regulator Ie, capacitors, resistors, coils, and a diode (ZD101) determined for

reference voltage

modulator, and +5

The RESET circuit consistsofT101,

proper level; Rl01 and T101 provide hysteresistothe

of

vee. This circuit generates +5-volt and +12-volt power - +12 volt

voltissuppliedtoallofthe

T102,

les

and

except

M41

the

other

RESET signal.

and

M44

components.

in the system BUS interface

T102

detects when

is

suppliedtothe

circuit.

the

DC

FDD

and RF

voltage reaches

the

the

4-16

5/Troubleshooting

This

section

is

find

identifies

After

completing any repairs, you should re·check

of

the CHECK

Troubleshooting Flowchart

shows

the

probleminthe

the

components

LIST

you

howtogo

Troubleshooting

associated

evenifthe

about

with

location and

solving a

Flowchart

the

circuitinquestion

conditionofthe

problemormalfunction

each

and

functional

refer to

and

malfunction

that

has been identified.

the

section

provides remedial

item accordingtothe CHECK LIST. You

are

not

indicated by

instructions.

readily clear.

the

number.

All

you

Each section

havetodo,

can

make

then

use

(

~~-l'---~~

- Doesn't workatall?

-<::::::::::==~::::~~~-==~

START )

.~~~-----1'

YES

~

~

NO

Fan ma'tOr doesn't

rotate?

YES

2

NO

~::::::::::::::::=~L~E~O~P~O~W~'~C";~"~d~;"'Et:O~C

-

doesn't

light? V

==:::::::::==~~YCECS~

~.~f?\

NO

System

doesn't

control program?

load

the

-----

YES

4

NO

FDD

doesn't

'function?

YES

YES

6

7

NO

- HomeTVdoesn't

~::::::::::==:;~~::::::-:-~-----~

END

function?

5-1

-------

-

~

Checking Procedure

1. Doesn't workatall.

Q

,

I

Check

the

power.

1.Isthe

2.

3.

~-------,-------

plugofAC

1$

the

power switch ON?

Isn't

the fuse

If

Then replace the fuse.

blown,

blown?

check the power transformer and

cord

plugged

(Itisin the fuse holder located on the rear side.)

into

(AC250V

theACoutlet?

Dl01-0104

1A)

~-~~~

and ClOT on the Power Supply

PCB

unit.

Check the power supply

1.

Isn't the fuse

If

blown, check the resistance between pin 15 and pin 6 of

(AC125V

2.

Is

15 - 25V appliedtothe

If

not, check

3.

Check

output

al vee.

b)

+12V.

,--------,-----------~-

Check

the

RESET signal.

1.

Is

it high level (2.5 - 5.25V)atpin 10ofM2l ?

If

not, check below.

2.

Is

the

voltageatthe

If not, check

3.

Is

the

voltageatthe cathodeof0106

If

not, check R102,

If OK, check tile cable from Power Supply

circuit.

F10l

blown?

3A)

cathode of

power

transformer and

voltages.

+5V

±O.25V

If

not,

check

ZD101,VR101, R107.

andMl01.

+12V fO.6V

If

not, check

collector of n 02 low level(0-

Rl03, Rl04,

Rl06,

Rlll,

0101?

Cl04, Cl05,

Rl05

and

high level (4.5 -

0106

and

Dl01

n02.

n01.

M10l,

- D104.

Rl09,R110,ClOG, e1C?, Cl08, ClOg, LT02, L

Cl06,

L10l and Ml01.

0.5V)?

5.25V)?

PCBtoMain

PCB,

Then replace

C77 and

the

M2l.

fuse.

103

Check

the

connectionofall

connectors.

(to next pagel

5-2

......

--~_

.._ ..

_-----

------

Check

the

Main

,.

Check all

a)

Pin 8ofM37

b)

Pin11of

c)

Pin 6ofM42

d} Pin 24ofM26

2. Check all

PCB.

dock

ICs.

signals.

M47

I

...

16 MHz

If

not,

check M37, R24, R26, C44, C45, C46, C51, C52 and

...

8 MHz

If

not,

check M47.

...

4 MHz

If

not, check M14 and M27.

...

1 MHz

If

not,

check M27

and

Xl.

M32.

Trytoreplace

2. Fan motor doesn't rotate.

Check

the

Refer to

Check

the

the

FDD unit.

power.

"1.

Doesn't workatall".

fan motor.

END

2

-_

.......•

~-,-------------

~--,I_~

( END )

5-3

3.

LED

power indicator doesn't light.

0)

Check

the

Refer to

r------~~~

Check

the

Check

the

4.

System

doesn't