5

www.schematic-x.blogspot.com

4

3

2

1

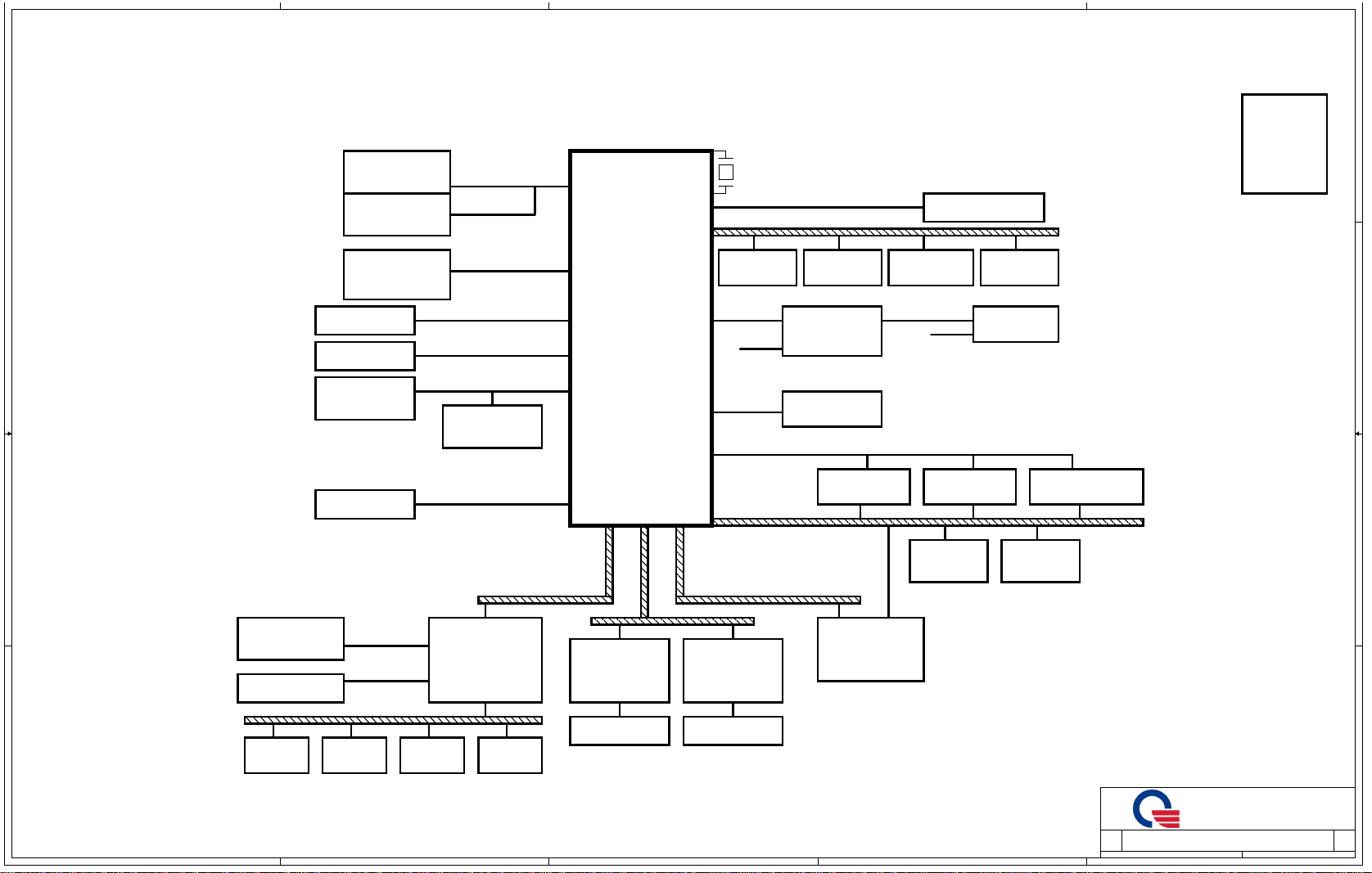

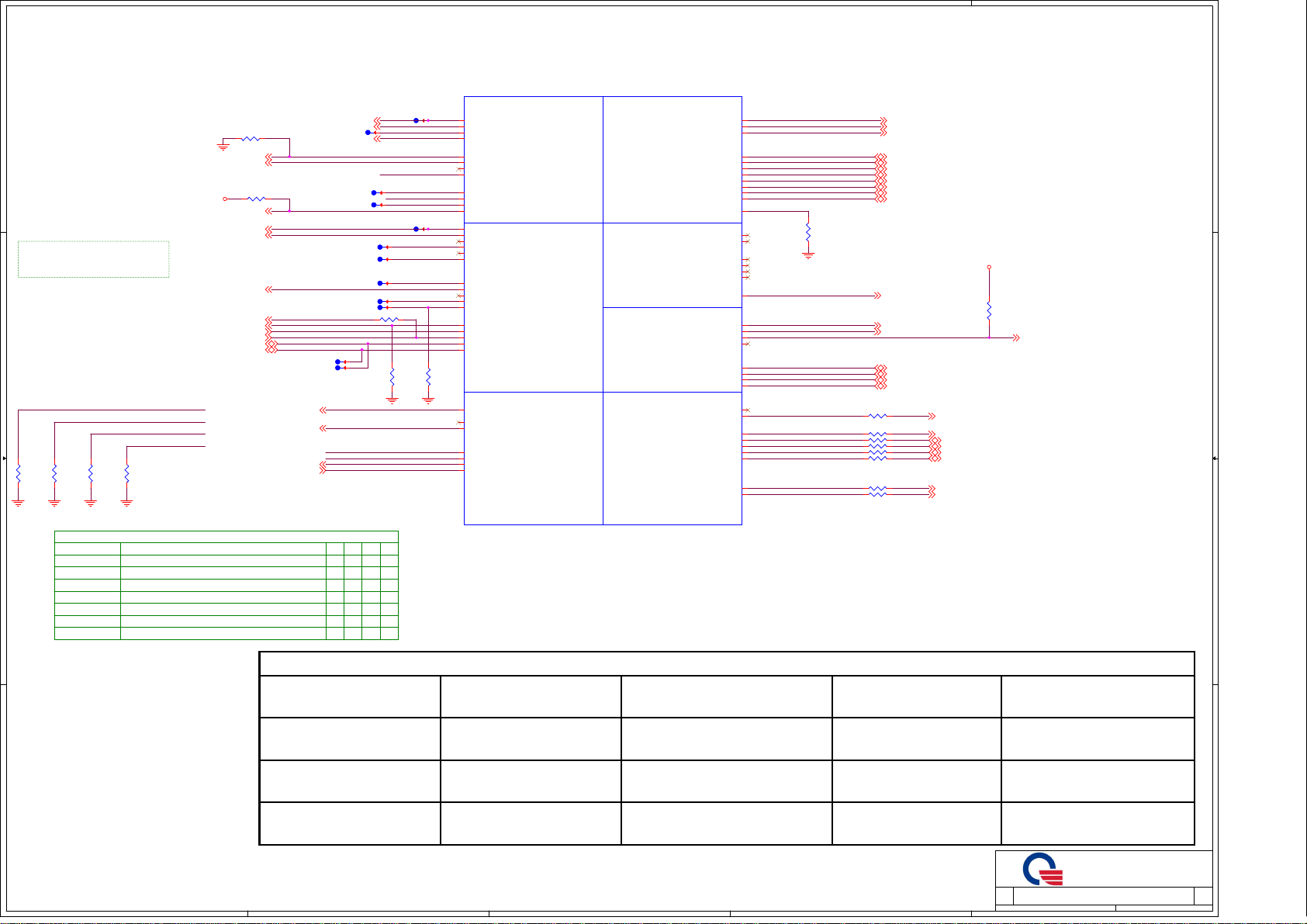

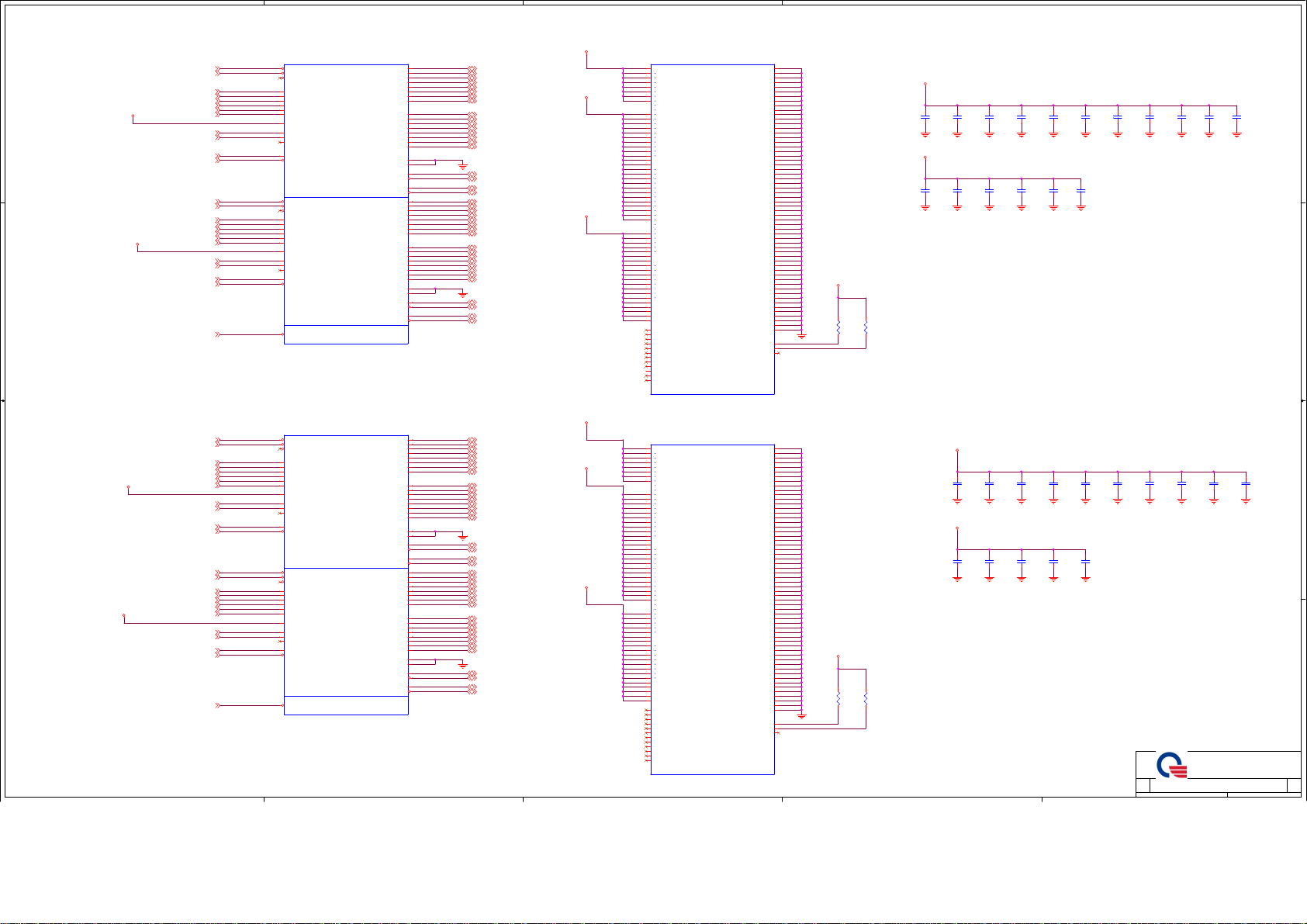

Intel Apollo Platform Block Diagram

PCB 6L STACK UP

D D

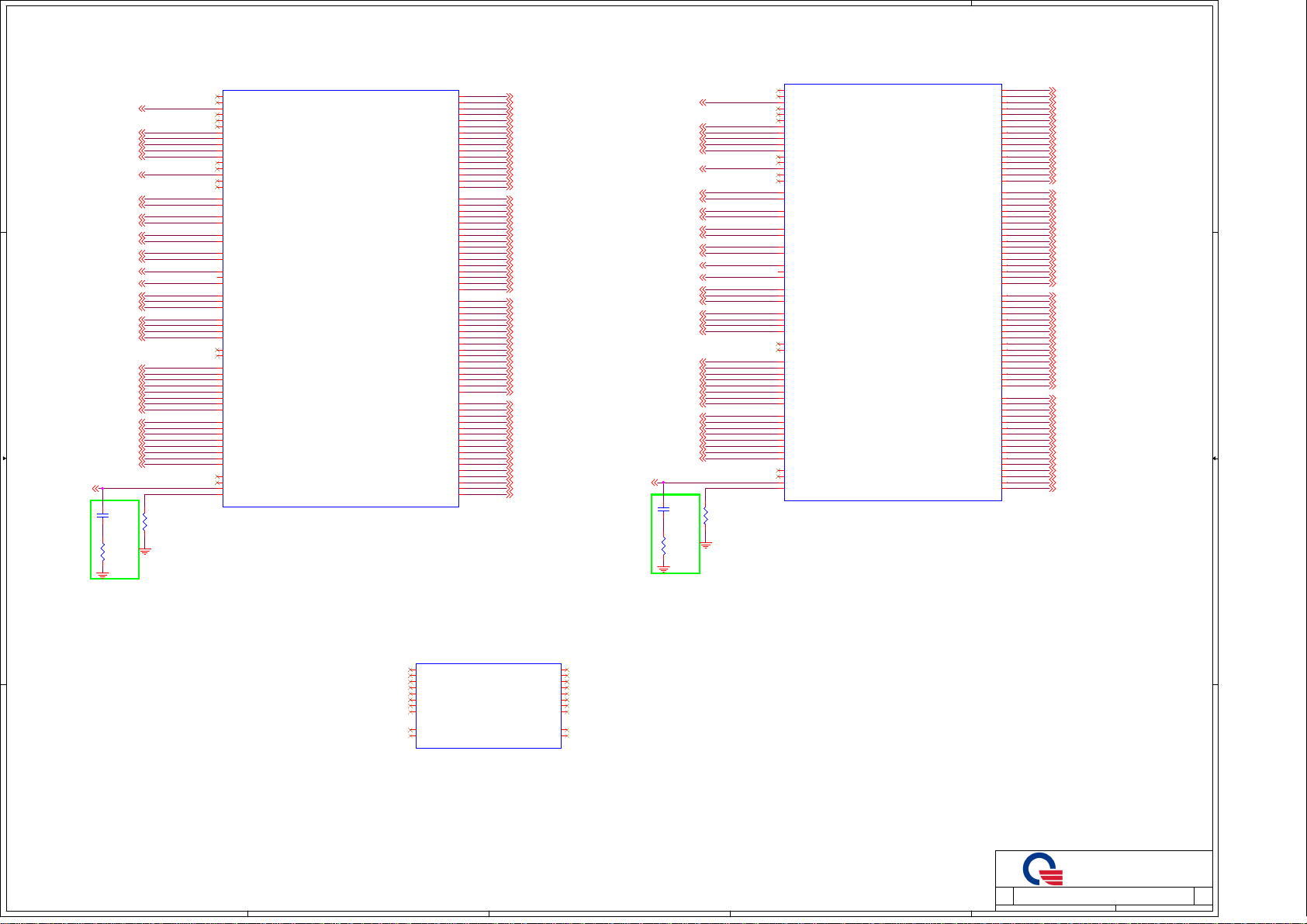

LPDDR4 SO-DIMM

Memory Down

CH0

LPDDR4 SO-DIMM

Memory Down

CH1

PAGE 11

PAGE 12

EMMC 5.0

16Gb/32GB/64GB

LPDDR4 1600/2133/

2400 MT/s

EMMC

Intel Apollo

32.768KHz / PAGE 6

19.2 Mhz / PAGE 4

eDP

I2C

AUDIO

eDP Conn PAGE 21

I2C0 I2C2 I2C3 I2C4

PAGE 19

H1

PAGE 35

TOUCH SCREEN

PAGE 21

TRACKPAD

PAGE 20

PAGE 18

Power : 4 ~ 6 Watt

PAGE 17

DMIC_CLK

DMIC_DATA

PAGE 24

SD

Package : FCBGA 1296

SPI

Size : 31 x 24 (mm)

Z-High : 1.32 (mm)

SPI

Tj : 80°C SDP/105°C TDP

Die Size : 8.89 x 10 (mm)

LPC

Audio Codec

DA7219-02VB6

Package : BGA32

PAGE 19

PAGE 2~10

I2S

SPEAKER AMP

MAX98357AETE+T

Package : QFN16

PCIE

DDI 0

DDI 1

USB3.0

USB 2.0

USB3.0

Port0

PAGE 19

Type-C Switch

ANX3429QN-AA-R

PAGE 27

TYPE-C Conn. DB

PAGE 36

USB3.0 Conn

Port4

NGFF Card

Half Mini Card

WLAN / BT Combo

Port4

PAGE 25

Port2

Port5

&

PAGE 23

USB3,1 TYPE-C

USB2.0

Port0

Port1

USB3.0 Conn DB

PAGE 36

Port3

Port6

H1

PAGE 35

PAGE 26

CAMERA

Port3

USB3,1 TYPE-C

Conn. DB

Port1

Port4

PAGE 21

PAGE 36

uSD

C C

PAGE 18

FINGER PRINT

PAGE 20

SPI ROM(16M)

W25Q128FWSIF

PAGE 14

TPM

SLB9670VQ1.2

_FW6.40

DMIC

PAGE 21

B B

SPI ROM(512K)

W25Q40EWSNIG

PAGE 14

Embedded Controller

NPCX586GA0BX

Package : BGA128

Keyboard

PAGE 20

LAYER 1 : TOP

LAYER 2 : VCC

LAYER 3 : IN1

LAYER 4 : IN2

LAYER 5 : GND

LAYER 6: BOT

HP+MIC

A A

TYPE-C

PAGE 27

TYPE-C DB

PAGE 36

GYRO

PAGE 22

CHARGER

PAGE 29

PAGE 19

SPEAKER

PAGE 19

QQQuuuaaannntttaaa CCCooommmpppuuuttteeerrr IIInnnccc...

PPPRRROOOJJJEEECCCTTT ::: ZZZRRRXXX

BBBLLLOOOCCCKKK DDDIIIAAAGGGRRRAAAMMM

1

333888111

5

SSSiiizzzeee DDDooocccuuummmeeennnttt NNNuuummmbbbeeerrr RRReeevvv

DDDaaattteee::: SSShhheeeeeettt ooofff

4

3

2

FFFrrriiidddaaayyy,,, JJJuuulllyyy 222111,,, 222000111777

111AAA

5

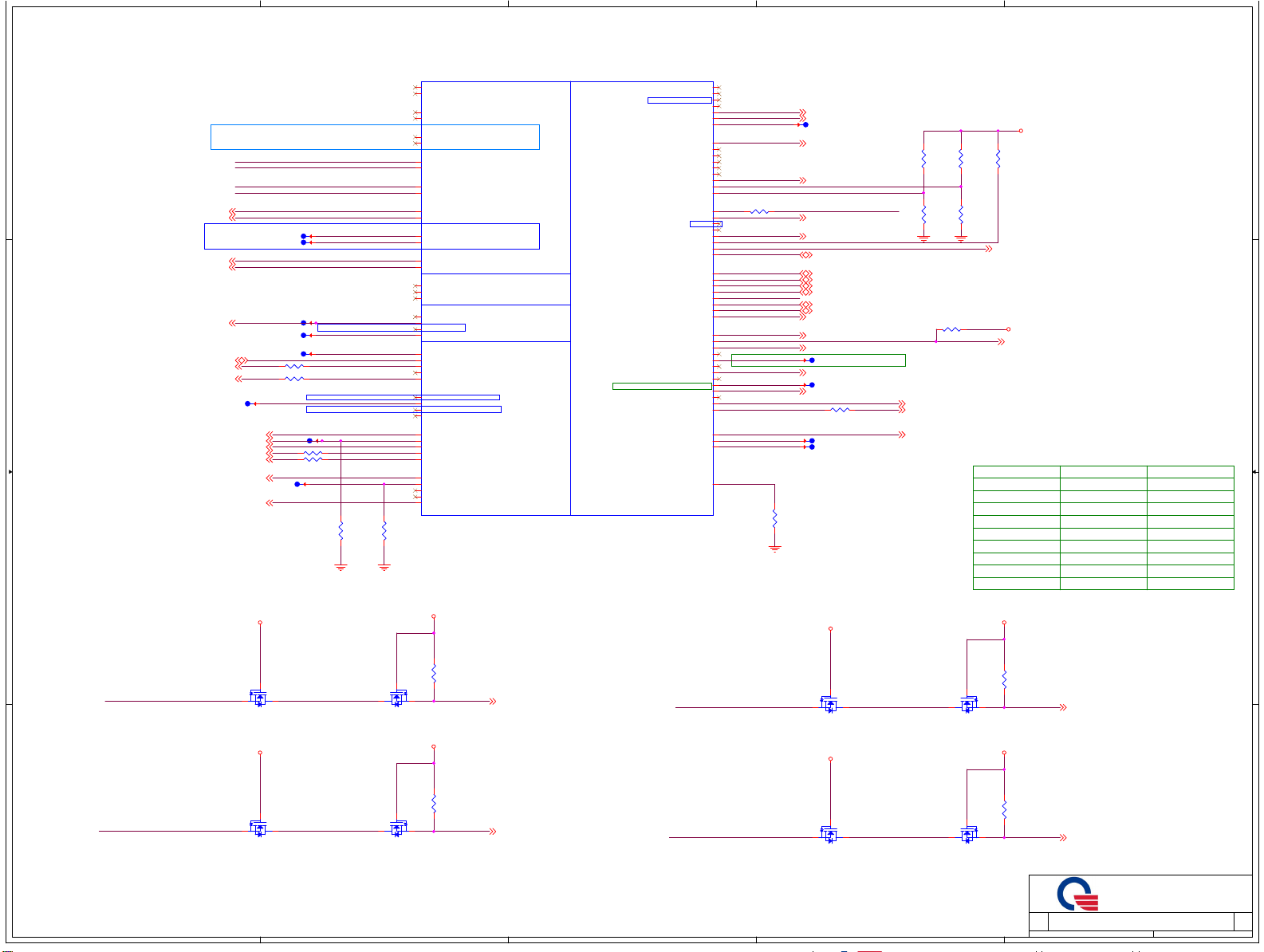

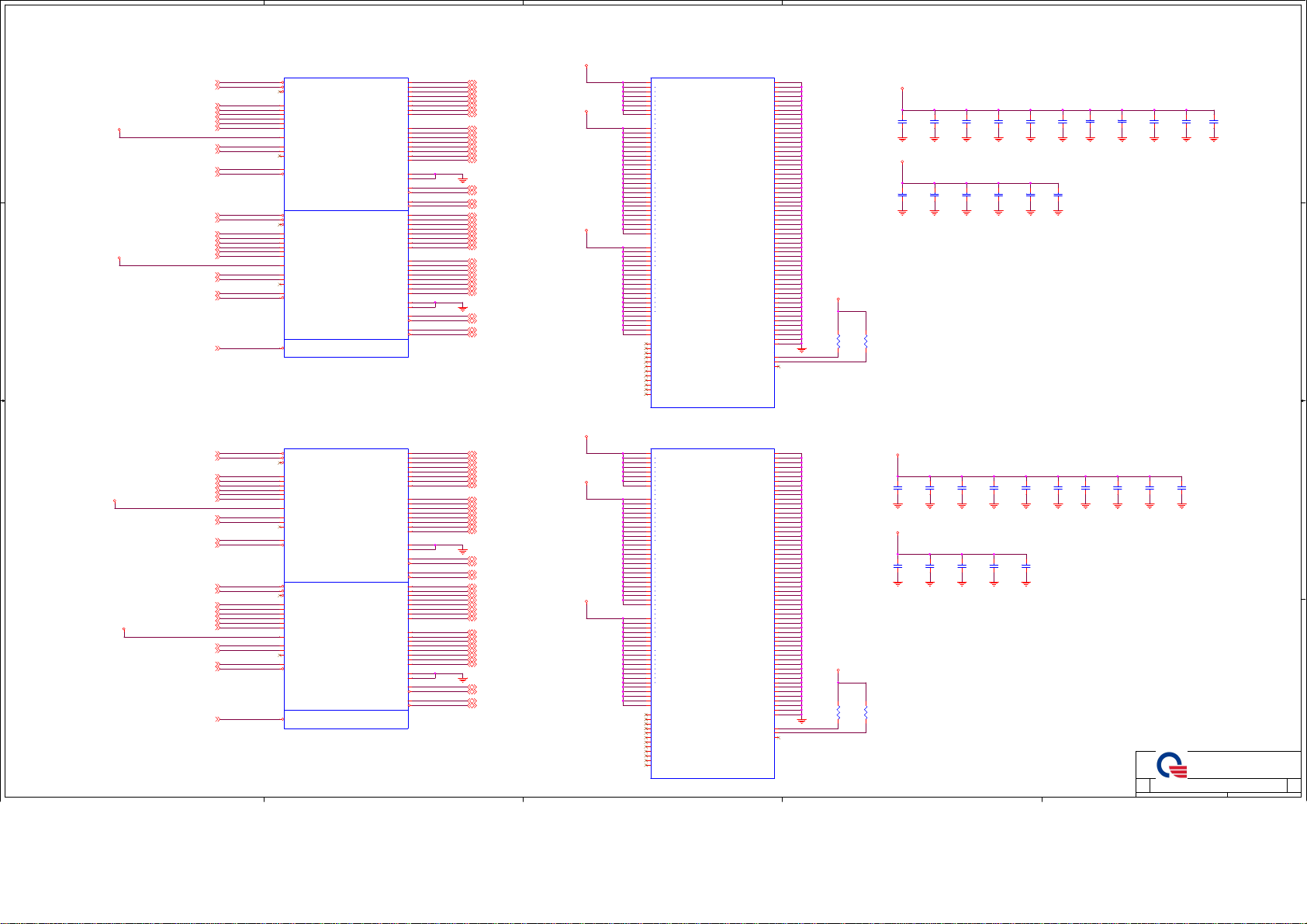

U4A

BG57

MEM0_MA15_CAA9_NC

BG56

MEM0_MA14_CAA8_NC

D D

C C

DDR_RST_CH0_L[11]

B B

DDR_0B_CA<0>[11]

DDR_0A_CA<4>[11]

DDR_0A_CA<0>[11]

DDR_0A_CA<3>[11]

DDR_0A_CA<1>[11]

DDR_0A_CA<2>[11]

DDR_0B_CA<5>[11]

DDR_0B_CLK_P[11]

DDR_0B_CLK_N[11]

DDR_0A_CLK_P[11]

DDR_0A_CLK_N[11]

DDR_0A_CKE<0>[11]

DDR_0A_CKE<1>[11]

DDR_0B_CKE<0>[11]

DDR_0B_CKE<1>[11]

DDR_0A_CA<5>[11]

DDR_0B_CA<4>[11]

DDR_0B_CA<3>[11]

DDR_0B_CA<2>[11]

DDR_0B_CA<1>[11]

DDR_0B_CS<1>[11]

DDR_0A_CS<0>[11]

DDR_0A_CS<1>[11]

DDR_0B_CS<0>[11]

DDR_0B_DQS_3_P[11]

DDR_0B_DQS_3_N[11]

DDR_0B_DQS_2_P[11]

DDR_0B_DQS_2_N[11]

DDR_0B_DQS_1_P[11]

DDR_0B_DQS_1_N[11]

DDR_0B_DQS_0_P[11]

DDR_0B_DQS_0_N[11]

DDR_0A_DQS_3_P[11]

DDR_0A_DQS_3_N[11]

DDR_0A_DQS_2_P[11]

DDR_0A_DQS_2_N[11]

DDR_0A_DQS_1_P[11]

DDR_0A_DQS_1_N[11]

DDR_0A_DQS_0_P[11]

DDR_0A_DQS_0_N[11]

DDR_RCOMP_CH0

C4881

R276

0.1u/16V_4

105_1%_4

R4532

10_5%_4

colsed to U4 AR34 pin

within 100 mils

BG46

MEM0_MA13_CAB0_CAB0

BG54

MEM0_MA12_CAA5_NC

BH55

MEM0_MA11_CAA6_NC

BH49

MEM0_MA10_CAB6_NC

BG52

MEM0_MA9_CAA4_CAA4

BH53

MEM0_MA8_CAA1_CAA0

BG55

MEM0_MA7_CAA3_CAA3

BG53

MEM0_MA6_CAA0_CAA1

BJ52

MEM0_MA5_CAA2_CAA2

BE41

MEM0_MA4_NC_NC

BD41

MEM0_MA3_NC_NC

BH51

MEM0_MA2_CAB5_CAB5

BG51

MEM0_MA1_CAB9_NC

BG50

MEM0_MA0_CAB7_NC

BD45

MEM0_CLKP0_CLKPB_CLKPB

BE45

MEM0_CLKN0_CLKNB_CLKNB

BB48

MEM0_CLKP1_CLKPA_CLKP

BD48

MEM0_CLKN1_CLKNA_CLKN

BH61

MEM0_CKE0_CKE0A_CKE0A

BH60

MEM0_CKE1_CKE1A_CKE1A

BH58

MEM0_NC_CKE0B_CKE0B

BJ58

MEM0_NC_CKE1B_CKE1B

BH57

MEM0_BA2_CAA7_CAA5

BG49

MEM0_BA1_CAB8_NC

BJ48

MEM0_BA0_CAB2_CAB4

BG47

MEM0_RASN_CAB3_CAB3

BG48

MEM0_WEN_CAB4_CAB2

BH47

MEM0_CASN_CAB1_CAB1

BA41

MEM0_CS1N_CSB1N_CS1B

AR43

MEM0_CS0N_CSA0N_CS0A

AT43

MEM0_NC_CSA1N_CS1A

BB41

MEM0_NC_CSB0N_CS0B

AW41

MEM0_ODT1_ODTB_NC

AW43

MEM0_ODT0_ODTA_NC

BG36

MEM0_DQSP7_DQSPB3_DQSPB3

BH35

MEM0_DQSN7_DQSNB3_DQSNB3

BB35

MEM0_DQSP6_DQSPB2_DQSPB2

BD35

MEM0_DQSN6_DQSNB2_DQSNB2

BJ42

MEM0_DQSP5_DQSPB1_DQSPB1

BG42

MEM0_DQSN5_DQSNB1_DQSNB1

AV39

MEM0_DQSP4_DQSPB0_DQSPB0

AW39

MEM0_DQSN4_DQSNB0_DQSNB0

BD52

MEM0_DQSP3_DQSPA3_DQSPA3

BB52

MEM0_DQSN3_DQSNA3_DQSNA3

BB59

MEM0_DQSP2_DQSPA2_DQSPA2

BB58

MEM0_DQSN2_DQSNA2_DQSNA2

AT59

MEM0_DQSP1_DQSPA1_DQSPA1

AT58

MEM0_DQSN1_DQSNA1_DQSNA1

BB63

MEM0_DQSP0_DQSPA0_DQSPA0

BC62

MEM0_DQSN0_DQSNA0_DQSNA0

AR35

MEM0_VREFCA_VREFCA_NC

AT34

MEM0_VREFDQ_VREFDQ_NC

AR34

MEM0_RESETN_NC_RESETN

AV34

MEM0_RCOMP_RCOMP_RCOMP

CPU_APL_1296P

4

MEM0_DQ63_DQB31_DQB31

MEM0_DQ62_DQB30_DQB30

MEM0_DQ61_DQB29_DQB29

MEM0_DQ60_DQB28_DQB28

MEM0_DQ59_DQB27_DQB27

MEM0_DQ58_DQB26_DQB26

MEM0_DQ57_DQB25_DQB25

MEM0_DQ56_DQB24_DQB24

MEM0_DQ55_DQB23_DQB23

MEM0_DQ54_DQB22_DQB22

MEM0_DQ53_DQB21_DQB21

MEM0_DQ52_DQB20_DQB20

MEM0_DQ51_DQB19_DQB19

MEM0_DQ50_DQB18_DQB18

MEM0_DQ49_DQB17_DQB17

MEM0_DQ48_DQB16_DQB16

MEM0_DQ47_DQB15_DQB15

MEM0_DQ46_DQB14_DQB14

MEM0_DQ45_DQB13_DQB13

MEM0_DQ44_DQB12_DQB12

MEM0_DQ43_DQB11_DQB11

MEM0_DQ42_DQB10_DQB10

MEM0_DQ41_DQB9_DQB9

MEM0_DQ40_DQB8_DQB8

MEM0_DQ39_DQB7_DQB7

MEM0_DQ38_DQB6_DQB6

MEM0_DQ37_DQB5_DQB5

MEM0_DQ36_DQB4_DQB4

MEM0_DQ35_DQB3_DQB3

MEM0_DQ34_DQB2_DQB2

MEM0_DQ33_DQB1_DQB1

MEM0_DQ32_DQB0_DQB0

MEM0_DQ31_DQA31_DQA31

MEM0_DQ30_DQA30_DQA30

MEM0_DQ29_DQA29_DQA29

MEM0_DQ28_DQA28_DQA28

MEM0_DQ27_DQA27_DQA27

MEM0_DQ26_DQA26_DQA26

MEM0_DQ25_DQA25_DQA25

MEM0_DQ24_DQA24_DQA24

MEM0_DQ23_DQA23_DQA23

MEM0_DQ22_DQA22_DQA22

MEM0_DQ21_DQA21_DQA21

MEM0_DQ20_DQA20_DQA20

MEM0_DQ19_DQA19_DQA19

MEM0_DQ18_DQA18_DQA18

MEM0_DQ17_DQA17_DQA17

MEM0_DQ16_DQA16_DQA16

MEM0_DQ15_DQA15_DQA15

MEM0_DQ14_DQA14_DQA14

MEM0_DQ13_DQA13_DQA13

MEM0_DQ12_DQA12_DQA12

MEM0_DQ11_DQA11_DQA11

MEM0_DQ10_DQA10_DQA10

MEM0_DQ9_DQA9_DQA9

MEM0_DQ8_DQA8_DQA8

MEM0_DQ7_DQA7_DQA7

MEM0_DQ6_DQA6_DQA6

MEM0_DQ5_DQA5_DQA5

MEM0_DQ4_DQA4_DQA4

MEM0_DQ3_DQA3_DQA3

MEM0_DQ2_DQA2_DQA2

MEM0_DQ1_DQA1_DQA1

MEM0_DQ0_DQA0_DQA0

BJ34

BG37

BH37

BG38

BH33

BG33

BG34

BJ38

BB34

BD39

BE39

BB37

BD37

BD34

BE34

BA34

BH41

BH45

BG44

BG43

BJ40

BG40

BG39

BJ44

AW35

AR41

AT41

AT37

AR37

AW37

AV37

AR39

BB54

BA50

BB50

BD50

BE50

BF58

BD54

BE56

BD58

AV52

AY55

AV54

BF59

BD59

BB57

AY57

AY59

AT54

AT55

AV57

AV58

AU62

AU63

AV59

BD62

AW63

AW62

BD63

BG62

BE62

AY61

AY62

DDR_0B_DQ<31> [11]

DDR_0B_DQ<30> [11]

DDR_0B_DQ<29> [11]

DDR_0B_DQ<28> [11]

DDR_0B_DQ<27> [11]

DDR_0B_DQ<26> [11]

DDR_0B_DQ<25> [11]

DDR_0B_DQ<24> [11]

DDR_0B_DQ<23> [11]

DDR_0B_DQ<22> [11]

DDR_0B_DQ<21> [11]

DDR_0B_DQ<20> [11]

DDR_0B_DQ<19> [11]

DDR_0B_DQ<18> [11]

DDR_0B_DQ<17> [11]

DDR_0B_DQ<16> [11]

DDR_0B_DQ<15> [11]

DDR_0B_DQ<14> [11]

DDR_0B_DQ<13> [11]

DDR_0B_DQ<12> [11]

DDR_0B_DQ<11> [11]

DDR_0B_DQ<10> [11]

DDR_0B_DQ<9> [11]

DDR_0B_DQ<8> [11]

DDR_0B_DQ<7> [11]

DDR_0B_DQ<6> [11]

DDR_0B_DQ<5> [11]

DDR_0B_DQ<4> [11]

DDR_0B_DQ<3> [11]

DDR_0B_DQ<2> [11]

DDR_0B_DQ<1> [11]

DDR_0B_DQ<0> [11]

DDR_0A_DQ<31> [11]

DDR_0A_DQ<30> [11]

DDR_0A_DQ<29> [11]

DDR_0A_DQ<28> [11]

DDR_0A_DQ<27> [11]

DDR_0A_DQ<26> [11]

DDR_0A_DQ<25> [11]

DDR_0A_DQ<24> [11]

DDR_0A_DQ<23> [11]

DDR_0A_DQ<22> [11]

DDR_0A_DQ<21> [11]

DDR_0A_DQ<20> [11]

DDR_0A_DQ<19> [11]

DDR_0A_DQ<18> [11]

DDR_0A_DQ<17> [11]

DDR_0A_DQ<16> [11]

DDR_0A_DQ<15> [11]

DDR_0A_DQ<14> [11]

DDR_0A_DQ<13> [11]

DDR_0A_DQ<12> [11]

DDR_0A_DQ<11> [11]

DDR_0A_DQ<10> [11]

DDR_0A_DQ<9> [11]

DDR_0A_DQ<8> [11]

DDR_0A_DQ<7> [11]

DDR_0A_DQ<6> [11]

DDR_0A_DQ<5> [11]

DDR_0A_DQ<4> [11]

DDR_0A_DQ<3> [11]

DDR_0A_DQ<2> [11]

DDR_0A_DQ<1> [11]

DDR_0A_DQ<0> [11]

3

U4B

BG16

MEM1_MA15_CAA9_NC

BG15

MEM1_MA14_CAA8_NC

DDR_1B_CA<0>[12]

DDR_1A_CA<4>[12]

DDR_1A_CA<0>[12]

DDR_1A_CA<3>[12]

DDR_1A_CA<1>[12]

DDR_1A_CA<2>[12]

DDR_1B_CA<5>[12]

DDR_1B_CLK_P[12]

DDR_1B_CLK_N[12]

DDR_1A_CLK_P[12]

DDR_1A_CLK_N[12]

DDR_1A_CKE<0>[12]

DDR_1A_CKE<1>[12]

DDR_1B_CKE<0>[12]

DDR_1B_CKE<1>[12]

DDR_1A_CA<5>[12]

DDR_1B_CA<4>[12]

DDR_1B_CA<3>[12]

DDR_1B_CA<2>[12]

DDR_1B_CA<1>[12]

DDR_1B_CS<1>[12]

DDR_1A_CS<0>[12]

DDR_1A_CS<1>[12]

DDR_1B_CS<0>[12]

DDR_1B_DQS_3_P[12]

DDR_1B_DQS_3_N[12]

DDR_1B_DQS_2_P[12]

DDR_1B_DQS_2_N[12]

DDR_1B_DQS_1_P[12]

DDR_1B_DQS_1_N[12]

DDR_1B_DQS_0_P[12]

DDR_1B_DQS_0_N[12]

DDR_1A_DQS_3_P[12]

DDR_1A_DQS_3_N[12]

DDR_1A_DQS_2_P[12]

DDR_1A_DQS_2_N[12]

DDR_1A_DQS_1_P[12]

DDR_1A_DQS_1_N[12]

DDR_1A_DQS_0_P[12]

DDR_1A_DQS_0_N[12]

DDR_RST_CH1_L[12]

DDR_RCOMP_CH1

C4882

R277

0.1u/16V_4

*105_1%_4

R4533

10_5%_4

colsed to U4 AR30 pin

within 100 mils

BH3

MEM1_MA13_CAB0_CAB0

BG13

MEM1_MA12_CAA5_NC

BH13

MEM1_MA11_CAA6_NC

BG7

MEM1_MA10_CAB6_NC

BH11

MEM1_MA9_CAA4_CAA4

BG12

MEM1_MA8_CAA1_CAA0

BG14

MEM1_MA7_CAA3_CAA3

BJ12

MEM1_MA6_CAA0_CAA1

BG11

MEM1_MA5_CAA2_CAA2

BB16

MEM1_MA4_NC_NC

BD16

MEM1_MA3_NC_NC

BH9

MEM1_MA2_CAB5_CAB5

BG10

MEM1_MA1_CAB9_NC

BG9

MEM1_MA0_CAB7_NC

BD19

MEM1_CLKP0_CLKPB_CLKPB

BE19

MEM1_CLKN0_CLKNB_CLKNB

BB21

MEM1_CLKP1_CLKPA_CLKPA

BD21

MEM1_CLKN1_CLKNA_CLKNA

BG18

MEM1_CKE0_CKE0A_CKE0A

BG17

MEM1_CKE1_CKE1A_CKE1A

BH17

MEM1_NC_CKE0B_CKE0B

BJ16

MEM1_NC_CKE1B_CKE1B

BH15

MEM1_BA2_CAA7_CAA5

BG8

MEM1_BA1_CAB8_NC

BH6

MEM1_BA0_CAB2_CAB4

BJ6

MEM1_RASN_CAB3_CAB3

BH7

MEM1_WEN_CAB4_CAB2

BH4

MEM1_CASN_CAB1_CAB1

AW17

MEM1_CS1N_CSB1N_CS1B

BD17

MEM1_CS0N_CSA0N_CS0A

BB17

MEM1_NC_CSA1N_CS1A

AV17

MEM1_NC_CSB0N_CS0B

AV16

MEM1_ODT1_ODTB_NC

AW16

MEM1_ODT0_ODTA_NC

BC2

MEM1_DQSP7_DQSPB3_DQSPB3

BB1

MEM1_DQSN7_DQSNB3_DQSNB3

AT5

MEM1_DQSP6_DQSPB2_DQSPB2

AT6

MEM1_DQSN6_DQSNB2_DQSNB2

BB5

MEM1_DQSP5_DQSPB1_DQSPB1

BB6

MEM1_DQSN5_DQSNB1_DQSNB1

BB12

MEM1_DQSP4_DQSPB0_DQSPB0

BD12

MEM1_DQSN4_DQSNB0_DQSNB0

AV25

MEM1_DQSP3_DQSPA3_DQSPA3

AW25

MEM1_DQSN3_DQSNA3_DQSNA3

BJ22

MEM1_DQSP2_DQSPA2_DQSPA2

BG22

MEM1_DQSN2_DQSNA2_DQSNA2

BD29

MEM1_DQSP1_DQSPA1_DQSPA1

BB29

MEM1_DQSN1_DQSNA1_DQSNA1

BG28

MEM1_DQSP0_DQSPA0_DQSPA0

BH29

MEM1_DQSN0_DQSNA0_DQSNA0

AR29

MEM1_VREFCA_VREFCA_NC

AT30

MEM1_VREFDQ_VREFDQ_NC

AR30

MEM1_RESETN_NC_RESETN

AV30

MEM1_RCOMP_RCOMP_RCOMP

CPU_APL_1296P

2

MEM1_DQ63_DQB31_DQB31

MEM1_DQ62_DQB30_DQB30

MEM1_DQ61_DQB29_DQB29

MEM1_DQ60_DQB28_DQB28

MEM1_DQ59_DQB27_DQB27

MEM1_DQ58_DQB26_DQB26

MEM1_DQ57_DQB25_DQB25

MEM1_DQ56_DQB24_DQB24

MEM1_DQ55_DQB23_DQB23

MEM1_DQ54_DQB22_DQB22

MEM1_DQ53_DQB21_DQB21

MEM1_DQ52_DQB20_DQB20

MEM1_DQ51_DQB19_DQB19

MEM1_DQ50_DQB18_DQB18

MEM1_DQ49_DQB17_DQB17

MEM1_DQ48_DQB16_DQB16

MEM1_DQ47_DQB15_DQB15

MEM1_DQ46_DQB14_DQB14

MEM1_DQ45_DQB13_DQB13

MEM1_DQ44_DQB12_DQB12

MEM1_DQ43_DQB11_DQB11

MEM1_DQ42_DQB10_DQB10

MEM1_DQ41_DQB9_DQB9

MEM1_DQ40_DQB8_DQB8

MEM1_DQ39_DQB7_DQB7

MEM1_DQ38_DQB6_DQB6

MEM1_DQ37_DQB5_DQB5

MEM1_DQ36_DQB4_DQB4

MEM1_DQ35_DQB3_DQB3

MEM1_DQ34_DQB2_DQB2

MEM1_DQ33_DQB1_DQB1

MEM1_DQ32_DQB0_DQB

MEM1_DQ31_DQA31_DQA31

MEM1_DQ30_DQA30_DQA30

MEM1_DQ29_DQA29_DQA29

MEM1_DQ28_DQA28_DQA28

MEM1_DQ27_DQA27_DQA27

MEM1_DQ26_DQA26_DQA26

MEM1_DQ25_DQA25_DQA25

MEM1_DQ24_DQA24_DQA24

MEM1_DQ23_DQA23_DQA23

MEM1_DQ22_DQA22_DQA22

MEM1_DQ21_DQA21_DQA21

MEM1_DQ20_DQA20_DQA20

MEM1_DQ19_DQA19_DQA19

MEM1_DQ18_DQA18_DQA18

MEM1_DQ17_DQA17_DQA17

MEM1_DQ16_DQA16_DQA16

MEM1_DQ15_DQA15_DQA15

MEM1_DQ14_DQA14_DQA14

MEM1_DQ13_DQA13_DQA13

MEM1_DQ12_DQA12_DQA12

MEM1_DQ11_DQA11_DQA11

MEM1_DQ10_DQA10_DQA10

MEM1_DQ9_DQA9_DQA9

MEM1_DQ8_DQA8_DQA8

MEM1_DQ7_DQA7_DQA7

MEM1_DQ6_DQA6_DQA6

MEM1_DQ5_DQA5_DQA5

MEM1_DQ4_DQA4_DQA4

MEM1_DQ3_DQA3_DQA3

MEM1_DQ2_DQA2_DQA2

MEM1_DQ1_DQA1_DQA1

MEM1_DQ0_DQA0_DQA0

BG2

AY3

AW2

AW1

BE2

BD1

BD2

AY2

AV7

AV6

AV5

AY5

AU1

AT9

AT10

AU2

BF5

AY7

AY9

AV10

BB7

BD5

BD6

AV12

BE8

BD14

BB14

BA14

BB10

BE14

BD10

BF6

AW27

AR23

AR25

AV27

AT23

AR27

AW29

AT27

BG25

BH19

BG21

BG20

BJ24

BH23

BJ20

BG24

BD27

BD25

BB27

BE25

BD30

BE30

BB30

BA30

BJ30

BG26

BG27

BH27

BG31

BH31

BG30

BJ26

1

DDR_1B_DQ<31> [12]

DDR_1B_DQ<30> [12]

DDR_1B_DQ<29> [12]

DDR_1B_DQ<28> [12]

DDR_1B_DQ<27> [12]

DDR_1B_DQ<26> [12]

DDR_1B_DQ<25> [12]

DDR_1B_DQ<24> [12]

DDR_1B_DQ<23> [12]

DDR_1B_DQ<22> [12]

DDR_1B_DQ<21> [12]

DDR_1B_DQ<20> [12]

DDR_1B_DQ<19> [12]

DDR_1B_DQ<18> [12]

DDR_1B_DQ<17> [12]

DDR_1B_DQ<16> [12]

DDR_1B_DQ<15> [12]

DDR_1B_DQ<14> [12]

DDR_1B_DQ<13> [12]

DDR_1B_DQ<12> [12]

DDR_1B_DQ<11> [12]

DDR_1B_DQ<10> [12]

DDR_1B_DQ<9> [12]

DDR_1B_DQ<8> [12]

DDR_1B_DQ<7> [12]

DDR_1B_DQ<6> [12]

DDR_1B_DQ<5> [12]

DDR_1B_DQ<4> [12]

DDR_1B_DQ<3> [12]

DDR_1B_DQ<2> [12]

DDR_1B_DQ<1> [12]

DDR_1B_DQ<0> [12]

DDR_1A_DQ<31> [12]

DDR_1A_DQ<30> [12]

DDR_1A_DQ<29> [12]

DDR_1A_DQ<28> [12]

DDR_1A_DQ<27> [12]

DDR_1A_DQ<26> [12]

DDR_1A_DQ<25> [12]

DDR_1A_DQ<24> [12]

DDR_1A_DQ<23> [12]

DDR_1A_DQ<22> [12]

DDR_1A_DQ<21> [12]

DDR_1A_DQ<20> [12]

DDR_1A_DQ<19> [12]

DDR_1A_DQ<18> [12]

DDR_1A_DQ<17> [12]

DDR_1A_DQ<16> [12]

DDR_1A_DQ<15> [12]

DDR_1A_DQ<14> [12]

DDR_1A_DQ<13> [12]

DDR_1A_DQ<12> [12]

DDR_1A_DQ<11> [12]

DDR_1A_DQ<10> [12]

DDR_1A_DQ<9> [12]

DDR_1A_DQ<8> [12]

DDR_1A_DQ<7> [12]

DDR_1A_DQ<6> [12]

DDR_1A_DQ<5> [12]

DDR_1A_DQ<4> [12]

DDR_1A_DQ<3> [12]

DDR_1A_DQ<2> [12]

DDR_1A_DQ<1> [12]

DDR_1A_DQ<0> [12]

U4C

BA45

MEM0_CB7_NC_NC

BD43

MEM0_CB6_NC_NC

AV47

MEM0_CB5_NC_NC

AV48

MEM0_CB4_NC_NC

AW45

MEM0_CB3_NC_NC

BB43

MEM0_CB2_NC_NC

AW47

MEM0_CB1_NC_NC

AW48

MEM0_CB0_NC_NC

BB47

MEM0_DQSN8_NC_NC

BD47

MEM0_DQSP8_NC_NC

CPU_APL_1296P

A A

5

4

MEM1_CB7_NC_NC

MEM1_CB6_NC_NC

MEM1_CB5_NC_NC

MEM1_CB4_NC_NC

MEM1_CB3_NC_NC

MEM1_CB2_NC_NC

MEM1_CB1_NC_NC

MEM1_CB0_NC_NC

MEM1_DQSN8_NC_NC

MEM1_DQSP8_NC_NC

BB23

BA23

AW19

BA19

AW21

AW23

AT21

AR21

BE23

BD23

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, July 21, 2017

Date: Sheet of

Friday, July 21, 2017

Date: Sheet of

3

2

Friday, July 21, 2017

PROJECT :

APL MEMORY

APL MEMORY

APL MEMORY

ZRX

ZRX

ZRX

1

1A

1A

1A

382

382

382

5

4

3

2

1

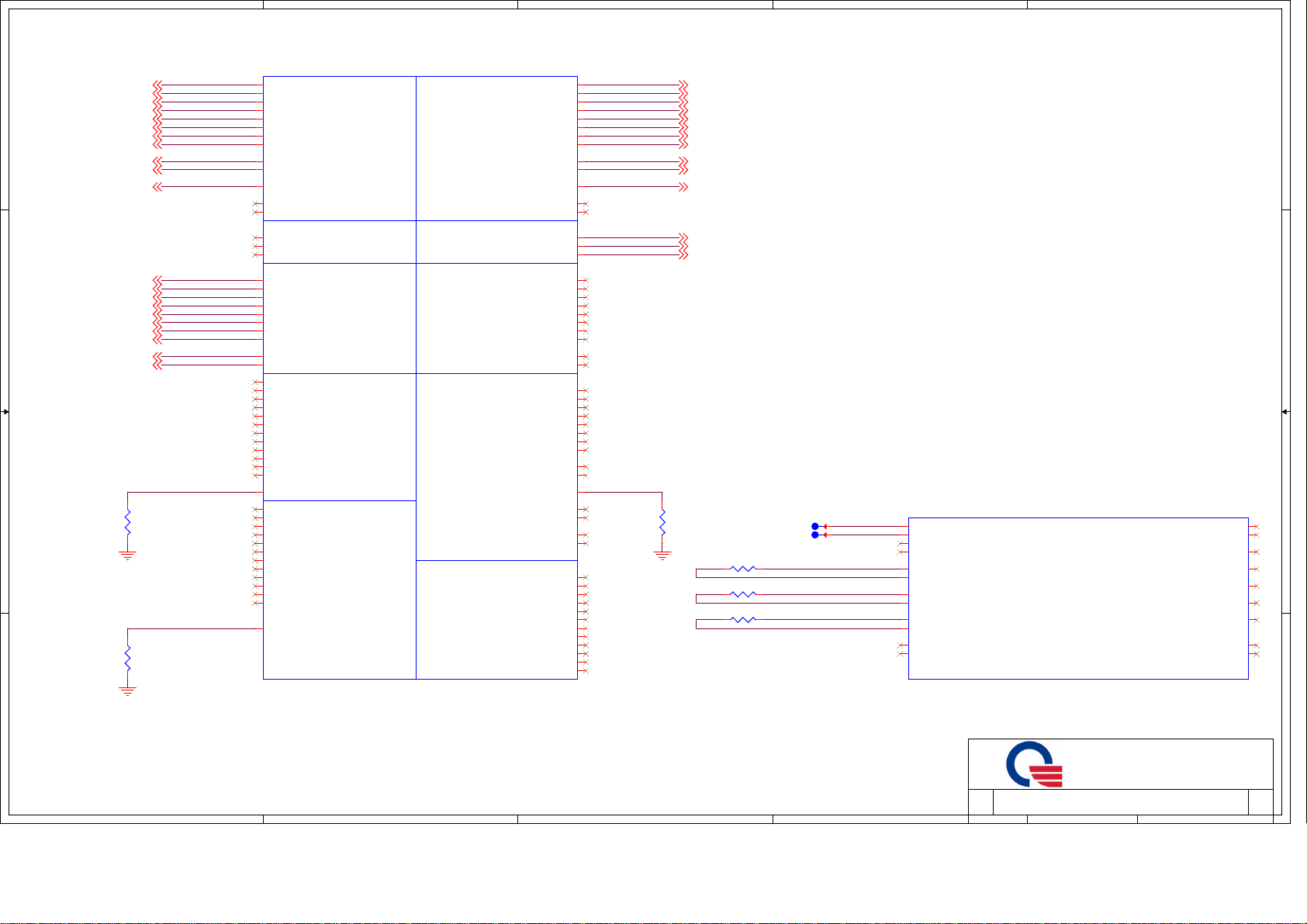

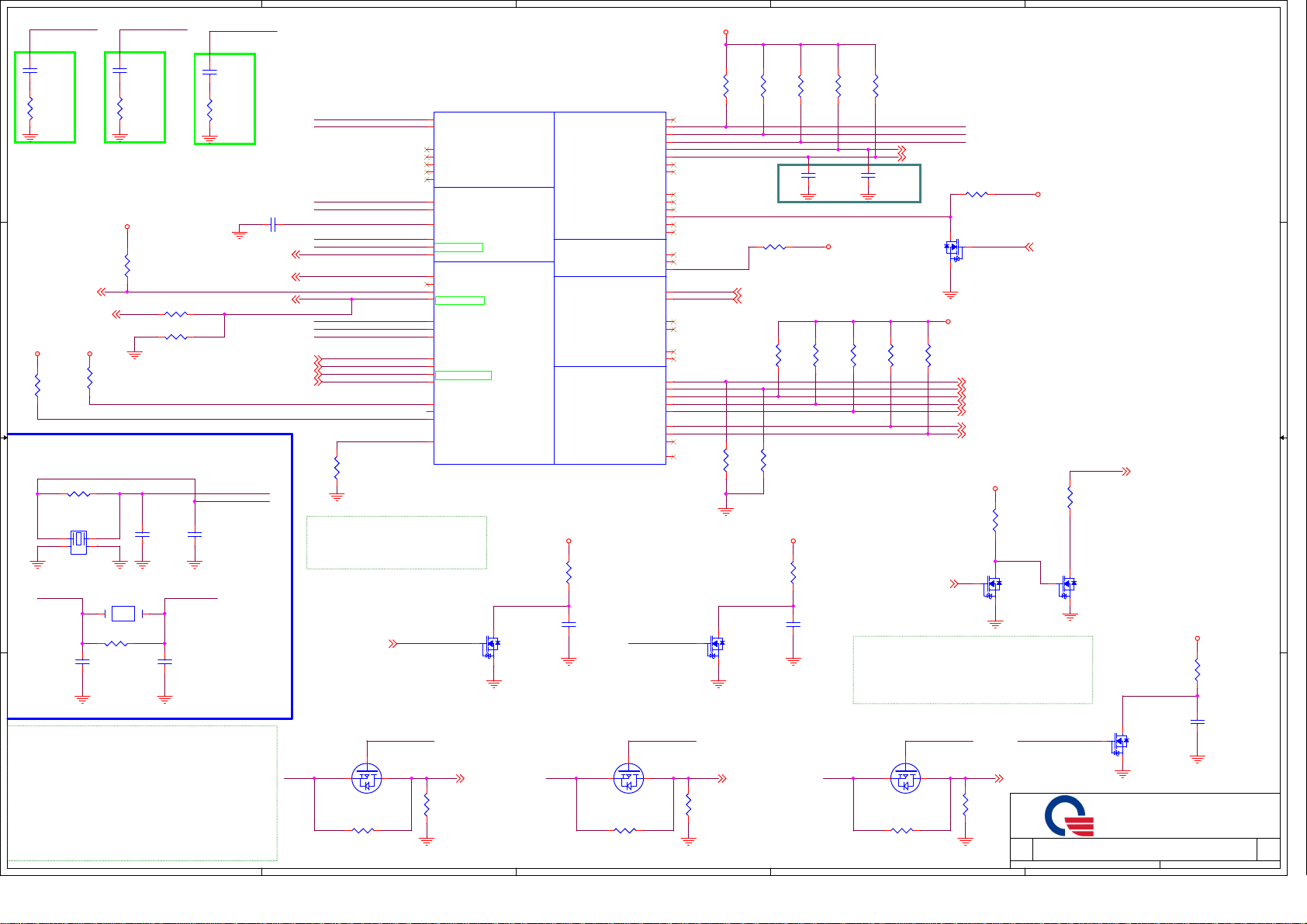

TYPE-C PORT 1 TYPE-C PORT 0

DDI1_TX3_P[36]

DDI1_TX3_N[36]

DDI1_TX2_P[36]

D D

C C

B B

A A

DDI1_TX2_N[36]

DDI1_TX1_P[36]

DDI1_TX1_N[36]

DDI1_TX0_P[36]

DDI1_TX0_N[36]

DDI1_AUX_P[36]

DDI1_AUX_N[36]

USB_C1_HPD_1V8_ODL[24,36]

EDP_TX3_P[21]

EDP_TX3_N[21]

EDP_TX2_P[21]

EDP_TX2_N[21]

EDP_TX1_P[21]

EDP_TX1_N[21]

EDP_TX0_P[21]

EDP_TX0_N[21]

EDP_AUX_P[21]

EDP_AUX_N[21]

MCSI1_RCOMP

R1

150_1%_4

MCSI2_RCOMP

R2

150_1%_4

U4D

AB3

DDI1_TXP_3

AB2

DDI1_TXN_3

AC1

DDI1_TXP_2

AC2

DDI1_TXN_2

AD3

DDI1_TXP_1

AD2

DDI1_TXN_1

AF2

DDI1_TXP_0

AF3

DDI1_TXN_0

AK16

DDI1_AUXP

AK15

DDI1_AUXN

A50

GP199_DBI_CSX/HV_DDI1_HPD

C54

GP189_HV_DDI1_DDC_SDA

A54

GP190_HV_DDI1_DDC_SCL

C52

GP196_PANEL1_VDDEN

B53

GP197_PANEL1_BKLTEN

C53

GP198_PANEL1_BKLTCTL

AC7

EDP_TXP_3

AC9

EDP_TXN_3

AC6

EDP_TXP_2

AC5

EDP_TXN_2

AG12

EDP_TXP_1

AG10

EDP_TXN_1

AG7

EDP_TXP_0

AG9

EDP_TXN_0

AH10

EDP_AUXP

AH9

EDP_AUXN

F17

MCSI1_DP_3

E17

MCSI1_DN_3

L17

MCSI1_DP_2

J17

MCSI1_DN_2

P21

MCSI1_DP_1

R21

MCSI1_DN_1

P17

MCSI1_DP_0

M17

MCSI1_DN_0

H19

MCSI1_CLKP_1

F19

MCSI1_CLKN_1

M19

MCSI1_CLKP_0

L19

MCSI1_CLKN_0

H27

MCSI1_RCOMP

H25

MCSI2_DP_3

J25

MCSI2_DN_3

F25

MCSI2_CLKP_1

E25

MCSI2_CLKN_1

M25

MCSI2_DP_2

L25

MCSI2_DN_2

J21

MCSI2_DP_1

H21

MCSI2_DN_1

L23

MCSI2_CLKP_0

J23

MCSI2_CLKN_0

M23

MCSI2_DP_0

P23

MCSI2_DN_0

F27

MCSI2_RCOMP

CPU_APL_1296P

DDI1

EDP MDSI_C

MIPI-CSI D-PHY 1.1

MIPI-CSI D-PHY 1.2

CAMERA_GPIO

DDI0_TXP_3

DDI0_TXN_3

DDI0_TXP_2

DDI0_TXN_2

DDI0

GP200_DBI_RESX/HV_DDI0_HPD

GP187_HV_DDI0_DDC_SDA

GP188_HV_DDI0_DDC_SCL

GP195_PANEL0_BKLTCTL

MDSI_A

GP73_GP_CAMERA_SB11

GP72_GP_CAMERA_SB10

GP71_GP_CAMERA_SB09

GP70_GP_CAMERA_SB08

GP69_GP_CAMERA_SB07

GP68_GP_CAMERA_SB06

GP67_GP_CAMERA_SB05

GP66_GP_CAMERA_SB04

GP65_GP_CAMERA_SB03

GP64_GP_CAMERA_SB02

GP63_GP_CAMERA_SB01

GP62_GP_CAMERA_SB00

DDI0_TXP_1

DDI0_TXN_1

DDI0_TXP_0

DDI0_TXN_0

DDI0_AUXP

DDI0_AUXN

GP193_PANEL0_VDDEN

GP194_PANEL0_BKLTEN

MDSI_C_DP_3

MDSI_C_DN_3

MDSI_C_DP_2

MDSI_C_DN_2

MDSI_C_DP_1

MDSI_C_DN_1

MDSI_C_DP_0

MDSI_C_DN_0

MDSI_C_CLKP

MDSI_C_CLKN

MDSI_A_DP_3

MDSI_A_DN_3

MDSI_A_DP_2

MDSI_A_DN_2

MDSI_A_DP_1

MDSI_A_DN_1

MDSI_A_DP_0

MDSI_A_DN_0

MDSI_A_CLKP

MDSI_A_CLKN

MDSI_RCOMP

GP201_INTD_DSI_TE1

GP202_INTD_DSI_TE2

DBI_SDA

DBI_SCL

AL2

AL1

AH3

AH2

AM3

AM2

AK3

AK2

AM16

AM15

C50

C49

B49

C47

B47

C46

AK13

AM13

AM12

AM10

AM5

AM6

AK7

AK6

AM9

AM7

AP6

AP5

AP15

AP13

AR2

AR1

AP12

AP10

AP2

AP3

AP7

M45

M43

B51

C51

E30

R34

M35

M34

L34

R35

F30

M37

H30

J34

P34

L37

MDSI_RCOMP

DDI0_TX3_P [27]

DDI0_TX3_N [27]

DDI0_TX2_P [27]

DDI0_TX2_N [27]

DDI0_TX1_P [27]

DDI0_TX1_N [27]

DDI0_TX0_P [27]

DDI0_TX0_N [27]

DDI0_AUX_P [27]

DDI0_AUX_N [27]

USB_C0_HPD_1V8_ODL [24,27]

EN_PP3300_EDP_DX [33]

SOC_EDP_BKLTEN [21]

SOC_EDP_BKLTCTL_1V8 [21]

R3

150_1%_4

R5 402_1%_4

R4 402_1%_4

R6 402_1%_4

ALL 1.8V

TP1

TP2

1

1

DDI0_RCOMP_P

DDI0_RCOMP_N

EDP_RCOMP_P

EDP_RCOMP_N

PCIE_USB3_RCOMP_P

PCIE_USB3_RCOMP_N

APL_C1

APL_F1

U4E

C1

DEBUG_OBS_PORT_B1

F1

DEBUG_OBS_PORT_B0

B4

DEBUG_OBS_PORT_A1

A4

DEBUG_OBS_PORT_A0

AG1

DDI0_RCOMP_PLLOBS_P

AG2

DDI0_RCOMP_PLLOBS_N

AG6

EDP_RCOMP_PLLOBS_P

AG5

EDP_RCOMP_PLLOBS_N

F6

PCIE_USB3_SATA_RCOMP_OBS_P

F5

PCIE_USB3_SATA_RCOMP_OBS_N

BJ3

VCCFX_1P24_GLML2_LDOOUT_M0_1P15

BJ61

VCCFX_1P24_GLML2_LDOOUT_M1_1P15

CPU_APL_1296P

RSVD_EDM1

RSVD_EDM0

GT_OBS

VCCRAM_OBS

VCCIOA_OBS

VDD1_OBS

VDD2_OBS

VCCCOREVID_1P03_G_M1C0

VMON_GLM

A18

C19

V49

D1

AN32

V48

AC22

BG63

BJ62

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

5

4

3

2

Date: Sheet of

Friday, July 21, 2017

Date: Sheet of

Friday, July 21, 2017

Date: Sheet of

Friday, July 21, 2017

PROJECT :

APL eDP/RCOMP

APL eDP/RCOMP

APL eDP/RCOMP

ZRX

ZRX

ZRX

1

1A

1A

1A

383

383

383

5

4

3

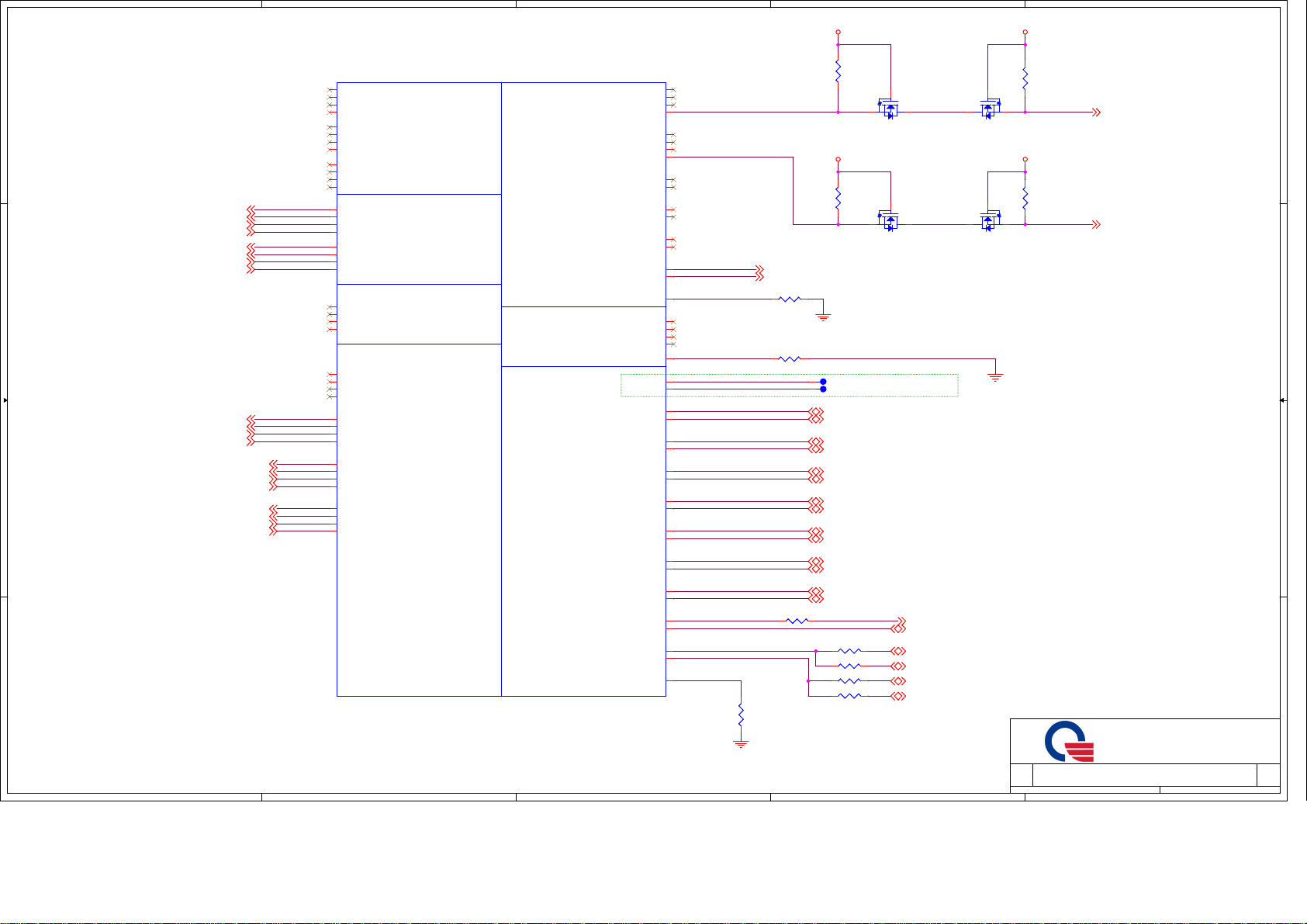

PP1800_SOC_A PP3300_WLAN_DX

2

1

U4F

T2

PCIE_P2_TXP

T3

PCIE_P2_TXN

M5

D D

USB3_1_A1_TX_P[36]

USB3_1_A1_TX_N[36]

TYPE A PORT 1

TYPE C PORT 0

C C

TYPE A PORT 0

B B

TYPE C PORT 1

A A

USB3_1_A1_RX_P[36]

USB3_1_A1_RX_N[36]

USB3_0_C0_TX_P[27]

USB3_0_C0_TX_N[27]

USB3_0_C0_RX_P[27]

USB3_0_C0_RX_N[27]

PCIE_PCH4TX_WLANRX_P[23]

PCIE_PCH4TX_WLANRX_N[23]

PCIE_PCH4RX_WLANTX_P[23]

PCIE_PCH4RX_WLANTX_N[23]

USB3_4_A0_TX_P[25]

USB3_4_A0_TX_N[25]

USB3_4_A0_RX_P[25]

USB3_4_A0_RX_N[25]

USB3_5_C1_TX_P[36]

USB3_5_C1_TX_N[36]

USB3_5_C1_RX_P[36]

USB3_5_C1_RX_N[36]

5

PCIE_P2_RXP

M6

PCIE_P2_RXN

R1

PCIE_P1_TXP

R2

PCIE_P1_TXN

T10

PCIE_P1_RXP

T12

PCIE_P1_RXN

V3

PCIE_P0_TXP

V2

PCIE_P0_TXN

P7

PCIE_P0_RXP

P6

PCIE_P0_RXN

K3

USB3_P1_TXP

K2

USB3_P1_TXN

F2

USB3_P1_RXP

G2

USB3_P1_RXN

J1

USB3_P0_TX

J2

USB3_P0_TXN

K9

USB3_P0_RXP

K10

USB3_P0_RXN

Y3

SATA_P0_TXP

Y2

SATA_P0_TXN

T9

SATA_P0_RXP

T7

SATA_P0_RXN

L2

PCIE_P5_USB3_P2_TXP

L1

PCIE_P5_USB3_P2_TXN

K7

PCIE_P5_USB3_P2_RXP

M7

PCIE_P5_USB3_P2_RXN

N2

PCIE_P4_USB3_P3_TXP

M2

PCIE_P4_USB3_P3_TXN

H5

PCIE_P4_USB3_P3_RXP

H6

PCIE_P4_USB3_P3_RXN

P3

PCIE_P3_USB3_P4_TXP

P2

PCIE_P3_USB3_P4_TXN

P12

PCIE_P3_USB3_P4_RXP

P10

PCIE_P3_USB3_P4_RXN

W1

SATA_P1_USB3_P5_TXP

W2

SATA_P1_USB3_P5_TXN

T5

SATA_P1_USB3_P5_RXP

T6

SATA_P1_USB3_P5_RXN

CPU_APL_1296P

PCIE

USB3

USB3 (OTG)

SATA0

USB_SSIC

PCIE/USB3/SATA

USB2

4

GP212_PCIE_CLKREQ3_B

GP211_PCIE_CLKREQ2_B

GP210_PCIE_CLKREQ1_B

GP209_PCIE_CLKREQ0_B

GP208_PCIE_WAKE3_B

GP207_PCIE_WAKE2_B

GP206_PCIE_WAKE1_B

GP205_PCIE_WAKE0_B

PCIE_CLKOUT_3P

PCIE_CLKOUT_3N

PCIE_CLKOUT_2P

PCIE_CLKOUT_2N

PCIE_CLKOUT_1P

PCIE_CLKOUT_1N

PCIE_CLKOUT_0P

PCIE_CLKOUT_0N

CLKDRV_RCOMP

USB_SSIC_0_TX_P

USB_SSIC_0_TX_N

USB_SSIC_0_RX_P

USB_SSIC_0_RX_N

USB_SSIC_RCOMP

USB2_OTG_DP0

USB2_OTG_DN0

USB_OTG_ID

USB_VBUS_SNS

GP204_USB2_OC1_B

GP203_USB2_OC0_B

USB2_RCOMP

USB2_DP7

USB2_DN7

USB2_DP6

USB2_DN6

USB2_DP5

USB2_DN5

USB2_DP4

USB2_DN4

USB2_DP3

USB2_DN3

USB2_DP2

USB2_DN2

USB2_DP1

USB2_DN1

3

AJ62

AH61

AH62

WLAN_PCIE_CLKREQ_1V8_ODL

AK62

N62

P61

P62

WLAN_PCIE_WAKE_1V8_ODL

R62

B7

B5

A7

B8

C10

A10

C11

B11

CLKDRV_RCOMP

E21

AH13

AH12

AG16

AG15

SSIC_RCOMP

AB15

V5

V6

AC12

AC10

AB6

AB7

Y9

Y10

V9

V7

Y13

V13

V16

V15

V12

V10

USB2_OTG_ID

AC15

AC16

USB_TYPEC_OC_ODL

C55

USB_TYPEA_OC_ODL

B55

USB2_RCOMP

Y15

WLAN_PCIE_CLK_P [23]

WLAN_PCIE_CLK_N [23]

R7 60.4_1%_4

R8 137_1%_4

R71 *0_5%_4

R9

113_1%_4

R10

10K_5%_4

2

Q1B

PMDXB600UNE

PP1800_SOC_A

R11

10K_5%_4

2

Q2B

PMDXB600UNE

TP83

TP84

Remove USB_CAM2

USB2_6_HAVEN_P [35]

USB2_6_HAVEN_N [35]

USB2_5_BT_P [23]

USB2_5_BT_N [23]

USB2_4_CAM_P [21]

USB2_4_CAM_N [21]

USB2_3_A1_P [25]

USB2_3_A1_N [25]

USB2_2_A0_P [25]

USB2_2_A0_N [25]

USB2_1_C1_P [29]

USB2_1_C1_N [29]

USB2_0_C0_P [29]

USB2_0_C0_N [29]

R12 *Short_4

R13 *Short_4

R14 *Short_4

R15 *Short_4

20K INTERNAL PU

2

WLAN_Q1

WLAN_Q2

3 4

PMDXB600UNE

3 4

PMDXB600UNE

61

61

H1 SECURITY KEY

BLUETOOTH ON M.2

CAMERA

TYPE A PORT 1

TYPE A PORT 0

TYPE C PORT 1

TYPE C PORT 0

TRACKPAD_INT_GATE [20,24]

USB2_OTG_VBUSSENSE [24]

USB_C0_OC_ODL [28]

USB_C1_OC_ODL [28]

USB_A0_OC_ODL [25]

USB_A1_OC_ODL [25]

R16

10K_5%_4

5

Q1A

PP3300_WLAN_DX

R17

10K_5%_4

5

Q2A

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, July 21, 2017

Date: Sheet of

Friday, July 21, 2017

Date: Sheet of

Friday, July 21, 2017

WLAN_PCIE_CLKREQ_3V3_ODL [23]

WLAN_PCIE_WAKE_3V3_ODL [23]

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

APL PCIE/USB/SATA

APL PCIE/USB/SATA

APL PCIE/USB/SATA

ZRX

ZRX

ZRX

1

1A

1A

1A

384

384

384

5

4

3

2

1

U4G

H41

1

D D

PP1800_SOC_A

UART_PCH_TX_GPS_RX[15]

UART_GPS_TX_PCH_RX[15]

SIO_SPI_2_TXD/GPIO123[15]

R280 3.3K_1%_4

R279 100K_5%_4

EC_IN_RW_OD[17,35]

WLAN_PE_RST[23]

PCHTX_SERVORX_UART[16,35]

PCHRX_SERVOTX_UART[16,35]

TP5

EC_SMI_ODL[24]

8/9/16

ADDED WLAN_PE_RST TO GPIO_122

HP_INT_ODL[19]

SIO_SPI_0_FS1/GPIO106[15]

PCH_SPI_FP_MOSI[20]

FINGER PRINT SPI

C C

PCH_SPI_FP_MISO[20]

TPM_SPI_CS2_L[17,35]

PCH_SPI_FP_CS_L[20]

PCH_SPI_FP_CLK[20]

1

TP13

1

TP14

*

*

TP3

GPIO_48

1

*

PCH_MEM_CONFIG3

GPIO_39

1

TP6

PCH_MEM_CONFIG2

*

GPIO_40

1

TP4

*

TP7

GPIO_120

1

TP8

*

GPIO_118

1

TP9

*

GPIO_117

1

TP10

*

GPIO_112

1

TP11

GPIO_111

1

*

TP12

*

R4545 *Short_4

R282

3.3K_1%_4

*

*

GP46_LPSS_UART2_RXD/ISH_UART2

L41

GP48_LPSS_UART2_RTS_B/ISH_UART2

M41

GP49_LPSS_UART2_CTS_B/ISH_UART2

B43

GP43_LPSS_UART1_TXD/ISH_UART1

C43

GP42_LPSS_UART1_RXD/ISH_UART1

A42

GP44_LPSS_UART1_RTS_B/ISH_UART1

C42

GP45_LPSS_UART1_CTS_B/ISH_UART1

B45

GP39_LPSS_UART0_TXD/ISH_UART0

C45

GP38_LPSS_UART0_RXD/ISH_UART0

A46

GP40_LPSS_UART0_RTS_B/ISH_UART0

C44

GP41_LPSS_UART0_CTS_B/ISH_UART0

E62

1

GP123_SSP2_TXD/ISH_SPI/TOUCHD3

C62

GP122_SSP2_RXD/ISH_SPI/TOUCHD2

D59

GP121_SSP2_FS2/SPARE/TOUCHD1

E56

GP120_SSP2_FS1/ISH_SPI/TOUCHD0

D61

GP119_SSP2_FS0/ISH_SPI/TOUCHF0

F62

GP118_SSP2_CLK/ISH_SPI/TOUCHCK

H58

GP117_SSP1_TXD//LPSS_UART3_CTS_B

H57

GP116_SSP1_RXD/LPSS_UART3_RTS_B

F61

GP113_SSP1_FS1/LPSS_UART3_TXD

K55

GP112_SSP1_FS0/LPSS_UART3_RXD

F58

GP111_SSP1_CLK

J52

GP110_SSP0_TXD

H54

GP109_SSP0_RXD

H52

GP106_SSP0_FS1/FST_SPI_CS2_B

F52

GP105_SSP0_FS0

F54

GP104_SSP0_CLK

R283

3.3K_1%_4

GP47_LPSS_UART2_TXD/ISH_UART2

J41

SPI FLASH/TPM

PCH_MEM_CONFIG3

PCH_MEM_CONFIG2

PCH_MEM_CONFIG1

PCH_MEM_CONFIG0

R479

R480

R481

3.3K_1%_2

3.3K_1%_2

Q PN

AKD5QZST507 SAMSUNG 8GB K4F8E304HB-MGCJ LF+HF

B B

AKD5RZST515

AKD5FWSTL04

AKD5JWSTL04

AKD5RG0TW09

AKD5RG0TW08

R482

3.3K_1%_2

3.3K_1%_2

MEMORY STRAPPING TABLE

CONFIG PIN

SAMSUNG 4GB K4F6E304HB-MGCJ LF+HF

MICRON 8GB MT53B512M32D2NP-062WT:C

MICRON 4GB MT53B256M32D1NP-062 WT:C

HYNIX 8GB H9HCNNNBPUMLHR-NME

HYNIX 4GB H9HCNNN8KUMLHR-NME 0 1 0 1

PCH_SPI_CLK[14,17,35]

PCH_SPI_CS0_L[14]

PCH_MEM_CONFIG1

PCH_SPI_MOSI[14,17,35]

PCH_SPI_MISO[14,17,35]

PCH_MEM_CONFIG0

3 2 100

00

0

0 0

0

0 0 1 1

0 1 0 0

0

1

010

1 1 1 1

C56

GP103_FST_SPI_CLK

C57

GP98_FST_SPI_CS1_B

B57

GP97_FST_SPI_CS0_B

B61

GP102_FST_SPI_IO3

B60

GP101_FST_SPI_IO2

A58

GP99_FST_SPI_MOSI_IO0

B58

GP100_FST_SPI_MISO_IO1

CPU_APL_1296P

UART EMMC

SDIO

SDCARDSPI

SPI NOR

LPC

GP156_EMMC0_CLK

GP182_EMMC0_STROBE

GP165_EMMC0_CMD

GP164_EMMC0_D7

GP163_EMMC0_D6

GP162_EMMC0_D5

GP161_EMMC0_D4

GP160_EMMC0_D3

GP159_EMMC0_D2

GP158_EMMC0_D1

GP157_EMMC0_D0

RCOMP_EMMC0

GP166_SDIO_CLK

GP171_SDIO_CMD

GP170_SDIO_D3

GP169_SDIO_D2

GP168_SDIO_D1

GP167_SDIO_D0

GP183_SDIO_PWR_DOWN_B

GP172_SDCARD_CLK

GP178_SDCARD_CMD

GP177_SDCARD_CD_B

GP186_SDCARD_LVL_W

GP176_SDCARD_D3

GP175_SDCARD_D2

GP174_SDCARD_D1

GP173_SDCARD_D0

LPC_CLKOUT1

LPC_CLKOUT0

LPC_FRAME_B

LPC_AD3

LPC_AD2

LPC_AD1

LPC_AD0

LPC_CLKRUN_B

LPC_ILB_SERIRQ

Y58

V54

Y51

V57

V55

Y49

V52

V51

T59

T58

V58

V59

P58

T57

T55

T54

P57

T52

P51

AB58

AC52

AB54

AB55

AB51

AC51

AC48

AC49

AA62

AB61

V61

W63

W62

Y62

Y61

V62

AB62

RCOMP_EMMC0

LPC_CLKOUT0_R

LPC_FRAME_L_R

LPC_AD3_R

LPC_AD2_R

LPC_AD1_R

LPC_AD0_R

LPC_CLKRUN_L_R

LPC_SERIRQ_R

R284

200_1%_4

SD_CLK

SD_CMD

SD_CD_OD

SD_DATA3

SD_DATA2

SD_DATA1

SD_DATA0

EMMC_DAT7 [18]

EMMC_DAT6 [18]

EMMC_DAT5 [18]

EMMC_DAT4 [18]

EMMC_DAT3 [18]

EMMC_DAT2 [18]

EMMC_DAT1 [18]

EMMC_DAT0 [18]

EN_SD_SOCKET_PWR_L [33]

SD_CLK [18]

SD_CMD [18]

SD_DATA3 [18]

SD_DATA2 [18]

SD_DATA1 [18]

SD_DATA0 [18]

R285 20_5%_4

R286 20_5%_4

R287 20_5%_4

R288 20_5%_4

R289 20_5%_4

R290 20_5%_4

R291 20_5%_4

R292 20_5%_4

EMMC_CLK [18]

EMMC_RCLK [18]

EMMC_CMD [18]

PP1800_S

LPC_CLKOUT0 [24]

LPC_FRAME_L [24]

LPC_AD3 [24]

LPC_AD2 [24]

LPC_AD1 [24]

LPC_AD0 [24]

LPC_CLKRUN_L [24]

LPC_SERIRQ [24]

R466

100K_5%_4

SD_CD_OD [16,18]

HARDWARE STRAPS (* = SYSTEM STRAP SELECTION)

GPIO_39: INTERNAL 20K PD

*DISABLE CSE ROM BYPASS: 0

ENABLE CSE ROM BYPASS: 1

GPIO_40: INTERNAL 20K PD

*MUST BE LOW WHEN

RSM_RST_N DEASSERTS

GPIO_43: INTERNAL 20K PU

ENABLE BOOT FROM EMMC: 1

A A

5

*DISABLE BOOT FROM EMMC: 0

GPIO_44: INTERNAL 20K PU

*ENABLE BOOT FROM SPI: 1

DISABLE BOOT FROM SPI: 0

4

GPIO_47: INTERNAL 20K PD

*DON'T FORCE DNX FW LOAD: 0

FORCE DNX FW LOAD: 1

GPIO_48: INTERNAL 20K PD

*MUST BE LOW WHEN

RSM_RST_N DEASSERTS

GPIO_104: INTERNAL 20K PD

*MUST BE LOW WHEN

RSM_RST_N DEASSERTS

GPIO_105: INTERNAL 20K PD

*MUST BE LOW WHEN

RSM_RST_N DEASSERTS

GPIO_106: INTERNAL 20K PU

*MUST BE HIGH WHEN

RSM_RST_N DEASSERTS

GPIO_111: INTERNAL 20K PU

DO NOT BOOT FROM SPI: 1

*BOOT FROM SPI: 0

GPIO_118: INTERNAL 20K PD

*NO FLASH DESCRIPTOR OVERRIDE: 0

OVERRIDE FLASH DESCRIPTOR: 1

GPIO_110: INTERNAL 20K PU

LPC BUFFERS AT 1.8V: 1

*LPC BUFFERS AT 3.3V: 0

3

GPIO_117: INTERNAL 20K PD

*MUST BE LOW WHEN

RSM_RST_N DEASSERTS

GPIO_123: INTERNAL 20K PU

MUST BE HIGH WHEN

RSM_RST_N DEASSERTS

GPIO_112: INTERNAL 20K PD

*MUST BE LOW WHEN

RSM_RST_N DEASSERTS

GPIO_113: INTERNAL 20K PD

*MUST BE LOW WHEN

RSM_RST_N DEASSERTS

2

GPIO_120: INTERNAL 20K PD

*TOP SWAP OVERRIDE DISABLE: 0

TOP SWAP OVERRIDE ENABLE: 1

GPIO_121: INTERNAL 20K PD

*MUST BE LOW WHEN

RSM_RST_N DEASSERTS

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, July 21, 2017

Date: Sheet of

Friday, July 21, 2017

Date: Sheet of

Friday, July 21, 2017

PROJECT :

APL UART/SPI/EMMC/SD/LPC

APL UART/SPI/EMMC/SD/LPC

APL UART/SPI/EMMC/SD/LPC

ZRX

ZRX

ZRX

385

385

1

385

1A

1A

1A

5

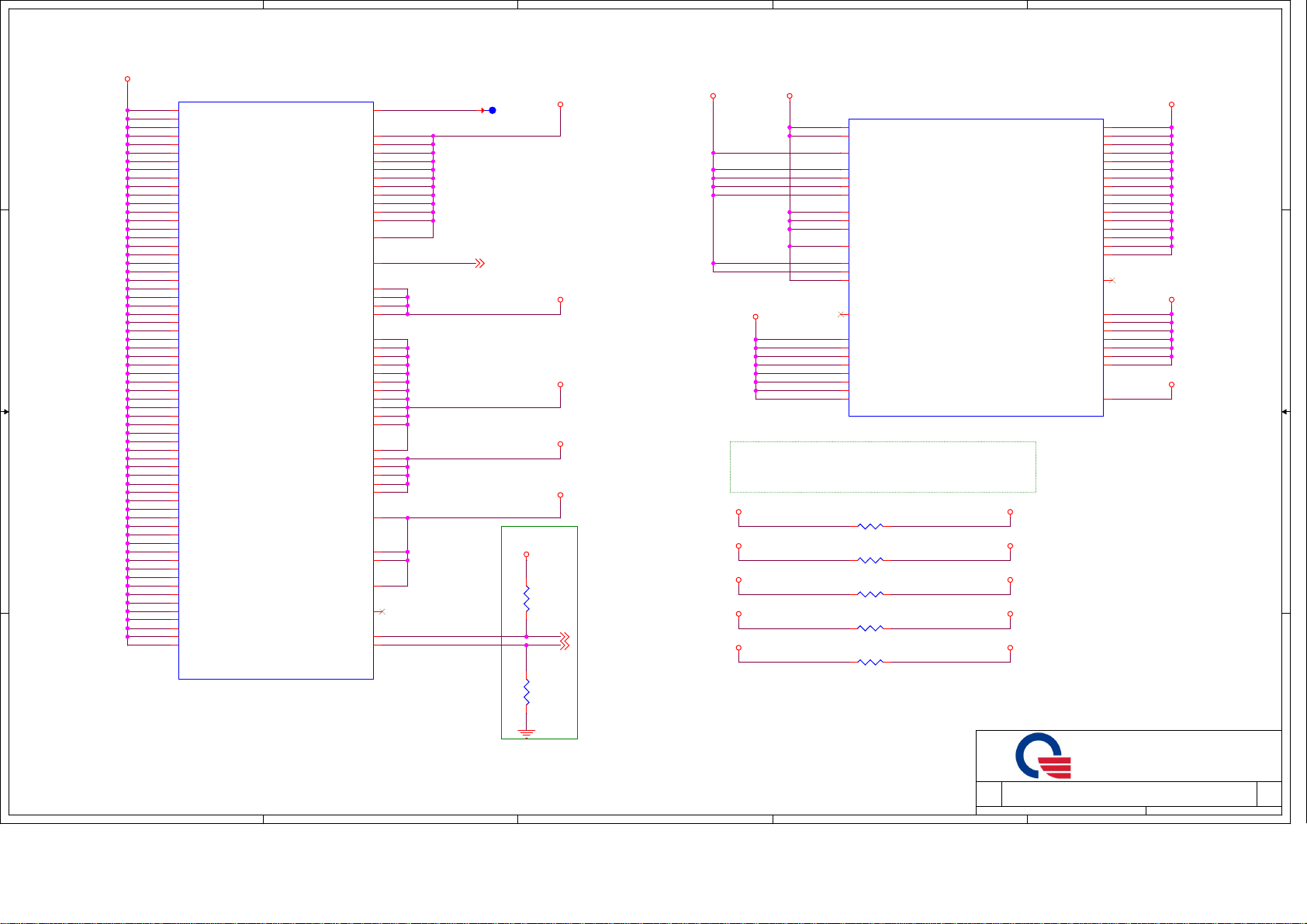

D D

Remove PEN I2C

PCH_I2C_TRACKPAD_1V8_SCL

PCH_I2C_TRACKPAD_1V8_SDA

PCH_I2C_TOUCHSCREEN_1V8_SCL

PCH_I2C_TOUCHSCREEN_1V8_SDA

PCH_I2C_HAVEN_TPM_SCL[35]

[35] PCH_I2C_HAVEN_TPM_SDA

Remove NFC I2C

[19] PCH_I2C_AUDIO_SCL

[19] PCH_I2C_AUDIO_SDA

[21] TOUCHSCREEN_RST_1V8

C C

B B

[21] DMIC_DATA

[21] DMIC_CLK2

[21] DMIC_CLK1

[19] I2S_SFRM_HP

[19] I2S_PCH_TX_HP_RX

[19] I2S_PCH_RX_HP_TX

[19] I2S_MCLK_HP

[19] I2S_SCLK_HP

[19] SPK_PA_EN

[14] PCH_WP_OD

TP19

R478 33_5%_2

R189 33_5%_2

1

*

PP1800_SOC_A

TP21

PCH_I2C_NFC_SCL

1

TP102

PCH_I2C_NFC_SDA

1

TP103

*

*

1

TP15

*

Remove Pen_Reset (C41)

GPIO_34

1

TP16

*

DMIC_CAM2_DATA_TP

1

TP17

*

DMIC_CLK2_R

DMIC_CLK1_R

Remove GPS_HOST_WAKE (M61)

Remove GPS_EN (M62)

1

TP20

*

R24 20_5%_4

R25 20_5%_4

GPIO_78

1

*

GPIO_92

I2S_MCLK_HP_R

I2S_SCLK_HP_R

R26

3.3K_1%_4

4

U4H

AP61

GP139_LPSS_I2C7_SCL/ISH_I2C2_SCL

AP62

GP138_LPSS_I2C7_SDA/ISH_I2C2_SDA

AK61

GP137_LPSS_I2C6_SCL/ISH_I2C1_SCL

AL63

GP136_LPSS_I2C6_SDA/ISH_I2C1_SDA

AP51

GP135_LPSS_I2C5_SCL/ISH_I2C0_SCL

AP49

GP134_LPSS_I2C5_SDA/ISH_I2C0_SDA

AP54

GP133_LPSS_I2C4_SCL

AP52

GP132_LPSS_I2C4_SDA

AL62

GP131_LPSS_I2C3_SCL

AM62

GP130_LPSS_I2C3_SDA

AP58

GP129_LPSS_I2C2_SCL

AP59

GP128_LPSS_I2C2_SDA

AM61

GP127_LPSS_I2C1_SCL

AN62

GP126_LPSS_I2C1_SDA

AR63

GP125_LPSS_I2C0_SCL

AR62

GP124_LPSS_I2C0_SDA

T62

SMB_CLK/LPSS_I2C7_SCL

T61

SMB_DATA/LPSS_I2C7_SDA

R63

SMB_ALERT_B

E41

GP37_PWM3

F41

GP36_PWM2

C41

GP35_PWM1

B41

GP34_PWM0

M52

GP83_AVS_M_DATA_2

M54

GP81_AVS_M_DATA_1/I2S4_SDI

P52

GP80_AVS_M_CLK_B1/I2S4_WS_SYNC

M55

GP82_AVS_M_CLK_AB2/I2S4_SDO

P54

GP79_AVS_M_CLK_A1/I2S4_BCLK

M61

GP90_AVS_I2S3_WS_SYNC

L63

GP92_AVS_I2S3_SDO

L62

GP91_AVS_I2S3_SDI

M62

GP89_AVS_I2S3_BCLK

M57

GP86_AVS_I2S2_WS_SYNC

M58

GP88_AVS_I2S2_SDO

K59

GP87_AVS_I2S2_SDI

K58

GP84_AVS_I2S2_MCLK

H59

GP85_AVS_I2S2_BCLK

J62

GP76_AVS_I2S1_WS_SYNC

K62

GP78_AVS_I2S1_SDO

K61

GP77_AVS_I2S1_SDI

G62

GP74_AVS_I2S1_MCLK

H63

GP75_AVS_I2S1_BCLK

CPU_APL_1296P

R29

*3.3K_1%_4

PP3300_TOUCHSCREEN_DX

I2C

SMB

PWM

I2S

3

GP26_SATA_LEDN

GP25_SATA_DEVSLP1

GP24_SATA_DEVSLP0

GP23_SATA_GP1

GP22_SATA_GP0

GP21_MCERR

GP20_IERR

GP_219

GP_218

GP_217

GP_216

GP_27

GP_19

GP_18

GP_17

GP_16

GP_15

GP_14

GP_13

GP_12

GP_11

GP_10

GP_9

GP_8

GPIO

GP153_ISH_GPIO_7/AVS_I2S5_SDO

GP152_ISH_GPIO_6/AVS_I2S5_SDI

GP151_ISH_GPIO_5/AVS_I2S5_WS_SYNC

GP150_ISH_GPIO_4/AVS_I2S5_BCLK

GP149_ISH_GPIO_3/AVS_I2S6_SDO

GP148_ISH_GPIO_2/AVS_I2S6_SDI

GP147_ISH_GPIO_1/AVS_I2S6_WS_SYNC

GP146_ISH_GPIO_0/AVS_I2S6_BCLK

GP33_ISH_GPIO_15/SUS_CLK3

GP32_ISH_GPIO_14/SUS_CLK2

GP31_ISH_GPIO_13/SUS_CLK1

GP_7

GP_6

GP_5

GP_4

GP_3

GP_2

GP_1

GP_0

GP30_ISH_GPIO_12

GP29_ISH_GPIO_11

GP28_ISH_GPIO_10

GP155_ISH_GPIO_9

GP154_ISH_GPIO_8

GPIO_RCOMP

C31

C27

C25

Remove PEN_PDCT_ODL (C25)

B25

A26

C26

NFC_INT_L

B27

L30

M30

M29

P30

C29

C33

TRACKPAD_INT_1V8_ODL

J39

CONFIG_STRAP1

C35

CONFIG_STRAP2

C36

F39

R4538 *Short_2

FP_INT

C38

C30

Remove PEN_INT_ODL (C30)

E39

C34

SHIPPING_STRAP

L39

A30

B29

H39

B31

A34

B35

FP_INT

B39

C39

B33

A38

C37

H35

B37

AK57

ISH_GPIO_8

AM52

AM55

AM57

AM49

NFC_RESET_ODL

AM51

AM54

AK51

AK58

I2S_SCLK_SPKR_R

AM48

F34

CLK_32K_GPS

F35

NFC_FW_DL

H34

GPIO_RCOMP

E34

EC_PCH_WAKE_ODL [24]

TOUCHSCREEN_INT_1V8_ODL [21]

1

TP96*

EMMC_RST_ODL [18]

TRACKPAD_INT_1V8_ODL [20]

TRACKPAD_INT_1V8_ODL

FP_INT [15,20]

EC_SCI_ODL [24]

TRC_DATA0[8] [15]

TRC_DATA0[7] [15]

TRC_DATA0[6] [15]

TRC_DATA0[5] [15]

TRC_DATA0[4] [15]

TRC_DATA0[2] [15]

TRC_DATA0[1] [15]

TRC_CLK0 [15]

EC_PCH_KB_INT_ODL [24]

HAVEN_PCH_INT_ODL [35]

1

TP18

*

EN_PP3300_TOUCHSCREEN [33]

1

TP101

*

I2S_PCH_TX_SPKR_RX [19]

R35 20_5%_4

1

TP107

1

*

TP95

NFC GPIO

*

R34

200_1%_4

PP1800_SOC_A

2

R533

*10K_1%_2

R70

*3.3K_1%_2

R42 *FP@10K_5%_4

TP83 ON BACKSIDE

I2S_SFRM_SPKR [19]

I2S_SCLK_SPKR [19]

PMIC_PCH_INT_ODL [30]

1

PP1800_A

R532

R534

*10K_1%_2

*3.3K_1%_2

R522

*3.3K_1%_2

TPM_PIRQ_L [17]

PP1800_A

FP_RST_ODL [20]

SPEAKER AMP

CONFIG_STRAP1PUCONFIG_STRAP2 CONFIG

PU

PU

PD

PD

PD

Z

Z

*Z

PP3300_TRACKPAD_DX

PU

PD

Z

PU

PD

Z

PU

PD

*Z

CONFIG_0

CONFIG_1

CONFIG_2

CONFIG_3

CONFIG_4

CONFIG_5

CONFIG_6

CONFIG_7

CONFIG_8

R30

5

3 4

PMDXB600UNE

PP3300_TOUCHSCREEN_DX

5

3 4

PMDXB600UNE

PMDXB600UNE

PP1800_SOC_A

Q3B

PMDXB600UNE

2

61

Q4B

2

61

PCH_I2C_TCS_1V8_SCL_Q

PCH_I2C_TCS_1V8_SDA_Q

PCH_I2C_TOUCHSCREEN_1V8_SCL

A A

PCH_I2C_TOUCHSCREEN_1V8_SDA

2.2K_1%_4

Q4A

R31

2.2K_1%_4

Q3A

PCH_I2C_TOUCHSCREEN_3V3_SCL [21]

PCH_I2C_TOUCHSCREEN_3V3_SDA [21]

PCH_I2C_TRACKPAD_1V8_SCL

PCH_I2C_TRACKPAD_1V8_SDA

PMDXB600UNE

PP1800_SOC_A

PMDXB600UNE

2

61

Q6B

2

61

Q5B

PCH_I2C_TCP_1V8_SCL_Q

PCH_I2C_TCP_1V8_SDA_Q

5

3 4

PMDXB600UNE

PP3300_TRACKPAD_DX

5

3 4

PMDXB600UNE

R38

1K_1%_4

Q6A

R39

1K_1%_4

Q5A

PCH_I2C_TRACKPAD_3V3_SCL [20]

PCH_I2C_TRACKPAD_3V3_SDA [20]

QQQuuuaaannntttaaa CCCooommmpppuuuttteeerrr IIInnnccc...

SSSiiizzzeee DDDooocccuuummmeeennnttt NNNuuummmbbbeeerrr RRReeevvv

DDDaaattteee::: SSShhheeeeeettt ooofff

5

4

3

2

FFFrrriiidddaaayyy,,, JJJuuulllyyy 222111,,, 222000111777

PPPRRROOOJJJEEECCCTTT ::: ZZZRRRXXX

AAAPPPLLL III222CCC///III222SSS///GGGPPPIIIOOO

1

111AAA

333888666

5

EC_PCH_PWROK PCH_RTCRST_ODL

PLT_RST_L

4

3

PP1800_SOC_A

2

1

C4874

0.1u/16V_4

R4525

10_5%_4

D D

colsed to U4 AG49 pin

within 100 mils

SUSPWRNACK[24]

PMIC_EC_PWROK_OD[24,30]

C C

PP3300_RTC

PP3300_SOC_A

R51

100K_5%_4

CLOCKS

R46 200K_1%_4

X3

3

B B

A A

4

19.2MHZ/20ppm

8/11/16

ADDED Q79, Q81, Q82, R507, R509, R510

CONNECTED GATE OF Q80 TO PCH_RSMRST_L

ADDED NET SLP_S4_PCH_L FROM U4.AK54 TO Q82.S

ADDED NET SLP_S3_PCH_L FROM U4.AC62 TO Q81.S

ADDED NET SLP_S0_PCH_L FROM U4.AD61 TO Q79.S

CONNECTED NET SLP_S4_L TO Q82.D

CONNECTED NET SLP_S3_L TO Q81.D

CONNECTED NET SLP_S0_L TO Q79.D

8/15/16

ADDED R516, R517, R518

C4875

0.1u/16V_4

R4526

10_5%_4

colsed to U4 AC55 pin

within 100 mils

PP3300_SOC_A

R52

100K_5%_4

R278

100K_5%_4

BATLOW_L

PCH_INTRUDER

1

2

X2

1 2

32.768KHZ/20ppm

R45 10M_5%_4

C2

15p/50V_4

5

R324 *0_5%_4

R325 *1M_1%_4

PCH_OSCOUT

PCH_OSCIN

C1

15p/50V_4

PCH_RTC_X2PCH_RTC_X1

C3

15p/50V_4

C4

15p/50V_4

C4880

0.1u/16V_4

R4531

10_5%_4

colsed to U4 AG57 pin

within 100 mils

C360 0.1u/16V_4

PCH_RSMRST_L[15,24]

PCH_SUSCLK[23]

EC_PCH_PWROK[24]

EC_PCH_PWR_BTN_ODL[15,24]

SYS_RST_ODL[15,16,24,35]

PLT_RST_L[7,15,17,18,23,24,35]

EN_PP3300_EMMC[33]

R58

R56

10K_5%_4

PCH_OSCIN

PCH_OSCOUT

PCH_RTC_X1

PCH_RTC_X2

RTC_EXPAD

PCH_RTEST_ODL

PCH_RTCRST_ODL

PCH_RSMRST_L

SLP_S4_PCH_L

SLP_S3_PCH_L

SLP_S0_PCH_L

PMU_RCOMP

R53

200_1%_4

6/30/16

Changed EN_PP3300_EMMC_ODL

to EN_PP3300_EMMC

EC_PCH_RTCRST[24]

PCH_RSMRST_OD

2

SLP_S0_PCH_L SLP_S3_PCH_L SLP_S4_PCH_L

R516 *0_5%_2

1

PJA3413

3

Q79

4

U4I

R27

OSCIN

P29

OSCOUT

AF62

OSC_CLK_OUT_4

AE60

OSC_CLK_OUT_3

AG63

OSC_CLK_OUT_2

AF61

OSC_CLK_OUT_1

AG62

OSC_CLK_OUT_0

AC59

BRTCX1_PAD

AC58

BRTCX2_PAD

AG51

BVCCRTC_EXTPAD

AH49

RTEST_B

AC55

SRTCRST_B

AC57

RSMRST_B

AE62

PMU_SUSCLK

AG58

SUS_STAT_B

AC63

SUSPWRDNACK

AG49

COREPWROK

AK54

PMU_SLP_S4_B

AC62

PMU_SLP_S3_B

AD61

PMU_SLP_S0_B

AK55

PMU_PWRBTN_B

AD62

PMU_RESETBUTTON_B

AG57

PMU_PLTRST_B

AG55

PMU_WAKE_B

AH51

PMU_BATLOW_B

AK49

PMU_AC_PRESENT

AC54

INTRUDER

AG59

PMU_RCOMP

CPU_APL_1296P

EC_PCH_RTCRST

R507

499K_1%_2

ICLK

PMC

RTC

PMIC_STDBY

GP213_PMIC_SDWN_B

PMIC_RESET_B

PMIC_PWRGOOD

PMIC_I2C_SDA

PMIC_I2C_SCL

GP214_PMIC_BCUDISW2

GP215_PMIC_BCUDISCRIT

PMC_SPI_TXD

PMC_SPI_RXD

PMC_SPI_FS2

PMC_SPI_FS1

PMC_SPI_FS0

PMC_SPI_CLK

SVID

SVID_ALERT_B

PROCHOT_B

THERMTRIP_B

THERMAL

PMU

THERMDACPU00

THERMDCCPU00

THERMDAGT

THERMDCGT

ITP/JTAG

CX_PREQ_B

CX_PRDY_B

PP3300_RTC PP3300_RTC

R50

20K_5%_4

PCH_RTCRST_ODL

3

2

Q7

PJE138K

1

SLP_S0_L [24,30] SLP_S3_L [7,17,24,30,33] SLP_S4_L [24,30]

C5

1u/6.3V_4

1

PJA3413

R517 *0_5%_2

J45

M47

F48

H48

F47

H45

L47

P47

H50

J50

M48

P48

L48

E52

C17

SVID_CLK

C18

SVID_DATA

B17

E47

J47

AG54

AG52

J43

H43

B23

TCK

C24

TRST_B

C23

TMS

C22

TDI

A22

TDO

C20

C21

B19

CX_PMODE

B21

JTAGX

EC_PCH_RTCRST

PCH_RSMRST_OD PCH_RSMRST_OD

2

3

Q81

3

10K_5%_4

EDP_HPD_1V8_ODL

SVID_ALERT_L

51_5%_4

PCH_RTEST_ODL

3

2

1

R509

499K_1%_2

R333 10K_5%_4

PCH_PROCHOT_ODL [24,29,30]

THERMTRIP_L [30]

R55

Q8

PJE138K

10K_5%_4

R62

51_5%_4

R57

*51_5%_4

R63

C418

*22p/25V_2

R65

51_5%_4

R54

20K_5%_4

C6

1u/6.3V_4

R64

*1K_5%_4

PP1050_S

R67

100_5%_4

8/11/16

ADDED Q80 R508, C447

CONNECTED GATE OF Q80.G TO PCH_RSMRST_L

ADDED NET PCH_RSMRST_OD AND CONNECTED IT

FROM Q80.D TO Q79.G, Q81.G, Q82.G

R66

*1K_5%_4

SOC_GPIO213

SOC_GPIO223

SOC_NCTF_H48

PCH_I2C_PMIC_SDA [30]

PCH_I2C_PMIC_SCL [30]

C419

*22p/25V_2

R68

100_5%_4

SLP_S3_L[7,17,24,30,33]

2

3

1

PJA3413

Q82

R518 *0_5%_2

2

4/13 Updated

R59 100K_5%_4

Q11

3

PJE138K

2

1

PP1800_SOC_A

R69

100_5%_4

TCK [15]

NTRST/EXTD [15]

TMS/TMSC [15]

TDI/EXTB [15]

TDO/EXTA [15]

EXTE/TRIGIN [15]

EXTF/TRIGOUT [15]

PP3300_A

3

2

1

R510

499K_1%_2

PP1800_SOC_A

EDP_HPD_3V3 [21]

PLT_RST_L [7,15,17,18,23,24,35]

R191

R190

100K_5%_2

SLP_S33

Q56

PJE138K

PCH_RSMRST_L

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

1K_1%_2

SLP_S33_Q

3

2

Q57

PJE138K

1

APL PMU/JTAG

APL PMU/JTAG

APL PMU/JTAG

Friday, July 21, 2017

Friday, July 21, 2017

Friday, July 21, 2017

PP3300_A

R508

499K_1%_2

PCH_RSMRST_OD

ZRX

ZRX

ZRX

C447

*1u/6.3V_4

3

2

Q80

PJE138K

1

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

387

387

387

1A

1A

1A

5

4

3

2

1

PPVAR_VCCGI

D D

C C

B B

A A

21A 3.3A

AA36

AA37

AA39

AC36

AC37

AE36

AE37

AG36

E43

E45

E48

E50

R45

R47

U36

U37

U39

U41

U42

U44

U46

U47

U48

V36

V37

V39

V41

Y36

Y37

Y39

Y41

AA28

AA30

AA32

AC28

AC30

AC32

AE28

AE30

AE32

AG28

AG30

AG32

AJ28

AJ30

AJ32

AK28

AK30

AK32

AK34

AM30

E29

E35

E37

F29

U28

U30

U32

V28

V30

V32

Y28

Y30

Y32

U4J

VCGI_SVID_AA36

VCGI_SVID_AA37

VCGI_SVID_AA39

VCGI_SVID_AC36

VCGI_SVID_AC37

VCGI_SVID_AE36

VCGI_SVID_AE37

VCGI_SVID_AG36

VCGI_SVID_E43

VCGI_SVID_E45

VCGI_SVID_E48

VCGI_SVID_E50

VCGI_SVID_R45

VCGI_SVID_R47

VCGI_SVID_U36

VCGI_SVID_U37

VCGI_SVID_U39

VCGI_SVID_U41

VCGI_SVID_U42

VCGI_SVID_U44

VCGI_SVID_U46

VCGI_SVID_U47

VCGI_SVID_U48

VCGI_SVID_V36

VCGI_SVID_V37

VCGI_SVID_V39

VCGI_SVID_V41

VCGI_SVID_Y36

VCGI_SVID_Y37

VCGI_SVID_Y39

VCGI_SVID_Y41

VCGI_SVID_AA28

VCGI_SVID_AA30

VCGI_SVID_AA32

VCGI_SVID_AC28

VCGI_SVID_AC30

VCGI_SVID_AC32

VCGI_SVID_AE28

VCGI_SVID_AE30

VCGI_SVID_AE32

VCGI_SVID_AG28

VCGI_SVID_AG30

VCGI_SVID_AG32

VCGI_SVID_AJ28

VCGI_SVID_AJ30

VCGI_SVID_AJ32

VCGI_SVID_AK28

VCGI_SVID_AK30

VCGI_SVID_AK32

VCGI_SVID_AK34

VCGI_SVID_AM30

VCGI_SVID_E29

VCGI_SVID_E35

VCGI_SVID_E37

VCGI_SVID_F29

VCGI_SVID_U28

VCGI_SVID_U30

VCGI_SVID_U32

VCGI_SVID_V28

VCGI_SVID_V30

VCGI_SVID_V32

VCGI_SVID_Y28

VCGI_SVID_Y30

VCGI_SVID_Y32

CPU_APL_1296P

RSVD_VNNAON

VNN_SVID_AJ37

VNN_SVID_AJ39

VNN_SVID_AJ41

VNN_SVID_AJ42

VNN_SVID_AJ46

VNN_SVID_AK37

VNN_SVID_AK39

VNN_SVID_AK41

VNN_SVID_AK42

VNN_SVID_AK44

VNN_SVID_AK46

VNN_SVID_LOAD_PIN

VNN_SENSE

VCCIOA_AM23

VCCIOA_AM25

VCCIOA_AM41

VCCIOA_AM42

VCCRAM_1P05_AA25

VCCRAM_1P05_AC25

VCCRAM_1P05_AE25

VCCRAM_1P05_U23

VCCRAM_1P05_V22

VCCRAM_1P05_V23

VCCRAM_1P05_V25

VCCRAM_1P05_Y23

VCCRAM_1P05_Y25

VCCRAM_1P05_U25

VCCRAM_1P05_U20

VCCRAM_1P05_LOAD_PIN

VCCRAM_1P05_IO_AA22

VCCRAM_1P05_IO_AC23

VCCRAM_1P05_IO_V18

VCCRAM_1P05_IO_Y18

VCCRAM_1P05_IO_Y20

VCCRAM_1P05_FUSE

VCCRAM_1P05_FHV1_T15

VCCRAM_1P05_FHV1_T13

VCCRAM_1P05_3PHASEIO

VCGI_SVID_LOAD_PIN

VCGI_SENSE

VCGI_VSS_SENSE

RSVD_VNNAON

AJ44

AJ37

AJ39

AJ41

AJ42

AJ46

AK37

AK39

AK41

AK42

AK44

AK46

AM44

AG48

AM23

AM25

AM41

AM42

AA25

AC25

AE25

U23

V22

V23

V25

Y23

Y25

U25

U20

U22

AA22

AC23

V18

Y18

Y20

P16

T15

T13

AA23

R25

R25 NCTF

PPVAR_VCCGI_SENSE_P

R41

PPVAR_VCCGI_SENSE_N

R43

1

PPVAR_VNN

TP22

*

PPVAR_VNN_SENSE [31]

1.5A

PP1100_VCCIO

PP1050_VCCRAM_S

PP1050_VCCRAM_IO_S

PP1050_VCCRAM_IO_S

PPVAR_VCCGI

R476

100_1%_2

R477

100_1%_2

2.7A

PPVAR_VCCGI_SENSE_P [31]

PPVAR_VCCGI_SENSE_N [31]

6/6/16

ADDED R476

ADDED R477

PP1240_A

PP1240_A

PP1050_S

PP1050_S

PP1100_VDDQ

1.8A0.13A

PP1240_VDD2_SRAM_APP1240_VDD2_IO_A

U4K

AJ20

VDD2_1P24_PLL_AJ20

AJ22

VDD2_1P24_PLL_AJ22

AG20

VDD2_1P24_USB2

AE18

VDD2_1P24_MPHY_AE18

AE20

VDD2_1P24_MPHY_AE20

AE22

VDD2_1P24_MPHY_AE22

AG22

VDD2_1P24_MPHY_AG22

AM20

VDD2_1P24_GLML2LDO_AM20

AM28

VDD2_1P24_GLML2LDO_AM28

AM37

VDD2_1P24_GLML2LDO_AM37

AK20

VDD2_1P24_GLML2

AA18

VDD2_1P24_DSI

AA20

VDD2_1P24_CSI

AK22

0.4A

PP1800_SOC_A

10/24/16

R461,R462,463,464,465 NEED CHANGE TO SHORT

PADS BEFORE RAMP

VDD2_1P24_AUD_ISH

AC20

VDD2_1P24_LOAD_PIN_OBS

AA46

VDD1_1P8_AA46

AC46

VDD1_1P8_AC46

AE44

VDD1_1P8_AE44

AE42

VDD1_1P8_AE42

AC44

VDD1_1P8_AC44

AE46

VDD1_1P8_AE46

AG25

VDD1_1P8_AG25

AC42

VDD1_1P8_MCIVR

CPU_APL_1296P

R461 *Short_6

R462 *Short_6

R463 *Short_6

R464 *Short_6

R465 *Short_6

PP1240_VDD2_IO_A

PP1240_VDD2_SRAM_A

PP1050_VCCRAM_IO_S

PP1050_VCCRAM_S

PP1100_VCCIO

VCCDDQ_AN18

VCCDDQ_AN20

VCCDDQ_AN22

VCCDDQ_AN23

VCCDDQ_AN41

VCCDDQ_AN42

VCCDDQ_AN44

VCCDDQ_AN46

VCCDDQ_AR17

VCCDDQ_AR47

VCCDDQ_AT13

VCCDDQ_AT17

VCCDDQ_AT47

VCCDDQ_AT51

VCCDDQ_AV14

VCCDDQ_AV50

VCCDDQ_LOAD_PIN_OBS

VDD3_3P3_AC41

VDD3_3P3_AA42

VDD3_3P3_Y44

VDD3_3P3_V44

VDD3_3P3_V46

VDD3_3P3_AJ25

VDD3_3P3_AK25

VCCRTC_3P3

AN18

AN20

AN22

AN23

AN41

AN42

AN44

AN46

AR17

AR47

AT13

AT17

AT47

AT51

AV14

AV50

AM32

AC41

AA42

Y44

V44

V46

AJ25

AK25

AA44

2.8A

PP1100_VDDQ

0.15A

PP3300_SOC_A

PP3300_RTC

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, July 21, 2017

Date: Sheet of

Friday, July 21, 2017

Date: Sheet of

5

4

3

2

Friday, July 21, 2017

PROJECT :

APL POWER

APL POWER

APL POWER

1

ZRX

ZRX

ZRX

1A

1A

1A

388

388

388

5

4

3

2

1

U4L

AN53

VSSA_AN53

AN54

VSS_AN54

AN56

VSS_AN56

AN57

VSS_AN57

AN59

VSS_AN59

AN63

D D

C C

B B

AN7

AN8

AP55

AP9

AR19

AR32

AR45

AT12

AT16

AT19

AT2

AT25

AT29

AT3

AT35

AT39

AT45

AT48

AT52

AT57

AT61

AT62

AT7

AU32

AV19

AV2

AV21

AV23

AV29

AV3

AV32

AV35

AV41

AV43

AV45

AV55

AV61

AV62

AV9

AW14

AW30

AW34

AW50

AY10

AY32

AY54

AY58

AY6

B62

B63

BA1

BA12

BA16

BA17

BA2

BA21

BA25

B2

B3

B9

VSS_AN63

VSS_AN7

VSS_AN8

VSS_AP55

VSS_AP9

VSS_AR19

VSS_AR32

VSS_AR45

VSS_AT12

VSS_AT16

VSS_AT19

VSS_AT2

VSS_AT25

VSS_AT29

VSS_AT3

VSS_AT35

VSS_AT39

VSS_AT45

VSS_AT48

VSS_AT52

VSS_AT57

VSS_AT61

VSS_AT62

VSS_AT7

VSS_AU32

VSS_AV19

VSS_AV2

VSS_AV21

VSS_AV23

VSS_AV29

VSS_AV3

VSS_AV32

VSS_AV35

VSS_AV41

VSS_AV43

VSS_AV45

VSS_AV55

VSS_AV61

VSS_AV62

VSS_AV9

VSS_AW14

VSS_AW30

VSS_AW34

VSS_AW50

VSS_AY10

VSS_AY32

VSS_AY54

VSS_AY58

VSS_AY6

VSS_B2

VSS_B3

VSS_B62

VSS_B63

VSS_B9

VSS_BA1

VSS_BA12

VSS_BA16

VSS_BA17

VSS_BA2

VSS_BA21

VSS_BA25

VSS_BA27

VSS_BA29

VSS_BA32

VSS_BA35

VSS_BA37

VSS_BA39

VSS_BA43

VSS_BA47

VSS_BA48

VSS_BA52

VSS_BA62

VSS_BA63

VSS_BB19

VSS_BB25

VSS_BB39

VSS_BB45

VSS_BB61

VSS_BC32

VSS_BD32

VSS_BD56

VSS_BD61

VSS_BE10

VSS_BE12

VSS_BE16

VSS_BE17

VSS_BE21

VSS_BE27

VSS_BE29

VSS_BE35

VSS_BE37

VSS_BE43

VSS_BE47

VSS_BE48

VSS_BE52

VSS_BE54

VSS_BE63

VSS_BF32

VSS_BF61

VSS_BG19

VSS_BG23

VSS_BG29

VSS_BG32

VSS_BG35

VSS_BG41

VSS_BG45

VSS_BH21

VSS_BH25

VSS_BH39

VSS_BH43

VSS_BH62

VSS_BH63

VSS_BJ10

VSS_BJ14

VSS_ BJ18

VSS_BJ28

VSS_BJ32

VSS_BJ36

VSS_BJ46

VSS_BB3

VSS_BD3

VSS_BD8

VSS_BE1

VSS_BF3

VSS_BH1

VSS_BH2

VSS_BJ4

BA27

BA29

BA32

BA35

BA37

BA39

BA43

BA47

BA48

BA52

BA62

BA63

BB19

BB25

BB3

BB39

BB45

BB61

BC32

BD3

BD32

BD56

BD61

BD8

BE1

BE10

BE12

BE16

BE17

BE21

BE27

BE29

BE35

BE37

BE43

BE47

BE48

BE52

BE54

BE63

BF3

BF32

BF61

BG19

BG23

BG29

BG32

BG35

BG41

BG45

BH1

BH2

BH21

BH25

BH39

BH43

BH62

BH63

BJ10

BJ14

BJ18

BJ28

BJ32

BJ36

BJ4

BJ46

R29

A12

A16

A20

A24

A28

A32

A36

A40

A44

A48

A52

A56

A62

AA1

AA2

AA27

AA34

AA41

AA63

AB10

AB12

AB16

AB48

AB5

AB52

AB57

AB59

AB9

AC18

AC27

AC34

AC39

AE1

AE10

AE11

AE13

AE14

AE16

AE17

AE2

AE23

AE27

AE34

AE39

AE4

AE41

AE47

AE48

AE5

AE50

AE51

AE53

AE54

AE56

AE57

AE59

AE63

AE7

AE8

AG13

AG18

AG23

AG27

A5

A9

U4M

VSSA_R29

VSS_A12

VSS_A16

VSS_A20

VSS_A24

VSS_A28

VSS_A32

VSS_A36

VSS_A40

VSS_A44

VSS_A48

VSS_A5

VSS_A52

VSS_A56

VSS_A62

VSS_A9

VSS_AA1

VSS_AA2

VSS_AA27

VSS_AA34

VSS_AA41

VSS_AA63

VSS_AB10

VSS_AB12

VSS_AB16

VSS_AB48

VSS_AB5

VSS_AB52

VSS_AB57

VSS_AB59

VSS_AB9

VSS_AC18

VSS_AC27

VSS_AC34

VSS_AC39

VSS_AE1

VSS_AE10

VSS_AE11

VSS_AE13

VSS_AE14

VSS_AE16

VSS_AE17

VSS_AE2

VSS_AE23

VSS_AE27

VSS_AE34

VSS_AE39

VSS_AE4

VSS_AE41

VSS_AE47

VSS_AE48

VSS_AE5

VSS_AE50

VSS_AE51

VSS_AE53

VSS_AE54

VSS_AE56

VSS_AE57

VSS_AE59

VSS_AE63

VSS_AE7

VSS_AE8

VSS_AG13

VSS_AG18

VSS_AG23

VSS_AG27

VSS_AG34

VSS_AG37

VSS_AG39

VSS_AG41

VSS_AG42

VSS_AG44

VSS_AG46

VSS_AH15

VSS_AH16

VSS_AH48

VSS_AH5

VSS_AH52

VSS_AH54

VSS_AH55

VSS_AH57

VSS_AH58

VSS_AH59

VSS_AH6

VSS_AH7

VSS_AJ1

VSS_AJ18

VSS_AJ2

VSS_AJ23

VSS_AJ27

VSS_AJ34

VSS_AJ36

VSS_AJ63

VSS_AK10

VSS_AK12

VSS_AK18

VSS_AK23

VSS_AK27

VSS_AK36

VSS_AK48

VSS_AK5

VSS_AK52

VSS_AK59

VSS_AK9

VSS_AM18

VSS_AM22

VSS_AM27

VSS_AM34

VSS_AM36

VSS_AM39

VSS_AM46

VSS_AN1

VSS_AN10

VSS_AN11

VSS_AN13

VSS_AN14

VSS_AN16

VSS_AN17

VSS_AN2

VSS_AN25

VSS_AN27

VSS_AN28

VSS_AN30

VSS_AN34

VSS_AN36

VSS_AN37

VSS_AN39

VSS_AN47

VSS_AN48

VSS_AN5

VSS_AN50

VSS_AN51

AG34

AG37

AG39

AG41

AG42

AG44

AG46

AH15

AH16

AH48

AH5

AH52

AH54

AH55

AH57

AH58

AH59

AH6

AH7

AJ1

AJ18

AJ2

AJ23

AJ27

AJ34

AJ36

AJ63

AK10

AK12

AK18

AK23

AK27

AK36

AK48

AK5

AK52

AK59

AK9

AM18

AM22

AM27

AM34

AM36

AM39

AM46

AN1

AN10

AN11

AN13

AN14

AN16

AN17

AN2

AN25

AN27

AN28

AN30

AN34

AN36

AN37

AN39

AN47

AN48

AN5

AN50

AN51

BJ50

BJ54

BJ56

BJ60

BJ8

C12

C16

C28

C32

C40

C48

D32

D58

E12

E14

E19

E27

E54

F10

F21

F32

F37

F43

F45

F50

F56

F59

F63

G32

H17

H23

H29

H37

H47

H61

J12

J14

J19

J27

J30

J32

J35

J37

J48

J63

K32

K54

K57

L21

L27

L29

L35

L43

L45

L50

M14

M21

M27

D6

E4

F3

G1

H3

H7

K5

K6

U4N

VSSA_BJ50

VSS_BJ54

VSS_BJ56

VSS_BJ60

VSS_BJ8

VSS_C12

VSS_C16

VSS_C28

VSS_C32

VSS_C40

VSS_C48

VSS_D32

VSS_D58

VSS_D6

VSS_E12

VSS_E14

VSS_E59

VSS_E27

VSS_E4

VSS_E54

VSS_F10

VSS_F21

VSS_F3

VSS_F32

VSS_F37

VSS_F43

VSS_F45

VSS_F50

VSS_F56

VSS_F59

VSS_F63

VSS_G1

VSS_G32

VSS_H17

VSS_H23

VSS_H29

VSS_H3

VSS_H37

VSS_H47

VSS_H61

VSS_H7

VSS_J12

VSS_J14

VSS_J19

VSS_J27

VSS_J30

VSS_J32

VSS_J35

VSS_J37

VSS_J48

VSS_J63

VSS_K32

VSS_K5

VSS_K54

VSS_K57

VSS_K6

VSS_L21

VSS_L27

VSS_L29

VSS_L35

VSS_L43

VSS_L45

VSS_L50

VSS_M14

VSS_M21

VSS_M27

VSS_M3

VSS_M32

VSS_M50

VSS_M59

VSS_M9

VSS_N1

VSS_N32

VSS_N63

VSS_P13

VSS_P19

VSS_P35

VSS_P37

VSS_P41

VSS_P43

VSS_P45

VSS_P5

VSS_P55

VSS_P59

VSS_P9

VSS_R23

VSS_R32

VSS_T49

VSS_U1

VSS_U10

VSS_U11

VSS_U13

VSS_U14

VSS_U16

VSS_U17

VSS_U18

VSS_U2

VSS_U27

VSS_U34

VSS_U5

VSS_U50

VSS_U51

VSS_U53

VSS_U54

VSS_U56

VSS_U57

VSS_U59

VSS_U62

VSS_U63

VSS_U7

VSS_U8

VSS_V20

VSS_V27

VSS_V34

VSS_V42

VSS_Y12

VSS_Y16

VSS_Y22

VSS_Y27

VSS_Y34

VSS_Y42

VSS_Y46

VSS_Y48

VSS_Y5

VSS_Y52

VSS_Y54

VSS_Y55

VSS_Y57

VSS_Y59

VSS_Y6

VSS_Y7

M3

M32

M50

M59

M9

N1

N32

N63

P13

P19

P35

P37

P41

P43

P45

P5

P55

P59

P9

R23

R32

T49

U1

U10

U11

U13

U14

U16

U17

U18

U2

U27

U34

U5

U50

U51

U53

U54

U56

U57

U59

U62

U63

U7

U8

V20

V27

V34

V42

Y12

Y16

Y22

Y27

Y34

Y42

Y46

Y48

Y5

Y52

Y54

Y55

Y57

Y59

Y6

Y7

CPU_APL_1296P

A A

5

4

CPU_APL_1296P

3

CPU_APL_1296P

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, July 21, 2017

Date: Sheet of

Friday, July 21, 2017

Date: Sheet of

Friday, July 21, 2017

PROJECT :

APL GROUND

APL GROUND

APL GROUND

1

ZRX

ZRX

ZRX

389

389

389

1A

1A

1A

5

D D

C C

4

U4O

L16

MCIVR_TDI

E16

MCIVR_TDO

B15

MCIVR_TMS

C14

MCIVR_TCK

E23

MCIVR_TRST_B

B13

MCIVR_BREAK_B

A14

MCIVR_GPIO1

D8

MCIVR_GPIO0

C13

MCIVR_VCCIN1P8CTL

J16

MCIVR_DIGPB0

E10

MCIVR_DIGPB1

F14

MCIVR_ANAPB0

E8

MCIVR_ANAPB1

M16

MCIVR_EDM1

C15

MCIVR_EDM0

F23

MCIVR_VCCFUSEPRG

C9

MCIVR_HVMCLKREF

CPU_APL_1296P

3

MCIVR_VCCIN_VR_RDY

MCIVR_PWRGOOD_OUT

MCIVR_EXTBGREF

MCIVR_VTGT_10B

MCIVR_VTGT_10A

MCIVR_VTGT_5B

MCIVR_VTGT_5A

MCIVR_VTGT_24B

MCIVR_VTGT_24A

MCIVR_VTGTVSS

MCIVR_RCOMP

H16

F16

H12

A3

C2

H10

F8

M12

M10

H14

F12

2

1

U4P

T51

NC_T51

L14

NC_L14

R19

NC_R19

E6

MCIVR_RSMRST_B

R17

NC_R17

E3

MCIVR_UBRKPT0

B B

A A

5

D4

A60

A61

BJ2

BG1

P27

AB49

AM59

AM58

4

MCIVR_GPIO2

NC_A60

NC_A61

NC_BJ2

NC_BG1

NC_P27

SPARE_2

SPARE_1

SPARE_0

CPU_APL_1296P

MCIVR_UBRKPT1

NC_P39

NC_R39

NC_R37

NC_J29

NC_P25

NC_R30

NC_C63

NC_E63

NC_AP57

NC_M39

SPARE_11

SPARE_10

3

P39

R39

R37

J29

P25

R30

C63

E63

D2

AP57

M39

AC13

AB13

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

APL NO CONNECT

APL NO CONNECT

APL NO CONNECT

Date: Sheet of

Date: Sheet of

Date: Sheet of

Friday, July 21, 2017

Friday, July 21, 2017

Friday, July 21, 2017

2

ZRX

ZRX

ZRX

3810

3810

1

3810

1A

1A

1A

5

4

3

2

1

PP1800_DRAM_U

PP1100_VDDQ

PP1100_VDDQ

PP1800_DRAM_U

PP1100_VDDQ

PP1100_VDDQ

LPDDR4_SDRAM

U22A

F1

VDD1_1

U1

VDD1_2

G4

VDD1_3

T4

VDD1_4

G9

VDD1_5

T9

VDD1_6

U12

VDD1_7

F12

VDD1_8

H1

VDD2_1

K1

VDD2_2

N1

VDD2_3

R1

VDD2_4

K3

VDD2_5

N3

VDD2_6

A4

VDD2_7

AB4

VDD2_8

F5

VDD2_9

H5

VDD2_10

R5

VDD2_11

U5

VDD2_12

F8

VDD2_13

H8

VDD2_14

R8

VDD2_15

U8

VDD2_16

A9

VDD2_17

AB9

VDD2_18

K10

VDD2_19

N10

VDD2_20

H12

VDD2_21

K12

VDD2_22

N12

VDD2_23

R12

VDD2_24

D1

VDDQ_1

W1

VDDQ_2

B3

VDDQ_3

F3

VDDQ_4

U3

VDDQ_5

AA3

VDDQ_6

B5

VDDQ_7

D5

VDDQ_8

W5

VDDQ_9

AA5

VDDQ_10

B8

VDDQ_11

D8

VDDQ_12

W8

VDDQ_13

AA8

VDDQ_14

B10

VDDQ_15

F10

VDDQ_16

U10

VDDQ_17

AA10

VDDQ_18

D12

VDDQ_19

W12

VDDQ_20

A1

DNU_1

B1

DNU_2

AA1

DNU_3

AB1

DNU_4

A2

DNU_5

AB2

DNU_6

A11

DNU_7

AB11

DNU_8

A12

DNU_9

B12

DNU_10

AA12

DNU_11

AB12

DNU_12

1 OF 2

LPDDR4_SDRAM

U23A

F1

VDD1_1

U1

VDD1_2

G4

VDD1_3

T4

VDD1_4

G9

VDD1_5

T9

VDD1_6

U12

VDD1_7

F12

VDD1_8

H1

VDD2_1

K1

VDD2_2

N1

VDD2_3

R1

VDD2_4

K3

VDD2_5

N3

VDD2_6

A4

VDD2_7

AB4

VDD2_8

F5

VDD2_9

H5

VDD2_10

R5

VDD2_11

U5

VDD2_12

F8

VDD2_13

H8

VDD2_14

R8

VDD2_15

U8

VDD2_16

A9

VDD2_17

AB9

VDD2_18

K10

VDD2_19

N10

VDD2_20

H12

VDD2_21

K12

VDD2_22

N12

VDD2_23

R12

VDD2_24

D1

VDDQ_1

W1

VDDQ_2

B3

VDDQ_3

F3

VDDQ_4

U3

VDDQ_5

AA3

VDDQ_6

B5

VDDQ_7

D5

VDDQ_8

W5

VDDQ_9

AA5

VDDQ_10

B8

VDDQ_11

D8

VDDQ_12

W8

VDDQ_13

AA8

VDDQ_14

B10

VDDQ_15

F10

VDDQ_16

U10

VDDQ_17

AA10

VDDQ_18

D12

VDDQ_19

W12

VDDQ_20

A1

DNU_1

B1

DNU_2

AA1

DNU_3

AB1

DNU_4

A2

DNU_5

AB2

DNU_6

A11

DNU_7

AB11

DNU_8

A12

DNU_9

B12

DNU_10

AA12

DNU_11

AB12

DNU_12

3

1 OF 2

VSS#P12

VSS#G12

VSS#K11

VSS#P10

VSS#G10

VSS#K9

VSS#G8

VSS#G5

VSS#K4

VSS#P3

VSS#G3

VSS#K2

VSS#P1

VSS#G1

VSS#J1

VSS#T1

VSS#N2

VSS#J3

VSS#T3

VSS#N4

VSS#T5

VSS#T8

VSS#N9

VSS#J10

VSS#T10

VSS#N11

VSS#J12

VSS#T12

VSS#E1

VSS#Y1

VSS#W2

VSS#AB3

VSS#W4

VSS#E5

VSS#Y5

VSS#C8

VSS#V8

VSS#AB8

VSS#W9

VSS#AB10

VSS#W11

VSS#E12

VSS#Y12

VSS#V12

VSS#C12

VSS#D11

VSS#A10

VSS#D9

VSS#Y8

VSS#E8

VSS#AB5

VSS#V5

VSS#C5

VSS#D4

VSS#A3

VSS#D2

VSS#V1

VSS#C1

NC/ZQ1

DNU#G11

VSS#P12

VSS#G12

VSS#K11

VSS#P10

VSS#G10

VSS#K9

VSS#G8

VSS#G5

VSS#K4

VSS#P3

VSS#G3

VSS#K2

VSS#P1

VSS#G1

VSS#J1

VSS#T1

VSS#N2

VSS#J3

VSS#T3

VSS#N4

VSS#T5

VSS#T8

VSS#N9

VSS#J10

VSS#T10

VSS#N11

VSS#J12

VSS#T12

VSS#E1

VSS#Y1

VSS#W2

VSS#AB3

VSS#W4

VSS#E5

VSS#Y5

VSS#C8

VSS#V8

VSS#AB8

VSS#W9

VSS#AB10

VSS#W11

VSS#E12

VSS#Y12

VSS#V12

VSS#C12

VSS#D11

VSS#A10

VSS#D9

VSS#Y8

VSS#E8

VSS#AB5

VSS#V5

VSS#C5

VSS#D4

VSS#A3

VSS#D2

VSS#V1

VSS#C1

NC/ZQ1

DNU#G11

P12

G12

K11

P10

G10

K9

G8

G5

K4

P3

G3

K2

P1

G1

J1

T1

N2

J3

T3

N4

T5

T8

N9

J10

T10

N11

J12

T12

E1

Y1

W2

AB3

W4