Page 1

Model Service Manual CD Mechanism Module Mechanism Unit

DEH-P400/X1N/UC

DEH-P4000/X1N/UC CRT2308 CXK5200 CXB3100

DEH-P4050/X1N/ES

DEH-P3000R/X1N/EW CRT2309 CXK5200 CXB3100

DEH-P200/X1N/UC

DEH-P300/X1N/UC CRT2310 CXK5200 CXB3100

DEH-P3000/X1N/UC

DEH-P20/X1N/UC

DEH-P2000/X1N/UC CRT2311 CXK5200 CXB3100

DEH-P2050/X1N/ES

DEH-2000R/X1N/EW

DEH-2020R/X1N/GR CRT2312 CXK5200 CXB3100

DEH-2030R/X1N/EW

DEH-10/X1N/UC

DEH-1000/X1N/UC CRT2313 CXK5200 CXB3100

DEH-1050/X1N/ES

PIONEER ELECTRONIC CORPORATION 4-1, Meguro 1-Chome, Meguro-ku, Tokyo 153-8654, Japan

PIONEER ELECTRONICS SERVICE INC. P.O.Box 1760, Long Beach, CA 90801-1760 U.S.A.

PIONEER ELECTRONIC [EUROPE] N.V. Haven 1087 Keetberglaan 1, 9120 Melsele, Belgium

PIONEER ELECTRONICS ASIACENTRE PTE.LTD. 253 Alexandra Road, #04-01, Singapore 159936

C PIONEER ELECTRONIC CORPORATION 1998

K-FZA. DEC. 1998 Printed in Japan

ORDER NO.

CRT2300

CD MECHANISM MODULE

CX-916

- This service manual describes the operation of the CD mechanism incorporated in models listed in the

table below.

- When performing repairs use this manual together with the specific manual for model under repair.

CONTENTS

1. CIRCUIT DESCRIPTIONS ...........................................2

2. MECHANISM DESCRIPTIONS.................................17

3. DISASSEMBLY .........................................................18

Page 2

2

CX-916

1. CIRCUIT DESCRIPTIONS

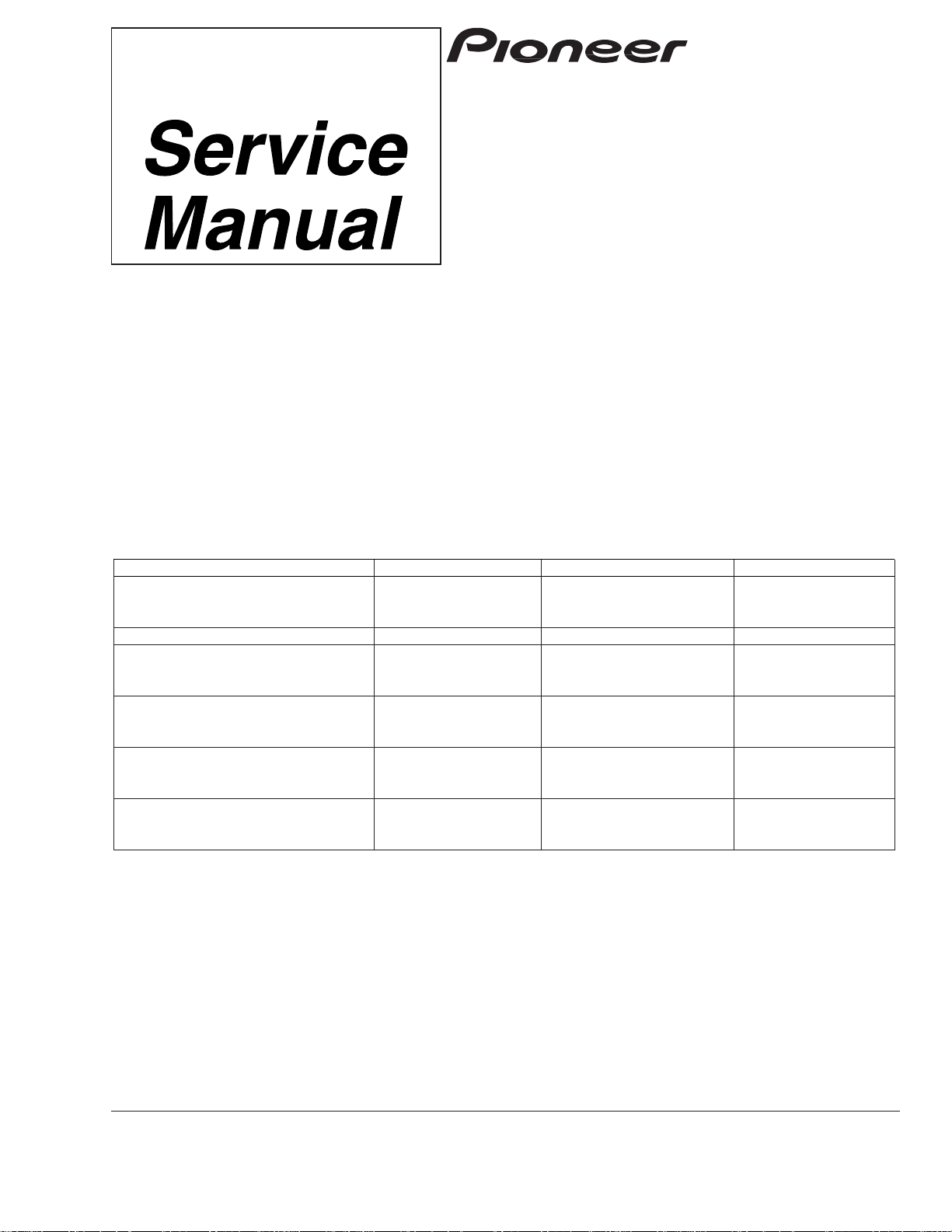

The LSI (UPD63710GC) used on this unit comprises five main blocks ; the pre-amp section, servo, signal processor,

DAC and CD text decoder (not used on this model). It also equips with nine automatic adjustment functions.

1.1 PRE-AMP SECTION

This section processes the pickup output signals to

create the signals for the servo, demodulator and

control.

The pickup output signals are I-V converted by the preamp with the built-in photo-detector in the pickup, then

added by the RF amp to obtain RF, FE, TE, TE zero cross

and other signals.

This pre-amp section is built in the servo LSI

UPD63710GC (IC201). The following describes function

of each section.

Since this system has a single power supply (+5V), the

reference voltage for this LSI and pickup are set to

REFO (2.5V). The REFO is obtained by passing the

REFOUT from the LSI through the buffer amplifier. The

REFO is output from Pin 89 of this LSI. All

measurements are done using this REFO as reference.

Note : During the measurement, do not try to short the

REFO and GND.

1) APC Circuit (Automatic Power Control)

When the laser diode is driven with constant current,

the optical output has large negative temperature

characteristics. Thus, the current must be controlled

from the monitor diode so that the output may be

constant. APC circuit is for it. The LD current is obtained

by measuring the voltage between LD1 and V+5. The

value of this current is about 35mA.

71

72

74

76

AGCI

77

RFO

75

78

79

80

73

91

90

93

92

C-3T

FEO

FE-

TEO

TE-

85

86

87

E

97

PD

99

PN

F

D

82

83

84

B

C

A

RF-

EQ1

EQ2

AGCO

RFI

ASY

EFM

PEAK DET.

LPF

BOTTOM DET.

S/H

D/A

A/D

D/A

A/D

94

98

TE2

LD

VREG

GND

APN

LDON

EFM

DEFECT

FOK

A3T

MIRR

To the

following stage

of the LSI

Vref

Vref

Vref

Vref

Vref

Vref

Vref

Vref

Vref

Vref

Vref

Vref

Vref

Vref

Vref

·····Vref(+2.5V)

97

PD

99

PN

98

LD

VREG

GND

AMP_PN

(H:Nch L:Pch)

LDON

(H:LD MOVE L:STOP)

Vref

·····Vref(+2.5V)

14

5

R102

10

R101

12

Q101

2SB1132

C102

0.1µF

C103

100µF/6.3V

PU UNIT

R103

2.2k

C105

0.33µF

+5V

1k

110k

3p

3p

150k

100k

100k

16k

1k

Fig.1 : BLOCK DIAGRAM OF BUILT-IN RF AMPLIFIER

Fig.2 : APC CIRCUIT

Page 3

CX-916

3

2) RF Amplifier and RFAGC Amplifier

The photo-detector outputs (A +C) and (B +D) are

added, amplified and equalized on this LSI and then

output to the RFI terminal as the RF signal. (The eye

pattern can be checked by this signal.)

The RFI voltage low frequency component is :

RFI = (A +B +C +D) ×3.2

RFI is used on the FOK generator circuit and RF offset

adjusting circuit.

R214 is an offset resistor for maintaining the bottom

reference voltage of the RFI signal at 1.5 VDC. The D/A

output used for the RF offset adjustment (to be

described later) is entered via this resistor.

After the RFI signal from Pin 77 is externally AC

coupled, entered to Pin 76 again, then amplified on the

RFAGC amplifier to obtain the RFO signal.

The RFAGC adjustment function (to be described later)

built-in the LSI is used for switching feedback gain of

the RFAGC amplifier so that the RFO output may go to

1.5 ±0.3Vpp.

The RFO signal is used for the EFM, DFCT, MIRR and

RFAGC adjustment circuits.

3) RFOK Circuit

This circuit generates the signal that is used for

indicating the timing of closing the focus or state of the

focus close currently being played. This signal is output

from Pin 4 as the FOK signal. It goes high when the

focus close and in-play.

The RFOK signal is generated by holding DC level of the

RFI at its peak with the succeeding digital section, then

comparing it at a specific threshold level. Thus, the

RFOK signal goes high even if the pit is absent. It

indicates that the focus close can take place on the disc

mirror surface, too.

This signal is also supplied to the micro computer via

the low pass filter as the FOK signal and used for the

protection and the RF amplifier gain switching.

CN101

84

6

13

83

82

10k

10k

85

FOK

CIRCUIT

A/D

4

A+C

16k

B+D

10k

16k

10k

R214

12k

C209 3pF

R212

10k

R207

1.8k

C206

27pF

R213

10k

80 79 74757677

D/A

12k

66

10k

RFOAGCIRFI

C207

0.22µF

C206

3900pF

FOK

TO EFM

CIRCUIT

Fig.3 : RFAMP, RFAGC AND FOK CIRCUIT

Page 4

4

CX-916

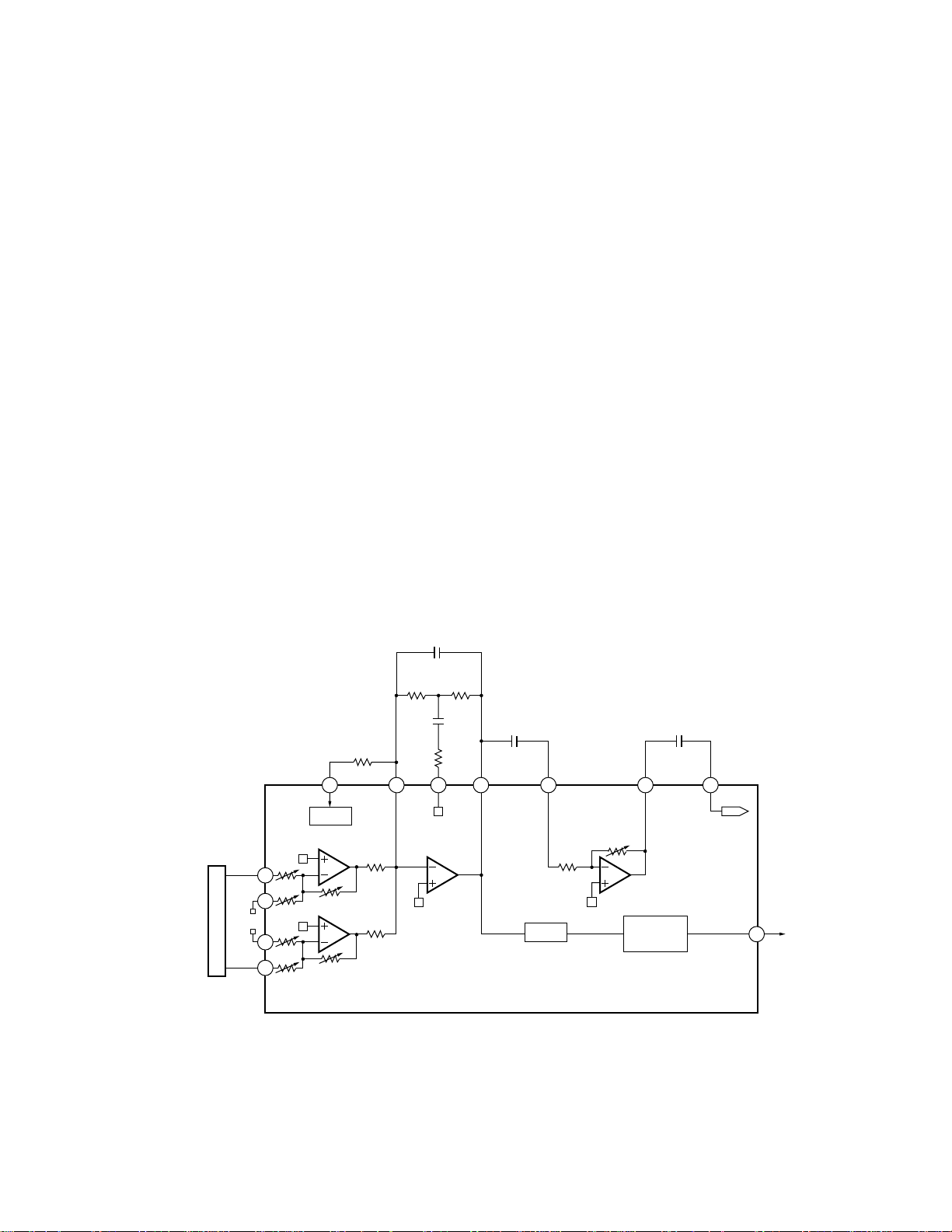

Fig.5 TRACKING ERROR AMPLIFIER AND TRACKING ZERO CROSSING AMPLIFIER

4) Focus Error Amplifier

The photo-detector outputs (A+C) and (B+D) are passed

through a differential amplifier and an error amplifier, and

then (A+C−B−D) is output from Pin 91 as the FE signal.

The FE voltage low frequency component is :

FE = (A + C − B − D) ××

= (A + C − B − D) × 5

Using REFO as the reference, an S-curve of approximately 1.5

Vpp is obtained for the FE output. The final-stage amplifier

cutoff frequency is 11.4 kHz.

5) Tracking Error Amplifier

The photo-detector outputs E and F are passed through

a differential amplifier and an error amplifier, and then

(E −F) is output from Pin 93 as the TE signal. The TE

voltage low frequency component is :

TE =(E −F)

××

=

(E −F) ×5.7 (Effective LSI output is 5.0).

Using REFO as the reference, the TE waveform of

approximately 1.3 Vpp is obtained for the TE output.

The final-stage amplifier cutoff frequency is 20 kHz.

6) Tracking Zero Crossing Amplifier

TEC signal (the tracking zero crossing signal) is

obtained by multiplying the TE signal four times. It is

used for locating the zero crossing points of the

tracking error. The zero cross point detection is done for

the following two reasons :

1

To count tracks for carriage moves and track jumps.

2

To detect the direction in which the lens is moving

when the tracking is closed (it is used on the

tracking brake circuit to be described later).

The TEC signal frequency range is 300 Hz to 20 kHz.

TEC voltage =TE level ×4

Theoretical TEC level is 5.2V. The signal exceeds Drange of the operational amplifier and thus is clipped.

It, however, can be ignored since this signal is used by

the servo LSI only at the zero crossing point.

20k

CN101

84

6

13

83

82

10k

20k

85

A+C

16k

B+D

48k

16k

10k

9190

D/A

80k

110k

FE

C210 220pF

R200 300k

A/D

FE OFFSET

TO DIG. EQ

48k

38k

CN101

9

11

86

56k

38k

87

F

E

F

224k

E

48k

224k

56k

9392

D/A

80k

110k

TE

C211 100pF

A/D

TE OFFSET

TO DIG. EQ

48k

R216

27k

R215

27k

60k

20k

95

94

TE2

TEC

R210

0

C212

6800pF

16k

10k

(80k//300k)

20k

Fig.4 : FOCUS ERROR AMPLIFIER

224k

(56k+27k)

80k

38k

Page 5

CX-916

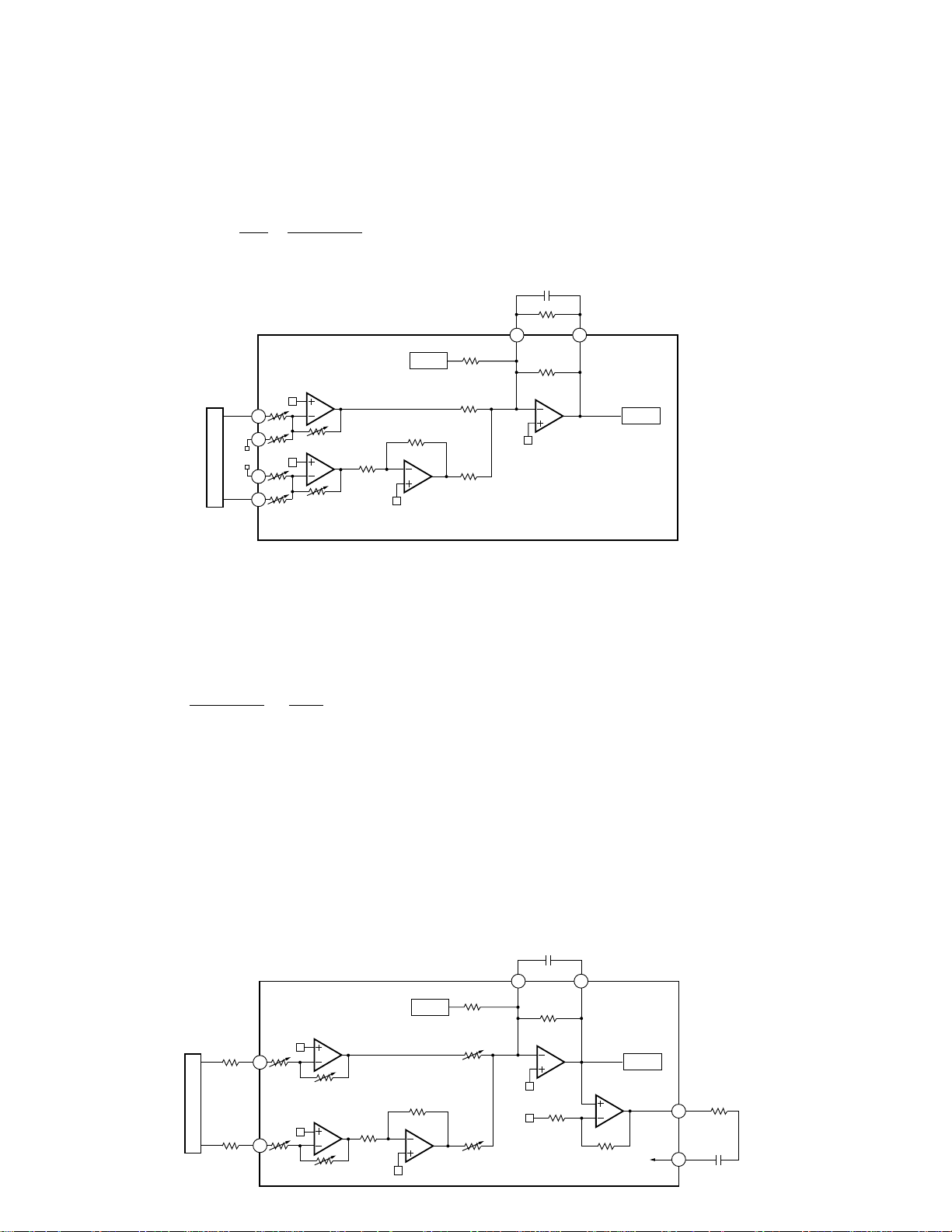

7) DFCT (Defect) Circuit

The DFCT signal is used for detecting defects on the

mirrored disc surface. It allows monitoring from the

HOLD pin (Pin 2). It goes high when defects are found

on the mirrored surface.

The DFCT signal is generated by comparing the RF

amplified signal (which is obtained by bottom holding

the RFO signal) at a specific threshold level by the

succeeding digital section.

Stains or scratches on the disc can constitute the

defects on the mirrored disc surface. Thus, as long as

the DFCT signal remains high in the LSI, the focus and

tracking servo drives are held in the current state so

that a better defect prevention may be ensured.

8) 3TOUT Circuit

The 3TOUT signal is generated by entering disturbance

to the focus servo loop, comparing phase of

fluctuations of the RF signal 3T component against that

of the FE signal at that time, then converting the signal

to DC level. This signal is used for adjusting bias of the

FE signal (to be described later). This signal is not

output from the LSI, thus its monitoring is not available.

9) MIRR (Mirror) Circuit

The MIRR signal shows the on track and off track data,

and is output from Pin 3.

When the laser beam is

On track : MIRR ="L"

Off track : MIRR ="H"

This signal is used on the brake circuit (to be described

later) and also as the trigger to turn on track counting

when jumping take place.

The MIRR signal is supplied to the micro computer, too,

for the protection purpose.

A/D

MIRR

CIRCUIT

3T

CIRCUIT

DFCT

CIRCUIT

BOTTOM DETECT

BOTTOM DETECT

PEAK DETECT

LPFS/H

A/D

A/D

76

75

73

3

2

40k

20k

20k

40k

40k

40k

200k

200k

C205

0.1µF

C3T

AGCI

RFO

12k

10k

20k

30k

MIRR

HOLD

Fig.6 : DFCT, MIRR AND 3T DETECTION CIRCUIT

Fig.7 : HOLD OUTPUT WAVEFORM

(When surface defects are present)

Fig.8 : MIRR OUTPUT WAVEFORM

(When an access is made)

5

Surface defects

RFI

HOLD

RFI

MIRR

OFF Track ON Track

Page 6

6

CX-916

10) EFM Circuit

This circuit is used for converting the RF signal to

digital signal consisting of “0” and “1”. The RFO signal

from Pin 75 is externally AC coupled, entered to Pin 74,

then applied to the EFM circuit.

Loss of the RF signal due to scratches or stains on the

disc, or vertical asymmetry of the RF due to variations

in the discs manufactured can’t be eliminated by AC

coupling alone. This circuit, therefore, controls the

reference voltage ASY on the EFM comparator by use

of the fact that “0” and “1” appear fifty fifty in the EFM

signal. By this arrangement, the comparate level is

constantly maintained at almost center of the RFO

signal level. The reference voltage ASY is generated

when the EFM comparator output is passed through

the low pass filter. The EFM signal is output from Pin

71. It is a 2.5 Vp-p amplitude signal centering on REFO.

74

RFI

40k

40k

C206

3900pF

72

71

ASY

EFM

40k

40k

15k75k

2k

R205

10k

R206

39k

C203

0.1µF

C204

3300pF

EFM. SIG

Fig.9 : EFM CIRCUIT

Page 7

7

CX-916

1.2 SERVO SECTION (UPD63710GC :

IC201)

The servo section controls the operations such as error

signal equalizing, in focus, track jump and carriage

move. The DSP is the signal processing section used

for data decoding, error correction and interpolation

processing, among others.

This circuit implements analog to digital conversion of

the FE and TE signals generated on the pre-amplifier,

then outputs them through the servo block as the drive

signal used on the focus, tracking and carriage system.

The EFM signal is decoded on the signal processing

section and finally output via the D/A converter as the

audio signal. The decoding process also generates the

spindle servo error signals which is fed to the spindle

servo block to generate the spindle drive signal.

The focus, tracking, carriage and spindle drive signals

are then amplified on the driver IC BA5985FM (IC301)

and fed to respective actuators and motors.

1) Focus Servo System

The focus servo main equalizer is consisted of the

digital equalizer. Fig.10 shows the focus servo block

diagram.

When implementing the focus close on the focus servo

system, the lens must be brought within the in-focus

range. Therefore, the lens is moved up and down

according to the triangular focus search voltage to find

the focus point. During this time, the spindle motor is

kicked and kept rotating as a set speed.

The servo LSI monitors the FE and RFOK signals and

automatically carries out the focus close at an

appropriate point.

The focus closing is carried out when the following

three conditions are met :

1

The lens approaches the disc from its current

position.

2

RFOK ="H"

3

The FZC signal is latched at high after it has once

crossed the threshold set on the FZD register (Edge

of the FZD).

As the result, the FE ( =REFO) is forced to low.

FE

AMP

DIG.

EQ

82

A+C

B+D

FD

FOP

FOM

IC301

BA5985FM

LENS

IC201 UPD63710GC

85

62

27

16

15

FOCUS SEARCH

TRIANGULAR

WAVE GENERATOR

DAC

CONTROL

A/D

R309

47k

Fig.10 : FOCUS SERVO BLOCK DIAGRAM

Page 8

8

CX-916

When the above conditions are all met and the focus is

closed, the XSI pin goes to low from the current high,

then 40 ms later, the microcomputer begins to monitor

the RFOK signal after it that has been passed through

the low pass filter.

When the RFOK signal is recognized as low, the micro

computer carries out various actions including

protection.

Fig.11 a series of operations carried out relevant to the

focus close (the figure shows the case where focus

close is not available).

You can check the S-curve, search voltage and actual

lens behavior by selecting the Display 01 for the focus

mode select in the test mode, and then pressing the

focus close button.

REFO

FD

LENS POSITION

RELATIVE TO DISC

NEAR

FAR

"JUST FOCUSED"

MD

REFO

Expanding around "Just Focused Point"

REFO

RFI

FOK

FE

FZD

THRESHOLD

LEVEL

FZD

(INTERNAL SIGNAL)

Focus closing would normally take place at these points

XSI

(IN THE EVENT

FOCUS IS

CLOSED)

LEVEL

Fig.11 : FOCUS CLOSE SEQUENCE

Page 9

9

CX-916

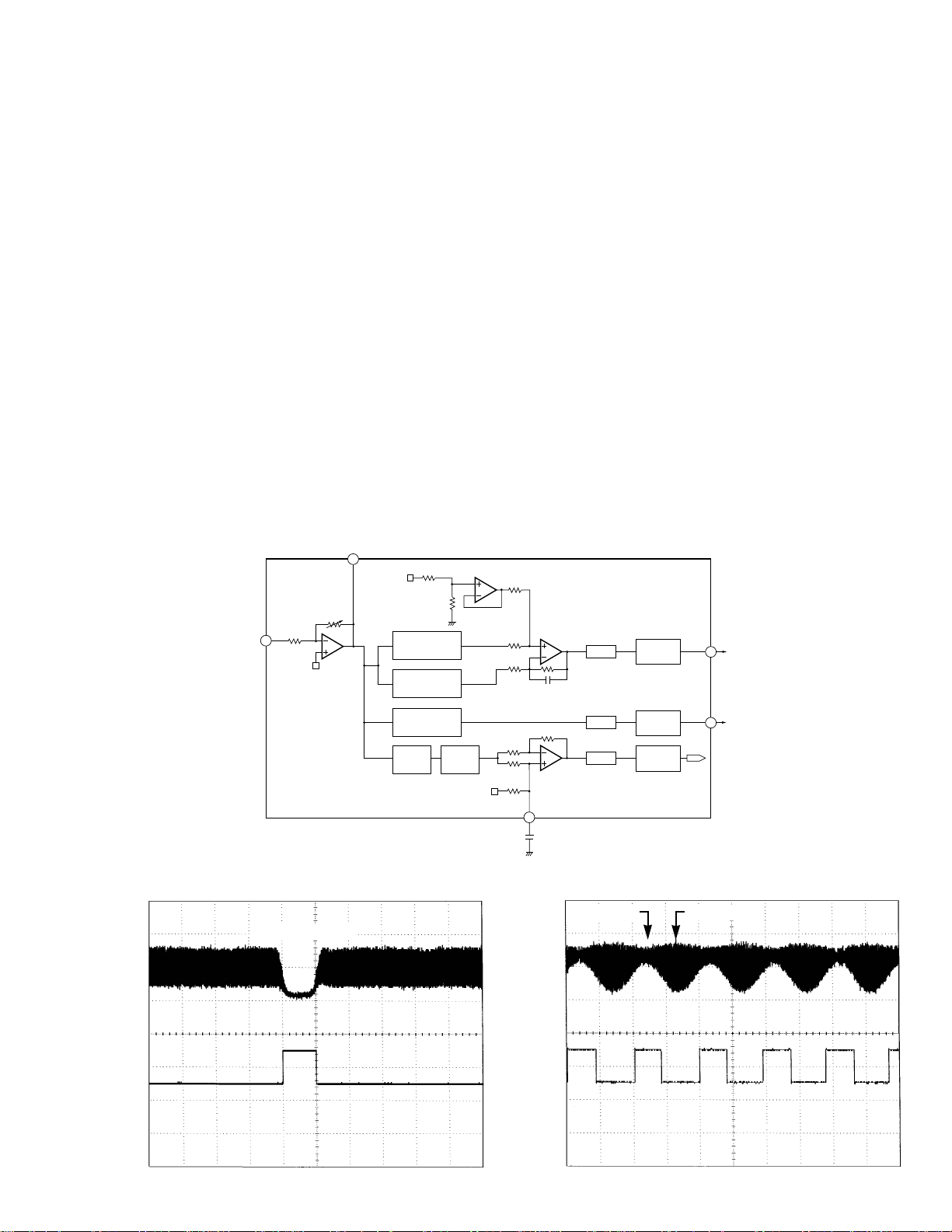

2) Tracking Servo System

The digital equalizer is employed for the main equalizer

on the tracking servo. Fig.12 shows the tracking servo

block diagram.

a) Track jump

When the LSI receives the track jump command from

the microcomputer, the operation is carried out

automatically by the auto sequence function of the LSI.

This system has five types of track jumps used for the

search : 1, 4, 10, 32 and 32 ×3. In the test mode, in

addition to three jumps (1, 32 and 32 ×3), move of the

carriage can be check by mode selection. For track

jumps, the microcomputer sets almost half of tracks (5

tracks for 10 tracks, for instance) and counts the set

number of tracks using the TEC signals. When the

microcomputer has counted the set number of tracks, it

outputs the brake pulse for a fixed period of time

(duration can be specified with the command) to stop

the lens. In this way, the tracking is closed and normal

play is continued.

To improve the servo loop retracting performance just

after the track jump, the brake circuit is turned on for 50

ms after the brake pulse has been terminated to

increase gain of the tracking servo.

Fast forward and reverse operations are realized by

through consecutive signal track jumps. The speed is

about 10 times as fast as that in the normal mode.

TE

AMP

DIG.

EQ

86

F

E

TD

TOP

TOM

IC301

BA5985FM

LENS

IC201 UPD63710GC

87

63

24

17

18

JUMP

PARAMETERS

DAC

CONTROL

A/D

R310

47k

t1

t2

GAIN NORMAL

TD

KICK

BRAKE

TEC

T. BRAKE

EQUALIZER

T. SERVO

CLOSED

OPEN

NORMAL

GAIN UP

OFF

ON

t1

TD

TEC

(10 TRACK)

EQUALIZER

T. BRAKE

SERVO

SD

2.9mS (4.10 TRACK JUMP)

5.8mS (32 TRACK JUMP)

GAIN UP

NORMAL

ON

OFF

OPEN

CLOSED

t2

50mS

t

Fig.12 : TRACKING SERVO BLOCK DIAGRAM

Fig.13 : SINGLE TRACK JUMP

Fig.14 : MULTI-TRACK JUMP

Page 10

10

CX-916

b) Brake Circuit

The servo retracting performance can be deteriorate

during the setup or track jump operation. In this

connection, the brake circuit is used to ensure steady

retract of the tracking servo. The brake circuit detects in

which direction the lens is moving, then slows down its

move by outputting the drive signal that moves the

lens into the opposite direction alone. Track slippage

direction is determined by referencing the TEC and

MIRR signals and their phase.

TEC

TZC

(TEC "SQUARED UP" )

(INTERNAL SIGNAL )

MIRR

MIRR LATCHED AT

TZC EDGES

=

SWITCHING PULSE

EQUALIZER OUTPUT

(SWITCHED)

DRIVE DIRECTION

Note : Equalizer output assumed to hava same phase as TEC.

FORWARD

LENS MOVING FORWARDS

(INNER TRACK TO OUTER)

LENS MOVING BACKWARDS

Time

REVERSE

Fig.15 : TRACKING BRAKE CIRCUIT

Page 11

11

CX-916

3) Carriage Servo System

The carriage servo supplies the tracking equalizer’s

low-frequency component (lens position data) output to

the carriage equalizer, then, after providing a fixed

amount of gain to it, outputs the drive signal from the

LSI. This signal is then applied to the carriage motor via

the driver IC.

When the lens offset reaches a certain level during play,

the entire pickup must be moved into the forward

direction. Therefore, the equalizer gain is set to the

level that allows to generate a voltage higher than the

carriage motor starting voltage. In actual operations, a

certain threshold level is set for the equalizer output by

the servo LSI so that the drive voltage may be output

from the servo LSI only when the equalizer output

exceeds the threshold level. This arrangement helps

reducing power consumption. Also, due to disc

eccentricity or other factors, the equalizer output may

cross the threshold level a number of times. In this

case, the drive voltage output from the LSI will have

pulse-like waveform.

DIG.

EQ

SD

COP

COM

IC301

BA5985FM

CARRIAGE

MOTOR

IC201 UPD63710GC

64

2

14

13

KICK, BRAKE

REGISTERS

DAC

CONTROL

FROM

TRACK. EQ

M

DRIVE ON/OFF THRESHOLD

CARRIAGE MOVED AT THESE POINTS

TRACKING DRIVE

(LOW FREQUENCY)

LENS POSITION

CRG DRIVE

(INSIDE UPD63710GC)

CRG MOTOR VOLTAGE

Fig.16 : CARRIAGE SERVO BLOCK DIAGRAM

Fig.17 : CARRIAGE SIGNAL WAVEFORM

Page 12

12

CX-916

4) Spindle Servo System

The spindle servo has the following modes.

1

Kick :

This mode is used for accelerating the disc rotation

during setup.

2

Offset :

(a) After the kick is over in the setup, this mode is

turned on until changing to rough servo mode.

(b) When focus is lost during play, this mode is

turned on until the focus is restored.

Both of the above are used for maintaining the disc

rotation rate near to the specified rate.

3

Applicable servo :

The CLV servo mode is turned on for the normal

operations.

In the EFM demodulation block, the frame sync

signal and internal counter output signal are

sampled for every WFCK/16 and a signal is produced

for indicating whether or not they are matching.

They are determined to be asynchronous only when

this signal fails to match 8 times in succession. In all

other cases, above two signals are assumed to be

synchronous. In the applicable servo mode, the

retracting servo is automatically selected if the two

signals are synchronous. If not, the regular servo is

automatically selected.

4

Brake :

This mode is turned on when stopping the spindle

motor.

The microcomputer outputs the brake voltage

through the servo LSI. The LSI monitors the EFM

waveform and, if its longest pattern exceeds a

certain interval (if the rotation is sufficiently slow),

the flag is set the LSI and the microcomputer turns

off the brake voltage. When the flag is not up within

a specified period time, the microcomputer switches

the mode from the brake to the stop mode, and

maintains this mode for a fixed period of time. If this

stop mode is continued for a fixed period of time,

the disc will be ejected.

5

Stop :

This mode is used for powering on the system and

the eject operation. When this mode is turned on,

voltage across the spindle motor is 0V.

6

Rough servo :

This mode is used for when the carriage feed

(carriage mode for the long search, etc.) is turned on.

The linear speed is calculated from the EFM

waveform and high or low level is entered to the

spindle equalizer. In the test mode, this mode is also

used for the grating check.

DSP

BLOCK

DIG.

EQ

MD

SOP

SOM

IC301

BA5985FM

SPINDLE

MOTOR

IC201 UPD63710GC

65

5

12

11

DAC

EFM

SIGNAL

M

SPEED ERROR SIGNAL

PHASE ERROR SIGNAL

Fig.18 : SPINDLE SERVO MOTOR BLOCK DIAGRAM

Page 13

13

CX-916

1.3 AUTOMATIC ADJUSTMENT FUNCTIONS

Every circuit adjustment on the CD-LSI of this system is

automated.

Every circuit adjustment is automatically implemented

when the disc is inserted or the CD mode is selected

from the source key. The following describes how the

adjustments are executed.

1) FZD Cancel Setting

This setting is used for executing the focus close

operation without fail.

When power is turned on, the FE offset level is read and

a voltage opposite to this offset value is written to the

CRAM on the IC to cancel the offset. In this manner, the

FZD threshold level can be set to a constant value

(+240mV), thereby ensuring to meet one of the

requirements for the IC to execute the focus close that

“the FZD signal is latched at high”.

2) Automatic Adjustment of TE, FE and RF Offset

Using REFO as the reference, this function adjusts the

pre-amp TE, FE and RF offsets to the respective target

value when power is turned on (targets values of the

TE, FE and RF are 0, 0 and −1V, respectively).

The following is the adjustment procedure :

(1) Respective offset (LD off) is read by the

microcomputer via the servo LSI.

(2) The microcomputer calculates the voltages to be

corrected from the read values, then sets them to

the specified field.

3) Automatic Adjustment of Tracking Balance (T.

BAL)

This adjustment is used for eliminating differences

between the pickup E and F channels outputs by

adjusting gain of the amplifier on the LSI. In the actual

operation, the TE waveform is adjusted so that it may

be vertically symmetric with REFO.

The following is the adjustment procedure :

(1) Make sure the focus close is complete.

(2) Kick the lens in the radial direction to generate the

TE waveform.

(3) At this time, the microcomputer reads the TE signal

offset value (via the servo LSI) being calculated by

the LSI.

(4) The microcomputer determines if the read offset

value is positive, negative or zero.

If the offset value =0, the adjustment is terminated.

If the offset value =A positive or negative value,

gain of the E and F channels amplifiers are modified

according the predetermined rule.

Then above steps (2) through (4) are repeated until the

“Offset value =0” or “Specified limit count” is reached.

4) Automatic Adjustment of FE Bias

This adjustment is intended at maximizing the RFI level

by optimizing the focus point in-play. This adjustment

utilizes the phase difference between the RF waveform

3T level and the focus error signal when disturbance is

applied.

Since disturbance is applied to the focus loop, this

adjustment is designed to take place in the same timing

as the auto gain control (to be described later).

The following is the adjustment procedure :

(1) Disturbance is injected to the focus loop by the

command from the microcomputer (within the servo

LSI).

(2) The LSI detects fluctuation of the RF signal 3T

component level.

(3) The LSI determines relationship between fluctuation

of the 3T component and the injected disturbance to

detect magnitude and direction of the off-focus

introduced.

(4) The microcomputer reads the detected results from

the LSI.

(5) The microcomputer calculates necessary correction,

then hands the calculated value to the bias

adjustment term set on the LSI.

This adjustment is repeated several times, as it is so

with the auto gain control, to ensure higher accuracy.

Page 14

CX-916

5) Focus and Tracking Automatic Gain Control

This function is used for implementing automatic

control of the focus and tracking loop gain.

The following is the adjustment procedure :

(1) Inject disturbance to the servo loop.

(2) Extract the error signal (FE and TE) generated at

when the disturbance is applied to obtain the

signals G1 and G2 via the B.P.F.

(3) The microcomputer reads the G1 and G2 signals via

the LSI.

(4) Based on the necessary correction calculated by the

microcomputer, the LSI performs the loop gain

adjustment.

Above adjustments are repeated several times to

ensure higher adjustment accuracy.

6) Automatic RF Level Adjustment (RFAGC)

This adjustment is used for implementing intended

signal transmission successfully by adjusting

unevenness of the RF signal (RFO) levels, that results

from disc and machine relevant factors, to a target

value. The adjustment is actually done by varying gain

of the amplifier provided between the RFI and RFO.

The following is the adjustment procedure :

(1) Using the command, the microcomputer reads the

output from the RF level detection circuit on the

servo LSI.

(2) Based on the read value, the microcomputer

calculates an amplifier gain that will produce the

target RFO level.

(3) The microcomputer sends the corresponding

command to the servo LSI so that the above gain

value may be set.

This adjustment takes place at the following timing :

• When the focus close alone is completed during the

setup process.

• Just before the setup is completed (just before the

play takes place).

• After the off-focus has been corrected during the play.

7) Adjustment of Pre-Amp Stage Gain

It is used for adjusting the entire RFAMP (FE, TE and RF

amplifiers) to +6dB or +12dB depending on given gain

level when reflected light from the disc is significantly

below the required level due to stained lens. This

phenomena can be noticed when playing back the CDRW.

The following is the adjustment procedure :

When reflected light from disc is judged to be

significantly below the required level during the setup,

set the entire RFAMP to +6dB or +12dB. In this case, if

the gain is modified, the setup have to be repeated

from the first step.

Through the adjustment, if you judged the play

becomes available by setting the entire RFAMP to +6dB,

+

6dB should be selected for the setup next time on.

See the figure below :

Play at +6dB increases due to stained lens or other reasons

(the typical gain is employed for the initial setup)

Time

Gain of entire RFAMP

+ 12dB

+ 6dB

TYP

Play the CD-RW with the gain being set to +12dB

Play is started with +6dB

judging the lens is stained

Fig.19 : CONCEPTUAL DIAGRAM OF PRE-AMP GAIN ADJUSTMENT

14

Page 15

15

CX-916

8) Initial Adjusting Values

All the automatic adjustments are implemented using

the previous adjustment values as the initial values

unless the microcomputer power (the backup power) is

not turned off (though there are some exceptions).

When the backup is turned off, automatic adjustment is

executed based on the initial values rather than the

previous adjustment values.

9) Displaying Coefficients After Adjustment

You can display and check results of some automatic

adjustments (FE and RF offset, FZD cancel and F / T /

RFAGC) from the test mode. The following coefficients

are displayed in each automatic adjustment :

(1) FE and RF offset and FZD cancel

Reference value =32 (The coefficient of 32 indicates

that no adjustment was required).

The results are displayed in multiples of

approximately 40 mV.

An example : When FZD cancel coefficient =35

35 −32 =3

3 ×40 mV =120 mV

Since the corrected value is

approximately +120 mV, the FE offset

before adjustment was −120 mV.

(2) F and T gain adjustment

Reference value =Focus/Tracking =20

A coefficient displayed indicates an amount of

adjustment conducted on the reference value.

An example : When AGC coefficient =40

40/20 =Overall gain has bee doubled

(+6dB). (The original loop gain of 1/2

has been doubled to have the targeted

overall gain.)

(3) RF level adjustment (RFAGC)

Reference value =8

Coefficient =9 to 15 ····· The direction in which the

RF level is increased (the

gain is increased).

Coefficient =7 to 0 ······· The direction in which the

RF level is decreased (the

gain is decreased).

Incrementing or decreasing the coefficient by “1”

varies the gain by 0.7 to 1dB.

Maximum gain =Typically +6.5dB. Coefficient at this

time is 15.

Minimum gain =Typically −6.0dB. Coefficient at this

time is 0.

Page 16

16

CX-916

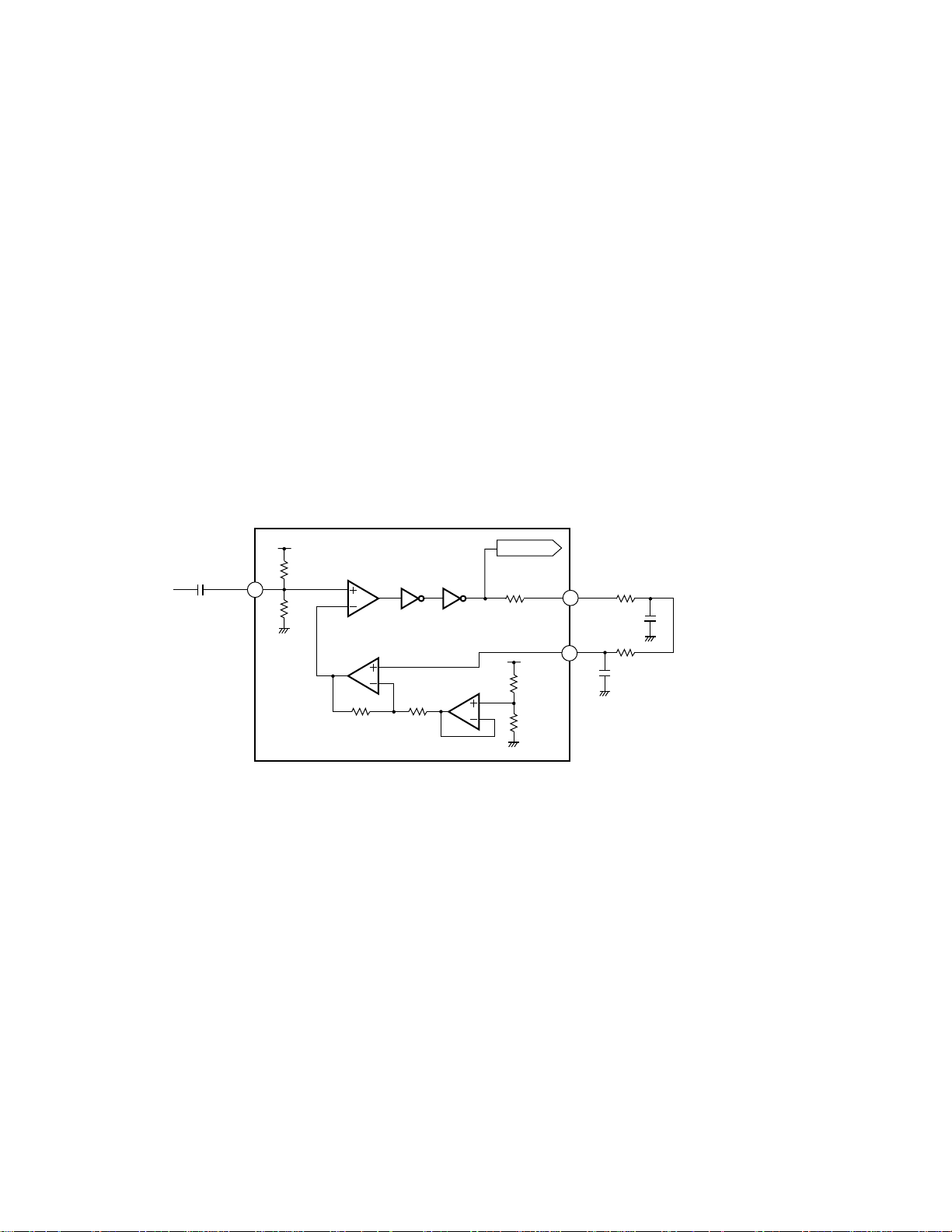

1.4 POWER SUPPLY AND LOADING

SECTION

The power supply of the system uses VD (8.3V) from

the mother board. VD is fed to 5 channel CD driver IC,

5V Reg IC and disc detection LED.

The microcomputer turns on or off the CD driver and

the 5V using “CONT” and “CD5VON”, respectively. The

loading drive is turned on or off by the input signals

“CDEJET” and “CDLOAD”. No control terminal is

provided for turning the loading drive on or off.

IC301

BA5985FM

+5V

LOADING

MOTOR

R801

750

D801

24

5

11

6

7

CN701

VD

CDEJET

CONT

CDLOAD

CD5VON

D802

IC701

BA05SFP

21

8

28

1

1

2

4

9

10

M

R802

750

Fig.20 : POWER SUPPLY AND LOADING SECTION

Page 17

17

CX-916

2. MECHANISM DESCRIPTIONS

- Loading Operation (when a 12 cm disc is used)

1. Insert a 12 cm disc (the sensor turns on the motor

revolution).

2. The disc pushes the Lock Lever in, thereby resetting

the lock currently applied to the Centering Arms.

3. The disc further pushes the Centering Arms in.

4. The right side and left side arms are engaged to

perform centering of the disc.

5. The disc pushes the Disc Detection Arm in, thereby

pushing the Disc Detection Lever forward.

6. Clamping action retracts the Disc Detection Lever

toward forward side, thereby rotating the Relief Arm.

7. The Relief Arm further pushes the Centering Arm in,

thus detaching it from the disc.

- Loading Operation (when a 8 cm disc is used)

1. Insert an 8 cm disc (the sensor turns on the motor

revolution).

2. The disc does not contact against the Lock Lever,

thus centering of the disc is performed by the

Centering Arm being locked.

3. When the right side slot is used, the lock currently

applied to the Centering Arm remains turned on

even if the disc may touch the Lock Lever because

the disc leaves the lever before it reaches the

Centering Arm.

4. Succeeding procedures are the same as that for 12

cm discs.

- Clamping Operation

1. Insert a disc.

2. The Detection Arm pushed forward by the Detection

Lever turns on rotation of the Jump In Rack.

3. The Jump In Rack then engages with the Two Step

Gear and moves toward right.

4. At the same time, the Mode Selector Lever

connected to the Jump In Rack starts moving toward

right, thereby rotating the Lock Arm and resetting

the mechanical lock. The Clamp Up Arm too is

rotated by the above action and, thus, the Clamp Up

Arm now being lifted by shape of the cam of the

Clamp Arm is lowered.

And, the Guide Arm is also moved down because of

shape of the cam of the Mode Selector Lever.

5. By use of the cam shape, the Jump In Rack being

moved toward right retracts the Disc Detection Lever

in forward direction, thereby turning on rotation of

the Relief Arm.

Centering Arm

Centering Arm

Disc Detection Arm

Disc Detection Lever

Relief Arm

Lock Lever

Centering Arm

Centering Arm

Disc Detection Arm

Disc Detection Lever

Relief Arm

Lock Lever

Clamp Up Arm

Two Step

Gear

Disc Detection Arm

Disc Detection Lever

Jump In Rack

Mode Selector Lever

Lock Arm

Page 18

18

CX-916

3. DISASSEMBLY

- Removing the Upper Frame

1. Remove six Springs A, two Springs B and four

Screws.

2. Remove two Tabs situated on rear side of the Upper

Frame, remove two Arms on the front side, then

remove two Tabs on the front side.

- Removing the Carriage Mechanism

1. Disengage the Carriage Mechanism from the two

dampers situated in the front side by driving it up,

then disengage and remove the mechanism from the

two dampers by driving it up aslant into front side

direction.

Note : When assembling the Carriage Mechanism, coat

the dampers with alcohol prior to the assembly.

- Removing the Clamp Arm Assy

1. Remove a Spring A, a B and a Spring C.

2. Drive the Clamp Arm Assy up into rear side direction,

then disengage the arm from its current position

Finally, drive the assembly approximately 45 degrees

upward, then slide the assembly toward right side to

remove it.

B

A

B A

A

A

Arm

Arm

A

B

C

Upper Frame

Carriage Mechanism Section

Clamp Arm Assy Section

A

A

Page 19

19

CX-916

- Removing the Guide Arm Assy

1. Remove a connector, a spring A and B

2. Drive the Guide Arm Assy up aslant into rear side

direction, then remove it from a Pin. Finally, drive the

assembly approximately 45 degrees upward, then

slide the assembly toward left side to remove it.

Note : When assembling the guide arm assembly, route

the cord inside the assembly. In this operation,

care must be exercised so that cord may be

caught by the gear.

- Removing the LO Arm Assy

1. Remove two Pins to dismount the LO Arm Assy.

- Removing the Control Unit and the Spindle

Motor

1. Remove from the connector after mounting the short

pin on the flexible PCB of the pickup unit.

2. Remove two Soldered joints, then remove two

Screws A.

3. Remove two connectors and a Screw B.

4. Disengage the Control Unit from two Tabs, then

dismount the unit by sliding it toward left.

5. Dismount the Spindle Motor.

A

Guide Arm Assy Section

B

Pin

LO Arm Assy Section

Spindle Motor

A

A

Control Unit

Short Pin

B

Page 20

CX-916

- Removing the Loading Motor and Carriage

Motor

1. Remove the Spring and two Screws A.

2. Dismount the Loading Motor.

3. Remove the Belt, a Screw B, two Screws C, a Guide

and a Screw Unit.

4. Dismount the Carriage Motor.

Note : When assembling the Belt, use care so that it

may not be contaminated by grease.

- Removing the Pickup Unit

1. Remove two Screws and a Shaft.

2. Dismount the Pickup Unit.

Pickup Unit

Shaft

C

Guide

B

Screw Unit

Carriage Motor

A

A

C

Belt

Loading Motor

Loading...

Loading...