Philips UDA1340 Service Manual

INTEGRATED CIRCUITS

DATA SH EET

UDA1340

Low-voltage low-power stereo

audio CODEC with DSP features

Preliminary specification

Supersedes data of 1997 May 20

File under Integrated Circuits, IC01

1997 Jul 09

Philips Semiconductors Preliminary specification

Low-voltage low-power stereo audio

CODEC with DSP features

FEATURES

General

• Low power consumption

• 3.0 V power supply

• 256, 384 and 512f

• Small package size (SSOP28)

• ADC plus integrated high pass filter to cancel DC offset

• Overload detector for easy record level control

• Separate power control for ADC and DAC

• Integrated digital filter plus DAC

• No analog post filter required for DAC

• Easy application

• Functions controllable by microcontroller interface.

Multiple format input interface

2

S-bus, MSB-justified and LSB-justified format

• I

compatible

• 1fs input and output format data rate.

DAC digital sound processing

• Digital volume control

• Digital tone control, bass boost and treble

• dB-linear volume and tone control (low microcontroller

load)

• Digital de-emphasis for 32, 44.1 and 48 kHz f

• Soft mute.

system clock

s

s

UDA1340

GENERAL DESCRIPTION

The UDA1340 is a single-chip stereo Analog-to-Digital

Converter (ADC) and Digital-to-Analog Converter (DAC)

with signal processing features employing bitstream

conversion techniques. The low power consumption and

low voltage requirements make the device eminently

suitable for use in low-voltage low-power portable digital

audio equipment which incorporates recording and

playback functions.

The UDA1340 supports the I

lengths of up to 20 bits, the MSB-justified data format with

word lengths of up to 20 bits and the LSB justified serial

data format with word lengths of 16, 18 and 20 bits.

The UDA1340 has special sound processing features in

playback mode, de-emphasis, volume, bass boost, treble,

and soft mute, which can be controlled via the

microcontroller interface.

2

S-bus data format with word

Advanced audio configuration

• Stereo single-ended input configuration

• Stereo line output (under microcontroller volume

control)

• Power-down click prevention circuitry

• High linearity, dynamic range, low distortion.

ORDERING INFORMATION

TYPE

NUMBER

UDA1340M SSOP28 plastic shrink small outline package; 28 leads; body width 5.3 mm SOT341-1

1997 Jul 09 2

NAME DESCRIPTION VERSION

PACKAGE

Philips Semiconductors Preliminary specification

Low-voltage low-power stereo audio

UDA1340

CODEC with DSP features

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Supply

V

DDA(ADC)

V

DDA(DAC)

V

DDO

V

DDD

I

DDA(ADC)

I

DDA(DAC)

I

DDO

I

DDD

I

PD(ADC)

I

PD(DAC)

T

amb

Analog-to-digital converter

V

I(rms)

(THD + N)/S total harmonic distortion plus

S/N signal-to-noise ratio V

α

cs

Digital-to-analog converter

V

o(rms)

(THD + N)/S total harmonic distortion plus

S/N signal-to-noise ratio code = 0; A weighted − 100 − dBA

α

cs

Power performance

P

ADDA

P

DA

P

AD

P

PD

ADC analog supply voltage 2.7 3.0 3.6 V

DAC analog supply voltage 2.7 3.0 3.6 V

operational amplifiers supply voltage 2.7 3.0 3.6 V

digital supply voltage 2.7 3.0 3.6 V

ADC supply current − 4.5 − mA

DAC supply current − 3.5 − mA

operational amplifier supply current − 4 − mA

digital supply current − 6 − mA

digital ADC power-down supply current − 3 − mA

digital DAC power-down supply current − 3 − mA

operating ambient temperature −20 − +85

°

input voltage (RMS value) − 0.8 − V

at 0 dB −−85 −80 dB

noise-to-signal ratio

at −60 dB; A-weighted −−35 −30 dBA

= 0 V; A-weighted − 95 − dBA

i

channel separation − 100 − dB

output voltage (RMS value) − 0.8 − V

at 0 dB −−85 −80 dB

noise-to-signal ratio

at −60 dB; A-weighted −−35 − dBA

channel separation − 100 − dB

power consumption in record and

− 54 − mW

playback mode

power consumption in playback only

− 33 − mW

mode

power consumption in record only

− 27 − mW

mode

power consumption in power-down

− 6 − mW

mode

C

1997 Jul 09 3

Philips Semiconductors Preliminary specification

Low-voltage low-power stereo audio

CODEC with DSP features

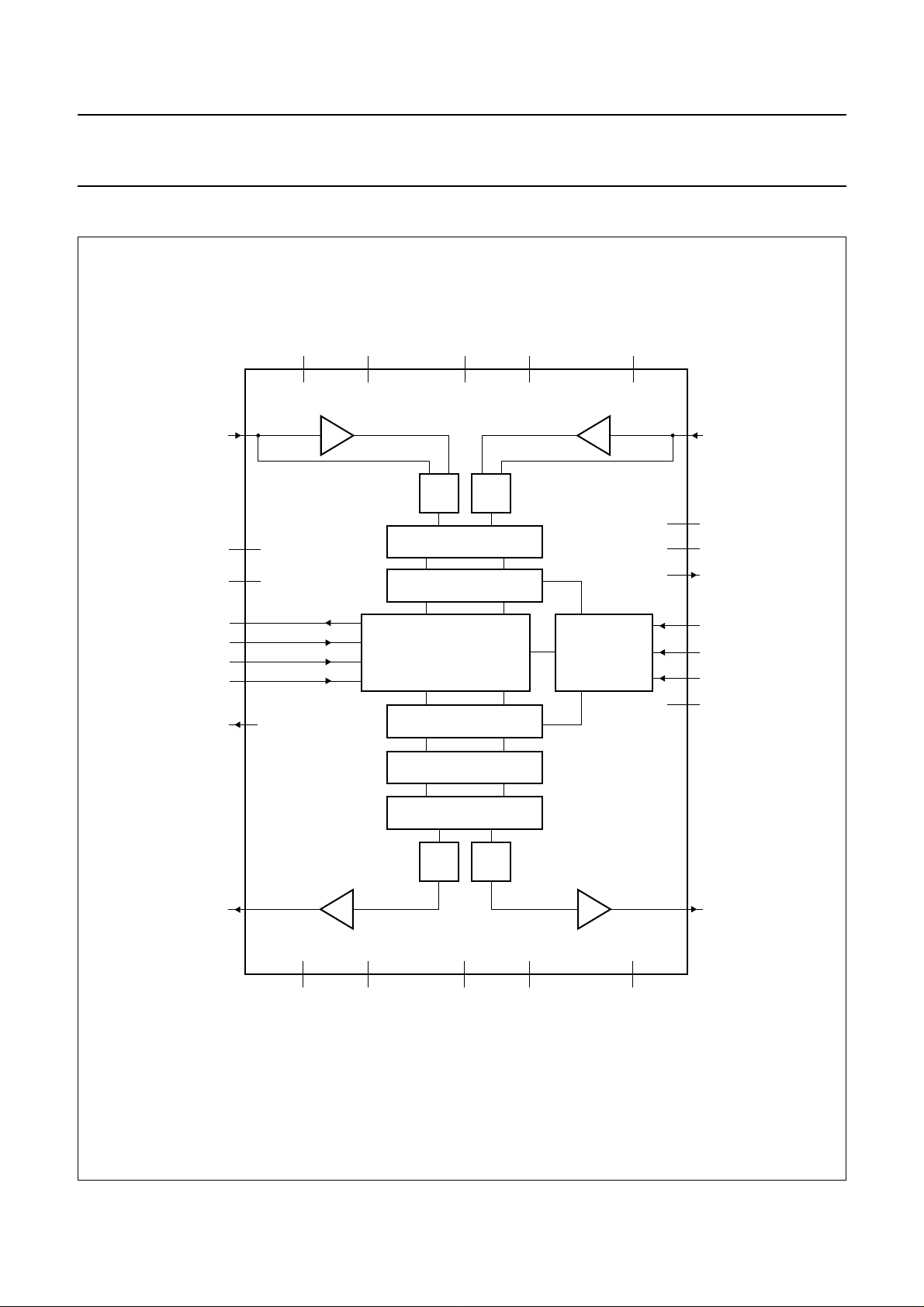

BLOCK DIAGRAM

handbook, full pagewidth

V

V

VINL

DDD

SSD

V

DDA(ADC)VSSA(ADC)

21

3 5

10

11

UDA1340

DC-CANCELLATION FILTER

V

ADCP

76 4

ADC

DECIMATION FILTER

ADC

V

ADCN

V

ref(A)

UDA1340

VINR

8

TEST1

21

TEST2

20

TEST3

DATAO

BCK

WS

DATAI

OVERFL

VOUTL

18

16

17

19

9

26

25 27 23 22

V

DDO

DIGITAL INTERFACE

INTERPOLATION FILTER

V

SSO

DSP FEATURES

NOISE SHAPER

DAC

V

DAC

DDA(DAC)VSSA(DAC)

L3-BUS

INTERFACE

V

ref(D)

13

L3MODE

14

L3CLOCK

15

L3DATA

12

SYSCLK

24

VOUTR

28

MGG839

Fig.1 Block diagram.

1997 Jul 09 4

Philips Semiconductors Preliminary specification

Low-voltage low-power stereo audio

CODEC with DSP features

PINNING

SYMBOL PIN

V

SSA(ADC)

V

DDA(ADC)

1 ADC analog ground

2 ADC analog supply voltage

VINL 3 ADC input left

V

ref(A)

4 ADC reference voltage

VINR 5 ADC input right

V

ADCN

V

ADCP

6 ADC negative reference voltage

7 ADC positive reference voltage

TEST1 8 test control 1 (pull-down)

OVERFL 9 overload flag output

V

V

DDD

SSD

10 digital supply voltage

11 digital ground

SYSCLK 12 system clock 256, 384 or 512f

L3MODE 13 L3-bus mode input

L3CLOCK 14 L3-bus clock input

L3DATA 15 L3-bus data input

BCK 16 bit clock input

WS 17 word selection input

DATAO 18 data output

DATAI 19 data input

TEST3 20 test output

TEST2 21 test control 2 (pull-down)

V

SSA(DAC)

V

DDA(DAC)

22 DAC analog ground

23 DAC analog supply voltage

VOUTR 24 DAC output right

V

DDO

25 operational amplifier supply voltage

VOUTL 26 DAC output left

V

V

SSO

ref(D)

27 operational amplifier ground

28 DAC reference voltage

Description

UDA1340

handbook, halfpage

s

V

SSA(ADC)

V

DDA(ADC)

V

ref(A)

V

ADCN

V

ADCP

TEST1

OVERFL

V

V

SYSCLK

L3MODE

L3CLOCK

VINL

VINR

DDD

SSD

1

2

3

4

5

6

7

8

9

10

11

12

13

UDA1340

MGG838

Fig.2 Pin configuration.

28

27

26

25

24

23

22

21

20

19

18

17

16

1514

V

ref(D)

V

SSO

VOUTL

V

DDO

VOUTR

V

DDA(DAC)

V

SSA(DAC)

TEST2

TEST3

DATAI

DATAO

WS

BCK

L3DATA

1997 Jul 09 5

Philips Semiconductors Preliminary specification

Low-voltage low-power stereo audio

CODEC with DSP features

FUNCTIONAL DESCRIPTION

System clock

The UDA1340 accommodates slave mode only, this

means that in all applications the system devices must

provide the system clock. The system frequency is

selectable. The options are 256f

The system clock must be locked in frequency to the digital

interface input signals.

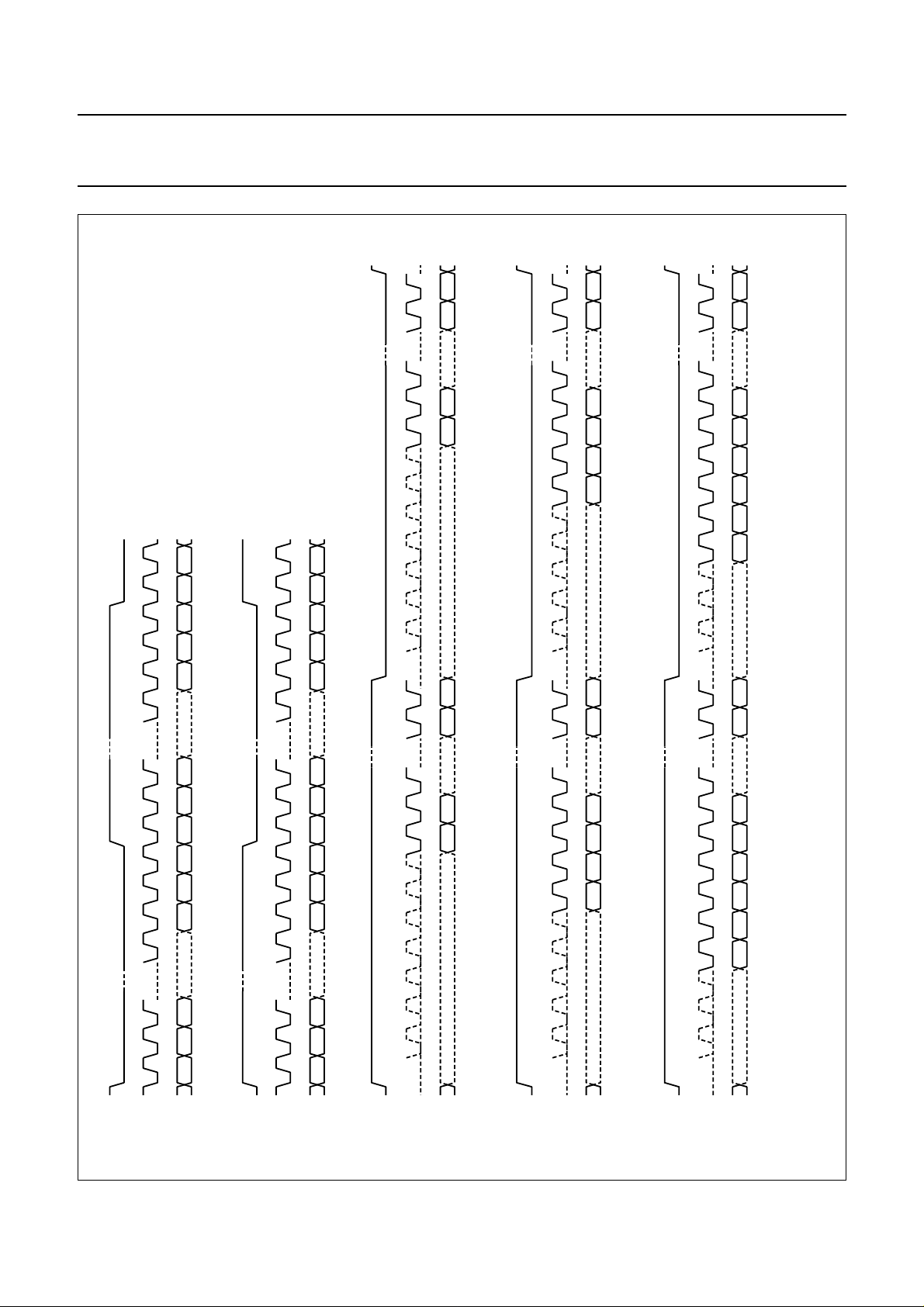

Multiple format input/output interface

The UDA1340 supports the following data input/output

formats:

2

S-bus with data word length of up to 20 bits

• I

• MSB justified serial format with data word length of up to

20 bits

• LSB justified serial format with data word lengths of

16, 18 or 20 bits.

The formats are illustrated in Fig.3. Left and right

data-channel words are time multiplexed.

Analog-to-Digital Converter (ADC)

The stereo ADC of the UDA1340 consists of two

third-order Sigma-Delta modulators. They have a modified

Ritchie-coder architecture in a differential switched

capacitor implementation. The over-sampling ratio is 128.

Decimation filter (ADC)

The decimation from 128f

s

The first stage realizes 3rd-order characteristic. This

filter decreases the sample rate by 16. The second stage,

an FIR filter, consists of 3 half-band filters, each

decimating by a factor of 2.

Table 1 Decimation filter characteristics

ITEM CONDITION VALUE (dB)

Passband Ripple 0 − 0.45f

Stop band >0.55f

Dynamic range 0 − 0.45f

Gain overall −1.16

, 384fs and 512fs.

s

is performed in two stages.

sin x

----------- x

s

s

s

±0.05

−60

108

UDA1340

DC cancellation filter (ADC)

An optional IIR high-pass filter is provided to remove

unwanted DC components. The operation is selected by

the microcontroller via the L3-bus. The filter characteristics

are given in Table 2.

Table 2 DC cancellation filter characteristics

ITEM CONDITION VALUE (dB)

Passband ripple none

Passband gain 0

Droop at 0.00045f

Attenuation at DC at 0.00000036f

Dynamic range 0 − 0.45f

s

s

s

Mute (ADC)

On recovery from power-down or switching on of the

system clock, the serial data output DATAO is held LOW

until valid data is available from the decimation filter. This

time depends on whether the DC cancellation filter is

selected:

DC cancel off: time = , t = 23.2 ms when

f

= 44.1 kHz

s

DC cancel on: time = , t = 279 ms when

f

= 44.1 kHz

s

1024

------------ f

s

12288

----------------

f

s

Overload detection (ADC)

In practice the output is used to indicate whenever the

output data, in either the left or right channel, is greater

than −1 dB (actual figure is −1.16 dB) of the maximum

possible digital swing. When this condition is detected the

OVERFL output is forced HIGH for at least 512f

(11.6 ms at fs= 44.1 kHz). This time-out is reset for each

infringement.

0.031

>40

>110

cycles

s

1997 Jul 09 6

Philips Semiconductors Preliminary specification

Low-voltage low-power stereo audio

CODEC with DSP features

Interpolation filter (DAC)

The digital filter interpolates from 1fsto 128fs by means of

a cascade of a recursive filter and an FIR filter.

Table 3 Interpolation filter characteristics

ITEM CONDITION VALUE (dB)

Passband ripple 0 − 0.45f

Stop band >0.55f

Dynamic range 0 − 0.45f

Gain DC −3.5

Noise shaper (DAC)

The 3rd-order noise shaper operates at 128fs. It shifts

in-band quantization noise to frequencies well above the

audio band. This noise shaping technique enables high

signal-to-noise ratios to be achieved. The noise shaper

output is converted into an analog signal using a filter

stream digital-to-analog converter.

s

s

s

±0.03

−50

108

UDA1340

The Filter Stream DAC (FSDAC)

The FSDAC is a semi-digital reconstruction filter that

converts the 1-bit data stream of the noise shaper to an

analog output voltage. The filter coefficients are

implemented as current sources and are summed at

virtual ground of the output operational amplifier. In this

way very high signal-to-noise performance and low clock

jitter sensitivity is achieved. A post-filter is not needed due

to the inherent filter function of the DAC. On-board

amplifiers convert the FSDAC output current to an output

voltage signal capable of driving a line output.

1997 Jul 09 7

Philips Semiconductors Preliminary specification

Low-voltage low-power stereo audio

CODEC with DSP features

21516 1

RIGHT

MSB LSBB2 B15

RIGHT

UDA1340

215161718 1

LSB

2151617181920 1

B17

RIGHT

MSB B2 B3 B4

LSB

B19

MSB B2 B3 B4 B5 B6

MGG841

book, full pagewidth

321321

RIGHT

>=8 >=8

LEFT

S-BUS

2

INPUT FORMAT I

MSB B2 MSBLSB LSB MSBB2

32

RIGHT

1321

>=8 >=8

LEFT

2

MSB-JUSTIFIED FORMAT

1516 1

LEFT

MSB B2 MSBLSB LSB MSB B2B2

B15

215161718 1

LSB-JUSTIFIED FORMAT 16 BITS

MSB LSBB2

LEFT

LSB

B17

LSB-JUSTIFIED FORMAT 18 BITS

MSB B2 B3 B4

2151617181920 1

LEFT

LSB

B19

LSB-JUSTIFIED FORMAT 20 BITS

Fig.3 Serial interface formats.

MSB B2 B3 B4 B5 B6

WS

BCK

DATA

WS

BCK

DATA

WS

BCK

DATA

1997 Jul 09 8

WS

BCK

DATA

WS

BCK

DATA

Loading...

Loading...