Philips UDA1335H Technical data

查询UDA1335H供应商

INTEGRATED CIRCUITS

DATA SH EET

UDA1335H

Universal Serial Bus (USB) Audio

Playback Recording Peripheral

(APRP)

Preliminary specification

File under Integrated Circuits, IC01

1998 Aug 28

Philips Semiconductors Preliminary specification

Universal Serial Bus (USB) Audio

Playback Recording Peripheral (APRP)

FEATURES

General

• USB stereo audio record and playback system with

20 bits analog-to-digital conversion (with 5 to 55 kHz

sample frequency range) and adaptive 20 bits

digital-to-analog conversion (with 5 to 55 kHz sample

frequency range) with integrated filtering

• USB-compliant audio/HID device

• Supports 12 Mbits/s ‘full speed’ serial data transmission

• Fully automatic ‘Plug-and-Play’ operation

• Supports multiple audio data formats (8, 16 and 24 bits)

• 5.0 and 3.3 V power supply

• Low power consumption

• Efficient power management

• On-chip master clock oscillators, only an external crystal

is required

• High linearity

• Wide dynamic range

• Superior signal-to-noise ratio

• Low total harmonic distortion

• Supports headphone and line output

• Partly programmable USB descriptors and configuration

via the I

Sound processing (for digital-to analog conversion)

• Separate digital volume control for left and right channel

• Soft mute

• Digital bass and treble tone control

• External Digital Sound Processor (DSP) option possible

via standard I

• Selectable clipping prevention

• Selectable Dynamic Bass Boost (DBB)

• On-chip digital de-emphasis.

2

C-bus.

2

S-bus or Japanese digital I/O format

UDA1335H

Document references

•

“USB Specification”

•

“USB Device Class Definition for Audio Devices”

•

“Device Class Definition for Human Interface Devices

(HID)”

•

“USB HID Usage Table”

•

“USB Common Class Specification”

GENERAL DESCRIPTION

The UDA1335H is a stereo CMOS codec incorporating

bitstream converters designed for implementation in

USB-compliant audio peripherals and multimedia audio

applications. The UDA1335H is an adaptive asynchronous

sink USB audio device with a continuous sampling

frequency range from 5 to 55 kHz. It contains a USB

interface, an embedded microcontroller, an

Analog-to-Digital Interface (ADIF) and an Asynchronous

Digital-to-Analog Converter (ADAC).

The USB interface is the interface between the USB, the

ADIF, the ADAC and the microcontroller. The USB

interface consists of an analog front-end and a USB

processor. The analog front-end transforms the differential

USB data into a digital data stream. The USB processor

buffers the incoming and outgoing data from the analog

front-end and handles all low-level USB protocols.

The USB processor selects the relevant data from the

universal serial bus, performs an extensive error detection

and separates control information (input and output) and

audio information (input and output). The control

information is made accessible to the microcontroller.

The audio information received from the PC becomes

available at the digital I/O output or is fed directly to the

ADAC. The audio information to be transmitted to the PC

is delivered by the ADIF or by the digital I

The microcontroller handles the high-level USB protocols,

translates the incoming control requests and manages the

user interface via general purpose pins and an I2C-bus.

.

2

S-bus interface.

1998 Aug 28 2

Philips Semiconductors Preliminary specification

Universal Serial Bus (USB) Audio

Playback Recording Peripheral (APRP)

The firmware for the microcontroller must be located in an

external (E)PROM.

The ADAC enables the wide and continuous range of input

sampling frequencies. By means of a Sample Frequency

Generator (SFG), the ADAC is able to reconstruct the

average sample frequency from the incoming audio

samples. The ADAC also performs the sound processing.

The ADAC consists of a FIFO, a unique audio feature

processing DSP, the SFG, digital upsampling filters, a

variable hold register, a Noise Shaper (NS) and a Filter

Stream DAC (FSDAC) with integrated filter and line output

drivers. The audio information is applied to the ADAC via

the USB processor or via the digital I/O input.

The ADIF consists of an Programmable Gain Amplifier

(PGA), an Analog-to-Digital Converter (ADC) and a

Decimator Filter (DF). An Analog Phase Lock Loop (APLL)

or oscillator is used for clocking the ADIF. The clock

frequency for the ADIF can be controlled via the

microcontroller. Several clock frequencies are possible for

sampling the analog input signal at different sampling

rates.

UDA1335H

Via the digital I/O-bus, an external DSP can be used for

adding extra sound processing features for the audio

received from the PC.

The UDA1335H supports the digital I/O and the I2S-bus

interface, with standard I2S-bus data input format and the

LSB justified serial data input format with word lengths of

16, 18 and 20 bits.

The wide dynamic range of the bitstream conversion

technique used in the UDA1335H guarantees a high audio

sound quality.

APPLICATIONS

• USB monitors

• USB speakers

• USB headsets

• USB telephone/answering machines

• USB links in consumer audio devices.

ORDERING INFORMATION

PACKAGE

TYPE NUMBER

NAME DESCRIPTION VERSION

UDA1335H QFP64 plastic quad flat package; 64 leads (lead length 1.95 mm);

body 14 × 20 × 2.8 mm

SOT319-2

1998 Aug 28 3

Philips Semiconductors Preliminary specification

Universal Serial Bus (USB) Audio

UDA1335H

Playback Recording Peripheral (APRP)

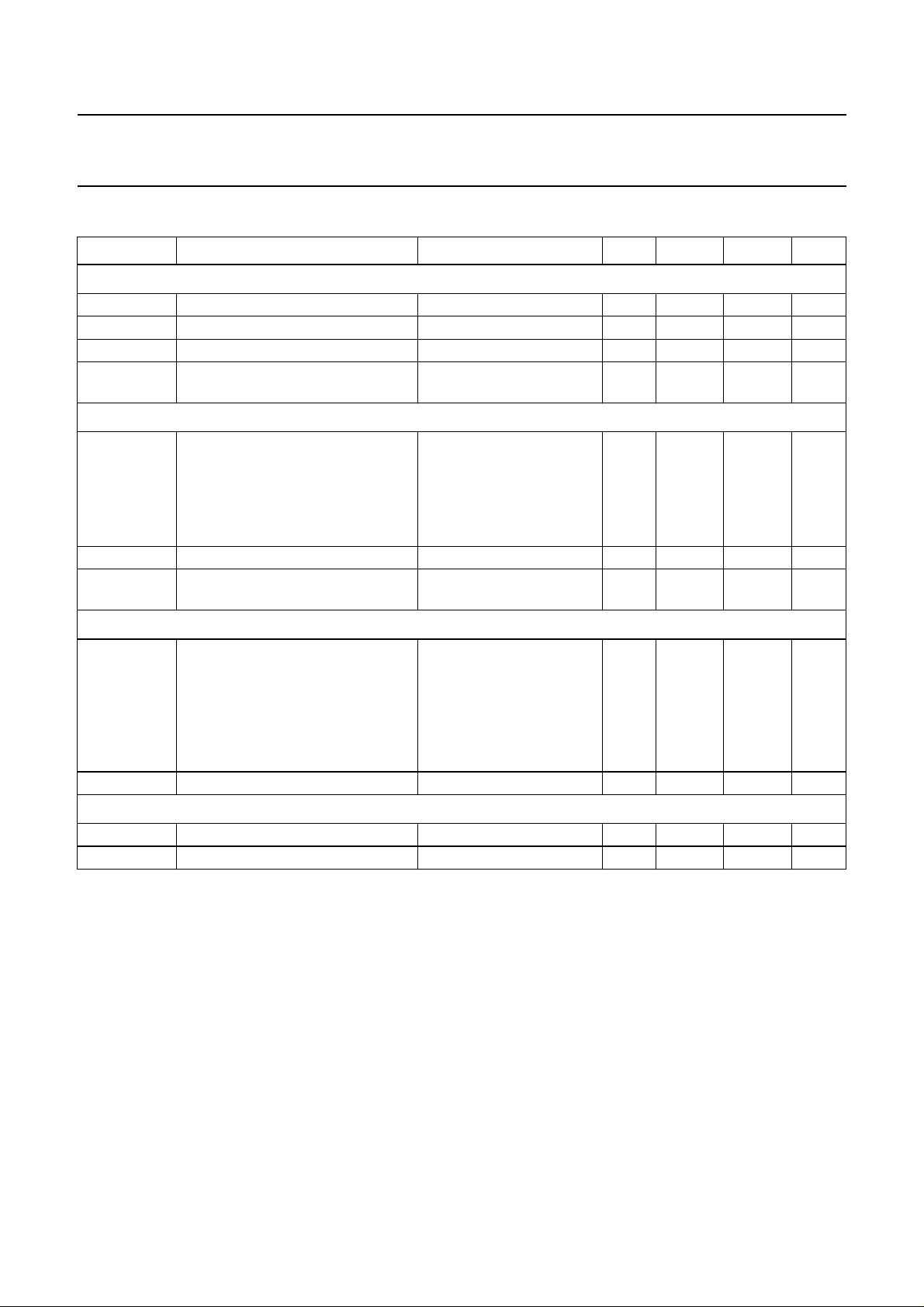

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Supplies

V

DDE

V

DDI

I

DD(tot)

I

DD(tot)(ps)

Dynamic performance DAC

(THD + N)/S total harmonic distortion plus

S/N signal-to-noise ratio at bipolar zero A-weighted at code 0000H 90 95 − dBA

V

o(FS)(rms)

supply voltage periphery 4.75 5.0 5.25 V

supply voltage core 3.0 3.3 3.6 V

total supply current − 60 tbf mA

total supply current in power-saving

note 1 − 360 −µA

mode

= 44.1 kHz; RL=5kΩ

f

s

noise-to-signal ratio

f

= 1 kHz (0 dB) −−90 −80 dB

i

− 0.0032 0.01 %

f

= 1 kHz (−60 dB) −−30 −20 dB

i

− 3.2 10 %

full-scale output voltage

VDD= 3.3 V − 0.66 − V

(RMS value)

Dynamic performance PGA and ADC

(THD + N)/S total harmonic distortion plus

noise-to-signal ratio

S/N signal-to-noise ratio V

General characteristics

f

i(s)

T

amb

audio input sample frequency 5 − 55 kHz

operating ambient temperature 0 25 70 °C

Note

1. Exclusive the I

current which depends on the components connected to the I/O pins.

DDE

f

= 44.1 kHz;

s

PGA gain = 0 dB

f

= 1 kHz; (0 dB);

i

Vi= 1.0 V (RMS)

f

= 1 kHz (−60 dB) −−30 −20 dB

i

−−85 −80 dB

− 0.0056 0.01 %

− 3.2 10.0 %

= 0.0 V 90 95 − dBA

i

1998 Aug 28 4

Philips Semiconductors Preliminary specification

Universal Serial Bus (USB) Audio

Playback Recording Peripheral (APRP)

BLOCK DIAGRAM

handbook, full pagewidth

V

SSX

XTAL1b

XTAL2b

V

DDX

V

DDA3

XTAL2a

XTAL1a

V

SSA3

GP2/DO

GP3/WSO

GP4/BCKO

GP1/DI

GP0/BCKI

GP5/WSI

CLK

27

24

25

26

28

52

53

54

55

63

1

2

13

17

15

OSC

48 MHz

OSC

ADC

TIMING

ANALOG

PLL

D+

8 6

ANALOG FRONT-END

USB-PROCESSOR

UDA1335H

D−

P0.7 to P0.0

7, 5, 3, 64,

62, 60, 58, 56

DIGITAL I/O

P2.0 to P2.7

14, 16, 18, 20,

22, 23, 29, 30

MICRO-

CONTROLLER

V

9

DDI

V

10

SSI

V

11

SSE

V

12

DDE

V

32

DDO

V

33

SSO

V

38

DDA1

V

39

SSA1

V

42

DDA2

V

44

SSA2

SCL

19

SDA

21

PSEN

WS

BCK

ALE

VINL

VINR

VRN

VRP

31

57

DA

59

61

48

EA

50

43

PGA

47

PGA

49

51

INTERFACE

MUX

SAMPLE

I2S-BUS

LEFT

Σ∆ ADC

DECIMATOR

FILTER

FREQUENCY

GENERATOR

UDA1335H

RIGHT

Σ∆ ADC

REFERENCE VOLTAGE

45, 46 41 40

n.c.

V

ref(AD)

AUDIO FEATURE

PROCESSING DSP

UPSAMPLE FILTERS

VARIABLE HOLD REGISTER

3rd-ORDER NOISE SHAPER

V

ref(DA)

FIFO

LEFT

DAC

RIGHT

DAC

TEST

CONTROL

BLOCK

−

+

+

−

35

36

34

37

MBK838

4

SHTCB

TC

RTCB

VOUTL

VOUTR

Fig.1 Block diagram.

1998 Aug 28 5

Philips Semiconductors Preliminary specification

Universal Serial Bus (USB) Audio

UDA1335H

Playback Recording Peripheral (APRP)

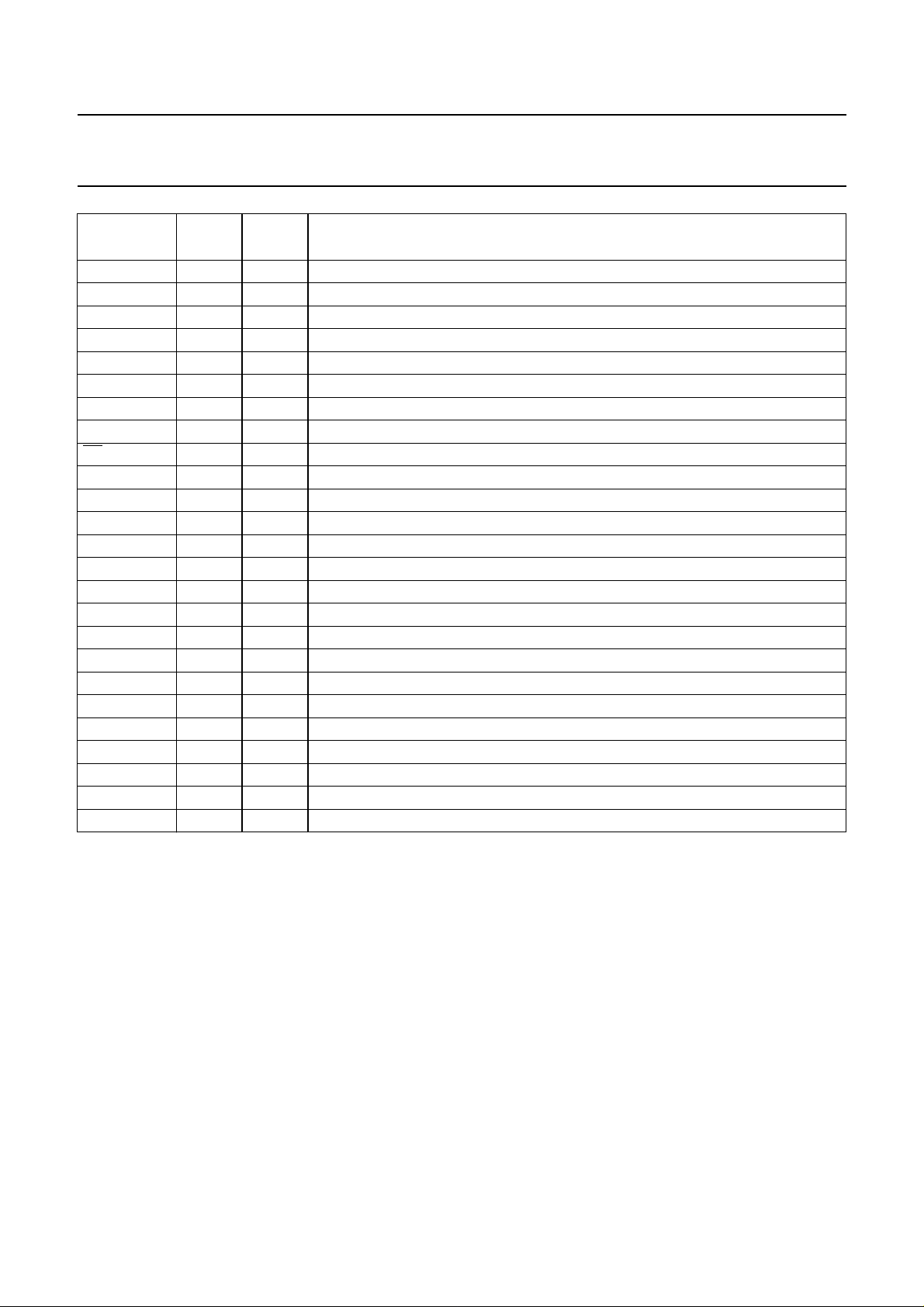

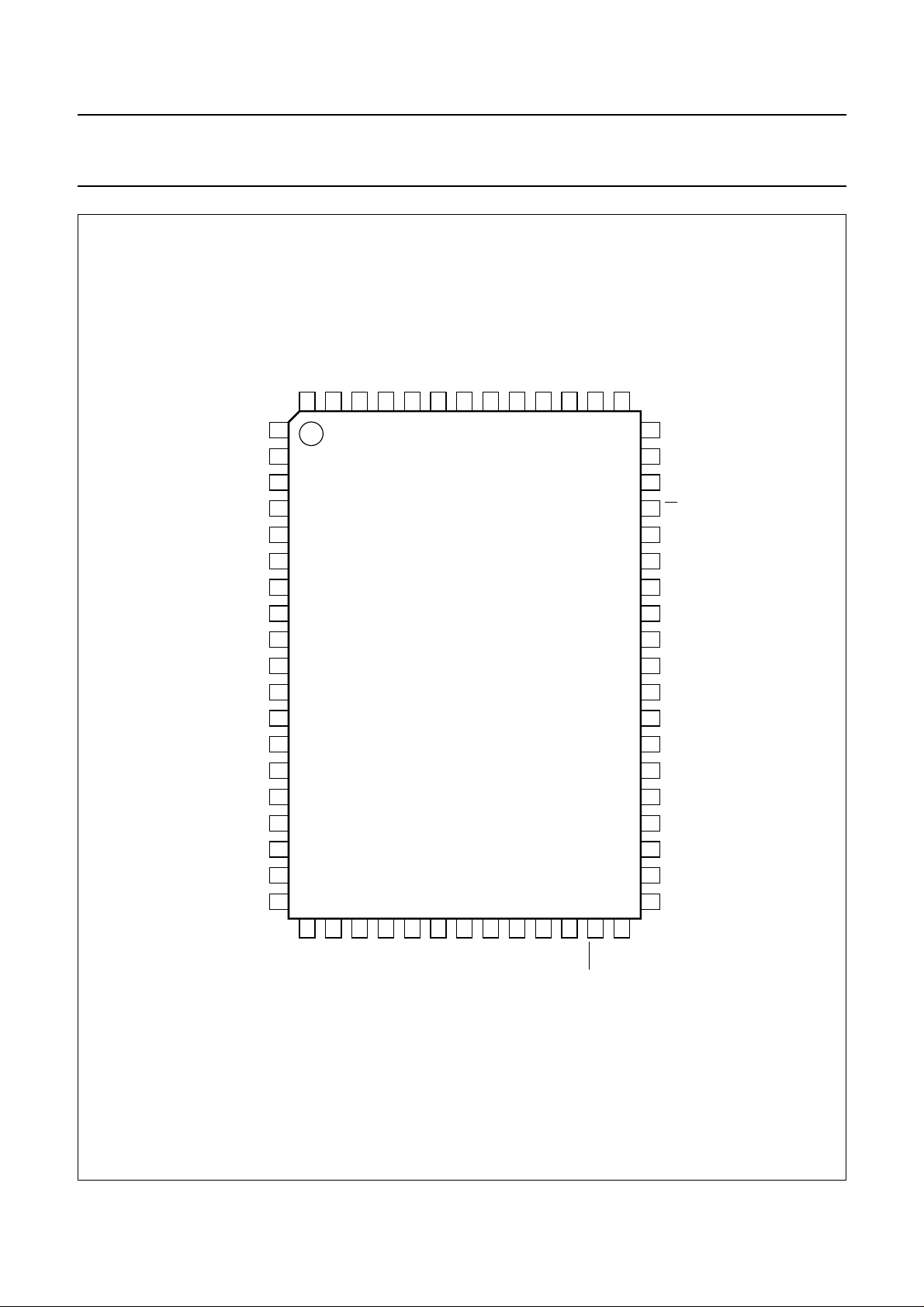

PINNING

SYMBOL

GP3/WSO 1 I/O general purpose pin 3 or word select output

GP4/BCKO 2 I/O general purpose pin 4 or bit clock output

P0.5 3 I/O port 0.5 of the microcontroller

SHTCB 4 I shift clock of the test control block (active HIGH)

P0.6 5 I/O port 0.6 of the microcontroller

D− 6 I/O negative data line of the differential data bus, conforms to the USB standard

P0.7 7 I/O port 0.7 of the microcontroller

D+ 8 I/O positive data line of the differential data bus, conforms to the USB standard

V

DDI

V

SSI

V

SSE

V

DDE

GP1/DI 13 I/O general purpose pin 1 or data input

P2.0 14 I/O port 2.0 of the microcontroller

GP5/WSI 15 I/O general purpose pin 5 or word select input

P2.1 16 I/O port 2.1 of the microcontroller

GP0/BCKI 17 I/O general purpose pin 0 or bit clock input

P2.2 18 I/O port 2.2 of the microcontroller

SCL 19 I/O serial clock line I

P2.3 20 I/O port 2.3 of the microcontroller

SDA 21 I/O serial data line I

P2.4 22 I/O port 2.4 of the microcontroller

P2.5 23 I/O port 2.5 of the microcontroller

V

SSX

XTAL1b 25 I crystal input (analog; 48 MHz)

XTAL2b 26 O crystal output (analog; 48 MHz)

CLK 27 O 48 MHz clock output signal

V

DDX

P2.6 29 I/O port 2.6 of the microcontroller

P2.7 30 I/O port 2.7 of the microcontroller

PSEN 31 I/O program store enable (active LOW)

V

DDO

V

SSO

VOUTL 34 O voltage output left channel

TC 35 I test control input (active HIGH)

RTCB 36 I asynchronous reset input of the test control block (active HIGH)

VOUTR 37 O voltage output right channel

V

DDA1

V

SSA1

PIN

QFP64

I/O DESCRIPTION

9 − digital supply voltage for core

10 − digital ground for core

11 − digital ground for I/O pads

12 − digital supply voltage for I/O pads

2

C-bus

2

C-bus

24 − crystal oscillator ground (48 MHz)

28 − supply crystal oscillator (48 MHz)

32 − supply voltage for operational amplifier

33 − operational amplifier ground

38 − analog supply voltage 1

39 − analog ground 1

1998 Aug 28 6

Philips Semiconductors Preliminary specification

Universal Serial Bus (USB) Audio

Playback Recording Peripheral (APRP)

SYMBOL

V

ref(DA)

V

ref(AD)

V

DDA2

VINL 43 I input signal left channel PGA

V

SSA2

n.c. 45 − not connected

n.c. 46 − not connected

VINR 47 I input signal right channel PGA

EA 48 − external access (active LOW)

VRN 49 I negative reference input voltage ADC

ALE 50 − address latch enable (active HIGH)

VRP 51 I positive reference input voltage ADC

V

DDA3

XTAL2a 53 O crystal output (analog; ADC)

XTAL1a 54 I crystal input (analog; ADC)

V

SSA3

P0.0 56 I/O port 0.0 of the microcontroller

DA 57 I data Input (digital)

P0.1 58 I/O port 0.1 of the microcontroller

WS 59 I word select input (digital)

P0.2 60 I/O port 0.2 of the microcontroller

BCK 61 I bit clock input (digital)

P0.3 62 I/O port 0.3 of the microcontroller

GP2/DO 63 I/O general purpose pin 2 or data output

P0.4 64 I/O port 0.4 of the microcontroller

PIN

QFP64

40 O reference voltage output DAC

41 O reference voltage output ADC

42 − analog supply voltage 2

44 − analog ground 2

52 − supply voltage for crystal oscillator and analog PLL

55 − crystal oscillator and analog PLL ground

I/O DESCRIPTION

UDA1335H

1998 Aug 28 7

Philips Semiconductors Preliminary specification

Universal Serial Bus (USB) Audio

Playback Recording Peripheral (APRP)

handbook, full pagewidth

P0.4

GP2/DO

P0.3

BCK

P0.2WSP0.1DAP0.0

64

63

62

61

60

GP3/WSO

GP4/BCKO

SHTCB

GP1/DI

GP5/WSI

GP0/BCKI

V

V

V

P0.5

P0.6

D−

P0.7

D+

DDI

V

SSI

SSE

DDE

P2.0

P2.1

P2.2

SCL

1

2

3

4

5

6

7

8

9

23

P2.5

UDA1335H

24

SSX

V

10

11

12

13

14

15

16

17

18

19

20

21

22

SDA

P2.3

P2.4

59

58

25

26

XTAL1b

XTAL2b

57

27

CLK

56

28

DDX

V

SSA3

V

55

29

P2.6

XTAL1a

XTAL2a

54

53

30

31

P2.7

PSEN

DDA3

V

52

32

DDO

V

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

MBK841

VRP

ALE

VRN

EA

VINR

n.c.

n.c.

V

SSA2

VINL

V

DDA2

V

ref(AD)

V

ref(DA)

V

SSA1

V

DDA1

VOUTR

RTCB

TC

VOUTL

V

SSO

UDA1335H

Fig.2 Pin configuration.

1998 Aug 28 8

Philips Semiconductors Preliminary specification

Universal Serial Bus (USB) Audio

Playback Recording Peripheral (APRP)

FUNCTIONAL DESCRIPTION

The Universal Serial Bus (USB)

Data and power is transferred via the USB over a 4-wire

cable. The signalling occurs over two wires and

point-to-point segments. The signals on each segment are

differentially driven into a cable of 90 Ω intrinsic

impedance. The differential receiver features input

sensitivity of at least 200 mV and sufficient common mode

rejection.

The analog front-end

The analog front-end is an on-chip generic USB

transceiver. It is designed to allow voltage levels up to V

from standard or programmable logic to interface with the

physical layer of the USB. It is capable of receiving and

transmitting serial data at full speed (12 Mbits/s).

The USB processor

The USB processor forms the interface between the

analog front-end, the ADIF, the ADAC and the

microcontroller. The USB processor consists of:

• The Philips Serial Interface Engine (PSIE)

• The Memory Management Unit (MMU)

• The Audio Sample Redistribution (ASR) module.

DD

UDA1335H

The MMU is the digital back-end of the USB processor.

It handles the temporary data storage of all USB packets

that are received or sent over the bus. Three types of

packets are defined on the USB. These are:

• Token packets

• Data packets

• Handshake packets.

The token packet contains information about the

destination of the data packet. The audio data is

transferred via an isochronous data sink endpoint or

source endpoint and, consequently, no handshaking

mechanism is used. The MMU also generates a 1 kHz

clock that is locked to the USB Start Of Frame (SOF)

token.

The Audio Sample Redistribution (ASR)

The ASR reads the audio samples from the MMU and

distributes these samples equidistant over a 1 ms frame

period. The distributed audio samples are translated by

the digital I/O module to standard I

Japanese digital I/O format. The ASR generates the bit

clock and the word select signal of the digital I/O.

The digital I/O formats the received audio samples to one

of the four specified serial digital audio formats

(I2S-bus, 16, 18 or 20 bits LSB-justified).

2

S-bus format or

The Philips Serial Interface Engine and Memory

Management Unit (PSIE/MMU)

The PSIE/MMU translates the electrical USB signals into

bytes and signals. Depending upon the USB device

address and the USB endpoint address, the USB data is

directed to the correct endpoint buffer on the PSIE/MMU

interface. The data transfer could be of bulk, isochronous,

control or interrupt type. The USB device address is

configured during the enumeration process.

The UDA1335H has four endpoints. These are:

• Control endpoint 0

• Status interrupt endpoint

• Isochronous data sink endpoint

• Isochronous data source endpoint.

The amount of bytes/packet on the control endpoint is

limited by the PSIE/MMU hardware to 8 bytes/packet.

The PSIE is the digital front-end of the USB processor.

This module recovers the 12 MHz USB clock, detects the

USB sync word and handles all low-level USB protocols

and error checking.

The microcontroller

The microcontroller receives the control information

selected from the USB by the USB processor. It handles

the high-level USB protocols and the user interfaces.

The major task of the software process, that is mapped

upon the microcontroller, is to control the different modules

of the UDA1335H in such a way that it behaves as a USB

device.

Therefore the microcontroller:

• Interprets the USB requests and maps them upon the

UDA1335H application

• Controls the internal operation of the UDA1335H, the

digital I/O pins and the GP I/O pins

• Communicates with the external world (external

controller, EEPROM) using the I

GP I/O pins.

The microcontroller does not handle the audio stream.

The UDA1335H will be delivered with USB compliant

firmware. The firmware must be located in an external

(E)PROM.

2

C-bus facility and the

1998 Aug 28 9

Philips Semiconductors Preliminary specification

Universal Serial Bus (USB) Audio

Playback Recording Peripheral (APRP)

The Analog-to-Digital Interface (ADIF)

The ADIF is used for sampling an analog input signal from

a microphone or line input and sending the audio samples

to the USB interface. The ADIF consists of a stereo

Programmable Gain Amplifier (PGA), a stereo

Analog-to-Digital Converter (ADC) and Decimation Filters

(DFs). The sample frequency of the ADC is determined by

the ADC clock (see Section “The timing of the

analog-to-digital interface”). The user can also select a

digital serial input instead of an analog input. In this event

the sample frequency is determined by the continuous WS

clock with a range between 5 to 55 kHz. Digital serial input

is possible with four formats (I2S-bus, 16, 18 or 20 bits

LSB-justified).

The Programmable Gain Amplifier circuit (PGA)

This circuit can be used for a microphone or line input.

The input audio signals can be amplified by 7 different

gains. The preferred gain is selected during start-up of the

device (configuration map).

UDA1335H

The Decimation Filter (DF)

The decimator filter converts the audio data from 128f

down to 1fs with a word width of 8, 16 or 24 bits. This data

will be transmitted over the USB as mono or stereo in

1, 2 or 3 bytes/sample. The decimator filters are clocked

by the ADC clock.

The timing of the analog-to-digital interface

The clock source of the ADIF is the analog PLL or the ADC

oscillator. The preferred clock source can be selected

during start-up of the device (configuration map). The ADC

clock used for the ADC and decimation filters is obtained

by dividing the clock signal coming from the analog PLL or

from the ADC oscillator by a factor Q.

Using the analog PLL the user can select 3 clock

frequencies via the microcontroller.

By connecting the appropriate crystal the user can choose

any clock signal between 8.192 and 14.08 MHz via the

ADC oscillator.

s

The gain settings are given in Table 1.

Table 1 The selectable gains of the PGA

SETTING GAIN UNIT

000 −3dB

001 0 dB

010 3 dB

011 9 dB

100 15 dB

101 21 dB

11X 27 dB

The Analog-to-Digital Converter (ADC)

The stereo ADC of the UDA1335H consists of two

3rd-order Sigma-Delta modulators. They have a modified

Ritchie-coder architecture in a differential switched

capacitor implementation. The oversampling ratio is 128.

Both ADCs can be switched off in power saving mode (left

and right separate). The ADC clock is generated by the

analog PLL or the ADC oscillator.

Table 2 The analog PLL clock output frequencies

FCODE

00 11.2896

01 8.1920

10 12.2880

11 11.2896

The dividing factor Q can be selected via the

microcontroller. With this dividing factor Q the user can

select a range of ADC clock signals allowing several

different sample frequencies (see Table 3).

APLL CLOCK

FREQUENCY (MHz)

1998 Aug 28 10

Philips Semiconductors Preliminary specification

Universal Serial Bus (USB) Audio

UDA1335H

Playback Recording Peripheral (APRP)

Table 3 ADC clock frequencies and sample frequencies based upon using the APLL as a clock source

(analog input topology 1), see note 1.

APLL CLOCK

FREQUENCY (MHz)

8.1920 1 4.096 32

11.2896 1 5.6448 44.1

12.2880 1 6.144 48

Note

1. By using the APLL as a clock source 12 sample frequencies will be reported to the USB host.

DIVIDE FACTOR Q ADC CLOCK FREQUENCY (MHz) SAMPLE FREQUENCY (kHz)

2 2.048 16

4 1.024 8

8 0.512 (not supported) 4 (not supported)

2 2.8224 22.05

4 1.4112 11.025

8 0.7056 5.5125

2 3.072 24

4 1.536 12

8 0.768 6

Table 4 ADC clock frequencies and sample frequencies based upon using the OSCAD as a clock source

(analog input topology 4), see note 1

OSCAD CLOCK

FREQUENCY (MHz)

(2)

f

osc

Notes

1. By using the OSCAD as a clock source, the sample frequency and the Q dividing factor must be filled in the

configuration map. Only this one sample frequency will be reported to the USB host.

2. The oscillator frequency (and therefore the crystal) of OSCAD must be between 8.192 and 14.08 MHz.

3. The Q factor can be 1, 2, 4 or 8.

4. Sample frequencies below 5 kHz and above 55 kHz are not supported.

DIVIDE FACTOR Q ADC CLOCK FREQUENCY (MHz) SAMPLE FREQUENCY (kHz)

(3)

Q

f

/(2Q) f

osc

/(256Q)

osc

(4)

1998 Aug 28 11

Philips Semiconductors Preliminary specification

Universal Serial Bus (USB) Audio

Playback Recording Peripheral (APRP)

The Asynchronous Digital-to-Analog Converter

(ADAC)

The ADAC receives USB audio information from the USB

processor or from the digital I/O-bus. The ADAC is able to

reconstruct the sample clock from the rate at which the

audio samples arrive and handles the audio sound

processing. After the processing, the audio signal is

upsampled, noise-shaped and converted to analog output

voltages capable of driving a line output. The ADAC

consists of:

• A Sample Frequency Generator (SFG)

• FIFO registers

• An audio feature processing DSP

• Two digital upsampling filters and a variable hold

register

• A digital Noise Shaper (NS)

• A Filter Stream DAC (FSDAC) with integrated filter and

line output drivers.

The Sample Frequency Generator (SFG)

The SFG controls the timing signals for the asynchronous

digital-to-analog conversion. By means of a digital PLL,

the SFG automatically recovers the applied sampling

frequency and generates the accurate timing signals for

the audio feature processing DSP and the upsampling

filters.

First-In First-Out (FIFO) registers

The FIFO registers are used to store the audio samples

temporarily coming from the USB processor or from the

digital I/O input. The use of a FIFO (in conjunction with the

SFG) is necessary to remove all jitter present on the

incoming audio signal.

UDA1335H

Table 5 Frequency domains for audio processing by the

DSP

DOMAIN SAMPLE FREQUENCY (kHz)

1 5 to 12

212to25

325to40

440to55

The upsampling filters and variable hold function

After the audio feature processing DSP two upsampling

filters and a variable hold function increase the

oversampling rate to 128f

The noise shaper

A 3rd-order noise shaper converts the oversampled data

to a noise-shaped bitstream for the FSDAC. The in-band

quantization noise is shifted to frequencies well above the

audio band.

The Filter Stream DAC (FSDAC)

The FSDAC is a semi-digital reconstruction filter that

converts the 1-bit data stream of the noise shaper to an

analog output voltage. The filter coefficients are

implemented as current sources and are summed at

virtual ground of the output operational amplifier. In this

way very high signal-to-noise performance and low clock

jitter sensitivity is achieved. A post filter is not needed

because of the inherent filter function of the DAC.

On-board amplifiers convert the FSDAC output current to

an output voltage signal capable of driving a line output.

USB Audio Playback Recording Peripheral (APRP)

descriptors

.

s

The audio feature processing DSP

A DSP processes the sound features. The control and

mapping of the sound features is explained in Section

“Controlling the USB APRP”. Depending on the sampling

rate (f

) the DSP knows four frequency domains in which

s

the treble and bass are regulated. The domain is chosen

automatically.

1998 Aug 28 12

In a typical USB environment the PC has to know which

kind of devices are connected. For this purpose each

device contains a number of USB descriptors. These

descriptors describe, from different points of view (USB

configuration, USB interface and USB endpoint), the

capabilities of a device. Each of them can be requested by

the host. The collection of descriptors is denoted as a

descriptor map. This descriptor map will be reported to the

USB host during enumeration and on request.

The USB descriptors and their most important fields, in

relationship to the characteristics of the UDA1335H are

explained briefly below.

Philips Semiconductors Preliminary specification

Universal Serial Bus (USB) Audio

UDA1335H

Playback Recording Peripheral (APRP)

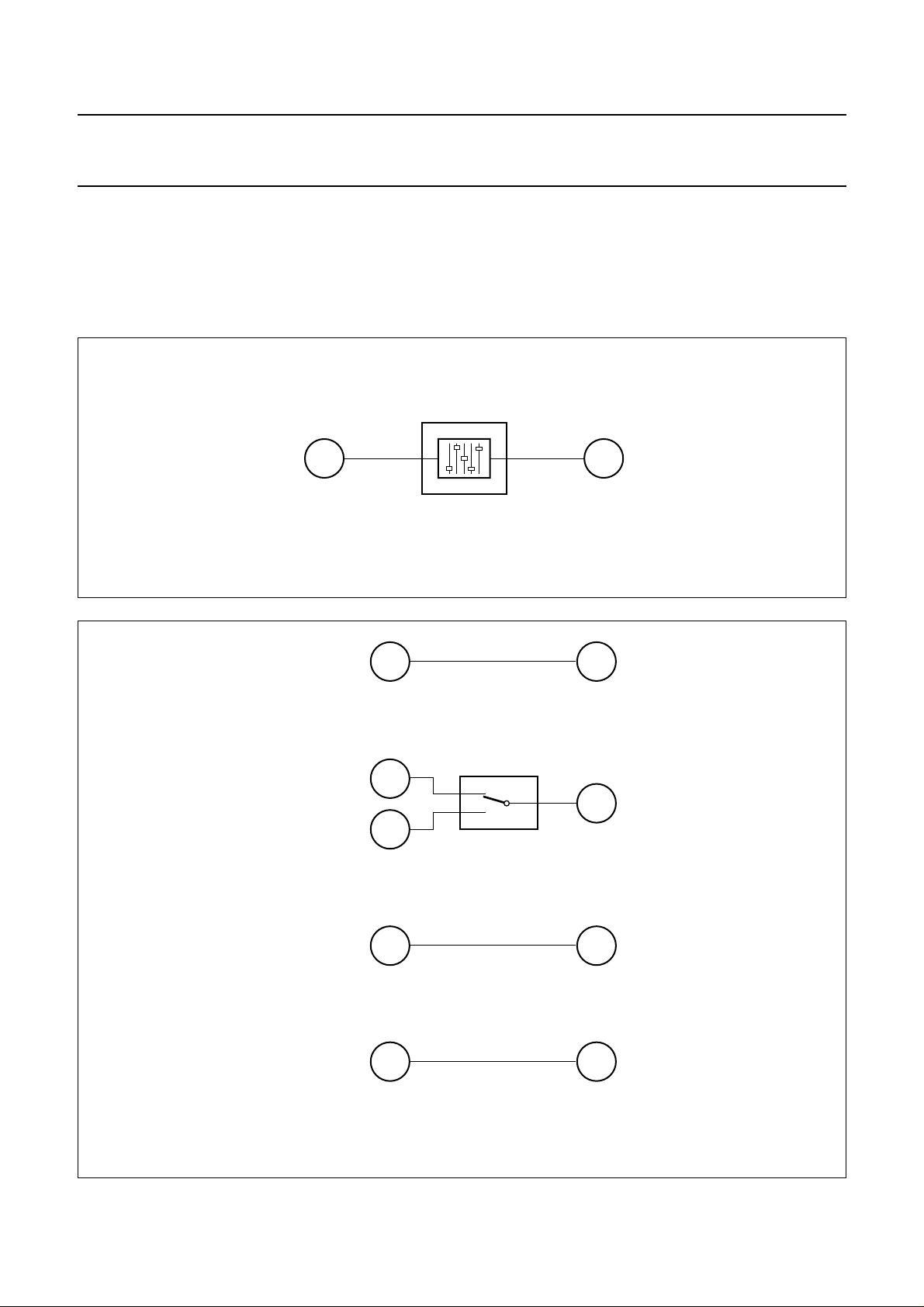

AUDIO FUNCTION TOPOLOGIES

Four audio function Input topologies and two audio function output topologies are supported by the UDA1335H. Each

configuration map can select only one Input and one output topology. The descriptors and the supported requests

depend on the selected topologies in the active configuration map. Figures 3 and 4 illustrate the different audio Input and

output topologies.

handbook, full pagewidth

INPUT TERMINAL

IT

Fig.3 One audio output function topology (with or without bass boost) is supported.

FEATURE UNIT

FU

OUTPUT TERMINAL

OT

MBK530

handbook, full pagewidth

Analog

Input Terminal

IT OT

a. Analog topology 1 (using APLL clock source).

Input Terminal 1

Input Terminal 2

IT

IT

SELECTOR UNIT

SU

b. Analog topology 2.

Digital

Input Terminal

IT OT

c. Digital topology 3.

Analog

Input Terminal

IT OT

d. Analog topology 4 (using OSCAD clock source).

OT

Output

Terminal

Output

Terminal

Output

Terminal

Output

Terminal

MGL437

Fig.4 Four input function topologies are supported.

1998 Aug 28 13

Philips Semiconductors Preliminary specification

Universal Serial Bus (USB) Audio

Playback Recording Peripheral (APRP)

GENERAL DESCRIPTORS

The UDA1335H supports one configuration containing a

control interface, two audio interfaces and a HID interface.

The descriptor map that describes this configuration is

partly fixed and partly programmable.

The programmable part can be retrieved from one of four

configuration maps located in the firmware or from an

I2C-bus EEPROM. At start-up time one of four internal

configuration maps can be selected depending on the

logical combination of GP3 and GP4. It is possible to

overwrite this configuration map with a configuration map

loaded from an I2C-bus EEPROM.

UDIO DEVICE CLASS SPECIFIC DESCRIPTORS

A

The audio device class is partly specified with standard

descriptors and partly with specific audio device class

descriptors. The standard descriptors specify the number

and the type of the interface or endpoint. The UDA1335H

supports 7 different audio modes:

• 8-bit PCM mono or stereo audio data

• 16-bit PCM mono or stereo audio data

• 24-bit PCM mono or stereo audio data

• Zero bandwidth mode.

Each mode is defined as an alternate setting of the audio

interface, selectable with the standard audio streaming

interface descriptor bAlternateSetting field.

The seven alternate settings are described in more detail

by the specific audio device class descriptors.

The UDA1335H supports the input terminal, output

terminal and the feature unit descriptors.

The input and output terminals are not controllable via the

USB. The feature unit provides the basic manipulation of

the incoming logical channels.

The supported sound features are:

• Volume control

• Mute control

• Treble control

• Bass control

• Bass Boost control.

The maximum number of audio data samples within a USB

packet arriving on the isochronous sink endpoint is

restricted by the buffer capacity of this isochronous

endpoint. The maximum buffer capacity is 336 bytes/ms.

UDA1335H

T

HE STANDARD AUDIO STREAMING INTERFACE DESCRIPTOR

FOR THE ISOCHRONOUS DATA SINK ENDPOINT

In this section the descriptors are given for interface 1

which is used for receiving isochronous audio data from

the host.

Although in this specific UDA1335H application no

endpoint control properties can be used on the

isochronous adaptive sink endpoint, the descriptors are

still necessary to inform the host about the definition of this

endpoint: isochronous, adaptive, sink, continuous

sampling frequency (at input side of this endpoint) with a

lower boundary of 5 kHz and an upper boundary of

55 kHz.

The audio class specific descriptors can be requested with

the ‘Get Descriptor: configuration request’, which returns

all the descriptors, except the device descriptor.

For each alternate setting with audio, a maximum

bandwidth is claimed as indicated in the standard

isochronous audio data endpoint descriptor

wMaxPacketSize field. To allow a small overshoot in the

number of audio samples per packet, the top sample

frequency of 55 kHz is taken in the calculation of the

bandwidth for each alternate setting. For each alternate

setting, with its own isochronous audio data endpoint

descriptor, wMaxPacketSize field is then defined as

described in Table 6.

Table 6 Audio bandwidth at each audio mode

ALTERNATE

SETTING

1 8-bit PCM, mono 3800

2 8-bit PCM, stereo 7000

3 16-bit PCM, mono 7000

4 16-bit PCM, stereo E000

5 24-bit PCM, mono A800

6 24-bit PCM, stereo 5001

THE STANDARD AUDIO STREAMING INTERFACE DESCRIPTOR

FOR THE ISOCHRONOUS DATA SOURCE ENDPOINT

Interface 2 is used for sending isochronous audio data to

the host. It has the same alternate settings as interface 1.

AUDIO MODE

wMaxPacketSize

(HEX)

The input terminals can be defined by means of

wTerminalType.

1998 Aug 28 14

Loading...

Loading...